**FEATURES**

• Good CMRR: typ. 50 dB at 60Hz

Wide bandwidth: typ. >8.6 MHz

High slew rate: typ. 12 V/μs

• Several gains: 0 dB, ±3 dB, ±6 dB

- Low distortion: typ. 0.0006% THD

Low cost, self-contained Excellent audio performance

- Low noise: typ. -103 dBu

• Low current: typ. 2 mA

• Industry Standard Pinout

## THAT 1250, 1253, 1256

# APPLICATIONS

- Balanced Audio Line Receivers

- Instrumentation Amplifiers

- Differential Amplifiers

- Precision Summers

- Current Shunt Monitors

# Description

The THAT 1250-series of precision differential amplifiers was designed primarily for use as balanced line receivers for audio applications. Gains of 0 db,  $\pm 3$  dB, and  $\pm 6$  dB are available to suit various applications requirements.

These devices include on-board precision thinfilm resistors which offer good matching and excellent tracking due to their monolithic construction. Manufactured in THAT Corporation's proprietary complementary dielectric isolation (DI) process, the THAT 1250-series provides the sonic benefits of discrete designs with the simplicity, reliability, matching and small size of an integrated solution.

All three versions of the part typically exhibit 50 dB of common-mode rejection. With 12 V/ $\mu$ s slew rate, >8.6 MHz bandwidth, and 0.0006% THD, these devices are sonically transparent. Moreover, current consumption is typically a low 2 mA. Both surface-mount and DIP packages are available.

The THAT 1256 is pin-compatible with the TI INA137 and Analog Devices SSM2143, while the THAT 1250 is pin-compatible with the TI INA134 and Analog Devices SSM2141.

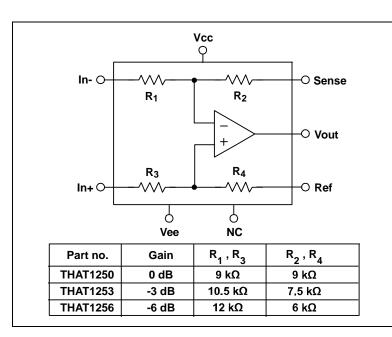

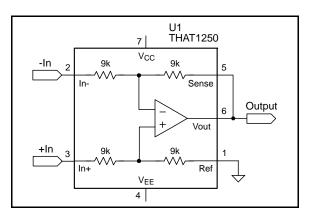

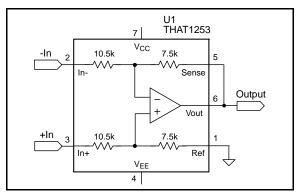

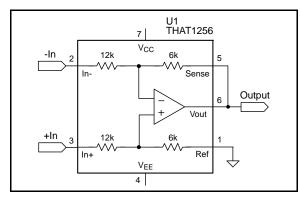

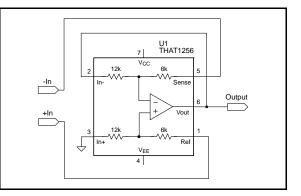

Figure 1. THAT 1250-series equivalent circuit diagram

| Pin Name | DIP Pin | SO Pin |

|----------|---------|--------|

| Ref      | 1       | 1      |

| In-      | 2       | 2      |

| In+      | 3       | 3      |

| Vee      | 4       | 4      |

| Sense    | 5       | 5      |

| Vout     | 6       | 6      |

| Vcc      | 7       | 7      |

| NC       | 8       | 8      |

Table 1. 1250-series pin assignments

| Gain  | Plastic DIP | Plastic SO |

|-------|-------------|------------|

| 0 dB  | 1250P08-U   | 1250S08-U  |

| ±3 dB | 1253P08-U   | 1253S08-U  |

| ±6 dB | 1256P08-U   | 1256S08-U  |

Table 2. Ordering information

# SPECIFICATIONS<sup>1</sup>

# Absolute Maximum Ratings<sup>2,3</sup>

| Supply Voltages (V <sub>CC</sub> - V <sub>EE</sub> ) | 40V                                            | Storage Temperature Range ( $T_{ST}$ )         | -40 to +125 ⁰C |

|------------------------------------------------------|------------------------------------------------|------------------------------------------------|----------------|

| Maximum In₋ or In₊ Voltage                           | $-50V + V_{CC}, 50V + V_{EE}$                  | Operating Temperature Range (T <sub>OP</sub> ) | 0 to +85 °C    |

| Max/Min Ref or Sense Voltage                         | $V_{CC}$ + 0.5V, $V_{EE}$ - 0.5V               | Output Short-Circuit Duration $(t_{SH})$       | Continuous     |

| Maximum Output Voltage (V <sub>OM</sub> )            | $V_{\text{CC}}$ + 0.5V, $V_{\text{EE}}$ - 0.5V | Junction Temperature (T <sub>J</sub> )         | +125 °C        |

|                                                      |                                                |                                                |                |

|                                           | Electrical Characteristics <sup>2,4</sup> |                                                                        |         |        |     |       |

|-------------------------------------------|-------------------------------------------|------------------------------------------------------------------------|---------|--------|-----|-------|

| Parameter                                 | Symbol                                    | Conditions                                                             | Min     | Тур    | Max | Units |

| Supply Current                            | Icc                                       | No signal                                                              |         | 2.0    | 2.8 | mA    |

| Supply Voltage                            | $V_{CC}$ - $V_{EE}$                       |                                                                        | 6       | _      | 36  | V     |

| Input Voltage Range                       | $V_{\text{IN-DIFF}}$                      | Differential (equal and opposite swing)                                |         |        |     |       |

|                                           |                                           | 1250 (0dB gain)                                                        | _       | 21.5   | —   | dBu   |

|                                           |                                           | 1253 (-3dB gain)                                                       | _       | 24.4   | —   | dBu   |

|                                           |                                           | 1256 (-6dB gain)                                                       | _       | 27.5   | —   | dBu   |

|                                           | $V_{IN-CM}$                               | Common Mode                                                            |         |        |     |       |

|                                           |                                           | 1250 (0dB gain)                                                        | _       | 27.5   | —   | dBu   |

|                                           |                                           | 1253 (-3dB gain)                                                       | —       | 29.1   | —   | dBu   |

|                                           |                                           | 1256 (-6dB gain)                                                       |         | 31     | —   | dBu   |

| Input Impedance <sup>5</sup>              | $Z_{\text{IN-DIFF}}$                      | Differential                                                           |         |        |     |       |

|                                           |                                           | 1250 (0dB gain)                                                        | _       | 18     | _   | kΩ    |

|                                           |                                           | 1253 (-3dB gain)                                                       | _       | 21     | _   | kΩ    |

|                                           |                                           | 1256 (-6dB gain)                                                       | _       | 24     | —   | kΩ    |

|                                           | Z <sub>IN-CM</sub>                        | Common Mode                                                            |         |        |     |       |

|                                           |                                           | All versions                                                           | _       | 18     | _   | kΩ    |

| Common Mode Rejection Ratio               | CMRR                                      | Matched source impedances; $V_{CM} = \pm 10 V$                         | /       |        |     |       |

|                                           |                                           | DC                                                                     | 40      | 50     | _   | dB    |

|                                           |                                           | 60Hz                                                                   | 40      | 50     | _   | dB    |

|                                           |                                           | 20kHz                                                                  | —       | 50     | —   | dB    |

| Power Supply Rejection Ratio <sup>6</sup> | PSRR                                      | $\pm 3V$ to $\pm 18V$ ; V <sub>CC</sub> = -V <sub>EE</sub> ; all gains | _       | 90     | _   | dB    |

| Total Harmonic Distortion                 | THD                                       | $V_{IN DIFF} = 10$ dBV, f = 1kHz, BW = 22kHz, RL                       | - 2 40  |        |     |       |

|                                           | עחו                                       | $V_{\text{IN}_{\text{DIFF}}} = 1000V, I = IKHZ, DVV = 22KHZ, KL$       | = 2 KS2 | 0.0006 | _   | %     |

| Output Noise                              | <b>e</b> out                              | 22 Hz to 22kHz bandwidth                                               |         |        |     |       |

|                                           |                                           | 1250 (0dB gain)                                                        | _       | -103   | _   | dBu   |

|                                           |                                           | 1253 (-3dB gain)                                                       | _       | -105   | _   | dBu   |

|                                           |                                           | 1256 (-6dB gain)                                                       | —       | -106   | —   | dBu   |

| Slew Rate                                 | SR                                        | $R_{\text{L}}$ = 2kΩ; $C_{\text{L}}$ = 300 pF, all gains               |         | 12     | _   | V/µs  |

All specifications are subject to change without notice.

Unless otherwise noted, T<sub>A</sub>=25°C, V<sub>CC</sub>=+15V, V<sub>EE</sub>= -15V.

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only; the functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

O dBu = 0.775 Vrms.

While specific rating rate vary expected timened absolute registrance values can vary +25% from the twicel values chown. Input impedance in

4. 0 dou = 0.773 vitus.

5. While specific resistor ratios are very closely trimmed, absolute resistance values can vary ±25% from the typical values show n. Input impedance is monitored by lot sampling.

6. Defined with respect to differential gain.

7. Parameter guaranteed over the entire range of power supply and temperature.

|                              | Electric                           | al Characteristics (                                                                                                                                                                                    | con't) <sup>2</sup> | ,4                                       |                        |                   |

|------------------------------|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------------------------------------------|------------------------|-------------------|

| Parameter                    | Symbol                             | Conditions                                                                                                                                                                                              | Min                 | Тур                                      | Max                    | Units             |

| Small signal bandwidth       | BW-3dB                             | $\begin{array}{l} {\sf R}_{\sf L} = 2k\Omega; \ {\sf C}_{\sf L} = 10 \ {\sf pF} \\ 1250 \ (0{\sf dB} \ {\sf gain}) \\ 1253 \ (-3{\sf dB} \ {\sf gain}) \\ 1256 \ (-6{\sf dB} \ {\sf gain}) \end{array}$ | <br><br>            | 8.6<br>12.2<br>18                        | <br><br>               | MHz<br>MHz<br>MHz |

| Output Gain Error            | G <sub>ER-OUT</sub>                | f = 1 kHz                                                                                                                                                                                               | -0.2                | 0                                        | +0.2                   | dB                |

| Output Voltage Swing         | V <sub>0+</sub><br>V <sub>0-</sub> | $\label{eq:RL} \begin{split} R_{L} &= 2k\Omega; \ C_{L} = 200 \ pF \\ R_{L} &= 2k\Omega; \ C_{L} = 200 \ pF \end{split}$                                                                                | V <sub>cc</sub> -3  | V <sub>CC</sub> -2<br>V <sub>EE</sub> +2 | <br>V <sub>EE</sub> +3 | V<br>V            |

| Output Offset Voltage        | V <sub>OFF</sub>                   | No signal                                                                                                                                                                                               | -10                 | _                                        | +10                    | mV                |

| Output Short Circuit Current | I <sub>SC</sub>                    | $R_L = 0 \ \Omega$                                                                                                                                                                                      |                     | ±25                                      | _                      | mA                |

| Capacitive Load <sup>7</sup> | C∟                                 |                                                                                                                                                                                                         |                     | _                                        | 200                    | pF                |

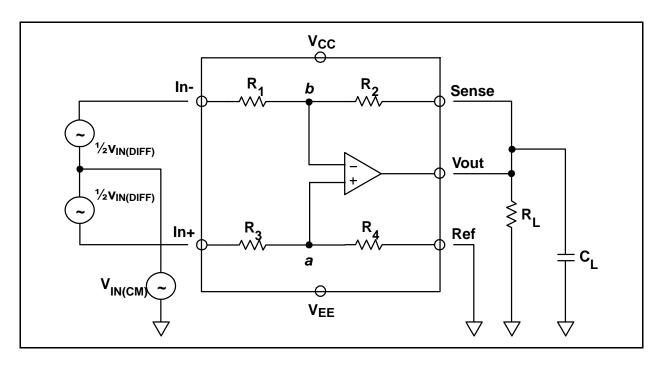

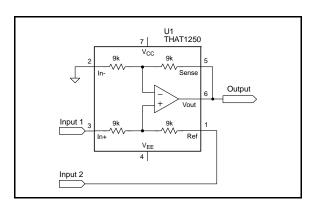

Figure 2. THAT 1250 series test circuit

## **Theory of Operation**

The THAT 1250-series ICs consist of high performance opamps with integrated, thin-film resistors. These designs take full advantage of THAT fully complementary dielectric isolation (DI) process to deliver excellent performance with low current consumption. The devices are simple to apply in many applications.

### Resistor Matching, Values, and CMRR

The 1250-series devices rely upon the inherent matching of silicon-chromium (Si-Cr), thin-film, integrated resistors to achieve a 50 dB common mode rejection ratio and tight gain accuracy. No trimming is performed. As a result of their monolithic construction, the  $R_3/R_4$  ratio generally matches within  $\pm 0.5\%$  of the  $R_1/R_2$  ratio. 0.5% matching is about 50 dB CMRR for the 1256 and 52 dB for the 1250.

However, while the resistor ratios are tightly controlled, the actual value of any individual resistor is not. Lot-to-lot variations of up to  $\pm 30$  % are to be expected.

If higher CMRR is required in a simple input stage, consider the THAT 1240-series ICs. These parts are laser trimmed to improve the inherent precision of our thin-film resistor process. For demanding applications in which the source impedance balance may be less than perfect, the 1200series ICs offer exceptional CMRR performance via a patented method of increasing common-mode input impedance.

#### Input Considerations

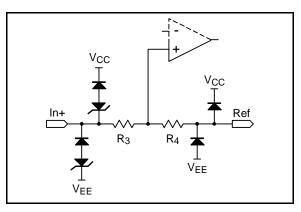

The 1250-series devices are internally protected against input overload via an unusual arrangement of diodes connecting the + and - Input pins to the power supply pins. The circuit of Figure 3 shows the arrangement used for the  $R_3 / R_4$  side; a similar one applies to the other side. The zener diodes prevent the protection network from conducting until an input pin is raised at least 50 V above  $V_{\rm CC}$  or below  $V_{\rm EE}$ . Thus, the protection networks protect the devices without constraining the allowable signal swing at the input pins. The reference (and sense) pins are protected via more conventional reverse-biased diodes which will conduct if these pins are raised above  $V_{\rm CC}$  or below  $V_{\rm EE}$ .

Because the 1250-series devices are input stages, their input pins are of necessity connected to the outside world. This is likely to expose the parts to ESD when cables are connected and disconnected. Our testing indicates that the 1250-series devices will typically withstand application of up to 1,000 volts under the human body ESD model.

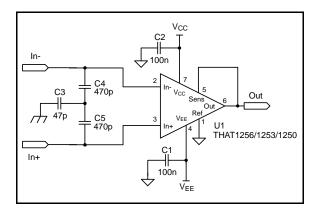

To reduce risk of damage from ESD, and to prevent RF from reaching the devices, THAT recommends the circuit of Figure 4.  $C_3$  through  $C_5$  should be located close to the point where the input signal comes into the chassis, preferably directly on the input connector. The unusual circuit design minimizes the unbalancing impact of differences in the values of  $C_4$  and  $C_5$  by forcing the capacitance from each input to chassis ground to depend primarily on the value of  $C_3$ . The circuit shown is approximately ten times less sensitive to mismatches between  $C_4$  and  $C_5$  than the more conventional approach in which the junction of  $C_4$  and  $C_5$  is grounded directly<sup>6</sup>.

Designers frequently seek to improve RF bypassing through the addition of R-C networks at the inputs (series resistor followed by a capacitor to ground at each input). Generally, THAT recommends keeping any such series resistances under 50W, so as not to upset the intrinsic balance between the 1250's internal  $R_1/R_2$  and  $R_3/R_4$  resistor ratios. Because the internal resistor absolute values are not well controlled, the external resistors can interact with the internal ones in unexpected ways. As an alternative to a resistor as additional build-out impedance, THAT recommends the use of a ferrite bead or balun instead.

If it is necessary to ac-couple the inputs of the 1250-series parts, the coupling capacitors should be sized to present negligible impedance at any frequencies of interest for common mode rejection. Regardless of the type of coupling capacitor chosen, variations in the values of the two capacitors, working against the 1250-series input impedance, can unbalance common mode input signals, converting them to balanced signals which will not be rejected by the CMRR of the devices. For this reason,

THAT recommends dc-coupling the inputs of the 1250-series devices.

### Input Voltage Limitations

When configured, respectively, for -3 dB and -6 dB gain, the 1253 and 1256 devices are capable of accepting input signals above the power supply rails. This is because the internal opamp's inputs connect to the outside world only through the on-chip resistors  $R_1$  through  $R_4$  at nodes a and b as shown in Figure 2. Consider the following analysis.

#### Differential Input Signals

For differential signals  $(v_{IN(DIFF)})$ , the limitation to signal handling will be output clipping. The outputs of all the devices typically clip at within 2V of the supply rails. Therefore, maximum differential input signal levels are directly related to the gain and supply rails.

#### Common-mode Input Signals

For common-mode input signals, there is very little output signal. The limitation on common-mode handling is the point at which the inputs are overloaded. So, we must consider the inputs of the opamp.

For common-mode signals ( $V_{IN(CM)}$ ), the commonmode input current splits to flow through both  $R_1/R_2$ and through  $R_3/R_4$ . Because  $v_b$  is constrained to follow  $V_a$ , we will consider only the voltage at node a.

The voltage at a can be calculated as:

$$v_{a} = v_{IN(CM)} \left[ \frac{R_{4}}{R_{3} + R_{4}} \right].$$

Again, solving for V<sub>IN(CM)</sub>,

$$v_{IN(CM)} = v_{a} \left[ \frac{R_{3} + R_{4}}{R_{4}} \right].$$

For the 1250,  $(R_3 + R_4) / R_4 = 2$ . For the 1253,  $(R_3 + R_4) / R_4 = 2.4$ . For the 1256,  $(R_3 + R_4) / R_4 = 3$ . Furthermore, the same constraints apply to Va as in the differential analysis.

Following the same reasoning as above, the maximum common-mode input signal for the 1250 is  $(2V_{\rm CC} - 4)$  V, and the minimum is  $(2V_{\rm EE} + 4)$  V. For the 1253, these figures are  $(2.4V_{\rm CC} - 4.8)$  V, and  $(2.4V_{\rm EE} + 4.8)$  V. For the 1256, these figures are  $(3V_{\rm CC} - 6)$  V, and  $(3V_{\rm EE} + 6)$  V.

Therefore, for common-mode signals and  $\pm 15$  V rails, the 1250 will accept up to ~26 V in either direction. As an ac signal, this is 52 V peak-peak, 18.4 V rms, or +27.5 dBu. With the same supply rails, the 1253 will accept up to ~31 V in either direction. As an ac signal, this is 62 V peak-peak, 21.9 V rms, or +29 dBu. With the same supply rails, the 1256 will accept up to ~39 V in either direction. As an ac signal, this is 78 V peak-peak, 27.6 V rms, or +31 dBu.

Of course, in the real world, differential and common-mode signals combine. The maximum signal that can be accommodated will depend on the

Figure 3. Representative input protection circuit

superposition of both differential and common-mode limitations.

#### **Output Considerations**

The 1250-series devices are typically capable of supplying 25 mA into a short circuit. While they will survive a short, power dissipation will rise dramatically if the output is shorted. Junction temperature must be kept under 125  $^{\circ}$ C to maintain the devices' specifications.

These devices are stable with up to 300 pF of load capacitance.

#### Power Supply Considerations

The 1250-series parts are not particularly sensitive to the power supply, but they do contain wide bandwidth opamps. Accordingly, small local bypass

Figure 4. RFI and supply bypassing

capacitors should be located within a few inches of the supply pins on these parts, as shown in Figure 4.

#### Selecting a Gain Variation

The three different parts offer different gain structures to suit different applications. The 1256 is customarily configured for -6 dB gain, but by reversing the resistor connections, can also be configured for +6 dB. The 1253 is most often configured for -3 dB gain, but can also be configured for +3 dB. The choice of input gain is determined by the input voltage range to be accommodated, and the power supply voltages used within the circuit.

To minimize noise and maximize signal-to-noise ratio, the input stage should be selected and configured for the highest possible gain that will ensure that maximum-level input signals will not clip the input stage or succeeding stages. For example, with  $\pm 18$  V supply rails, the 1250-series parts have a maximum output signal swing of +23 dBu. In order to accommodate +24 dBu input signals, the maximum gain for the stage is -1 dB. With ±15 V supply rails, the maximum output signal swing is  $\sim +21.1$  dBu; here, -3 dB is the maximum gain. In each case, a 1253 configured for -3 dB gain is the ideal choice. The 1250 (0dB gain only) will not provide enough headroom at its output to support a +24 dBu input signal. The 1256 (configured for -6 dB gain) will increase noise, thus reducing dynamic range, by attenuating the input signal more than necessary to support a +24 dBu input.

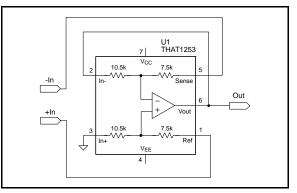

In fact, for most professional audio applications, THAT recommends the -3 dB input configuration possible only with the 1253 in order to preserve dynamic range within a reasonable range of power supply voltages and external headroom limits.

Figure 5. Zero dB line receiver

### Applications

The THAT 1250, 1253, and 1256 are usually thought of as precision differential amplifiers with gains of zero, -3 and -6 dB respectively. These devices are primarily intended as balanced line receivers for audio applications. However, their topology lends itself to other applications as well.

#### **Basic Balanced Receiver Applications**

Figures 5, 6, and 7, respectively, show the THAT 1250, 1256, and 1253 configured as zero, -6 dB, and -3 dB line receivers. Figures 8 and 9, respectively, show the 1253 and 1256 configured as +3 dB and +6 dB line receivers. The higher gains are achieved by swapping the positions of the resistors within each pair in regard to signal input vs. Output. In all five cases, no external resistors are required to set the desired gain.

Figure 10 shows a THAT 1250 configured as a precision summing amplifier. This circuit uses both the In+ and Ref pins as inputs. Because of the good matching between the resistor pairs, the output voltage is precisely equal to the sum of the two input voltages.

#### More Complex Applications

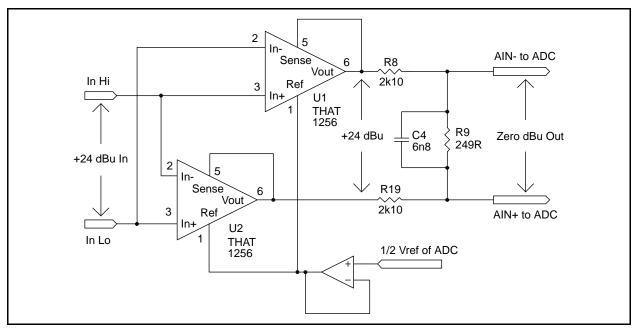

Figure 11 shows a convenient method of driving a typical audio ADC with balanced inputs. This circuit accepts +24 dBu in. By using a pair of THAT 1256 ICs connected in anti-phase, the signal level between their respective outputs is +24 dBu. An attenuator network brings this signal down by 24 dB

Figure 6. -3 dB line receiver

Figure 7. -6 dB line receiver

while attenuating the noise of the line receivers as well.

The output noise of a THAT 1256 is -106 dBu. Since there are two of them, and uncorrelated noise sources add in RMS fashion, the total noise level going into the resistive pad will be 3 dB higher, or -103 dBu. The pad reduces the noise level to -127 dBu at the input to the ADC. The noise density resulting from the line receivers will therefore be

$$e_{n \text{ line receiver}} = \frac{10^{\left(\frac{-127dBu}{20}\right) \times 0.775}}{\sqrt{20kHz}} = 2.45 \frac{nV}{\sqrt{Hz}}$$

The thermal noise of the 249  $\Omega$  resistor is 2.05 nV//Hz. We can assume that the noise contribution of  $R_{\rm s}$  and  $R_{\rm 19}$  will be negligible, and therefore, the total noise density going into the input of the ADC will be

$$e_{n \ total} = \sqrt{(2.45 \frac{nV}{\sqrt{Hz}})^2 + (2.06 \frac{nV}{\sqrt{Hz}})^2} = 3.2 \frac{nV}{\sqrt{Hz}}$$

The noise floor can then be calculated to be

$$Noise_{(dBu)} = 20 \log \frac{3.2 \frac{nV}{\sqrt{Hz}} \times \sqrt{20kHz}}{0.775} = -124.7 \ dBu$$

Figure 12 shows the recommended method for controlling gain in a balanced system. In such circuits, designers are sometimes tempted to keep the signal balanced and use two Voltage Controlled Amplifiers (VCAs) to independently control the gain on each half of the balanced signal. Unfortunately, this can result in common-mode to differential-mode

Figure 8. +3 dB line receiver

Figure 9. +6 dB line receiver

Figure 10. Precision two-input summing circuit

conversion (degrading CMRR) when there are even slight differences in gain between the VCAs. A better approach is to convert the signal to single-ended, alter the gain, and then convert back to balanced.

In Figure 12 we use a THAT 1253 -3 dB line receiver to do the balanced-to-single-ended conversion. The VCA section also has a static gain of -3 dB due to the ratio of  $R_2$  to  $R_3$ . This circuit can accept +24 dBu at its input, since the THAT 1253 output stage is capable of delivering 21 dBu without distortion. Reducing  $R_3$  to 14 k $\Omega$  results in a 3 dB reduction in VCA output noise. This arrangement results in 3 dB greater dynamic range compared to the case where a -6 dB line receiver and a VCA with zero dB static gain are used. After the VCA, the signal is restored to 24 dBu by the THAT 1606.

Figure 11. Circuit for audio ADCs with balanced inputs

Figure 12. Automated gain control of a balanced signal

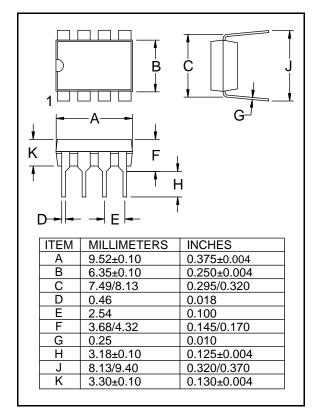

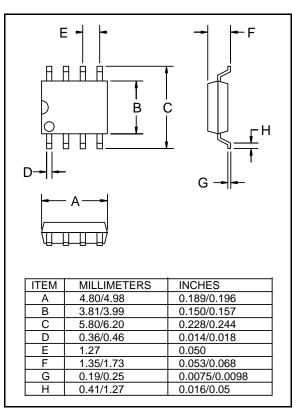

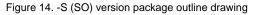

# **Package Information**

The THAT 1250 series is available in 8-pin PDIP and 8-pin surface mount (SOIC) packages. Package dimensions are shown below;

The 1250 series packages are entirely lead-free. The lead-frames are copper, plated with successive layers of nickel, palladium, and gold. This approach makes it possible to solder these devices using leadfree and lead-bearing solders. Neither the lead-frames nor the plastic mold compounds used in the 1250-series contains any hazardous substances as specified in the European Union's Directive on the Restriction of the Use of Certain Hazardous Substances in Electrical and Electronic Equipment 2002/95/EG of January 27, 2003. The surface-mount package is suitable for use in a 100% tin solder process

|                             | ]             | Package Characteristics                  | 5        |              |             |           |

|-----------------------------|---------------|------------------------------------------|----------|--------------|-------------|-----------|

| Parameter                   | Symbol        | Conditions                               | Min      | Тур          | Max         | Units     |

| Through-hole package        |               | See Fig. 13 for dimensions               |          | 8 Pin PDIP   |             |           |

| Thermal Resistance          | $\theta_{JA}$ | DIP package soldered to board            |          | 100          |             | °C/W      |

| Environmental Regulation Co | ompliance     | Complies wi                              | th Janua | ary 27, 2003 | RoHS requ   | uirements |

| Surface mount package       |               | See Fig. 14 for dimensions               |          | 8 Pin SOP    |             |           |

| Thermal Resistance          | $\theta_{JA}$ | SO package soldered to board             |          | 150          |             | °C/W      |

| Soldering Reflow Profile    |               | JE                                       | DEC JE   | SD22-A113    | -D (250 °C) |           |

| Moisture Sensitivity Level  | MSL           | Above-referenced JEDEC soldering profile | Э        | 1            |             |           |

| Environmental Regulation Co | ompliance     | Complies wi                              | th Janua | ary 27, 2003 | RoHS requ   | uirements |

Figure 13. -P (DIP) version package outline drawing

#### ООО "ЛайфЭлектроникс"

ИНН 7805602321 КПП 780501001 Р/С 40702810122510004610 ФАКБ "АБСОЛЮТ БАНК" (ЗАО) в г.Санкт-Петербурге К/С 3010181090000000703 БИК 044030703

Компания «Life Electronics» занимается поставками электронных компонентов импортного и отечественного производства от производителей и со складов крупных дистрибьюторов Европы, Америки и Азии.

С конца 2013 года компания активно расширяет линейку поставок компонентов по направлению коаксиальный кабель, кварцевые генераторы и конденсаторы (керамические, пленочные, электролитические), за счёт заключения дистрибьюторских договоров

Мы предлагаем:

- Конкурентоспособные цены и скидки постоянным клиентам.

- Специальные условия для постоянных клиентов.

- Подбор аналогов.

- Поставку компонентов в любых объемах, удовлетворяющих вашим потребностям.

- Приемлемые сроки поставки, возможна ускоренная поставка.

- Доставку товара в любую точку России и стран СНГ.

- Комплексную поставку.

- Работу по проектам и поставку образцов.

- Формирование склада под заказчика.

- Сертификаты соответствия на поставляемую продукцию (по желанию клиента).

- Тестирование поставляемой продукции.

- Поставку компонентов, требующих военную и космическую приемку.

- Входной контроль качества.

- Наличие сертификата ISO.

В составе нашей компании организован Конструкторский отдел, призванный помогать разработчикам, и инженерам.

Конструкторский отдел помогает осуществить:

- Регистрацию проекта у производителя компонентов.

- Техническую поддержку проекта.

- Защиту от снятия компонента с производства.

- Оценку стоимости проекта по компонентам.

- Изготовление тестовой платы монтаж и пусконаладочные работы.

Тел: +7 (812) 336 43 04 (многоканальный) Email: org@lifeelectronics.ru

### www.lifeelectronics.ru