## **L6258EA**

# PWM controlled high current DMOS universal motor driver

#### **Features**

- Able to drive both windings of a bipolar stepper motor or two DC motors

- Output current up to 1.5A each winding

- Wide voltage range: 12V to 40V

- Four quadrant current control, ideal for microstepping and dc motor control

- Precision PWM control

- No need for recirculation diodes

- TTL/CMOS compatible inputs

- Cross conduction protection

- Thermal shutdow

- Extended low operating temperature range: -40°C

## **Description**

L6258EA is a dual full bridge for motor control applications realized in BCD technology, with the capability of driving both windings of a bipolar stepper motor or bidirectionally control two DC motors.

L6258EA and a few external components form a complete control and drive circuit. It has high efficiency phase shift chopping that allows a very low current ripple at the lowest current control levels, and makes this device ideal for steppers as well as for DC motors.

The power stage is a dual DMOS full bridge capable of sustaining up to 40V, and includes the diodes for current recirculation. The output current capability is 1.5A per winding in continuous mode, with peak start-up current up to 2A. A thermal protection circuitry disables the outputs if the chip temperature exceeds the safe limits.

Table 1. Device summary

|   | Order code | Package   | Packing |

|---|------------|-----------|---------|

| ſ | E-L6258EA  | PowerSO36 | Tube    |

Contents L6258EA

## **Contents**

| 1 | Bloc                | ck diagram                                               | 5  |  |  |

|---|---------------------|----------------------------------------------------------|----|--|--|

| 2 | Fund                | ctional description                                      | 10 |  |  |

|   | 2.1                 | Reference voltage                                        | 11 |  |  |

|   | 2.2                 | Input logic (I0 - I1 - I2 - I3)                          | 12 |  |  |

|   | 2.3                 | Phase input ( PH )                                       | 13 |  |  |

|   | 2.4                 | Triangular generator                                     | 13 |  |  |

|   | 2.5                 | Charge pump circuit                                      | 13 |  |  |

|   | 2.6                 | Current control loop                                     | 14 |  |  |

|   | 2.7                 | Current control loop compensation                        | 15 |  |  |

| 3 | PWN                 | M current control loop                                   | 16 |  |  |

|   | 3.1                 | Open loop transfer function analysis                     | 16 |  |  |

|   | 3.2                 | Power amplifier                                          | 17 |  |  |

|   | 3.3                 | Load attenuation                                         | 18 |  |  |

|   | 3.4                 | Error amplifier and sense amplifier                      | 19 |  |  |

|   | 3.5                 | Effect of the Bemf on the current control loop stability | 22 |  |  |

| 4 | Арр                 | lication information                                     | 24 |  |  |

|   | 4.1                 | Interference                                             | 24 |  |  |

|   | 4.2                 | Motor selection                                          | 25 |  |  |

|   | 4.3                 | Notes on PCB design                                      | 26 |  |  |

| 5 | Ope                 | ration mode time diagrams                                | 27 |  |  |

| 6 | Package information |                                                          |    |  |  |

| 7 | Dovi                | icion history                                            | 21 |  |  |

L6258EA List of tables

## List of tables

| Device summary                 | 1                                                                                                                                                                    |

|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                |                                                                                                                                                                      |

| Pin functions                  | 6                                                                                                                                                                    |

| Electrical characteristics     | 8                                                                                                                                                                    |

| Current levels                 | 2                                                                                                                                                                    |

| Charge pump capacitor's values | 3                                                                                                                                                                    |

| Document revision history      | 1                                                                                                                                                                    |

|                                | Device summary.  Absolute maximum rating.  Pin functions.  Electrical characteristics.  Current levels.  Charge pump capacitor's values.  Document revision history. |

**577**

List of figures L6258EA

## **List of figures**

| Figure 1.  | Block diagram                                 | 5    |

|------------|-----------------------------------------------|------|

| Figure 2.  | Pin connection (top view)                     | 6    |

| Figure 3.  | Thermal characteristics                       | 8    |

| Figure 4.  | Power bridge configuration                    | . 11 |

| Figure 5.  | Current control loop block diagram            | . 12 |

| Figure 6.  | Output comparator waveforms                   | . 14 |

| Figure 7.  | Ax bode plot                                  | . 19 |

| Figure 8.  | Aloop bode plot (uncompensated)               | . 20 |

| Figure 9.  | Aloop bode plot (compensated)                 | . 22 |

| Figure 10. | Electrical model of the load                  |      |

| Figure 11. | Typical application circuit                   | . 25 |

| Figure 12. | Full step operation mode timing diagram       | . 27 |

| Figure 13. | Half step operation mode timing diagram       |      |

| Figure 14. | 4 bit microstep operation mode timing diagram |      |

| Figure 15  | · ·                                           | 30   |

L6258EA Block diagram

## 1 Block diagram

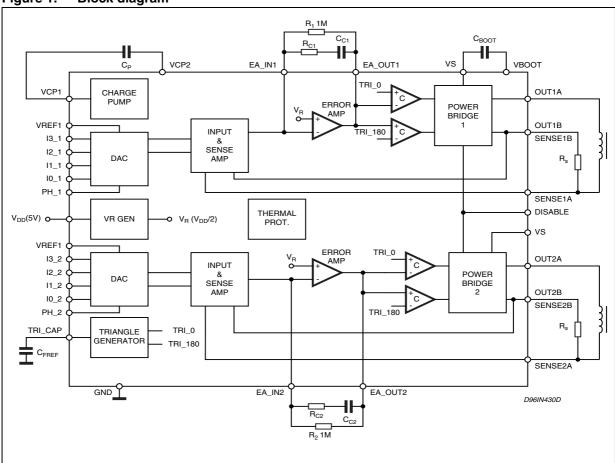

Figure 1. Block diagram

Table 2. Absolute maximum rating

| Parameter                            | Description                                | Value     | Unit |

|--------------------------------------|--------------------------------------------|-----------|------|

| V <sub>s</sub>                       | Supply voltage                             | 45        | V    |

| V <sub>DD</sub>                      | Logic supply voltage                       | 7         | V    |

| V <sub>ref1</sub> /V <sub>ref2</sub> | Reference voltage                          | 2.5       | V    |

| Io                                   | Output current (peak) <sup>(1)</sup>       | 2         | Α    |

| Io                                   | Output current (continuous)                | 1.5       | Α    |

| V <sub>in</sub>                      | Logic input voltage range                  | -0.3 to 7 | V    |

| V <sub>boot</sub>                    | Bootstrap supply                           | 60        | V    |

| V <sub>boot</sub> - V <sub>s</sub>   | Maximum Vgate applicable                   | 15        | V    |

| T <sub>j</sub>                       | T <sub>j</sub> Junction temperature        |           | °C   |

| T <sub>stg</sub>                     | T <sub>stg</sub> Storage temperature range |           | °C   |

<sup>1.</sup> This current is intended as not repetitive current for max. 1 second.

5/

Block diagram L6258EA

Figure 2. Pin connection (top view)

Table 3. Pin functions

| Pin # | Name             | Description                                                                                                                                                        |  |

|-------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1, 36 | PWR_GND          | Ground connection (1). They also conduct heat from die to printed circuit copper.                                                                                  |  |

| 2, 17 | PH_1, PH_2       | These TTL compatible logic inputs set the direction of current flow through the load. A high level causes current to flow from OUTPUT A to OUTPUT B.               |  |

| 3     | I <sub>1_1</sub> | Logic input of the internal DAC (1). The output voltage of the DAC is a percentage of the Vref voltage applied according to the thruth <i>Table 5 on page 12</i> . |  |

| 4     | l <sub>0_1</sub> | See pin 3                                                                                                                                                          |  |

| 5     | OUT1A            | Bridge output connection (1)                                                                                                                                       |  |

| 6     | DISABLE          | Disables the bridges for additional safety during switching. When not connected the bridges are enabled                                                            |  |

| 7     | TRI_cap          | Triangular wave generation circuit capacitor. The value of this capacitor defines the output switching frequency                                                   |  |

L6258EA Block diagram

Table 3. Pin functions (continued)

| Pin #  | Name                                  | Description                                                                                                                                                                  |  |

|--------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 8      | V <sub>DD</sub> (5V)                  | Supply voltage input for logic circuitry                                                                                                                                     |  |

| 9      | GND                                   | Power ground connection of the internal charge pump circuit                                                                                                                  |  |

| 10     | V <sub>CP1</sub>                      | Charge pump oscillator output                                                                                                                                                |  |

| 11     | V <sub>CP2</sub>                      | Input for external charge pump capacitor                                                                                                                                     |  |

| 12     | V <sub>BOOT</sub>                     | Overvoltage input for driving of the upper DMOS                                                                                                                              |  |

| 13, 31 | V <sub>S</sub>                        | Supply voltage input for output stage. They are shorted internally                                                                                                           |  |

| 14     | OUT2A                                 | Bridge output connection (2)                                                                                                                                                 |  |

| 15     | I <sub>0_2</sub>                      | Logic input of the internal DAC (2). The output voltage of the DAC is a percentage of the VRef voltage applied according to the truth <i>Table 5 on page 12</i> .            |  |

| 16     | I <sub>1_2</sub>                      | See pin 15                                                                                                                                                                   |  |

| 18, 19 | PWR_GND                               | Ground connection. They also conduct heat from die to printed circuit copper                                                                                                 |  |

| 20, 35 | SENSE2, SENSE1                        | Negative input of the transconductance input amplifier (2, 1)                                                                                                                |  |

| 21     | OUT2B                                 | Bridge output connection and positive input of the tranconductance (2)                                                                                                       |  |

| 22     | l <sub>3_2</sub>                      | See pin 15                                                                                                                                                                   |  |

| 23     | l <sub>2_2</sub>                      | See pin 15                                                                                                                                                                   |  |

| 24     | EA_OUT_2                              | Error amplifier output (2)                                                                                                                                                   |  |

| 25     | EA_IN_2                               | Negative input of error amplifier (2)                                                                                                                                        |  |

| 26, 28 | V <sub>REF2</sub> , V <sub>REF1</sub> | Reference voltages for the internal DACs, determining the output current value. Output current also depends on the logic inputs of the DAC and on the sensing resistor value |  |

| 27     | SIG_GND                               | Signal ground connection                                                                                                                                                     |  |

| 29     | EA_IN_1                               | Negative input of error amplifier (1)                                                                                                                                        |  |

| 30     | EA_OUT_1                              | Error amplifier output (1)                                                                                                                                                   |  |

| 32     | l <sub>2_1</sub>                      | See pin 3                                                                                                                                                                    |  |

| 33     | I <sub>3_1</sub>                      | See pin 3                                                                                                                                                                    |  |

| 34     | OUT1B                                 | Bridge output connection and positive input of the tranconductance (1)                                                                                                       |  |

Note:

The number in parenthesis shows the relevant Power Bridge of the circuit. Pins 18, 19, 1 and 36 are connected together.

7/32

Block diagram L6258EA

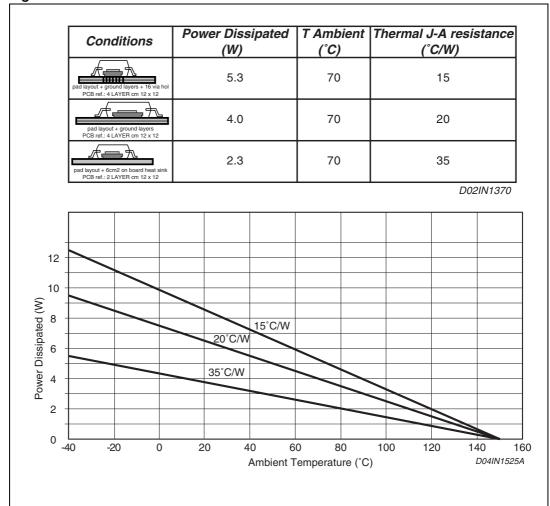

Figure 3. Thermal characteristics

Table 4. Electrical characteristics  $(V_S = 40V; V_{DD} = 5V; T_j = 25^\circ; unless otherwise specified.)$

| Parameter            | Description                       | Test condition             | Min.              | Тур. | Max.               | Unit |

|----------------------|-----------------------------------|----------------------------|-------------------|------|--------------------|------|

| V <sub>S</sub>       | Supply voltage                    |                            | 12                |      | 40                 | V    |

| $V_{DD}$             | Logic supply voltage              |                            | 4.75              |      | 5.25               | V    |

| V <sub>BOOT</sub>    | Storage voltage                   | V <sub>S</sub> = 12 to 40V | V <sub>S</sub> +6 |      | V <sub>S</sub> +12 | V    |

| V <sub>Sense</sub>   | Max drop across sense resistor    |                            |                   |      | 1.25               | V    |

| V <sub>S(off)</sub>  | Power off reset                   | Off threshold              | 6                 |      | 7.2                | V    |

| V <sub>DD(off)</sub> | Power off reset                   | Off threshold              | 3.3               |      | 4.1                | V    |

| I <sub>S(on)</sub>   | V <sub>S</sub> quiescent current  | Both bridges ON, no load   |                   |      | 15                 | mA   |

| I <sub>S(off)</sub>  | V <sub>S</sub> quiescent current  | Both bridges OFF           |                   |      | 7                  | mA   |

| I <sub>DD</sub>      | V <sub>DD</sub> operative current |                            |                   |      | 15                 | mA   |

577

L6258EA Block diagram

Table 4. Electrical characteristics (continued)

( $V_S = 40V$ ;  $V_{DD} = 5V$ ;  $T_i = 25^\circ$ ; unless otherwise specified.)

| Parameter                                 | Description                                                                   | Test condition                                                                     | Min. | Тур. | Max.                | Unit |

|-------------------------------------------|-------------------------------------------------------------------------------|------------------------------------------------------------------------------------|------|------|---------------------|------|

| ΔT <sub>SD-H</sub>                        | Shut down hysteresis                                                          |                                                                                    |      | 25   |                     | °C   |

| T <sub>SD</sub>                           | Thermal shutdown                                                              |                                                                                    |      | 150  |                     | °C   |

| f <sub>osc</sub>                          | Triangular oscillator frequency <sup>(1)</sup>                                | C <sub>FREF</sub> = 1nF                                                            | 12.5 | 15   | 18.5                | KHz  |

| TRANSISTO                                 | ORS                                                                           |                                                                                    | I.   |      | I.                  | II.  |

| I <sub>DSS</sub>                          | Leakage current                                                               | OFF State                                                                          |      |      | 500                 | μΑ   |

| R <sub>ds(on)</sub>                       | On resistance                                                                 | ON state                                                                           |      | 0.6  | 0.75                | W    |

| V <sub>f</sub>                            | Flywheel diode voltage                                                        | If =1.0A                                                                           |      | 1    | 1.4                 | V    |

| CONTROL                                   | LOGIC                                                                         |                                                                                    |      |      |                     |      |

| V <sub>in(H)</sub>                        | Input voltage                                                                 | All Inputs                                                                         | 2    |      | $V_{DD}$            | V    |

| V <sub>in(L)</sub>                        | Input voltage                                                                 | All inputs                                                                         | 0    |      | 0.8                 | V    |

| I <sub>in</sub>                           | Input current (2)                                                             | 0 - 1/ - 51/                                                                       | -150 |      | +10                 | μА   |

| I <sub>dis</sub>                          | Disable pin input current                                                     | $0 < V_{in} < 5V$                                                                  | -10  |      | +150                | μΑ   |

| V <sub>ref1</sub> / <sub>ref2</sub>       | Reference voltage                                                             | Operating                                                                          | 0    |      | (3)                 | V    |

| I <sub>ref</sub>                          | V <sub>ref</sub> terminal input current                                       | V <sub>ref</sub> = 1.25                                                            | -2   |      | 5                   | μΑ   |

| FI = V <sub>ref</sub> /V <sub>sense</sub> | PWM loop transfer ratio                                                       |                                                                                    |      | 2    |                     |      |

| V <sub>FS</sub>                           | $V_{FS}$ DAC full scale precision $V_{ref} = 2.5 V I_0 / I_1 / I_2 / I_3 = L$ |                                                                                    | 1.23 |      | 1.34                | V    |

|                                           |                                                                               | $V_{ref} = 2.5V I_0/I_1/I_2/I_3 = H$                                               | -30  |      | +30                 | mV   |

| V <sub>offset</sub>                       | Current loop offset                                                           | $V_{ref} = 2V I_0/I_1/I_2/I_3 = H;$<br>$T_j = -40 \text{ to } 125^{\circ}\text{C}$ | -60  |      | +60                 | mV   |

|                                           | DAC factor ratio                                                              | Normalized @ full scale value                                                      | -2   |      | +2                  | %    |

| SENSE AM                                  | PLIFIER                                                                       |                                                                                    |      |      |                     |      |

| V <sub>cm</sub>                           | Input common mode voltage range                                               |                                                                                    | -0.7 |      | V <sub>S</sub> +0.7 | V    |

| I <sub>inp</sub>                          | Input bias                                                                    | sense1/sense2                                                                      | -200 |      | 0                   | μΑ   |

| ERROR AM                                  | IPLIFIER                                                                      |                                                                                    | •    | •    | •                   | •    |

| G <sub>V</sub>                            | Open loop voltage gain                                                        |                                                                                    |      | 70   |                     | dB   |

| SR                                        | Output slew rate                                                              | Open loop                                                                          |      | 0.2  |                     | V/µs |

| GBW                                       | Gain bandwidth product                                                        |                                                                                    |      | 400  |                     | kHz  |

|                                           |                                                                               |                                                                                    | _    | _    |                     |      |

<sup>1.</sup> Chopping frequency is twice fosc value.

57

<sup>2.</sup> This is true for all the logic inputs except the disable input.

<sup>3.</sup> If T<sub>j</sub> is inside the range -40 to -10°C then  $V_{ref}$  max is  $2V+0.5V\cdot(T_j+40^\circ C)/30^\circ C$ . If T<sub>j</sub> is greater than -10°C then  $V_{ref}$  max is 2.5V.

## 2 Functional description

The circuit is intended to drive both windings of a bipolar stepper motor or two DC motors.

The current control is generated through a switch mode regulation.

With this system the direction and the amplitude of the load current are depending on the relation of phase and duty cycle between the two outputs of the current control loop.

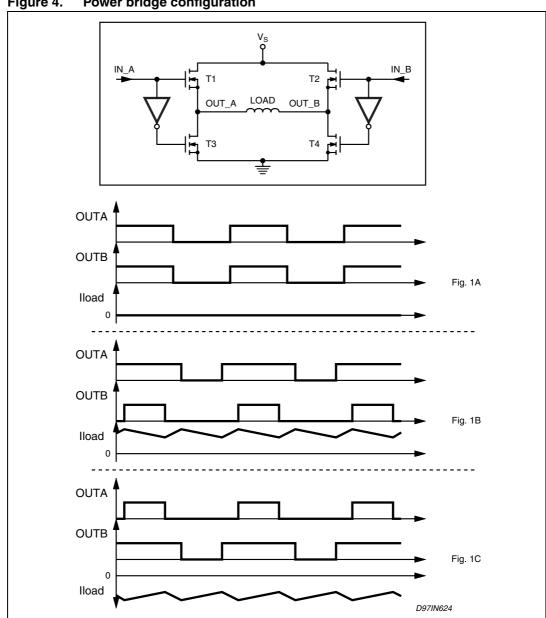

The L6258EA power stage is composed by power DMOS in bridge configuration as it is shown in *Figure 4*, where the bridge outputs OUT\_A and OUT\_B are driven to  $V_s$  with an high level at the inputs IN\_A and IN\_B while are driven to ground with a low level at the same inputs.

The zero current condition is obtained by driving the two half bridge using signals IN\_A and IN\_B with the same phase and 50% of duty cycle.

In this case the outputs of the two half bridges are continuously switched between power supply  $(V_s)$  and ground, but keeping the differential voltage across the load equal to zero.

In *Figure 4* is shown the timing diagram of the two outputs and the load current for this working condition.

Following we consider positive the current flowing into the load with a direction from OUT\_A to OUT\_B, while we consider negative the current flowing into load with a direction from OUT\_B to OUT\_A.

Now just increasing the duty cycle of the IN\_A signal and decreasing the duty cycle of IN\_B signal we drive positive current into the load.

In this way the two outputs are not in phase, and the current can flow into the load trough the diagonal bridge formed by T1 and T4 when the output OUT\_A is driven to  $V_s$  and the output OUT\_B is driven to ground, while there will be a current recirculation into the higher side of the bridge, through T1 and T2, when both the outputs are at Vs and a current recirculation into the lower side of the bridge, through T3 and T4, when both the outputs are connected to ground.

Since the voltage applied to the load for recirculation is low, the resulting current discharge time constant is higher than the current charging time constant during the period in which the current flows into the load through the diagonal bridge formed by T1 and T4. In this way the load current will be positive with an average amplitude depending on the difference in duty cycle of the two driving signals.

In Figure 4 is shown the timing diagram in the case of positive load current

On the contrary, if we want to drive negative current into the load is necessary to decrease the duty cycle of the IN\_A signal and increase the duty cycle of the IN\_B signal. In this way we obtain a phase shift between the two outputs such to have current flowing into the diagonal bridge formed by T2 and T3 when the output OUT\_A is driven to ground and output OUT\_B is driven to Vs, while we will have the same current recirculation conditions of the previous case when both the outputs are driven to Vs or to ground.

So, in this case the load current will be negative with an average amplitude always depending by the difference in duty cycle of the two driving signals.

In *Figure 4* is shown the timing diagram in the case of negative load current.

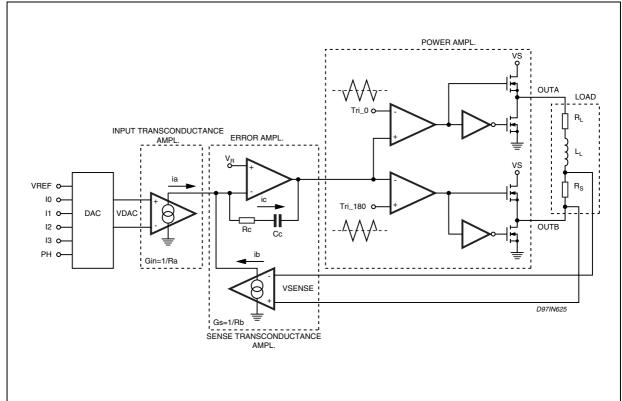

Figure 5 shows the device block diagram of the complete current control loop.

#### Reference voltage 2.1

The voltage applied to VREF pin is the reference for the internal DAC and, together with the sense resistor value, defines the maximum current into the motor winding according to the following relation:

$$I_{MAX} = \frac{0.5 \cdot V_{REF}}{R_{S}} = \frac{1}{FI} \cdot \frac{V_{REF}}{R_{S}}$$

where  $R_s$  = sense resistor value

Power bridge configuration

577

Figure 5. Current control loop block diagram

## **2.2** Input logic $(I_0 - I_1 - I_2 - I_3)$

The current level in the motor winding is selected according to this table:

| Table 5. | Current | levels |

|----------|---------|--------|

|----------|---------|--------|

| 13 | I2 | l1 | 10 | Current level % of IMAX |  |  |  |

|----|----|----|----|-------------------------|--|--|--|

| Н  | Н  | Н  | Н  | No Current              |  |  |  |

| Н  | Н  | Н  | L  | 9.5                     |  |  |  |

| Н  | Н  | L  | Н  | 19.1                    |  |  |  |

| Н  | Н  | L  | L  | 28.6                    |  |  |  |

| Н  | L  | Н  | Н  | 38.1                    |  |  |  |

| Н  | L  | Н  | L  | 47.6                    |  |  |  |

| Н  | L  | L  | Н  | 55.6                    |  |  |  |

| Н  | L  | L  | L  | 63.5                    |  |  |  |

| L  | Н  | Н  | Н  | 71.4                    |  |  |  |

| L  | Н  | Н  | L  | 77.8                    |  |  |  |

| L  | Н  | L  | Н  | 82.5                    |  |  |  |

| 13 | 12 | l1 | 10 | Current level % of IMAX |

|----|----|----|----|-------------------------|

| L  | Н  | L  | L  | 88.9                    |

| L  | L  | Н  | Н  | 92.1                    |

| L  | L  | Н  | L  | 95.2                    |

| L  | L  | L  | Н  | 98.4                    |

| L  | L  | L  | L  | 100                     |

Table 5. Current levels (continued)

## 2.3 Phase input (PH)

The logic level applied to this input determines the direction of the current flowing in the winding of the motor.

High level on the phase input causes the motor current flowing from OUT\_A to OUT\_B through the load.

## 2.4 Triangular generator

This circuit generates the two triangular waves TRI\_0 and TRI\_180 internally used to generate the duty cycle variation of the signals driving the output stage in bridge configuration.

The frequency of the triangular wave defines the switching frequency of the output, and can be adjusted by changing the capacitor connected at TR1\_CAP pin:

$$F_{ref} = \frac{K}{C}$$

where:  $K = 1.5 \times 10^{-5}$

## 2.5 Charge pump circuit

To ensure the correct driving of the high side drivers a voltage higher than Vs is supplied on the Vboot pin. This boostrap voltage is not needed for the low side power DMOS transistors because their sources terminals are grounded. To produce this voltage a charge pump method is used. It is made by using two external capacitors; one connected to the internal oscillator (CP) and the other (Cboot) to storage the overvoltage needed for the driving the gates of the high side DMOS. The value suggested for the capacitors are:

Table 6. Charge pump capacitor's values

| Component name    | Component's function | Value | Unit |

|-------------------|----------------------|-------|------|

| C <sub>boot</sub> | Storage capacitor    | 100   | nF   |

| C <sub>P</sub>    | Pump capacitor       | 10    | nF   |

### 2.6 Current control loop

The current control loop is a transconductance amplifier working in PWM mode.

The motor current is a function of the programmed DAC voltage.

To keep under control the output current, the current control modulates the duty cycle of the two outputs OUT\_A and OUT\_B, and a sensing resistor Rs is connected in series with the motor winding in order to produce a voltage feedback compared with the programmed voltage of the DAC.

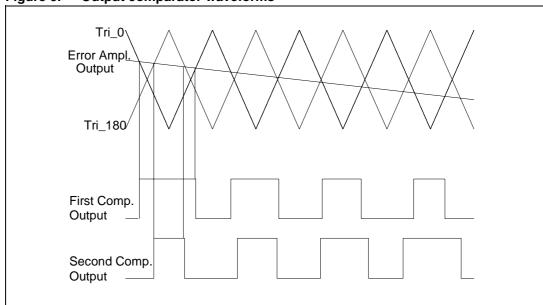

The duty cycle modulation of the two outputs is generated comparing the voltage at the outputs of the error amplifier, with the two triangular wave references.

In order to drive the output bridge with the duty cycle modulation explained before, the signals driving each output (OUTA & OUTB) are generated by the use of the two comparators having as reference two triangular wave signals Tri\_0 and Tri\_180 of the same amplitude, the same average value (in our case Vr), but with a 180° of phase shift each other.

The two triangular wave references are respectively applied to the inverting input of the first comparator and to the non inverting input of the second comparator.

The other two inputs of the comparators are connected together to the error amplifier output voltage resulting by the difference between the programmed DAC. The reset of the comparison between the mentioned signals is shown in *Figure 6*.

Figure 6. Output comparator waveforms

In the case of  $V_{DAC}$  equal to zero, the transconductance loop is balanced at the value of Vr, so the outputs of the two comparators are signals having the same phase and 50% of duty cycle.

As we have already mentioned, in this situation, the two outputs OUT\_A and OUT\_B are simultaneously driven from  $V_s$  to ground; and the differential voltage across the load in this case is zero and no current flows in the motor winding.

577

With a positive differential voltage on V<sub>DAC</sub> (see *Figure 5*, the transconductance loop will be positively unbalanced respected Vr.

In this case being the error amplifier output voltage greater than Vr, the output of the first comparator is a square wave with a duty cycle higher than 50%, while the output of the second comparator is a square wave with a duty cycle lower than 50%.

The variation in duty cycle obtained at the outputs of the two comparators is the same, but one is positive and the other is negative with respect to the 50% level.

The two driving signals, generated in this case, drive the two outputs in such a way to have switched current flowing from OUT\_A through the motor winding to OUT\_B.

With a negative differential voltage  $V_{DAC}$ , the transconductance loop will be negatively unbalanced respected Vr.

In this case the output of the first comparator is a square wave with a duty cycle lower than 50%, while the output of the second comparator is a square wave with a duty cycle higher than 50%.

The variation in the duty cycle obtained at the outputs of the two comparators is always of the same.

The two driving signals, generated in this case, drive the two outputs in order to have the switched current flowing from OUT\_B through the motor winding to OUT\_A.

### 2.7 Current control loop compensation

In order to have a flexible system able to drive motors with different electrical characteristics, the non inverting input and the output of the error amplifier (EA\_OUT) are available.

Connecting at these pins an external RC compensation network it is possible to adjust the gain and the bandwidth of the current control loop.

5/

## 3 PWM current control loop

## 3.1 Open loop transfer function analysis

Block diagram: refer to Figure 5.

Input parameters:

- $\bullet$   $V_S = 24V$

- L₁ = 12mH

- $R_L = 12\Omega$

- $R_S = 0.33\Omega$

- R<sub>C</sub> = to be calculated

- C<sub>C</sub> = to be calculated

- Gs transconductance gain = 1/Rb

- Gin transconductance gain = 1/Ra

- Ampl. of the Tria\_0\_180 ref. = 1.6V (peak to peak)

- $R_a = 40K\Omega$

- $R_b = 20K\Omega$

- $V_r$  = Internal reference equal to  $V_{DD}/2$  (Typ. 2.5V)

these data refer to a typical application, and will be used as an example during the analysis of the stability of the current control loop.

The block diagram shows the schematics of the L6258 internal current control loop working in PWM mode; the current into the load is a function of the input control voltage  $V_{DAC}$ , and the relation between the two variables is given by the following formula:

$$\begin{split} I_{LOAD} \cdot R_S \cdot G_S &= V_{DAC} \cdot G_{in} \\ I_{LOAD} \cdot R_S \cdot \frac{1}{R_b} &= V_{DAC} \cdot \frac{1}{R_a} \\ I_{LOAD} &= V_{DAC} \cdot \frac{R_b}{R_a \cdot R_s} &= 0.5 \cdot \frac{V_{DAC}}{R_S}(A) \end{split}$$

where:

V<sub>DAC</sub> is the control voltage defining the load current value

G<sub>in</sub> is the gain of the input transconductance amplifier (1/Ra)

G<sub>s</sub> is the gain of the sense transconductance amplifier (1/Rb)

R<sub>s</sub> is the resistor connected in series to the output to sense the load current

In this configuration the input voltage is compared with the feedback voltage coming from the sense resistor, then the difference between this two signals is amplified by the error amplifier in order to have an error signal controlling the duty cycle of the output stage keeping the load current under control.

It is clear that to have a good performance of the current control loop, the error amplifier must have an high DC gain and a large bandwidth.

Gain and bandwidth must be chosen depending on many parameters of the application, like the characteristics of the load, power supply etc..., and most important is the stability of the system that must always be guaranteed.

To have a very flexible system and to have the possibility to adapt the system to any application, the error amplifier must be compensated using an RC network connected between the output and the negative input of the same.

For the evaluation of the stability of the system, we have to consider the open loop gain of the current control loop:

where AC... is the gain of the blocks that refers to the error, power and sense amplifier plus the attenuation of the load block.

The same formula in dB can be written in this way:

$$Aloop_{dB} = ACerr_{dB} + ACpw_{dB} + ACload_{dB} + ACsense_{dB}$$

So now we can start to analyse the dynamic characteristics of each single block, with particular attention to the error amplifier.

## 3.2 Power amplifier

The power amplifier is not a linear amplifier, but is a circuit driving in PWM mode the output stage in full bridge configuration.

The output duty cycle variation is given by the comparison between the voltage of the error amplifier and two triangular wave references Tri\_0 and Tri\_180. Because all the current control loop is referred to the Vr reference, the result is that when the output voltage of the error amplifier is equal to the Vr voltage the two output Out\_A and Out\_B have the same phase and duty cycle at 50%; increasing the output voltage of the error amplifier above the Vr voltage, the duty cycle of the Out\_A increases and the duty cycle of the Out\_B decreases of the same percentage; on the contrary decreasing the voltage of the error amplifier below the Vr voltage, the duty cycle of the Out\_A decreases and the duty cycle of the Out\_B increases of the same percentage.

The gain of this block is defined by the amplitude of the two triangular wave references; more precisely the gain of the power amplifier block is a reversed proportion of the amplitude of the two references.

In fact a variation of the error amplifier output voltage produces a larger variation in duty cycle of the two outputs Out\_A and Out\_B in case of low amplitude of the two triangular wave references.

The duty cycle has the max value of 100% when the input voltage is equal to the amplitude of the two triangular references.

The transfer function of this block consist in the relation between the output duty cycle and the amplitude of the triangular references.

Vout =

$$2 \cdot V_S \cdot (0.5 - DutyCycle)$$

$$ACpw_{dB} = 20 \cdot log \frac{\Delta V_{out}}{\Delta V_{in}} = \frac{2 \cdot V_{S}}{Triangular Amplitude}$$

$$ACpw|_{dB} = 20 \cdot log \frac{2 \cdot 24}{1.6} = 29,5dB$$

Moreover, having the two references Tri\_0 and Tri\_180 a triangular shape it is clear that the transfer function of this block is a linear constant gain without poles and zeros.

#### 3.3 Load attenuation

The load block is composed by the equivalent circuit of the motor winding (resistance and inductance) plus the sense resistor.

We will considered the effect of the Bemf voltage of the motor in the next chapter.

The input of this block is the PWM voltage of the power amplifier and as output we have the voltage across the sense resistor produced by the current flowing into the motor winding. The relation between the two variable is:

$$V_{\text{sense}} = \frac{V_{\text{out}}}{R_L + R_S} \cdot R_S$$

so the gain of this block is:

ACload =

$$\frac{V_{sense}}{v_{out}} = \frac{R_S}{R_L + R_S}$$

$$ACload_{dB} = 20 \cdot log \frac{R_S}{R_L + R_S}$$

Aload<sub>dB</sub> =

$$20 \cdot \log \frac{0.33}{12 + 0.33} = -31.4$$

dB

where:

R<sub>I</sub> = equivalent resistance of the motor winding

R<sub>S</sub> = sense resistor

Because of the inductance of the motor L<sub>L</sub>, the load has a pole at the frequency:

$$\mathsf{Fpole} = \frac{1}{2\pi \cdot \frac{\mathsf{L}_{\mathsf{L}}}{\mathsf{R}_{\mathsf{L}} + \mathsf{R}_{\mathsf{S}}}}$$

Fpole =

$$\frac{1}{6,28 \cdot \frac{12 \cdot 10^{-3}}{12 + 0,33}} = 163 \text{Hz}$$

Before analysing the error amplifier block and the sense transconductance block, we have to do this consideration:

$$Aloop_{dB} = Ax_{dB} + Bx_{dB}$$

$$Axl_{dB} = ACpwl_{dB} + ACloadl_{dB}$$

and

$$Bxl_{dB} = ACerrl_{dB} + ACsensel_{dB}$$

this means that AxIdB is the sum of the power amplifier and load blocks;

$$AxI_{dB} = (29,5) + (-31.4) = -1.9dB$$

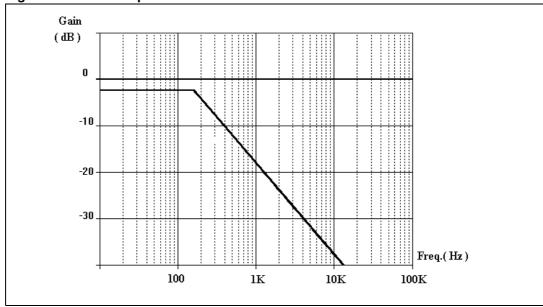

The BODE analysis of the transfer function of Ax is:

The Bode plot of the AxldB function shows a DC gain of -1.9dB and a pole at 163Hz.

It is clear now that (because of the negative gain of the Ax function), Bx function must have an high DC gain in order to increment the total open loop gain increasing the bandwidth too.

## 3.4 Error amplifier and sense amplifier

As explained before the gain of these two blocks is:

$$Bx_{dB} = ACerr_{dB} + ACsense_{dB}$$

Being the voltage across the sense resistor the input of the Bx block and the error amplifier voltage the output of the same, the voltage gain is given by:

ib = Vsense · Gs = Vsense ·

$$\frac{1}{Rb}$$

Verr\_out = -(ic · Zc) so ic = -(Verr\_out ·

$$\frac{1}{Zc}$$

)

because ib = icwe have:

$$Vsense \cdot \frac{1}{Rb} = -(Verr\_out \cdot \frac{1}{Zc})$$

$$Bx = -\frac{Verr\_out}{Vsense} = -\frac{Zc}{Rb}$$

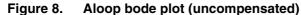

In the case of no external RC network is used to compensate the error amplifier, the typical open loop transfer function of the error plus the sense amplifier is something with a gain around 80dB and a unity gain bandwidth at 400kHz. In this case the situation of the total transfer function Aloop, given by the sum of the  $Ax_{dB}$  and  $Bx_{dB}$  is:

The BODE diagram shows together the error amplifier open loop transfer function, the Ax function and the resultant total Aloop given by the following equation:

$$Aloop_{dB} = AxdB + Bx_{dB}$$

The total Aloop has an high DC gain of 78.1dB with a bandwidth of 15KHz, but the problem in this case is the stability of the system; in fact the total Aloop cross the zero dB axis with a slope of -40dB/decade.

Now it is necessary to compensate the error amplifier in order to obtain a total Aloop with an high DC gain and a large bandwidth. Aloop must have enough phase margin to guarantee the stability of the system.

A method to reach the stability of the system, using the RC network showed in the block diagram, is to cancel the load pole with the zero given by the compensation of the error amplifier.

The transfer function of the Bx block with the compensation on the error amplifier is:

$$Bx = -\frac{Zc}{Rb} = -\frac{Rc - j\frac{1}{2\pi \cdot f \cdot Cc}}{Rb}$$

In this case the Bx block has a DC gain equal to the open loop and equal to zero at a frequency given by the following formula:

$$Fzero = \frac{1}{2\pi \cdot Rc \cdot Cc}$$

In order to cancel the pole of the load, the zero of the Bx block must be located at the same frequency of 163Hz; so now we have to find a compromise between the resistor and the capacitor of the compensation network.

Considering that the resistor value defines the gain of the Bx block at the zero frequency, it is clear that this parameter will influence the total bandwidth of the system because, annulling the load pole with the error amplifier zero, the slope of the total transfer function is -20dB/decade.

So the resistor value must be chosen in order to have an error amplifier gain enough to guarantee a desired total bandwidth.

In our example we fix at 35dB the gain of the Bx block at zero frequency, so from the formula:

$$Bx_{gain} = 20 \cdot \log \frac{Rc}{Rh}$$

where:  $Rb = 20k\Omega$

we have:  $Rc = 1.1M\Omega$

Therefore we have the zero with a 163Hz the capacitor value:

$$Cc = \frac{1}{2\pi \cdot Fzero \cdot Rc} = \frac{1}{6,28 \cdot 163 \cdot 1,1 \cdot 10^{-6}} = 880pF$$

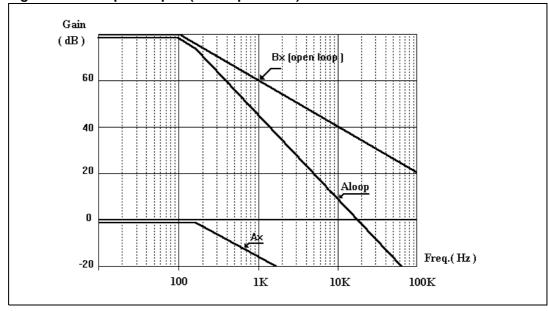

Now we have to analyse how the new Aloop transfer function with a compensation network on the error amplifier is.

The following bode diagram shows:

- the Ax function showing the position of the load pole

- the open loop transfer function of the Bx block

- the transfer function of the Bx with the RC compensation network on the error amplifier

- the total Aloop transfer function that is the sum of the Ax function plus the transfer function of the compensated Bx block.

Figure 9. Aloop bode plot (compensated)

We can see that the effect of the load pole is cancelled by the zero of the Bx block; the total Aloop cross a the 0dB axis with a slope of -20dB/decade, having in this way a stable system with an high gain at low frequency and a bandwidth of around 8KHz.

To increase the bandwidth of the system, we should increase the gain of the Bx block, keeping the zero in the same position. In this way the result is a shift of the total Aloop transfer function up to a greater value.

## 3.5 Effect of the Bemf on the current control loop stability

In order to evaluate what is the effect of the Bemf voltage of the stepper motor we have to look at the load block:

Bemf

R L

L L

R s

to Sense

Amplifier

Figure 10. Electrical model of the load

The schematic now shows the equivalent circuit of the stepper motor including a sine wave voltage generator of the Bemf. The Bemf voltage of the motor is not constant, its value changes depending on the speed of the motor.

Increasing the motor speed the Bemf voltage increases:

Bemf =  $Kt \cdot \omega$

where:

Kt is the motor constant

$\omega$  is the motor speed in radiant per second

The formula defining the gain of the load considering the Bemf of the stepper motor becomes:

$$\begin{aligned} \text{ACload} &= \frac{\text{Vsense}}{\text{Vout}} = \frac{(\text{V}_S - \text{Bemf}) \cdot \frac{\text{R}_S}{\text{R}_L + \text{R}_S}}{\text{V}_S} \\ \text{Acload} &= \frac{\text{V}_S - \text{Bemf}}{\text{V}_S} \cdot \frac{\text{R}_S}{\text{R}_L + \text{R}_S} \end{aligned}$$

$$\mathsf{ACload}_{dB} = 20 \cdot \mathsf{log} \left( \frac{\mathsf{V}_S \mathsf{-Bemf}}{\mathsf{V}_S} \cdot \frac{\mathsf{R}_S}{\mathsf{R}_L \mathsf{+R}_S} \right)$$

we can see that the Bemf influences only the gain of the load block and does not introduce any other additional pole or zero, so from the stability point of view the effect of the Bemf of the motor is not critical because the phase margin remains the same.

Practically the only effect of the Bemf is to limit the gain of the total Aloop with a consequent variation of the bandwidth of the system.

## 4 Application information

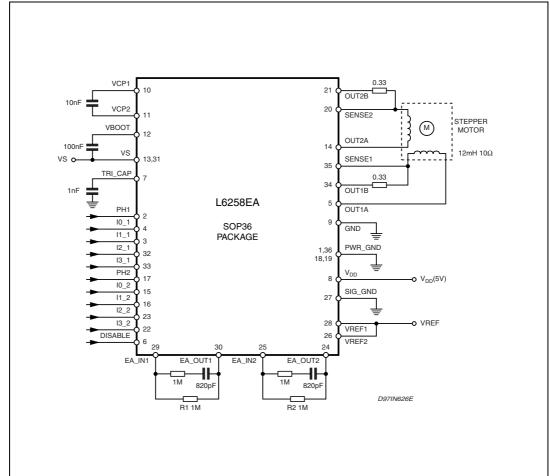

A typical application circuit is shown in Figure 11.

Note: For avoid current spikes on falling edge of DISABLE

For avoid current spikes on falling edge of DISABLE a "DC feedback" would be added to the ERROR Amplifier. (R1-R2 on Figure 11).

### 4.1 Interference

Due to the fact that the circuit operates with switch mode current regulation, to reduce the effect of the wiring inductance a good capacitor (100nF) can be placed on the board near the package, between the power supply line (pin 13,31) and the power ground (pin 1,36,18,19) to absorb the small amount of inductive energy.

It should be noted that this capacitor is usually required in addition to an electrolytic capacitor, that has poor performance at the high frequencies, always located near the package, between power supply voltage (pin 13,31) and power ground (pin 1,36,18,19), just to have a current recirculation path during the fast current decay or during the phase change.

The range value of this capacitor is between few  $\mu F$  and  $100\mu F$ , and it must be chosen depending on application parameters like the motor inductance and load current amplitude. A decoupling capacitor of 100nF is suggested also between the logic supply and ground.

The EA\_IN1 and EA\_IN2 pins carry out high impedance lines and care must be taken to avoid coupled noise on this signals. The suggestion is to put the components connected to this pins close to the L6258, to surround them with ground tracks and to keep as far as possible fast switching outputs of the device. Remember also an 1 Mohm resistor between EA\_INx and EA\_OUTx to avoid output current spike during supply startup/shutdown. A non inductive resistor is the best way to implement the sensing. Whether this is not possible, some metal film resistor of the same value can be paralleled. The two inputs for the sensing of the winding motor current (SENSE\_A & SENSE\_B) should be connected directly on the sensing resistor Rs terminals, and the path lead between the Rs and the two sensing inputs should be as short as possible.

Note:

Connect the DISABLE pin to a low impedance ( $< 300~\Omega$ ) voltage source to reduce at minimum the interference on the output current due to capacitive coupling of OUT1A (pin5) and DISABLE (pin 6).

Figure 11. Typical application circuit

### 4.2 Motor selection

Some stepper motor have such high core losses that they are not suitable for switch mode current regulation. Furthermore, some stepper motors are not designed for continuous operating at maximum current. Since the circuit can drive a constant current through the motor, its temperature might exceed, both at low and high speed operation.

## 4.3 Notes on PCB design

We recommend to observe the following layout rules to avoid application problems with ground and anomalous recirculation current.

The by-pass capacitors for the power and logic supply must be kept as near as possible to the IC.

It's important to separate on the PCB board the logic and power grounds and the internal charge pump circuit ground avoiding that ground traces of the logic signals cross the ground traces of the power signals.

Because the IC uses the board as a heat sink, the dissipating copper area must be sized in accordance with the required value of  $R_{thi-amb}$ .

## 5 Operation mode time diagrams

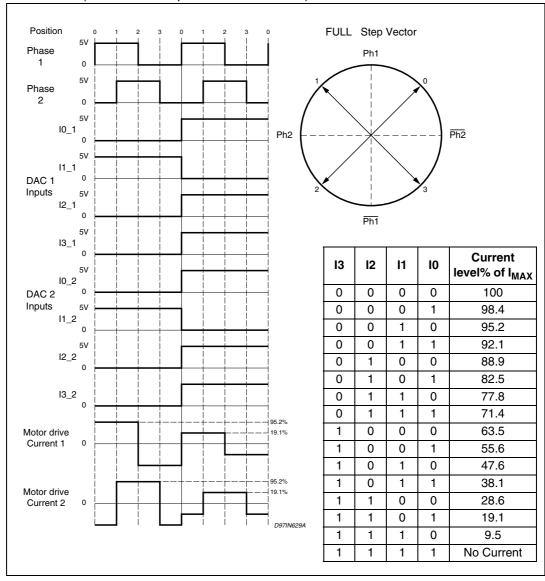

Figure 12. Full step operation mode timing diagram

(Phase - DAC input and motor current)

(Phase - DAC input and motor current) 1 2 3 4 5 6 7 5V Phase 1 0 5V Half Step Vector Phase 2 0 Ph1 5V 10\_1 0 5V DAC 1 11\_1 0 Inputs 5V 12\_1 0 5V I3\_1 o Ph2 0 Ph2 5V 10\_2 0 5V 11\_2 DAC 2 0 Inputs 5V 12\_2 0 5V 13\_2 0 Ph1 100% Current 71.4% 13 12 11 10 level% of  $I_{\text{MAX}}$ 100 0 0 0 0 0 98.4 0 0 1 0 0 0 1 0 95.2 Motor drive 92.1 0 0 1 1 Current 1 0 1 0 0 88.9 -71.4% 0 1 0 1 82.5 -100% 0 0 77.8 1 1 100% 0 71.4 1 1 1 71.4% 1 0 0 0 63.5 55.6 1 0 0 1 Motor drive 1 0 1 0 47.6 Current 2 38.1 0 1 1 1 0 1 1 0 28.6 1 1 0 1 19.1 9.5 1 1 1 0

Figure 13. Half step operation mode timing diagram

28/32

D97IN627C

1

1

1

No Current

-71.4%

-100%

Position Micro Step Vector 5V Ph1 0 Phase 5V 0 Phase 5V 10\_1 o Ph2 Ph2 32 0 5V 0 DAC 1 Inputs 5V 12\_1 0 Ph1 5V 13\_1 0 5V 10\_2 DAC 2 Current 13 12 10 11 Inputs level% of I<sub>MAX</sub> 11\_2 100 0 0 0 0 0 5V 0 0 0 1 98.4 12\_2 0 0 1 0 95.2 0 0 1 1 92.1 13\_2 0 1 0 88.9 0 0 1 0 1 82.5 0 1 1 0 77.8 0 1 1 1 71.4 Motor drive 1 0 0 0 63.5 Current 1 1 0 0 1 55.6 1 0 1 0 47.6 1 0 1 1 38.1 0 28.6 1 1 0 1 1 0 1 19.1 Motor drive 0 1 1 1 9.5 0 Current 2 1 1 1 1 No Current

Figure 14. 4 bit microstep operation mode timing diagram (Phase - DAC input and motor current)

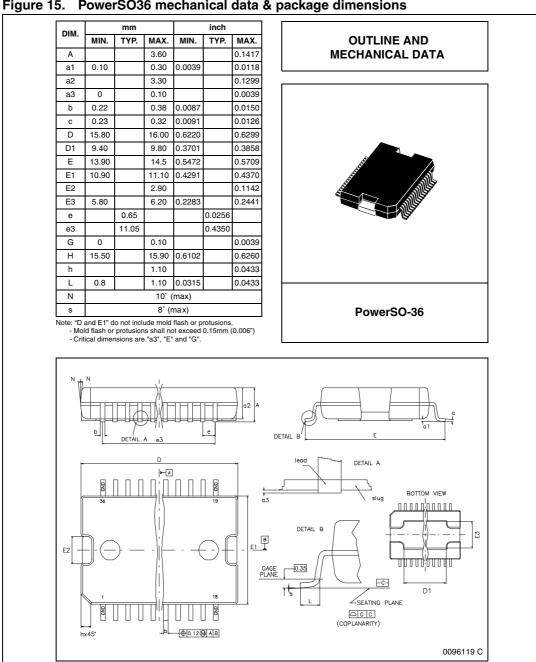

**Package information** L6258EA

#### **Package information** 6

In order to meet environmental requirements, ST offers these devices in ECOPACK® packages. These packages have a Lead-free second level interconnect. The category of second Level Interconnect is marked on the package and on the inner box label, in compliance with JEDEC Standard JESD97. The maximum ratings related to soldering conditions are also marked on the inner box label.

ECOPACK is an ST trademark. ECOPACK specifications are available at: www.st.com.

PowerSO36 mechanical data & package dimensions

L6258EA Revision history

## 7 Revision history

Table 7. Document revision history

| Date        | Revision | Changes                                                                                                                        |  |

|-------------|----------|--------------------------------------------------------------------------------------------------------------------------------|--|

| 11-May-2004 | 1        | First Issue                                                                                                                    |  |

| 29-Jun-2004 | 2        | Updated the table 1: Order Codes                                                                                               |  |

| 24-Sep-2004 | 3        | Changed on the page 5 the f <sub>osc</sub> parameter max. value from 17.5 to 18.5kHz                                           |  |

| 23-Mar-2005 | 4        | Add. note at the bottom of Table 2: Absolute maximum rating.                                                                   |  |

| 03-Dec-2007 | 5        | Document reformatted.  Modified the ACpw formula in Section 3.2 on page 17.  Added the disable note in Section 4.1 on page 24. |  |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2007 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

577

OOO «ЛайфЭлектроникс" "LifeElectronics" LLC

ИНН 7805602321 КПП 780501001 P/C 40702810122510004610 ФАКБ "АБСОЛЮТ БАНК" (ЗАО) в г.Санкт-Петербурге К/С 3010181090000000703 БИК 044030703

Компания «Life Electronics» занимается поставками электронных компонентов импортного и отечественного производства от производителей и со складов крупных дистрибьюторов Европы, Америки и Азии.

С конца 2013 года компания активно расширяет линейку поставок компонентов по направлению коаксиальный кабель, кварцевые генераторы и конденсаторы (керамические, пленочные, электролитические), за счёт заключения дистрибьюторских договоров

#### Мы предлагаем:

- Конкурентоспособные цены и скидки постоянным клиентам.

- Специальные условия для постоянных клиентов.

- Подбор аналогов.

- Поставку компонентов в любых объемах, удовлетворяющих вашим потребностям.

- Приемлемые сроки поставки, возможна ускоренная поставка.

- Доставку товара в любую точку России и стран СНГ.

- Комплексную поставку.

- Работу по проектам и поставку образцов.

- Формирование склада под заказчика.

- Сертификаты соответствия на поставляемую продукцию (по желанию клиента).

- Тестирование поставляемой продукции.

- Поставку компонентов, требующих военную и космическую приемку.

- Входной контроль качества.

- Наличие сертификата ISO.

В составе нашей компании организован Конструкторский отдел, призванный помогать разработчикам, и инженерам.

Конструкторский отдел помогает осуществить:

- Регистрацию проекта у производителя компонентов.

- Техническую поддержку проекта.

- Защиту от снятия компонента с производства.

- Оценку стоимости проекта по компонентам.

- Изготовление тестовой платы монтаж и пусконаладочные работы.

Тел: +7 (812) 336 43 04 (многоканальный) Email: org@lifeelectronics.ru