Low Power Consumption Class D Speaker Amplifier series

# 9 W + 9 W Analog Input Class D Stereo Speaker Amplifier

#### **BD28412MUV**

## **General Description**

BD28412MUV is 9 W + 9 W stereo (or 18 W monaural under parallel connection) class D amplifier which can output power without an external heat sink.

This LSI has built-in precise oscillator which generate selectable switching frequencies, so AM radio interference can be avoided. In addition, 2.1 Ch audio system can be achieved by master and slave operation without caring about beat noise.

This LSI achieves lower power consumption under low output power, and suitable for speaker systems in which battery is equipped such as wireless speakers.

#### **Features**

- **Analog Differential Input**

- Low Standby Current

- Output Feedback Circuitry Prevents Sound Quality Degradation Caused by Power Supply Voltage Fluctuation, Achieves Low Noise and Low Distortion, Eliminates the Need of Large Electrolytic-Capacitors for Decoupling

- **Power Limit Function** (Linearly-programmable for voltage of PLIMIT)

- Selectable Switching Frequency (AM Avoidance Function)

- Synchronization Control is Supported (Selectable Master and Slave Operation)

- Parallel BTL (PBTL) is Supported

- Wide Voltage Range (Vcc = 4.5 V to 13 V)

- Operate with Single Power Supply

- High Efficiency and Low-heat-generation Make the System Smaller, Thinner, and More Power-saving

- Pop Noise Prevention During Power Supply

- High Reliability Design by Built-in Protection Circuits

- Overheat Protection

- Under Voltage Protection

- Output Short Protection

- Output DC Voltage Protection

- Small Package (VQFN032V5050) Achieves Mount Area Reduction

#### **Applications**

Wireless Speakers, Small Active Speakers, Portable Audio Equipments, etc.

#### **Key Specifications**

| ■Supply vollage Kallge.          | 4.5 V 10 13 V                 |

|----------------------------------|-------------------------------|

| ■Speaker Output Power:           | 9 W + 9 W (Typ)               |

| $(V_{CC} = 12 \text{ V}, R_L =$  | $8 \Omega$ , PLIMIT = $0 V$ ) |

| ■Speaker Output Power(PBTL):     | 18 W (Typ)                    |

| $(V_{CC} = 12 \text{ V}, R_L =$  | $4 \Omega$ , PLIMIT = $0 V$ ) |

| ■Total Harmonic Distortion Ratio | ·                             |

$0.03 \% (Typ) @P_0 = 1 W$  $(V_{CC} = 11 \text{ V}, R_L = 8 \Omega, PLIMIT = 0 \text{ V})$ ■Crosstalk: 100 dB (Typ) ■PSRR: 55 dB (Typ) ■Output Noise Voltage: -80 dBV (Typ) ■Standby Current: 0.1 µA (Typ) ■Operating Current: 16 mA (Typ) (No Load nor Filter, No Signal) ■Operating Temperature Range: -25 °C to +85 °C

**Package** W (Typ) x D (Typ) x H (Max) VQFN032V5050 5.00 mm x 5.00 mm x 1.00 mm

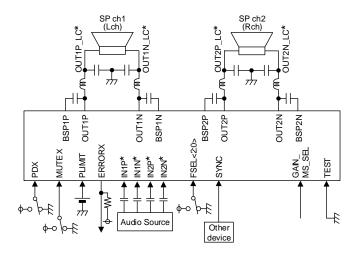

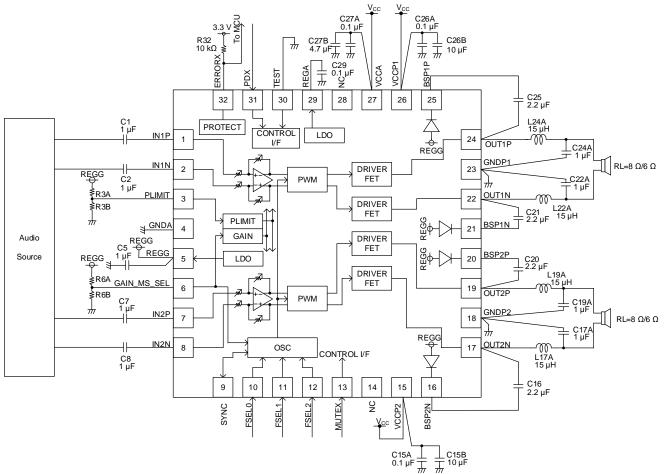

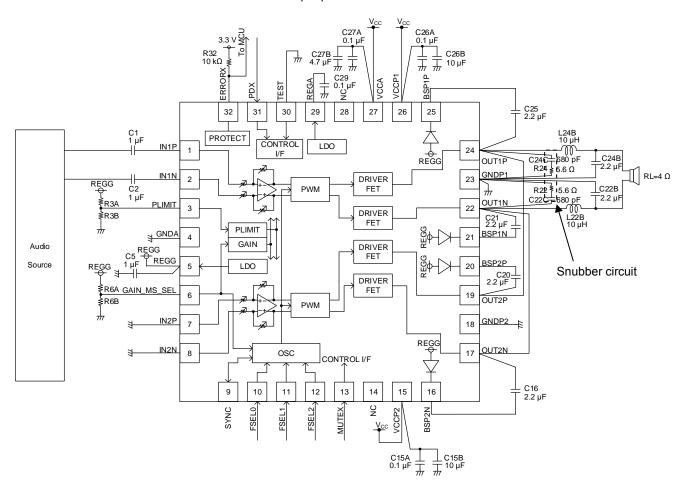

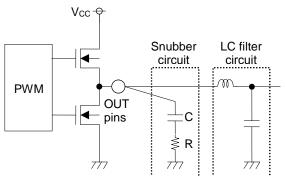

# **Typical Application Circuit**

Figure 1. Typical Application Circuit

\*The phase of OUTxx LC is inverted from the phase of INxx. ex. The phase of OUT1P\_LC is inverted from the phase of IN1P.

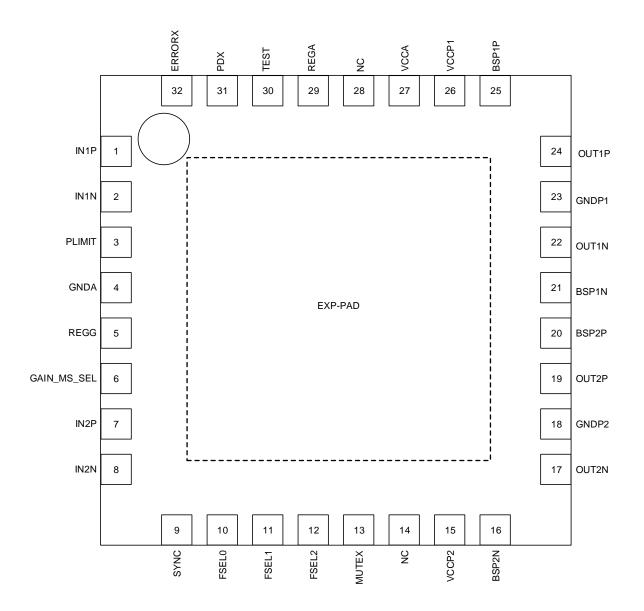

# **Pin Configuration**

(TOP VIEW)

Figure 2. Pin Configuration

**Pin Description**

|            | Description                  |     |                                                                                                                                                                                                                                                                              |                                                 |  |  |  |  |

|------------|------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|--|--|--|--|

| Pin<br>No. | Pin Name <sup>(Note 2)</sup> | Ю   | Function                                                                                                                                                                                                                                                                     | Internal Equivalent Circuit <sup>(Note 1)</sup> |  |  |  |  |

| 1          | IN1P                         | I   | Positive audio signal input pin for Ch1                                                                                                                                                                                                                                      | 30 kΩ to 127.9 kΩ 202.1 kΩ to 300 kΩ            |  |  |  |  |

| 2          | IN1N                         | I   | Negative audio signal input pin for Ch1                                                                                                                                                                                                                                      | 2<br>30 kΩ to 127.9 kΩ<br>202.1 kΩ to 300 kΩ    |  |  |  |  |

| 3          | PLIMIT                       | I   | Power limit level setting pin                                                                                                                                                                                                                                                | 3 100 kΩ 100 kΩ 4                               |  |  |  |  |

| 4          | GNDA                         | -   | Ground pin for Analog                                                                                                                                                                                                                                                        | -                                               |  |  |  |  |

| 5          | REGG                         | O   | Internal power supply pin for gate driver Please connect a capacitor.  Caution: REGG of BD28412MUV should not be used as external supply. Therefore, do not connect anything except the capacitor for stabilization and the resistors for setting of GAIN_MS_SEL and PLIMIT. | 27 5 200 κΩ 5                                   |  |  |  |  |

| 6          | GAIN_MS_SEL                  | I   | Gain and Master/Slave mode setting pin                                                                                                                                                                                                                                       | 6 2 kΩ + + + + + + + + + + + + + + + + + +      |  |  |  |  |

| 7          | IN2P                         | I   | Positive audio signal input pin for Ch2                                                                                                                                                                                                                                      | 30 kΩ to 127.9 kΩ 202.1 kΩ to 300 kΩ            |  |  |  |  |

| 8          | IN2N                         | I   | Negative audio signal input pin for Ch2                                                                                                                                                                                                                                      | 8 30 kΩ to 127.9 kΩ 202.1 kΩ to 300 kΩ          |  |  |  |  |

| 9          | SYNC                         | I/O | PWM clock input/output pin to synchronize multiple class D amplifiers                                                                                                                                                                                                        | 9 100 κΩ                                        |  |  |  |  |

| 10         | FSEL0                        | I   | PWM frequency setting pin 0                                                                                                                                                                                                                                                  | 100 kΩ                                          |  |  |  |  |

Pin Description - continued

|            | ription – continu            | ed |                                                                                                                                                                                                                             |                                                 |

|------------|------------------------------|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| Pin<br>No. | Pin Name <sup>(Note 2)</sup> | Ю  | Function                                                                                                                                                                                                                    | Internal Equivalent Circuit <sup>(Note 1)</sup> |

| 11         | FSEL1                        | I  | PWM frequency setting pin 1                                                                                                                                                                                                 | 1100 κΩ                                         |

| 12         | FSEL2                        | I  | PWM frequency setting pin 2                                                                                                                                                                                                 | (12, 13) + +                                    |

| 13         | MUTEX                        | 1  | Speaker output mute control pin<br>High: Mute OFF<br>Low: Mute ON                                                                                                                                                           | 100 κΩ                                          |

| 14         | NC                           | -  | Non- connection This pin should be opened. Connecting to ground is also available.                                                                                                                                          | -                                               |

| 15         | VCCP2                        | -  | Power supply pin for Ch2 Please connect a capacitor.                                                                                                                                                                        | (15)                                            |

| 16         | BSP2N                        | 0  | Boot-strap pin of Ch2 negative Please connect a capacitor.                                                                                                                                                                  | 5                                               |

| 17         | OUT2N <sup>(Note 3)</sup>    | 0  | Output pin of Ch2 negative PWM signal Please connect to output LPF.                                                                                                                                                         | 16, 20                                          |

| 18         | GNDP2                        | -  | Ground pin for Ch2 for power.                                                                                                                                                                                               | 17, 19                                          |

| 19         | OUT2P <sup>(Note 3)</sup>    | 0  | Output pin of Ch2 positive PWM signal Please connect to output LPF.                                                                                                                                                         |                                                 |

| 20         | BSP2P                        | 0  | Boot-strap pin of Ch2 positive Please connect a capacitor.                                                                                                                                                                  | (18)                                            |

| 21         | BSP1N                        | 0  | Boot-strap pin of Ch1 negative Please connect a capacitor.                                                                                                                                                                  | (26)                                            |

| 22         | OUT1N <sup>(Note 3)</sup>    | 0  | Output pin of Ch1 negative PWM signal Please connect to output LPF.                                                                                                                                                         | (5)                                             |

| 23         | GNDP1                        | -  | Ground pin for Ch1 for power                                                                                                                                                                                                | 21, 25                                          |

| 24         | OUT1P <sup>(Note 3)</sup>    | 0  | Output pin of Ch1 positive PWM signal Please connect to output LPF.                                                                                                                                                         | 22, 24                                          |

| 25         | BSP1P                        | 0  | Boot-strap pin of Ch1 positive Please connect a capacitor.                                                                                                                                                                  |                                                 |

| 26         | VCCP1                        | -  | Power supply pin for Ch1 Please connect a capacitor.                                                                                                                                                                        | (23)———                                         |

| 27         | VCCA                         | -  | Power supply pin for Analog Please connect a capacitor.                                                                                                                                                                     | -                                               |

| 28         | NC                           | -  | Non- connection This pin should be opened. Connecting to ground is also available.                                                                                                                                          | -                                               |

| 29         | REGA                         | 0  | Internal power supply pin Please connect a capacitor.  Caution: Regulator output pin for internal circuit should not be used as external supply. Therefore, do not connect anything except the capacitor for stabilization. | 27<br>180 kΩ 29                                 |

Pin Description - continued

| <u>Desc</u> | Description – continued      |   |                                                                                                                                                                                                                                                                                                                                |                                                 |  |  |  |  |

|-------------|------------------------------|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|--|--|--|--|

| Pin<br>No.  | Pin Name <sup>(Note 2)</sup> | Ю | Function                                                                                                                                                                                                                                                                                                                       | Internal Equivalent Circuit <sup>(Note 1)</sup> |  |  |  |  |

| 30          | TEST                         | I | Test pin Please connect to ground.                                                                                                                                                                                                                                                                                             | 30 100 kΩ                                       |  |  |  |  |

| 31          | PDX                          | I | Power down setting pin High: Active Low: Standby                                                                                                                                                                                                                                                                               | 27<br>55 kΩ<br>45 kΩ                            |  |  |  |  |

| 32          | ERRORX                       | 0 | Error flag pin Please connect to pull-up resistor.  High: Normal Low: Error detected  Caution: An error flag occurs when Output Short Protection, DC Voltage Protection, or High Temperature Protection is activated. This flag shows LSI condition during operation. Use for purposes other than this product cannot be used. | 500 Ω  4                                        |  |  |  |  |

| -           | EXP-PAD                      | - | There is no problem when EXP-PAD is left unconnected. However, connecting it to ground is recommended because the radiation performance will be degraded. The connection to any place except for the ground is prohibited.                                                                                                     | EXP-PAD for heat radiation                      |  |  |  |  |

<sup>(</sup>Note 1) The numerical value of internal equivalent circuit is typical value, not guaranteed value.

(Note 2) On succeeding pages, each pin names means the name of the pin and voltage value which is applied to the pin.

(Note 3) On succeeding pages, OUT1P - OUT1N is OUT1, OUT2P - OUT2N is OUT2.

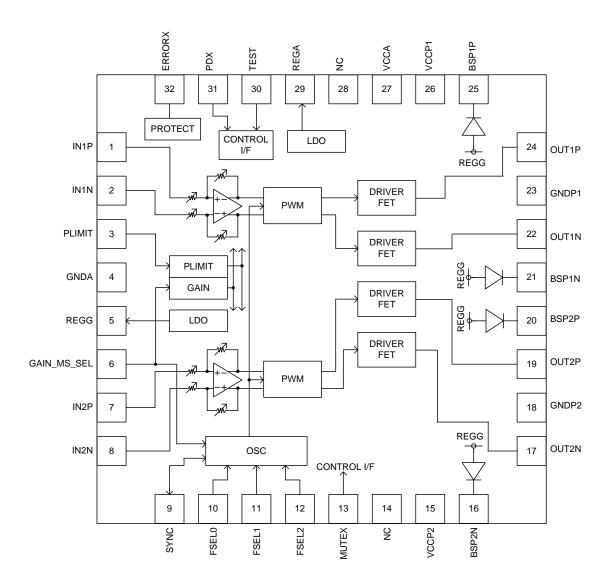

# **Block Diagram**

# (TOP VIEW)

Figure 3. Block Diagram

Absolute Maximum Ratings (Ta = 25 °C)

| <u></u>                                   | /                |                             |      |                                                                                                         |

|-------------------------------------------|------------------|-----------------------------|------|---------------------------------------------------------------------------------------------------------|

| Parameter                                 | Symbol           | Rating                      | Unit | Target Pins, Conditions                                                                                 |

| Supply Voltage <sup>(Note 4)</sup>        | VCCMAX           | -0.3 to +15.5               | V    | VCCA, VCCP1, VCCP2                                                                                      |

| Input Voltage1 <sup>(Note 4)</sup>        | Vin              | -0.3 to +7                  | V    | IN1P, IN1N, IN2P, IN2N, PLIMIT, GAIN_MS_SEL, SYNC <sup>(Note 5)</sup> , FSEL0, FSEL1, FSEL2, PDX, MUTEX |

| Input Voltage2(Note 4)                    | $V_{ERR}$        | -0.3 to +7                  | V    | ERRORX                                                                                                  |

| Pin Voltage <sup>(Note 4), (Note 6)</sup> | $V_{\text{PIN}}$ | -0.3 to +V <sub>CCMAX</sub> | V    | OUT1P, OUT1N, OUT2P, OUT2N                                                                              |

| Storage Temperature Range                 | Tstg             | -55 to +150                 | °C   | -                                                                                                       |

| Maximum Junction Temperature              | Tjmax            | +150                        | °C   | -                                                                                                       |

Caution 1: Operating the LSI over the absolute maximum ratings may damage the LSI. The damage can either be a short circuit between pins or an open circuit between pins and the internal circuitry. Therefore, it is important to consider circuit protection measures, such as adding a fuse, in case the LSI is operated over the absolute maximum ratings.

Caution 2: Should by any chance the maximum junction temperature rating be exceeded the rise in temperature of the chip may result in deterioration of the properties of the chip. In case of exceeding this absolute maximum rating, design a PCB with thermal resistance taken into consideration by increasing board size and copper area so as not to exceed the maximum junction temperature rating.

(Note 4) The voltage that can be applied reference to ground (GNDA, GNDP1, GNDP2). (Note 5) In case SYNC is specified as input mode.

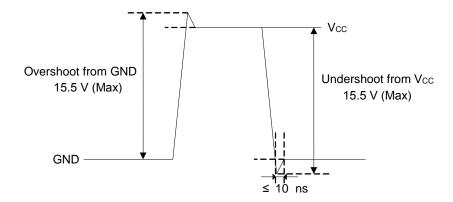

(Note 6) Please use under this rating including the AC peak waveform (overshoot) for all conditions. Only undershoot is allowed at condition of ≤ 15.5 V by the VCC reference and ≤ 10 ns (cf. Figure 4)

Figure 4. Overshoot and Undershoot

#### Thermal Resistance(Note 7)

| Doromotor                                                      | Cumbal         | Thermal Res            | Unit                      |      |  |

|----------------------------------------------------------------|----------------|------------------------|---------------------------|------|--|

| Parameter                                                      | Symbol         | 1s <sup>(Note 9)</sup> | 2s2p <sup>(Note 10)</sup> | Uill |  |

| VQFN032V5050                                                   |                |                        |                           |      |  |

| Junction to Ambient                                            | $\theta_{JA}$  | 138.9                  | 39.1                      | °C/W |  |

| Junction to Top Characterization Parameter <sup>(Note 8)</sup> | $\Psi_{ m JT}$ | 11                     | 5                         | °C/W |  |

(Note 7) Based on JESD51-2A (Still-Air)

(Note 8) The thermal characterization parameter to report the difference between junction temperature and the temperature at the top center of the outside surface of the component package.

(Note 9) Using a PCB board based on JESD51-3.

(Note 10) Using a PCB board based on JESD51-5.

| (Note 10) Using a PCB board base     | d on JESD51-5, | 7.                   |            | 1                |                     |           |

|--------------------------------------|----------------|----------------------|------------|------------------|---------------------|-----------|

| Layer Number of<br>Measurement Board | Material       | Board Size           |            |                  |                     |           |

| Single                               | FR-4           | 114.3 mm x 76.2 mm x | k 1.57 mmt |                  |                     |           |

| Тор                                  |                |                      |            |                  |                     |           |

| Copper Pattern                       | Thickness      |                      |            |                  |                     |           |

| Footprints and Traces                | 70 μm          |                      |            |                  |                     |           |

| Layer Number of                      | Material       | Doord Cine           |            | Thermal V        | ia <sup>(Not)</sup> | e 11)     |

| Measurement Board                    | Material       | Board Size           |            | Pitch            |                     | Diameter  |

| 4 Layers                             | TR-4           | 114.3 mm x 76.2 mm   | x 1.6 mmt  | 1.20 mm          | Ф                   | 0.30 mm   |

| Тор                                  |                | 2 Internal Layers    |            | Botto            | om                  |           |

| Copper Pattern                       | Thickness      | Copper Pattern       | Thickness  | Copper Pattern   | 1                   | Thickness |

| Footprints and Traces                | 70 µm          | 74.2 mm x 74.2 mm    | 35 µm      | 74.2 mm x 74.2 n | nm                  | 70 μm     |

(Note 11) This thermal via connects with the copper pattern of all layers.

Use a thermal design that allows for a sufficient margin in consideration of power dissipation under actual operating conditions. This LSI exposes its frame at the backside of package. Note that this part is assumed to use after providing heat dissipation treatment to improve heat dissipation efficiency. Try to occupy as wide as possible with heat dissipation pattern not only on the board surface but also the backside.

**Recommended Operating Conditions**

| similaria a perating conditions     |                 |     |     |     |      |                                    |

|-------------------------------------|-----------------|-----|-----|-----|------|------------------------------------|

| Parameter                           | Symbol          | Min | Тур | Max | Unit | Target Pins, Conditions            |

| Operating Temperature               | Topr            | -25 | +25 | +85 | °C   | -                                  |

| Supply Voltage                      | Vcc             | 4.5 | -   | 13  | V    | VCCA, VCCP1, VCCP2                 |

| Load Impedance <sup>(Note 12)</sup> | R <sub>L1</sub> | 5.4 | -   | -   | Ω    | BTL                                |

| Load impedance 127                  | R <sub>L2</sub> | 3.2 | -   | -   | Ω    | PBTL                               |

| High Level Input Voltage            | V <sub>IH</sub> | 2.0 | -   | 3.3 | V    | FSEL0, FSEL1, FSEL2,<br>PDX, MUTEX |

| Low Level Input Voltage             | VıL             | 0   | -   | 0.8 | V    | FSEL0, FSEL1, FSEL2,<br>PDX, MUTEX |

| Low Level Output Voltage            | Vol             | -   | -   | 0.8 | V    | ERRORX, I <sub>OL</sub> = 0.5 mA   |

(Note 12) Tj < 150 °C

# **Electrical Characteristics**

(Unless otherwise specified, Ta = 25 °C,  $V_{CC}$  = 11 V,  $f_{PWM}$  = 600 kHz,  $f_{IN}$  = 1 kHz,  $R_L$  = 8  $\Omega$ , PDX = 3.3 V, MUTEX = 3.3 V, PLIMT = 0 V, Gain = 26 dB, Output LC filter: L = 15  $\mu$ H, C = 1  $\mu$ F when  $V_{CC}$  > 11 V, snubber circuit is added: C = 680 pF, R = 5.6  $\Omega$ )

| Parameter                                      | Symbol            | Min  | Тур  | Max  | Unit | Target Pins, Conditions                                       |

|------------------------------------------------|-------------------|------|------|------|------|---------------------------------------------------------------|

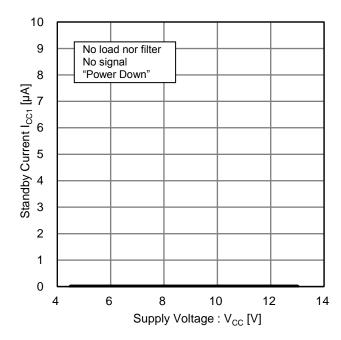

| Standby Current                                | Icc1              | -    | 0.1  | 25   | μA   | No load nor filter,<br>PDX = 0 V, MUTEX = 0 V                 |

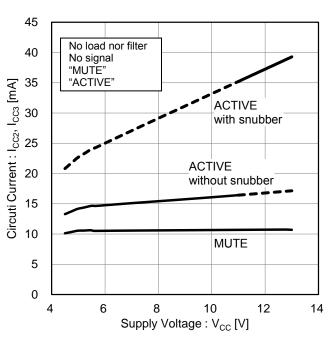

| Mute Current                                   | Icc2              | -    | 10   | 20   | mA   | No load nor filter,<br>PDX = 3.3 V, MUTEX = 0 V               |

| Active Current                                 | I <sub>CC3</sub>  | -    | 16   | 32   | mA   | No load or filter, No signal,<br>PDX = 3.3 V, MUTEX = 3.3 V   |

| Regulator Output Voltage                       | V <sub>REGG</sub> | 4.45 | 5.55 | 6.05 | V    | PDX = 3.3 V, MUTEX = 3.3 V                                    |

| Input Impedance 1                              | R <sub>IN1</sub>  | 50   | -    | -    | kΩ   | MUTEX, PDX,<br>FSEL0, FSEL1, FSEL2,<br>SYNC (Slave mode only) |

| Input Impedance 2                              | R <sub>IN2</sub>  | 140  | 200  | 260  | kΩ   | PLIMIT                                                        |

| Output Power <sup>(Note 13)</sup>              | P <sub>01</sub>   | -    | 9    | -    | W    | Vcc = 12 V, THD+N = 10 %                                      |

| Gain 1 <sup>(Note 13)</sup>                    | G <sub>V1</sub>   | 19   | 20   | 21   | dB   | Po = 1 W,<br>GAIN_MS_SEL = 0 V                                |

| Gain 2 <sup>(Note 13)</sup>                    | G <sub>V2</sub>   | 25   | 26   | 27   | dB   | $P_0 = 1 W$ , $GAIN_MS_SEL = 2/9 \times V_{REGG}$             |

| Gain 3 <sup>(Note 13)</sup>                    | G <sub>V3</sub>   | 31   | 32   | 33   | dB   | $P_0 = 1 W$ ,<br>$GAIN_MS_SEL = 3/9 \times V_{REGG}$          |

| Gain 4 <sup>(Note 13)</sup>                    | G <sub>V4</sub>   | 35   | 36   | 37   | dB   | $P_0 = 1 W$ , $GAIN_MS_SEL = 4/9 \times V_{REGG}$             |

| Total Harmonic Distortion <sup>(Note 13)</sup> | THD               | -    | 0.03 | -    | %    | Po = 1 W,<br>BW = AES17                                       |

| Crosstalk <sup>(Note 13)</sup>                 | CT                | 60   | 100  | -    | dB   | Po = 1 W, 1 kHz BPF                                           |

| PSRR <sup>(Note 13)</sup>                      | PSRR              | -    | 55   | -    | dB   | VRIPPLE = 0.2 VP-P, f = 1 kHz                                 |

| Output Noise Voltage <sup>(Note 13)</sup>      | V <sub>NO</sub>   | -    | -80  | -70  | dBV  | Po = 0 W, BW = A-Weight                                       |

|                                                | f <sub>PWM1</sub> | 1128 | 1200 | 1272 | kHz  | FSEL2 = 3.3 V,<br>FSEL1 = 3.3 V,<br>FSEL0 = 3.3 V             |

|                                                | f <sub>PWM2</sub> | 940  | 1000 | 1060 | kHz  | FSEL2 = 3.3 V,<br>FSEL1 = 3.3 V,<br>FSEL0 = 0 V               |

| PWM (Pulse Width Modulation)<br>Frequency      | f <sub>PWM3</sub> | 564  | 600  | 636  | kHz  | FSEL2 = 3.3 V,<br>FSEL1 = 0 V,<br>FSEL0 = 3.3 V               |

|                                                | f <sub>PWM4</sub> | 470  | 500  | 530  | kHz  | FSEL2 = 3.3 V,<br>FSEL1 = 0 V,<br>FSEL0 = 0 V                 |

| (N. (a. (a)) The decised an effective in the   | f <sub>PWM5</sub> | 376  | 400  | 424  | kHz  | FSEL2 = 0 V,<br>FSEL1 = 3.3 V,<br>FSEL0 = 3.3 V               |

(Note 13) The typical performance of device is shown in the Limits of these items. It largely depends on the board layout, parts, and power supply.

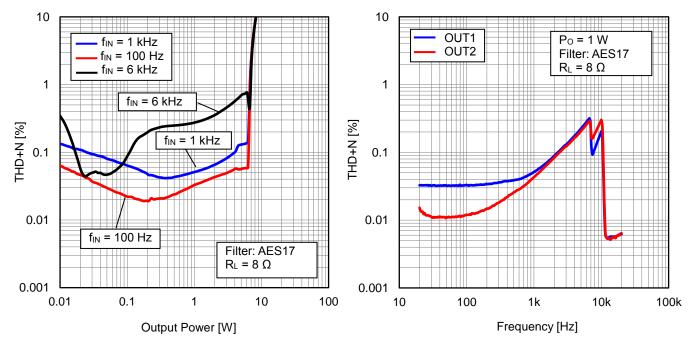

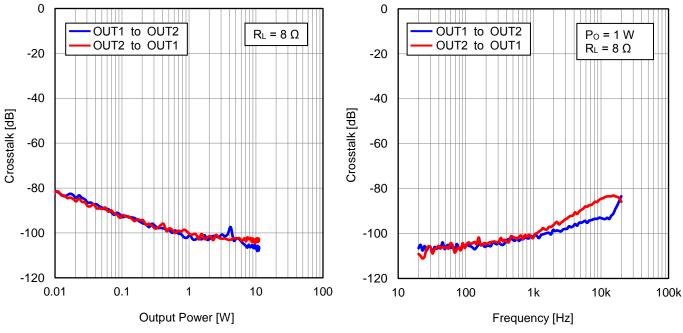

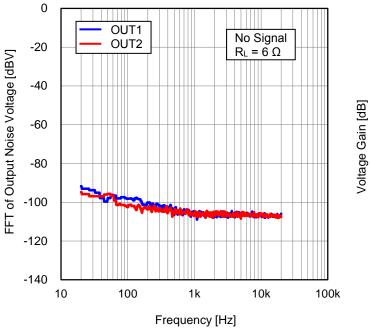

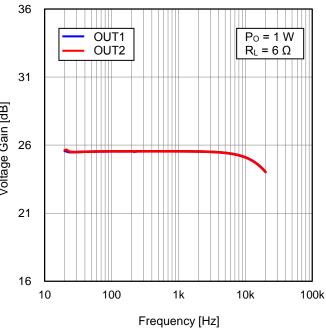

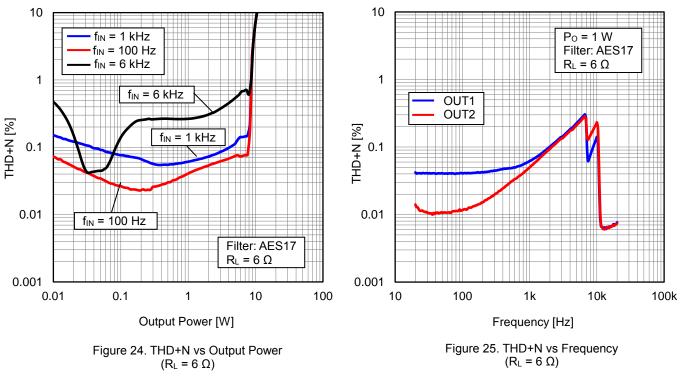

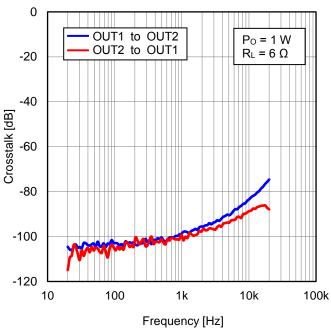

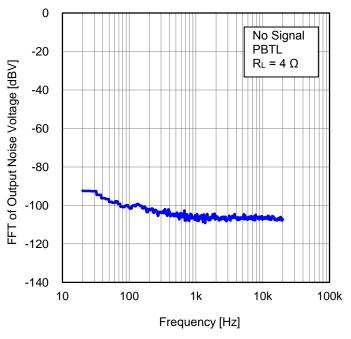

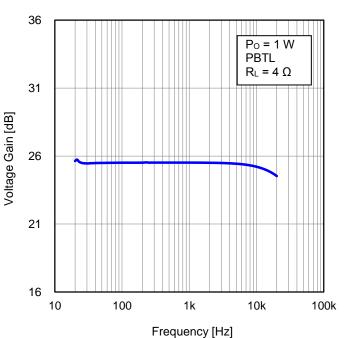

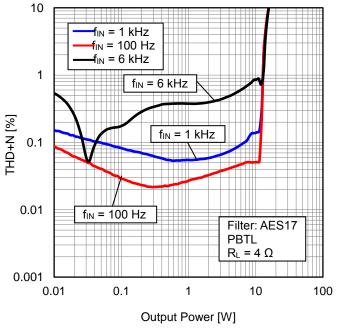

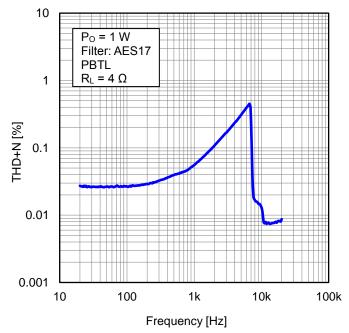

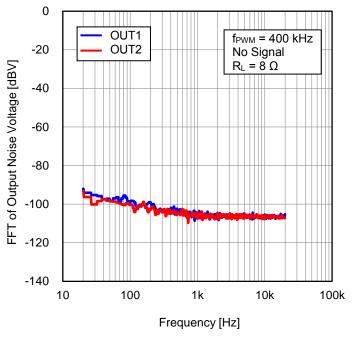

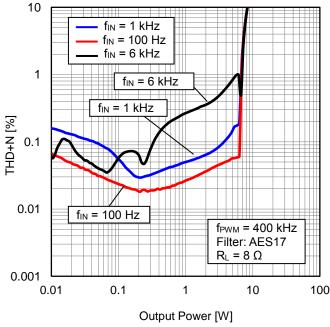

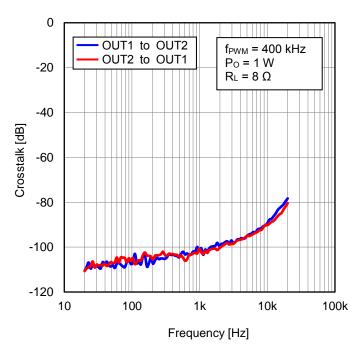

#### **Typical Performance Curves**

Figure 5. Standby Current vs Supply Voltage (Power Down)

Figure 6. Circuit Current vs Supply Voltage (MUTE, ACTIVE)

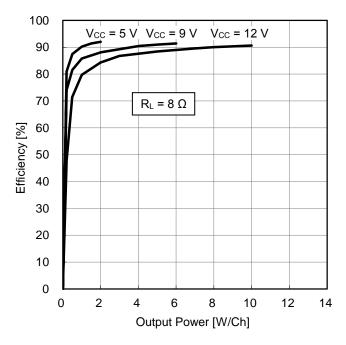

Figure 7. Efficiency vs Output Power  $(R_L = 8 \Omega)$

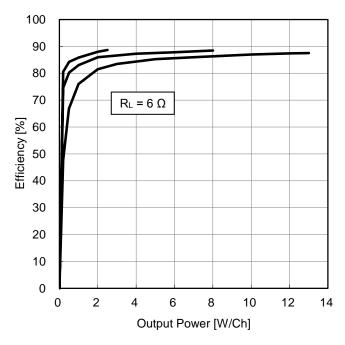

Figure 8. Efficiency vs Output Power  $(R_L = 6 \Omega)$

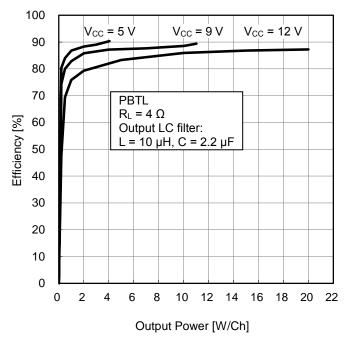

Figure 9. Efficiency vs Output Power (PBTL,  $R_L = 4 \Omega$ )

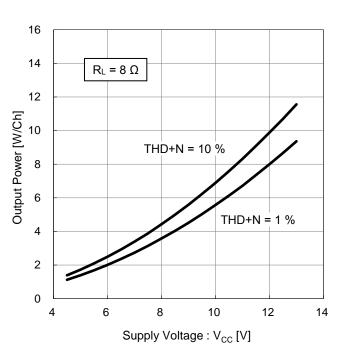

Figure 10. Output Power vs Supply Voltage ( $R_L = 8 \Omega$ )

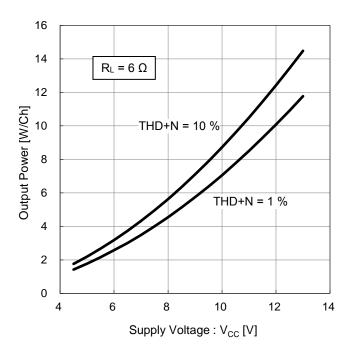

Figure 11. Output Power vs Supply Voltage  $(R_L = 6 \Omega)$

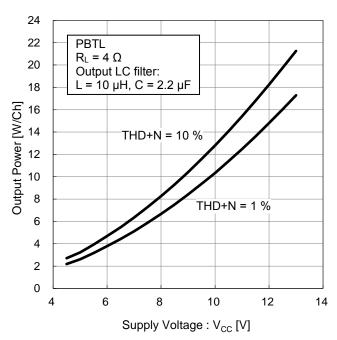

Figure 12. Output Power vs Supply Voltage (PBTL,  $R_L = 4 \Omega$ )

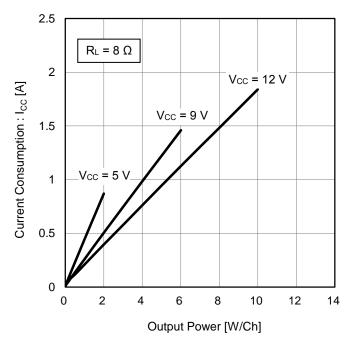

Figure 13. Current Consumption vs Output Power  $(R_L = 8 \Omega)$

Figure 14. Current Consumption vs Output Power  $(R_L = 6 \Omega)$

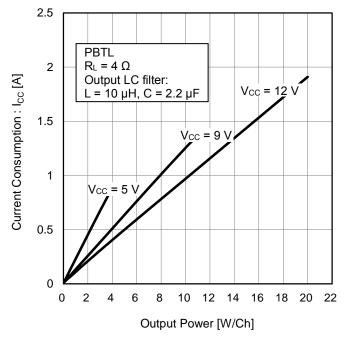

Figure 15. Current Consumption vs Output Power (PBTL,  $R_L = 4 \Omega$ )

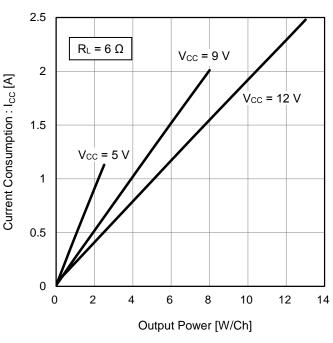

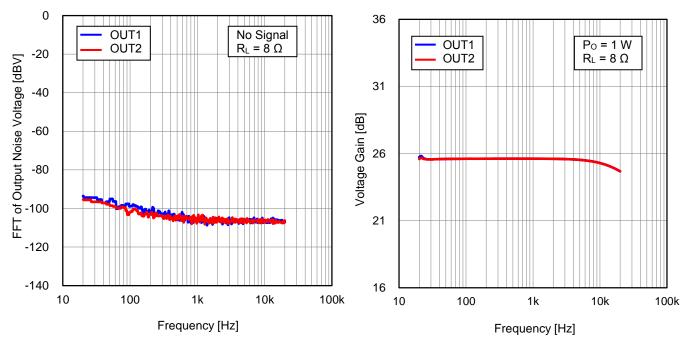

Figure 16. FFT of Output Noise Voltage vs Frequency ( $R_L$  = 8  $\Omega$ )

Figure 17. Voltage Gain vs Frequency  $(R_L = 8 \Omega)$

Figure 18. THD+N vs Output Power  $(R_L = 8 \Omega)$

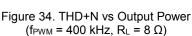

Figure 19. THD+N vs Frequency  $(R_L = 8 \Omega)$

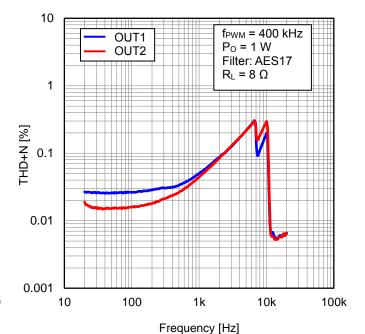

Figure 20. Crosstalk vs Output Power  $(R_L = 8 \Omega)$

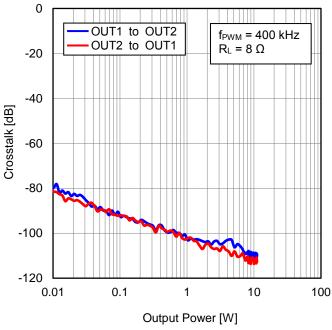

Figure 21. Crosstalk vs Frequency  $(R_L = 8 \Omega)$

Figure 22. FFT of Output Noise Voltage vs Frequency  $(R_L = 6 \Omega)$

Figure 23. Voltage Gain vs Frequency  $(R_L = 6 \Omega)$

0 OUT1 to OUT2  $R_L = 6 \Omega$ OUT2 to OUT1 -20 -40 Crosstalk [dB] -60 -80 -100 -120 0.01 0.1 1 10 100 Output Power [W]

Figure 26. Crosstalk vs Output Power  $(R_L = 6 \Omega)$

Figure 27. Crosstalk vs Frequency  $(R_L = 6 \Omega)$

Figure 28. FFT of Output Noise Voltage vs Frequency (PBTL,  $R_L = 4 \Omega$ )

Figure 29. Voltage Gain vs Frequency (PBTL,  $R_L = 4 \Omega$ )

Figure 30. THD+N vs Output Power (PBTL,  $R_L = 4 \Omega$ )

Figure 31. THD+N vs Frequency (PBTL,  $R_L = 4 \Omega$ )

36

| Fpwm = 400 kHz | Po = 1 W | RL = 8 Ω |

| The state of the state

Figure 32. FFT of Output Noise Voltage vs Frequency ( $f_{PWM} = 400 \text{ kHz}, R_L = 8 \Omega$ )

Figure 33. Voltage Gain vs Frequency ( $f_{PWM} = 400 \text{ kHz}, R_L = 8 \Omega$ )

Figure 35. THD+N vs Frequency (f<sub>PWM</sub> = 400 kHz, R<sub>L</sub> = 8 Ω)

(Unless otherwise specified, Ta = 25  $^{\circ}$ C, V<sub>CC</sub> = 11 V, f<sub>IN</sub> = 1 kHz, PDX = 3.3 V, MUTEX = 3.3 V, PLIMT = 0 V, Gain = 26 dB, Output LC filter: L = 15 μH, C = 1 μF when  $V_{CC} > 11 \text{ V}$ , snubber circuit is added: C = 680 pF,  $R = 5.6 \Omega$ )

Figure 36. Crosstalk vs Output Power

$(f_{PWM} = 400 \text{ kHz}, R_L = 8 \Omega)$

Figure 37. Crosstalk vs Frequency  $(f_{PWM} = 400 \text{ kHz}, R_L = 8 \Omega)$

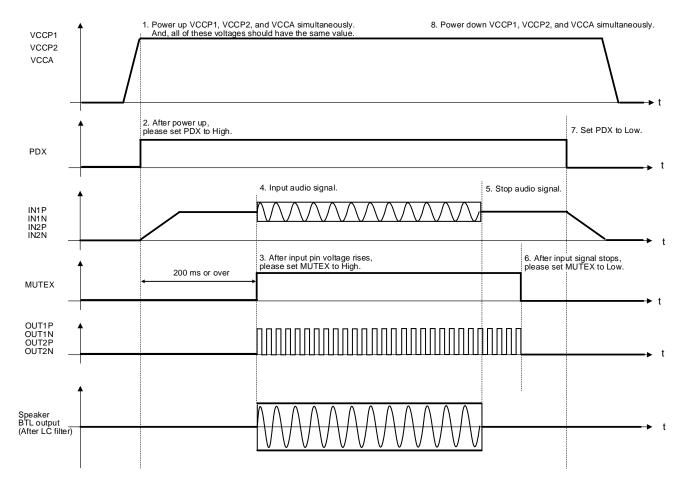

# **Timing Chart**

Figure 38. Power Up/Down Sequence

#### **Function Descriptions**

1 The Setting of Power Down and Mute

| Pin Setting |              | Norn                                         | nal                         | ERROR Detection                              |                                       |  |

|-------------|--------------|----------------------------------------------|-----------------------------|----------------------------------------------|---------------------------------------|--|

| PDX         | MUTEX        | PWM output                                   | ERRORX                      | PWM output                                   | ERRORX<br>Output <sup>(Note 15)</sup> |  |

|             |              | OUT1P, 1N, 2P, 2N                            | Output <sup>(Note 15)</sup> | OUT1P, 1N, 2P, 2N                            | Output(Moto 70)                       |  |

| Low         | Low/<br>High | High-Z_Low <sup>(Note 14)</sup><br>(Standby) | High                        | High-Z_Low <sup>(Note 14)</sup><br>(Standby) | High                                  |  |

| High        | Low          | High-Z_Low <sup>(Note 14)</sup><br>(MUTE_ON) | High                        | High-Z_Low <sup>(Note 14)</sup><br>(MUTE_ON) | Low                                   |  |

| High        | High         | Active<br>(MUTE_OFF)                         | High                        | High-Z_Low <sup>(Note 14)</sup><br>(MUTE_ON) | Low                                   |  |

(Note 14) All power transistors are OFF and output pins are pulled down by 40 k $\Omega$  (Typ). (Note 15) ERRORX is pulled up by 10 k $\Omega$  resistor.

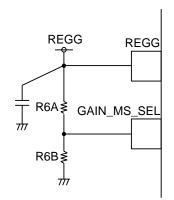

#### 2 Gain and Master/Slave Setting

Master/slave and gain are set by GAIN\_MS\_SEL voltage.

| R6A <sup>(Note 16)</sup><br>(to REGG)<br>[kΩ] | R6B <sup>(Note 16)</sup> (to ground) [kΩ] | Master/Slave | Gain<br>[dB] | Input Impedance<br>(IN1P,IN1N,IN2P,IN2N)<br>[kΩ] |

|-----------------------------------------------|-------------------------------------------|--------------|--------------|--------------------------------------------------|

| 18                                            | Open                                      | Slave        | 36           | 30.0 (Typ)                                       |

| 18                                            | 68                                        | Slave        | 32           | 45.1 (Typ)                                       |

| 33                                            | 68                                        | Slave        | 26           | 79.3 (Typ)                                       |

| 51                                            | 68                                        | Slave        | 20           | 127.9 (Typ)                                      |

| 68                                            | 51                                        | Master       | 36           | 30.0 (Typ)                                       |

| 68                                            | 33                                        | Master       | 32           | 45.1 (Typ)                                       |

| 68                                            | 18                                        | Master       | 26           | 79.3 (Typ)                                       |

| open                                          | 18                                        | Master       | 20           | 127.9 (Typ)                                      |

(Note 16) Please use 1 % tolerance resistor.

Figure 39. GAIN\_MS\_SEL Setting

Setting cannot be changed when LSI is active, but it can be set by rebooting (PDX = High to Low to High).

#### Master/Slave Function

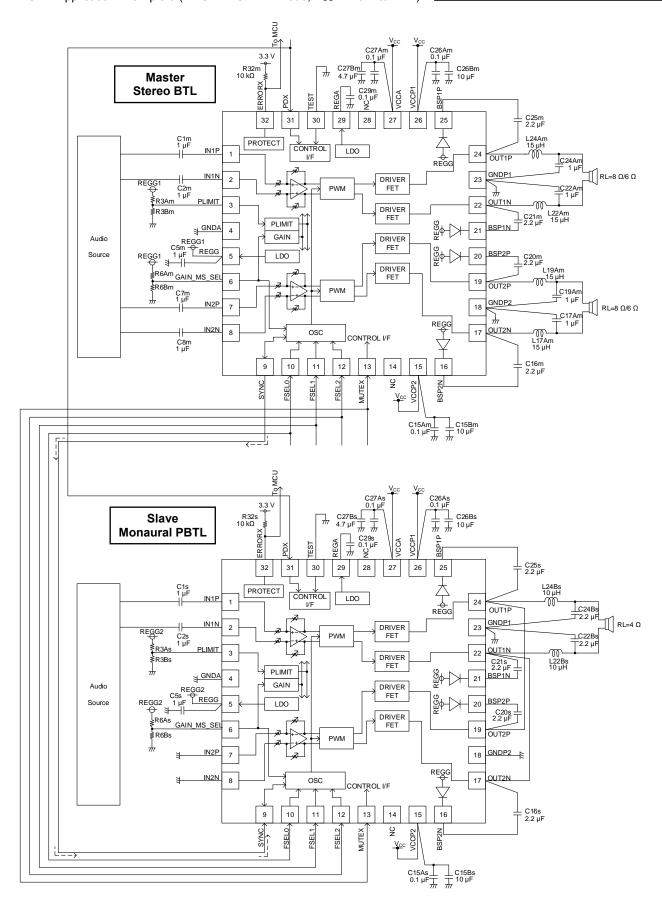

This LSI has master and slave mode, and PWM frequency of two LSIs can be synchronized. In case the LSI is master mode, SYNC becomes signal output pin for synchronization and in case the LSI is slave mode, it becomes signal input pin for synchronization. So, in case PWM frequency of two LSIs need to be synchronized, be sure to connect the SYNC pins each other. Also setting of the FSEL2, FSEL1 and FSEL0 pins of 2 LSIs must be the same.

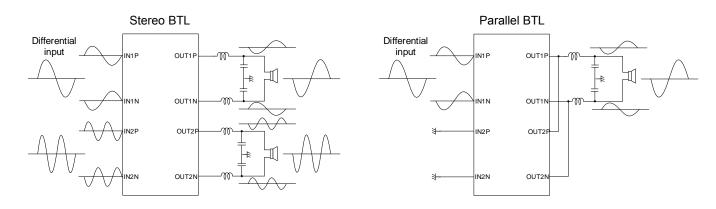

#### 3 Parallel BTL Function

Parallel BTL mode can be set by connecting IN2P and IN2N to ground. Please short OUT1P to OUT2P and OUT1N to OUT2N at near the LSI as much as possible. Do not connect IN1P and IN1N to ground.

Figure 40. Parallel BTL Mode

# **Function Descriptions - continued**

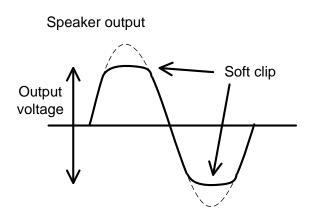

#### 4 Power Limit Function

It is possible to limit the maximum output voltage for protection of speaker.

12 Тур Limited Output Power: PLIM [W] 10 Vcc = 12 V  $R_L = 8 \Omega$ 8 6 4 2 0 0 2 6 4 PLIMIT Voltage: VPLIMIT [V]

Figure 41. Power Limit Waveform

Figure 42. Power Limit

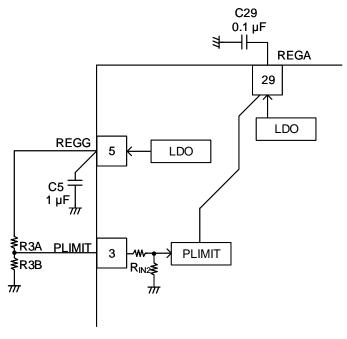

Figure 43. PLIMIT Setting

When the DC voltage is applied to PLIMIT, an output wave is clipped (Figure 41), and output power is limited. The relation between the voltage of PLIMIT ( $V_{\text{PLIMIT}}$ ) and limited output power  $P_{\text{LIM}}$  is shown in Figure 42. It is possible that the voltage  $V_{\text{PLIMIT}}$  is set by connecting external resistance R3A and R3B (Figure 43). The examples of setting R3A and R3B is shown in the table below. In case the power limit function is not used, connect PLIMIT to ground.

| R3A [kΩ]  | R3B [kΩ]        | Max output power $P_{\text{LIM}}$ [W] (R <sub>L</sub> = 8 $\Omega$ ) |             |      |  |  |

|-----------|-----------------|----------------------------------------------------------------------|-------------|------|--|--|

| NOA [KIZ] | K2D [K22]       | Min                                                                  | Тур         | Max  |  |  |

| Open      | Short to ground | -                                                                    | (unlimited) | -    |  |  |

| 12        | 20              | 3.4                                                                  | 6.8         | 13.6 |  |  |

| 10        | 20              | 2.5                                                                  | 5.0         | 10.0 |  |  |

| 8.2       | 20              | 1.7                                                                  | 3.4         | 6.8  |  |  |

#### **Function Descriptions - continued**

In case the power limit function is used under the setting except the table, PLIM is

$$\begin{split} P_{LIM} &= \frac{(V_{REGA} - V_{PLIMIT})^2 \times 39.8}{2R_L} \text{ [W]} \\ V_{PLIMIT} &= \frac{1}{R_{3A}(\frac{1}{R_{3A}} + \frac{1}{R_{3B}} + \frac{1}{R_{IN2}})} V_{REGG} \text{ [V]} \end{split}$$

Where:

$V_{\textit{REGA}}$  is the voltage of REGA, 5.0 V (Typ)

$V_{REGG}$  is the voltage of REGG, 5.55 V (Typ)

$R_{IN2}$  is pull-down resistance of PLIMIT, 200 k $\Omega$  (Typ)

Set the R3A and R3B to become the limited power.

5 FSEL2, FSEL1 and FSEL0 Setting (AM Avoidance Function)

The FSEL2, FSEL1 and FSEL0 pins are used for PWM frequency setting. They can change the PWM frequency like below.

| FSEL2 | FSEL1 | FSEL0 | PWM Frequency [kHz] |

|-------|-------|-------|---------------------|

| High  | High  | High  | 1200 (Typ)          |

| High  | High  | Low   | 1000 (Typ)          |

| High  | Low   | High  | 600 (Typ)           |

| High  | Low   | Low   | 500 (Typ)           |

| Low   | High  | High  | 400 (Typ)           |

Do not set following conditions to become un-recommended frequency:

FSEL2 = Low, FSEL1 = High, FSEL0 = Low

FSEL2 = Low, FSEL1 = Low, FSEL0 = High

FSEL2 = FSEL1 = FSEL0 = Low

#### 6 AM Avoidance Function

PWM frequency is near to AM radio frequency band when this makes interference during AM radio is used, and may negatively affects reception of AM radio wave. This interference can be reduced by adjusting PWM frequency. Below are the recommended settings. For example, when receiving AM radio wave of 1269 kHz in Asia/Europe, PWM frequency must be set to 500 kHz.

| AM Frequency [kHz] |                          | Recommended PWM Frequency Setting |                                                                          |                                                                           |                                                                            |                                                                             |  |  |

|--------------------|--------------------------|-----------------------------------|--------------------------------------------------------------------------|---------------------------------------------------------------------------|----------------------------------------------------------------------------|-----------------------------------------------------------------------------|--|--|

| Americas           | Americas Asia/<br>Europe |                                   | f <sub>PWM</sub> = 500 kHz<br>FSEL2 = High<br>FSEL1 = Low<br>FSEL0 = Low | f <sub>PWM</sub> = 600 kHz<br>FSEL2 = High<br>FSEL1 = Low<br>FSEL0 = High | f <sub>PWM</sub> = 1000 kHz<br>FSEL2 = High<br>FSEL1 = High<br>FSEL0 = Low | f <sub>PWM</sub> = 1200 kHz<br>FSEL2 = High<br>FSEL1 = High<br>FSEL0 = High |  |  |

|                    | 522 to 540               | 0                                 | -                                                                        | 0                                                                         | 0                                                                          | 0                                                                           |  |  |

| 540 to 917         | 540 to 914               | -                                 | 0                                                                        | -                                                                         | 0                                                                          | 0                                                                           |  |  |

| 917 to 1125        | 914 to 1122              | 0                                 | -                                                                        | 0                                                                         | -                                                                          | 0                                                                           |  |  |

| 1125 to 1375       | 1122 to 1373             | -                                 | 0                                                                        | -                                                                         | 0                                                                          | -                                                                           |  |  |

| 1375 to 1547       | 1373 to 1548             | 0                                 | -                                                                        | 0                                                                         | 0                                                                          | 0                                                                           |  |  |

| 1547 to 1700       | 1548 to 1701             | 0                                 | -                                                                        | 0                                                                         | 0                                                                          | 0                                                                           |  |  |

# **Application Examples**

1 Application Circuit Example 1 (Stereo BTL, Vcc = 4.5 V to 11 V)

Overshoot of PWM output occurs depending on the board layout. Be sure to confirm that the voltage of the output pins are lower than absolute maximum ratings. If it exceeds the absolute maximum ratings, snubber circuit need to be added. The example of snubber circuit is shown in the next page.

Figure 44. Application Circuit 1

BOM 1 (Stereo BTL, Vcc = 4.5 V to 11 V)

| Parts     | Qty. | Parts No.                               | Description                                               |

|-----------|------|-----------------------------------------|-----------------------------------------------------------|

|           | 1    | R3A                                     | Dof Function Description 4 Dower Limit Function           |

| Resistor  | 1    | R3B                                     | Ref. Function Description 4 Power Limit Function          |

|           | 1    | R6A                                     | Pof Function Description 2 Cain and Master/Slave Setting  |

|           | 1    | R6B                                     | Ref. Function Description 2 Gain and Master/Slave Setting |

|           | 1    | R32                                     | 10 kΩ, 1/16 W, J (±5 %)                                   |

|           | 4    | C1, C2, C7, C8                          | 1 μF, 16 V, B (±10 %)                                     |

|           | 1    | C5 <sup>(Note 17)</sup>                 | 1 μF, 16 V, B (±10 %)                                     |

|           | 3    | C15A, C26A, C27A <sup>(Note 17)</sup>   | 0.1 μF, 25 V, B (±10 %)                                   |

| Capacitor | 2    | C15B, C26B <sup>(Note 17)</sup>         | 10 μF, 25 V, B (±10 %)                                    |

| Capacitoi | 4    | C16, C20, C21, C25 <sup>(Note 17)</sup> | 2.2 μF, 16 V, B (±10 %)                                   |

|           | 4    | C17A, C19A, C22A, C24A                  | 1 µF, 25 V, B (±10 %)                                     |

|           | 1    | C27B <sup>(Note 17)</sup>               | 4.7 μF, 25 V, B (±10 %)                                   |

|           | 1    | C29 <sup>(Note 17)</sup>                | 0.1 µF, 16 V, B (±10 %)                                   |

| Inductor  | 4    | L17A, L19A, L22A, L24A                  | 15 μH, 2.1 A, ±20 %                                       |

(Note 17) Please place it near pin as much as possible. Also, please mount C15 and C26 as close as possible to the Vcc/ground pin on the same side as the LSI mounted side. Even if Vcc/ground wiring is shorted on the board, either C15 or C26 cannot be removed.

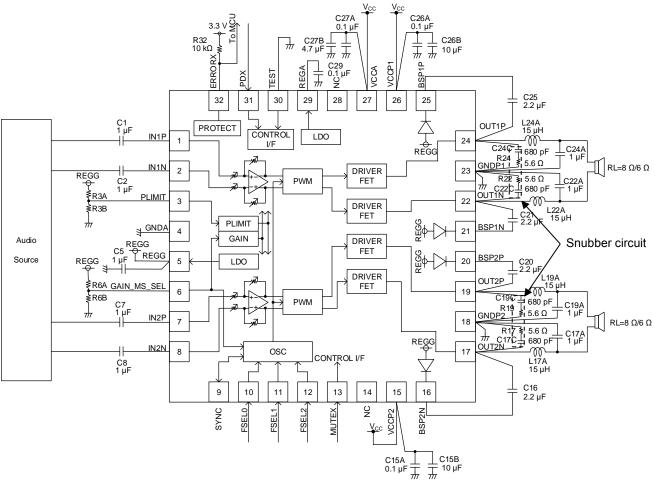

Application Circuit Example 2 (Stereo BTL,  $V_{CC}$  = 11 V to 13 V)

Please add the snubber circuit at the output pins as shown below when  $V_{CC}$  = 11 V to 13 V.

Figure 45. Application Circuit 2

BOM 2 (Stereo BTL, V<sub>CC</sub> = 11 V to 13 V)

| Parts     | Qty. | Parts No.                                      | Description                                               |

|-----------|------|------------------------------------------------|-----------------------------------------------------------|

|           | 1    | R3A                                            | Pof Function Description 4 Dower Limit Function           |

|           | 1    | R3B                                            | Ref. Function Description 4 Power Limit Function          |

| Resistor  | 1    | R6A                                            | Ref. Function Description 2 Gain and Master/Slave Setting |

| Resisioi  | 1    | R6B                                            | Ref. Function Description 2 Gain and Master/Stave Setting |

|           | 1    | R32                                            | 10 kΩ, 1/16 W, J (±5 %)                                   |

|           | 4    | R17, R19, R22, R24 <sup>(Note 18)</sup>        | 5.6 Ω, 1/10 W, J (±5 %)                                   |

|           | 4    | C1, C2, C7, C8                                 | 1 μF, 16 V, B (±10 %)                                     |

|           | 1    | C5 <sup>(Note 18)</sup>                        | 1 μF, 16 V, B (±10 %)                                     |

|           | 3    | C15A, C26A, C27A <sup>(Note 18)</sup>          | 0.1 μF, 25 V, B (±10 %)                                   |

|           | 2    | C15B, C26B <sup>(Note 18)</sup>                | 10 μF, 25 V, B (±10 %)                                    |

| Capacitor | 4    | C16, C20, C21, C25 <sup>(Note 18)</sup>        | 2.2 μF, 16 V, B (±10 %)                                   |

| Capacitoi | 4    | C17A, C19A, C22A, C24A                         | 1 μF, 25 V, B (±10 %)                                     |

|           | 4    | C17C, C19C, C22C,<br>C24C <sup>(Note 18)</sup> | 680 pF, 25 V, B (±10 %)                                   |

|           | 1    | C27B <sup>(Note 18)</sup>                      | 4.7 μF, 25 V, B (±10 %)                                   |

|           | 1    | C29 <sup>(Note 18)</sup>                       | 0.1 μF, 16 V, B (±10 %)                                   |

| Inductor  | 4    | L17A, L19A, L22A, L24A                         | 15 μH, 2.1 A, ±20 %                                       |

(Note 18) Please place it near pin as much as possible. Also, please mount C15 and C26 as close as possible to the V<sub>CC</sub>/ground pin on the same side as the LSI mounted side. Even if V<sub>CC</sub>/ground wiring is shorted on the board, either C15 or C26 cannot be removed.

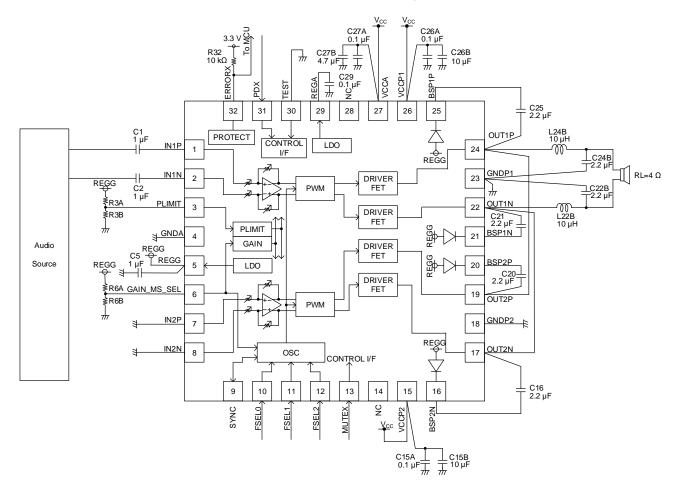

3 Application Circuit Example 3 (Monaural PBTL, V<sub>CC</sub> = 4.5 V to 11 V)

Overshoot of PWM output occurs depending on the board layout. Be sure to confirm that the voltage of the output pins are lower than absolute maximum ratings. If it exceeds the absolute maximum ratings, snubber circuit need to be added. The example of snubber circuit is shown in the next page.

Figure 46. Application Circuit 3

BOM 3 (Monaural PBTL, V<sub>CC</sub> = 4.5 V to 11 V)

| Parts     | Qty. | Parts No.                             | Description                                               |

|-----------|------|---------------------------------------|-----------------------------------------------------------|

|           | 1    | R3A                                   | Pof. Function Description 4 Dower Limit Function          |

|           | 1    | R3B                                   | Ref. Function Description 4 Power Limit Function          |

| Resistor  | 1    | R6A                                   | Ref. Function Description 2 Gain and Master/Slave Setting |

|           | 1    | R6B                                   | Ref. Function Description 2 Gain and Master/Stave Setting |

|           | 1    | R32                                   | 10 kΩ, 1/16 W, J (±5 %)                                   |

|           | 2    | C1, C2                                | 1 μF, 16 V, B (±10 %)                                     |

|           | 1    | C5 <sup>(Note 19)</sup>               | 1 μF, 16 V, B (±10 %)                                     |

|           | 3    | C15A, C26A, C27A <sup>(Note 19)</sup> | 0.1 μF, 25 V, B (±10 %)                                   |

| Canacitar | 2    | C15B, C26B <sup>(Note 19)</sup>       | 10 μF, 25 V, B (±10 %)                                    |

| Capacitor | 4    | C16, C20, C21, C25                    | 2.2 μF, 16 V, B (±10 %)                                   |

|           | 2    | C22B, C24B <sup>(Note 19)</sup>       | 2.2 μF, 25 V, B (±10 %)                                   |

|           | 1    | C27B                                  | 4.7 μF, 25 V, B (±10 %)                                   |

|           | 1    | C29 <sup>(Note 19)</sup>              | 0.1 μF, 16 V, B (±10 %)                                   |

| Inductor  | 2    | L22B, L24B                            | 10 μH, 2.6 A, ±20 %                                       |

(Note 19) Please place it near pin as much as possible. Also, please mount C15 and C26 as close as possible to the Vcc/ground pin on the same side as the LSI mounted side. Even if Vcc/ground wiring is shorted on the board, either C15 or C26 cannot be removed.

4 Application Circuit Example 4 (Monaural PBTL,  $V_{CC}$  = 11 V to 13 V) Please add the snubber circuit at the output pins as shown below when  $V_{CC}$  = 11 V to 13 V.

Figure 47. Application Circuit 4

BOM 4 (Monaural PBTL, Vcc = 11 V to 13 V)

| BOW 4 (Worlaurai PBTL, VCC = 11 V to 13 V) |       |                                         |                                                           |  |  |  |  |

|--------------------------------------------|-------|-----------------------------------------|-----------------------------------------------------------|--|--|--|--|

| Parts                                      | Qty.  | Parts No.                               | Description                                               |  |  |  |  |

|                                            | 1     | R3A                                     | Ref. Function Description 4 Power Limit Function          |  |  |  |  |

|                                            | 1     | R3B                                     | Ref. Function Description 4 Power Limit Function          |  |  |  |  |

| Resistor                                   | 1     | R6A                                     | Pof Function Description 2 Cain and Master/Slave Setting  |  |  |  |  |

| Resisioi                                   | 1     | R6B                                     | Ref. Function Description 2 Gain and Master/Slave Setting |  |  |  |  |

|                                            | 1 R32 |                                         | 10 kΩ, 1/16 W, J (±5 %)                                   |  |  |  |  |

|                                            | 2     | R22, R24 <sup>(Note 20)</sup>           | 5.6 Ω, 1/10 W, J (±5 %)                                   |  |  |  |  |

|                                            | 2     | C1, C2                                  | 1 μF, 16 V, B (±10 %)                                     |  |  |  |  |

|                                            | 1     | C5 <sup>(Note 20)</sup>                 | 1 μF, 16 V, B (±10 %)                                     |  |  |  |  |

|                                            | 3     | C15A, C26A, C27A <sup>(Note 20)</sup>   | 0.1 μF, 25 V, B (±10 %)                                   |  |  |  |  |

|                                            | 2     | C15B, C26B <sup>(Note 20)</sup>         | 10 μF, 25 V, B (±10 %)                                    |  |  |  |  |

| Capacitor                                  | 4     | C16, C20, C21, C25 <sup>(Note 20)</sup> | 2.2 μF, 16 V, B (±10 %)                                   |  |  |  |  |

|                                            | 2     | C22B, C24B                              | 2.2 μF, 25 V, B (±10 %)                                   |  |  |  |  |

|                                            | 2     | C22C, C24C <sup>(Note 20)</sup>         | 680 pF, 25 V, B (±10 %)                                   |  |  |  |  |

|                                            | 1     | C27B <sup>(Note 20)</sup>               | 4.7 μF, 25 V, B (±10 %)                                   |  |  |  |  |

|                                            | 1     | C29 <sup>(Note 20)</sup>                | 0.1 μF, 16 V, B (±10 %)                                   |  |  |  |  |

| Inductor                                   | 2     | L22B, L24B                              | 10 μH, 2.6 A, ±20 %                                       |  |  |  |  |

(Note 20) Please place it near pin as much as possible. Also, please mount C15 and C26 as close as possible to the Vcc/ground pin on the same side as the LSI mounted side. Even if Vcc/ground wiring is shorted on the board, either C15 or C26 cannot be removed.

5 Application Example 5 (MASTER/SLAVE mode, V<sub>CC</sub> = 4.5 V to 11 V)

This GAIN\_MS\_SEL setting is one example. So, another Gain setting can be used.

Figure 48. Application Circuit 5

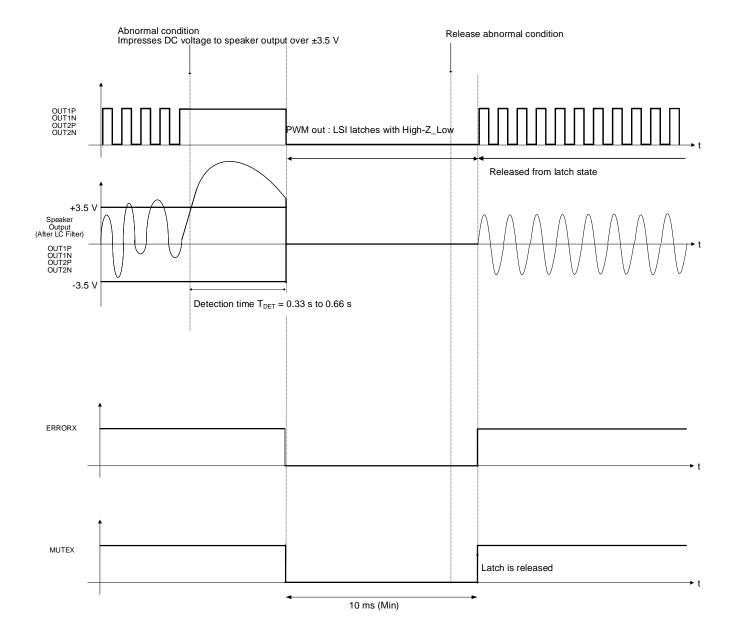

#### **About the Protection Function**

| Protection<br>Function                 |                                                                                                | Detecting & Releasing Condition              | PWM Output<br>OUT1P, 1N, 2P, 2N            | ERRORX<br>Output <sup>(Note 21)</sup> |

|----------------------------------------|------------------------------------------------------------------------------------------------|----------------------------------------------|--------------------------------------------|---------------------------------------|

| Output Short<br>Protection             | Detecting Condition Detecting Current = 8 A (Typ)                                              |                                              | High-Z_Low<br>(Latch) <sup>(Note 22)</sup> | Low<br>(Latch) <sup>(Note 22)</sup>   |

| DC Voltage<br>Protection at<br>Speaker | Detecting Condition DC voltage is ±3.5 V (Typ) or more for a period of 0.33 s to 0.66 s (Typ). |                                              | High-Z_Low<br>(Latch) <sup>(Note 22)</sup> | Low<br>(Latch) <sup>(Note 22)</sup>   |

| Overheat                               | Detecting Condition                                                                            | Chip temperature is 150 °C (Typ) or more.    | High-Z_Low                                 | Low                                   |

| Protection                             | Releasing<br>Condition                                                                         | Chip temperature is 120 °C (Typ) or less.    | Active                                     | LOW                                   |

| Under Voltage                          | Detecting<br>Condition                                                                         | Power supply voltage is 4.0 V (Typ) or less. | High-Z_Low                                 | Lligh                                 |

| Protection                             | Releasing<br>Condition                                                                         | Power supply voltage is 4.1 V (Typ) or more. | Active                                     | High                                  |

<sup>(</sup>Note 21) ERRORX is pulled up by 10 k $\Omega$  resistor.

<sup>(</sup>Note 27) Entertor to planed up by to ker resistent

(Note 22) Once an LSI is latched, the circuit is not released automatically even after an abnormal status is gone.

The following procedures 1. or 2. is available for recovery.

1. After turning MUTEX pin to Low (holding time to Low = 10 ms (Min)), turn back to High again.

<sup>2.</sup> Restore power supply after dropping to power supply voltage Vcc < 3 V (10 ms (Min) holding) which internal power on reset circuit activates.

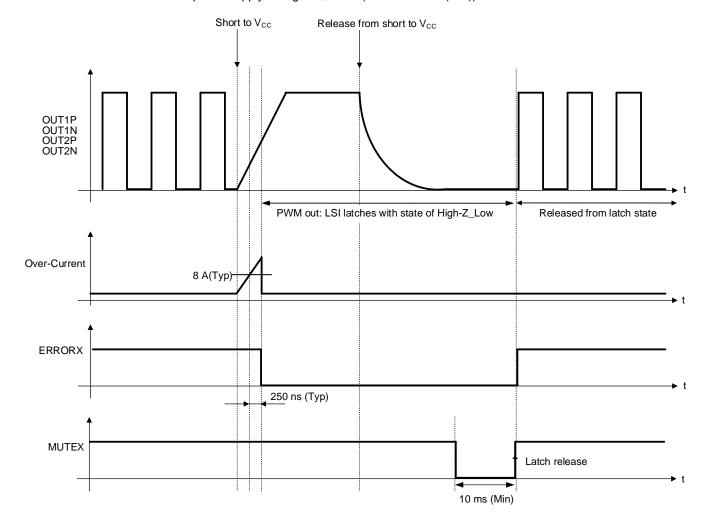

Output Short Protection (Short to the Power Supply Protection)

This LSI has PWM output short protection circuit that stops the PWM output when the output speaker is short-circuited to the power supply (Vcc) unintentionally.

Detecting Condition - It will detect when MUTEX is set High and the current that flows into the PWM output pin becomes 8 A (Typ) or more for 250 ns (Typ). When the protection function starts, it stops the

PWM output and latch output pins to High-Z\_Low. Latch can be released by the next "1" or "2".

Releasing Method -

1. After turning the MUTEX pin to Low (holding time to Low = 10 ms (Min)), turn back to High

2. Restore power supply after the voltage dropped to internal power on reset circuit activating power supply voltage  $V_{CC} < 3 \text{ V (hold for 10 ms (Min))}$ .

Figure 49. Output Short to the Power Supply Protection Sequence

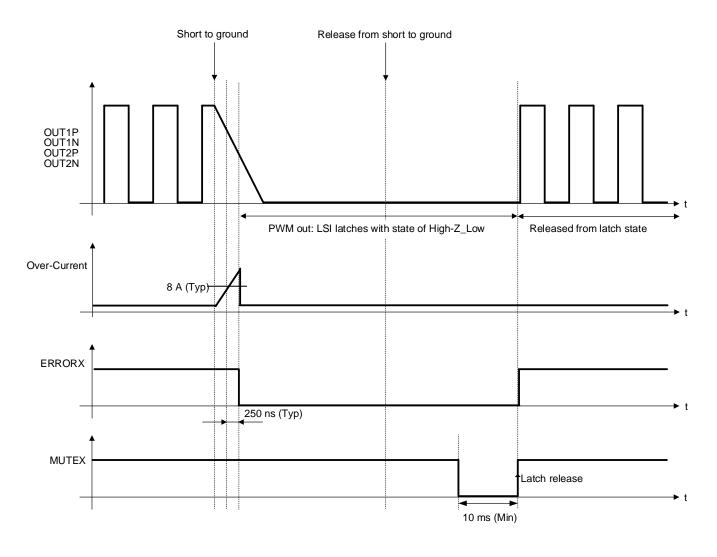

2 Output Short Protection (Short to ground)

This LSI has PWM output short protection circuit that stops the PWM output when the output speaker is short-circuited to ground unintentionally.

Detecting Condition - It will detect when MUTEX is set High and the current that flows into the PWM output pin becomes 8 A (Typ) or more for 250 ns (Typ). When the protection function starts, it stops the

PWM output and latch output pins to High-Z\_Low.

Releasing Method - Latch can be released by the next "1" or "2".

1. After turning the MUTÉX pin to Low (holding time to Low = 10ms (Min)), turn back to High again.

2. Restore power supply after the voltage dropped to internal power on reset circuit activating power supply voltage Vcc < 3 V (hold for 10 ms (Min)).

Figure 50. Output Short to GND Protection Sequence

3 DC Voltage Protection at speaker

This LSI is integrated with DC voltage protection circuit. When DC voltage is applied to the speaker unintentionally, speaker output will mute, and this protection will prevent the speaker from destruction.

Detecting Condition - In case that the voltage of speaker output is  $\pm 3.5$  V (Typ) or more in the time interval 0.33 s to

0.66 s (Typ) or more under the condition MUTEX is set to High the protection function starts. When the protection function starts, it stops the PWM output and latch output pins to

High-Z\_Low.

Releasing Method - Latch can be released by the next "1" or "2".

1. After turning the MUTÉX pin to Low (holding time to Low = 10 ms (Min)), turn back to High again.

2. Restore power supply after the voltage dropped to internal power on reset circuit activating power supply voltage  $V_{CC} < 3 \text{ V}$  (hold for 10 ms (Min)).

Figure 51. DC Voltage Protection at Speaker Sequence

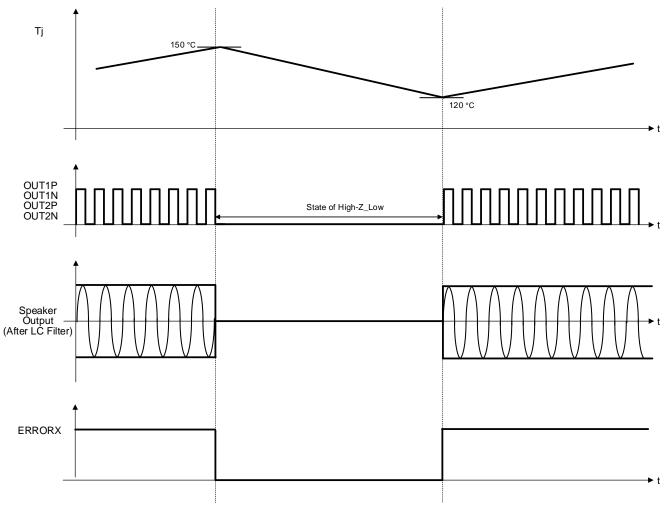

#### 4 Overheat Protection

This LSI has overheat protection circuit that prevents thermal runaway under an abnormal state for the chip temperature exceeded Tjmax = 150 °C (Typ).

Detecting Condition - It will detect when MUTEX is set High and the temperature of the chip becomes 150 °C

(Typ) or more. When the protection circuit is activated, the speaker output instantly goes to

the state of High-Z\_Low.

Releasing Condition - It will release when MUTEX is set High and the temperature of the chip becomes 120 °C

(Typ) or less. The speaker output is back to its normal operation immediately when

released. (Auto recovery)

Figure 52. Overheat Protection Sequence

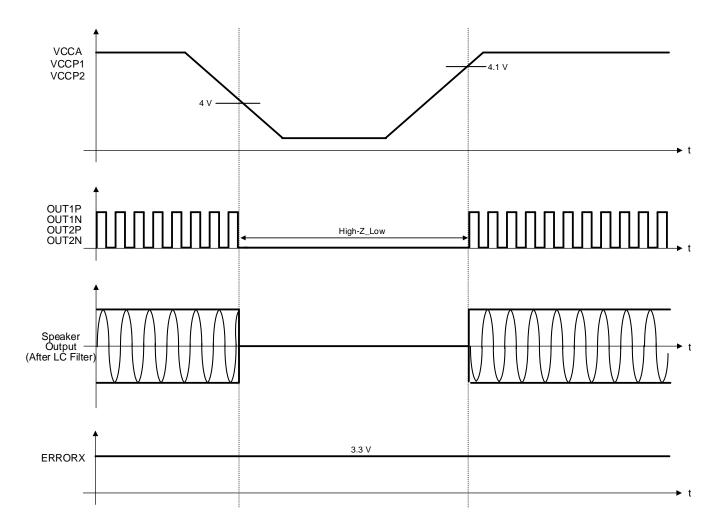

#### 5 Under Voltage Protection

This LSI has under voltage protection circuit that mutes the output speaker once extreme drop in the power supply voltage is detected.

Detecting Condition - It will detect when MUTEX is set High and the power supply voltage becomes 4 V or under f(Typ). When under voltage protection circuit is activated, the speaker output instantly goes to the state of High-Z\_Low.

Releasing Condition - It will release when MUTEX is set High and the power supply voltage becomes 4.1 V or over (Typ). The speaker output is back to its normal operation immediately when released. (Auto recovery)

Figure 53. Under Voltage Protection Sequence

#### **Selecting External Components**

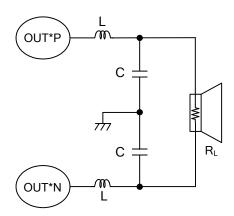

#### 1 Output LC Filter Circuit

This LSI uses output PWM frequencies any of 400 kHz, 500 kHz, 600 kHz, 1000 kHz or 1200 kHz. Since the current necessary for driving the speaker is supplied through a speaker cable with a long wiring length, the PWM frequency and harmonic components are emitted as EMI noise. Therefore, LC filter is required to eliminate EMI noise.

This section takes an example of an LC type LPF shown below, in which coil L and capacitor C compose a differential filter with an attenuation property of -12 dB/oct. A large part of switching currents flow to capacitor C, and only a small part of the currents flow to speaker  $R_L$ . This filter reduces unwanted emission this way.

The following shows output LC filter constants and cutoff frequencies  $f_{\text{C}}$  with typical load impedances.

#### Stereo BTL

| RL       | L     | L C  |        |

|----------|-------|------|--------|

| 6 Ω, 8 Ω | 15 µH | 1 μF | 41 kHz |

#### Monaural PBTL

| RL  | L     | С      | f <sub>C</sub> |

|-----|-------|--------|----------------|

| 4 Ω | 10 μH | 2.2 µF | 34 kHz         |

Figure 54. Output LC Filter

Use inductors with low ESR (equivalent series resistance) and with sufficient margin of allowable currents. Power loss will increase if inductors with high ESR are used.

Select a closed magnetic circuit type product in normal cases to prevent emission noise.

Use capacitors with low ESR, and good impedance characteristics at high frequency ranges (100 kHz or higher). Also, select an item with sufficient voltage rating because massive amount of high-frequency current flow is expected.

#### 2 Snubber Circuit Constant

When overshoot/undershoot of PWM Output exceeds absolute maximum rating, or when overshoot/undershoot of PWM output negatively affects EMI noise, snubber circuit is used as shown below. And if  $V_{CC} > 11 \text{ V}$ , the snubber circuit must be added.

The following table shows ROHM recommended value of "Snubber filter constants" when using ROHM board.

Stereo BTL

| $R_{L}$ | С                      | R                      |

|---------|------------------------|------------------------|

| 6 Ω     | 680 pF, 25 V B (±10 %) | 5.6 Ω, 1/10 W J (±5 %) |

| 8Ω      | 680 pF, 25 V B (±10 %) | 5.6 Ω, 1/10 W J (±5 %) |

#### Monaural PBTL

| $R_L$ | С                      | R                      |

|-------|------------------------|------------------------|

| 4 Ω   | 680 pF, 25 V B (±10 %) | 5.6 Ω, 1/10 W J (±5 %) |

Figure 55. Snubber Circuit

Caution 1: If the impedance characteristics of the speakers at high-frequency range rise sharply, the LSI might not have stable operation in the resonance frequency range of the LC filter. Therefore, consider adding damping-circuit, etc., depending on the impedance of the speaker.

Caution 2: This LSI has a short protection function. In case that speaker output is shorted to V<sub>CC</sub> or ground, over current occurs and short protection function starts. Be careful about that back electromotive force of the inductor in LC filter cause output over/undershoot, and the voltage of the output pins may exceed the maximum standard ratings, which leads to LSI destruction.

# Selecting External Components - continued

# 3 Operating condition with the application component

| Dorometer                      | Parts No.             |                          | Limit |                           | Unit  | Conditions                                                                        |

|--------------------------------|-----------------------|--------------------------|-------|---------------------------|-------|-----------------------------------------------------------------------------------|

| Parameter                      | Parts No.             | Min                      | Тур   | Max                       | Ullit | Conditions                                                                        |

| Tolerance of Capacitor for BSP | C16, C20,<br>C21, C25 | 1.0 <sup>(Note 23)</sup> | 2.2   | 2.95 <sup>(Note 24)</sup> | μF    | B characteristics, Rated voltage 16 V or more, Ceramic type capacitor recommended |

(Note 23) Set the capacitance not to be less than the minimum value in consideration of temperature characteristics and DC-bias properties. (Note 24) It is the value in consideration of ±10 % tolerance of capacitance and 22 % capacitance change rate. Please use the capacitor within this rating.

#### **Operational Notes**

#### 1. Reverse Connection of Power Supply

Connecting the power supply in reverse polarity can damage the LSI. Take precautions against reverse polarity when connecting the power supply, such as mounting an external diode between the power supply and the LSI's power supply pins.

#### 2. Power Supply Lines

Design the PCB layout pattern to provide low impedance supply lines. Furthermore, connect a capacitor to ground at all power supply pins. Consider the effect of temperature and aging on the capacitance value when using electrolytic capacitors.

#### 3. Ground Voltage

Ensure that no pins are at a voltage below that of the ground pin at any time, even during transient condition.

#### 4. Ground Wiring Pattern

When using both small-signal and large-current ground traces, the two ground traces should be routed separately but connected to a single ground at the reference point of the application board to avoid fluctuations in the small-signal ground caused by large currents. Also ensure that the ground traces of external components do not cause variations on the ground voltage. The ground lines must be as short and thick as possible to reduce line impedance.

#### 5. Recommended Operating Conditions

The function and operation of the LSI are guaranteed within the range specified by the recommended operating conditions. The characteristic values are guaranteed only under the conditions of each item specified by the electrical characteristics.

#### 6. Inrush Current

When power is first supplied to the LSI, it is possible that the internal logic may be unstable and inrush current may flow instantaneously due to the internal powering sequence and delays, especially if the LSI has more than one power supply. Therefore, give special consideration to power coupling capacitance, power wiring, width of ground wiring, and routing of connections.

#### 7. Testing on Application Boards

When testing the LSI on an application board, connecting a capacitor directly to a low-impedance output pin may subject the LSI to stress. Always discharge capacitors completely after each process or step. The LSI's power supply should always be turned off completely before connecting or removing it from the test setup during the inspection process. To prevent damage from static discharge, ground the LSI during assembly and use similar precautions during transport and storage.

#### 8. Inter-pin Short and Mounting Errors

Ensure that the direction and position are correct when mounting the LSI on the PCB. Incorrect mounting may result in damaging the LSI. Avoid nearby pins being shorted to each other especially to ground, power supply and output pin. Inter-pin shorts could be due to many reasons such as metal particles, water droplets (in very humid environment) and unintentional solder bridge deposited in between pins during assembly to name a few.

#### 9. Unused Input Pins

Input pins of an LSI are often connected to the gate of a MOS transistor. The gate has extremely high impedance and extremely low capacitance. If left unconnected, the electric field from the outside can easily charge it. The small charge acquired in this way is enough to produce a significant effect on the conduction through the transistor and cause unexpected operation of the LSI. So unless otherwise specified, unused input pins should be connected to the power supply or ground line.

### **Operational Notes - continued**

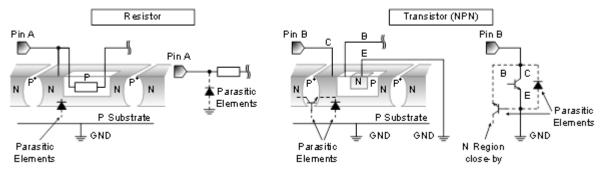

#### 10. Regarding the Input Pin of the LSI

This monolithic LSI contains P+ isolation and P substrate layers between adjacent elements in order to keep them isolated. P-N junctions are formed at the intersection of the P layers with the N layers of other elements, creating a parasitic diode or transistor. For example (refer to figure below):

When ground > Pin A and ground > Pin B, the P-N junction operates as a parasitic diode. When ground > Pin B, the P-N junction operates as a parasitic transistor.

Parasitic diodes inevitably occur in the structure of the LSI. The operation of parasitic diodes can result in mutual interference among circuits, operational faults, or physical damage. Therefore, conditions that cause these diodes to operate, such as applying a voltage lower than the ground voltage to an input pin (and thus to the P substrate) should be avoided

Figure 56. Example of monolithic LSI structure

#### 11. Ceramic Capacitor

When using a ceramic capacitor, determine a capacitance value considering the change of capacitance with temperature and the decrease in nominal capacitance due to DC bias and others.

#### 12. Thermal Shutdown Circuit(TSD)

This LSI has a built-in thermal shutdown circuit that prevents heat damage to the LSI. Normal operation should always be within the LSI's maximum junction temperature rating. If however the rating is exceeded for a continued period, the junction temperature (Tj) will rise which will activate the TSD circuit that will turn OFF power output pins. When the Tj falls below the TSD threshold, the circuits are automatically restored to normal operation.

Note that the TSD circuit operates in a situation that exceeds the absolute maximum ratings and therefore, under no circumstances, should the TSD circuit be used in a set design or for any purpose other than protecting the LSI from heat damage.

#### 13. Over Current Protection Circuit (OCP)

This LSI incorporates an integrated overcurrent protection circuit that is activated when the load is shorted. This protection circuit is effective in preventing damage due to sudden and unexpected incidents. However, the LSI should not be used in applications characterized by continuous operation or transitioning of the protection circuit.

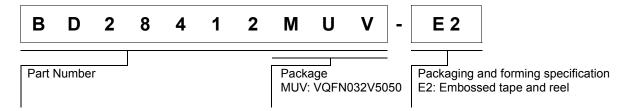

# **Ordering Information**

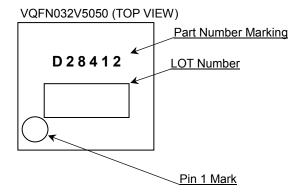

# **Marking Diagram**

**Physical Dimension and Packing Information** Package Name VQFN032V5050 5.  $0\pm0.1$  $0\pm0$ Q 1PIN MARK 0 MAX \_\_\_\_\_  $0.2^{+0}_{-0}$ , 03 22) 0. 08S (0) C0. 2 3.  $4\pm0.1$ 32  $4\pm 0.1$ 0 25 16 24 (UNIT: mm) 17 PKG: VQFN032V5050  $0.25_{\,-0.04}^{\,+0.05}$ 0.75 0. 5  $D\,r\,a\,w\,i\,n\,g\quad N\,o.\ E\,X\,4\,6\,1\,-\,5\,0\,0\,1\,-\,2$ <Tape and Reel information> Embossed carrier tape Tape 2500pcs Quantity Direction ( The direction is the 1pin of product is at the upper left when you hold reel on the left hand and you pull out the tape on the right hand of feed 0 0 0 0 0 0 0 0 TR TR TR TR TR E2 E2 E2 E2 E2 E2 TR Ε1 TL E1 TL E1 TL E1 TL E1 TL Ε1 Direction of feed Pocket Quadrants

**Revision History**

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|-------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 29.Jan.2016 | 001      | New Release                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 06.Jun.2016 | 002      | P.3 to P.5 Pin Description P.7 Absolute Maximum Ratings P.7 Thermal Resistance P.8 Thermal Resistance, Copper Pattern P.9 Electrical Characteristics, Input Impedance 1 P.11 to P.18 Typical Performance Curves P.19 Power Up/Down Sequence Figure 38. P.21 Power Limit Function P.23 to P.27 Application Circuit Example P.35 Operating condition with the application component ADD |  |  |

| 21.Sep.2016 | 003      | P.28 DC voltage protection P.31 DC voltage protection                                                                                                                                                                                                                                                                                                                                 |  |  |

| 15.Feb.2019 | 004      | P.1 Typical Application Circuit Figure 1. P.7 Absolute Maximum Ratings Input Voltage 1 P.10 Typical Performance Curves Figure 5, Figure 6. P.19 Power Up/Down Sequence Figure 38. P.20 (3) Parallel BTL Function P.21 Figure number (41 to 43). P.28 to 31 Japanese font                                                                                                              |  |  |