# 36 V,1 A, Synchronous, Step-Down DC-to-DC Regulator

Data Sheet ADP2441

#### **FEATURES**

Wide input voltage range of 4.5 V to 36 V Low minimum on time of 50 ns Maximum load current of 1 A High efficiency of up to 94% Adjustable output down to 0.6 V ±1% output voltage accuracy Adjustable switching frequency of 300 kHz to 1 MHz Pulse skip mode at light load for power saving Precision enable input pin Open-drain power good External soft start with tracking **Overcurrent-limit protection** Shutdown current of less than 15 µA **UVLO** and thermal shutdown 12-lead, 3 mm × 3 mm LFCSP package Reference similar product ADP2442 with synchronization capability

#### **APPLICATIONS**

Point of load applications

Distributed power systems

Industrial control supplies

Standard rail conversion to 24 V/12 V/5 V/3.3 V

#### **GENERAL DESCRIPTION**

The ADP2441 is a constant frequency, current mode control, synchronous, step-down dc-to-dc regulator that is capable of driving loads up to 1 A with excellent line and load regulation characteristics. The ADP2441 operates with a wide input voltage range of 4.5 V to 36 V, which makes it ideal for regulating power from a wide variety of sources. In addition, the ADP2441 has very low minimum on time (50 ns) and is, therefore, suitable for applications requiring a very high step-down ratio.

The output voltage can be adjusted from 0.6 V to 0.9 V  $\times$  V<sub>IN</sub>. High efficiency is obtained with integrated low resistance N-channel MOSFETs for both high-side and low-side devices.

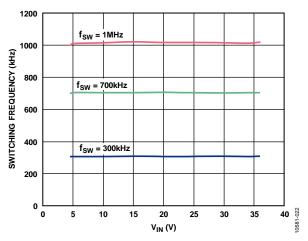

The switching frequency is adjustable from 300 kHz to 1 MHz with an external resistor. The ADP2441 also has an accurate power-good (PGOOD) open-drain output signal.

At light load conditions, the regulator operates in pulse skip mode by skipping pulses and reducing switching losses to improve energy efficiency. In addition, at medium to heavy load conditions, the regulator operates in fixed frequency pulse-width modulation (PWM) mode to reduce electromagnetic interference (EMI).

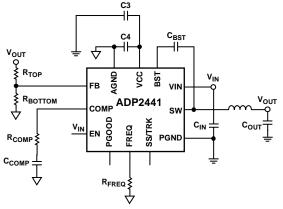

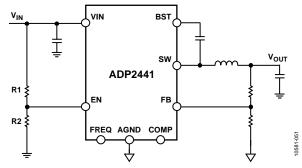

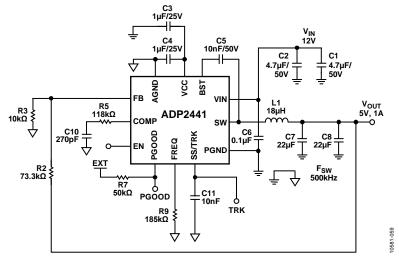

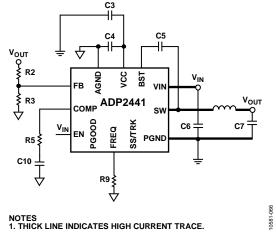

#### TYPICAL CIRCUIT CONFIGURATION

Figure 1.

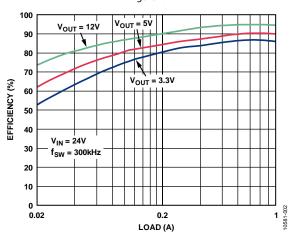

Figure 2. Efficiency vs. Load Current,  $V_{IN} = 24 \text{ V}$

The ADP2441 uses hiccup mode to protect the IC from short circuits or from overcurrent conditions on the output. The external programmable soft start limits inrush current during startup for a wide variety of load capacitances. Other key features include tracking, input undervoltage lockout (UVLO), thermal shutdown (TSD), and precision enable (EN), which can also be used as a logic level shutdown input.

The ADP2441 is available in a 3 mm  $\times$  3 mm, 12-lead LFCSP package and is rated for a junction temperature range of  $-40^{\circ}$ C to  $+125^{\circ}$ C.

# **TABLE OF CONTENTS**

| Features1                                                 |

|-----------------------------------------------------------|

| Applications1                                             |

| General Description1                                      |

| Typical Circuit Configuration1                            |

| Revision History2                                         |

| Specifications3                                           |

| Absolute Maximum Ratings5                                 |

| Thermal Resistance5                                       |

| ESD Caution5                                              |

| Pin Configuration and Function Descriptions6              |

| Typical Performance Characteristics                       |

| Internal Block Diagram14                                  |

| Theory of Operation15                                     |

| Control Architecure                                       |

| Adjustable Frequency                                      |

| Power Good                                                |

| Soft Start                                                |

| Tracking                                                  |

| Undervoltage Lockout (UVLO)17                             |

| Precision Enable/Shutdown                                 |

| Current-Limit and Short-Circuit Protection                |

| Thermal Shutdown                                          |

|                                                           |

| REVISION HISTORY                                          |

| 8/15—Rev. B to Rev. C                                     |

| Changes to Figure 4514                                    |

| 6/14—Rev. A to Rev. B                                     |

| Change to Features Section 1                              |

| •                                                         |

| 11/12—Rev. 0 to Rev. A                                    |

| Changes to Figure 11                                      |

| Changed $I_{VIN}$ Maximum Parameter from 2.2 mA to 2 mA 3 |

| Changes to Pin 3 and Pin 5 Descriptions6                  |

| Changes to Boost Capacitor Section21                      |

| Changes to Figure 6631                                    |

| Changes to Ordering Guide                                 |

| Applications Information                         | 8 |

|--------------------------------------------------|---|

| Selecting the Output Voltage                     | 8 |

| Setting the Switching Frequency                  | 8 |

| Soft Start                                       | 9 |

| External Components Selection                    | 9 |

| Boost Capacitor                                  | 1 |

| VCC Capacitor                                    | 1 |

| Loop Compensation                                | 1 |

| Large Signal Analysis of the Loop Compensation 2 | 1 |

| Design Example2                                  | 3 |

| Configuration and Components Selection2          | 3 |

| System Configuration                             | 4 |

| Typical Application Circuits2                    | 5 |

| Design Example                                   | 5 |

| Other Typical Circuit Configurations             | 6 |

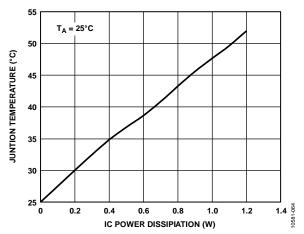

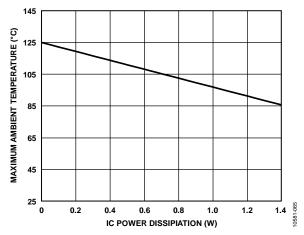

| Power Dissipation and Thermal Considerations2    | 9 |

| Power Dissipation                                | 9 |

| Thermal Considerations                           | 9 |

| Evaluation Board Thermal Performance 3           | 0 |

| Circuit Board Layout Recommendations 3           | 1 |

| Outline Dimensions                               | 2 |

| Ordering Guide                                   | 2 |

6/12—Revision 0: Initial Version

# **SPECIFICATIONS**

$V_{\rm IN}$  = 4.5 V to 36 V,  $T_J$  =  $-40^{\circ} C$  to  $+125^{\circ} C$  , unless otherwise noted.

Table 1.

| Parameter                                   | Symbol                  | <b>Test Conditions/Comments</b>                       | Min   | Тур   | Max                 | Unit   |

|---------------------------------------------|-------------------------|-------------------------------------------------------|-------|-------|---------------------|--------|

| POWER SUPPLY                                |                         |                                                       |       |       |                     |        |

| Input Voltage Range                         | V <sub>IN</sub>         |                                                       | 4.5   |       | 36                  | V      |

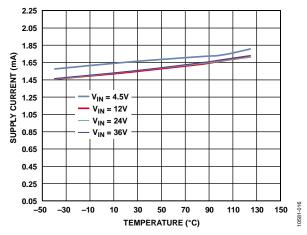

| Supply Current                              | I <sub>VIN</sub>        | $V_{EN} = 1.5 V$ not switching                        |       | 1.7   | 2                   | mA     |

| Shutdown Current                            | I <sub>SHDN</sub>       | $V_{EN} = AGND$                                       |       | 10    | 15                  | μΑ     |

| UVLO                                        |                         |                                                       |       |       |                     | '      |

| Threshold                                   | V <sub>UVLO</sub>       | V <sub>IN</sub> falling                               | 3.8   | 4     | 4.2                 | V      |

| Hysteresis                                  |                         | 3                                                     |       | 200   |                     | mV     |

| INTERNAL REGULATOR                          |                         |                                                       |       |       |                     |        |

| Regulator Output Voltage                    | Vcc                     | $V_{IN} = 5 \text{ V to } 36 \text{ V}$               |       | 5     | 5.5                 | V      |

| OUTPUT                                      |                         |                                                       |       |       |                     |        |

| Output Voltage Range                        | V <sub>OUT</sub>        |                                                       | 0.6   |       | $0.9 \times V_{IN}$ | V      |

| Maximum Output Current                      | Іоит                    |                                                       | 1     |       | 0.5 X VIII          | A      |

| Feedback Regulation Voltage                 | V <sub>FB</sub>         | $T_{J} = -40^{\circ}\text{C to } +85^{\circ}\text{C}$ | 0.594 | 0.6   | 0.606               | v      |

| reedback negatation voltage                 | V FB                    | $T_1 = -40^{\circ}\text{C to} + 125^{\circ}\text{C}$  | 0.591 | 0.6   | 0.609               | v      |

| Line Regulation                             |                         | 1) = -40 C t0 +123 C                                  | 0.391 | 0.005 | 0.009               | %/V    |

| _                                           |                         |                                                       |       |       |                     |        |

| Load Regulation                             |                         |                                                       |       | 0.05  |                     | %/A    |

| ERROR AMPLIFIER                             |                         | N 06W                                                 |       | 50    | 200                 |        |

| Feedback Bias Current                       | FB_BIAS                 | $V_{FB} = 0.6 V$                                      | 200   | 50    | 200                 | nA     |

| Transconductance                            | g <sub>m</sub>          | $I_{COMP} = \pm 20 \mu A$                             | 200   | 250   | 300                 | μA/V   |

| Open-Loop Voltage Gain <sup>1</sup>         | Avol                    |                                                       |       | 65    |                     | dB     |

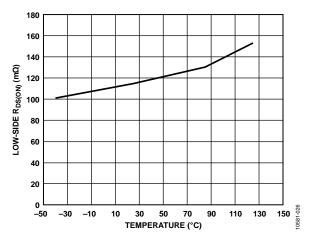

| MOSFETS                                     |                         |                                                       |       |       |                     |        |

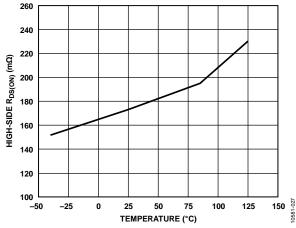

| High-Side Switch On Resistance <sup>2</sup> | R <sub>DS_H(ON)</sub>   | BST - SW = 5 V                                        |       | 170   | 270                 | mΩ     |

| Low-Side Switch On Resistance <sup>2</sup>  | R <sub>DS_L(ON)</sub>   | $V_{CC} = 5 V$                                        |       | 120   | 180                 | mΩ     |

| Leakage Current                             | I <sub>LKG</sub>        | $V_{EN} = AGND$                                       |       | 1     | 25                  | μΑ     |

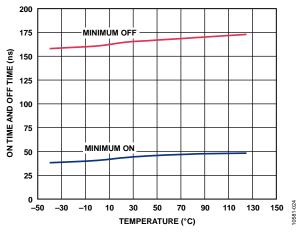

| Minimum On Time <sup>3</sup>                | ton_min                 | All switching frequencies                             |       | 50    | 65                  | ns     |

| Minimum Off Time <sup>4</sup>               | toff_min                |                                                       |       | 165   | 175                 | ns     |

| CURRENT SENSE                               |                         |                                                       |       |       |                     |        |

| Current Sense Amplifier Gain                | G <sub>CS</sub>         |                                                       | 1.6   | 2     | 2.4                 | A/V    |

| Hiccup Time                                 |                         | f <sub>sw</sub> = 300 kHz to1 MHz                     |       | 6     |                     | ms     |

| Number Of Cumulative Current-Limit Cycles   |                         |                                                       |       | 8     |                     | Events |

| to Go into Hiccup Mode                      |                         |                                                       |       |       |                     |        |

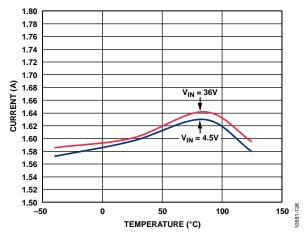

| Peak Current Limit                          | Icl                     |                                                       | 1.4   | 1.6   | 1.8                 | Α      |

| FREQUENCY                                   |                         |                                                       |       |       |                     |        |

| Switching Frequency Range                   | $f_{SW}$                |                                                       | 300   |       | 1000                | kHz    |

| Frequency Set Accuracy                      |                         | FREQ pin = $308 \text{ k}\Omega$                      | 270   | 300   | 330                 | kHz    |

|                                             |                         | FREQ pin = $92.5 \text{ k}\Omega$                     | 900   | 1000  | 1100                | kHz    |

| SOFT START                                  |                         | ·                                                     |       |       |                     |        |

| Soft Start Current                          | Iss                     | $V_{SS} = 0 V$                                        | 0.9   | 1     | 1.2                 | μΑ     |

| PRECISION ENABLE                            |                         |                                                       |       |       |                     | 1      |

| Input Threshold                             | V <sub>EN(RISING)</sub> |                                                       | 1.15  | 1.20  | 1.25                | V      |

| Hysteresis                                  | V <sub>EN(HYST)</sub>   |                                                       |       | 100   | 5                   | mV     |

| Leakage Current                             | IIEN LEAK               | $V_{IN} = V_{EN}$                                     |       | 0.1   | 1                   | μΑ     |

| Thermal Shutdown                            | HEN_LEAK                | A IIA — A EIA                                         |       | 0.1   | •                   | μ,,    |

| Rising                                      | T <sub>SD</sub>         |                                                       |       | 150   |                     | °C     |

| Hysteresis                                  |                         |                                                       |       | 25    |                     | .€     |

| пуѕіегеѕіѕ                                  | T <sub>SD(HYST)</sub>   |                                                       |       | 25    |                     | Ĺ      |

| Parameter                                   | Symbol                  | Test Conditions/Comments | Min | Тур | Max | Unit |

|---------------------------------------------|-------------------------|--------------------------|-----|-----|-----|------|

| POWER GOOD                                  |                         |                          |     |     |     |      |

| PGOOD High, FB Rising Threshold⁵            |                         |                          | 89  | 92  | 95  | %    |

| PGOOD Low, FB Rising Threshold <sup>5</sup> |                         |                          | 111 | 115 | 118 | %    |

| PGOOD High, FB Falling Threshold⁵           |                         |                          | 106 | 109 | 112 | %    |

| PGOOD Low, FB Falling Threshold⁵            |                         |                          | 83  | 86  | 89  | %    |

| PGOOD                                       |                         |                          |     |     |     |      |

| Delay                                       | <b>t</b> PGOOD          |                          |     | 50  |     | μs   |

| High Leakage Current                        | I <sub>PGOOD(SRC)</sub> | $V_{PGOOD} = V_{CC}$     |     | 1   | 10  | μΑ   |

| Pull-Down Resistor                          | I <sub>PGOOD(SNK)</sub> | FB = 0 V                 |     | 0.5 | 0.7 | kΩ   |

| TRK                                         |                         |                          |     |     |     |      |

| TRK Input Voltage Range                     |                         |                          | 0   |     | 600 | mV   |

| TRK to FB Offset Voltage                    |                         | TRK = 0  mV to  500  mV  |     | 10  |     | mV   |

<sup>&</sup>lt;sup>1</sup> Guaranteed by design.

<sup>2</sup> Measured between VIN and SW pins—includes bond wires and pin resistance.

<sup>3</sup> Based on bench characterization. Measured with  $V_{IN} = 12 \text{ V}$ ,  $V_{OUT} = 1.2 \text{ V}$ , load = 1 A,  $f_{SW} = 1 \text{ MHz}$ , and the output in regulation. Measurement does not include dead time.

<sup>4</sup> Based on bench characterization. Measured with  $V_{IN} = 15 \text{ V}$ ,  $V_{OUT} = 12 \text{ V}$ , load = 1 A,  $f_{SW} = 600 \text{ kHz}$ , and the output in regulation. Measurement does not include dead time.

<sup>&</sup>lt;sup>5</sup> This threshold is expressed as a percentage of the nominal output voltage.

### **ABSOLUTE MAXIMUM RATINGS**

Table 2.

| Parameter                             | Rating          |

|---------------------------------------|-----------------|

| VIN to PGND                           | −0.3 V to +40 V |

| EN to AGND                            | −0.3 V to +40 V |

| SW to PGND                            | −0.3 V to +40 V |

| BST to PGND                           | −0.3 V to +45 V |

| VCC to AGND                           | −0.3 V to +6 V  |

| BST to SW                             | −0.3 V to +6 V  |

| FREQ, PGOOD, SS/TRK, COMP, FB to AGND | −0.3 V to +6 V  |

| PGND to AGND                          | ±0.3 V          |

| Operating Junction Temperature Range  | −40°C to +125°C |

| Storage Temperature Range             | −65°C to +150°C |

| Lead Temperature (Soldering, 10 sec)  | 260°C           |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### THERMAL RESISTANCE

$\theta_{JA}$  is specified for the worst-case conditions, that is, a device soldered in a circuit board for surface-mount packages, and is based on a 4-layer standard JEDEC board.

**Table 3. Thermal Resistance**

| Package Type  | θ <sub>JA</sub> | θ <sub>JC</sub> | Unit |

|---------------|-----------------|-----------------|------|

| 12-Lead LFCSP | 40              | 2.4             | °C/W |

#### **ESD CAUTION**

**ESD (electrostatic discharge) sensitive device.**Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

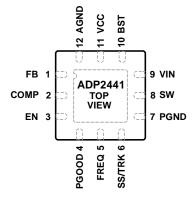

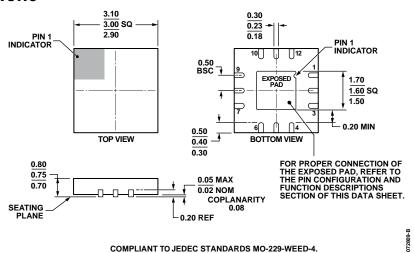

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

NOTES

1. THE EXPOSED PAD SHOULD BE CONNECTED

TO THE SYSTEM AGND PLANE AND PGND PLANE.

Figure 3. Pin Configuration, Top View

**Table 4. Pin Function Descriptions**

| Pin No. | Mnemonic | Description                                                                                                                                                                                                                                                                                                     |  |  |

|---------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1       | FB       | Feedback Regulation Voltage is 0.6 V. Connect this pin to a resistor divider from the output of the dc-to-dc regulator.                                                                                                                                                                                         |  |  |

| 2       | COMP     | Error Amplifier Compensation. Connect a resistor and capacitor in series to ground.                                                                                                                                                                                                                             |  |  |

| 3       | EN       | ecision Enable. This features offers ±5% accuracy when using a 1.25 V reference voltage. Pull this pin high to able the regulator. Do not leave the EN pin floating.                                                                                                                                            |  |  |

| 4       | PGOOD    | Active High Power-Good Output. This pin is pulled low when the output is out of regulation.                                                                                                                                                                                                                     |  |  |

| 5       | FREQ     | Switching Frequency. A resistor to AGND sets the switching frequency (see the Setting the Switching Frequency section). Do not leave the FREQ pin floating.                                                                                                                                                     |  |  |

| 6       | SS/TRK   | Soft Start/Tracking Input. A capacitor to ground is required to program the soft start time, which gradually ramps up the output. A resistive divider to an external reference is required on this pin to track an external voltage.                                                                            |  |  |

| 7       | PGND     | ower Ground. Connect a decoupling ceramic capacitor as close as possible between the VIN pin and this pin.                                                                                                                                                                                                      |  |  |

| 8       | SW       | Switch. The midpoint for the drain of the low-side N-channel power MOSFET switch and the source for the high-sic N-channel power MOSFET switch.                                                                                                                                                                 |  |  |

| 9       | VIN      | Power Supply Input. Connect this pin to the input power source, and connect a bypass ceramic capacitor directly from this pin to PGND, as close as possible to the IC. The operation voltage is 4.5 V to 36 V.                                                                                                  |  |  |

| 10      | BST      | Boost. Connect a 10 nF ceramic capacitor between the BST and SW pins as close to the IC as possible to form a floating supply for the high-side N-Channel power MOSFET driver. This capacitor is needed to drive the gate of the N-channel power MOSFET above the supply voltage.                               |  |  |

| 11      | VCC      | Output of the Internal Low Dropout Regulator. This pin supplies power for the internal controller and driver circuitry. Connect a 1 $\mu$ F ceramic capacitor between VCC and AGND and a 1 $\mu$ F ceramic capacitor between VCC and PGND. The VCC output is active when the EN pin voltage is more than 0.7 V. |  |  |

| 12      | AGND     | Analog Ground. This pin is the internal ground for the control functions. Connect this pin directly to the exposed pad.                                                                                                                                                                                         |  |  |

|         | EP       | Exposed Thermal Pad. The exposed pad should be connected to AGND and PGND.                                                                                                                                                                                                                                      |  |  |

### TYPICAL PERFORMANCE CHARACTERISTICS

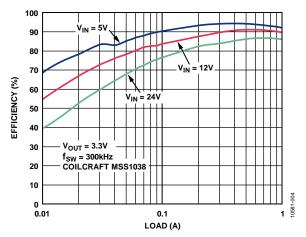

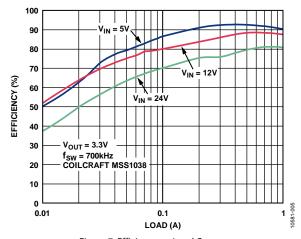

Figure 4. Efficiency vs. Load Current,  $V_{OUT} = 3.3 V$ ,  $f_{SW} = 300 kHz$

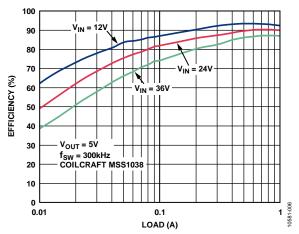

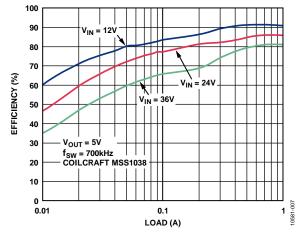

Figure 5. Efficiency vs. Load Current,  $V_{OUT} = 5 V$ ,  $f_{SW} = 300 \text{ kHz}$

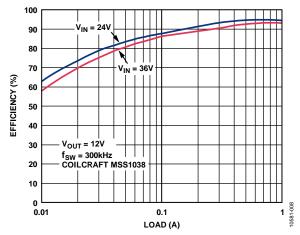

Figure 6. Efficiency vs. Load Current,  $V_{OUT} = 12 \text{ V}, f_{SW} = 300 \text{ kHz}$

Figure 7. Efficiency vs. Load Current,  $V_{OUT} = 3.3 \text{ V}, f_{SW} = 700 \text{ kHz}$

Figure 8. Efficiency vs. Load Current,  $V_{OUT} = 5 V$ ,  $f_{SW} = 700 \text{ kHz}$

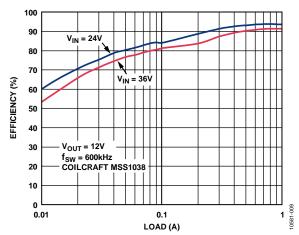

Figure 9. Efficiency vs. Load Current,  $V_{OUT} = 12 V$ ,  $f_{SW} = 600 kHz$

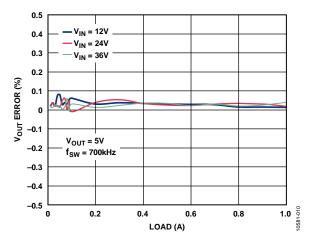

Figure 10. Load Regulation for Different Supplies

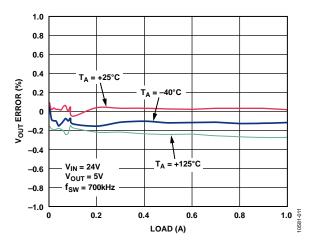

Figure 11. Load Regulation for Different Temperatures

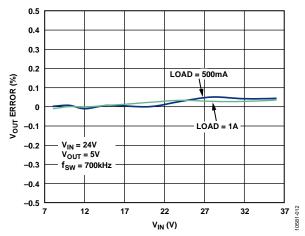

Figure 12. Line Regulation,  $V_{OUT} = 5 V$  for Different Loads

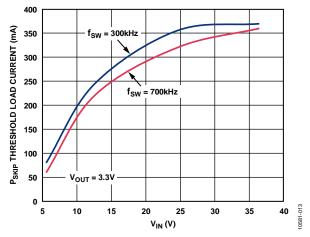

Figure 13. Pulse Skip Threshold,  $V_{OUT} = 3.3 \text{ V}$

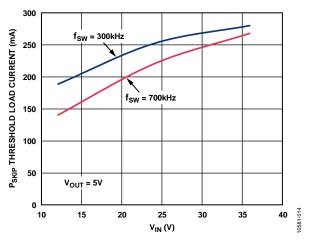

Figure 14. Pulse Skip Threshold,  $V_{OUT} = 5 V$

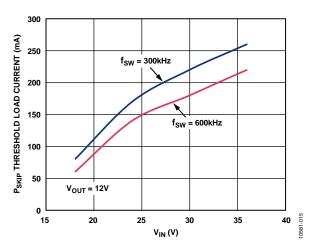

Figure 15. Pulse Skip Threshold,  $V_{OUT} = 12 V$

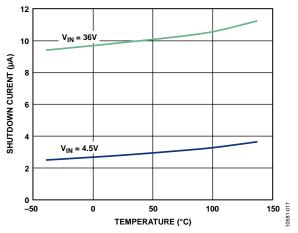

Figure 16. Shutdown Current vs. Temperature

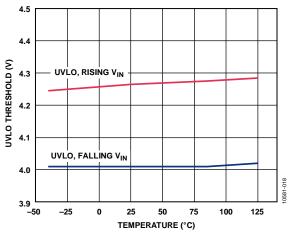

Figure 17. UVLO Threshold vs. Temperature

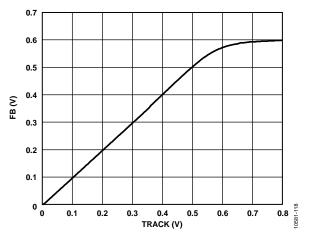

Figure 18. Tracking Range

Figure 19. Supply Current vs. Temperature

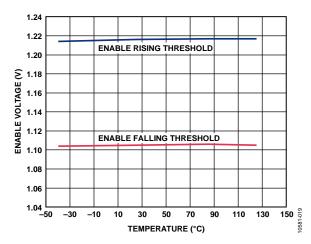

Figure 20. Enable Threshold vs. Temperature

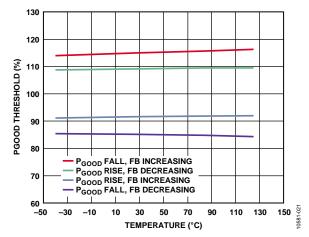

Figure 21. PGOOD Threshold vs. Temperature

Figure 22. Switching Frequency vs. Supply

Figure 23. Minimum On Time and Minimum Off Time vs. Temperature

Figure 24. High-Side R<sub>DS(ON)</sub> vs. Temperature

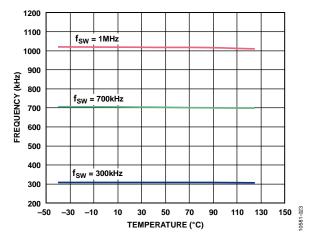

Figure 25. Switching Frequency vs. Temperature

Figure 26. Current Limit vs. Temperature

Figure 27. Low-Side R<sub>DS(ON)</sub> vs. Temperature

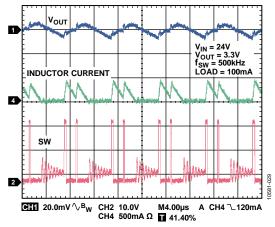

Figure 28. Pulse Skip Mode,  $V_{IN} = 24 \text{ V}, V_{OUT} = 3.3 \text{ V}, f_{SW} = 500 \text{ kHz}, \text{ No Load}$

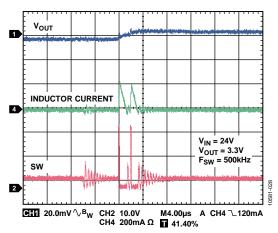

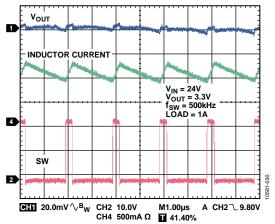

Figure 29. PWM Mode,  $V_{IN} = 24 \text{ V}, V_{OUT} = 3.3 \text{ V}, f_{SW} = 500 \text{ kHz}, Load = 1 \text{ A}$

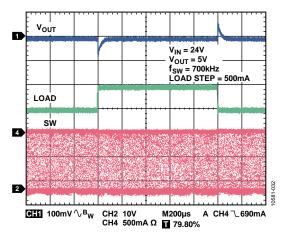

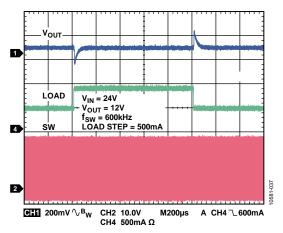

Figure 30. Load Transient Response,  $V_{IN} = 24 \text{ V}$ ,  $V_{OUT} = 5 \text{ V}$ ,  $f_{SW} = 700 \text{ kHz}$ , Load Step = 500 mA

Figure 31. Pulse Skip Mode,  $V_{IN} = 24 \text{ V}, V_{OUT} = 3.3 \text{ V}, f_{SW} = 500 \text{ kHz}, Load = 100 \text{ mA}$

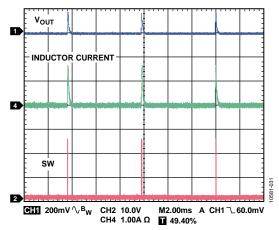

Figure 32. Hiccup Mode,  $V_{IN} = 24 \text{ V}$ ,  $V_{OUT} = 3.3 \text{ V}$ ,  $f_{SW} = 500 \text{ kHz}$ , Output Short to PGND

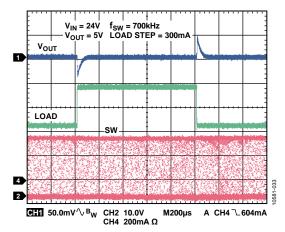

Figure 33. Load Transient Response,  $V_{IN} = 24 \text{ V}$ ,  $V_{OUT} = 5 \text{ V}$ ,  $f_{SW} = 700 \text{ kHz}$ , Load Step = 300 mA

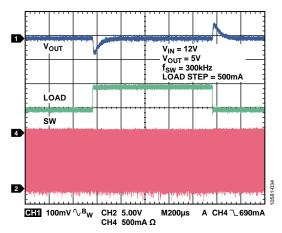

Figure 34. Load Transient Response,  $V_{IN} = 12 \text{ V}, V_{OUT} = 5 \text{ V}, f_{SW} = 300 \text{ kHz}, Load Step = 500 \text{ mA}$

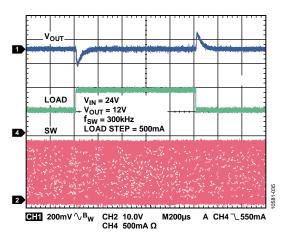

Figure 35. Load Transient Response,  $V_{IN} = 24 \text{ V}$ ,  $V_{OUT} = 12 \text{ V}$ ,  $f_{SW} = 300 \text{ kHz}$ , Load Step = 500 mA

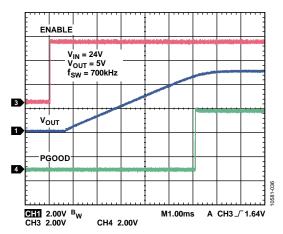

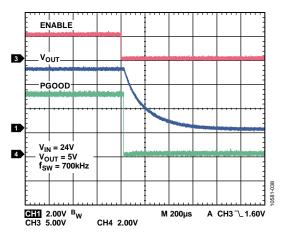

Figure 36. Power Good Startup,  $V_{IN} = 24 \text{ V}$ ,  $V_{OUT} = 5 \text{ V}$ ,  $f_{SW} = 700 \text{ kHz}$

Figure 37. Load Transient Response,  $V_{IN} = 24 \text{ V}$ ,  $V_{OUT} = 12 \text{ V}$ ,  $f_{SW} = 600 \text{ kHz}$ , Load Step = 500 mA

Figure 38. Power-Good Shutdown,  $V_{IN} = 24 \text{ V}, V_{OUT} = 5 \text{ V}, f_{SW} = 700 \text{ kHz}$

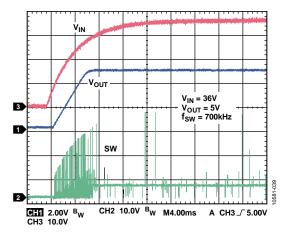

Figure 39. Startup with  $V_{IN}$ ,  $V_{IN} = 36 \text{ V}$ ,  $V_{OUT} = 5 \text{ V}$ ,  $f_{SW} = 700 \text{ kHz}$ , No Load

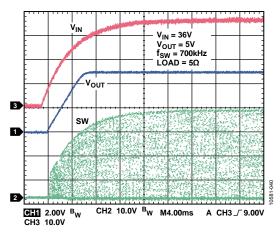

Figure 40. Startup with  $V_{IN}$ ,  $V_{IN} = 36 \text{ V}$ ,  $V_{OUT} = 5 \text{ V}$ ,  $f_{SW} = 700 \text{ kHz}$ ,  $Load = 5 \Omega$

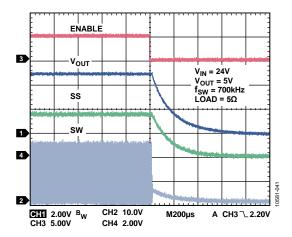

Figure 41. Shutdown with Precision Enable,  $V_{IN} = 24 \text{ V}$ ,  $V_{OUT} = 5 \text{ V}$ ,  $f_{SW} = 700 \text{ kHz}$ , Load =  $5 \Omega$

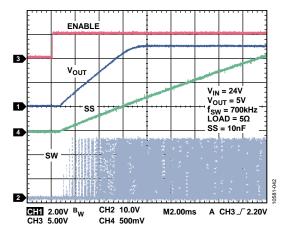

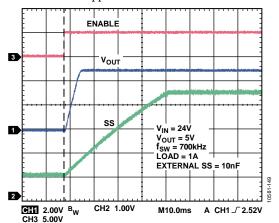

Figure 42. Startup with Precision Enable,  $V_{\rm IN}$  = 24 V,  $V_{\rm OUT}$  = 5 V,  $f_{\rm SW}$  = 700 kHz, Load = 5  $\Omega$ , SS = 10 nF

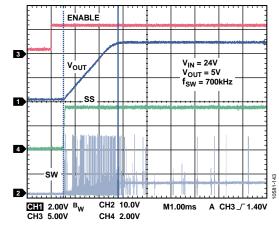

Figure 43. Soft Start Startup with Precision Enable,  $V_{IN} = 24 \text{ V}$ ,  $V_{OUT} = 5 \text{ V}$ ,  $f_{SW} = 700 \text{ kHz}$ , No Load, Internal SS

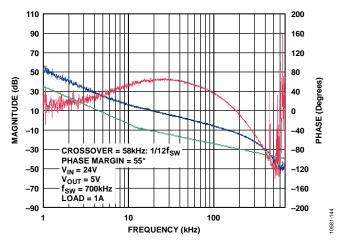

Figure 44. Magnitude and Phase vs. Frequency

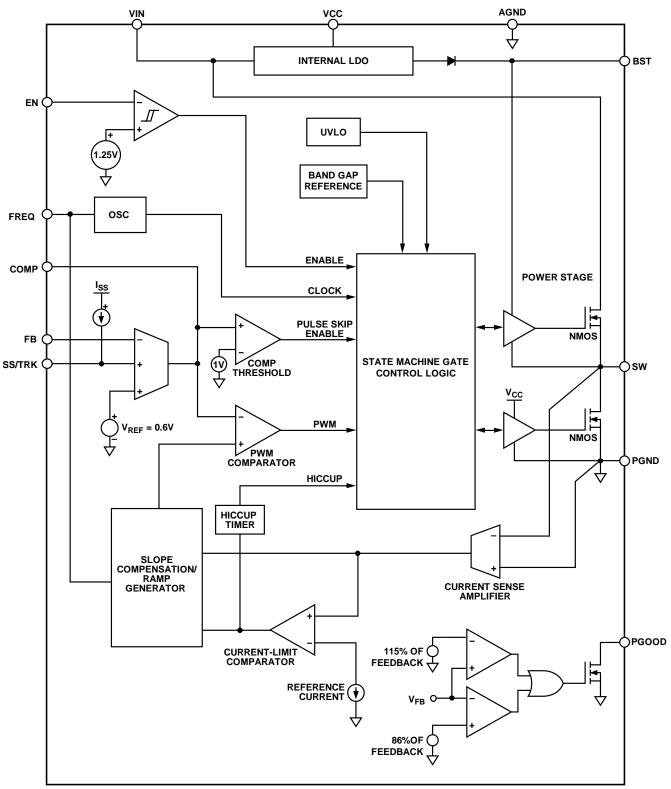

# INTERNAL BLOCK DIAGRAM

Figure 45. Block Diagram

#### THEORY OF OPERATION

The ADP2441 is a fixed frequency, current mode control, step-down, synchronous switching regulator that is capable of driving 1 A loads. The device operates with a wide input voltage range from 4.5 V to 36 V, and its output is adjustable from 0.6 V to 0.9 V  $\times$  V\_{IN}. The integrated high-side N-channel power MOSFET and the low-side N-channel power MOSFET yield high efficiency with medium to heavy loads. Pulse skip mode is available to improve efficiency at light loads.

The ADP2441 includes programmable features, such as soft start, output voltage, switching frequency, and power good. These features are programmed externally via tiny resistors and capacitors. The ADP2441 also includes protection features, such as UVLO with hysteresis, output short-circuit protection, and thermal shutdown.

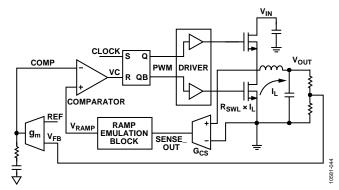

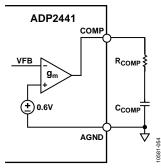

#### **CONTROL ARCHITECURE**

The ADP2441 is based on the emulated peak current mode control architecture.

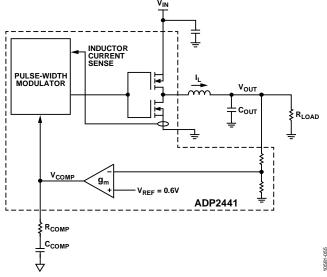

#### Fixed Frequency Mode

A basic block diagram of the control architecture is shown in Figure 46. With medium to heavy loads, the ADP2441 operates in the fixed switching frequency PWM mode. The output voltage, V<sub>OUT</sub>, is sensed on the feedback pin, FB. An error amplifier integrates the error between the feedback voltage and the reference voltage ( $V_{REF} = 0.6 \text{ V}$ ) to generate an error voltage at the COMP pin. A current sense amplifier senses the valley inductor current (I<sub>L</sub>) during the off period when the low-side power MOSFET is on and the high-side power MOSFET is off. An internal oscillator initiates a PWM pulse to turn off the low-side power MOSFET and turn on the high-side power MOSFET at a fixed switching frequency. When the high-side N-channel power MOSFET is enabled, the valley inductor current information is added to an emulated ramp signal, and then the PWM comparator compares this value to the error voltage on the COMP pin. The output of the PWM comparator modulates the duty cycle by adjusting the trailing edge of the PWM pulse that turns off the high-side power MOSFET and turns on the low-side power MOSFET.

Slope compensation is programmed internally into the emulated ramp signal and is automatically selected, depending on the input voltage, output voltage, and switching frequency. This prevents subharmonic oscillations for near or greater than 50% duty cycle operation. The one restriction of this feature is that the inductor ripple current must be set between 0.2 A and 0.5 A to provide sufficient current information to the loop.

Figure 46. Control Architecture Block Diagram

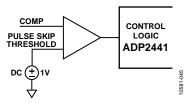

#### **Pulse Skip Mode**

The ADP2441 has built-in pulse skip circuitry that turns on during light loads, switching only as necessary so that the output voltage remains within regulation. This allows the regulator to maintain high efficiency during operation with light loads by reducing switching losses. The pulse skip circuitry includes a comparator, which compares the COMP voltage to a fixed pulse skip threshold.

Figure 47. Pulse Skip Comparator

With light loads, the output voltage discharges at a very slow rate (load dependent). When the output voltage is within regulation, the device enters sleep mode and draws a very small quiescent current. As the output voltage drops below the regulation voltage, the COMP voltage rises above the pulse skip threshold. The device wakes up and starts switching until the output voltage is within regulation.

As the load increases, the settling value of the COMP voltage increases. At a particular load, COMP settles above the pulse skip threshold, and the device enters the fixed frequency PWM mode. Therefore, the load current at which COMP exceeds the pulse skip threshold is defined as the pulse skip current threshold; the value varies with the duty cycle and the inductor ripple current.

The measured value of pulse skip threshold over  $V_{\rm IN}$  is given in Figure 13, Figure 14, and Figure 15.

#### **ADJUSTABLE FREQUENCY**

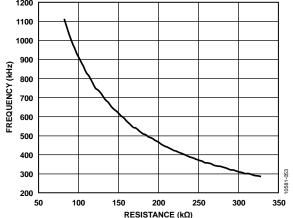

The ADP2441 features a programmable oscillator frequency with a resistor connected between the FREQ and AGND pins.

At power-up, the FREQ pin is forced to 1.2 V and current flows from the FREQ pin to AGND; the current value is based on the resistor value on the FREQ pin. Then, the same current replicates in the oscillator to set the switching frequency. Note that the resistor connected to the FREQ pin should be placed as close as possible to the FREQ pin (see the Applications Information section for more information).

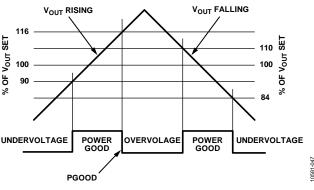

#### **POWER GOOD**

The PGOOD pin is an open-drain output that indicates the status of the output voltage. When the voltage of the FB pin is between 92% and 109% of the internal reference voltage, the PGOOD output is pulled high, provided there is a pull-up resistor connected to the pin. When the voltage of the FB pin is not within this range, the PGOOD output is pulled low to AGND. The PGOOD threshold is shown in Figure 48.

Likewise, the PGOOD pin is pulled low to AGND when the input voltage is below the internal UVLO threshold, when the EN pin is low, or when a thermal shutdown event has occurred.

Figure 48. PGOOD Threshold

In a typical application, a pull-up resistor connected between the PGOOD pin and an external supply is used to generate a logic signal. This pull-up resistor should range in value from 30 k $\Omega$  to 100 k $\Omega$ , and the external supply should be less than 5.5 V.

#### **SOFT START**

The ADP2441 soft start feature allows the output voltage to ramp up in a controlled manner, limiting the inrush current during startup. An external capacitor connected between the SS/TRK and AGND pins is required to program the soft start time.

The programmable soft start feature is useful when a load requires a controlled voltage slew rate at startup. When the regulator powers up and soft start is enabled, the internal 1  $\mu$ A current source charges the external soft start capacitor, establishing a voltage ramp slope at the SS pin, as shown in Figure 49.

The soft start period ends when the soft start ramp voltage exceeds the internal reference of 0.6 V. The ADP2441 also features an internal default soft start time of 2 ms. For more information, see the Applications Information section.

Figure 49. External Soft Start

#### **TRACKING**

The ADP2441 has a tracking feature that allows the output voltage to track an external voltage. This feature is especially useful in a system where power supply sequencing and tracking is required.

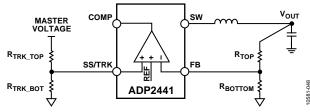

The ADP2441 SS/TRK pin is connected to the internal error amplifier. The internal error amplifier includes three inputs: the internal reference voltage, the SS/TRK voltage, and the feedback voltage. The error amplifier regulates the feedback voltage to the lower of the other two voltages. To track a master voltage, tie the SS/TRK pin to a resistor divider from the master voltage as shown in Figure 50.

Figure 50. Tracking Feature Block Diagram

The ratio of the slave output voltage to the master voltage is a function of the two dividers as follows:

$$\frac{V_{OUT}}{V_{MASTER}} = \frac{\left(1 + \frac{R_{TOP}}{R_{BOTTOM}}\right)}{\left(1 + \frac{R_{TRK\_TOP}}{R_{TRK\_BOT}}\right)}$$

(1)

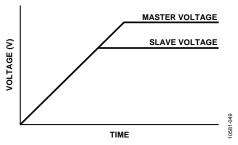

#### **Coincident Tracking**

The most common mode of tracking is coincident tracking. In this method, the slope of the slave voltage matches that of the master voltage, as shown in Figure 51. As the master voltage rises, the slave voltage rises identically. Eventually, the slave voltage reaches its regulation voltage, at which point the internal reference takes over the regulation while the SS/TRK input continues to increase, thus preventing itself from influencing the output voltage.

Figure 51. Coincident Tracking

For coincident tracking, select resistor values such that  $R_{TRK\_TOP} = R_{TOP}$  and  $R_{TRK\_BOT} = R_{BOTTOM}$  in Equation 1.

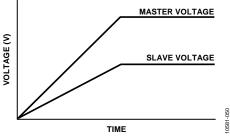

#### **Ratiometric Tracking**

In the ratiometric tracking scheme, the master and the slave voltages rise with different slopes.

Figure 52. Ratiometric Tracking

For ratiometric tracking in which the master voltage rises faster than the slave voltage (as shown in Figure 52), select  $R_{TRK\_TOP} \ge R_{TOP}$  and  $R_{TRK\_BOT} = R_{BOTTOM}$  in Equation 1.

#### **UNDERVOLTAGE LOCKOUT (UVLO)**

The UVLO function prevents the IC from turning on while the input voltage is below the specified operating range to avoid an undesired operating mode. If the input voltage drops below the specified range, the UVLO function shuts off the device. The rising input voltage threshold for the UVLO function is 4.2 V with 200 mV hysteresis. The 200 mV of hysteresis prevents the regulator from turning on and off repeatedly with slow voltage ramp on the VIN pin.

#### PRECISION ENABLE/SHUTDOWN

The ADP2441 features a precision enable pin (EN) that can be used to enable or shut down the device. The  $\pm 5\%$  accuracy lends itself to using a resistor divider from the VIN pin (or another external supply) to program a desired UVLO threshold that is higher than the fixed internal UVLO of 4.2 V. The hysteresis is 100~mV

If a resistor divider is not used, a logic signal can be applied. A logic high enables the device, and a logic low forces the device into shutdown mode.

Figure 53. Precision Enable Used as a Programmable UVLO

# CURRENT-LIMIT AND SHORT-CIRCUIT PROTECTION

The ADP2441 has a current-limit comparator that compares the current sensed across the low-side power MOSFET to the internally set reference current. If the sensed current exceeds the reference current, the high-side power MOSFET is not turned on in the next cycle and the low-side power MOSFET stays on until the inductor current ramps down below the current-limit level.

If the output is overloaded and the peak inductor current exceeds the preset current limit for more than eight consecutive clock cycles, the hiccup mode current-limit condition occurs. The output goes to sleep for 6 ms, during which time the output is discharged, the average power dissipation is reduced, and the device wakes up with a soft start period. If the current-limit condition is triggered again, the output goes to sleep and wakes up after 6 ms. Figure 32 shows the current-limit hiccup mode when the output is shorted to PGND.

#### THERMAL SHUTDOWN

If the ADP2441 junction temperature rises above 150°C, the thermal shutdown circuit turns off the switching regulator. Extreme junction temperatures can be the result of high current operation, poor circuit board design, or high ambient temperature. A 25°C hysteresis is included so that when a thermal shutdown occurs, the ADP2441 does not return to normal operation until the junction temperature drops below 125°C. Soft start is active upon each restart cycle.

# APPLICATIONS INFORMATION SELECTING THE OUTPUT VOLTAGE

The output voltage is set using a resistor divider connected between the output voltage and the FB pin (see Figure 54). The resistor divider divides down the output voltage to the 0.6 V FB regulation voltage. The output voltage can be set to as low as 0.6 V and as high as 90% of the power input voltage.

The ratio of the resistive voltage divider sets the output voltage, and the absolute value of the resistors sets the divider string current. For lower divider string currents, the small 50 nA (0.1  $\mu A$  maximum) FB bias current should be taken into account when calculating the resistor values. The FB bias current can be ignored for a higher divider string current; however, using small feedback resistors degrades efficiency at very light loads.

To limit degradation of the output voltage accuracy due to FB bias current to less than 0.005% (0.5% maximum), ensure that the divider string current is greater than 20  $\mu A.$  To calculate the desired resistor values, first determine the value of the bottom resistor,  $R_{\rm BOTTOM}$ , as follows:

$$R_{BOTTOM} = \frac{V_{REF}}{I_{STRING}} \tag{2}$$

where:

$V_{REF}$  is the internal reference and equals 0.6 V.  $I_{STRING}$  is the resistor divider string current.

Then calculate the value of the top resistor,  $R_{\text{TOP}}$ , as follows:

$$R_{TOP} = R_{BOTTOM} \times \left( \frac{V_{OUT} - V_{REF}}{V_{REF}} \right)$$

$$\begin{array}{c} V_{OUT} \\ R_{TOP} \end{array}$$

$$\begin{array}{c} ADP2441 \\ \hline \\ PGOOD & FREQ & SS/TRK \\ \hline \\ EXTERNAL \end{array}$$

$$\begin{array}{c} C_{SS} \\ \\ \end{array}$$

Figure 54. Voltage Divider

**Table 5. Output Voltage Selection**

| Voltage (V) | R <sub>TOP</sub> (kΩ) | $R_{BOTTOM}$ ( $k\Omega$ ) |

|-------------|-----------------------|----------------------------|

| 12          | 190                   | 10                         |

| 5           | 73                    | 10                         |

| 3.3         | 45                    | 10                         |

| 1.2         | 10                    | 10                         |

#### **SETTING THE SWITCHING FREQUENCY**

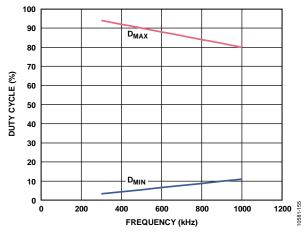

The choice of the switching frequency depends on the required dc-to-dc conversion ratio and is limited by the minimum and maximum controllable duty cycle, as shown in Figure 55. This is due to the requirement of minimum on time and minimum off time for current sensing and robust operation.

However, the choice is also influenced by whether there is a need for small external components. For example, for small, area limited power solutions, higher switching frequencies are required.

Figure 55. Duty Cycle vs. Switching Frequency

Calculate the value of the frequency resistor using the following equation:

$$R_{FREQ} = \frac{92,500}{f_{SW}} \tag{4}$$

where  $R_{FREQ}$  is in k $\Omega$ , and  $f_{SW}$  is in kHz.

Table 6 and Figure 56 provide examples of frequency resistor values, which are based on the switching frequency.

**Table 6. Frequency Resistor Selection**

| R <sub>FREQ</sub> (kΩ) | Frequency |  |

|------------------------|-----------|--|

| 308                    | 300 kHz   |  |

| 132                    | 700 kHz   |  |

| 92.5                   | 1 MHz     |  |

| 1200                   |           |  |

|                        |           |  |

Figure 56. Frequency vs. Resistance

#### **SOFT START**

The soft start function limits the input inrush current and prevents output overshoot at startup. The soft start time is programmed by connecting a small ceramic capacitor between the SS/TRK and AGND pins, with the value of this capacitor defining the soft start time, tss, as follows:

$$\frac{V_{REF}}{t_{SS}} = \frac{I_{SS}}{C_{SS}} \tag{5}$$

where:

$V_{REF}$  is the internal reference voltage and equals 0.6 V.  $I_{SS}$  is the soft start current and equals 1  $\mu$ A.  $C_{SS}$  is the soft start capacitor value.

**Table 7. Soft Start Time Selection**

| Soft Start Capacitor (nF) | Soft Start Time (ms) |

|---------------------------|----------------------|

| 5                         | 3                    |

| 10                        | 6                    |

| 20                        | 12                   |

Alternatively, the user can float the SS/TRK pin and use the internal soft start time of 2 ms.

#### **EXTERNAL COMPONENTS SELECTION**

#### **Input Capacitor Selection**

The input current to a buck regulator is pulsating in nature. The current is zero when the high-side switch is off and is approximately equal to the load current when the switch is on. Because switching occurs at reasonably high frequencies (300 kHz to 1 MHz), the input bypass capacitor usually supplies most of the high frequency current (ripple current), allowing the input power source to supply only the average (dc) current. The input capacitor needs a sufficient ripple current rating to handle the input ripple and needs an ESR that is low enough to mitigate the input voltage ripple. In many cases, different types of capacitors are placed in parallel to minimize the effective ESR and ESL.

The minimum input capacitance required for a particular load is

$$C_{IN\_MIN} = \frac{I_{OUT} \times D \times (1 - D)}{(V_{PP} - I_{OUT} \times D \times R_{ESR}) f_{SW}}$$

(6)

where:

$V_{PP}$  is the desired input ripple voltage.

$R_{ESR}$  is the equivalent series resistance of the capacitor.

*I*<sub>OUT</sub> is the maximum load current.

It is recommended to use a ceramic bypass capacitor because the ESR associated with this type of capacitor is near zero, simplifying the equation to

$$C_{IN\_MIN} = \frac{I_{OUT} \times D \times (1 - D)}{V_{DD} \times f_{SW}}$$

(7)

In addition, it is recommended to use a ceramic capacitor with a voltage rating that is 1.5 times the input voltage with X5R and X7R dielectrics. Using Y5V and Z5U dielectrics is not recommended due to their poor temperature and dc bias characteristics.

Table 10 shows a list of recommended MLCC capacitors from Murata and Taiyo Yuden.

For large step load transients, add more bulk capacitance by, for example, using electrolytic or polymer capacitors. Make sure that the ripple current rating of the bulk capacitor exceeds the minimum input ripple current of a particular design.

#### **Inductor Selection**

The high switching frequency of the ADP2441 allows for minimal output voltage ripple even when small inductors are used. Selecting the size of the inductor involves considering the trade-off between efficiency and transient response. A smaller inductor results in larger inductor current ripple, which provides excellent transient response but degrades efficiency. Due to the high switching frequency of the ADP2441, using shielded ferrite core inductors is recommended because of their low core losses and low EMI.

The inductor ripple current also affects the stability of the loop because the ADP2441 uses the emulated peak current mode architecture. In the traditional approach of slope compensation, the user sets the inductor ripple current and then sets the slope compensation using an external ramp resistor. In most cases, the inductor ripple current is typically set to be 1/3 of the maximum load current for optimal transient response and efficiency. The ADP2441 has internal slope compensation, which assumes that the inductor ripple current is set to 0.3 A (30% of the maximum load of 1 A), eliminating the need for an external ramp resistor.

For the ADP2441, choose an inductor such that the peak-to-peak ripple current of the inductor is between 0.2 A and 0.5 A for stable operation.

Therefore, calculate the inductor value as follows:

$$\Delta I_L = \frac{V_{OUT} \times (V_{IN} - V_{OUT})}{V_{IN} \times f_{SW} \times L}$$

(8)

$0.2 \text{ A} \leq \Delta I_L \leq 0.5 \text{ A}$

$$\frac{2 \times V_{OUT} \times (V_{IN} - V_{OUT})}{V_{IN} \times f_{SW}} \leq L \leq \frac{5 \times V_{OUT} \times (V_{IN} - V_{OUT})}{V_{IN} \times f_{SW}}$$

$$L_{IDEAL} = \frac{3.3 \times V_{OUT} \times (V_{IN} - V_{OUT})}{V_{IN} \times f_{SW}}$$

(9)

where:

$V_{IN}$  is the input voltage.

$V_{OUT}$  is the desired output voltage.

*f*<sub>SW</sub> is the regulator switching frequency.

For applications with a wide input  $(V_{\rm IN})$  range, choose the inductor based on the geometric mean of the input voltage extremes.

$$V_{\mathit{IN}(\mathit{GEOMETRIC})} = \sqrt{V_{\mathit{IN}\_\mathit{MAX}} \times V_{\mathit{IN}\_\mathit{MIN}}}$$

where:

$V_{IN\ MAX}$  is the maximum input voltage.

$V_{IN\_MIN}$  is the minimum input voltage.

The inductor value is based on V<sub>IN(GEOMETRIC)</sub> as follows:

$$L_{IDEAL} = \frac{3.3 \times V_{OUT} \times (V_{IN(GEOMETRIC)} - V_{OUT})}{V_{IN(GEOMETRIC)} \times f_{SW}}$$

Table 8. Inductor Values for Various  $V_{\rm IN},\,V_{\rm OUT},\,$  and  $f_{\rm SW}$  Combinations

|                       |                     |                      | Inductor Value |          |

|-----------------------|---------------------|----------------------|----------------|----------|

| f <sub>sw</sub> (kHz) | V <sub>IN</sub> (V) | V <sub>OUT</sub> (V) | Min (μH)       | Max (μH) |

| 300                   | 12                  | 3.3                  | 22             | 27       |

| 300                   | 12                  | 5                    | 27             | 33       |

| 300                   | 24                  | 3.3                  | 27             | 33       |

| 300                   | 24                  | 5                    | 39             | 47       |

| 300                   | 24                  | 12                   | 56             | 68       |

| 300                   | 36                  | 3.3                  | 27             | 33       |

| 300                   | 36                  | 5                    | 39             | 47       |

| 300                   | 36                  | 12                   | 68             | 82       |

| 600                   | 12                  | 3.3                  | 12             | 15       |

| 600                   | 12                  | 5                    | 15             | 18       |

| 600                   | 24                  | 3.3                  | 15             | 18       |

| 600                   | 24                  | 5                    | 18             | 22       |

| 600                   | 24                  | 12                   | 27             | 33       |

| 600                   | 36                  | 3.3                  | 15             | 18       |

| 600                   | 36                  | 5                    | 22             | 27       |

| 1000                  | 12                  | 5                    | 6.8            | 10       |

| 1000                  | 24                  | 5                    | 10             | 12       |

| 1000                  | 24                  | 12                   | 18             | 22       |

| 1000                  | 36                  | 5                    | 12             | 15       |

To avoid inductor saturation and ensure proper operation, choose the inductor value so that neither the saturation current nor the maximum temperature rated current ratings are exceeded. Inductor manufacturers specify both of these ratings in data sheets or the rating can be calculated as follows:

$$I_{L_{\_}PEAK} = I_{LOAD(MAX)} + \frac{\Delta I_{L}}{2}$$

(10)

where:

$I_{LOAD(MAX)}$  is the maximum dc load current.  $\Delta I_L$  is the peak-to-peak inductor ripple current.

**Table 9. Recommended Inductors**

| Value (μH) | Small Size Inductors (<10 mm × 10 mm) | Large Size Inductors (>10 mm × 10 mm) |

|------------|---------------------------------------|---------------------------------------|

| 10         | XAL4040-103ME                         | MSS1260                               |

| 18         | LPS6235-183ML                         | MSS1260                               |

| 33         | LPS6235-33ML                          | MSS1260                               |

| 15         | XAL4040-153ME                         | MSS1260                               |

#### **Output Capacitor Selection**

The output capacitor selection affects both the output voltage ripple and the loop dynamics of the regulator. The ADP2441 is designed to operate with small ceramic output capacitors that have low ESR and ESL; therefore, the device can easily meet tight output voltage ripple specifications. For best performance, use X5R or X7R dielectric capacitors with a voltage rating that is 1.5 times the output voltage and avoid using Y5V and Z5U dielectric capacitors, which have poor temperature and dc bias characteristics. Table 10 lists some recommended capacitor from Murata and Taiyo Yuden.

For acceptable maximum output voltage ripple, determine the minimum output capacitance, C<sub>OUT(MIN)</sub>, as follows:

$$\Delta V_{RIPPLE} \cong \Delta I_L \times \left( ESR + \frac{1}{8 \times f_{SW} \times C_{OUT(MIN)}} \right)$$

(11)

Therefore,

$$C_{OUT(MIN)} \cong \frac{\Delta I_L}{8 \times f_{SW} \times (\Delta V_{RIPPLE} - \Delta I_L \times ESR)}$$

(12)

where:

$\Delta V_{RIPPLE}$  is the allowable peak-to-peak output voltage ripple.  $\Delta I_L$  is the inductor ripple current.

*ESR* is the equivalent series resistance of the capacitor. *f*<sub>SW</sub> is the switching frequency of the regulator.

If there is a step load requirement, choose the output capacitor value based on the value of the step load. For the maximum acceptable output voltage droop/overshoot caused by the step load,

$$C_{OUT(MIN)} \cong \Delta I_{OUT(STEP)} \times \left(\frac{3}{f_{SW} \times \Delta V_{DROOP}}\right)$$

(13)

where:

$\Delta I_{OUT(STEP)}$  is the load step.

$f_{SW}$  is the switching frequency of the regulator.

$\Delta V_{DROOP}$  is the maximum allowable output voltage droop/overshoot.

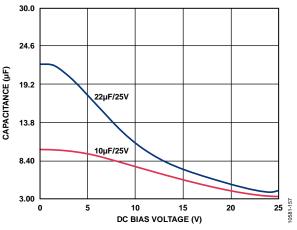

Select the largest output capacitance given by Equation 12 and Equation 13. When choosing the type of ceramic capacitor for the output filter of the regulator, select one with a nominal capacitance that is 20% to 30% larger than the calculated value because the effective capacitance degrades with dc voltage and temperature. Figure 57 shows the capacitance loss due to the output voltage dc bias for three X7R MLCC capacitors from Murata.

Figure 57. Capacitance vs. DC Bias Voltage

For example, to attain 20  $\mu F$  of output capacitance with an output voltage of 5 V while providing some margin for temperature variation, use a 22  $\mu F$  capacitor with a voltage rating of 25 V and a 10  $\mu F$  capacitor with a voltage rating of 25 V in parallel. This configuration ensures that the output capacitance is sufficient under all conditions and, therefore, that the device exhibits stable behavior.

Table 10. Recommended Output Capacitors for ADP2441

|                    | Vendor             |                  |  |  |

|--------------------|--------------------|------------------|--|--|

| Capacitor          | Murata             | Taiyo Yuden      |  |  |

| 10 μF/25 V         | GRM32DR71E106KA12L | TMK325B7106KN-TR |  |  |

| $22  \mu F/25  V$  | GRM32ER71E226KE15L | TMK325B7226MM-TR |  |  |

| $47  \mu F/6.3  V$ | GCM32ER70J476KE19L | JMK325B7476MM-TR |  |  |

| $4.7~\mu F/50~V$   | GRM31CR71H475KA12L | UMK325B7475MMT   |  |  |

#### **BOOST CAPACITOR**

The boost pin (BST) is used to power up the internal driver for the high-side power MOSFET. In the ADP2441, the high-side power MOSFET is an N-channel device to achieve high efficiency in mid and high duty cycle applications. To power up the high-side driver, a capacitor is required between the BST and SW pins. The size of this boost capacitor is critical because it affects the light load functionality and efficiency of the device. Therefore, choose a boost ceramic capacitor with a value between 10 nF to 22 nF with a voltage rating of 50 V and place the capacitor as close as possible to the IC. It is recommended to use a boost capacitor within this range because a capacitor beyond 22 nF can cause the LDO to reach the current-limit threshold.

#### **VCC CAPACITOR**

The ADP2441 has an internal regulator to power up the internal controller and the low-side driver. The VCC pin is the output of the internal regulator. The internal regulator provides the pulse current when the low-side driver turns on. Therefore, it is recommended that a 1  $\mu F$  ceramic capacitor be placed between the VCC and PGND pins as close as possible to the IC and that a 1  $\mu F$  ceramic capacitor be placed between the VCC and AGND pins.

#### LOOP COMPENSATION

The ADP2441 uses peak current mode control architecture for excellent load and line transient response. This control architecture has two loops: an external voltage loop and an inner current loop.

The inner current loop senses the current in the low-side switch and controls the duty cycle to maintain the average inductor current. Slope compensation is added to the inner current loop to ensure stable operation when the duty cycle is above 50%.

The external voltage loop senses the output voltage and adjusts the duty cycle to regulate the output voltage to the desired value. A transconductance amplifier with an external series RC network connected to the COMP pin compensates the external voltage loop.

Figure 58. RC Compensation Network

# LARGE SIGNAL ANALYSIS OF THE LOOP COMPENSATION

The control loop can be broken down into the following three sections:

- V<sub>OUT</sub> to V<sub>COMP</sub>

- V<sub>COMP</sub> to I<sub>L</sub>

- I<sub>L</sub> to V<sub>OUT</sub>

Figure 59. Large Signal Model

Correspondingly, there are three transfer functions:

$$\frac{V_{COMP}(s)}{V_{OUT}(s)} = \frac{V_{REF}}{V_{OUT}} \times g_m \times Z_{COMP}(s)$$

(14)

$$\frac{I_L(s)}{V_{COMP}(s)} = G_{CS} \tag{15}$$

$$\frac{V_{OUT}(s)}{I_I(s)} = Z_{FILT}(s) \tag{16}$$

where:

$g_m$  is the transconductance of the error amplifier and equals 250  $\mu$ A/V.

$G_{CS}$  is the current sense gain and equals 2 A/V.

$V_{OUT}$  is the output voltage of the regulator.

$V_{REF}$  is the internal reference voltage and equals 0.6 V.

$Z_{COMP}(s)$  is the impedance of the RC compensation network that forms a pole at the origin and a zero as expressed in Equation 17.

$$Z_{COMP}(s) = \frac{1 + s \times R_{COMP} \times C_{COMP}}{s \times C_{COMP}}$$

(17)

$Z_{FILT}(s)$  is the impedance of the output filter and is expressed as

$$Z_{FILT}(s) = \frac{R_{LOAD}}{1 + s \times R_{LOAD} \times C_{OUT}}$$

(18)

where *s* is the angular frequency, which can be written as  $s = 2\pi f$ .

The overall loop gain, H(s), is obtained by multiplying the three transfer functions previously mentioned as follows:

$$H(s) = g_m \times G_{CS} \times \frac{V_{REF}}{V_{OUT}} \times Z_{COMP}(s) \times Z_{FILT}(s)$$

(19)

When the switching frequency ( $f_{SW}$ ), output voltage ( $V_{OUT}$ ), output inductor (L), and output capacitor ( $C_{OUT}$ ) values are selected, the unity crossover frequency can be set to 1/12 of the switching frequency.

At the crossover frequency, the gain of the open-loop transfer function is unity.

$$H(f_{CROSSOVER}) = 1 (20)$$

This yields Equation 21 for the RC compensation network impedance at the crossover frequency.

$$Z_{COMP}(f_{CROSSOVER}) = \frac{2 \times \pi \times f_{CROSSOVER} \times C_{OUT}}{g_m \times G_{CS}} \times \frac{V_{OUT}}{V_{REF}}$$

(21)

Placing  $s = f_{CROSSOVER}$  in Equation 17,

$$Z_{COMP}(f_{CROSSOVER}) = \frac{1 + 2 \times \pi \times f_{CROSSOVER} \times R_{COMP} \times C_{COMP}}{2 \times \pi \times f_{CROSSOVER} \times C_{COMP}}$$

(22)

To ensure that there is sufficient phase margin at the crossover frequency, place the compensator zero at 1/8 of the crossover frequency, as shown in the following equation:

$$f_{ZERO} = \frac{1}{2 \times \pi \times R_{COMP} \times C_{COMP}} \approx \frac{f_{CROSSOVER}}{8}$$

(23)

Solving Equation 21, Equation 22, and Equation 23 yields the value for the resistor and capacitor in the RC compensation network, as shown in Equation 24 and Equation 25.

$$R_{COMP} = 0.9 \times \frac{2 \times \pi \times f_{CROSSOVER}}{g_m \times G_{CS}} \times \frac{C_{OUT} \times V_{OUT}}{V_{REF}}$$

(24)

$$C_{COMP} = \frac{1}{2 \times \pi \times f_{ZFRO} \times R_{COMP}}$$

(25)

Using these equations allows calculating the compensations for the voltage loop.

#### **DESIGN EXAMPLE**

Consider an application with the following specifications:

- $V_{\rm IN}$  =24 V ± 10%

- $V_{OUT} = 5 V \pm 1\%$

- Switching frequency = 700 kHz

- Load = 800 mA typical

- Maximum load current = 1 A

- Soft start time = 6 ms

- Overshoot ≤ 2% under all load transient conditions

#### **CONFIGURATION AND COMPONENTS SELECTION**

#### **Resistor Divider**

The first step in selecting the external components is to calculate the resistance of the resistor divider that sets the output voltage.

Using Equation 2 and Equation 3,

$$R_{BOTTOM} = \frac{V_{REF}}{I_{STRING}} = \frac{0.6}{60 \,\mu\text{A}} = 10 \,\text{k}\Omega$$

$$R_{TOP} = R_{BOTTOM} \times \left( \frac{V_{OUT} - V_{REF}}{V_{REF}} \right)$$

$$R_{TOP} = 10 \text{ k}\Omega \times \left(\frac{5 \text{ V} - 0.6 \text{ V}}{0.6 \text{ V}}\right) = 73.3 \text{ k}\Omega$$

#### Switching Frequency

Choosing the switching frequency involves considering the trade-off between efficiency and component size. Low frequency improves the efficiency by reducing the gate losses but requires a large inductor. The choice of high frequency is limited by the minimum and maximum duty cycle.

Table 11. Duty Cycle

| V <sub>IN</sub> |                    | Duty Cycle                   |

|-----------------|--------------------|------------------------------|

| 24 V (Nom       | inal)              | D <sub>NOMINAL</sub> = 20.8% |

| 26 V (10%       | Above Nominal)     | D <sub>MIN</sub> = 19%       |

| 22 V (10%       | Less than Nominal) | D <sub>MAX</sub> = 23%       |

Based on the estimated duty cycle range, choose the switching frequency according to the minimum and maximum duty cycle limitations, as shown in Figure 55. For example, a 700 kHz, frequency is well within the maximum and minimum duty cycle limitations.

Using Equation 4,

$$R_{FREQ} = \frac{92,500}{f_{SW}}$$

$$R_{FREQ} = 132 \text{ k}\Omega$$

#### **Soft Start Capacitor**

For a given soft start time, the soft start capacitor can be calculated using Equation 5,

$$\frac{V_{REF}}{t_{SS}} = \frac{I_{SS}}{C_{SS}}$$

$$C_{SS} = \frac{I_{SS} \times t_{SS}}{V_{REF}}$$

$$C_{SS} = \frac{1 \,\mu\text{A} \times 6 \,\text{ms}}{0.6 \,\text{V}} = 10 \,\text{nF}$$

#### **Inductor Selection**

Select the inductor by using Equation 9.

$$L_{IDEAL} = \frac{3.3 \times V_{OUT} \times (V_{IN} - V_{OUT})}{V_{IN} \times f_{SW}}$$

$$L_{IDEAL} = \frac{3.3 \times 5 \text{ V} \times (24 - 5) \text{ V}}{24 \text{ V} \times 700 \text{ kHz}} = 18.66 \,\mu\text{H} \approx 18.3 \,\mu\text{H}$$

In Equation 9,  $V_{\rm IN}=24$  V,  $V_{\rm OUT}=5$  V,  $I_{\rm LOAD(MAX)}=1$  A, and  $f_{\rm SW}=700$  kHz, which results in L = 18.66  $\mu$ H. When L = 18  $\mu$ H (the closest standard value) in Equation 8,  $\Delta I_{\rm L}=0.314$  A. Although the maximum output current required is 1 A, the maximum peak current is 1.6 A. Therefore, the inductor should be rated for higher than 1.6 A current.

#### **Input Capacitor Selection**

The input filter consists of a small 0.1  $\mu$ F ceramic capacitor placed as close as possible to the IC.

The minimum input capacitance required for a particular load is

$$C_{IN\_MIN} = \frac{I_{OUT} \times D \times (1 - D)}{V_{PP} \times f_{SW}}$$

where:

$V_{PP} = 50 \text{ mV}.$

$I_{OUT} = 1 \text{ A}.$

D = 0.23.

$f_{SW} = 700 \text{ kHz}.$

Therefore,

$$C_{IN\_MIN} = \frac{1 \text{ A} \times 0.22 \times (1 - 0.22)}{0.05 \text{ V} \times 700 \text{ kHz}} \approx 4.9 \,\mu\text{F}$$

Choosing an input capacitor of  $10 \mu F$  with a voltage rating of 50 V ensures sufficient capacitance over voltage and temperature.

#### **Output Capacitor Selection**

Select the output capacitor by using Equation 12 and Equation 13:

$$C_{OUT(MIN)} \cong \frac{\Delta I_L}{8 \times f_{SW} \times (\Delta V_{RIPPLE} - \Delta I_L \times ESR)}$$

Equation 12 is based on the output voltage ripple ( $\Delta V_{RIPPLE}$ ), which is 1% of the output voltage.

$$C_{OUT(MIN)} \cong \Delta I_{OUT(STEP)} \left( \frac{3}{f_{SW} \times \Delta V_{DROOP}} \right)$$

Equation 13 calculates the capacitor selection based on the transient load performance requirement of 2%. Perform these calculations, and then use the equation that yields the larger capacitor size to select a capacitor.

In this example, the values listed in Table 12 are substituted for the variables in Equation 12 and Equation 13.

Table 12. Requirements

| Parameter                              | Test Conditions/Comments       | Value   |  |

|----------------------------------------|--------------------------------|---------|--|

| Ripple Current                         | Fixed at 0.3 A for the ADP2441 | 0.3 A   |  |

| Voltage Ripple                         | 1% of V <sub>оит</sub>         | 50 mV   |  |

| Voltage Droop Due<br>to Load Transient | 2% of V <sub>оит</sub>         | 100 mV  |  |

| ESR                                    |                                | 5 mΩ    |  |

| f <sub>sw</sub>                        |                                | 700 kHz |  |

The calculation based on the output voltage ripple (see Equation 12) dictates that the minimum output capacitance is

$$C_{\it OUT(MIN)} \cong \frac{0.3~{\rm A}}{8 \times 700~{\rm kHz} \times (50~{\rm mV} - 0.3~{\rm A} \times 5~{\rm m}\Omega)} = 1.1~\mu F$$

whereas the calculation based on the transient load (see Equation 13) dictates that the minimum output capacitance is

$$C_{OUT(MIN)} \cong 0.5 \times \frac{3}{700 \text{ kHz} \times 0.1 \text{ V}} \approx 22 \,\mu\text{F}$$

To meet both requirements, use the value determined by the latter equation. As shown in Figure 57, capacitance degrades with dc bias; therefore, choose a capacitor that is 1.5 times the calculated value.

$$C_{OUT} = 1.5 \times 22 \ \mu\text{F} = 32 \ \mu\text{F}$$

#### **Compensation Selection**

Calculate the compensation component values for the feedback loop by using the following equations:

$$R_{COMP} = 0.9 \times \frac{2 \times \pi \times f_{CROSSOVER}}{g_m \times G_{CS}} \times \frac{C_{OUT} \times V_{OUT}}{V_{REF}}$$

$$C_{COMP} = \frac{1}{2 \times \pi \times f_{ZERO} \times R_{COMP}}$$

Selecting the crossover frequency to be 1/12 of the switching frequency and placing the zero frequency at 1/8 of the crossover frequency ensures that there is enough phase margin in the system.

**Table 13. Calculated Parameter Value**

| Parameter              | Test Conditions/Comments            | Value    |

|------------------------|-------------------------------------|----------|

| f <sub>CROSSOVER</sub> | 1/12 of f <sub>sw</sub>             | 58.3 kHz |

| $f_{ZERO}$             | 1/8 of f <sub>CROSSOVER</sub>       | 7.3 kHz  |

| $V_{REF}$              | Fixed reference                     | 0.6 V    |

| <b>g</b> m             | Transconductance of error amplifier | 250 μΑ/V |

| $G_{CS}$               | Current sense gain                  | 2 A/V    |

| Соит                   | Output capacitor                    | 22 μF    |

| Vout                   | Output voltage                      | 5 V      |

Based on the values listed in Table 13, calculate the compensation value:

$$R_{COMP} = 0.9 \times \frac{2 \times \pi \times 58.3}{250 \times 2} \times \frac{22 \times 5}{0.6} \approx 121 \text{ k}\Omega$$

The closest standard resistor value is 118 k $\Omega$ . Therefore,

$$C_{COMP} = \frac{1}{2 \times \pi \times 7.3 \times 118} = 185 \text{ pF} \approx 180 \text{ pF}$$

#### **SYSTEM CONFIGURATION**

Configure the system as follows:

- 1. Connect a capacitor of 1  $\mu$ F between the VCC and PGND pins and another capacitor of 1  $\mu$ F between the VCC and AGND pins. For best performance, use ceramic X5R or X7R capacitors with a 25 V voltage rating.

- 2. Connect a ceramic capacitor of 10 nF with a 50 V voltage rating between the BST and SW pins.

- 3. Connect a resistor between the FREQ and AGND pins as close as possible to the IC.

- 4. If using the power-good feature, connect a pull-up resistor of 50 k $\Omega$  to an external supply of 5 V.

- Connect a capacitor of 10 nF between the SS and AGND pins.

If the tracking feature is needed, connect a resistor divider between the TRK pin and another supply, as shown in Figure 50.

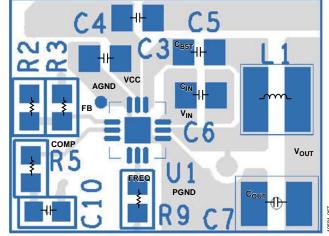

See Figure 60 for a schematic of this design example and Table 14 for the calculated component values.

# TYPICAL APPLICATION CIRCUITS

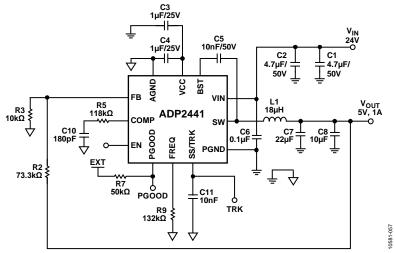

#### **DESIGN EXAMPLE**

$V_{\rm IN}$  = 24 V  $\pm$  10%,  $V_{\rm OUT}$  = 5 V,  $f_{\rm SW}$  = 700 kHz.

Figure 60. ADP2441 Typical Application Circuit,  $V_{IN} = 24 \text{ V} \pm 10\%$ ,  $V_{OUT} = 5 \text{ V}$ ,  $f_{SW} = 700 \text{ kHz}$

**Table 14. Calculated Component Values for Figure 60**

| Qty. | Reference Designator | Value   | Description                                       | Part Number               |

|------|----------------------|---------|---------------------------------------------------|---------------------------|

| 2    | C1, C2               | 4.7 μF  | Capacitor ceramic, X7R, 50 V                      | GRM31CR71H475KA12L        |

| 2    | C3, C4               | 1 μF    | Capacitor ceramic, 1 μF, 25 V, X7R, 10%, 0603     | GRM188R71E105KA12D        |

| 2    | C5, C11              | 10 nF   | Capacitor ceramic, 10,000 pF, 50 V, 10%, X7R, 603 | ECJ-1VB1H103K             |

| 1    | C7                   | 22 μF   | Capacitor ceramic, 22 μF, 25 V, X7R, 1210         | GRM32ER71E226K            |

| 1    | C8                   | 10 μF   | Capacitor ceramic, 10 μF, 25 V, X7R, 1210         | GRM32DR71E106KA12L        |

| 1    | L1                   | 18.3 μH | Inductor, 18.3 μH                                 | CoilCraft MSS1260T-183NLB |

| 1    | C6                   | 0.1 μF  | Capacitor ceramic, 0.1 μF, 50 V, X7R, 0805        | ECJ-2FB1H104K             |

| 1    | C10                  | 185 pF  | Capacitor ceramic, 50 V                           | Vishay, Panasonic         |

| 1    | R9                   | 132 kΩ  | Resistor, 1/10 W, 1%, 0603, SMD                   |                           |

| 1    | R5                   | 118 kΩ  | Resistor, 1/10 W, 1%, 0603, SMD                   |                           |

| 1    | R2                   | 74 kΩ   | Resistor, 1/10 W, 1%, 0603, SMD                   |                           |

| 1    | R3                   | 10 kΩ   | Resistor, 1/10 W, 1%, 0603, SMD                   |                           |

| 1    | R7                   | 50 kΩ   | Resistor, 1/10 W, 1%, 0603, SMD                   |                           |

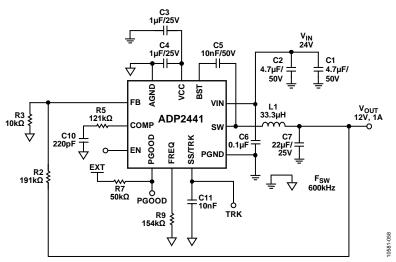

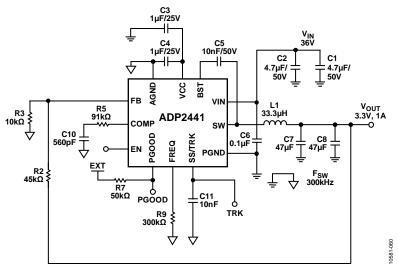

#### OTHER TYPICAL CIRCUIT CONFIGURATIONS

$V_{\rm IN}$  = 24 V  $\pm$  10%,  $V_{\rm OUT}$  = 12 V,  $f_{SW}$  = 600 kHz.

Figure 61. ADP2441 Typical Application Circuit,  $V_{IN}$  = 24 V  $\pm$  10%,  $V_{OUT}$  = 12 V,  $f_{SW}$  = 600 kHz

Table 15. Calculated Component Values for Figure 61

| Qty. | Reference Designator | Value   | Description                                        | Part Number             |

|------|----------------------|---------|----------------------------------------------------|-------------------------|

| 2    | C1, C2               | 4.7 μF  | Capacitor ceramic, X7R, 50 V                       | GRM31CR71H475KA12L      |

| 2    | C3, C4               | 1 μF    | Capacitor ceramic, 1 μF, 25 V, X7R, 10%, 0603      | GRM188R71E105KA12D      |

| 2    | C5, C11              | 10 nF   | Capacitor ceramic, 10,000 pF, 50 V, 10%, X7R, 0603 | ECJ-1VB1H103K           |

| 1    | C7                   | 22 μF   | Capacitor ceramic, 22 μF, 25 V, X7R, 1210          | GRM32ER71E226K          |

| 1    | L1                   | 33.3 μH | Inductor, 33.3 μH                                  | CoilCraft MSS1038-333ML |

| 1    | C6                   | 0.1 μF  | Capacitor ceramic, 0.1 μF, 50 V, X7R, 0805         | ECJ-2FB1H104K           |

| 1    | C10                  | 220 pF  | Capacitor ceramic, 50 V                            | Vishay, Panasonic       |

| 1    | R9                   | 154 kΩ  | Resistor, 1/10 W, 1%, 0603, SMD                    |                         |

| 1    | R5                   | 121 kΩ  | Resistor, 1/10 W, 1%, 0603, SMD                    |                         |

| 1    | R2                   | 191 kΩ  | Resistor, 1/10 W, 1%, 0603, SMD                    |                         |

| 1    | R3                   | 10 kΩ   | Resistor, 1/10 W, 1%, 0603, SMD                    |                         |

| 1    | R7                   | 50 kΩ   | Resistor, 1/10 W, 1%, 0603, SMD                    |                         |

$V_{\rm IN}$  = 12 V  $\pm$  10%,  $V_{\rm OUT}$  = 5 V,  $f_{\rm SW}$  = 500 kHz.

Figure 62. ADP2441 Typical Application Circuit,  $V_{IN} = 12 \text{ V} \pm 10\%$ ,  $V_{OUT} = 5 \text{ V}$ ,  $f_{SW} = 500 \text{ kHz}$

Table 16. Calculated Component Values for Figure 62

| Qty. | Qty. Reference Designator Value |         | Description                                        | Part Number             |  |

|------|---------------------------------|---------|----------------------------------------------------|-------------------------|--|

| 2    | C1, C2                          | 4.7 μF  | Capacitor ceramic, X7R, 50 V                       | GRM31CR71H475KA12L      |  |

| 2    | C3, C4                          | 1 μF    | Capacitor ceramic, 1 µF, 25 V, X7R, 10%, 0603      | GRM188R71E105KA12D      |  |

| 2    | C5, C11                         | 10 nF   | Capacitor ceramic, 10,000 pF, 50 V, 10%, X7R, 0603 | ECJ-1VB1H103K           |  |

| 1    | C7                              | 22 μF   | Capacitor ceramic, 22 μF, 25 V, X7R, 1210          | GRM32ER71E226K          |  |

| 1    | C8                              | 22 μF   | Capacitor ceramic, 22 μF, 25 V, X7R, 1210          |                         |  |

| 1    | L1                              | 18.3 μH | Inductor, 18.3 μH                                  | CoilCraft MSS1038-183ML |  |

| 1    | C6                              | 0.1 μF  | Capacitor ceramic, 0.1 μF, 50 V, X7R, 0805         | ECJ-2FB1H104K           |  |

| 1    | C10                             | 270 pF  | Capacitor ceramic, 50 V                            | Vishay, Panasonic       |  |

| 1    | R9                              | 185 kΩ  | Resistor, 1/10 W, 1%, 0603, SMD                    |                         |  |

| 1    | R5                              | 118 kΩ  | Resistor, 1/10 W, 1%, 0603, SMD                    |                         |  |

| 1    | R2                              | 74 kΩ   | Resistor, 1/10 W, 1%, 0603, SMD                    |                         |  |

| 1    | R3                              | 10 kΩ   | Resistor, 1/10 W, 1%, 0603, SMD                    |                         |  |

| 1    | R7                              | 50 kΩ   | Resistor, 1/10 W, 1%, 0603, SMD                    |                         |  |

$V_{\rm IN}$  = 36 V  $\pm$  10%,  $V_{\rm OUT}$  = 3.3 V,  $f_{\rm SW}$  = 300 kHz.

Figure 63. ADP2441 Typical Application Circuit,  $V_{IN}$  = 36 V  $\pm$  10%,  $V_{OUT}$  = 3.3 V,  $f_{SW}$  = 300 kHz

Table 17. Calculated Component Values for Figure 63

| Qty. | Reference Designator | Value   | Description                                        | Part Number              |

|------|----------------------|---------|----------------------------------------------------|--------------------------|

| 2    | C1, C2               | 4.7 μF  | Capacitor ceramic, X7R, 50 V                       | GRM31CR71H475KA12L       |

| 2    | C3, C4               | 1 μF    | Capacitor ceramic, 1 μF, 25 V, X7R, 10%, 0603      | GRM188R71E105KA12D       |

| 2    | C5, C11              | 10 nF   | Capacitor ceramic, 10,000 pF, 50 V, 10%, X7R, 0603 | ECJ-1VB1H103K            |

| 1    | C7                   | 47 μF   | Capacitor ceramic, 47 μF, 6.3 V, X7R, 1210         | GRM32ER70J476KE20L       |

| 1    | C8                   | 47 μF   | Capacitor ceramic, 47 μF, 6.3 V, X7R, 1210         | GRM32ER70J476KE20L       |

| 1    | L1                   | 33.3 μΗ | Inductor, 33.3 μH                                  | CoilCraft MSS1038T-333ML |

| 1    | C6                   | 0.1 μF  | Capacitor ceramic, 0.1 μF, 50 V, X7R, 0805         | ECJ-2FB1H104K            |

| 1    | C10                  | 560 pF  | Capacitor ceramic, 50 V                            | Vishay, Panasonic        |

| 1    | R9                   | 300 kΩ  | Resistor, 1/10 W, 1%, 0603, SMD                    |                          |

| 1    | R5                   | 91 kΩ   | Resistor, 1/10 W, 1%, 0603, SMD                    |                          |

| 1    | R2                   | 45 kΩ   | Resistor, 1/10 W, 1%, 0603, SMD                    |                          |

| 1    | R3                   | 10 kΩ   | Resistor, 1/10 W, 1%, 0603, SMD                    |                          |