# RENESAS

# DATASHEET

# ISL59833

200MHz Single Supply Video Driver With Charge Pump

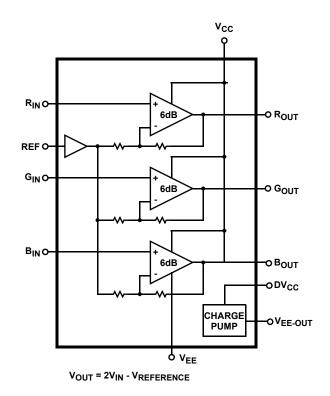

The ISL59833 is a revolutionary device that allows true singlesupply operation of video amplifiers. Designed for systems requiring output swing below ground but lacking a negative power supply, the ISL59833 generates the required negative rail internally from a +3.3V power supply. This allows for DC-accurate coupling of video onto a 75 $\Omega$  double-terminated line. The buffers have an integrated 6dB, eliminating the need for external gain-setting resistors. An external reference voltage can be applied to the REF pin to shift the analog video level down by the desired amount.

# **Ordering Information**

| PART NUMBER<br>(Note) | PART<br>MARKING | TAPE &<br>REEL | PACKAGE<br>(Pb-free) | PKG.<br>DWG. # |

|-----------------------|-----------------|----------------|----------------------|----------------|

| ISL59833IAZ           | 59833 IAZ       | -              | 16 Ld QSOP           | MDP0040        |

| ISL59833IAZ-T7        | 59833 IAZ       | 7"             | 16 Ld QSOP           | MDP0040        |

NOTE: Intersil Pb-free plus anneal products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate termination finish, which are RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

### Features

- Triple single-supply buffer

- · Generates negative rail from from single +3.3V supply

- No output DC blocking capacitor needed

- · 200MHz -3dB bandwidth

- 50MHz 0.1dB bandwidth

- · Fixed gain of 2 output buffer

- · Amplifier enable/disable function control

- · Outputs are high impedance in power-down mode

- · Pb-free plus anneal available (RoHS compliant)

### Applications

١

Driving video

#### Pinout

|         | ISL59833<br>(16 LD QSOP)<br>TOP VIEW |         |

|---------|--------------------------------------|---------|

| RIN 1   |                                      | 16 ROUT |

| GIN 2   |                                      | 15 GOUT |

| BIN 3   |                                      | 14 BOUT |

| REF 4   |                                      | 13 VCC  |

| VEE 5   |                                      | 12 EN   |

| GND 6   |                                      | 11 VCC  |

| EEOUT 7 |                                      | 10 NC   |

| DGND 8  |                                      | 9 DVCC  |

FN6334 Rev 1.00 March 5, 2007

#### **Absolute Maximum Ratings**

| V <sub>CC</sub> , Supply Voltage between V <sub>S</sub> and GND | .5V  |

|-----------------------------------------------------------------|------|

| V <sub>IN</sub> , V <sub>REF</sub> VCC + 0.3V, VEE - (          | ).3V |

| Voltage between V <sub>IN</sub> and V <sub>REF</sub>            |      |

| Maximum Continuous Output Current                               | JmA  |

| ESD Classification                                              |      |

| Human Body Model 20                                             | V00V |

| Machine Model 2                                                 | 200V |

#### **Thermal Information**

| Operating Temperature                            | 40°C to +85°C   |

|--------------------------------------------------|-----------------|

| Maximum Die Temperature                          | +150°C          |

| Storage Temperature                              | -65°C to +150°C |

| Lead Temperature                                 | +260°C          |

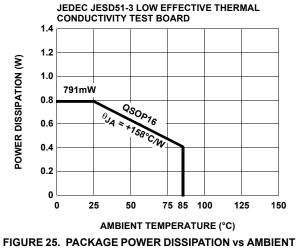

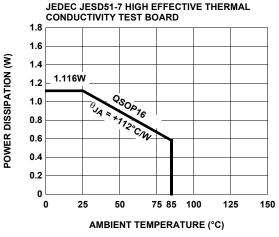

| Power Dissipation                                | See Curves      |

| Pb-free reflow profile                           | see link below  |

| http://www.intersil.com/pbfree/Pb-FreeReflow.asp |                 |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

IMPORTANT NOTE: All parameters having Min/Max specifications are guaranteed. Typical values are for information purposes only. Unless otherwise noted, all tests are at the specified temperature and are pulsed tests, therefore:  $T_J = T_C = T_A$

#### **AC Electrical Specifications** $V_{CC} = DV_{CC} = +3.3V$ , REF = GND, $T_A = +25^{\circ}C$ , $R_L = 150\Omega$ , unless otherwise specified.

| PARAMETER           | DESCRIPTION                     | CONDITIONS                             | MIN | TYP  | MAX | UNIT   |

|---------------------|---------------------------------|----------------------------------------|-----|------|-----|--------|

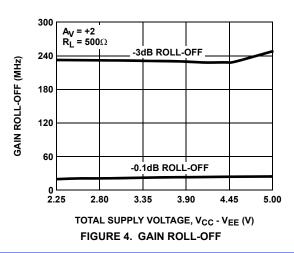

| BW - 3dB            | 3dB Bandwidth                   | V <sub>OUT</sub> = 200mV <sub>PP</sub> |     | 200  |     | MHz    |

|                     |                                 | V <sub>OUT</sub> = 2V <sub>PP</sub>    |     | 100  |     | MHz    |

| BW 0.1dB            | 0.1dB Bandwidth                 | V <sub>OUT</sub> = 2V <sub>PP</sub>    |     | 50   |     | MHz    |

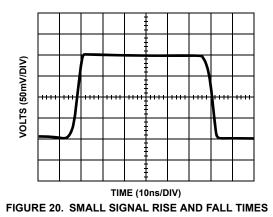

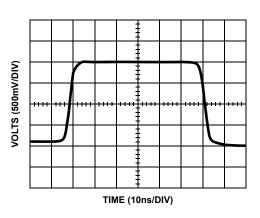

| S <sub>R</sub>      | Slew Rate                       | V <sub>IN</sub> = 2V <sub>PP</sub>     | 500 |      |     | V/µs   |

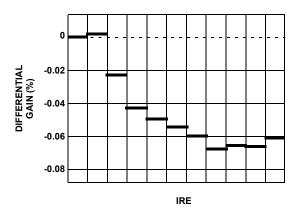

| d <sub>G</sub>      | Differential Gain               |                                        |     | 0.07 |     | %      |

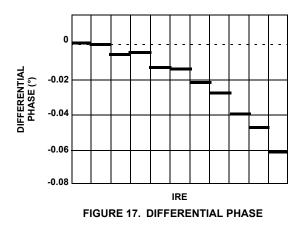

| d <sub>P</sub>      | Differential Phase              |                                        |     | 0.06 |     | 0      |

| X <sub>T</sub>      | Hostile Crosstalk               | 6MHz                                   |     | -90  |     | dB     |

| 1                   | Input to Output Isolation       | 6MHz                                   |     | -70  |     | dB     |

| V <sub>N</sub>      | Input Noise Voltage             |                                        |     | 20   |     | nV/√Hz |

| f <sub>CP</sub>     | Charge Pump Switching Frequency |                                        |     | 168  |     | MHz    |

| Load Reg            | V <sub>EE</sub> Load Regulation | I <sub>EE</sub> = 0mA to 10mA          |     | 9    | 30  | mV     |

| V <sub>RIPPLE</sub> | Output Amp Ripple Voltage       |                                        |     | 30   |     | mV     |

|                     |                                 | With Bead Core to $DV_{CC}$            |     | 10   |     | mV     |

**DC Electrical Specifications**  $V_{CC} = D_{VCC} = +3.3V$ , REF = GND,  $T_A = +25^{\circ}C$ ,  $R_L = 150\Omega$ , unless otherwise specified.

| PARAMETER          | DESCRIPTION                     | CONDITIONS                                      | MIN | ТҮР  | MAX  | UNIT |

|--------------------|---------------------------------|-------------------------------------------------|-----|------|------|------|

| V+                 | Supply Range                    |                                                 | 3.0 |      | 3.6  | V    |

| V <sub>G</sub> %   | Gain Error                      | $R_L$ = 150 $\Omega$ , $V_{OUT}$ = -1V to +2.5V |     |      | 1.5  | %    |

| ΔG                 | Gain Matching                   | R <sub>L</sub> = 150Ω                           |     | 0.5  |      | %    |

| I <sub>IN</sub>    | Analog Input Leakage Current    | V <sub>IN</sub> = 0V to 1.5V                    |     | ±0.1 | ±1   | μA   |

| V <sub>OS</sub>    | Output Offset Voltage           | V <sub>REF</sub> = 0                            | -25 | 7    | +25  | mV   |

| V <sub>OUT +</sub> | Maximum Output Voltage          | R <sub>L</sub> = 75Ω                            | 2.4 | 2.5  |      | V    |

|                    |                                 | R <sub>L</sub> = 150Ω                           | 2.7 | 2.9  |      | V    |

| V <sub>OUT</sub> - | Minimum Output Voltage          | R <sub>L</sub> = 75Ω                            |     | -1.3 | -1   | V    |

|                    |                                 | R <sub>L</sub> = 150Ω                           |     | -1.5 | -1.2 | V    |

| I <sub>OUT +</sub> | Output Current                  | R <sub>L</sub> = 10Ω, V <sub>IN</sub> = 1.2V    | 50  | 80   |      | mA   |

| IOUT -             | Output Current                  | R <sub>L</sub> = 10Ω, V <sub>IN</sub> = -0.3V   |     | -40  | -18  | mA   |

| Z <sub>OUT</sub>   | Disabled Output Impedance       | EN = 3.3V (Amp Disabled)                        |     | 500  |      | kΩ   |

| I <sub>REF</sub>   | Reference Input Leakage Current |                                                 | 1   | 2.3  | 3.5  | μA   |

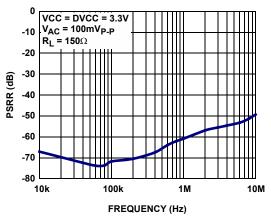

| PSRR               | Power Supply Rejection Ratio    |                                                 | 50  | 62   |      | dB   |

**DC Electrical Specifications**  $V_{CC} = D_{VCC} = +3.3V$ , REF = GND,  $T_A = +25^{\circ}C$ ,  $R_L = 150\Omega$ , unless otherwise specified. (Continued)

| PARAMETER      | DESCRIPTION    | CONDITIONS                                 | MIN | TYP | MAX | UNIT |

|----------------|----------------|--------------------------------------------|-----|-----|-----|------|

| I <sub>S</sub> | Supply Current | $\overline{\text{EN}}$ = GND (Amp Enabled) |     | 97  | 130 | mA   |

|                |                | EN = 3.3V (Amp Disabled)                   |     | 60  | 90  | mA   |

## **Pin Descriptions**

| PIN NUMBER | PIN NAME | PIN FUNCTION                                                                | EQUIVALENT CIRCUIT                                                                                                                                                                    |

|------------|----------|-----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | RIN      | Analog input                                                                | V <sub>cc</sub><br>V <sub>cc</sub><br>V <sub>cc</sub><br>V <sub>cc</sub><br>V <sub>cc</sub><br>CIRCUIT 1                                                                              |

| 2          | GIN      | Analog input                                                                | Reference Circuit 1                                                                                                                                                                   |

| 3          | BIN      | Analog input                                                                | Reference Circuit 1                                                                                                                                                                   |

| 4          | REF      | Reference input<br>High impedance input controlling<br>offset of amplifiers | REF E VCC RIN<br>GIN E REF E CIRCUIT 2                                                                                                                                                |

| 5          | VEE      | Chip substrate (negative power supply<br>for amplifiers)                    | V <sub>CC</sub><br>V <sub>EE</sub> OUT<br>V <sub>EE</sub> OUT<br>V <sub>EE</sub> OUT<br>V <sub>EE</sub> OUT<br>V <sub>EE</sub> OUT<br>CHARGE<br>PUMP<br>D <sub>GND</sub><br>CIRCUIT 3 |

| 6          | GND      | Analog ground                                                               |                                                                                                                                                                                       |

| 7          | VEE OUT  | Charge pump output                                                          | Reference Circuit 3                                                                                                                                                                   |

| 8          | DGND     | Charge pump ground                                                          | Reference Circuit 3                                                                                                                                                                   |

| 9          | DVCC     | Charge pump supply voltage                                                  | Reference Circuit 3                                                                                                                                                                   |

| 10         | NC       | Not connected                                                               |                                                                                                                                                                                       |

| 11, 13     | VCC      | Positive power supply                                                       |                                                                                                                                                                                       |

| PIN NUMBER | PIN NAME | PIN FUNCTION                                                                                | EQUIVALENT CIRCUIT  |

|------------|----------|---------------------------------------------------------------------------------------------|---------------------|

| 12         | ĒN       | Power-down Input<br>Low: Normal Operation<br>High: Power-down Charge Pump and<br>Amplifiers | V <sub>CC</sub>     |

| 14         | BOUT     | Analog output                                                                               |                     |

| 15         | GOUT     | Analog output                                                                               | Reference Circuit 5 |

| 16         | ROUT     | Analog output                                                                               | Reference Circuit 5 |

# Pin Descriptions (Continued)

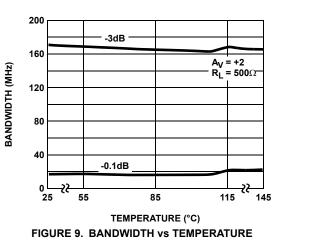

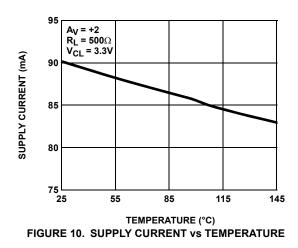

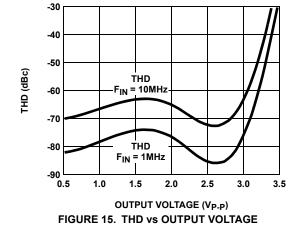

## **Typical Performance Curves**

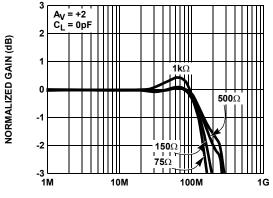

FREQUENCY (Hz) FIGURE 1. GAIN vs FREQUENCY FOR VARIOUS R<sub>LOAD</sub>

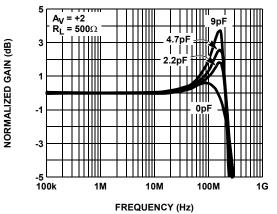

FIGURE 2. GAIN vs FREQUENCY FOR VARIOUS CLOAD

FN6334 Rev 1.00 March 5, 2007

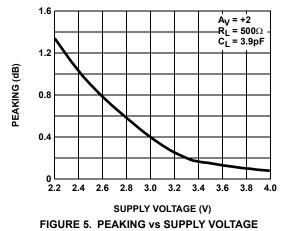

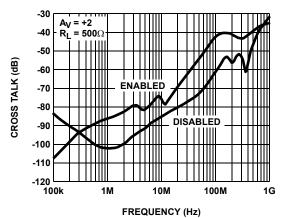

FIGURE 6. CROSS TALK CHANNEL TO CHANNEL (TYPICAL)

120

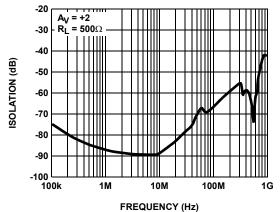

FIGURE 7. INPUT TO OUTPUT ISOLATION vs FREQUENCY

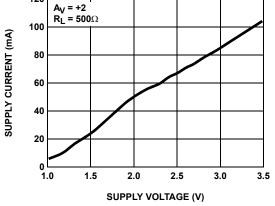

FIGURE 8. SUPPLY CURRENT vs SUPPLY VOLTAGE

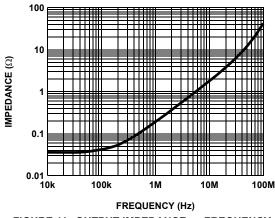

FIGURE 11. OUTPUT IMPEDANCE vs FREQUENCY

FIGURE 12. POWER SUPPLY REJECTION RATIO vs FREQUENCY

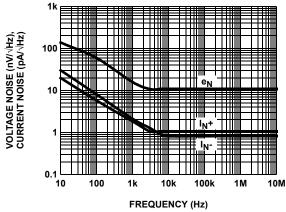

FIGURE 13. VOLTAGE AND CURRENT NOISE vs FREQUENCY

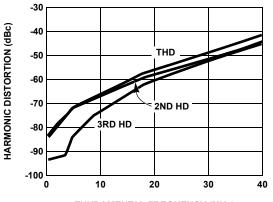

FUNDAMENTAL FREQUENCY (MHz) FIGURE 14. HARMONIC DISTORTION vs FREQUENCY

Typical Performance Curves (Continued)

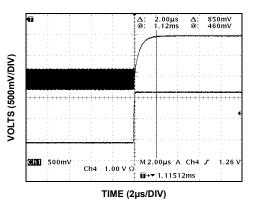

FIGURE 18. DISABLE TIME

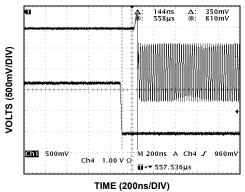

FIGURE 19. ENABLE TIME

FIGURE 21. LARGE SIGNAL RISE AND FALL TIMES

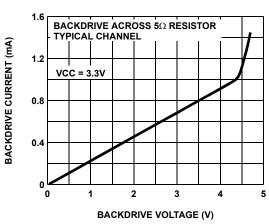

FIGURE 24. BACKDRIVE VOLTAGE vs CURRENT AMP DISABLED OUTPUT LOADING

TEMPERATURE

FIGURE 26. PACKAGE POWER DISSIPATION vs AMBIENT TEMPERATURE

## Block Diagram

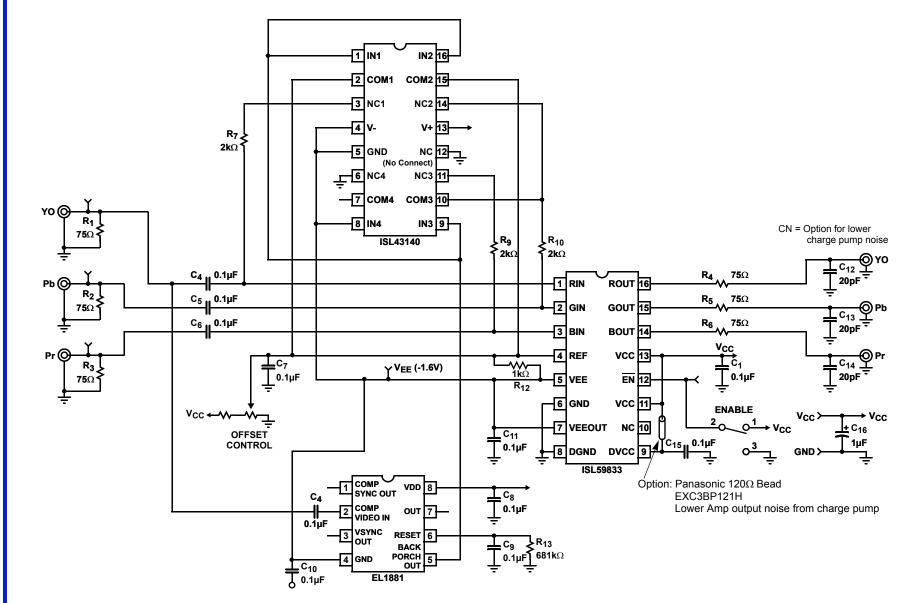

#### ISL59833 + DC-Restore Solution

FN6334 Rev 1.00 March 5, 2007

RENESAS

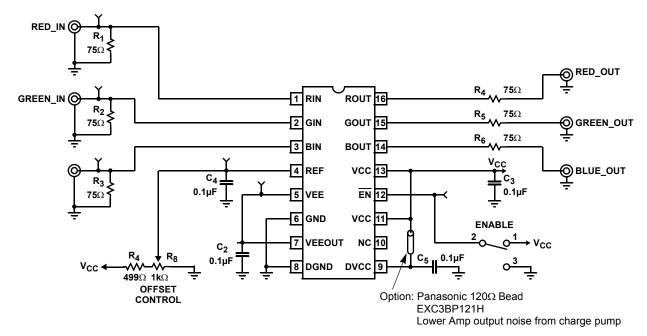

### **Demo Board Schematic**

# Description of Operation and Application Information

### Theory Of Operation

The ISL59833 is a highly practical and robust marriage of three high bandwidth, high speed, low power, rail-to-rail voltage feedback amplifiers with a charge pump to provide a negative rail without an additional power supply. Designed to operate with a single supply voltage range from 0V to 3.3V, the ISL59833 eliminates the need for a split supply with the incorporation of a charge pump capable of generating a bottom rail as much as 1.6V below ground for a 4.9V range on a single 3.3V supply. This performance is ideal for NTSC video with its negative-going sync pulses.

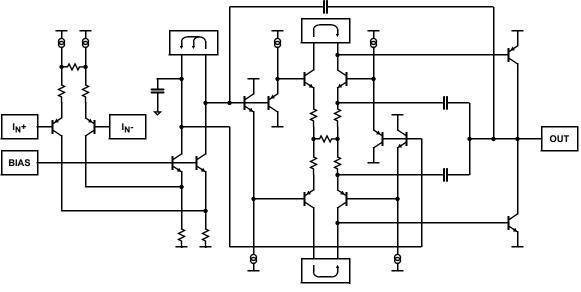

#### THE AMPLIFIER

The ISL59833 fabricated on a di-electrically isolated high speed 5V Bi-CMOS process with 4GHz PNPs and NPN transistor exceeding 20GHz - perfect for low distortion, low power demand and high frequency circuits. While the ISL59833 utilizes somewhat standard voltage mode feedback topologies, there are many non-standard analog features providing its outstanding bandwidth, rail-to-rail operation, and output drive capabilities. The input signal initially passes through a folded cascode, a topology providing enhanced frequency response by essentially fixing the base collector voltage at the junction of the input and gain stage. The collector of each input device looks directly into an emitter that is tied closely to ground through a resistor and biased with a very stable DC source. Since the voltage of this collector is "locked stable" the effective bandwidth limiting of the Miller capacitance is greatly reduced. The signal is then passed through a second fully-realized differential gain stage and

finally through a proprietary common emitter output stage for improved

rail-to-rail output performance. The result is a highly-stable, low distortion, low power, and high frequency amplifier capable of driving moderately capacitive loads with near rail-to-rail performance.

#### INPUT OUTPUT RANGE

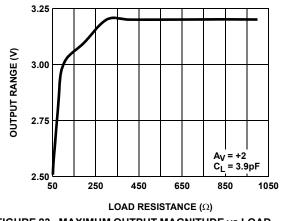

The three amplifier channels have an input common mode voltage range from 0.15V below the bottom rail to within 100mV of the positive supply,  $V_S$ + pin (Note: bottom rail is established by the charge pump at negative one half the positive supply). As the input signal moves outside the specified range, the output signal will exhibit increasingly higher levels of harmonic distortion. And of course, as load resistance becomes lower, the current drive capability of the device will be challenged and its ability to drive close to each rail is reduced. For instance, with a load resistance of  $1k\Omega$  the output swing is within a 100mV of the rails, while a load resistance of  $150\Omega$  limits the output swing to within around 300mV of the rails.

#### AMPLIFIER OUTPUT IMPEDANCE

To achieve near rail-to-rail performance, the output stage of the ISL59833 uses transistors in the common emitter configuration, typically producing higher output impedance than the standard emitter follower output stage. The exceptionally high open loop gain of the ISL59833 and local feedback reduces output impedance to less than a  $2\Omega$  at low frequency. However, since output impedance of the device is exponentially modulated by the magnitude of the open loop gain, output impedance increases with frequency as the open loop gain decreases with frequency. This inductive-like effect of the output impedance is countered in the ISL59833 with

proprietary output stage topology, keeping the output impedance low over a wide frequency range and making it possible to easily and effectively drive relatively heavy capacitive loads (see Figure 11).

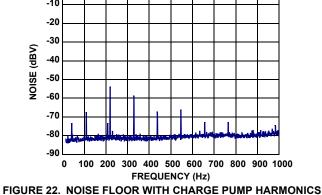

#### THE CHARGE PUMP

The ISL59833 charge pump provides a bottom rail up to 1.65V below ground while operating on a 0V to 3.3V power supply. The charge pump is internally regulated to one-half the potential of the positive supply. This internal multi-phase charge pump is driven by a 110MHz differential ring oscillator driving a series of inverters and charge storage circuitry. Each series inverter charges and places parallel adjoining charge circuitry slightly out of phase with the immediately preceding block. This generates a negative rail of about -1.6V with a low amplitude ripple voltage from the charge pump action. Some of this ripple is coupled into the output signals at a very low

amplitude, as seen in Figure 22. The ripple on the outputs is typically well below the noise floor of the signal.

There are two ways to further reduce the output supply noise:

- Add a 120Ω bead in series between V<sub>CC</sub> and DV<sub>CC</sub>. This reduces the coupling between the charge pump and the analog amplifier supplies.

- Add a 20pF capacitor between the back load 75Ω resistor and ground (see "ISL59833 + DC-Restore Solution" on page 10). This will attenuate frequencies above 100MHz.

The system operates at sufficiently high frequencies that any related charge pump noise is far beyond standard video bandwidth requirements. Still, appropriate bypassing discipline must be observed, and all pins related to either the power supply or the charge pump must be properly bypassed. See "Power Supply Bypassing and Printed Circuit Board Layout" on page 14.

FIGURE 27. SIMPLIFIED SCHEMATIC

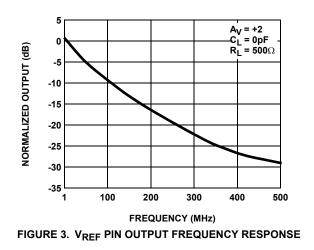

#### THE VREF PIN

Applying a voltage to the VREF pin simply places that voltage on what would usually be the ground side of the gain resistor of the amplifier, resulting in a DC-level shift of the output signal. Applying 100mV to the VREF pin would apply a -100mV DC level shift to the outgoing signal. The charge pump provides sufficient bottom room to accommodate the shifted signal. VREF may be connected to ground for back porch at ground.

The ISL59833 buffers the VREF voltage before applying it to the triple amplifiers, isolating the input from the amplifiers and allowing it to be driven by moderate-impedance voltage sources.

#### THE VEE PIN

The VEE pin is the output pin for the charge pump. A voltmeter applied to this pin will display the output of the charge pump. This pin does not affect the functionality of the part. One may use this pin as an additional voltage source. Keep in mind that the output of this pin is generated by the internal charge pump and a fully regulated supply that must be properly bypassed. We recommend a  $0.1\mu$ F ceramic capacitor placed as close to the pin and connected to the ground plane of the board.

#### INPUT, OUTPUT AND SUPPLY VOLTAGE RANGE

The ISL59833 is designed to operate with a single supply voltage range of from 0V to 3.3V. The need for a split supply has been eliminated with the incorporation of a charge pump capable of generating a bottom rail as much as 1.6V below ground, for a 4.9V range on a single 3.3V supply. This performance is ideal for NTSC video with its negative-going sync pulses.

#### VIDEO PERFORMANCE

For good video performance, an amplifier is required to maintain the same output impedance and the same frequency and phase response as DC levels are changed at the output. This is especially difficult when driving a standard video load of 150 $\Omega$  because of the change in output current with changing DC levels. Special circuitry has been incorporated into the ISL59833 for the reduction of output impedance variation with the current output. This results in outstanding differential gain and differential phase specifications of 0.06% and 0.1°, while driving 150 $\Omega$  at a gain of +2. Driving higher impedance loads would result in similar or better differential gain and differential phase performance.

#### NTSC

The ISL59833 (generating a negative rail internally) is ideally suited for NTSC video with its accompanying negative-going sync signals, which is easily handled by the ISL59833 without the need for an additional supply as the ISL59833 generates a negative rail with an internal charge pump referenced at negative 1/2 the positive supply.

#### YPbPr

YPbPr signals originating from a DVD player requiring three channels of very tightly-controlled amplifier gain accuracy present no difficulty for the ISL59833. Specifically, this standard encodes sync on the Y channel and it is a negative-going signal, which is easily handled by the ISL59833 without the need for an additional supply as the ISL59833 generates a negative rail placed at negative 1/2 the positive supply. Additionally, the Pb and Pr are bipolar analog signals and the video signals are negative-going, and again, easily handled by the ISL59833.

#### DRIVING CAPACITIVE LOADS AND CABLES

The ISL59833 (internally-compensated to drive  $75\Omega$  cables) will drive 10pF loads in parallel with  $1k\Omega$  with less than 5dB of peaking. If less peaking is required, a small series resistor, usually between  $5\Omega$  to  $50\Omega$ , can be placed in series with the output. This will reduce peaking at the expense of a slight closed loop gain reduction. When used as a cable driver, double termination is always recommended for reflection-free performance. For those applications, a back-termination series resistor at the amplifier's output will isolate the amplifier from the cable and allow extensive capacitive drive. However, other applications may have high capacitive loads without a back-termination resistor. Again, a small series resistor at the output can help to reduce peaking. The ISL59833 is a triple amplifier designed to drive three channels; simply deal with each channel separately as described in this section.

#### DC-RESTORE

When the ISL59833 is AC-coupled it becomes necessary to restore the DC reference for the signal. This is accomplished with a DC-restore system applied between the capacitive "AC" coupling and the input of the device. Refer to "ISL59833 + DC-Restore Solution" on page 10.

#### AMPLIFIER DISABLE

The ISL59833 can be disabled and its output placed in a high impedance state. The turn-off time is around 25ns and the turn-on time is around 200ns. When disabled, the amplifier's supply current is reduced to 80mA typically, reducing power consumption. The amplifier's power-down can be controlled by standard TTL or CMOS signal levels at the EN pin. The applied logic signal is relative to the GND pin. Letting the EN pin float or applying a signal that is less than 0.8V above GND will enable the amplifier. The amplifier will be disabled when the signal at EN pin is 2V above GND. The V<sub>EE</sub> charge pump remains active.

#### OUTPUT DRIVE CAPABILITY

The ISL59833 does not have internal short-circuit protection circuitry. A short-circuit current of 80mA sourcing and 150mA sinking for the output is connected half way between the rails with a  $10\Omega$  resistor. If the output is shorted indefinitely, the power dissipation could easily increase such that the part will be destroyed. Maximum reliability is maintained if the output

current never exceeds ±40mA, after which the electromigration limit of the process will be exceeded and the part will be damaged. This limit is set by the design of the internal metal interconnections.

#### POWER DISSIPATION

With the high output drive capability of the ISL59837, it is possible to exceed the +150°C absolute maximum junction temperature under certain load current conditions. Therefore, it is important to calculate the maximum junction temperature for an application to determine if load conditions or package types need to be modified to assure operation of the amplifier in a safe operating area.

The maximum power dissipation allowed in a package is determined according to:

$$PD_{MAX} = \frac{T_{JMAX} - T_{AMAX}}{\Theta_{JA}}$$

(EQ.1)

Where:

T<sub>JMAX</sub> = Maximum junction temperature

T<sub>AMAX</sub> = Maximum ambient temperature

$\Theta_{JA}$  = Thermal resistance of the package

The maximum power dissipation actually produced by an IC is the total quiescent supply current times the total power supply voltage, plus the power in the IC due to the load, or:

for sourcing:

$$PD_{MAX} = V_{S} \times I_{SMAX} + (V_{S} - V_{OUT}i) \times \frac{V_{OUT}i}{R_{L}i}$$

(EQ. 2)

for sinking:

$$PD_{MAX} = V_{S} \times I_{SMAX} + (V_{OUT}i - V_{S}) \times I_{LOAD}i$$

(EQ. 3)

#### Where:

V<sub>S</sub> = Supply voltage

I<sub>SMAX</sub> = Maximum quiescent supply current

V<sub>OUT</sub> = Maximum output voltage of the application

R<sub>LOAD</sub> = Load resistance tied to ground

ILOAD = Load current

i = Number of output channels

By setting the two  $P_{DMAX}$  equations equal to each other, we can solve the output current and  $R_{LOAD}$  to avoid the device overheat.

# Power Supply Bypassing and Printed Circuit Board Layout

Strip line design techniques are recommended for the input and output signal traces. As with any high frequency device, a good printed circuit board layout is necessary for optimum performance. Lead lengths should be as short as possible. The power supply pin must be well bypassed to reduce the risk of oscillation. For normal single supply operation, where the V<sub>S</sub>-pin is connected to the ground plane, a single 4.7µF tantalum capacitor in parallel with a 0.1µF ceramic capacitor from V<sub>S</sub>+ to GND will suffice. This same capacitor combination should be placed at each supply pin to ground if split-internal supplies are to be used. In this case, the V<sub>S</sub>- pin becomes the negative supply rail.

For good AC performance, parasitic capacitance should be kept to a minimum. Use of wire-wound resistors should be avoided because of their additional series inductance. Use of sockets should also be avoided if possible. Sockets add parasitic inductance and capacitance can result in compromised performance. Minimizing parasitic capacitance at the amplifier's inverting input pin is also very important.

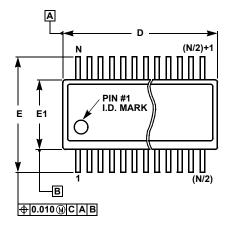

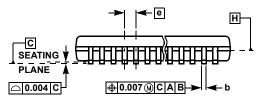

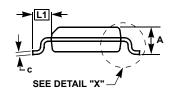

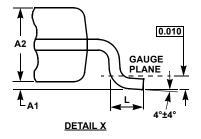

## Quarter Size Outline Plastic Packages Family (QSOP)

#### **MDP0040**

QUARTER SIZE OUTLINE PLASTIC PACKAGES FAMILY

|        | INCHES |        |        |           |            |

|--------|--------|--------|--------|-----------|------------|

| SYMBOL | QSOP16 | QSOP24 | QSOP28 | TOLERANCE | NOTES      |

| A      | 0.068  | 0.068  | 0.068  | Max.      | -          |

| A1     | 0.006  | 0.006  | 0.006  | ±0.002    | -          |

| A2     | 0.056  | 0.056  | 0.056  | ±0.004    | -          |

| b      | 0.010  | 0.010  | 0.010  | ±0.002    | -          |

| с      | 0.008  | 0.008  | 0.008  | ±0.001    | -          |

| D      | 0.193  | 0.341  | 0.390  | ±0.004    | 1, 3       |

| E      | 0.236  | 0.236  | 0.236  | ±0.008    | -          |

| E1     | 0.154  | 0.154  | 0.154  | ±0.004    | 2, 3       |

| е      | 0.025  | 0.025  | 0.025  | Basic     | -          |

| L      | 0.025  | 0.025  | 0.025  | ±0.009    | -          |

| L1     | 0.041  | 0.041  | 0.041  | Basic     | -          |

| N      | 16     | 24     | 28     | Reference | -          |

|        |        |        |        | R         | ev. F 2/07 |

NOTES:

1. Plastic or metal protrusions of 0.006" maximum per side are not included.

2. Plastic interlead protrusions of 0.010" maximum per side are not included.

3. Dimensions "D" and "E1" are measured at Datum Plane "H".

4. Dimensioning and tolerancing per ASME Y14.5M-1994.

© Copyright Intersil Americas LLC 2006-2007. All Rights Reserved. All trademarks and registered trademarks are the property of their respective owners.

For additional products, see www.intersil.com/en/products.html

Intersil products are manufactured, assembled and tested utilizing ISO9001 quality systems as noted in the quality certifications found at <u>www.intersil.com/en/support/qualandreliability.html</u>

Intersil products are sold by description only. Intersil may modify the circuit design and/or specifications of products at any time without notice, provided that such modification does not, in Intersil's sole judgment, affect the form, fit or function of the product. Accordingly, the reader is cautioned to verify that datasheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

FN6334 Rev 1.00 March 5, 2007

#### ООО "ЛайфЭлектроникс"

ИНН 7805602321 КПП 780501001 Р/С 40702810122510004610 ФАКБ "АБСОЛЮТ БАНК" (ЗАО) в г.Санкт-Петербурге К/С 3010181090000000703 БИК 044030703

Компания «Life Electronics» занимается поставками электронных компонентов импортного и отечественного производства от производителей и со складов крупных дистрибьюторов Европы, Америки и Азии.

С конца 2013 года компания активно расширяет линейку поставок компонентов по направлению коаксиальный кабель, кварцевые генераторы и конденсаторы (керамические, пленочные, электролитические), за счёт заключения дистрибьюторских договоров

Мы предлагаем:

- Конкурентоспособные цены и скидки постоянным клиентам.

- Специальные условия для постоянных клиентов.

- Подбор аналогов.

- Поставку компонентов в любых объемах, удовлетворяющих вашим потребностям.

- Приемлемые сроки поставки, возможна ускоренная поставка.

- Доставку товара в любую точку России и стран СНГ.

- Комплексную поставку.

- Работу по проектам и поставку образцов.

- Формирование склада под заказчика.

- Сертификаты соответствия на поставляемую продукцию (по желанию клиента).

- Тестирование поставляемой продукции.

- Поставку компонентов, требующих военную и космическую приемку.

- Входной контроль качества.

- Наличие сертификата ISO.

В составе нашей компании организован Конструкторский отдел, призванный помогать разработчикам, и инженерам.

Конструкторский отдел помогает осуществить:

- Регистрацию проекта у производителя компонентов.

- Техническую поддержку проекта.

- Защиту от снятия компонента с производства.

- Оценку стоимости проекта по компонентам.

- Изготовление тестовой платы монтаж и пусконаладочные работы.

Тел: +7 (812) 336 43 04 (многоканальный) Email: org@lifeelectronics.ru

#### www.lifeelectronics.ru