### **General Description**

The SC2200 belongs to the 4th-generation family of RF PA linearizers (RFPAL) that provides increased integration and functionality over the previous generations. The device is a dual-path linearizer that is a fully-adaptive, RFIN/RFOUT predistortion linearization solution optimized for a wide range of amplifiers, power levels, and communication protocols. It supports 2G to 4G standards (FDD and TDD) from 698MHz to 2700MHz as well as an expanded range of signal bandwidths from 60MHz down to 1.2MHz. The SC2200 accepts singleended RF signals to eliminate baluns and features a mirrored pinout facilitating design of both paths. The device uses the PA output and input signals to adaptively generate an optimized correction function to minimize the PA's distortion. Using RF-domain analog signal processing enables the SC2200 to operate over wide bandwidths and with very low power consumption. The dual linearizer can be used for small-cell MIMO, active antennas, distributed antennas, or in systems requiring two different simplex bands.

## **Applications**

- Cellular Infrastructure

- Single/Multicarrier, Multistandard: CDMA/EVDO, TD-SCDMA, WiMAX, WCDMA/HSDPA, LTE, and TD-LTE

- BTS Amplifiers, RRH, Booster Amplifiers, Repeaters, Small Cells, Microcells, Picocells, DAS, AAS and MIMO Systems

- Wide Range of PAs and Output Power

- · Amplifier: Class A/AB, Doherty

- Average PA Output Power Examples:

Cellular Infrastructure: 27dBm to 40dBm

- · PA Process: LDMOS, GaN, HBT, GaAs and InGaP

#### **Benefits**

- · Ease of Use

- Integrated RFIN/RFOUT Solution

- Smaller Total System Form Factor (24mm x 26mm)

- Reduces System Power Consumption and OPEX

- Reduces BOM Costs and Total Volume

- Smaller Power Supply, Heat Sink, and Enclosure

- · Lower Back-Off Reduces Transistor Costs

#### **Features**

- Frequency Range: 698MHz-2700MHz

- Integrated Preamp and Single-Ended RF I/Os

- Single +1.8V Supply Voltage

- External Reference Clock Support:

- 10, 13, 15.36, 19.2, 20, 26, and 30.72MHz

- Packaged in 11mm x 11mm SAWN QFN Package

- Operating Case Temperature: -40°C to +100°C

- RoHS, Green, REACH, and ISO9001 Compliant

- Dual-Path RFIN/RFOUT Linearizer in CMOS SoC

- Fully Adaptive Correction

- Up to 28dB ACLR and 38dB IMD Improvement (1)

- 1.2MHz < BWSIG ≤ 60MHz</li>

- Power Consumption:

- Duty-Cycled (10%) Feedback: 1500mW (Dual-Path)

- 100% Adaptation: 1.95W (Dual-Path)

<u>Ordering Information</u> and <u>Block Diagram</u> appears at end of data sheet.

# Dual RF Power Amplifier Linearizer (RFPAL)

## **Absolute Maximum Ratings**

| Supply Voltage (AVDD18 to GND)0.2V to +2.2V                            | Input to RF Inputs (RMS)+0dBm            |

|------------------------------------------------------------------------|------------------------------------------|

| Supply Voltage (DVDD18 to GND)0.2V to +2.2V                            | Junction Temperature+150°C               |

| Supply Voltage (V <sub>DDIO</sub> to GND)0.2V to +2.2V                 | Storage Temperature65°C to +150°C        |

| Input Voltage (1.8V pins)0.2V to V <sub>DD18</sub> + 0.2V              | Operating Case Temperature40°C to +100°C |

| Input Voltage (V <sub>DDIO</sub> pins)0.2V to V <sub>DDIO</sub> + 0.2V |                                          |

Warning: Any stress beyond the ranges indicated may damage the device permanently. The specified stress ratings do not imply functional performance in these ranges. Exposure of the device to the absolute maximum ratings for extended periods of time is likely to degrade the reliability of this product

#### **DC Characteristics**

| PARAMETER (Note 1)                                               | MIN | TYP  | MAX  | UNITS |

|------------------------------------------------------------------|-----|------|------|-------|

| Supply Voltage (DVDDIO to GND)                                   | 1.7 | 1.8  | 1.9  | V     |

| Supply Voltage (AVDD18 to GND)                                   | 1.7 | 1.8  | 1.9  | V     |

| Supply Voltage (DVDD18 to GND)                                   | 1.7 | 1.8  | 1.9  | V     |

| Supply Peak Current (DVDDIO to GND) (Notes 2, 3, 5, 6)           |     |      | 50   | mA    |

| Supply Peak Current (AVDD18 to GND) (Notes 1, 2, 3, 5)           |     |      | 1300 | A     |

| Supply Peak Current (DVDD18 to GND) (Notes 1, 2, 3, 5)           |     |      | 400  | mA    |

| Average Power Dissipation: Full-Speed Adaptation (Notes 3, 4, 6) |     | 1950 |      | mW    |

| Average Power Dissipation: Duty-Cycled Feedback (Notes 3, 5, 6)  |     | 1500 |      | mW    |

- **Note 1:** All specifications in this table apply to both paths being enabled.

- Note 2: Peak current includes supply decoupling network. Refer to the Hardware Design Guide for sizing of the voltage regulators.

- Note 3: Characterized at over operating voltages, case temperature with 20MHz input signal BW, and V<sub>DVDDIO</sub> = 1.8V.

- Note 4: Continuous adaptation, tracking (100% duty cycled feedback), and advanced features active or inactive.

- Note 5: Duty-cycled feedback power dissipations averaged over on time of 100ms (9%) and off time of 1.0s (91%).

- Note 6: Power dissipation can be FW dependent. Refer to the FW release notes for any changes to values listed above.

#### **Radio Frequency Signals**

(Operation at T<sub>A</sub> = +25°C, V<sub>AVDD18</sub> = 1.8V, V<sub>DVDDIO</sub> = 1.8V, V<sub>DVDD18</sub> = 1.8V and 20MHz external clock, unless otherwise specified.)

| PARAMETER                             | SYMBOL                 | CONDITIONS                                  | MIN | TYP  | MAX  | UNITS  |

|---------------------------------------|------------------------|---------------------------------------------|-----|------|------|--------|

| Operating Frequency (Note 7)          | f                      |                                             | 698 |      | 2700 | MHz    |

| Input Signal Bandwidth (Note 8)       | BW <sub>SIG</sub>      |                                             | 1.2 |      | 60   | MHz    |

| Noise Power                           |                        | Relative to -3dBm at RFOUT                  |     | -137 |      | dBm/Hz |

| RFINDLY-RFOUT Preamp Gain             | G                      | When set to default FW settings             |     | 10   |      | dB     |

| RFINDLY-RFOUT Preamp Gain             | NDLY-RFOUT Preamp Gain | T <sub>C</sub> = -40°C to +100°C at 2140MHz |     | +1   |      | dB     |

| Deviation from T <sub>C</sub> = +25°C | G <sub>TEMPDEV</sub>   | T <sub>C</sub> = -40°C to +100°C at 2700MHz |     | -2   |      | uB     |

| Path A/B Isolation                    | ISO                    | At 2700MHz                                  |     | 43   |      | dB     |

Note 7: See the Operating Frequency Range table for frequency limits of each defined band.

Note 8: Correction performance across range of input signal BWs also depends on PA output power and carrier configuration.

## RF Range for Maximum Correction—698MHz to 2700MHz

(Operation at T<sub>A</sub> = +25°C, V<sub>AVDD18</sub> = 1.8V, V<sub>DVDDIO</sub> = 1.8V, V<sub>DVDD18</sub> = 1.8V and 20MHz external clock, unless otherwise specified.)

| PARAMETER                    | SYMBOL                    | CONDITIONS                                                       | MIN | TYP | MAX | UNITS |  |

|------------------------------|---------------------------|------------------------------------------------------------------|-----|-----|-----|-------|--|

|                              | P <sub>RFIN_PKL</sub>     | 698MHz-2200MHz (Note 10)                                         | -3  | 0   | 3   |       |  |

| RFIN Peak Power              | P <sub>RFIN_PKH</sub>     | 2200MHz-2700MHz (Note 10)                                        | -3  | 0   | 3   |       |  |

| (Note 9)                     | P <sub>RFINRG_PKL</sub>   | Operating range, 698MHz–2200MHz                                  | -32 |     | 3   | dBm   |  |

|                              | PRFINRG_PKH               | Operating range,<br>2200MHz–2700MHz                              | -32 |     | 3   |       |  |

| RFINDLY Peak Power           | P <sub>RFINDLY_PK</sub>   | PA operated at maximum power                                     | -11 | -8  | -5  | dBm   |  |

| (Notes 9, 11)                | P <sub>RFINDLYRG_PK</sub> | Operating range                                                  | -40 |     | -5  |       |  |

| RFFB Peak Power              | P <sub>RFFB_PK</sub>      | PA operated at maximum power                                     | -8  | -4  | -2  | 15    |  |

| (Note 9)                     | P <sub>RFFBRG_PK</sub>    | Operating range                                                  | -37 |     | -2  | dBm   |  |

| RFOUT Peak Power<br>(Note 9) | PRFOUT_PKL                | PA operated at maximum power (Note 12) 698MHz–2200MHz (Note 10)  | -1  | 2   | 5   | dDm   |  |

|                              | PRFOUT_PKH                | PA operated at maximum power (Note 12) 2200MHz–2700MHz (Note 10) | -1  | 2   | 5   | dBm   |  |

**Note 9:** Peak power is defined as the 10<sup>-4</sup> point on the CCDF (complementary cumulative distribution function) of the signal.

Note 10: PA operated at maximum power.

Note 11: PRFOUT\_PK must be below +7dBm pk under all conditions.

Note 12: Only when the internal through path is enabled.

Note 13: IO type (input/output, pull up/down, push pull, open drain...) is programmable for DIO\* pins. Refer to the *Programming Guide and HW Design Guide* for more information.

Note 14: User can configure the SC2200 to accept the following external clock frequencies: 10, 13, 15.36, 19.2, 20, 26 and 30.72MHz. External clock frequency other than 20MHz requires programming through the SPI bus. Refer to the *Programming Guide and Hardware Design Guide* for more information.

#### **Digital I/O—DC Characteristics**

(Guaranteed performance across worst-case supply voltage and temperature range, unless otherwise specified.)

| PARAMETER                     | SYMBOL                               | CONDITIONS                 | MIN                   | TYP MAX               | UNITS |

|-------------------------------|--------------------------------------|----------------------------|-----------------------|-----------------------|-------|

| CMOS Input Logic-Low          | V <sub>IL</sub>                      |                            | -0.2                  | 0.2 x V <sub>DD</sub> | V     |

| CMOS Input Logic-High         | V <sub>IH</sub>                      | V <sub>DD</sub> = DVDDIO   | V <sub>DD</sub> x 0.8 | V <sub>DD</sub> x 1.1 | V     |

| CMOS Output Logic-High        | V <sub>OH</sub>                      | V <sub>DD</sub> = DVDDIO   | V <sub>DD</sub> x 0.9 | $V_{DD}$              | V     |

| CMOS Output Logic-Low         | V <sub>OL</sub>                      |                            | 0.0                   | 0.1 x V <sub>DD</sub> | V     |

| CMOS Output Current (Note 13) | I <sub>OL18</sub> /I <sub>OH18</sub> | V <sub>DVDDIO</sub> = 1.8V | -4.0                  | +4.0                  | mA    |

Note 13: IO type (input/output, pull up/down, push pull, open drain...) is programmable for DIO\* pins. Refer to the *Programming Guide and HW Design Guide* for more information.

## **Digital I/O—External Clock (XTALI)**

(Guaranteed performance across worst-case supply voltage and temperature range, unless otherwise specified.)

| PARAMETER                                  | SYMBOL            | CONDITIONS                      | MIN | TYP | MAX   | UNITS             |

|--------------------------------------------|-------------------|---------------------------------|-----|-----|-------|-------------------|

| User Programmable External Clock (Note 14) | fclk              |                                 | 10  | 20  | 30.72 | MHz               |

| External Clock Frequency<br>Accuracy       |                   |                                 |     |     | 1     | %                 |

| External Clock Frequency Drift             |                   | Including aging and temperature |     |     | 100   | ppm               |

| Duty Cycle                                 |                   | Square wave                     | 45  |     | 55    | %                 |

| External Clock Amplitude                   | V <sub>CLK</sub>  | Sine or square wave             | 500 |     | 1500  | mV <sub>P-P</sub> |

| External Clock Phase Noise                 | P <sub>NCLK</sub> | At 100kHz offset                |     |     | -130  | dBc/Hz            |

Note 14: User can configure the SC2200 to accept the following external clock frequencies: 10, 13, 15.36, 19.2, 20, 26 and 30.72MHz. External clock frequency other than 20MHz requires programming through the SPI bus. Refer to the *Programming Guide and Hardware Design Guide* for more information.

### **Crystal Requirements (XTALI/XTALO)**

(Guaranteed performance across worst-case supply voltage and temperature range, unless otherwise specified.)

| PARAMETER                 | CONDITIONS                      | MIN | TYP | MAX | UNITS |

|---------------------------|---------------------------------|-----|-----|-----|-------|

| ESR                       |                                 |     |     | 50  | Ω     |

| Capacitive Load to Ground |                                 |     | 10  | 12  | pF    |

| Frequency Accuracy        |                                 |     |     | 250 | ppm   |

| Frequency Drift           | Including aging and temperature |     |     | 100 | ppm   |

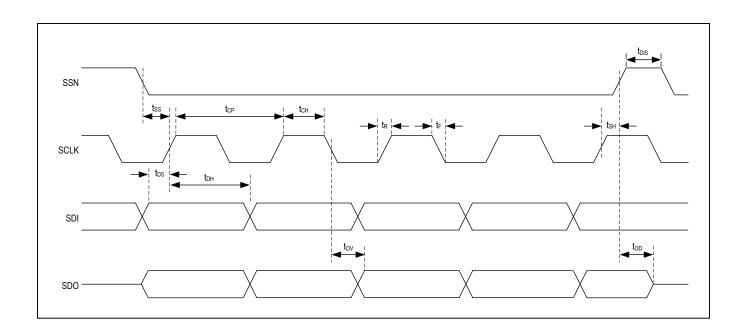

## Serial Peripheral Interface (SPI) Bus Specifications

(Guaranteed performance across worst-case supply voltage and temperature range, unless otherwise specified.)

| PARAMETER            | SYMBOL           | CONDITIONS | MIN | TYP | MAX | UNITS |

|----------------------|------------------|------------|-----|-----|-----|-------|

| Select Setup Time    | tss              |            | 100 |     |     | ns    |

| Select Hold Time     | tsн              |            | 100 |     |     | ns    |

| Select Disable Time  | t <sub>DIS</sub> |            | 100 |     |     | ns    |

| Data Setup Time      | t <sub>DS</sub>  |            | 25  |     |     | ns    |

| Data Hold Time       | t <sub>DH</sub>  |            | 45  |     |     | ns    |

| Rise Time            | t <sub>R</sub>   |            |     |     | 25  | ns    |

| Fall Time            | t <sub>F</sub>   |            |     |     | 25  | ns    |

| Clock Period         | t <sub>CP</sub>  |            | 250 |     |     | ns    |

| Clock High Time      | t <sub>CH</sub>  |            | 100 |     |     | ns    |

| Time to Output Valid | t <sub>OV</sub>  |            |     |     | 100 | ns    |

| Output Data Disable  | t <sub>OD</sub>  |            |     |     | 0   | ns    |

# **CAS25512DWFL EEPROM Endurance**

| PARAMETER                 | SYMBOL              | CONDITIONS                        | MIN | TYP | MAX | UNITS         |

|---------------------------|---------------------|-----------------------------------|-----|-----|-----|---------------|

| EEPROM Write/Erase Cycles | C <sub>EEPROM</sub> | Page mode, T <sub>A</sub> = +25°C | 1M  |     |     | E/W<br>cycles |

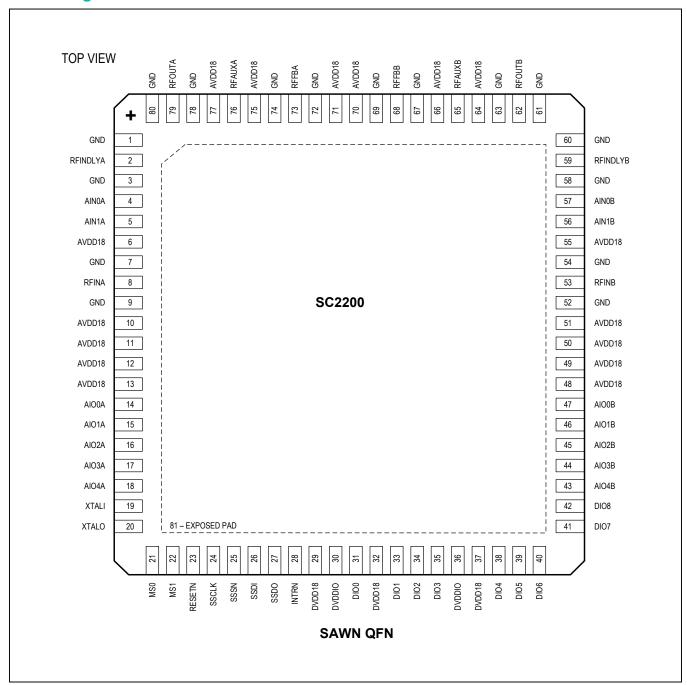

# **Pin Configuration**

# **Pin Description**

| PIN                                                                 | NAME         | TYPE           | FUNCTION                                                                                                                                                                                                                                                       |

|---------------------------------------------------------------------|--------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 3, 7, 9, 52, 54,<br>58, 60, 61, 63,<br>67, 69, 72,<br>74, 78, 80 | GND          | RF Shield      | Ground for Shield of RF Signal                                                                                                                                                                                                                                 |

| 2                                                                   | RFINDLYA     | Analog In      | Delayed RF Single-Ended Input Signal for Tx Path A                                                                                                                                                                                                             |

| 4, 5                                                                | AIN0A, AIN1A | Analog In      | Do not connect. Reserved for internal use.                                                                                                                                                                                                                     |

| 6, 10–13, 48–51,<br>55, 64, 66,<br>70, 71, 75, 77                   | AVDD18       | Supply         | +1.8V DC Supply Voltage for Analog Circuits                                                                                                                                                                                                                    |

| 8                                                                   | RFINA        | Analog In      | RF 50Ω Input Signal for Tx Path A                                                                                                                                                                                                                              |

| 14–18                                                               | AIO0A-AIO4A  | Analog In/Out  | Do not connect. Reserved for internal use.                                                                                                                                                                                                                     |

| 19                                                                  | XTALI        | Analog In      | Oscillator or External Clock Input. For the oscillator, connect a 20MHz crystal across XTALI to XTALO. For the external clock, connect clock source operating at 10, 13, 15.36, 19.2, 20, 26, 30.72MHz. Refer to the <i>Hardware Design Guide</i> for details. |

| 20                                                                  | XTALO        | Analog Out     | Crystal Output. Excitation driver for crystal or ceramic resonator.                                                                                                                                                                                            |

| 21                                                                  | MS0          | Digital In     | Load Enable. Required to program FW upgrades to internal EEPROM. Has internal pulldown to GND.                                                                                                                                                                 |

| 22                                                                  | MS1          | Digital In     | Do not connect. Reserved for internal use. Has internal pulldown to GND.                                                                                                                                                                                       |

| 23                                                                  | RESETN       | Digital In     | Reset when Low. Has internal pullup to DVDDIO.                                                                                                                                                                                                                 |

| 24                                                                  | SSCLK        | Digital In     | Slave SPI Clock. Has internal pulldown to GND.                                                                                                                                                                                                                 |

| 25                                                                  | SSSN         | Digital In     | Slave SPI Select Enabled Low. Has internal pullup to DVDDIO.                                                                                                                                                                                                   |

| 26                                                                  | SSDI         | Digital In     | Slave SPI Data Input to RFPAL. Has internal pulldown to GND.                                                                                                                                                                                                   |

| 27                                                                  | SSDO         | Digital Out    | Slave SPI Data Output from RFPAL. Three-state. DVDDIO logic levels.                                                                                                                                                                                            |

| 28                                                                  | INTRN        | Digital Out    | General-Purpose Digital Output Controlled by FW. Notifies or interrupts the SPI host when low that (e.g., alarm) information is available to be collected. Open-drain output with internal pullup to DVDDIO.                                                   |

| 29, 32, 37                                                          | DVDD18       | Supply         | +1.8V DC Supply Voltage for Digital Circuits                                                                                                                                                                                                                   |

| 30, 36                                                              | DVDDIO       | Supply         | +1.8V DC Supply Voltage for Digital I/O Interface Circuits                                                                                                                                                                                                     |

| 31, 33–35, 38–42                                                    | DIO0-DI08    | Digital In/Out | Do not connect. Reserved for internal use.                                                                                                                                                                                                                     |

| 43–47                                                               | AIO4B-AIO0B  | Analog In/Out  | Do not connect. Reserved for internal use.                                                                                                                                                                                                                     |

| 53                                                                  | RFINB        | Analog In      | RF Single-Ended Input Signal for Tx Path B                                                                                                                                                                                                                     |

| 56, 57                                                              | AIN1B, AIN0B | Analog In      | Do not connect. Reserved for internal use.                                                                                                                                                                                                                     |

| 59                                                                  | RFINDLYB     | Analog In      | Delayed RF Single-Ended Input Signal for Tx Path B                                                                                                                                                                                                             |

| 62                                                                  | RFOUTB       | Analog Out     | RF Single-Ended Output Signal for Tx Path B                                                                                                                                                                                                                    |

| 65                                                                  | RFAUXB       | Analog Out     | Do not connect. Reserved for internal use.                                                                                                                                                                                                                     |

| 68                                                                  | RFFBB        | Analog In      | RF Single-Ended Feedback Signal for Tx Path B                                                                                                                                                                                                                  |

| 73                                                                  | RFFBA        | Analog In      | RF Single-Ended Feedback Signal for Tx Path A                                                                                                                                                                                                                  |

| 76                                                                  | RFAUXA       | Analog Out     | Do not connect. Reserved for internal use.                                                                                                                                                                                                                     |

| 79                                                                  | RFOUTA       | Analog Out     | RF Single-Ended Output Signal for Tx Path A                                                                                                                                                                                                                    |

| 81                                                                  | GND          | Supply         | Exposed Pad. Serves as supply ground and thermal interface.                                                                                                                                                                                                    |

## **Detailed Description**

# Introduction to Predistortion Using the SC2200

Wideband signals in today's telecommunications systems have high peak-to-average ratios and stringent spectral regrowth specifications. These specifications place high linearity demands on power amplifiers. Linearity can be achieved by backing off output power at the price of reducing efficiency. However, this increases the component and operating costs of the power amplifier. Better linearity can be achieved through the use of digital predistortion and other linearization techniques, but many of these methods are time consuming and costly to implement.

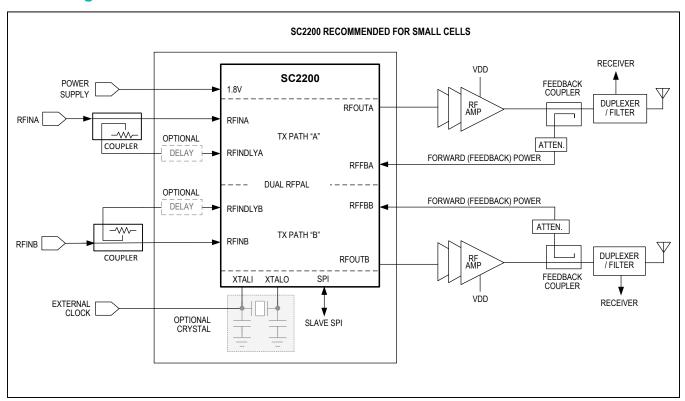

The SC2200 is a true RFIN and RFOUT solution where the complex signal processing is done in the RF domain, supporting modular power amplifier designs that are independent of the baseband and transceiver subsystems. This simple system-on-chip offers wide signal bandwidth, broad frequency of operation, and very low power consumption. It reduces development costs and speeds time to market. Applicable across a broad range of signals—including 2G, 3G, 4G wireless, and other modulation types—the powerful analog signal processing engine is capable of linearizing the most efficient power amplifier topologies. The SC2200 delivers the required efficiency and performance demanded by today's wireless systems.

Wireless service providers are deploying networks with wider coverage, greater subscriber density, and higher data rates. These networks require more efficient power amplifiers. Additionally, the emergence of MIMO, distributed architectures, and active antenna systems is driving the increased need to support smaller, more-efficient power amplifier implementations. Furthermore, a strong push continues toward reducing the total capital and operating costs of base stations.

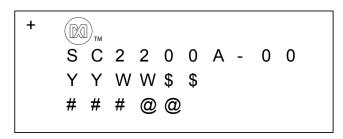

## **Top Mark**

**OPTIONAL NOTES:**

MAXIM INTEGRATED MARKING STANDARDS SPECIFICATION REFERENCE: 20-0400.

| LINE | TOP MARK | DESCRIPTION                                                                                       |

|------|----------|---------------------------------------------------------------------------------------------------|

| 1    | +        | Indicates the part is lead (Pb)-free and designates location of pin one/ball A1Pb-free laser mark |

| 2    | SC2200   | Product part number                                                                               |

| 2    | Α        | Product revision                                                                                  |

| 2    | -00      | Product configuration: -00 = Dual-RFPAL Base Configuration                                        |

| 3    | YY       | Date code—year                                                                                    |

| 3    | WW       | Date code—work week                                                                               |

| 3    | \$\$     | Indicates the package revision code from the reliability database                                 |

| 4    | ###      | Indicates the last 3 numeric characters from the lot number                                       |

| 4    | @@       | Indicates the first 2 alpha characters after the numeric characters from the lot number           |

### **ESD**

ESD (Electro-Static Discharge) sensitive device. Although this product incorporates ESD protection circuitry, permanent damage may occur on devices subjected to electrostatic discharges. Proper ESD precautions are recommended to avoid performance degradation or device failure.

| TEST METHODOLOGY                      | CLASS | VOLTAGE | UNIT |

|---------------------------------------|-------|---------|------|

| Human Body Model (per JS-001-2012)    | 1C    | 1000    | V    |

| Charge Device Model (per JESD22-C101) | II    | 250     | V    |

# **Block Diagram**

# **Ordering Information**

| PART          | DESCRIPTION                                  |

|---------------|----------------------------------------------|

| SC2200A-00A00 | IC, dual-RFPAL, 698-2700 MHz,<br>FW5.0.09.04 |

PON = Part ordering number.

#### Shipping designator:

E = 7in tape and reel. Append shipping designator (E) at end of part number. If left blank, designates bulk shipping option.

# **Evaluation Kit Ordering Information**

| PART NUMBER    | DESCRIPTION                                    |

|----------------|------------------------------------------------|

| SC2200-EVK900  | Evaluation kit, dual-RFPAL,<br>698MHz–960MHz   |

| SC2200-EVK1900 | Evaluation kit, dual-RFPAL,<br>1800MHz–2200MHz |

| SC2200-EVK2400 | Evaluation kit, dual-RFPAL,<br>2300MHz–2700MHz |

| SC-USB-SPI2*   | Adapter, SPI-USB Interface/Controller          |

EV kits ship with most recent release of FW.

# **Package Information**

For the latest package outline information and land patterns (footprints), go to <a href="https://www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE<br>TYPE | PACKAGE<br>CODE | OUTLINE<br>NO. | LAND<br>PATTERN<br>NO. |

|-----------------|-----------------|----------------|------------------------|

| SAWN QFN        | K8011MK+1B      | <u>21-0766</u> | <u>90-0606</u>         |

<sup>\*</sup>Not required for operating evaluation kits. Only recommended for prototypes debug and/or programming linearizer during manufacturing (if no other means are available, such as onboard controller, etc.).

# **Revision History**

| REVISION | REVISION | DESCRIPTION     | PAGES   |

|----------|----------|-----------------|---------|

| NUMBER   | DATE     |                 | CHANGED |

| 0        | 12/15    | Initial release | _       |

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim Integrated's website at www.maximintegrated.com.

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.

OOO «ЛайфЭлектроникс" "LifeElectronics" LLC

ИНН 7805602321 КПП 780501001 P/C 40702810122510004610 ФАКБ "АБСОЛЮТ БАНК" (ЗАО) в г.Санкт-Петербурге К/С 3010181090000000703 БИК 044030703

Компания «Life Electronics» занимается поставками электронных компонентов импортного и отечественного производства от производителей и со складов крупных дистрибьюторов Европы, Америки и Азии.

С конца 2013 года компания активно расширяет линейку поставок компонентов по направлению коаксиальный кабель, кварцевые генераторы и конденсаторы (керамические, пленочные, электролитические), за счёт заключения дистрибьюторских договоров

#### Мы предлагаем:

- Конкурентоспособные цены и скидки постоянным клиентам.

- Специальные условия для постоянных клиентов.

- Подбор аналогов.

- Поставку компонентов в любых объемах, удовлетворяющих вашим потребностям.

- Приемлемые сроки поставки, возможна ускоренная поставка.

- Доставку товара в любую точку России и стран СНГ.

- Комплексную поставку.

- Работу по проектам и поставку образцов.

- Формирование склада под заказчика.

- Сертификаты соответствия на поставляемую продукцию (по желанию клиента).

- Тестирование поставляемой продукции.

- Поставку компонентов, требующих военную и космическую приемку.

- Входной контроль качества.

- Наличие сертификата ISO.

В составе нашей компании организован Конструкторский отдел, призванный помогать разработчикам, и инженерам.

Конструкторский отдел помогает осуществить:

- Регистрацию проекта у производителя компонентов.

- Техническую поддержку проекта.

- Защиту от снятия компонента с производства.

- Оценку стоимости проекта по компонентам.

- Изготовление тестовой платы монтаж и пусконаладочные работы.

Тел: +7 (812) 336 43 04 (многоканальный) Email: org@lifeelectronics.ru