**Automotive Serial EEPROMs**

# 125°C SPI BUS ICs BR35□□□□ Family

BR35H□□□-WC Series

No.11001ECT09

#### Description

BR35H D-WC Series is a SPI BUS interface method serial EEPROM.

#### Features

- 1) High speed clock operation up to 5MHz(Max.)

- 2) 2.5V to 5.5V single power source operation most suitable for battery use.

- 3) Page write mode useful for initial value at factory shipment.

- 4) Highly reliable connection by Au pad and Au wire.

- 5) For SPI bus interface (CPOL, CPHA)=(0,0),(1,1)

- 6) Auto erase and auto end function at data rewrite.

- 7) Low operating current

At write operation (5V): 0.6mA(Typ.)

At read operation (5V): 1.3mA(Typ.) At standby operation (5V): 0.1µA(Typ.)

- 8) Address auto increment function at read operation.

- 9) Write mistake prevention function

Write prohibition at power on.

Write prohibition by command code (WRDI)

Write mistake prevention function at low voltage.

- 10) MSOP8 / TSSOP-B8 / SOP8 / SOP-J8 Package.

- 11) Data at shipment Memory array:FFh.

- 12) Data Retention : 20 years(Ta≦125°C)

- 13) Endurance : 300,000 cycles(Ta≦125°C)

#### ●Page Write

| Number of pages | 32Byte                                    | 64Byte      |

|-----------------|-------------------------------------------|-------------|

| Product number  | BR35H160-WC<br>BR35H320-WC<br>BR35H640-WC | BR35H128-WC |

## ●BR35H□□□ Series

| Capacity | Bit Format | Product Name | Supply<br>Voltage | MSOP8 | TSSOP-B8 | SOP8 | SOP-J8 |

|----------|------------|--------------|-------------------|-------|----------|------|--------|

| 16Kbit   | 2K×8       | BR35H160-WC  | 2.5~5.5V          | •     | •        | •    | •      |

| 32Kbit   | 4K×8       | BR35H320-WC  | 2.5~5.5V          | •     | •        | •    | •      |

| 64Kbit   | 8K×8       | BR35H640-WC  | 2.5~5.5V          | -     | •        | •    | •      |

| 128Kbit  | 16Kx8      | BR35H128-WC  | 2.5~5.5V          | -     | -        | •    | •      |

#### ● Absolute Maximum Ratings (Ta=25°C)

| Parameter                    | Symbol | Limits           | Unit  |

|------------------------------|--------|------------------|-------|

| Impressed Voltage            | Vcc    | -0.3 to +6.5     | V     |

|                              |        | 560(SOP8) *1     |       |

| Permissible                  | Pd     | 560(SOP-J8) *2   | mW    |

| Dissipation                  | Pu     | 410(TSSOP-B8) *3 | IIIVV |

|                              |        | 380(MSOP8) *4    |       |

| Storage<br>Temperature Range | Tstg   | -65 to +150      | °C    |

| Operating Temperature Range  | Topr   | -40 to +125      | °C    |

| Terminal Voltage             | -      | -0.3 toVcc+0.3   | V     |

<sup>\*</sup> When using at Ta=25°C or higher, 4.5mW (\*1,\*2), 3.3mW (\*3), 3.1 mW (\*4)to be reduced per 1°C

## Recommended Operating Conditions

| Parameter      | Symbol | Limits     | Unit |

|----------------|--------|------------|------|

| Supply Voltage | Vcc    | 2.5 to 5.5 | \/   |

| Input Voltage  | Vin    | 0 to Vcc   | V    |

## ● Memory Cell Characteristics (Vcc=2.5V to 5.5V)

| Doromotor            | Limits    |      |      | Unit   | Condition |  |

|----------------------|-----------|------|------|--------|-----------|--|

| Parameter            | Min.      | Тур. | Max. | Offic  | Condition |  |

|                      | 1,000,000 | -    | -    | Cycles | Ta≦85°C   |  |

| Endurance*5          | 500,000   | -    | -    | Cycles | Ta≦105°C  |  |

|                      | 300,000   | -    | -    | Cycles | Ta≦125°C  |  |

| Dete                 | 40        | -    | -    | Years  | Ta≦25°C   |  |

| Data<br>Retention *5 | 25        | -    | -    | Years  | Ta≦105°C  |  |

| Retention            | 20        | -    | -    | Years  | Ta≦125°C  |  |

<sup>\*5:</sup>Not 100% TESTED

## ●Input / Output Capacitance (Ta=25°C, frequency=5MHz)

| Parameter                | Symbol           | Conditions            | Min. | Max. | Unit |

|--------------------------|------------------|-----------------------|------|------|------|

| Input<br>Capacitance *6  | C <sub>IN</sub>  | V <sub>IN</sub> =GND  | -    | 8    | ۲    |

| Output<br>Capacitance *6 | C <sub>OUT</sub> | V <sub>OUT</sub> =GND | ı    | 8    | pF   |

<sup>\*6:</sup>Not 100% TESTED

## ● Electrical Characteristics (Unless otherwise specified, Ta=-40 to +125°C, Vcc=2.5 to 5.5V)

| Parameter              | meter Symbol Limits |         | Unit | Conditions |       |                                                                                  |

|------------------------|---------------------|---------|------|------------|-------|----------------------------------------------------------------------------------|

| Parameter              | Symbol              | Min.    | Тур. | Max.       | Offic | Conditions                                                                       |

| "H" Input Voltage      | VIH                 | 0.7xVcc | -    | Vcc+0.3    | V     | 2.5V≦Vcc≦5.5V                                                                    |

| "L" Input Voltage      | VIL                 | -0.3    | -    | 0.3xVcc    | V     | 2.5V≦Vcc≦5.5V                                                                    |

| "L" Output Voltage     | VOL                 | 0       | 1    | 0.4        | V     | IOL=2.1mA                                                                        |

| "H" Output Voltage     | VOH                 | Vcc-0.5 | -    | Vcc        | V     | IOH=-0.4mA                                                                       |

| Input Leakage Current  | ILI                 | -10     | _    | 10         | μA    | VIN=0V to Vcc                                                                    |

| Output Leakage Current | ILO                 | -10     | _    | 10         | μΑ    | VOUT=0V to Vcc, CSB=Vcc                                                          |

|                        | ICC1                |         |      | 2.0 *7     | m 1   | Vcc=2.5V,fSCK=5MHz, tE/W=5ms,                                                    |

| Operating Current      | 1001                | _       | _    | 2.5 *8     | mA    | VIH/VIL=0.9Vcc/0.1Vcc, SO=OPEN Byte Wrte, Page Write                             |

| (Write)                | 1000                |         |      | 3.0 *7     | A     | Vcc=5.5V,fSCK=5MHz, tE/W=5ms,                                                    |

|                        | ICC2                | _       | -    | 5.5 *8     | mA    | VIH/VIL=0.9Vcc/0.1Vcc, SO=OPEN Byte Wirte, Page Write                            |

| Operating Current      | ICC3                | _       | _    | 1.5        | mA    | Vcc=2.5V,fSCK=5MHz, VIH/VIL=0.9Vcc/0.1Vcc<br>SO=OPEN, Read, Read Status Register |

| (Read)                 | ICC4                | _       | 1    | 2.0        | mA    | Vcc=5.5V,fSCK=5MHz, VIH/VIL=0.9Vcc/0.1Vcc<br>SO=OPEN, Read, Read Status Register |

| Standby Current        | ISB                 | _       | 1    | 10         | μΑ    | Vcc=5.5V<br>CSB=Vcc, SCK=SI=Vcc or GND, SO=OPEN                                  |

<sup>\*</sup> This product is not designed for protection against radioactive rays.

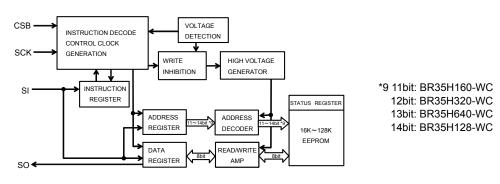

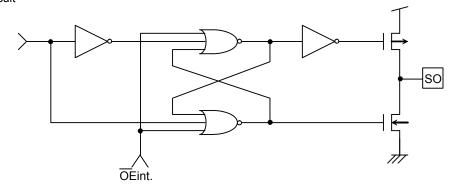

## Block Diagram

Fig.1 Block Diagram

<sup>\*7</sup> BR35H160/320-WC \*8 BR35H640/128-WC

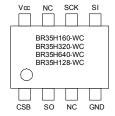

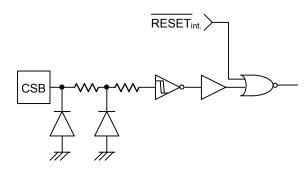

## Pin Assignment and Description

Fig.2 Pin Assignment Diagram

| Terminal Name | Input/Output | Function                                            |

|---------------|--------------|-----------------------------------------------------|

| Vcc           | _            | Power Supply to be connected                        |

| GND           | _            | All input / output reference voltage, 0V            |

| CSB           | Input        | Chip select input                                   |

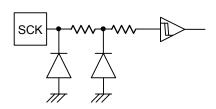

| SCK           | Input        | Serial clock input                                  |

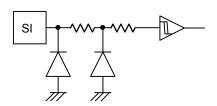

| SI            | Input        | Start bit, ope code, address, and serial data input |

| SO            | Output       | Serial data output                                  |

| NC            | _            | Non connection                                      |

## Operating Timing Characteristics

(Ta=-40°C, to +125°C, unless otherwise specified, load capacitance Cu=100nF

| (Ta=-40°C to +125°C, unless otherwise specified, load capacitance C <sub>L1</sub> =100pF |        |      |       |      |      |  |  |

|------------------------------------------------------------------------------------------|--------|------|-------|------|------|--|--|

| Parameter                                                                                | Symbol | 2.5≦ | Linit |      |      |  |  |

| Parameter                                                                                | Symbol | Min. | Тур.  | Max. | Unit |  |  |

| SCK frequency                                                                            | fSCK   | -    | -     | 5    | MHz  |  |  |

| SCK high time                                                                            | tSCKWH | 85   | -     | -    | ns   |  |  |

| SCK low time                                                                             | tSCKWL | 85   | -     | -    | ns   |  |  |

| CSB high time                                                                            | tCS    | 85   | -     | -    | ns   |  |  |

| CSB setup time                                                                           | tCSS   | 90   | -     | -    | ns   |  |  |

| CSB hold time                                                                            | tCSH   | 85   | -     | -    | ns   |  |  |

| SCK setup time                                                                           | tSCKS  | 90   | -     | -    | ns   |  |  |

| SCK hold time                                                                            | tSCKH  | 90   | -     | -    | ns   |  |  |

| SI setup time                                                                            | tDIS   | 20   | -     | -    | ns   |  |  |

| SI hold time                                                                             | tDIH   | 30   | -     | -    | ns   |  |  |

| Data output delay time1                                                                  | tPD1   | -    | -     | 70   | ns   |  |  |

| Data output delay time2                                                                  | tPD2   | _    | _     | 55   | ns   |  |  |

| (C <sub>L2</sub> =30pF)                                                                  |        |      |       | 00   | 110  |  |  |

| Output hold time                                                                         | tOH    | 0    | -     | -    | ns   |  |  |

| Output disable time                                                                      | tOZ    | -    | -     | 100  | ns   |  |  |

| SCK rise time                                                                            | tRC    | -    | -     | 1    | μs   |  |  |

| SCK fall time *1                                                                         | tFC    | -    | -     | 1    | μs   |  |  |

| OUTPUT                                                                                   | tRO    |      |       | 50   | no   |  |  |

| rise time                                                                                | iko    | _    | _     | 50   | ns   |  |  |

| OUTPUT                                                                                   | tFO    |      |       | 50   | ns   |  |  |

| fall time                                                                                | ii-O   | _    | _     | 50   | 115  |  |  |

| Write time                                                                               | tE/W   | -    | -     | 5    | ms   |  |  |

<sup>\*1</sup> NOT 100% TESTED

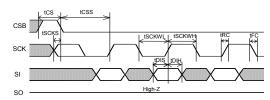

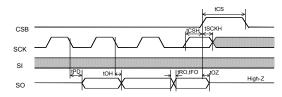

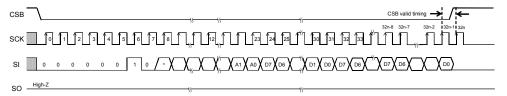

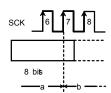

## Sync data input / output timing

Fig.3 Input timing

Data through SI enters the IC in sync with the data rise edge of SCK. Please input address and data starting from the most significant bit MSB.

Fig.4 Input / Output timing

Data through SO is output in sync with the data fall edge of SCK. Data is output starting from the most significant bit MSB.

#### AC measurement conditions

| Darameter                       | Cumbal          |                   | Unit |      |       |  |

|---------------------------------|-----------------|-------------------|------|------|-------|--|

| Parameter                       | Symbol          | Min.              | Тур. | Max. | Offic |  |

| Load capacitance 1              | C <sub>L1</sub> | -                 | -    | 100  | pF    |  |

| Load capacitance 2              | C <sub>L2</sub> | -                 | -    | 30   | pF    |  |

| Input rise time                 | -               | -                 | -    | 50   | ns    |  |

| Input fall time                 | -               | -                 | -    | 50   | ns    |  |

| Input voltage                   | -               | 0.2Vcc / 0.8Vcc   |      | V    |       |  |

| Input / Output judgment voltage | -               | 0.3Vcc / 0.7Vcc V |      |      | V     |  |

#### ●tOZ measurement condition

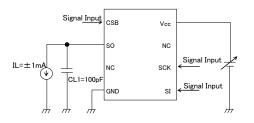

IL is the load current that changes the SO voltage to  $0.5 \times Vcc$ . IL =  $\pm 1mA$ . After CSB starts to rise, the time needed for SO to change to High-Z is defined with 10% changing point from SO=High or SO=Low.

Fig.5 tOZ measurement circuit

Fig.6 tOZ measurement timing

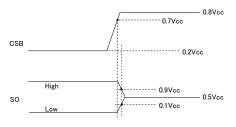

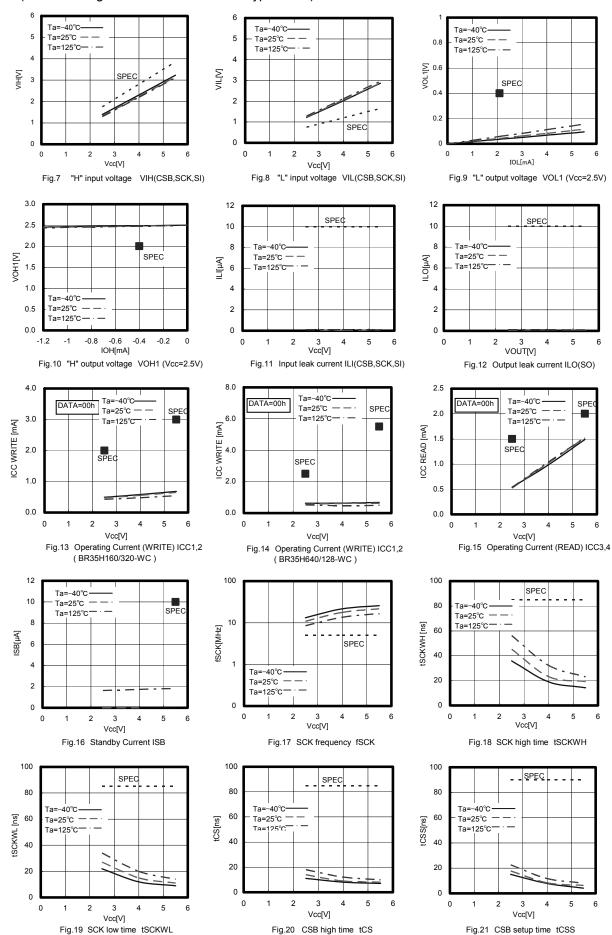

#### Characteristics Data

(The following characteristic data are Typ. value.)

#### Characteristics Data

(The following characteristic data are Typ. value.)

#### Features

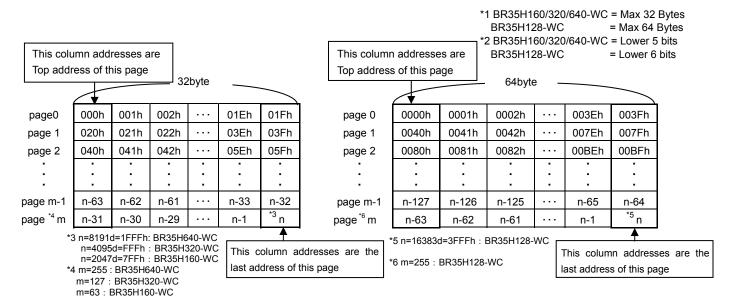

#### OStatus registers

This IC has status registers. The status register has 8 bits and expresses the following parameters.

WEN is set by the write enable command and write disable command. WEN goes into the write disable status when the power source is turned off. The R/B bit is for write confirmation and therefore cannot be set externally.

The status register value can be read by use of the read status command.

## Status registers

| Product Number | bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1  | bit 0    |

|----------------|-------|-------|-------|-------|-------|-------|--------|----------|

| BR35H160-WC    |       |       |       |       |       |       |        |          |

| BR35H320-WC    |       | _     | _     | _     | _     | _     | \A/ENI | <u>_</u> |

| BR35H640-WC    | U     | U     | U     | U     | U     | U     | WEN    | R/B      |

| BR35H128-WC    |       |       |       |       |       |       |        |          |

| bit | Memory location | Function                                                                                                                     |

|-----|-----------------|------------------------------------------------------------------------------------------------------------------------------|

| WEN | Register        | Write and write status register write enable / disable status confirmation bit  WEN=0=prohibited  WEN=1=permitted            |

| R/B | Register        | Write cycle status (READY / BUSY) status confirmation bit  \begin{align*} \bar{R}/B=0=READY \\ \bar{R}/B=1=BUSY \end{align*} |

#### ■Command mode

| onimana mode |                      |                              |             |      |  |

|--------------|----------------------|------------------------------|-------------|------|--|

| Command      |                      |                              | Ope code    |      |  |

|              |                      |                              | BR35H160-WC |      |  |

|              |                      | Contents                     | BR35H320-WC |      |  |

|              |                      |                              | BR35H640-WC |      |  |

|              |                      |                              | BR35H128-WC |      |  |

| WREN         | Write enable         | Write enable command         | 0000        | 0110 |  |

| WRDI         | Write disable        | Write disable command        | 0000        | 0100 |  |

| READ         | Read                 | Read command                 | 0000        | 0011 |  |

| WRITE        | Write                | Write command                | 0000        | 0010 |  |

| RDSR         | Read status register | Status register read command | 0000        | 0101 |  |

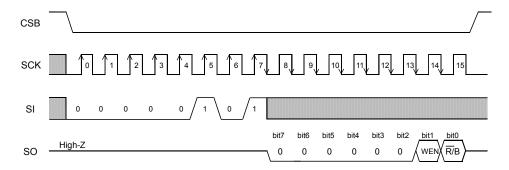

## Timing chart

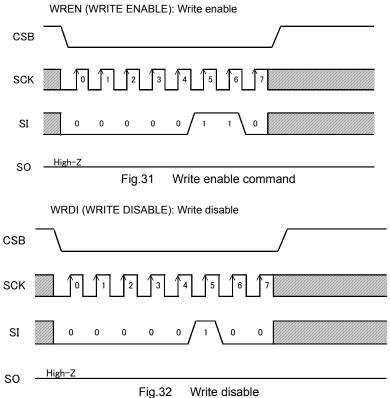

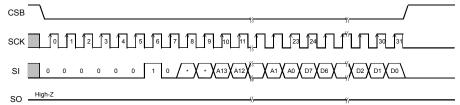

1. Write enable (WREN) / disable (WRDI) cycle

OThis IC has a write enable status and a write disable status. Write enable status is achieved by the write enable command and write disable status is achieved by the write disable command. As for these commands, set CSB to LOW and then input the respective ope codes. The respective commands are accepted at the 7-th clock rise. The command is also valid with Inputs over 7 clocks.

In order to perform a write command it is necessary to use the write enable command to set the IC to the write enable status. If a write command is input during write disable status the command will be cancelled. After a write command is input during write enable status the IC will return to the write disable status. When turning on the power the IC will be in write disable status.

| Product     | Address |

|-------------|---------|

| number      | Length  |

| BR35H160-WC | A10-A0  |

| BR35H320-WC | A11-A0  |

| BR35H640-WC | A12-A0  |

| BR35H128-WC | A13-A0  |

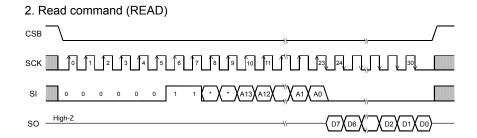

Fig.33 Read command (BR35H160/320/640/128-WC)

By use of the read command, the data of the EEPROM can be read. As for this command, set CSB to LOW, then input the address after the read ope code. EEPROM starts data output of the designated address. Data output is started from the SCK fall of 23 clock and from D7 to D0 sequentially. The IC features an increment read function. After the output of 1 byte (8bits) of data, by continuing input of SCK the next data addresses can be read. Increment read can read all addresses of the EEPROM. After reading the data of the most the significant address, by continuing with the increment read the data of the most insignificant address is read.

| Product     | Address |  |  |

|-------------|---------|--|--|

| number      | Length  |  |  |

| BR35H160-WC | A10-A0  |  |  |

| BR35H320-WC | A11-A0  |  |  |

| BR35H640-WC | A12-A0  |  |  |

| BR35H128-WC | A13-A0  |  |  |

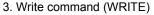

Fig.34 Write command (BR35H160/320/640/128-WC)

Fig.35 N Byte page write command (BR35H160/320/640-WC)

Fig.36 N Byte page write command (BR35H128-WC)

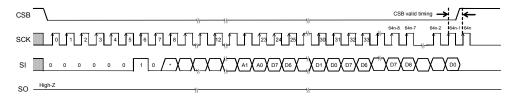

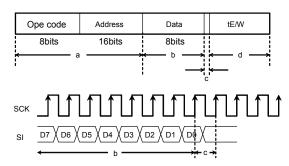

With the write command data can be written to the EEPROM. As for this command, set CSB to LOW, then input address and data after inputting the write ope code. Then, by making CSB HIGH, the EEPROM starts writing. The write time of EEPROM requires time of tE/W (Max 5ms). During tE/W, commands other than the status read command are not accepted. Start CSB after taking the last data (D0) and before the next SCK clock starts. At other timings the write command will not be executed and will be cancelled. The IC has page write functionality. After input 1 byte (8bits) of data, by continuing data input without starting CSB, data up to  $32/64^{*1}$  bytes can be written in one tE/W. In page write, the insignificant  $5/6^{*2}$  bit of the designated address is incremented internally every time 1 byte of data is input, and data is written to the respective addresses. When data larger then the maximum bytes is input the address rolls over and previously input data is overwritten.

Write command is executed when CSB rises between the SCK clock rising edge to recognize the 8th bit's of data input and the next SCK rising edge. At other timings the write command is not executed and cancelled (Fig.42 valid timing c). In page write, the CSB valid timing is every 8 bits. If CSB rises at other timings page write is cancelled together with the write command and the input data is reset.

Fig.37 EEPROM physical address for Page write command (32/64Byte)

## ●Example of Page write command

| No. | Addresses of Page0 | 000h | 001h | 002h | <br>01Eh | 01Fh |

|-----|--------------------|------|------|------|----------|------|

| 1   | Previous data      | 00h  | 01h  | 02h  | <br>1Eh  | 1Fh  |

| 2   | 2 bytes input data | AAh  | 55h  | -    | <br>ı    | -    |

| 3   | After No.2         | AAh  | 55h  | 02h  | <br>1Eh  | 1Fh  |

| 4   | 34 byte input data | AAh  | 55h  | AAh  | <br>AAh  | 55h  |

|     |                    | FFh  | 00h  | -    | <br>1    | -    |

| 5   | After No.4         | FFh  | 00h  | AAh  | <br>AAh  | 55h  |

- a : In case of input the data of No.② which is 2 bytes page write command for the data of No.①, EEPROM data changes like No.③.

- b : In case of input the data of No. 4 which is 34 bytes page write command for the data of No. 1, EEPROM data changes like No. 5.

- c: In case of a or b, when write command is cancelled, EEPROM data keep No.  $\ensuremath{\textcircled{\scriptsize 1}}.$

In page write command, when data is set to the last address of a page (e.g. address "03Fh" of page 1), the next data will be set to the top address of the same page (e.g. address "020h" of page 1). This is why page write address increment is available in the same page. As a reference, if of 32 bytes, page write command is executed for 2 bytes the data of the other 30 bytes without addresses will not be changed.

### 4. Status register read command

Fig.38 Status register read command (BR35H160/320/640/128-WC)

The EEPROM status can be read by use of the status register read command. For this command set CSB to Low then input the ope code of the status register read command followed by the clock input as shown above. The data of status register will then be read out. This command features increment functionality. When clock input is continued during CSB=Low, 8 bytes of status register data will be continuously read out. When this command is executed from the start of write programming to the end of write programming, the end of write programming can be confirmed by checking the following changes: WEN=Low followed by  $\overline{R}$ /B=Low. After confirming the end of write programming, before inputting the next command CSB first needs to be High and then put back to Low.

#### At standby

#### OCurrent at standby

Set CSB "H", and be sure to set SCK, SI input "L" or "H". Do not input intermediate electric potantial.

#### **OTiming**

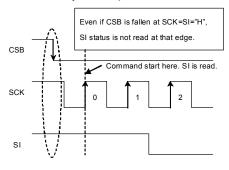

As shown in Fig.39, at standby, when SCK is "H", even if CSB falls, SI status is not read at fall edge. SI status is read at SCK rise edge after fall of CSB. At standby and at power ON/OFF, set CSB "H" status

Fig.39 Operating timing

## Method to cancel each command

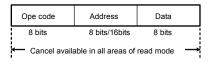

#### **OREAD**

· Cancellation method: cancel by CSB = "H"

Fig.40 READ cancel valid timing

Fig.41 RDSR cancel valid timing

#### **ORDSR**

· Cancellation method: cancel by CSB = "H"

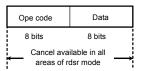

#### OWRITE, PAGE WRITE

- a : Ope code, address input area. Cancellation possible by CSB="H"

- b : Data input area (D7~D1 input area) Cancellation possible by CSB="H"

- c : Data input area (D0 area) Write starts after CSB rise. After CSB rise, cancellation is no longer possible.

- d : tE/W area. Cancellation is possible by CSB = "H". However, when write starts (CSB rise) in area c, cancellation is no longer possible. Also, cancellation is not possible by continues inputting of SCK clock. In page write mode, there is a write enable area at every 8 clocks.

Fig.42 WRITE cancel valid timing

- Note 1) If Vcc is set to OFF during execution of write the data of the designated address is not guaranteed. Please execute write again.

- Note 2) If CSB rises at the same timing as that the SCK rises, write execution / cancel will become unstable.

Therefore, it is recommended to let CSB rise in the SCK = "L" area. As for SCK rise, ensure a timing of tCSS / tCSH or higher.

## OWREN/WRDI

- a: From ope code to 7-th clock rise, cancel by CSB = "H".

- b: Cancellation is not possible when CSB rises after the 7-th clock.

Fig.43 WREN/WRDI cancel valid timing

#### High speed operations

In order to realize stable high speed operations, pay attention to the following input / output pin conditions.

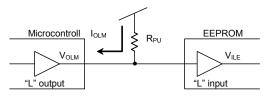

#### Olnput pin pull up, pull down resistance

When attaching pull up, pull down resistance to the EEPROM input pin, select an appropriate value for the microcontroller VOL, IOL from the VIL characteristics of this IC.

#### OPull up resistance

Fig.44 Pull up resistance

$$R_{PU} \ge \frac{V_{CC} - V_{OLM}}{I_{OLM}} \cdots 1$$

$V_{OLM} \le V_{ILE} \cdots 2$

Example) When Vcc=5V,  $V_{ILE}$ =1.5V,  $V_{OLM}$ =0.4V,  $I_{OLM}$ =2mA, from the equation ①,

$$R_{PU} \ge \frac{5 - 0.4}{2 \times 10^{-3}}$$

$$\therefore R_{PU} \ge 2.3[k\Omega]$$

With the value of Rpu to satisfy the above equation,  $V_{OLM}$  becomes 0.4V or lower, and with  $V_{ILE}$  (=1.5V), the equation ② is also satisfied.

- V<sub>ILE</sub> :EEPROM V<sub>IL</sub> specifications

- V<sub>OLM</sub>:Microcontroller V<sub>OL</sub> specifications

- I<sub>OLM</sub> :Microcontroller I<sub>OL</sub> specifications

Also, in order to prevent malfunction or erroneous write at power ON/OFF, be sure to make CSB pull up.

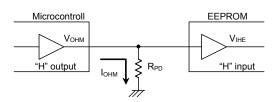

#### OPull down resistance

Fig.45 Pull down resistance

$$R_{PD} \ge \frac{V_{OHM}}{I_{OHM}} \cdots 3$$

$$V_{OHM} \ge V_{IHE} \cdots 4$$

Example) When  $V_{CC}$ =5V,  $V_{OHM}$ = $V_{CC}$ -0.5V,  $I_{OHM}$ =0.4mA,  $V_{IHE}$ = $V_{CC}$ ×0.7V, from the equation③,

$$R_{PD} \ge \frac{5 - 0.5}{0.4 \times 10^{-3}}$$

$R_{PD} \ge 11.3[k \Omega]$

The operations speed changes according to the amplitude VIHE, VILE of the signals input to the EEPROM. More stable high speed operations can be realized by inputting signals with Vcc / GND levels of amplitude. On the contrary, when signals with an amplitude of 0.8Vcc / 0.2Vcc are input, operation speed slows down.\*1

In order to realize more stable high speed operation, it is recommended to set the values of  $R_{PU}$ ,  $R_{PD}$  as large as possible, and to have the amplitude of the signals input to the EEPROM close to the Vcc / GND amplitude level. (1 In this case, the guaranteed value of operating timing is guaranteed.)

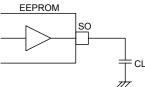

#### OSO load capacitance condition

The load capacitance of the SO output pin affects the SO output delay characteristic. (Data output delay time, time from HOLDB to High-Z, output rise time, output fall time.). Make the SO load capacitance small to improve the output delay characteristic.

Fig.46 SO load dependency of data output delay time tPD

## OOther cautions

Make all wires from the microcontroller to EEPROM input pin the same length. This in order to prevent setup / hold violation to the EEPROM.

## ● Equivalent circuit Output circuit

Fig.47 SO output equivalent circuit

## OInput circuit

Fig.48 CSB input equivalent circuit

Fig.49 SCK input equivalent circuit

Fig.50 SI input equivalent circuit

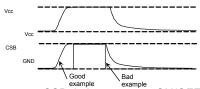

## ●Notes on power ON/OFF

OAt power ON/OFF set CSB="H" (=Vcc).

When CSB is "L", the IC goes into input accept status (active). If power is turned on in this status noises, etc. may cause malfunction or erroneous write. To prevent this, set CSB to "H" at power ON. (When CSB is in "H" status, all inputs are canceled.)

Fig.51 CSB timing at power ON/OFF

(Good example) CSB terminal is pulled up to Vcc.

After turning power off allow for 10ms or more before turning power on again. If power is turned on without observing this condition, the IC internal circuit may not be reset.

(Bad example) CSB terminal is "L" at power ON/OFF.

In this case, CSB always becomes "L" (active status), and the EEPROM may malfunction or perform an erroneous write due to noises, etc.

This can even occur when CSB input is High-Z.

#### **OLVCC** circuit

LVCC (Vcc-Lockout) circuit prevents data rewrite action at low power and prevents erroneous write.

At LVCC voltage (Typ. =1.9V) or below, it prevents data rewrite.

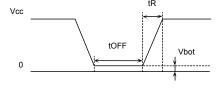

#### OP.O.R. circuit

This IC has a POR (Power On Reset) circuit as countermeasure against erroneous write. After the POR operation is performed, write disable status is entered. The POR circuit is only valid when power is ON and does not work when power is OFF. When power is ON and the following recommended tR, tOFF, Vbot conditions are not satisfied, write enable status might be entered due to noise etc.

Fig.52 Rise waveform

| Recommended conditions for t <sub>R</sub> , t <sub>OFF</sub> , vbot |                |               |  |  |  |

|---------------------------------------------------------------------|----------------|---------------|--|--|--|

| tR                                                                  | tR tOFF        |               |  |  |  |

| 10ms or below                                                       | 10ms or higher | 0.3V or below |  |  |  |

| 100ms or below                                                      | 10ms or higher | 0.2V or below |  |  |  |

## Noise countermeasures

OVcc noise (bypass capacitor)

When noise or surge gets in the power source line, malfunction may occur. To prevent this, it is recommended to attach a bypass capacitor (0.1µF) between IC Vcc and GND, as close to IC as possible.

It is also recommended to attach a bypass capacitor between the board Vcc and GND.

#### OSCK noise

When the rise time of SCK (tRC) is long and a there is a certain degree of noise, malfunction may occur due to clock bit displacement. To avoid this, a Schmitt trigger circuit is built in the SCK input. The hysteresis width of this circuit is set to about 0.2V. If noises exist at the SCK input set the noise amplitude to 0.2Vp-p or below. Also, it is recommended to set the rise time of SCK (tRC) to 100ns or below. In case the rise time is 100ns or higher, sufficient noise countermeasures are needed. Clock rise, fall time should be as small as possible.

#### Notes for use

- (1) Described numeric values and data are design representative values and not guaranteed.

- (2) We believe that the application circuit examples are recommendable. However, in actual use, please sufficiently further characteristics. When changing the fixed number of external parts, make your decision with sufficient margin, in consideration of static characteristics, transition characteristics and fluctuations of external parts and our LSI.

- (3) Absolute maximum ratings

If the absolute maximum ratings such as impressed voltage, operating temperature range, etc. are exceeded, the LSI might be damaged. Please do not impress voltage or temperature exceeding the absolute maximum ratings. In case of fear of exceeding the absolute maximum ratings please take physical safety countermeasures such as fuses and see to it that conditions exceeding the absolute maximum ratings are impressed to LSI.

- (4) GND electric potential

- Set the voltage of the GND terminal as low as possible with all action conditions. Ensure that that all terminal voltages are higher than that of the GND terminal.

- (5) Heat design

- In consideration of permissible dissipation in actual use condition, please carry out the heat design with sufficient margin.

- (6) Inter-terminal short circuit and wrong packaging

- When packaging the LSI onto a board, pay sufficient attention to the LSI direction and displacement. Wrong packaging may damage LSI. Short circuit between LSI terminals, terminals and power source, terminal and GND due to foreign matters may also result in LSI damage.

- (7) Use in strong electromagnetic fields may cause malfunction. Therefore, please evaluate the design sufficiently.

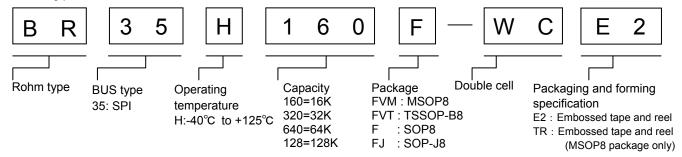

## Ordering part number

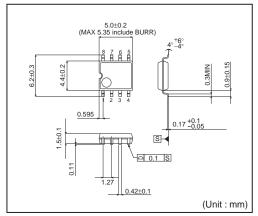

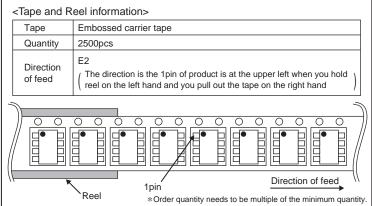

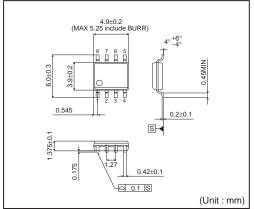

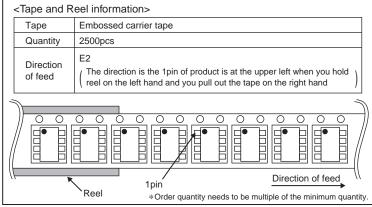

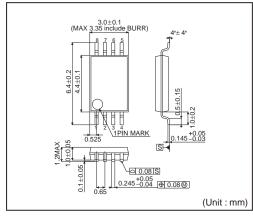

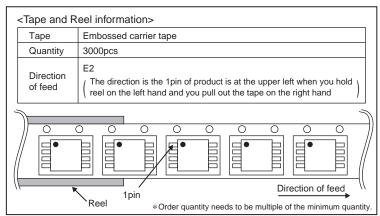

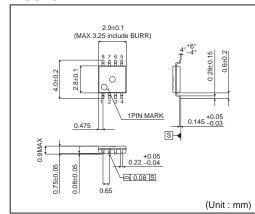

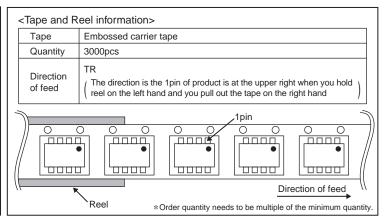

## Package specifications

## SOP8

#### SOP-J8

## TSSOP-B8

## ● Package specifications (Continue)

## MSOP8

#### Notes

No copying or reproduction of this document, in part or in whole, is permitted without the consent of ROHM Co.,Ltd.

The content specified herein is subject to change for improvement without notice.

The content specified herein is for the purpose of introducing ROHM's products (hereinafter "Products"). If you wish to use any such Product, please be sure to refer to the specifications, which can be obtained from ROHM upon request.

Examples of application circuits, circuit constants and any other information contained herein illustrate the standard usage and operations of the Products. The peripheral conditions must be taken into account when designing circuits for mass production.

Great care was taken in ensuring the accuracy of the information specified in this document. However, should you incur any damage arising from any inaccuracy or misprint of such information, ROHM shall bear no responsibility for such damage.

The technical information specified herein is intended only to show the typical functions of and examples of application circuits for the Products. ROHM does not grant you, explicitly or implicitly, any license to use or exercise intellectual property or other rights held by ROHM and other parties. ROHM shall bear no responsibility whatsoever for any dispute arising from the use of such technical information.

The Products specified in this document are intended to be used with general-use electronic equipment or devices (such as audio visual equipment, office-automation equipment, communication devices, electronic appliances and amusement devices).

The Products specified in this document are not designed to be radiation tolerant.

While ROHM always makes efforts to enhance the quality and reliability of its Products, a Product may fail or malfunction for a variety of reasons.

Please be sure to implement in your equipment using the Products safety measures to guard against the possibility of physical injury, fire or any other damage caused in the event of the failure of any Product, such as derating, redundancy, fire control and fail-safe designs. ROHM shall bear no responsibility whatsoever for your use of any Product outside of the prescribed scope or not in accordance with the instruction manual.

The Products are not designed or manufactured to be used with any equipment, device or system which requires an extremely high level of reliability the failure or malfunction of which may result in a direct threat to human life or create a risk of human injury (such as a medical instrument, transportation equipment, aerospace machinery, nuclear-reactor controller, fuel-controller or other safety device). ROHM shall bear no responsibility in any way for use of any of the Products for the above special purposes. If a Product is intended to be used for any such special purpose, please contact a ROHM sales representative before purchasing.

If you intend to export or ship overseas any Product or technology specified herein that may be controlled under the Foreign Exchange and the Foreign Trade Law, you will be required to obtain a license or permit under the Law.

Thank you for your accessing to ROHM product informations. More detail product informations and catalogs are available, please contact us.

## ROHM Customer Support System

http://www.rohm.com/contact/

OOO «ЛайфЭлектроникс" "LifeElectronics" LLC

ИНН 7805602321 КПП 780501001 P/C 40702810122510004610 ФАКБ "АБСОЛЮТ БАНК" (ЗАО) в г.Санкт-Петербурге К/С 3010181090000000703 БИК 044030703

Компания «Life Electronics» занимается поставками электронных компонентов импортного и отечественного производства от производителей и со складов крупных дистрибьюторов Европы, Америки и Азии.

С конца 2013 года компания активно расширяет линейку поставок компонентов по направлению коаксиальный кабель, кварцевые генераторы и конденсаторы (керамические, пленочные, электролитические), за счёт заключения дистрибьюторских договоров

## Мы предлагаем:

- Конкурентоспособные цены и скидки постоянным клиентам.

- Специальные условия для постоянных клиентов.

- Подбор аналогов.

- Поставку компонентов в любых объемах, удовлетворяющих вашим потребностям.

- Приемлемые сроки поставки, возможна ускоренная поставка.

- Доставку товара в любую точку России и стран СНГ.

- Комплексную поставку.

- Работу по проектам и поставку образцов.

- Формирование склада под заказчика.

- Сертификаты соответствия на поставляемую продукцию (по желанию клиента).

- Тестирование поставляемой продукции.

- Поставку компонентов, требующих военную и космическую приемку.

- Входной контроль качества.

- Наличие сертификата ISO.

В составе нашей компании организован Конструкторский отдел, призванный помогать разработчикам, и инженерам.

Конструкторский отдел помогает осуществить:

- Регистрацию проекта у производителя компонентов.

- Техническую поддержку проекта.

- Защиту от снятия компонента с производства.

- Оценку стоимости проекта по компонентам.

- Изготовление тестовой платы монтаж и пусконаладочные работы.

Тел: +7 (812) 336 43 04 (многоканальный) Email: org@lifeelectronics.ru