# Middle Power Class-D Speaker Amplifier series

# 20W+20W Full Digital Speaker Amplifier with built-in DSP

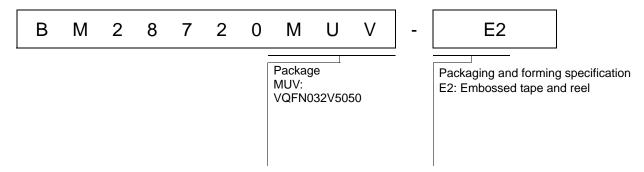

## **BM28720MUV**

## **General Description**

BM28720MUV is a Full Digital Speaker Amplifier with built-in DSP (Digital Sound Processor) designed for Flat-panel TVs in particular for space-saving and low-power consumption, delivers an output power of 20W+20W. This IC employs Bipolar, CMOS, and DMOS (BCD) process technology that eliminates turn-on resistance in the output power stage and internal loss due to line resistances up to an ultimate level. With this technology, the IC can achieve high efficiency. In addition, the IC is packaged in a compact reverse heat radiation type power package to achieve low power consumption and low heat generation and eliminates necessity of external heat-sink up to a total output power of 40W. This product satisfies both needs for drastic downsizing, low-profile structures and many function, high quality playback of sound system.

## **Key Specifications**

■ Supply voltage (VCC) 10V to 24V

■ Speaker output power (VCC=18.5V, RL=8Ω)

■ THD+N 0.07 [%] (Typ.)

# **Applications**

- Flat Panel TVs (LCD, Plasma)

- Home Audio

- Desktop PC

- Amusement equipments

- Electronic Music equipments, etc.

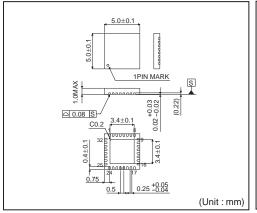

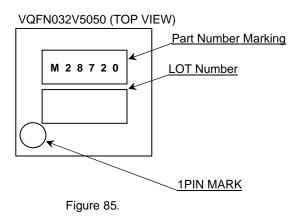

**Package** W(Typ) x D(Typ) x H(Max) VQFN032V5050 5.00mm x 5.00mm x 1.00mm

#### **Features**

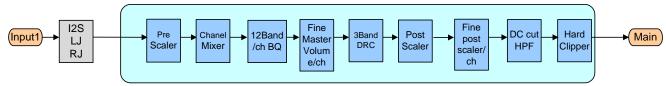

- This IC includes the DSP (digital sound processor) for Audio signal processing for Flat TVs.

12 Band/ch P-EQ, 3 Band DRC, Pre-scaler, Channel mixer, Fine Master Volume, Hard Clipper, Level Meter etc.

- This IC has one input systems of digital audio interface. (No needs of Master Clock)

- I<sup>2</sup>S / LJ / RJ format

- LRCLK: 32k/44.1k/48KHz

- BCLK: 32fs / 48fs / 64fs

- SDATA: 16 / 20 / 24bit

- This IC has one output systems of digital audio interface.

- I<sup>2</sup>S format

- SDATA: 16 / 20 / 24bit

- With wide range of power supply voltage.

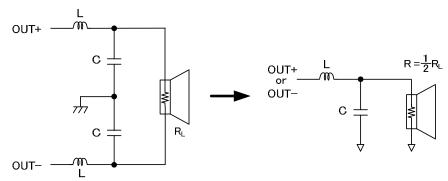

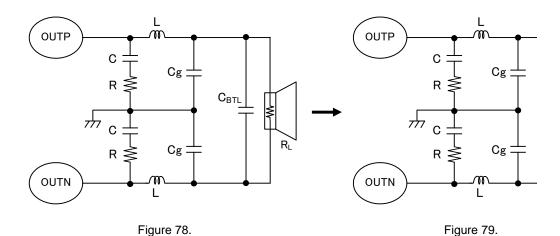

- The monaural output that can reduce the number of external parts can be used.

- With high efficiency and low heat dissipation contributing to miniaturization, slim design, and also power saving of the system.

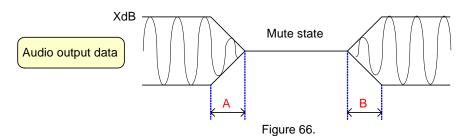

- Eliminates pop-noise generated during the power supply on/off. High quality muting performance is realized by using the soft-muting technology.

- This IC is built-in with various protection functions for highly reliability design.

- High temperature protection

- Under voltage protection

- Output short protection

- DC voltage protection

- Clock stop protection

Small package

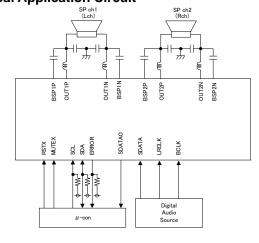

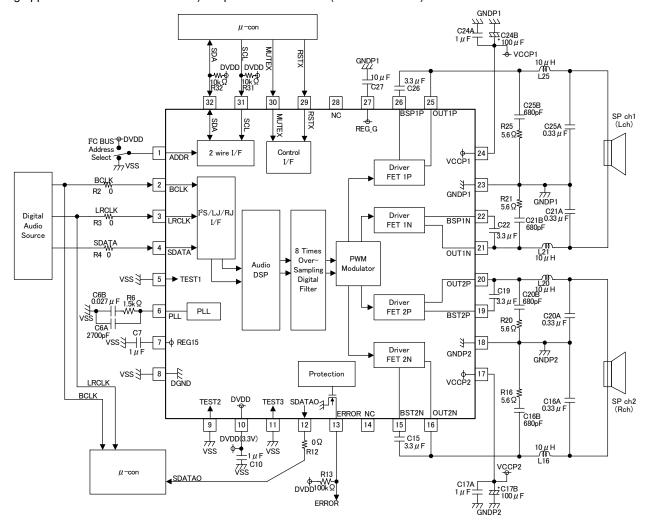

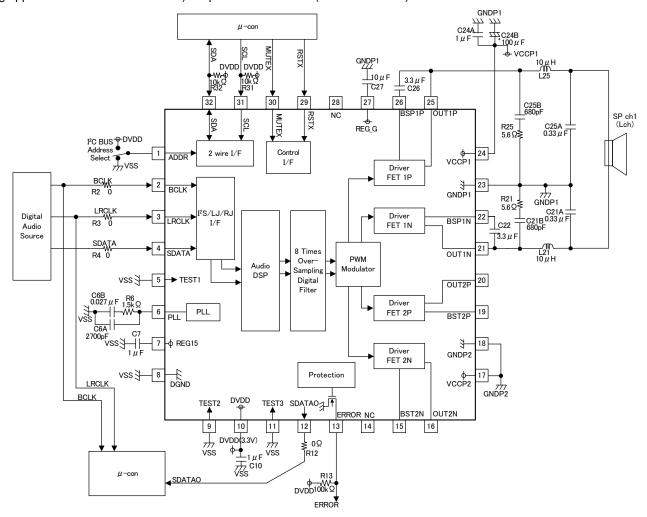

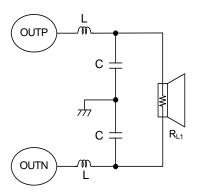

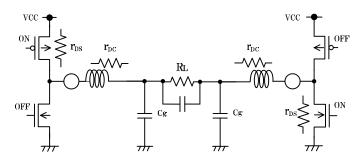

# **Typical Application Circuit**

Figure 1. Typical application circuits

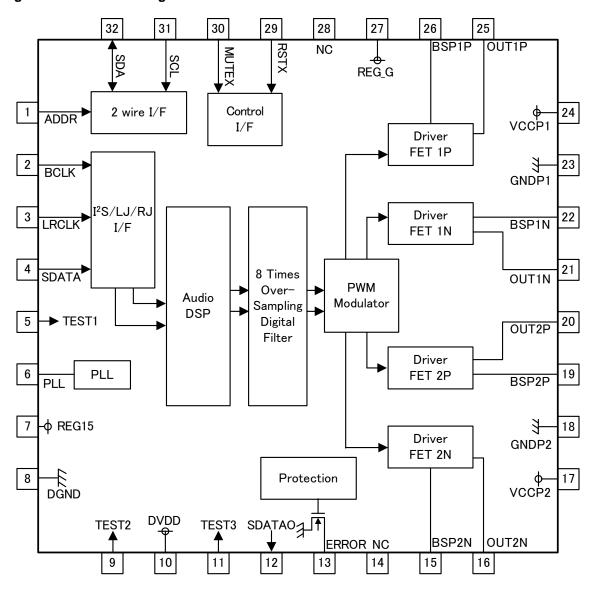

# Pin configuration and Block diagram

Figure 2. Pin configurations and Block diagram (Top View)

# **Pin Description**

| No. | Name  | I/O | No. | Name   | I/O | No. | Name  | I/O | No. | Name  | I/O |

|-----|-------|-----|-----|--------|-----|-----|-------|-----|-----|-------|-----|

| 1   | ADDR  | I   | 9   | TEST2  | I   | 17  | VCCP2 | -   | 25  | OUT1P | 0   |

| 2   | BCLK  | I   | 10  | DVDD   | -   | 18  | GNDP2 | -   | 26  | BSP1P | I   |

| 3   | LRCK  | I   | 11  | TEST3  | I   | 19  | BSP2P | I   | 27  | REG_G | 0   |

| 4   | SDATA | I   | 12  | SDATAO | 0   | 20  | OUT2P | 0   | 28  | NC    | -   |

| 5   | TEST1 | I   | 13  | ERROR  | 0   | 21  | OUT1N | 0   | 29  | RSTX  | I   |

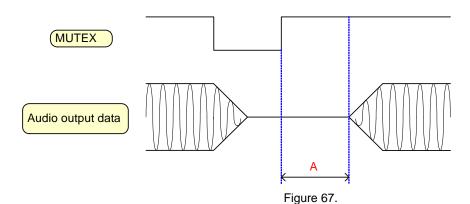

| 6   | PLL   | 0   | 14  | NC     | -   | 22  | BSP1N | I   | 30  | MUTEX | Ι   |

| 7   | REG15 | 0   | 15  | BSP2N  | I   | 23  | GNDP1 | -   | 31  | SCL   | I   |

| 8   | DGND  | -   | 16  | OUT2N  | 0   | 24  | VCCP1 | 0   | 32  | SDA   | I/O |

# Absolute Maximum Ratings (Ta=25°C)

| Item                         | Symbol | Limit               | Unit | Conditions                       |                   |

|------------------------------|--------|---------------------|------|----------------------------------|-------------------|

|                              | VCC    | -0.3 to 34          | V    | Pin 17, 24                       | (Note 1) (Note 2) |

| Supply voltage               | DVDD   | -0.3 to 4.5         | V    | Pin 10                           | (Note 1)          |

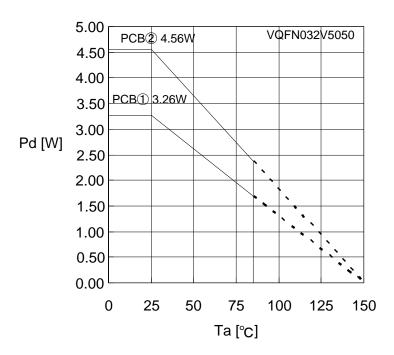

| <b>.</b>                     | D.I    | 3.26                | W    |                                  | (Note 3)          |

| Power dissipation            | Pd     | 4.56                | W    |                                  | (Note 4)          |

| Input voltage 1              | VIN1   | -0.3 to<br>DVDD+0.3 | V    | Pin 1 - 5, 9, 11, 12, 13, 29 -32 | (Note 1)          |

| Terminal voltage 1           | VPIN1  | -0.3 to 7.0         | V    | Pin 27                           | (Note 1)          |

| Terminal voltage 2           | VPIN2  | -0.3 to 29          | V    | Pin 16, 20, 21, 25               | (Note 1)(Note 5)  |

| Terminal voltage 3           | VPIN3  | OUTxx+6.0           | V    | Pin 15, 19, 22, 26               | (Note 1)          |

| Operating temperature range  | Topr   | -25 to +85          | °C   |                                  |                   |

| Storage temperature range    | Tstg   | -55 to +150         | °C   |                                  |                   |

| Maximum junction temperature | Tjmax  | +150                | °C   |                                  |                   |

(Note 1) The voltage that can be applied reference to GND (Pin 8, 18, 23).

(Note 2) Do not exceed Pd and Tjmax=150°C.

(Note 3) 74.2mm × 74.2mm × 1.6mm, FR4, 4-layer glass epoxy board

(Top and bottom layer back copper foil size: 20.2mm², 2nd and 3rd layer back copper foil size: 5505mm²)

Derating in done at 26.1 mW/°C for operating above Ta=25°C. There are thermal via on the board.

(Note 4) 74.2mm × 74.2mm × 1.6mm, FR4, 4-layer glass epoxy board (Copper area 5505mm²)

Derating in done at 36.5 mW/°C for operating above Ta=25°C. There are thermal via on the board.

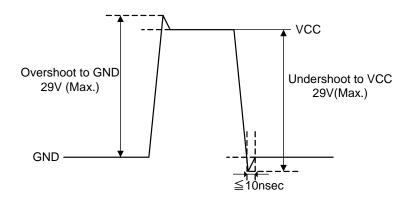

(Note 5) It should use it below this ratings limit including the AC peak waveform (overshoot) for all conditions.

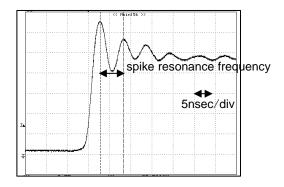

At only undershoot, it is admitted using at ≦10nse and ≦29V by the VCC reference. (Please refer following figure.)

Figure 3.

# Recommended Operating Ratings (Ta=25°C)

| Item                   | Symbol         | Limit    | Unit | Condition                              | ns                |  |

|------------------------|----------------|----------|------|----------------------------------------|-------------------|--|

| Cumply voltage         | VCC            | 10 to 24 | V    | Pin 17, 24                             | (Note 1) (Note 2) |  |

| Supply voltage         | DVDD           | 3 to 3.6 | V    | Pin 10                                 | (Note 1)          |  |

| Minimum load immades   | Б              | 5.4      | Ω    | Pin 16, 20, 21, 25<br>VCC = 18V to 24V | (Note 6)          |  |

| Minimum load impedance | R <sub>L</sub> | 3.6      | Ω    | Pin 16, 20, 21, 25<br>VCC < 18V        | (Note 6)          |  |

(Note 6) Do not exceed Pd.

# **Electrical Characteristics**

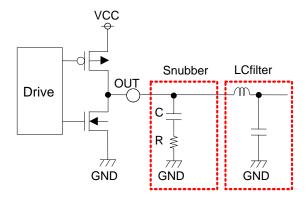

(Unless otherwise specified Ta=25°C, VCC=18V, DVDD=3.3V, RSTX=3.3V, MUTEX=3.3V, f=1kHz, R<sub>L</sub>=8 $\Omega$ , DSP: Through, fs=48kHz, MCLK=256fs, Snubber circuit for output terminal: R=5.6 $\Omega$ , C=680pF)

| Itom Symbol                 |                   |          | Limit |            | 11.7    | 0 150                                     |

|-----------------------------|-------------------|----------|-------|------------|---------|-------------------------------------------|

| Item                        | Symbol            | Min      | Тур   | Max        | Unit    | Conditions                                |

| Total circuit               |                   |          |       |            |         |                                           |

| Circuit current 1           | I <sub>CC1</sub>  | -        | 45    | 90         | mA      | Pin 17, 24, No load                       |

| (Normal mode)               | I <sub>DD1</sub>  | -        | 9     | 19         | mA      | Pin 10, -infinity dBFS input, No load     |

|                             | -                 |          | 10    | 40         |         | Pin 17, 24, No load                       |

| Circuit current 2           | I <sub>CC2</sub>  | -        | 10    | 40         | μA      | RSTX=0V, MUTEX=0V                         |

| (Reset mode)                |                   |          | 0.5   | 7.0        | A       | Pin 10,infinity dBFS input, No load       |

|                             | I <sub>DD2</sub>  | -        | 2.5   | 7.0        | mA      | RSTX=0V, MUTEX=0V                         |

| Open-drain terminal         | \/                | _        | _     | 0.0        | V       | Dia 22 L 0 5 m A                          |

| Low level voltage           | V <sub>ERR</sub>  | -        | -     | 8.0        | V       | Pin 23, I <sub>o</sub> =0.5mA             |

| Regulator output voltage 1  | $V_{REG\_G}$      | 4.9      | 5.7   | 6.5        | V       | Pin 27                                    |

| Regulator output voltage 2  | $V_{REG15}$       | 1.3      | 1.5   | 1.7        | V       | Pin 7                                     |

| High level input voltage    | V <sub>IH</sub>   | 2.5      | -     | 3.3        | V       | Pin 1 - 5, 9, 11, 12, 29 -32              |

| Low level input voltage     | V <sub>IL</sub>   | 0        | -     | 0.8        | V       | Pin 1 - 5, 9, 11, 12, 29 -32              |

| Input current               | -                 | 450      | 400   | <b>F</b> 0 |         | D' O ANIN ON                              |

| (Input pull-up terminal)    | I <sub>UP</sub>   | -150     | -100  | -50        | μA      | Pin 2 - 4 VIN = 0V                        |

| Input current               | -                 | 25       | 70    | 105        |         | Dia 4 00 00 VIN 0 0V                      |

| (Input pull-down terminal)  | I <sub>DN</sub>   | 35       | 70    | 100        | μA      | Pin 1, 29, 30, VIN = 3.3V                 |

| Input current               |                   | 4        | 0     | -          | μΑ      | Pin 31, 32, V                             |

| (SCL, SDA terminal)         | I <sub>IL</sub>   | -1       |       |            |         | IN = 0V                                   |

| Input current               |                   | _        | 0     | 4          |         | Di- 24 22 VIN 2 2V                        |

| (SCL, SDA terminal)         | I <sub>IH</sub>   | -        | 0     | 1          | μA      | Pin 31, 32, VIN = 3.3V                    |

| Speaker amplifier output    |                   |          |       |            |         |                                           |

| Maximum output power 1      | P <sub>O1</sub>   | -        | 10    | -          | W       | VCC=13V,THD+n=10% *8                      |

| Maximum autaut navuar 2     | J                 |          | 20    | _          | W       | VCC=18.5V,THD+n=10%                       |

| Maximum output power 2      | P <sub>O2</sub>   | -        | 20    | -          | VV      | (Note 7)                                  |

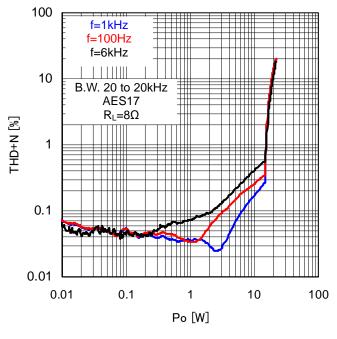

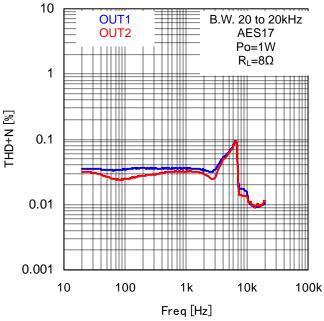

| Total harmonia diatortion 1 | TUD1              |          | 0.07  |            | %       | P <sub>O</sub> =1W, BW=20 to 20kHz(AES17) |

| Total harmonic distortion 1 | THD1              | -        | 0.07  | -          | 70      | (Note 7)                                  |

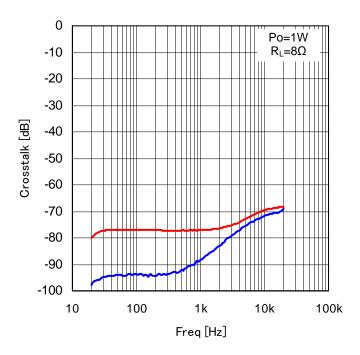

| Crosstalk 1                 | CT1               | 60       | 80    |            | dB      | VCC=13V, P <sub>O</sub> =1W, BW=IHF-A     |

| CIUSSIAIK I                 | CII               | 60       | 0U    | -          | ub      | (Note 7)                                  |

| Output noise voltage 1      | V <sub>NO1</sub>  | _        | 80    | _          | μVrms   | -∞dBFS Input, BW=IHF-A                    |

| Output hoise voltage i      | V NO1             | <u>-</u> | 00    | -          | μνιιιίδ | (Note 7)                                  |

|                             | f <sub>PWM1</sub> | -        | 256   | -          | kHz     | fs=32 kHz                                 |

| PWM sampling frequency      | f <sub>PWM2</sub> | -        | 352.8 | -          | kHz     | fs=44.1 kHz                               |

|                             | f <sub>PWM3</sub> | -        | 384   | -          | kHz     | fs=48 kHz                                 |

(Note 7) These items show the typical performance of device and depend on board layout, parts, and power supply.

The standard value is in mounting device and parts on surface of ROHM's board directly.

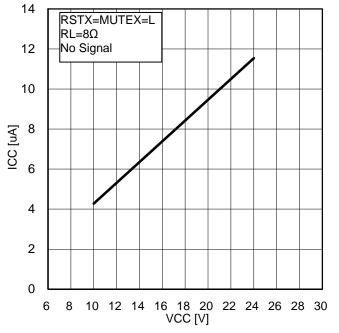

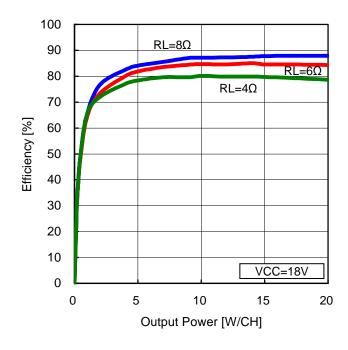

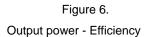

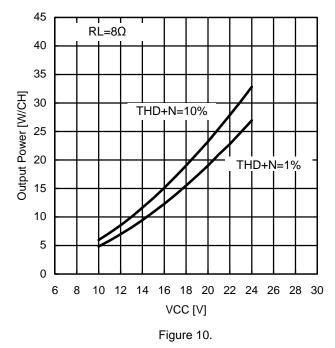

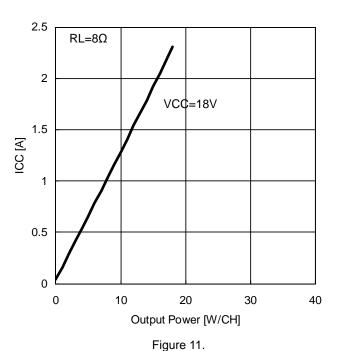

Speaker output(Ta=25°C, VCC=18V, DVDD=3.3V, RSTX=0V/3.3V, MUTEX=0V/3.3V, f=1kHz, DSP: Through, fs=48kHz, MCLK=256fs, Snubber circuit for output terminal: R=5.6Ω, C=680pF)

60 RSTX=H RL=8Ω No Signal MUTEX=H — MUTEX=H — MUTEX=L 0 6 8 10 12 14 16 18 20 22 24 26 28 30 VCC [V]

Figure 4.

Power supply voltage- Current consumption

Figure 5.

Power supply voltage- Current consumption

Figure 7.

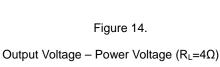

Output power - Current consumption

Speaker output(Ta=25°C, VCC=18V, DVDD=3.3V, RSTX=3.3V, MUTEX=3.3V, f=1kHz, DSP: Through, fs=48kHz, MCLK=256fs, Snubber circuit for output terminal: R=5.6Ω, C=680pF)

Measured by ROHM designed 4 layer board.

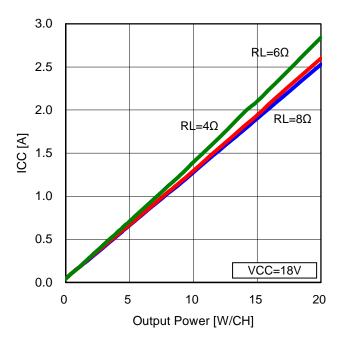

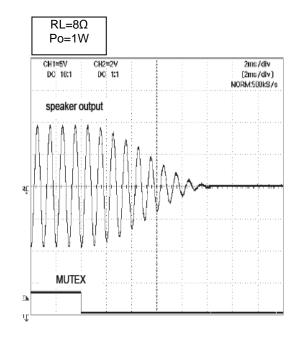

Figure 8.

Waveform at soft start

Figure 9. Waveform at soft mute

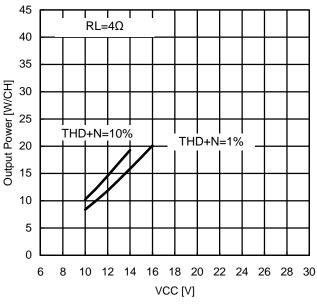

Output voltage - Power voltage (R<sub>L</sub>=8Ω)

Output power - Current consumption ( $R_L=8\Omega$ )

\*Dotted line means internal dissipation is over package power.

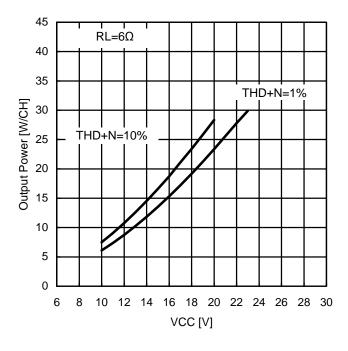

Speaker output(Ta=25°C, VCC=18V, DVDD=3.3V, RSTX=3.3V, MUTEX=3.3V, f=1kHz, DSP: Through, fs=48kHz, MCLK=256fs, Snubber circuit for output terminal: R=5.6Ω, C=680pF)

Measured by ROHM designed 4 layer board.

3.5 RL=6Ω VCC=18V 3 2.5 2 ICC [A] 1.5 1 0.5 0 0 10 20 30 40 Output Power [W/CH]

$\label{eq:Figure 12} Figure \ 12.$  Output voltage - Power voltage (RL=6 $\Omega$ )

$\label{eq:Figure 13} Figure \ 13.$  Output power - Current consumption (RL=6 $\Omega$ )

$\label{eq:Figure 15} Figure \ 15.$  Output power - Current consumption (RL=4 $\Omega$ )

XDotted line means internal dissipation is over package power.

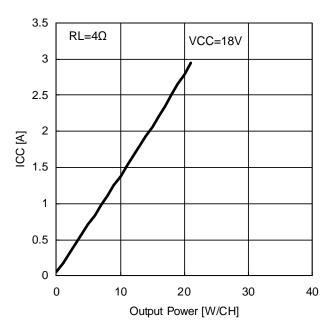

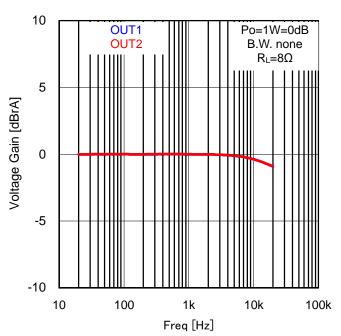

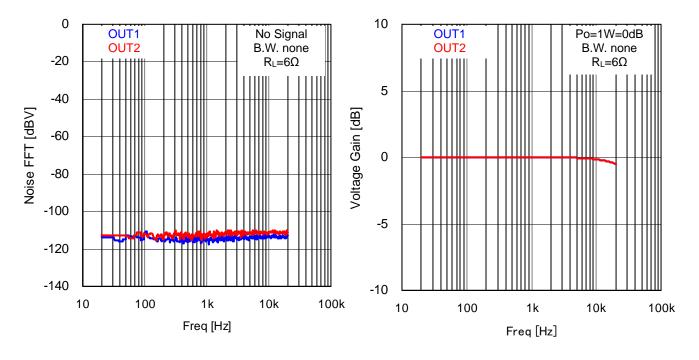

Speaker output( $R_L=8\Omega$ ,  $Ta=25^{\circ}C$ , VCC=18V, DVDD=3.3V, RSTX=3.3V, MUTEX=3.3V, f=1kHz, DSP: Through, fs=48kHz, MCLK=256fs, Snubber circuit for output terminal: R=5.6 $\Omega$ , C=680pF)

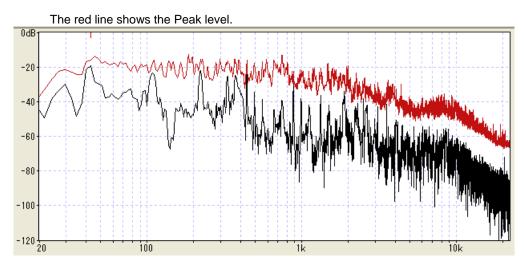

Figure 16.

FFT of output noise voltage

Figure 17.

Frequency – Output power

Figure 18.

Output Power - THD+N

Figure 19. Frequency - THD+N

Speaker output( $R_L=8\Omega$ ,  $Ta=25^{\circ}C$ , VCC=18V, DVDD=3.3V, RSTX=3.3V, MUTEX=3.3V, f=1kHz, DSP: Through, fs=48kHz, MCLK=256fs, Snubber circuit for output terminal: R=5.6 $\Omega$ , C=680pF)

Figure 20.

Frequency - Crosstalk

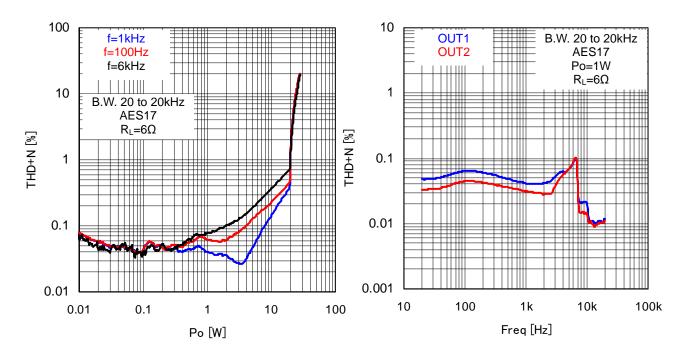

Speaker output( $R_L=6\Omega$ ,  $Ta=25^{\circ}C$ , VCC=18V, DVDD=3.3V, RSTX=3.3V, MUTEX=3.3V, f=1kHz, DSP: Through, fs=48kHz, MCLK=256fs, Snubber circuit for output terminal: R=5.6 $\Omega$ , C=680pF)

Figure 21.

FFT of output noise voltage

Figure 22.

Frequency – Output power

Figure 23.

Output Power - THD+N

Figure 24. Frequency - THD+N

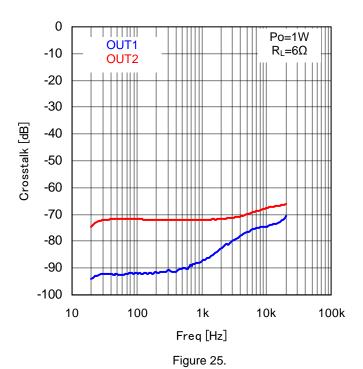

Speaker output R<sub>L</sub>= $6\Omega$ , Ta= $25^{\circ}$ C, VCC=18V, DVDD=3.3V, RSTX=3.3V, MUTEX=3.3V, f=1kHz, DSP: Through, fs=48kHz, MCLK=256fs, Snubber circuit for output terminal: R= $5.6\Omega$ , C=680pF) Measured by ROHM designed 4 layer board.

Frequency - Crosstalk

www.rohm.com © 2013 ROHM Co., Ltd. All rights reserved. TSZ22111 • 15 • 001

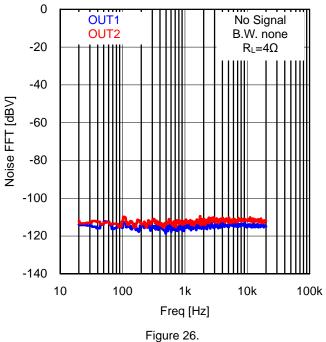

Po=1W=0dB

B.W. none

$R_L=4\Omega$

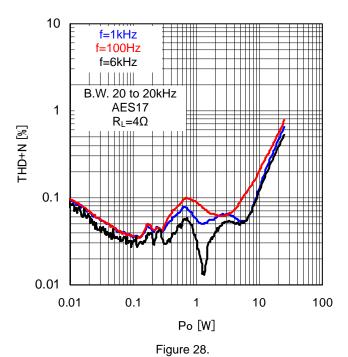

#### **Typical Performance Curves**

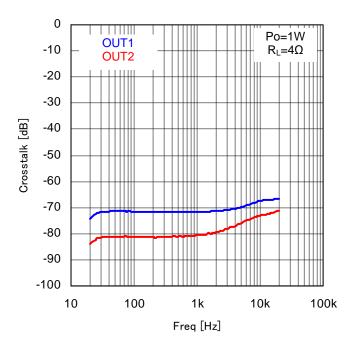

Speaker output( $R_L=4\Omega$ ,  $Ta=25^{\circ}C$ , VCC=18V, DVDD=3.3V, RSTX=3.3V, MUTEX=3.3V, f=1kHz, DSP: Through, fs=48kHz, MCLK=256fs, Snubber circuit for output terminal: R=5.6 $\Omega$ , C=680pF) Measured by ROHM designed 4 layer board.

10

OUT1

OUT2

5 Ooltage Gain [dB] O Ooltage Gain [dB] Ooltage

Figure 27.

Frequency – Output power

FFT of output noise voltage

Output Power - THD+N

10 B.W. 20 to 20kHz OUT1 OUT2 AES17 Po=1W  $R_L=4\Omega$ 1 THD+N [%] 0.1 0.01 0.001 10 100 10k 100k 1k Freq [Hz] Figure 29.

www.rohm.com © 2013 ROHM Co., Ltd. All rights reserved. TSZ22111 • 15 • 001

Frequency - THD+N

Speaker output( $R_L=4\Omega$ ,  $Ta=25^{\circ}C$ , VCC=18V, DVDD=3.3V, RSTX=3.3V, MUTEX=3.3V, f=1kHz, DSP: Through, fs=48kHz, MCLK=256fs, Snubber circuit for output terminal: R=5.6 $\Omega$ , C=680pF)

Figure 30.

Frequency - Crosstalk

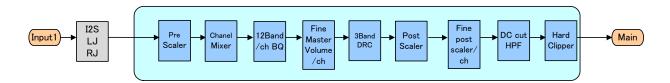

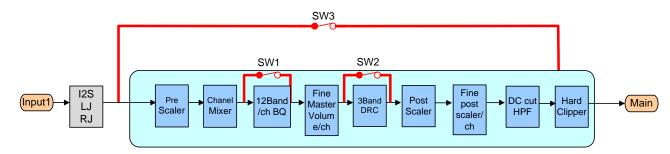

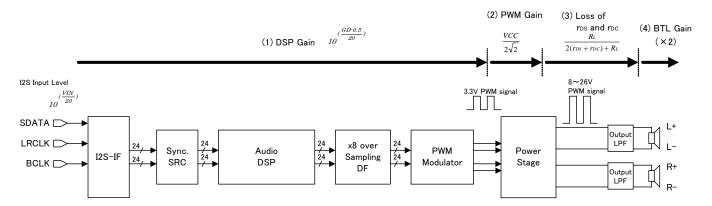

# **Digital Block Functional Overview**

| No. | Function             | Specification                                                                                                     |

|-----|----------------------|-------------------------------------------------------------------------------------------------------------------|

| 1   | Pre-scaler           | Lch / Rch become same set point.                                                                                  |

|     |                      | • +48dB to -79dB (0.5dB step),-∞dB                                                                                |

|     |                      | default 0dB                                                                                                       |

| 2   | Channel Mixer        | <ul><li>Lch &lt;= Mute, Lch(default), Rch, (L+R)/2, L-R</li></ul>                                                 |

|     |                      | <ul> <li>Rch &lt;= Mute, Lch, Rch(default), (L+R)/2, L-R</li> </ul>                                               |

|     |                      | <ul> <li>Lch/Rch are independent phase reversal control available.</li> </ul>                                     |

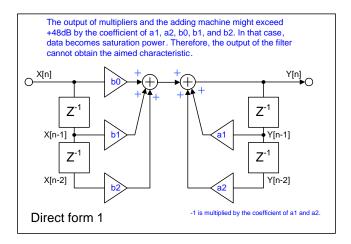

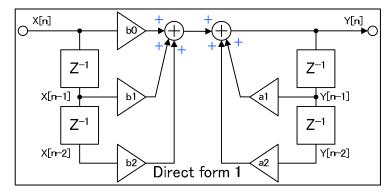

| 3   | 12-Band              | <ul> <li>12-Band Bi-quad type Parametric Equalizer .</li> </ul>                                                   |

|     | Parametric Equalizer | <ul> <li>Only 5 coefficient is required.(b0,b1,b2,a1,a2)</li> </ul>                                               |

|     |                      | The Filter types which can be realized is                                                                         |

|     |                      | Peaking/Low-shelf/High-shelf/Low-pass/High-pass/All-pass/Notch.                                                   |

|     |                      | <ul> <li>Lch/Rch become same set point or independent set. There is soft transition<br/>function.</li> </ul>      |

| 4   | Fine Master Volume   | <ul> <li>Lch / Rch become same set point or independent set.</li> </ul>                                           |

|     |                      | • +24dB to -103dB (0.125dB step),-∞dB                                                                             |

|     |                      | There is soft transition function.                                                                                |

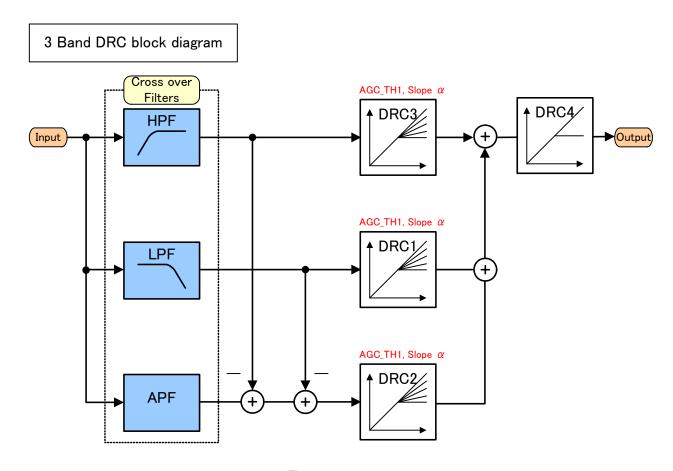

| 5   | 3 Band DRC           | Non clip output is achieved.                                                                                      |

|     |                      | <ul> <li>Lch/Rch becomes the same control.</li> </ul>                                                             |

|     |                      | <ul> <li>Low-pass and a high region become an independent control.</li> </ul>                                     |

|     |                      | Threshold level: +12dB to -32dB (0.5dB step)                                                                      |

|     |                      | The set point of Cross-over frequency : Divide between into 61 from 20 Hz to                                      |

|     |                      | 20 kHz.                                                                                                           |

|     | Post-scaler          | The voice below the set-up detect level is decreased gently.      In the V Park to a series a series to a single. |

| 6   | Post-scaler          | • Lch / Rch become same set point.                                                                                |

|     |                      | • +48dB to -79dB (0.5dB step),-∞dB<br>• default 0dB                                                               |

|     | Fire Deet Ocales     | Lch / Rch become independent set point.                                                                           |

| 7   | Fine Post-Scaler     | · ·                                                                                                               |

|     |                      | • +0.7dB to -0.8dB (0.1dB step)                                                                                   |

| 8   | DC cut HPF           | • 1 <sup>st</sup> order HPF                                                                                       |

|     |                      | • Fc : 1Hz                                                                                                        |

| 9   | Clipper              | Lch / Rch become same set point.                                                                                  |

|     |                      | Clip level: +3dB to -22.5dB (-0.1dB step)                                                                         |

Figure 31. DSP Block diagram

**RSTX** pin, MUTEX pin function

| RSTX    | MUTEX   | DSP block        | Speaker output    |  |  |

|---------|---------|------------------|-------------------|--|--|

| (29pin) | (30pin) | condition        | condition         |  |  |

|         | ı       | Reset ON         | HiZ_Low           |  |  |

| L       | L       | Reset ON         | (Low consumption) |  |  |

| н       | ı       | Normal operation | HiZ_Low           |  |  |

| П       | L       | (Mute ON)        | (Mute ON)         |  |  |

| н       | н       | Normal operation | Normal operation  |  |  |

| П       | П       | (Mute OFF)       | (Mute OFF)        |  |  |

| L       | Н       | Don't use.       |                   |  |  |

<sup>(</sup>Note 1) RSTX is set Low, internal registers are initialized.

# Input Digital sound sampling frequency (fs) explanation

PWM sampling frequency of Speaker output and Soft-mute transition time depends on sampling frequency (fs) of the digital sound input. These transition times are changed by sending select address &h15[1:0].

| Sampling frequency              | Speaker output         | Soft-mute Tr | ansition time |

|---------------------------------|------------------------|--------------|---------------|

| of the Digital sound input (fs) | PWM sampling frequency | Mute ON      | Mute OFF      |

|                                 |                        | 85.4msec     | 10.7msec      |

|                                 |                        | 42.7msec     | 10.7msec      |

| 48kHz                           | 384kHz                 | 21.4msec     | 10.7msec      |

|                                 |                        | 10.7msec     | 10.7msec      |

|                                 |                        | 92.9msec     | 11.7msec      |

| 44.1kHz                         | 352.8kHz               | 46.5msec     | 11.7msec      |

| 44.1KHZ                         | SSZ.OKITZ              | 23.3msec     | 11.7msec      |

|                                 |                        | 11.7msec     | 11.7msec      |

|                                 |                        | 128.1msec    | 16.1msec      |

| 22 14 1-                        | 050111-                | 64.1msec     | 16.1msec      |

| 32 kHz                          | 256kHz                 | 32.1msec     | 16.1msec      |

|                                 |                        | 16.1msec     | 16.1msec      |

<sup>(</sup>Note 2) VCCP1, VCCP2< 2.5V, IC latched by protection circuit and ERROR terminal condition are initialized.

<sup>(</sup>Note 3) If DVDD is under 3V, RSTX is set Low once for 10ms(min), and set High again. Then DSP is needed to set parameter again.

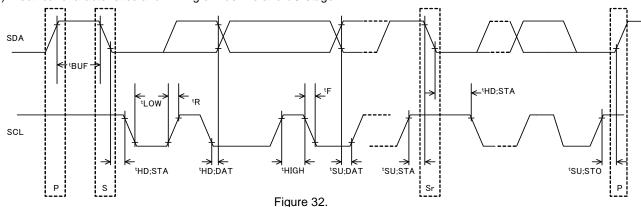

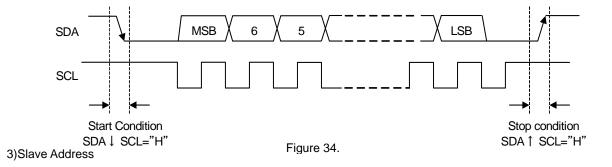

#### 2 wire Bus control signal specification

1) Electrical characteristics and Timing of Bus line and I/O stage

SDA and SCL bus line characteristics(Unless otherwise specified Ta=25°C, VDD=3.3V)

|    | Devenueter                                                                                          | Comple of | High spee             | ed mode | 1.1  |

|----|-----------------------------------------------------------------------------------------------------|-----------|-----------------------|---------|------|

|    | Parameter                                                                                           | Symbol    | Min.                  | Max.    | Unit |

| 1  | SCL clock frequency                                                                                 | fSCL      | 0                     | 400     | kHz  |

| 2  | Bus free time between 「Stop」 condition and 「Start」 condition                                        | tBUF      | 1.3                   | _       | μS   |

| 3  | Hold-time of (sending again) Start condition. After this period the first clock pulse is generated. | tHD;STA   | 0.6                   | _       | μS   |

| 4  | SCL clock's LOW state Hold-time                                                                     | tLOW      | 1.3                   | _       | μS   |

| 5  | SCL clock's HIGH state Hold-time                                                                    | tHIGH     | 0.6                   | _       | μS   |

| 6  | Set-up time of sending again 「Start」 condition                                                      | tSU;STA   | 0.6                   | _       | μS   |

| 7  | Data hold time                                                                                      | tHD;DAT   | 0 <sup>(Note 1)</sup> | _       | μS   |

| 8  | Data set-up time (Note 2)                                                                           | tSU;DAT   | 500/250/150           | _       | ns   |

| 9  | Rise-time of SDA and SCL signal                                                                     | tR        | 20+0.1Cb              | 300     | ns   |

| 10 | Fall-time of SDA and SCL signal                                                                     | tF        | 20+0.1Cb              | 300     | ns   |

| 11 | Set-up time of 「Stop」 condition                                                                     | tSU;STO   | 0.6                   | _       | μS   |

| 12 | Capacitive load of each bus line                                                                    | Cb        | _                     | 400     | pF   |

The above-mentioned numerical values are all the values corresponding to VIH min and the VIL max level.

(Note 1) To exceed an undefined area on the fall-edge of SCL (VIH min of the SCL signal), the transmitting set should internally offer the holding time of 300ns or more for the SDA signal.

(Note 2) The data set-up time is different according to the setting of SYS\_CLK.

When SYS\_CLK=128fs it is 500ns, for SYS\_CLK=256fs it is 250ns, for SYS\_CLK=512fs it will be 150ns.

Initial setting is SYS\_CLK=256fs.

(Note 3) SCL and SDA pin is not corresponding to threshold tolerance of 5V.

Please use it within 4.5V of the absolute maximum rating.

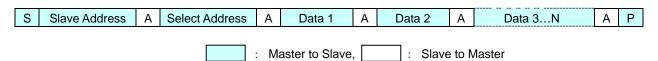

#### 2)Command interface

2 wire Bus control is used for command interface between host CPU. It not only writes but also it is possible to read it excluding a part of register. In addition to "Slave Address", set and write 1 byte of "Select Address" to read out the data. 2 wire bus Slave mode format is illustrated below.

| MSB LS |             | LSB |   | MSB      | LSB     |   | MSB  | LSB |   |   |

|--------|-------------|-----|---|----------|---------|---|------|-----|---|---|

| S      | Slave Addre | SS  | Α | Select A | Address | Α | Data |     | Α | Р |

Figure 33.

S: Start Condition

Slave Address: The data of eight bits in total is sent putting up bit of Read mode (H) or Write mode (L) after slave address (7bit) set with the terminal ADDR. (MSB first)

A: The acknowledge bit adds to data that the acknowledge is sent and received in each byte.

When data is correctly sent and received, "L" is sent and received.

There was no acknowledgement for "H".

Select Address: The select address in one byte is used.(MSB first)

Data: Data byte is sent and received data(MSB first)

P: Stop Condition

· While ADDR pin is"L"

| MSB |    |    |    |    |    |    |    |     |  |

|-----|----|----|----|----|----|----|----|-----|--|

|     | A6 | A5 | A4 | А3 | A2 | A1 | A0 | R/W |  |

|     | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 1/0 |  |

· While ADDR pin is"H"

| MSB |    |    |    |    |    |    |     |  |  |

|-----|----|----|----|----|----|----|-----|--|--|

| A6  | A5 | A4 | A3 | A2 | A1 | A0 | R/W |  |  |

| 1   | 0  | 0  | 0  | 0  | 0  | 1  | 1/0 |  |  |

4) Writing of dataBasic format

Figure 35.

| S | Slave Address | Α | Select Address | Α | Data | Α | Р |

|---|---------------|---|----------------|---|------|---|---|

: Master to Slave, : Slave to Master

· Auto-increment format

# 5)Reading of data

First of all, the address ( 20h in the example) for reading is written in the register of the D0h address at the time of reading. In the following stream, data is read after the slave address. Please do not return the acknowledge when you end the reception.

Figure 36.

Figure 37.

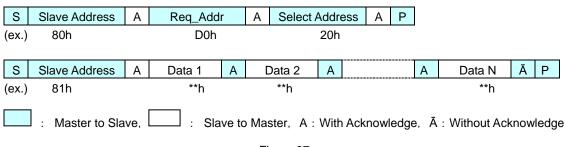

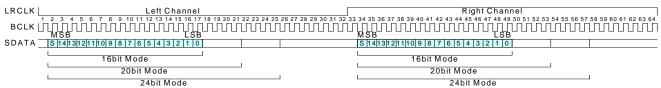

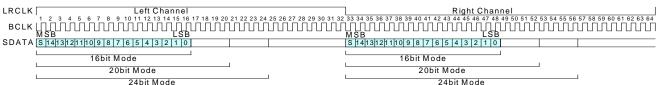

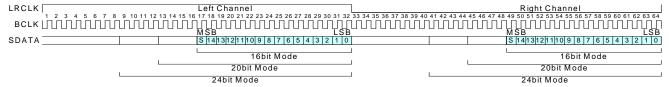

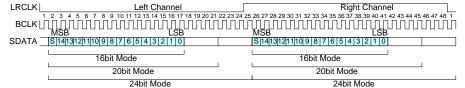

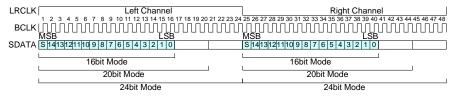

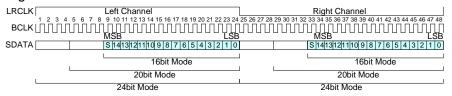

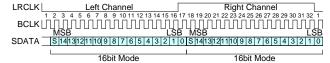

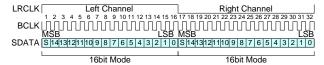

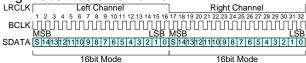

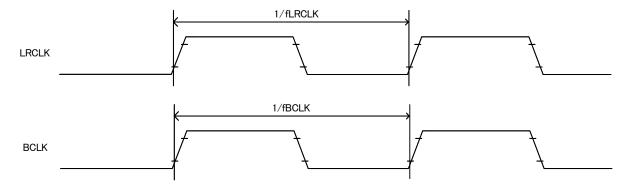

## Format of digital audio input

· LRCLK: It is L/R clock input signal.

It corresponds to 32kHz/44.1kHz/48kHz with those clock (fs) that are same to the sampling frequency (fs) . The audio data of a left channel and a right channel for one sample is input to this section.

BCLK: It is Bit Clock input signal.

It is used for the latch of data in every one bit by sampling frequency's 48 times frequency (48fs) or 64 times sampling frequency (64fs). However if the 48fs being selected, the input will be Right-justified data format and held static.

SDATA: It is Data input signal.

It is amplitude data. The data length is different according to the resolution of the input digital data. It corresponds to 16/20/24 bit.

The digital input has I2S, Left-justified and Right-justified formats.

The figure below shows the timing chart of each transmission mode.

SDATAO: Audio data after DSP processing.

Output audio data after DSP processing.

This output synchronous to inputted LRCK and BCLK.

Bit clock 64fs

#### I<sup>2</sup>S 64fs Format

#### Left-Justified 64fs Format

## Right-Justified 64fs Format

Figure 38.

Bit clock 48fs

# I<sup>2</sup>S 48fs Format

# Left-Justified 48fs Format

## Right-Justified 48fs Format

Figure 39.

Bit clock 32fs

## I<sup>2</sup>S 32fs Format

## Left-Justified 32fs Format

Right-Justified 32fs Format

Figure 40.

# Format setting for Digital Audio Interface

Please set Bit clock fs , Data strength and Format by transmitting command according to inputted Digital Serial Audio signal.

SDATAO output data bit width is able to be set independently.

#### Bit clock

## Default = 0

| Select Address | Value | Explanation of operation |

|----------------|-------|--------------------------|

| &h03[ 5:4 ]    | 0     | 64fs                     |

|                | 1     | 48fs                     |

|                | 2     | 32fs                     |

## **Data Format**

## Default = 0

| Select Address | Value | Explanation of operation |  |

|----------------|-------|--------------------------|--|

| &h03[ 3:2 ]    | 0     | IIS format               |  |

|                | 1     | Left-justified format    |  |

|                | 2     | Right-justified format   |  |

# Data width

## Default = 2

| Select Address | Value | Explanation of operation |

|----------------|-------|--------------------------|

| &h03[ 1:0 ]    | 0     | 16 bit                   |

|                | 1     | 20 bit                   |

|                | 2     | 24 bit                   |

# **SDATAO** output Data strength

#### Default = 2

| Select Address | Value | Explanation of operation |

|----------------|-------|--------------------------|

| &h78[ 1:0 ]    | 0     | 16 bit                   |

|                | 1     | 20 bit                   |

|                | 2     | 24 bit                   |

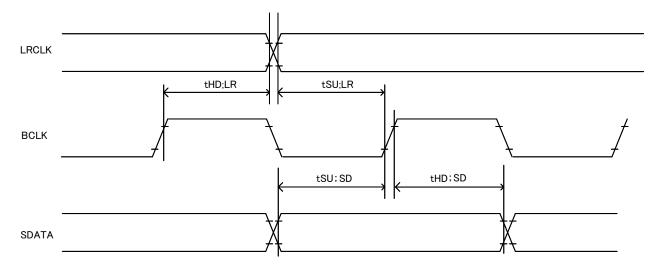

# **Audio Interface format and timing**

Recommended timing and operating conditions (BCLK, LRCLK, SDATA)

Figure 41. Clock timing

Figure 42. Audio Interface timing

| No.  | Parameter                             | Symbol       | Li    | Unit  |       |

|------|---------------------------------------|--------------|-------|-------|-------|

| INO. | Farameter                             | ietei Symbol |       | Max.  | Offic |

| 1    | LRCLK frequency                       | fLRCLK       | 32    | 48    | kHz   |

| 2    | BCLK frequency                        | fBCLK        | 2.048 | 3.072 | MHz   |

| 3    | Setup time, LRCLK <sup>(Note 1)</sup> | tSU;LR       | 20    | -     | ns    |

| 4    | Hold time, LRCLK <sup>(Note 1)</sup>  | tHD;LR       | 20    | 1     | ns    |

| 5    | Setup time, SDATA                     | tSU;SD       | 20    | _     | ns    |

| 6    | Hold time, SDATA                      | tHD;SD       | 20    | -     | ns    |

| 7    | LRCLK, DUTY                           | dLRCLK       | 40    | 60    | %     |

| 8    | BCLK, DUTY                            | dBCLK        | 40    | 60    | %     |

(Note 1) This regulation is to keep rising edge of LRCK and rising edge of BCLK from overlapping.

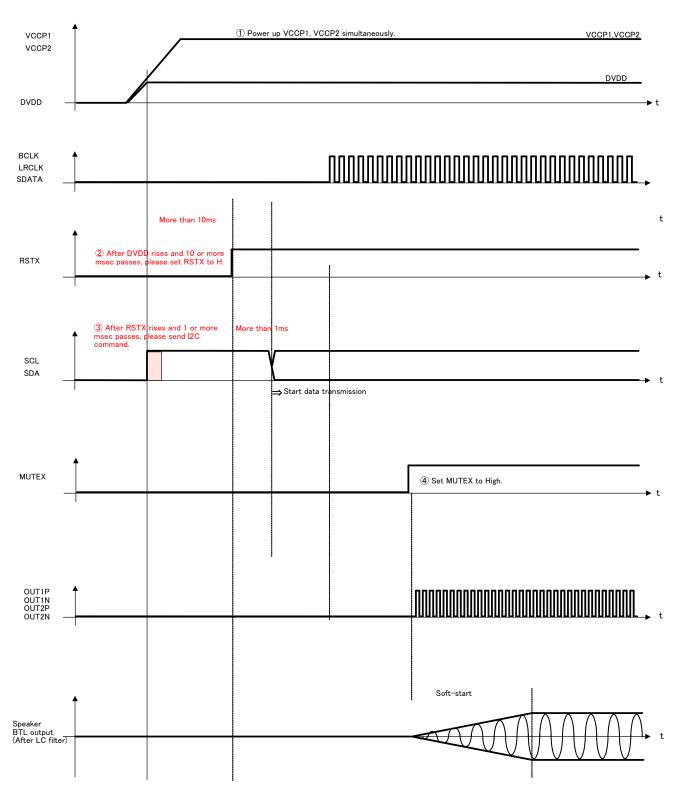

# Power supply start-up sequence

%To avoid POP noise or canceling error protection of IC, please set RSTX is L⇒H before MUTEX is L⇒H regularly.

Figure 43.

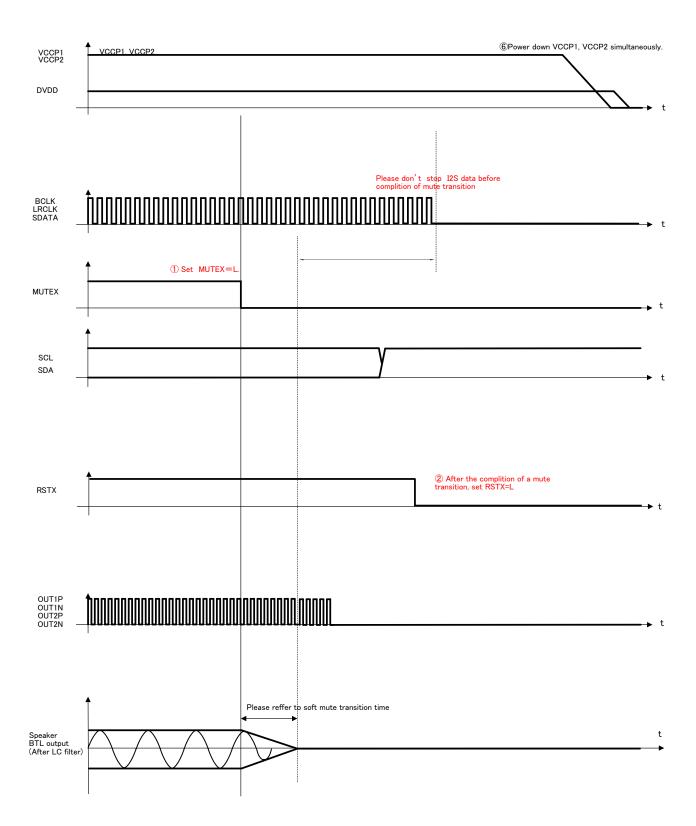

# Power supply shut-down sequence

%To avoid POP noise or canceling error protection of IC, please set MUTEX is H⇒L and keep mute transition time before RSTX is H⇒L regularly.

Figure 44.

# About the protection function

| Protection function             |                                              | Detecting & Releasing condition                                                                                                                                                                                                 | Speaker<br>PWM output       | ERROR<br>output |

|---------------------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----------------|

| Output short protection         | Detecting condition                          | Detecting current = 7.2A (TYP.)                                                                                                                                                                                                 | HiZ_Low<br>(Latch) (Note 2) | L<br>(Latch)    |

| DC voltage protection           | Detecting condition                          | PWM output Duty=0% or 100% for 12µsec(TYP)and over                                                                                                                                                                              | HiZ_Low<br>(Latch) (Note 2) | L<br>(Latch)    |

| High                            | Detecting condition                          | Chip temperature to be above 150°C (TYP.)                                                                                                                                                                                       | HiZ_Low                     |                 |

| temperature Releasing condition |                                              | Chip temperature to be below 120°C (TYP.)                                                                                                                                                                                       | Normal operation            | L               |

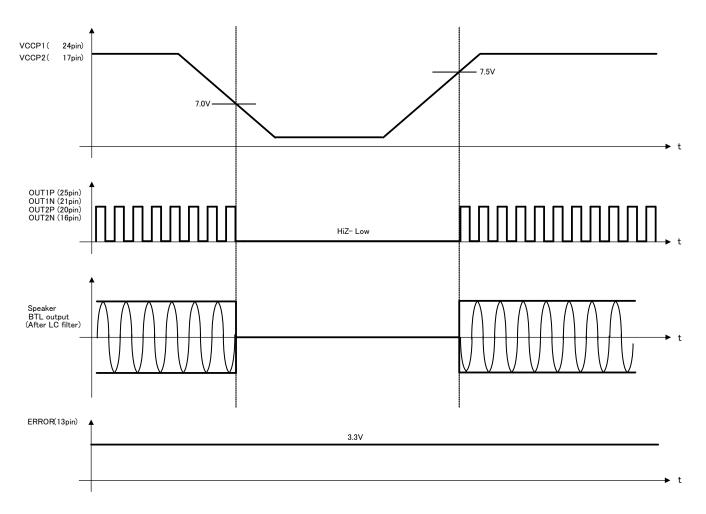

| Under voltage                   | Detecting condition                          | Power supply voltage to be below 7.0V (TYP.)                                                                                                                                                                                    | HiZ_Low                     | н               |

| protection Releasing condition  | Power supply voltage to be above 7.5V (TYP.) | Normal operation                                                                                                                                                                                                                | П                           |                 |

| Clock stop                      | Detecting condition                          | BCLK signal have stopped among constant period. LRCLK signal have stopped among constant period. BCLK frequency is under constant value. BCLK frequency is over constant value. Please refer to chapter 6 about constant value. | HiZ_Low                     | Н               |

| Releasing condition             |                                              | LRCLK signal haven't stopped among constant period and BCLK continues 30 or more msec of condition within constant frequency.                                                                                                   | Normal operation            |                 |

<sup>(</sup>Note 1) The ERROR pin is Nch open-drain output.

<sup>(</sup>Note 2) Once an IC is latched, the circuit is not released automatically even after an abnormal status is removed.

The following procedures ① or ② is available for recovery.

①After MUTEX pin is made Low once over the soft mute transition time, MUTEX pin is returned to High again.

②Turning on the power supply again (VCCP1, VCCP2<2.5V, 10ms(min)).

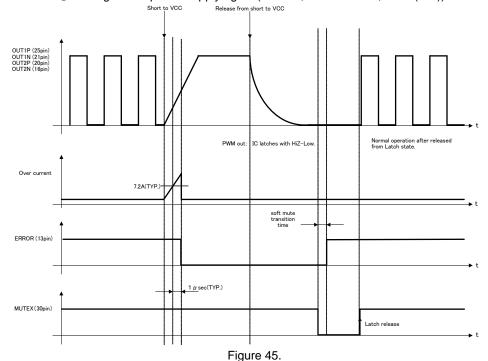

1) Output short protection (Short to the power supply)

This IC has the output short protection circuit that stops the PWM output when the PWM output is short-circuited to the power supply due to abnormality.

Detecting condition - It will detect when MUTEX pin is set High and the current that flows in the PWM output pin becomes 7.2A(TYP.) or more. The PWM output instantaneously enters the state of HiZ-Low if detected, and IC does the latch.

Releasing method - ①After MUTEX pin is set Low once over the soft mute transition time(see page 15/80), MUTEX pin is returned to High again.

2 Turning on the power supply again (VCCP1, VCCP2<2.5V, 10ms(min)).

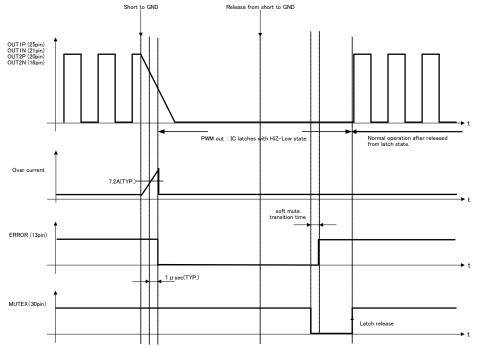

2) Output short protection (Short to GND)

This IC has the output short protection circuit that stops the PWM output when the PWM output is short-circuited to GND due to abnormality.

Detecting condition - It will detect when MUTEX pin is set High and the current that flows in the PWM output terminal becomes 7.2A(TYP.) or more. The PWM output instantaneously enters the state of HiZ-Low if detected, and IC does the latch.

Releasing method – ①After MUTEX pin is set Low once over the soft mute transition time(see page 15/76), MUTEX pin is returned to High again.

②Turning on the power supply again (VCCP1, VCCP2<2.5V, 10ms(min)).

Figure 46.

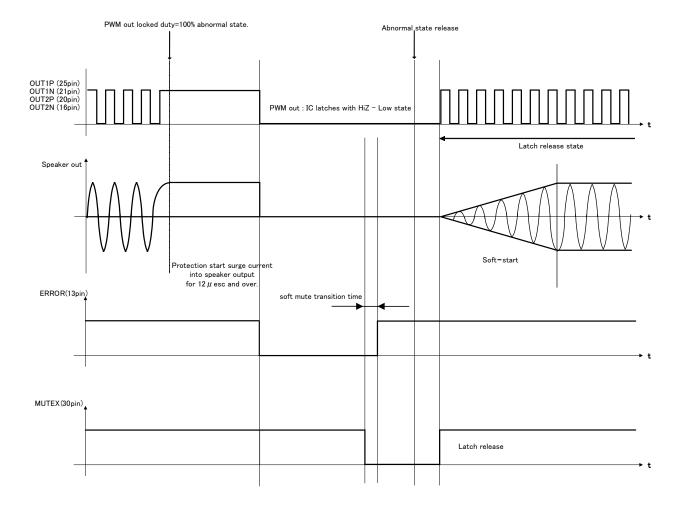

3) DC voltage protection in the speaker

When the DC voltage in the speaker is impressed due to abnormality, this IC has the protection circuit where the speaker is defended from destruction.

Detecting condition - It will detect when MUTEX pin is set High and PWM output Duty=0% or 100% over 12  $\mu$  sec.(fs=48kHz) Once detected, The PWM output instantaneously enters the state of HiZ-Low, and IC does the latch.

Releasing method – ①After MUTEX pin is set Low once over the soft mute transition time(see page 15/76), MUTEX pin is returned to High again.

2)Turning on the power supply again (VCCP1, VCCP2<2.5V, 10ms(min)).

Figure 47.

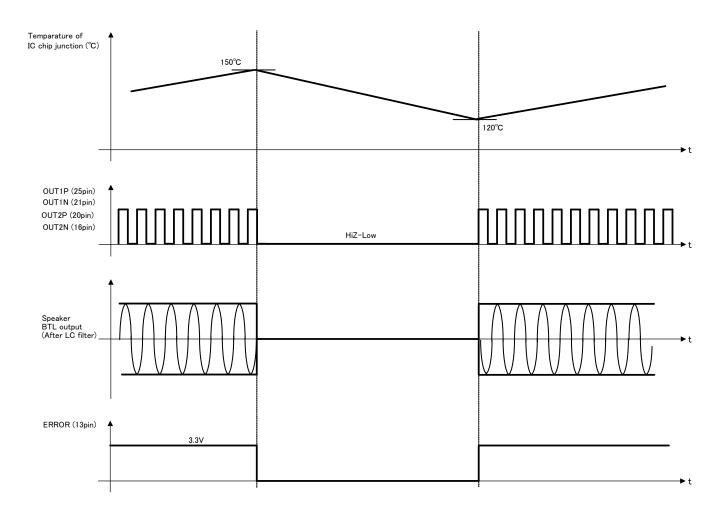

#### 4) High temperature protection

This IC has the high temperature protection circuit that prevents thermal reckless driving under an abnormal state for the temperature of the chip to exceed Tjmax=150°C.

Detecting condition - It will detect when MUTEX pin is set High and the temperature of the chip becomes 150°C(TYP.) or more. The speaker output is muted when detected.

Releasing condition - It will release when MUTEX pin is set High and the temperature of the chip becomes 120°C (TYP.) or less. The speaker output is outputted when released.

Figure 48.

## 5) Under voltage protection

This IC has the under voltage protection circuit that make speaker output mute once detecting extreme drop of the power supply voltage.

Detecting condition – It will detect when MUTEX pin is set High and the power supply voltage becomes lower than 7.0V. The speaker output is muted when detected.

Releasing condition – It will release when MUTEX pin is set High and the power supply voltage becomes more than 7.5V. The speaker output is outputted when released.

Figure 49.

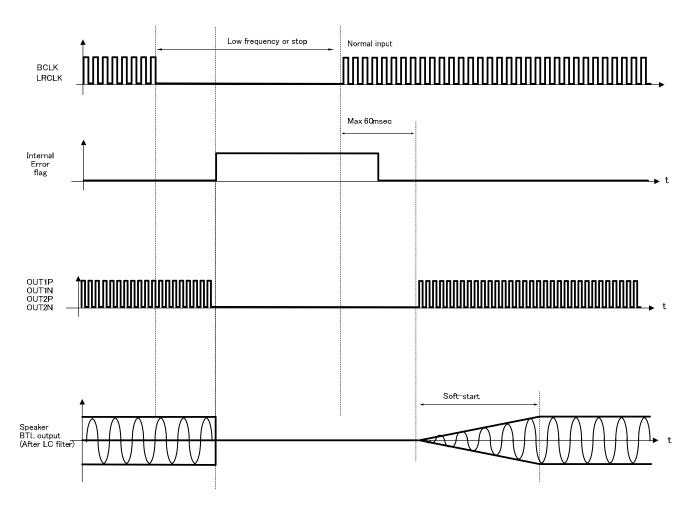

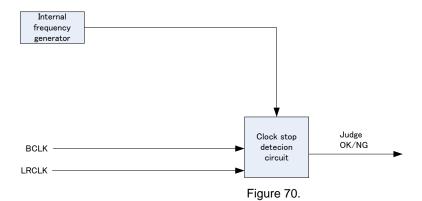

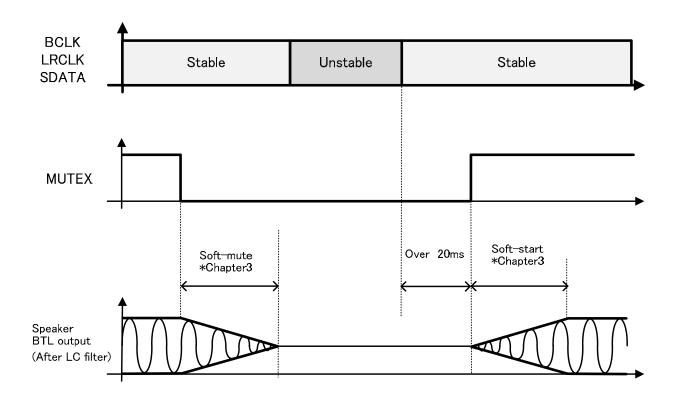

#### 6) Clock stop protection

This IC has the clock stop protection circuits that make the speaker output mute when the BCLK and LRCLK frequency of the digital sound input are decreased or low frequency.

Detecting condition - BCLK frequency is low or stop, LRCLK frequency is stop. The speaker output is muted. Releasing condition - BCLK and LRCK are OK over 60msec (max).

Figure 50.

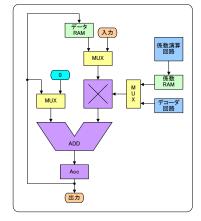

# **Functional descriptions of DSP Block**

1. Digital Sound Processing(DSP)

Coefficient RAM:

The digital sound processing (DSP) part of BM28720 is composed of the special hard ware which is the optimal for FPD-TV, the Mini/Micro Compo. BM28720MUV does the following processing using this special DSP.

Pre-scaler, Channel mixer, 12 Band P-EQ, Fine Master Volume, 3 Band DRC, Fine Post-scaler, DC cutHPF, Hard Clipper

The outline and signal flow of the DSP part

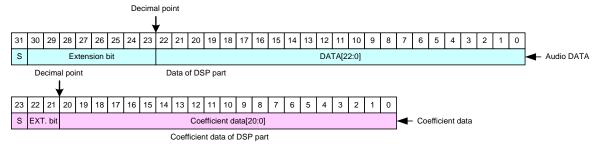

Data width: 32 bit (DATA RAM)

Machine cycle: 20.3ns (1024fs, fs=48kHz)

512 × 24 bit

Multiplier:  $32 \times 24 \rightarrow 56 \text{ bit}$ Adder:  $56+56 \rightarrow 56 \text{ bit}$ Data RAM:  $512 \times 32 \text{ bit}$

Sampling frequency: fs=32k,44.1k,48kHz

Figure 51.

The digital signal from 16 bits to 24 bits is inputted to the DSP but extends 8bit(+48dB) as the overflow margin to the upper side. When doing the processing which exceeds this range, it processes a clip in the DSP. Incidentally, in case of the 2nd IIR-type (BQ) filter which is often used generally as the digital filter, because it consumes a lot of overflow margins, the output of the multiplier and the adder inside needs note.

Figure 52.

The management of audio data is as follows by each block.

Figure 53.

#### 1-1. Bypass

It passes in the each function of the DSP by the command. Because it left the set value of the each function can be passed in, it is possible to do the confirmation of ON/OFF of the sound effect easily.

The effect which is possible about the bypass, 1) 10Band BQ, 2) 10Band DRC and the whole DSP can be passed.

Figure 54.

| Default = | = 00h |

|-----------|-------|

|-----------|-------|

| Select Address | bit | Explanation of operation (*) '1' by | passes each function. |

|----------------|-----|-------------------------------------|-----------------------|

|                | 2   | Bypass of 12Band BQ (SW1)           | 0:Normal 1:Bypass     |

| &h02 [2:0]     | 1   | Bypass of 3band DRC (SW2)           | 0:Normal 1:Bypass     |

|                | 0   | Bypass of DSP (SW3)                 | 0:Normal 1:Bypass     |

#### 1-2. Pre-scaler

To overflow when the level sometimes is full scale entry in case of the digital signal which is inputted to the sound DSP and does surround and equalizer processing, it adjusts an entry gain with Pre-scaler. The adjustable-range can be set from +48 dB to -79 dB with the 0.5-dB step. (Lch/Rch concurrency control) Pre-scaler doesn't have a soft transfer feature.

Default = 60h

| Select Address | Explanation   | of operation |

|----------------|---------------|--------------|

| &h16 [ 7:0 ]   | Command Value | Gain         |

|                | 00            | +48dB        |

|                | 01            | +47.5dB      |

|                | :             | :            |

|                | 60            | 0dB          |

|                | 61            | -0.5dB       |

|                | 62            | -1dB         |

|                | :             | :            |

|                | FE            | -79dB        |

|                | FF            | -∞           |

|                | <u> </u>      |              |

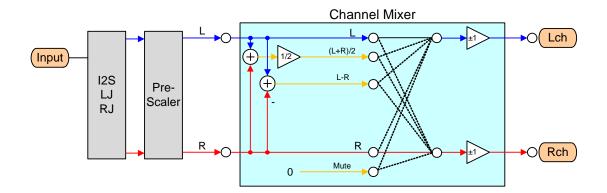

# 1-3. Channel setup with a phase inversion function (Channel Mixer 1)

It sets a mixing in the sound on the left channel and the right channel of the digital signal which was inputted to the DSP. It makes a stereo signal a monaural here. Also, the phase-inversion, the mute on each channel can be set.

Figure 55.

DSP Input: The data inputted into Lch of DSP is inverted.

Default = 0

| Select Address | Value | Explanation of operation |  |

|----------------|-------|--------------------------|--|

| &h17[7]        | 0     | Normal                   |  |

|                | 1     | Invert                   |  |

DSP Input: The data inputted into Lch of DSP is mixed.

Default = 1

| Select Address | Value | Explanation of operation |  |

|----------------|-------|--------------------------|--|

| &h17 [ 6:4 ]   | 0     | Mute                     |  |

|                | 1     | Lch data input           |  |

|                | 2     | Rch data input           |  |

|                | 3     | (Lch + Rch) / 2          |  |

|                | 4     | Lch-Rch                  |  |

DSP input: The data inputted into Rch of DSP is inverted.

Default = 0

| Select Address | Value | Explanation of operation |

|----------------|-------|--------------------------|

| &h17 [3]       | 0     | Normal                   |

|                | 1     | Invert                   |

DSP Input: The data inputted into Rch of DSP is mixed.

Default = 2

| Select Address | Value | Explanation of operation |

|----------------|-------|--------------------------|

| &h17 [ 2:0 ]   | 0     | Mute                     |

|                | 1     | Lch data input           |

|                | 2     | Rch data input           |

|                | 3     | (Lch + Rch) / 2          |

|                | 4     | Lch-Rch                  |

#### 1-4. Parametric Equalizer

In this IC, the following block has the feature of the parametric equalizer.

12Band BQ, Crossover filter of 3Band DRC block and BQ of the smooth transition.

The shape is used peaking filter, low shelf filter, high shelf filter, lowpass filter, highpass filter, notch filter and all path filters. Setting the coefficient of the digital filter in the IC by transmit to the coefficient RAM via command. 12Band BQ have the soft transfer feature. Incidentally, the detailed order of the parameter setting refers to the following PEQ setting method.

#### Select of PEQ independence or synchronous setting

#### Default = 0h

| Select Address | Value | Explanation of operation |

|----------------|-------|--------------------------|

| &h60 [ 4 ]*    | 0     | L/R common setting       |

| Since [ 1 ]    | 1     | L/R independence setting |

<sup>\*&</sup>amp;h60[4] setting note.

Please re-set all the parametric equalizers when you change the setting of &h60[4].

The parametric equalizers for which the re-setting is necessary are 18 (BQ1-12, DRC1,DRC2,and DRC3).

#### Select of smooth transition

#### Default = 0h

| Select Address | Value | Explanation of operation  |

|----------------|-------|---------------------------|

| &h53 [ 6 ]     | 0     | Use smooth transition     |

| S55 [ 5 ]      | 1     | Not use smooth transition |

#### Select of PEQ soft transition independent setting(This needs to set if &h60[4] is set to 1.)

#### Default = 0h

| Select Address | Value | Explanation of operation |

|----------------|-------|--------------------------|

| &h51 [ 7 ]*    | 0     | Transmit to Lch          |

| S [ 1 ]        | 1     | Transmit to Rch          |

#### Select of PEQ soft transition Band

## Default = 0h

| Select Address | E       | Explanation o | f operation |            |

|----------------|---------|---------------|-------------|------------|

| &h51 [ 4:0 ]*  |         |               |             |            |

| Q1131 [ 4.0 ]  | Command | PEQ           | Command     | PEQ        |

|                | 00      | 12BAND(1)     | 0A          | 12BAND(11) |

|                | 01      | 12BAND(2)     | 0B          | 12BAND(12) |

|                | 02      | 12BAND(3)     |             |            |

|                | 03      | 12BAND(4)     |             |            |

|                | 04      | 12BAND(5)     |             |            |

|                | 05      | 12BAND(6)     |             |            |

|                | 06      | 12BAND(7)     |             |            |

|                | 07      | 12BAND(8)     |             |            |

|                | 08      | 12BAND(9)     |             |            |

|                | 09      | 12BAND(10)    |             |            |

|                |         |               |             |            |

# Setting of smooth transition time

# Default = 3h

| Select Address | Value | Explanation of operation |

|----------------|-------|--------------------------|

| &h53 [ 3:2 ]   | 0     | 2.7ms                    |

|                | 1     | 5.3ms                    |

|                | 2     | 10.7ms                   |

|                | 3     | 21.3ms                   |

# Setting of smooth transition wait time

## Default = 0h

| Select Address | Value | Explanation of operation |

|----------------|-------|--------------------------|

| &h53 [ 1:0 ]   | 0     | 2.7ms                    |

|                | 1     | 5.3ms                    |

|                | 2     | 10.7ms                   |

|                | 3     | 21.3ms                   |

# Transfer start setting to coefficient RAM

## Default = 0

| Select Address | Value | Explanation of operation                                                                   |

|----------------|-------|--------------------------------------------------------------------------------------------|

| &h57 [ 0 ]     | 0     | Transfer stop                                                                              |

|                | 1     | Transfer start (After transferring is completed, it becomes 0 by the automatic operation.) |

# Setting of smooth transition start

#### Default = 0

| Select Address | Value | Explanation of operation                                                                                           |

|----------------|-------|--------------------------------------------------------------------------------------------------------------------|

| &h58 [ 0 ]     | 0     | Stop the smooth transition operation                                                                               |

|                | 1     | Start the smooth transition operation (After the transition is completed, it becomes 0 by the automatic operation) |

<sup>\*</sup> This register cannot read-out.

# Read-out smooth transition status

| Select Address | Explanation of operation                |

|----------------|-----------------------------------------|

| &h59 [ 0 ]     | "1" is read while software is changing. |

|                | "0" is read usually.                    |

$[Attention] \ The \ data \ of \ coefficient \ RAM \ can \ be \ read. \quad Set \ values \ such \ as \ F, \ Q, \ and \ Gain \ cannot \ be \ read.$

## 1-5. Volume

Volume is from+24dB to -103dB, and can be selected by the step of 0.125dB. And it is possible to be setting of  $-\infty$ dB, too. At the time of switching of Volume, smooth transition is performed. Soft transition duration is optional with the command. L/R synchronous or L/R independent can be selected by &h10[7].

It becomes the following formula at the transition from AdB to BdB. C is smooth transition duration selected by &h15[7:6] command.

Transition time =

$$|(10^{\frac{A}{20}} - 10^{\frac{B}{20}})^* \text{ C ms}|$$

## Setting of soft transition time

#### Default = 0

| Select Address | Value | Explanation of operation |

|----------------|-------|--------------------------|

| &h15 [ 7:6 ]   | 0     | 21.3ms                   |

|                | 1     | 42.7ms                   |

|                | 2     | 85.3ms                   |

## Lch/common volume setting

## Default = FFh

| Select Address | Explanation | of operati |

|----------------|-------------|------------|

| &h11 [ 7:0 ]   | Command     | Gain       |

| G.111 [ 7.0 ]  | 00          | +24dB      |

|                | 01          | +23.5dB    |

|                | :           | :          |

|                | 30          | 0dB        |

|                | 31          | -0.5dB     |

|                | 32          | -1dB       |

|                | :           | :          |

|                | FE          | -103dB     |

|                | FF          | -∞         |

Setting of fine volume

This command becomes effective by sending the following command after setting.

When using this command, it is possible to set a volume in 0.125dB carving.

When L/R synchronous volume setting, &11[7:0] is enable.

When L/R independent volume setting, &11[7:0] is the volume setting of Lch.

#### Lch/common fine volume setting

#### Default = 0h

| Select Address | Value | Explanation of operation |

|----------------|-------|--------------------------|

| &h10 [ 1:0 ]   | 0     | 0dB                      |

|                | 1     | -0.125dB                 |

|                | 2     | -0.25dB                  |

|                | 3     | -0.375dB                 |

#### [Note1]

It is possible to use with the 0.5-dB step in changing only &h11[7:0] when &h10[1:0]=0.

The Lch/Rch independent volume setting and the synchronous volume setting can be selected by &h10[7] command. When Lch/Rch independent volume set, the volume setting of Lch is the setting of &h10[1:0] and &h11, and the volume setting of Rch is the settings of &h10[5:4] and &h13.

#### Setting of Lch/Rch independent volume

#### Default = 0

| Select Address | Value | Explanation of operation           |

|----------------|-------|------------------------------------|

| &h10[7]        | 0     | Lch/Rch common volume setting      |

|                | 1     | Lch/Rch independent volume setting |

Setting of volume (Setting of Rch volume, It is enable only to set an independent volume.)

Default = FFh

| Select Address | Explanation o | of operation |

|----------------|---------------|--------------|

| &h12 [ 7:0 ]   | Command       | Gain         |

|                | 00            | +24dB        |

|                | 01            | +23.5dB      |

|                | :             | :            |

|                | 30            | 0dB          |

|                | 31            | -0.5dB       |

|                | 32            | -1dB         |

|                | :             | ÷            |

|                | FE            | -103dB       |

|                | FF            | -∞           |

#### Setting of fine volume

This command becomes effective by sending the following command after setting.

When using this command, it is possible to set a volume in 0.125dB carving.

Setting of fine volume (Setting of Rch fine volume, It is enable only to set an independent volume.)

# Default = 0h

| Select Address | Value | Explanation of operation |

|----------------|-------|--------------------------|

| &h10 [ 5:4 ]   | 0     | 0dB                      |

|                | 1     | -0.125dB                 |

|                | 2     | -0.25dB                  |

|                | 3     | -0.375dB                 |

#### [Note2]

It is possible to use with the 0.5-dB step in changing only &h13[7:0] when &h10[5:4]=0.

#### [Note3]

It is possible to use with the 0.125-dB step in setting both &h10[1:0] and &h11[7:0].

In case of &h10[1:0]=0, it becomes the set value of &h11[7:0].

In case of &h10[1:0]=1, it becomes the -0.125dB set value of &h11[7:0].

In case of &h10[1:0]=2, it becomes the -0.25dB set value of &h11[7:0].

In case of &h10[1:0]=3, it becomes the -0.375dB set value of &h11[7:0].

Because it is fixed by the transfer of &h11 in any case, the soft transfer can be beforehand begun in the set value for the direct following of the purpose in setting &h11 after setting in &h10.

Figure 56.

#### 1-6. 3 band DRC

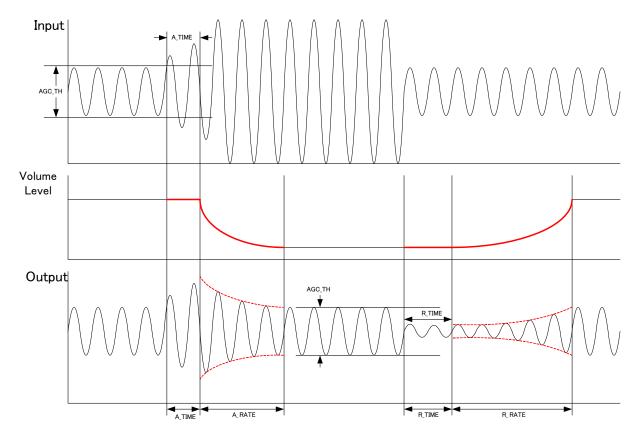

This DRC is used in order to prevent speaker protection and the clip output of a large audio signal. There are three kinds of DRC (DRC1, DRC2, and DRC3), and no clip can be output to each three BAND. DRC1, DRC2 and DRC3 can set up two threshold value levels. Moreover, it is possible to also change slope.

Figure 57.

#### DRC transition figure

Figure 58.

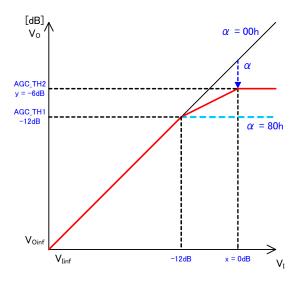

# DRC input-and-output gain characteristics

Figure 59.

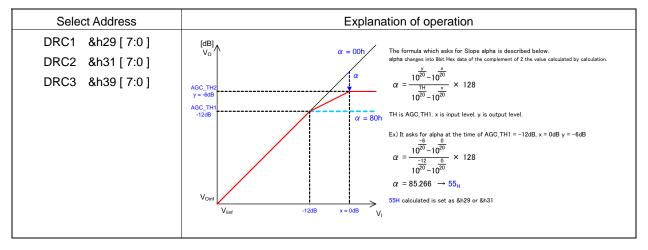

The formula which asks for Slope alpha is described below.

Alpha changes into 8bit Hex data of the complement of 2 the value calculated by calculation.

$$\alpha = \frac{10^{\frac{y}{20}} - 10^{\frac{20}{20}}}{10^{\frac{TH}{20}} - 10^{\frac{x}{20}}} \times 128$$

TH is AGC\_TH1. x is input level. y is output level.

Ex) It asks for alpha at the time of AGC\_TH1 = -12dB, x = 0dB y = -6dB

$$\alpha = \frac{10^{\overline{20}} - 10^{\overline{20}}}{10^{\overline{20}} - 10^{\overline{20}}} \times 128$$

$$\alpha = 85.266 \rightarrow 55_{H}$$

55н calculated is set as &h25 or &h2A

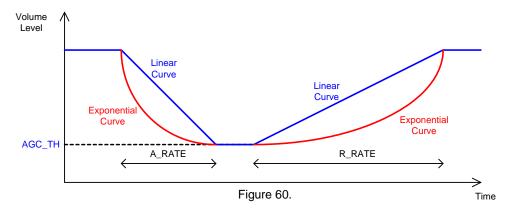

#### Volume Curve

DRC1 ON/OFF setting of slope variable function.

OFF is through output.

Default = 1

| Select Address | Value | Explanation of operation |

|----------------|-------|--------------------------|

| &h20 [ 7]      | 0     | Not use                  |

|                | 1     | Use                      |

# DRC1 ON/OFF setting of compressor

OFF is through output.

Default = 1

| Select Address | Value | Explanation of operation |

|----------------|-------|--------------------------|

| &h20 [ 6 ]     | 0     | Not use                  |

|                | 1     | Use                      |

# DRC2 ON/OFF setting of slope variable function.

OFF is through output.

Default = 1

| Select Address | Value | Explanation of operation |

|----------------|-------|--------------------------|

| &h20 [ 5 ]     | 0     | Not use                  |

|                | 1     | Use                      |

# DRC2 ON/OFF setting of compressor

OFF is through output.

Default = 1

| Select Address | Value | Explanation of operation |

|----------------|-------|--------------------------|

| &h20 [ 4 ]     | 0     | Not use                  |

|                | 1     | Use                      |

# DRC3 ON/OFF setting of slope variable function.

OFF is through output.

Default = 1

| Select Address | Value | Explanation of operation |

|----------------|-------|--------------------------|

| &h20 [ 3 ]     | 0     | Not use                  |

|                | 1     | Use                      |

DRC3 ON/OFF setting of compressor

OFF is through output.

Default = 1

| Select Address | Value | Explanation of operation |

|----------------|-------|--------------------------|

| &h20 [ 2 ]     | 0     | Not use                  |

|                | 1     | Use                      |

### DRC4 ON/OFF setting of compressor

OFF is through output.

Default = 0

| Select Address | Value | Explanation of operation |

|----------------|-------|--------------------------|

| &h3F [ 4 ]     | 0     | Not use                  |

|                | 1     | Use                      |

The volume curve at the time of an attack (A\_RATE) is selected.

#### Default = 0

| Select Address | Value | Explanation of operation |

|----------------|-------|--------------------------|

| &h21[7]        | 0     | Linear curve             |

|                | 1     | Exponential curve        |

The volume curve at the time of a release (R\_RATE) is selected.

#### Default = 0

| Select Address | Value | Explanation of operation |

|----------------|-------|--------------------------|

| &h21 [ 6 ]     | 0     | Linear curve             |

|                | 1     | Exponential curve        |

The choice of the DRC composition

It uses a standard in 3Band DRC but it is possible to use as 1Band DRC, too.

To make the composition of 1Band DRC, it chooses through setting in HPF, LPF and APF.

To set the crossover filter (HPF, LPF and APF) which divides the frequency band of 3Band DRC, therefore, it is referred to the chapter 1-4.

Slope (a) setting of DRC1, DRC2, and DRC3

DRC1, DRC2 and DRC3 are individually setting.

#### Default = 80h

AGC\_TH1 setting of DRC1, DRC2, and DRC3

DRC1, DRC2 and DRC3 are individually setting.

Please set below to the setting value of AGC\_TH2.

#### Default = 40h

| Select Address    | Explanation of operation |           |  |

|-------------------|--------------------------|-----------|--|

| DRC1 &h28 [6:0]   | Command                  | Threshold |  |

| DRC2 &h30 [ 6:0 ] | 00                       | -32dB     |  |

| DRC3 &h38 [ 6:0 ] | :                        | i i       |  |

|                   | 3F                       | -0.5dB    |  |

|                   | 40                       | 0dB       |  |

|                   | 41                       | +0.5dB    |  |

|                   | <b>:</b>                 | i i       |  |

|                   | 58                       | +12dB     |  |

|                   |                          |           |  |

AGC\_TH2 setting of DRC1, DRC2, DRC3, and DRC4

DRC1, DRC2, DRC3 and DRC4 are individually setting.

Default = 40h

| Select Address    | Explanation of operation |           |  |

|-------------------|--------------------------|-----------|--|

| DRC1 &h2C [ 6:0 ] |                          |           |  |

| DRC2 &h34 [ 6:0 ] | Command                  | Threshold |  |

| DRC3 &h3C [6:0]   | 00                       | -32dB     |  |

|                   | i i                      | :         |  |

| DRC4 &h40 [ 6:0 ] | 3F                       | -0.5dB    |  |

|                   | 40                       | 0dB       |  |

|                   | 41                       | +0.5dB    |  |

|                   | :                        | :         |  |

|                   | 58                       | +12dB     |  |

A\_RATE setting of DRC1, DRC2, DRC3, and DRC4

(It is the transition time of a compression curve at the time of an attack.)

DRC1, DRC2, DRC3 and DRC4 are individually setting.

Default = 3h

| Select Address                      | Explanation of operation |                 |         |             |

|-------------------------------------|--------------------------|-----------------|---------|-------------|

| Slope function of DRC1 &h2A [ 6:4 ] | Comm                     | and A_RATE time | Command | A_RATE time |

| Slope function of DRC2 &h32 [ 6:4 ] | 0                        | 1ms             | 4       | 5ms         |

| Slope function of DRC3 &h3A [ 6:4 ] | 1                        | 2ms             | 5       | 10ms        |

| Compressor of DRC1 &h2E [ 6:4 ]     | 2                        | 3ms             | 6       | 20ms        |

| Compressor of DRC2 &h36 [ 6:4 ]     | 3                        | 4ms             | 7       | 40ms        |

| Compressor of DRC3 &h3D [ 6:4 ]     |                          |                 |         |             |

| Compressor of DRC4 &h41 [ 6:4 ]     |                          |                 |         |             |

R\_RATE setting of DRC1, DRC2, DRC3, and DRC4 (It is the transition time of an extension curve at the time of release.) DRC1, DRC2, DRC3 and DRC4 are individually setting.

Default = Bh

| Select Address                      | Explanation of operation |         |             |         |             |

|-------------------------------------|--------------------------|---------|-------------|---------|-------------|

| Slope function of DRC1 &h2A [ 3:0 ] |                          | Command | R_RATE time | Command | R_RATE time |

| Slope function of DRC2 &h32 [ 3:0 ] |                          | 0       | 0.125s      | 8       | 2s          |

| Slope function of DRC3 &h3A [ 3:0 ] |                          | 1       | 0.1825s     | 9       | 2.5s        |

| Compressor of DRC1 &h2E [ 3:0 ]     |                          | 2       | 0.25s       | Α       | 3s          |

| Compressor of DRC2 &h36 [ 3:0 ]     |                          | 3       | 0.5s        | В       | 4s          |

| Compressor of DRC3 &h3D [ 3:0 ]     |                          | 4       | 0.75s       | С       | 5s          |

| Compressor of DRC4 &h41 [ 3:0 ]     |                          | 5       | 1s          | D       | 6s          |

| Compressor of Divo4 an41 [ 3.0 ]    |                          | 6       | 1.25s       | Е       | 7s          |

|                                     |                          | 7       | 1.5s        | F       | 8s          |

A\_TIME1 setting of DRC1, DRC2, DRC3, and DRC4 (Detection time setting of attack operation) DRC1, DRC2, DRC3 and DRC4 are individually setting.

Default = 1h

| Slope function of DRC1 &h2B [ 7:4 ] Slope function of DRC2 &h33 [ 7:4 ] | Command | A TIME time | 0       |             |

|-------------------------------------------------------------------------|---------|-------------|---------|-------------|

| Slope function of DRC2 &h33 [7:4]                                       |         |             | Command | A_TIME time |

|                                                                         | 0       | 0ms         | 8       | 6ms         |

| Slope function of DRC3 &h3B [ 7:4 ]                                     | 1       | 0.5ms       | 9       | 7ms         |

|                                                                         | 2       | 1ms         | Α       | 8ms         |

| Compressor of DRC1 &h2F [ 7:4 ]                                         | 3       | 1.5ms       | В       | 9ms         |

| Compressor of DRC2 &h37 [7:4]                                           | 4       | 2ms         | С       | 10ms        |

| Compressor of DRC3 &h3E [ 7:4 ]                                         | 5       | 3ms         | D       | 20ms        |

|                                                                         | 6       | 4ms         | E       | 30ms        |

| Compressor of DRC4 &h42 [ 7:4 ]                                         | 7       | 5ms         | F       | 40ms        |

R\_TIME setting of DRC1, DRC2, DRC3, and DRC4 (Detection time setting of release operation) DRC1, DRC2, DRC3 and DRC4 are individually setting.

Default = 3h

| Select Address                      | s |         | Explanation of operation |         |             |  |

|-------------------------------------|---|---------|--------------------------|---------|-------------|--|

| Slope function of DRC1 &h2B [ 2:0 ] |   | Command | R_TIME time              | Command | R_TIME time |  |

| Slope function of DRC2 &h33 [ 2:0 ] |   | 0       | 5ms                      | 4       | 100ms       |  |

| Slope function of DRC3 &h3B [ 2:0 ] |   | 1       | 10ms                     | 5       | 200ms       |  |

| Compressor of DRC1 &h2F [ 2:0 ]     |   | 2       | 25ms                     | 6       | 300ms       |  |

| Compressor of DRC2 &h37 [ 2:0 ]     |   | 3       | 50ms                     | 7       | 400ms       |  |

|                                     |   |         |                          |         |             |  |

| Compressor of DRC3 &h3E [ 2:0 ]     |   |         |                          |         |             |  |

| Compressor of DRC4 &h42 [ 2:0 ]     |   |         |                          |         |             |  |

#### [Question]

Recommendation value setting of 3 bands DRC?

#### [Answer]

The recommendation value of 3 band DRC was examined to speaker protection using FPD TV.

A\_RATE: 4msR\_RATE: 2s or moreA\_TIME: 0.5msR\_TIME: 50ms or more

It is not uncomfortable to a music source to arrange all DRC (DRC1, DRC2 and DRC3) with the same value.

#### [Question]

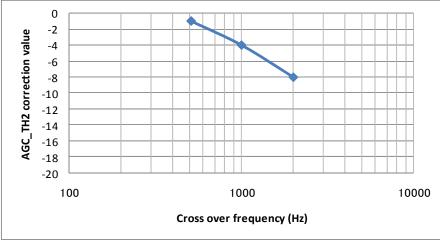

When master volume is increased, why is it that only the sound of a high region becomes large? [Answer]

It investigated about the cross over frequency and the relation of AGC\_TH2 of DRC for high frequency band. Its sound energy decreases, so that music data becomes high frequency. When a cross over frequency is set up highly, unless it lowers AGC\_TH2 of DRC for high frequency band, when master volume is increased, the effect by limit cannot be heard.

Figure 61.

About the amount of adjustments of AGC\_TH2 of DRC3.

Please use as a standard of the adjustment value from AGC\_TH2 value of DRC for low frequency band.

Moreover, the amount of adjustments decreases by setting up a cross over frequency lowness.

Figure 62.

#### 1-7. Post-scaler

To overflow when the level sometimes is full scale entry in case of the digital signal which is inputted to the sound DSP and does surround and equalizer processing, it adjusts an entry gain with Pre-scaler. The adjustable-range can be set from +48 dB to -79 dB with the 0.5-dB step. (Lch/Rch concurrency control) Pre-scaler doesn't have a soft transfer feature.

#### Default = 60h

| elect Address | Explanation of operation |         |  |

|---------------|--------------------------|---------|--|

| &h13 [ 7:0 ]  | Command Value            | Gain    |  |

|               | 00                       | +48dB   |  |

|               | 01                       | +47.5dB |  |

|               | :                        | ÷       |  |

|               | 60                       | 0dB     |  |

|               | 61                       | -0.5dB  |  |

|               | 62                       | -1dB    |  |

|               | :                        | :       |  |

|               | FE                       | -79dB   |  |

|               | FF                       | -∞      |  |

#### 1-8. Fine Post-scaler

An adjustable range can be set up at a 0.1dB step from +0.7dB to -0.8dB. Fine Post-scaler does not have a smooth transition function. (Independent control of Lch/Rch.)

| Default=8h       |                          |        |         |        |  |  |

|------------------|--------------------------|--------|---------|--------|--|--|

| Select Address   | Explanation of operation |        |         |        |  |  |

| Lch &h14 [7:4]   | Command                  | Gain   | Command | Gain   |  |  |

| Rch &h14 [ 3:0 ] | 0                        | -0.8dB | 8       | 0dB    |  |  |

|                  | 1                        | -0.7dB | 9       | +0.1dB |  |  |

|                  | 2                        | -0.6dB | Α       | +0.2dB |  |  |

|                  | 3                        | -0.5dB | В       | +0.3dB |  |  |

|                  | 4                        | -0.4dB | C       | +0.4dB |  |  |

|                  | 5                        | -0.3dB | D       | +0.5dB |  |  |

|                  | 6                        | -0.2dB | Е       | +0.6dB |  |  |

|                  | 7                        | -0.1dB | F       | +0.7dB |  |  |

|                  |                          |        |         |        |  |  |

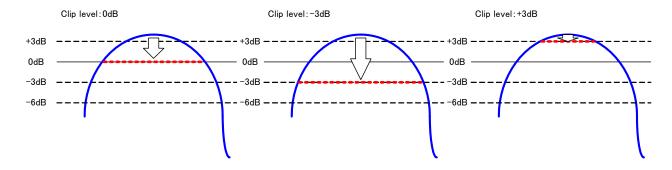

#### 1-9. Hard Clipper

When measuring the rated output of the television, THD+N measures in 10%. It can be made to clip with any output amplitude by using a clipper function. For example, the rated output of 10W or 5W can be gained using the amplifier of 15W output.

#### Hard clip

Clipper setting Default = 1

Figure 63.

| Select Address | Value | Explanation of operation       |

|----------------|-------|--------------------------------|

| &h1A [ 0 ]     | 0     | Clipper function is not used.  |

|                | 1     | Hard clipper function is used. |

#### Clip level selection

#### Default = E1h

| Select Address | Explanation | n of operation |

|----------------|-------------|----------------|

| &h1B [ 7:0 ]   | Command     | Gain           |

|                | 00          | -22.5dB        |

|                | :           | :              |

|                | E0          | -0.1dB         |

|                | E1          | 0dB            |

|                | E2          | +0.1dB         |

|                | 1           | :              |

|                | FF          | +3dB           |

|                |             |                |

#### 1-10. DC cut HPF (Back)

DC offset element of the digital signal outputted from audio DSP is cut by this HPF. The cutoff frequency fc of HPF uses the 1Hz filter, and the degree uses the first-order filter.

#### Default = 1

| Select Address | Value | Explanation of operation |

|----------------|-------|--------------------------|

| &h18 [ 0 ]     | 0     | Not use                  |

|                | 1     | Use                      |

#### 1-11. RAM clear

The data RAM of DSP and coefficient RAM are cleared. 40us or more is required until all the data is cleared.

#### Clear of the data RAM

#### Default = 1

| Select Address | Value | Explanation of operation |

|----------------|-------|--------------------------|

| &h01 [ 7 ]     | 0     | Normal                   |

|                | 1     | Clear operation          |

#### Clear of coefficient RAM

#### Default = 1

| Select Address | Value | Explanation of operation |

|----------------|-------|--------------------------|

| &h01 [ 6 ]     | 0     | Normal                   |

|                | 1     | Clear operation          |

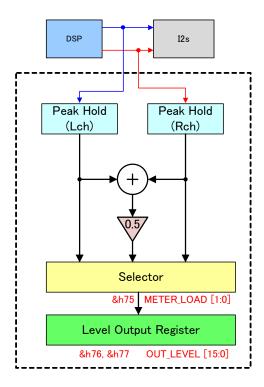

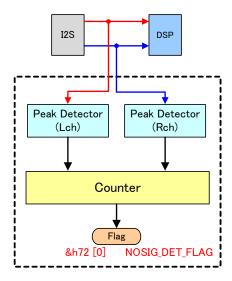

#### 1-12. Audio Output Level Meter

It is possible to output the peak level of the PCM data inputted into a PWM processor. A peak value can be read using the 2-wire command interface as 16 bit data of an absolute value. The interval holding a peak value can be selected from six steps (50ms step) from 50ms to 300ms. A peak hold result can be selected from L channel, R channel, and a monophonic channel {(Lch+Rch) /2}.

# Audio Output Level Meter block diagram

Figure 64.

Setting of the peak level hold time interval of Audio Output Level Meter Default = 00h

| Select Address | Explanation of operation |           |  |

|----------------|--------------------------|-----------|--|

| &h74 [ 2:0 ]   | Command                  | Hold time |  |

|                | 0                        | 50ms      |  |

|                | 1                        | 100ms     |  |

|                | 2                        | 150ms     |  |

|                | 3                        | 200ms     |  |

|                | 4                        | 250ms     |  |

|                | 5                        | 300ms     |  |

The signal of Audio Level Meter read-back is selected.

A value will be taken into a read-only register if a setting value is written in.

In order to update this register value, it is necessary to write in a setting value again.

#### Default = 0

| Select Address | Value | Explanation of operation                            |

|----------------|-------|-----------------------------------------------------|

| &h75 [ 1:0 ]   | 0     | The peak level of L channel                         |

|                | 1     | The peak level of R channel                         |

|                | 2     | The peak level of monophonic channel {(Lch+Rch) /2} |

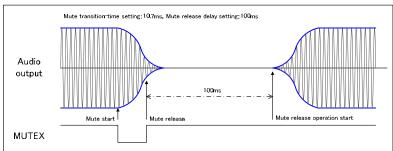

#### Read-back of Audio Output Level