## Is Now Part of

## ON Semiconductor®

# To learn more about ON Semiconductor, please visit our website at www.onsemi.com

Please note: As part of the Fairchild Semiconductor integration, some of the Fairchild orderable part numbers will need to change in order to meet ON Semiconductor's system requirements. Since the ON Semiconductor product management systems do not have the ability to manage part nomenclature that utilizes an underscore (\_), the underscore (\_) in the Fairchild part numbers will be changed to a dash (-). This document may contain device numbers with an underscore (\_). Please check the ON Semiconductor website to verify the updated device numbers. The most current and up-to-date ordering information can be found at <a href="www.onsemi.com">www.onsemi.com</a>. Please email any questions regarding the system integration to Fairchild <a href="guestions@onsemi.com">guestions@onsemi.com</a>.

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any EDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officer

## **FDMF8704**

## High Efficiency / High Frequency FET plus Driver Multi-chip Module

#### **Benefits**

- Fully optimized system efficiency. Higher efficiency levels are achievable compared with conventional discrete components.

- Space savings of up to 50% PCB versus discrete solutions.

- Higher frequency of operation.

- Simpler system design and board layout. Reduced time in component selection and optimization.

#### **Features**

- 7V to 20V Input Voltage Range

- Output current to 32A

- 1MHz switching frequency capable

- Internal adaptive gate drive

- Low Side FET with Integrated Schottky Diode

- Peak Efficiency >90%

- Output disable for lost phase shutdown

- Low profile SMD package

- RoHS Compliant

## **General Description**

The FDMF8704 is a fully optimized integrated Driver plus MOSFET power stage solution for high current synchronous buck DC-DC applications. The device integrates a driver IC and two Power MOSFETs into a space saving, MLP 8x8, 56-pin package. Fairchild Semiconductor's integrated approach optimizes the complete switching power stage with regards to driver to FET dynamic performance, system inductance and overall solution ON resistance. Package parasitics and problematical layouts associated with conventional discrete solutions are greatly reduced. This integrated approach results in significant board space saving, therefore maximizing footprint power density. This solution is based on the Intel™ DrMOS specification.

## **Applications**

- Desktop and server VR11.x V-core and non V-core buck converters.

- CPU/GPU power train in game consoles and high end desktop systems.

- High-current DC-DC Point of Load (POL) converters.

- Networking and telecom microprocessor voltage regulators.

- Small form factor voltage regulator modules.

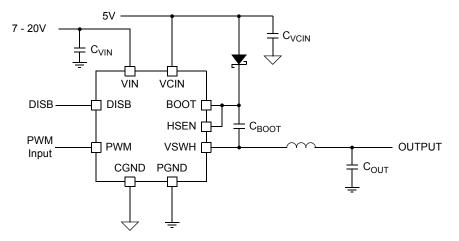

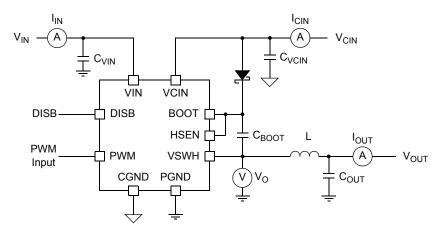

## **Powertrain Application Circuit**

Figure 1. Powertrain Application Circuit

## **Ordering Information**

| Part     | Current Rating<br>Max<br>[A] | Input Voltage<br>Typical<br>[V] | Frequency<br>Max<br>[KHz] | Device<br>Marking |

|----------|------------------------------|---------------------------------|---------------------------|-------------------|

| FDMF8704 | 32                           | 12-19                           | 1000                      | FDMF8704          |

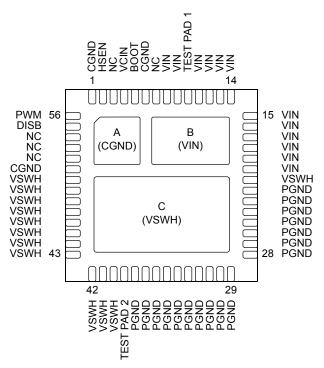

## **Pin Configuration**

Figure 2. MLP 8x8 56L Bottom View

## **Pin Description**

| Pin                                                                                               | Name       | Function                                                                                                                                  |

|---------------------------------------------------------------------------------------------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 6, 51, A                                                                                       | CGND       | IC Ground. Ground return for driver IC.                                                                                                   |

| 2                                                                                                 | HSEN       | High Side FET Enable. Must be connected to BOOT pin.                                                                                      |

| 3, 7, 52-54                                                                                       | NC         | No connect                                                                                                                                |

| 4                                                                                                 | VCIN       | IC Supply. +5V chip bias power. Bypass with a 1µF ceramic capacitor.                                                                      |

| BOOT  Bootstrap Supply Input. Provides voltage supply to high-side MOSFET dr bootstrap capacitor. |            | Bootstrap Supply Input. Provides voltage supply to high-side MOSFET driver. Connect bootstrap capacitor.                                  |

| 21, 40-50, C                                                                                      | VSWH       | Switch Node Input. SW Provides return for high-side bootstrapped driver and acts as a sense point for the adaptive shoot-thru protection. |

| 8, 9, 11-20, B                                                                                    | VIN        | Power Input. Output stage supply voltage.                                                                                                 |

| TEST PAD 1 For manufacturing test only. HDRV pin. This pin must be flany pin.                     |            | For manufacturing test only. HDRV pin. This pin must be floated. Must not be connected to any pin.                                        |

| 22-38                                                                                             | PGND       | Power ground. Output stage ground. Source pin of low side MOSFET(s).                                                                      |

| 39                                                                                                | TEST PAD 2 | For manufacturing test only. LDRV pin. This pin must be floated. Must not be connected to any pin.                                        |

| 55                                                                                                | DISB       | Output Disable. When low, this pin disable FET switching (HDRV and LDRV are held low).                                                    |

| 56                                                                                                | PWM        | PWM Signal Input. This pin accepts a logic-level PWM signal from the controller.                                                          |

2

## **Absolute Maximum Rating**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Parameter                                                     | •                                                                   | Min. | Max. | Units |

|---------------------------------------------------------------|---------------------------------------------------------------------|------|------|-------|

| V <sub>CIN</sub> , PWM, [                                     | DISB to PGND                                                        | -0.3 | 6    | V     |

| V <sub>IN</sub> to PGND                                       |                                                                     | -0.3 | 24   | V     |

| BOOT to VSV                                                   | VH                                                                  | -0.3 | 6    | V     |

| VSWH to PGI                                                   | ND                                                                  | -1.0 | 24   | V     |

| BOOT to PGN                                                   | ND                                                                  | -0.3 | 30   | V     |

| I <sub>O(AV)</sub>                                            | $V_{IN} = 12V, V_{O} = 1.3V, f_{SW} = 1MHz, T_{PCB} = 100^{\circ}C$ |      | 32   | Α     |

| I <sub>O(PK)</sub>                                            | $V_{IN} = 12V, t_{PULSE} = 10\mu s$                                 |      | 65   | Α     |

| $R_{\theta JPCB}$ Junction to PCB Thermal Resistance (note 1) |                                                                     |      | 5    | °C/W  |

| P <sub>D</sub>                                                | T <sub>PCB</sub> = 100°C (note 1)                                   |      | 10   | W     |

| Operating and                                                 | d Storage Junction Temperature Range                                | -55  | 150  | °C    |

Note 1: Package power dissipation based on 4 layers, 2 square inch, 2 oz. copper pad. R<sub>0JPCB</sub> is the steady state junction to PCB thermal resistance with PCB temperature referenced at VSWH pin.

## **Recommended Operating Range**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to Absolute Maximum Ratings.

| Parameter        |                                | Min. | Тур. | Max. | Units |

|------------------|--------------------------------|------|------|------|-------|

| V <sub>CIN</sub> | Control Circuit Supply Voltage | 4.5  | 5    | 5.5  | V     |

| V <sub>IN</sub>  | Output Stage Supply Voltage    | 7    | 12   | 20   | V     |

| V <sub>OUT</sub> | Output Voltage                 | 0.8  | 1.3  | 3.2  | V     |

### **Electrical Characteristics**

$V_{IN}$  = 12V,  $V_{CIN}$  = 5V,  $T_A$  = 25°C unless otherwise noted.

| Parameter                      | Symbol                                | Conditions                                      | Min. | Тур. | Max. | Units |

|--------------------------------|---------------------------------------|-------------------------------------------------|------|------|------|-------|

| Operating Voltage Range        | V <sub>CIN</sub>                      |                                                 | 4.5  | 5    | 5.5  | V     |

| Control Circuit Cumply Current |                                       | f <sub>SW</sub> = 0Hz, V <sub>DISB</sub> = 0V   |      | 1    | 3    | m Λ   |

| Control Circuit Supply Current | Icc                                   | f <sub>SW</sub> = 1MHz, V <sub>DISB</sub> = 5V  |      | 50   |      | mA    |

| PWM Input High Voltage         | V <sub>IH(PWM)</sub>                  |                                                 | 2.4  |      |      | V     |

| PWM Input Low Voltage          | V <sub>IL(PWM)</sub>                  |                                                 |      |      | 0.8  | V     |

| PWM Input Current              | I <sub>IL(PWM)</sub>                  |                                                 | -2   |      | 2    | μA    |

| DISB Input High Voltage        | V <sub>IHDISB)</sub>                  |                                                 | 2.4  |      |      | V     |

| DISB Input Low Voltage         | V <sub>IL(DISB)</sub>                 |                                                 |      |      | 0.8  | V     |

| DISB Input Current             | I <sub>IL(DISB)</sub>                 |                                                 | -2   |      | 2    | μΑ    |

|                                | t <sub>PDL(DISB-LDRV)</sub> (2)       |                                                 |      | 8    |      | ns    |

|                                | t <sub>PDH(DISB-LDRV)</sub> (2)       |                                                 |      | 6    |      | ns    |

| Propagation Delay              | t <sub>PDL(LDRV)</sub> (2)            | V <sub>IN</sub> = 12V, V <sub>OUT</sub> = 1.3V, |      | 9    |      | ns    |

| Propagation Delay              | t <sub>PDL(HDRV)</sub> <sup>(2)</sup> | f <sub>sw</sub> = 1MHz, I <sub>O</sub> = 30A    |      | 22   |      | ns    |

|                                | t <sub>PDH(LDRV)</sub> <sup>(2)</sup> |                                                 |      | 12   |      | ns    |

|                                | t <sub>PDH(HDRV)</sub> <sup>(2)</sup> |                                                 |      | 20   |      | ns    |

Note 2: t<sub>PDL(LDRV/HRDV)</sub> refers to HIGH-to-LOW transition, t<sub>PDH(LDRV/HDRV)</sub> refers to LOW-to-HIGH transition.

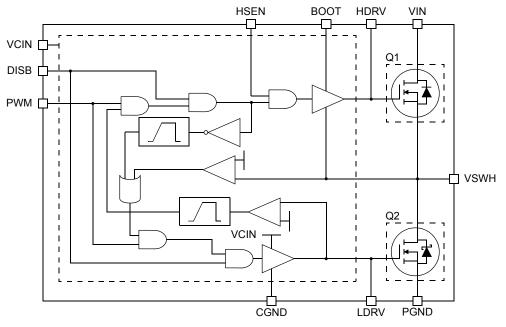

## **Functional Block Diagram**

Figure 3. Functional Block Diagram

## **Functional Description**

The FDMF8704 is a driver plus FET module optimized for synchronous buck converter topology. A single PWM input signal is all that is required to properly drive the high-side and the low-side MOSFETs. Each part is capable of driving speeds up to 1MHz.

#### Low-Side Driver

The low-side driver (LDRV) is designed to drive a ground referenced low  $R_{DS(ON)}$  N-channel MOSFET. The bias for LDRV is internally connected between VCIN and CGND. When the driver is enabled, the driver's output is 180° out of phase with the PWM input. When the driver is disabled (DISB = 0V), LDRV is held low.

#### **High-Side Driver**

The high-side driver (HDRV) is designed to drive a floating N-channel MOSFET. The bias voltage for the high-side driver is developed by a bootstrap supply circuit, consisting of the external diode and external bootstrap capacitor ( $C_{BOOT}$ ). During start-up, VSWH is held at PGND, allowing  $C_{BOOT}$  to charge to VCIN through the internal diode. When the PWM input goes high, HDRV will begin to charge the high-side MOSFET's gate (Q1). During this transition, charge is removed from  $C_{BOOT}$  and delivered to Q1's gate. As Q1 turns on, VSWH rises to  $V_{IN}$ , forcing the BOOT pin to  $V_{IN}$  + $V_{C(BOOT)}$ , which provides sufficient VGS enhancement for Q1. To complete the switching cycle, Q1 is turned off by pulling HDRV to VSWH.  $C_{BOOT}$  is then recharged to VCIN when VSWH falls to PGND. HDRV output is in phase with the PWM input. When the driver is disabled, the high-side gate is held low.

### **Adaptive Gate Drive Circuit**

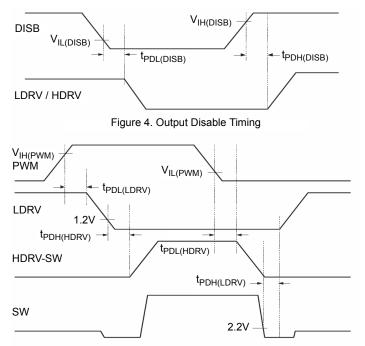

The driver IC embodies an advanced design that ensures minimum MOSFET dead-time while eliminating potential shootthrough (cross-conduction) currents. It senses the state of the MOSFETs and adjusts the gate drive, adaptively, to ensure they do not conduct simultaneously. Refer to Figure 4 and 5 for the relevant timing waveforms. To prevent overlap during the lowto-high switching transition (Q2 OFF to Q1 ON), the adaptive circuitry monitors the voltage at the LDRV pin. When the PWM signal goes HIGH, Q2 will begin to turn OFF after some propagation delay  $(t_{PDL(LDRV)})$ . Once the LDRV pin is discharged below ~1.2V, Q1 begins to turn ON after adaptive delay t<sub>PDH(HDRV)</sub>. To preclude overlap during the high-to-low transition (Q1 OFF to Q2 ON), the adaptive circuitry monitors the voltage at the SW pin. When the PWM signal goes LOW, Q1 will begin to turn OFF after some propagation delay (t<sub>PDL(HDRV)</sub>). Once the VSWH pin falls below ~2.2V, Q2 begins to turn ON after adaptive delay t<sub>PDH(LDRV)</sub>. Additionally, V<sub>GS</sub> of Q1 is monitored. When V<sub>GS(Q1)</sub> is discharged below ~1.2V, a secondary adaptive delay is initiated, which results in Q2 being driven ON after  $t_{\text{PDH(LDRV)}}$ , regardless of SW state. This function is implemented to ensure CBOOT is recharged each switching cycle, particularly for cases where the power converter is sinking current and SW voltage does not fall below the 2.2V adaptive threshold. Secondary delay t<sub>PDH(HDRV)</sub> is longer than t<sub>PDH(LDRV)</sub>.

## **Timing Diagram**

Figure 5. Adaptive Gate Drive Timing

## **Typical Characteristics**

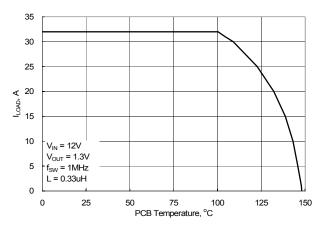

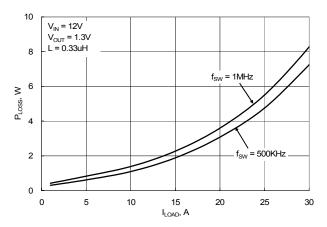

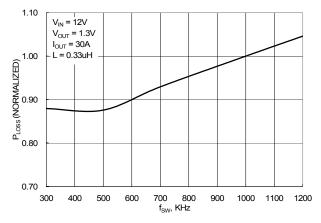

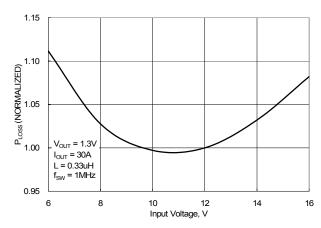

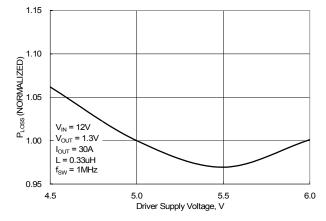

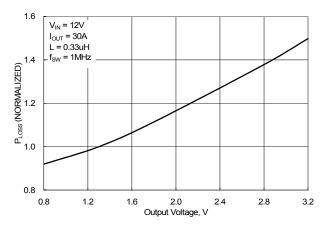

$V_{IN}$  = 12V,  $V_{CIN}$  = 5V,  $T_A$  = 25°C unless otherwise noted.

Figure 6. Safe Operating Area

Figure 7. Module Power Loss vs. Output Current

Figure 8. Power Loss vs. Switching Frequency

Figure 9. Power Loss vs. Input Voltage

Figure 10. Power Loss vs. Driver Supply Voltage

Figure 11. Power Loss vs. Output Voltage

## **Typical Characteristics**

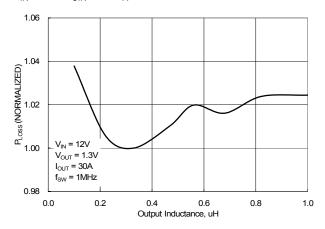

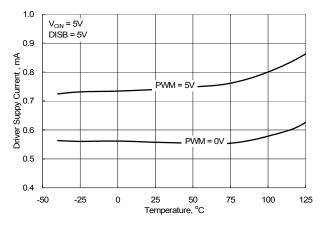

$V_{IN}$  = 12V,  $V_{CIN}$  = 5V,  $T_A$  = 25°C unless otherwise noted.

Figure 12. Power Loss vs. Output Inductance

Figure 13. Driver Supply Current vs. Temperature

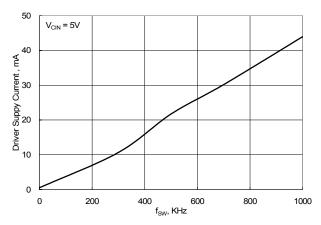

Figure 14. Driver Supply Current vs. Frequency

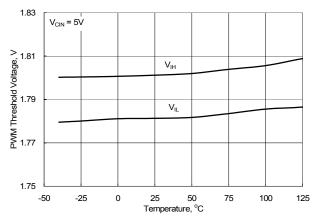

Figure 15. PWM Threshold Voltage vs. Temperature

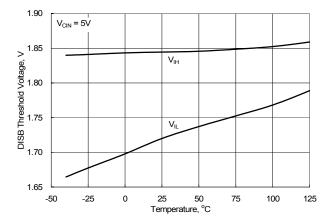

Figure 16. DISB Threshold Voltage vs. Temperature

# **Application Information** Supply Capacitor Selection

For the supply input ( $V_{CIN}$ ) of the FDMF8704, a local ceramic bypass capacitor is recommended to reduce the noise and to supply the peak current. Use at least a 1µF, X7R or X5R capacitor. Keep this capacitor close to the FDMF8704  $V_{CIN}$  and CGND pins.

#### **Bootstrap Circuit**

The bootstrap circuit uses a charge storage capacitor ( $C_{BOOT}$ ) and the external schottky diode, as shown in Figure 18. A

bootstrap capacitance of 100nF, X7R or X5R capacitor is adequate.

The peak surge current rating of the boot diode should be checked in-circuit, since this is dependent on the equivalent impedance of the entire bootstrap circuit, including the PCB traces. Boot diode must be sized big enough to carry the forward charge current. Refer to Figure 14 for boot diode average forward current.

The bootstrap diode must have low  $V_{\text{F}}$  and low reverse current leakage. Breakdown voltage of the bootstrap diode must be greater than the BOOT to VSWH voltage.

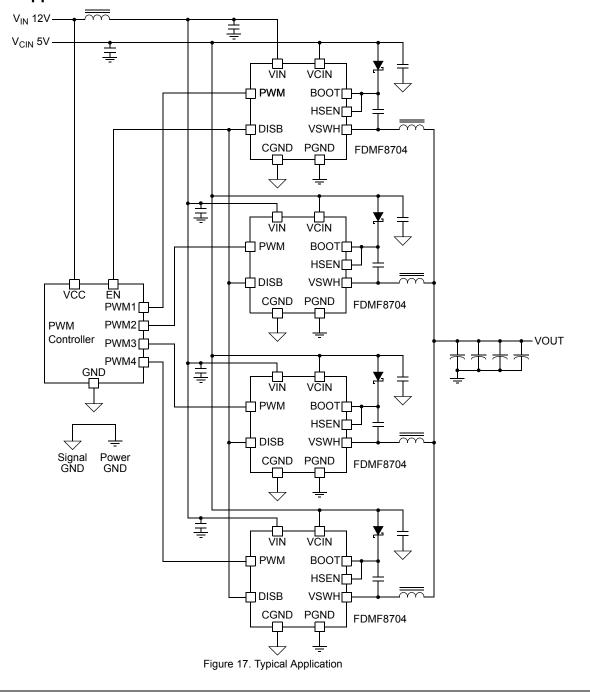

## **Typical Application**

# Module Power Loss Measurement and Calculation

Refer to Figure 18 for module power loss testing method. Power loss calculation are as follows:

(a)  $P_{IN} = (V_{IN} \times I_{IN}) + (V_{CIN} \times I_{CIN})$  (W)

$\begin{array}{ll} \text{(b) } \mathsf{P}_{\mathsf{OUT}} & = \mathsf{V}_{\mathsf{O}} \, \mathsf{x} \, \mathsf{I}_{\mathsf{OUT}} \, \mathsf{(W)} \\ \text{(c) } \mathsf{P}_{\mathsf{LOSS}} & = \mathsf{P}_{\mathsf{IN}} \, \text{-} \, \mathsf{P}_{\mathsf{OUT}} \, \mathsf{(W)} \\ \end{array}$

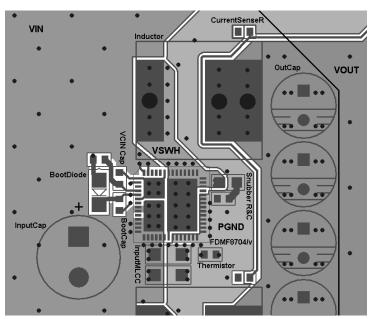

## **PCB Layout Guideline**

Figure 19. shows a proper layout example of FDMF8704 and critical parts. All of high current flow path, such as  $V_{\rm IN}$ , VSWH,  $V_{\rm OUT}$  and GND copper, should be short and wide for better and stable current flow, heat radiation and system performance.

Following is a guideline which the PCB designer should consider:

1. Input bypass capacitors should be close to  $V_{\rm IN}$  and GND pin of FDMF8704 to help reduce input current ripple component induced by switching operation.

- 2. It is critical that the VSWH copper has minimum area for lower switching noise emission. VSWH copper trace should also be wide enough for high current flow. Other signal routing path, such as PWM IN and BOOT signal, should be considered with care to avoid noise pickup from VSWH copper area.

- 3. Output inductor location should be as close as possible to the FDMF8704 for lower power loss due to copper trace.

- 4. Snubber for suppressing ringing and spiking of VSWH voltage should be placed near the FDMF8704. The resistor and capacitor need to be of proper size for power dissipation.

- 5. Place boot diode, ceramic bypass capacitor and boot capacitor as close to  $V_{\text{CIN}}$  and BOOT pin of FDMF8704 in order to supply stable power. Routing width and length should also be considered

- 6. Use multiple Vias on each copper area to interconnect each top, inner and bottom layer to help smooth current flow and heat conduction. Vias should be relatively large and of reasonable inductance.

Figure 18. Power Loss Measurement Block Diagram

Figure 19. Typical PCB Layout Example (Top View)

**9** www.fairchildsemi.com FDMF8704 Rev. G

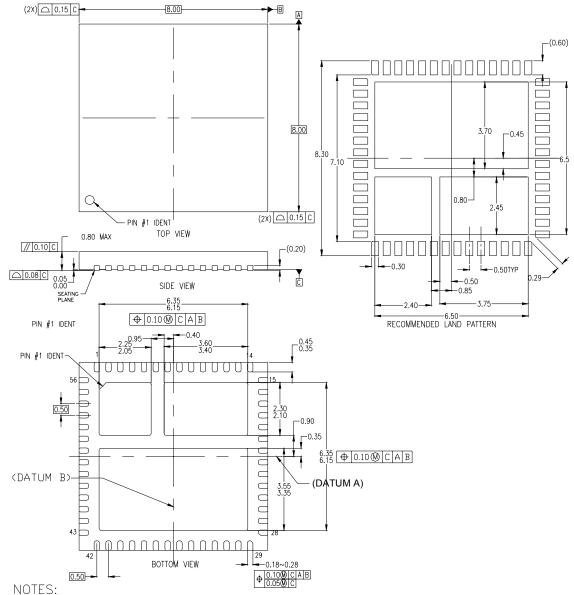

## **Dimensional Outline and Pad layout**

- A. CONFORMS TO JEDEC REGISTRATION MO-220, VARIATION WLLD-5,6

- B. DIMENSIONS ARE IN MILLIMETERS.

- C. DIMENSIONS ARE NOT INCLUSIVE OF BURRS, MOLD FLASH, NOR TIE BAR PROTRUSIONS.

#### **TRADEMARKS**

The following includes registered and unregistered trademarks and service marks, owned by Fairchild Semiconductor and/or its global subsidiaries, and is not intended to be an exhaustive list of all such trademarks.

ACEx<sup>®</sup>

Build it Now<sup>™</sup>

CorePLUS<sup>™</sup>

CROSSVOLT<sup>™</sup>

CTL<sup>™</sup>

Current Transfer Logic™ EcoSPARK®

EcoSPARK<sup>®</sup> EZSWITCH™ \*

Fairchild®

Fairchild Semiconductor® FACT Quiet Series™

FACT<sup>®</sup>

FAST<sup>®</sup>

FastvCore<sup>™</sup>

FlashWriter<sup>®</sup>

$\begin{array}{c} \mathsf{FPS^{\mathsf{TM}}} \\ \mathsf{FRFET}^{\mathbb{R}} \end{array}$

Global Power Resource<sup>SM</sup>

Green FPS™

Green FPS™ e-Series™

GTO™

i-Lo™

IntelliMAX™

ISOPLANAR™

MegaBuck™

MICROCOUPLER™

MicroFET™ MicroPak™ MillerDrive™ Motion-SPM™ OPTOLOGIC® OPTOPLANAR® PDP-SPM™ Power220® Power247® POWEREDGE® Power-SPM™ PowerTrench®

Programmable Active Droop™

QFET<sup>®</sup> QS™

QT Optoelectronics™ Quiet Series™ RapidConfigure™ SMART START™

SPM®

STEALTH™

SuperFET™

SuperSOT™-3

SuperSOT™-6

SuperSOT™-6

SuperSOT™-8

SyncFET<sup>TM</sup>

SYSTEM ®

GENERAL

The Power Franchise®

Franchise

TinyBoost™

TinyBuck™

TinyLogic®

TINYOPTO™

TinyPower™

TinyPower™

TinyPWM™

TinyWire™

µSerDes™

UHC®

UHC®

Ultra FRFET™ UniFET™ VCX™

\* EZSWITCH™ and FlashWriter® are trademarks of System General Corporation, used under license by Fairchild Semiconductor.

#### DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD'S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.

#### As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

- A critical component in any component of a life support, device, or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### **PRODUCT STATUS DEFINITIONS**

#### **Definition of Terms**

| Datasheet Identification | Product Status         | Definition                                                                                                                                                                                               |  |

|--------------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Advance Information      | Formative or In Design | This datasheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                       |  |

| Preliminary              | First Production       | This datasheet contains preliminary data; supplementary data will be published at a later date. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve design. |  |

| No Identification Needed | Full Production        | This datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve the design.                                               |  |

| Obsolete                 | Not In Production      | This datasheet contains specifications on a product that has been discontinued by Fairchild Semiconductor. The datasheet is printed for reference information only.                                      |  |

Rev. I32

ON Semiconductor and in are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdt/Patent-Marking.pdf">www.onsemi.com/site/pdt/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and exp

### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910

Japan Customer Focus Center

Phone: 81-3-5817-1050

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative

## **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

ON Semiconductor:

FDMF8704

OOO «ЛайфЭлектроникс" "LifeElectronics" LLC

ИНН 7805602321 КПП 780501001 P/C 40702810122510004610 ФАКБ "АБСОЛЮТ БАНК" (ЗАО) в г.Санкт-Петербурге К/С 3010181090000000703 БИК 044030703

Компания «Life Electronics» занимается поставками электронных компонентов импортного и отечественного производства от производителей и со складов крупных дистрибьюторов Европы, Америки и Азии.

С конца 2013 года компания активно расширяет линейку поставок компонентов по направлению коаксиальный кабель, кварцевые генераторы и конденсаторы (керамические, пленочные, электролитические), за счёт заключения дистрибьюторских договоров

### Мы предлагаем:

- Конкурентоспособные цены и скидки постоянным клиентам.

- Специальные условия для постоянных клиентов.

- Подбор аналогов.

- Поставку компонентов в любых объемах, удовлетворяющих вашим потребностям.

- Приемлемые сроки поставки, возможна ускоренная поставка.

- Доставку товара в любую точку России и стран СНГ.

- Комплексную поставку.

- Работу по проектам и поставку образцов.

- Формирование склада под заказчика.

- Сертификаты соответствия на поставляемую продукцию (по желанию клиента).

- Тестирование поставляемой продукции.

- Поставку компонентов, требующих военную и космическую приемку.

- Входной контроль качества.

- Наличие сертификата ISO.

В составе нашей компании организован Конструкторский отдел, призванный помогать разработчикам, и инженерам.

Конструкторский отдел помогает осуществить:

- Регистрацию проекта у производителя компонентов.

- Техническую поддержку проекта.

- Защиту от снятия компонента с производства.

- Оценку стоимости проекта по компонентам.

- Изготовление тестовой платы монтаж и пусконаладочные работы.

Тел: +7 (812) 336 43 04 (многоканальный) Email: org@lifeelectronics.ru