# IS34ML02G081 IS35ML02G081

2Gb SLC-1b ECC 3.3V X8 NAND FLASH MEMORY STANDARD NAND INTERFACE

# 2Gb (x8) 3.3V NAND FLASH MEMORY with 1b ECC

# **FEATURES**

# Flexible & Efficient Memory **Architecture**

- Organization: 256Mb x8

- Memory Cell Array: (256M + 8M) x 8bit

- Data Register: (2K + 64) x 8bit

- Page Size: (2K + 64) Byte

- Block Erase: (128K + 4K) Byte

- Memory Cell: 1bit/Memory Cell

# **Highest performance**

- Read Performance

- Random Read: 25us (Max.)

- Serial Access: 25ns (Max.)

- Write Performance

- Program time: 400us typical

- Block Erase time: 2ms typical

# Low Power with Wide Temp. Ranges

- Single 3.3V (2.7V to 3.6V) Voltage Supply

- 15 mÁ Active Read Current

- 10 µA Standby Current

- Temp Grades:

- Industrial: -40°C to +85°C

- Extended: -40°C to +105°C

- Automotive, A1: -40°C to +85°C

- Automotive, A2: -40°C to +105°C

# **Reliable CMOS Floating Gate Technology**

- ECC Requirement: X8 1bit/512Bvte

- Endurance: 100K Program/Erase cycles

- Data Retention: 10 years

# **Efficient Read and Program modes**

- Command/Address/Data Multiplexed I/O Interface

- Command Register Operation

- Automatic Page 0 Read at Power-Up Option

- Boot from NAND support

- Automatic Memory Download

- NOP: 4 cycles

- Cache Program Operation for High Performance Program

- Cache Read Operation

- Copy-Back Operation

- EDO mode

- OTP operation

- Two-Plane Operation

- Bad-Block-Protect

## **Advanced Security Protection**

- Hardware Data Protection:

- Program/Erase Lockout during Power **Transitions**

## **Industry Standard Pin-out & Packages**

- T =48-pin TSOP (Type I)

- B =63-ball VFBGA

## GENERAL DESCRIPTION

The IS34/35ML2G081 is a 256Mx8bit with spare 8Mx8bit capacity. The device is offered in 3.3V Vcc Power Supply. Its NAND cell provides the most cost-effective solution for the solid state mass storage market. The memory is divided into blocks that can be erased independently so it is possible to preserve valid data while old data is erased.

The device contains 2,048 blocks, composed by 64 pages consisting in two NAND structures of 32 series connected Flash cells. A program operation allows to write the 2,112-Byte page in typical 300us and an erase operation can be performed in typical 3ms on a 128K-Byte for X8 device block.

Data in the page mode can be read out at 25ns cycle time per Word. The I/O pins serve as the ports for address and command inputs as well as data input/output.

The copy back function allows the optimization of defective blocks management: when a page program operation fails, the data can be directly programmed in another page inside the same array section without the time consuming serial data insertion phase.

The cache program feature allows the data insertion in the cache register while the data register is copied into the Flash array.

This pipelined program operation improves the program throughput when long files are written inside the memory. A cache read feature is also implemented. This feature allows to dramatically improving the read throughput when consecutive pages have to be streamed out. This device includes extra feature: Automatic Read at Power Up.

# **TABLE OF CONTENTS**

| FE/ | ATURES                                                            | 2  |

|-----|-------------------------------------------------------------------|----|

| GE  | NERAL DESCRIPTION                                                 | 3  |

| TAI | BLE OF CONTENTS                                                   | 4  |

| 1.  | PIN CONFIGURATION                                                 | 6  |

| 2.  | PIN DESCRIPTIONS                                                  | 8  |

| 3.  | BLOCK DIAGRAM                                                     | 9  |

| 4.  | OPERATION DESCRIPTION                                             | 11 |

| 5.  | ELECTRICAL CHARACTERISTICS                                        | 13 |

|     | 5.1 ABSOLUTE MAXIMUM RATINGS (1)                                  | 13 |

|     | 5.2 Recommended Operating Conditions                              | 13 |

|     | 5.3 DC CHARACTERISTICs                                            | 14 |

|     | 5.4 Valid Block                                                   | 14 |

|     | 5.5 AC Measurement Condition                                      | 15 |

|     | 5.6 AC PIN CAPACITANCE (TA = 25°C, VCC=3.3V, 1MHz)                | 15 |

|     | 5.7 Mode Selection                                                | 15 |

|     | 5.8 ROGRAM/ERASE PERFORMANCne                                     | 16 |

|     | 5.9 AC CHARACTERISTICS for address/ command/data input            | 16 |

|     | 5.10 AC CHARACTERISTICS for Operation                             | 17 |

| 6.  | TIMING DIAGRAMS                                                   | 18 |

|     | 6.1 Command Latch Cycle                                           | 18 |

|     | 6.2 Address Latch Cycle                                           | 18 |

|     | 6.3 Input Data Latch Cycle                                        | 19 |

|     | 6.4 Serial Access Cycle after Read (CLE=L, WE#=H, ALE=L)          | 19 |

|     | 6.5 Serial Access Cycle after Read (EDO Type CLE=L, WE#=H, ALE=L) | 20 |

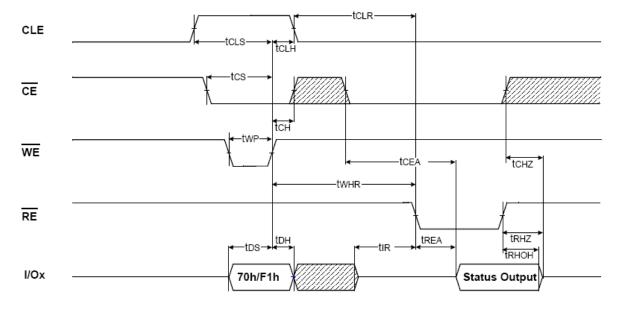

|     | 6.6 Status Read Cycle                                             | 20 |

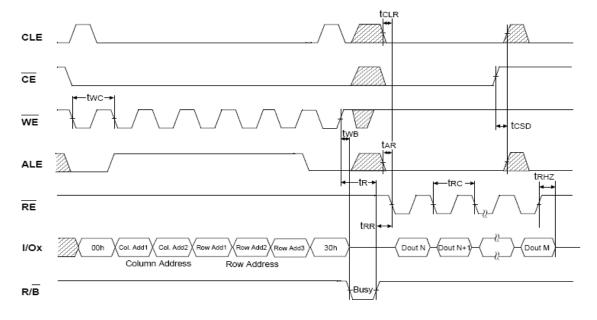

|     | 6.7 Read Operation (One PAGE)                                     | 21 |

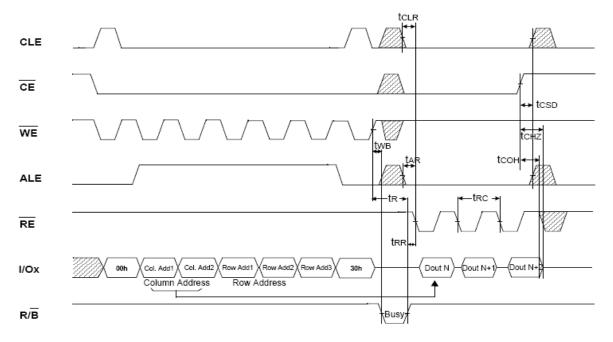

|     | 6.8 Read Operation (Intercepted by CE#)                           | 21 |

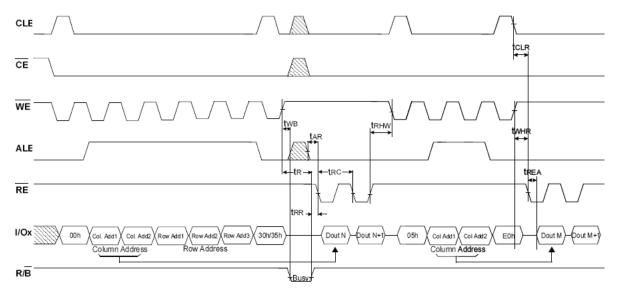

|     | 6.9 Random Data Output In a Page                                  | 22 |

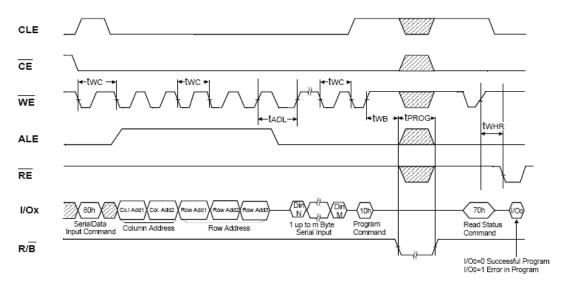

|     | 6.10 Page program Operation                                       | 22 |

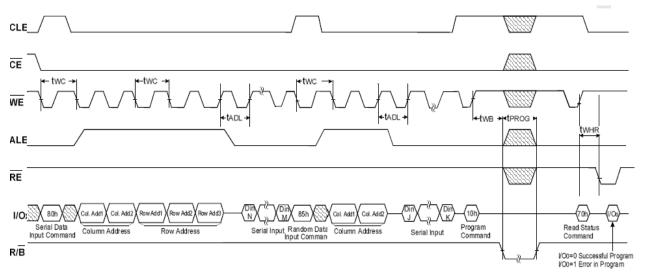

|     | 6.11 Page Program Operation with Random Data Input                | 23 |

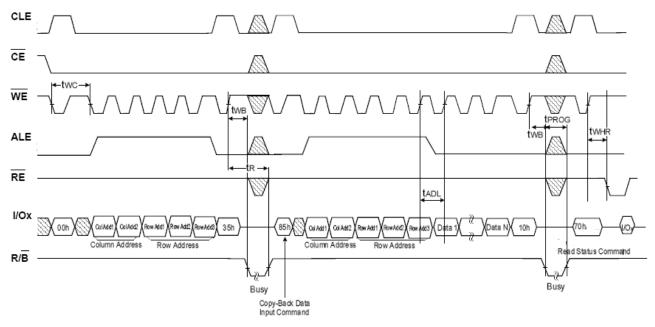

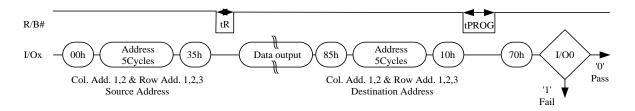

|     | 6.12 Copy-Back Operation with Random Data InpuT                   | 23 |

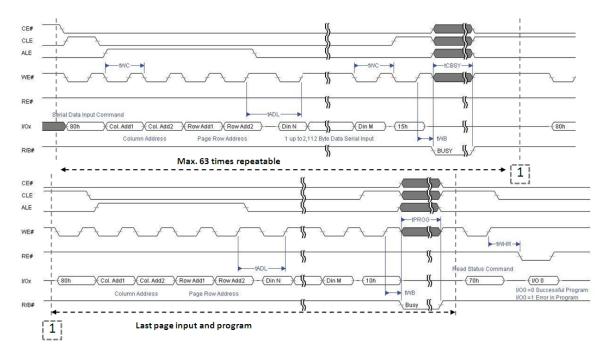

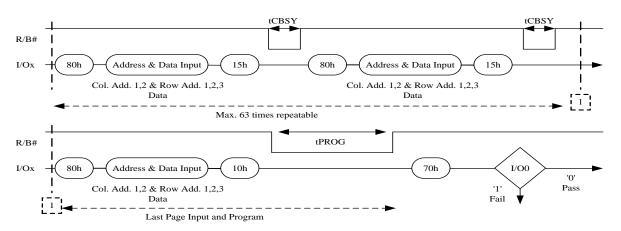

|     | 6.13 Cache Program Operation                                      | 24 |

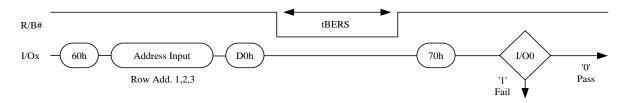

|     | 6.14 Block Erase Operation                                        | 24 |

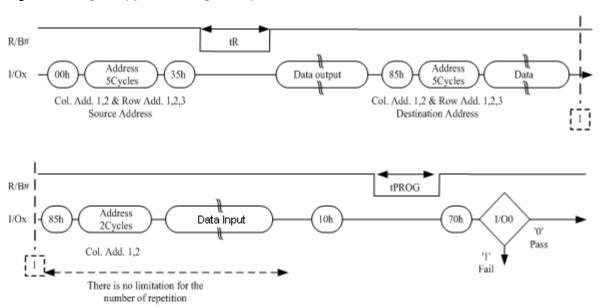

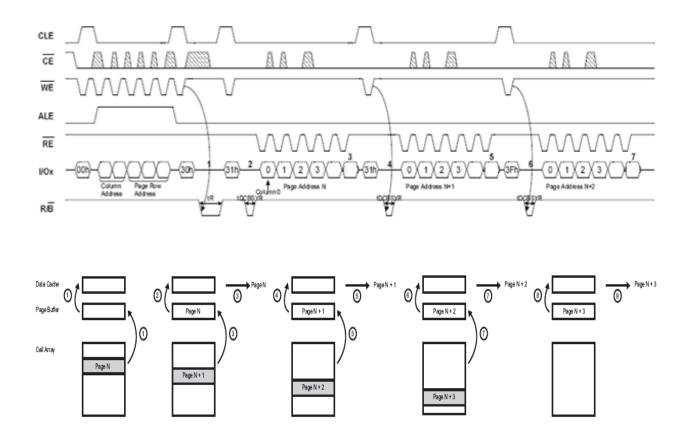

|     | 6.15 Cache Read Operation                                         | 25 |

|     | 6.16 Read ID Operation                                            | 26 |

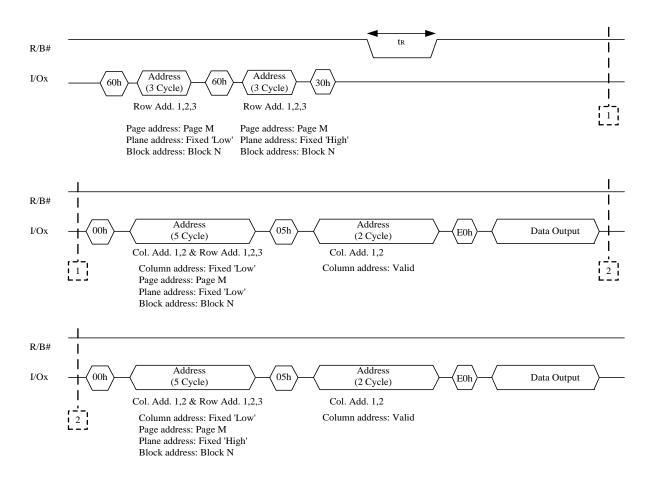

|     | 6.17 TWo-plane Page Read Operation with Two-Plane Random Data Out | 27 |

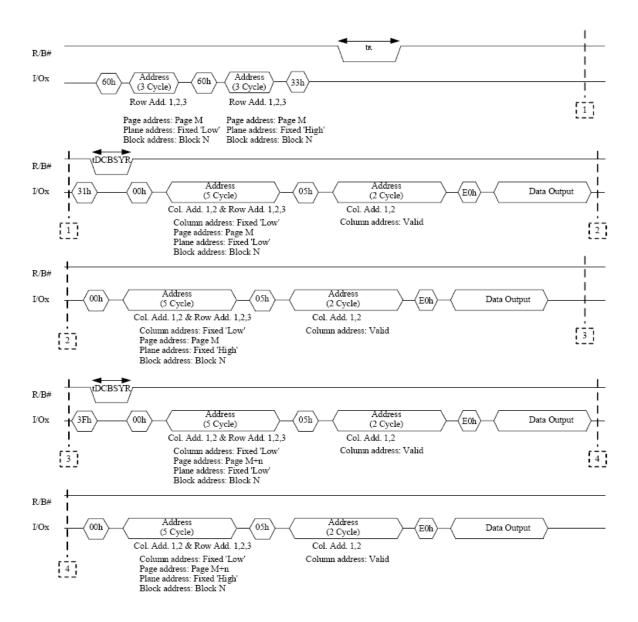

|     | 6.18 two-plane Cache Read Operation                               |    |

|     | 6.19 Two-plane Page Program Operation                             |    |

|     |                                                                   |    |

|     | 6.20 two-plane Cache Program Operation                                    | 30 |

|-----|---------------------------------------------------------------------------|----|

|     | 6.21 READ Two Plane Block Erase Operation                                 | 31 |

| 7.  | ID Definition Table                                                       | 32 |

| 8.  | DEVICE OPERATION                                                          | 34 |

|     | 8.1 Page READ OPERATION                                                   | 34 |

|     | 8.2 Page Program                                                          | 36 |

|     | 8.3 Cache Program                                                         | 37 |

|     | 8.4 Copy-Back Program                                                     | 38 |

|     | 8.5 Block Erase                                                           | 39 |

|     | 8.6 Read Status                                                           | 39 |

|     | 8.7 Read ID                                                               | 41 |

|     | 8.8 Reset                                                                 | 42 |

|     | 8.9 Cache Read                                                            | 43 |

|     | 8.10 Two-Plane Page Read                                                  | 44 |

|     | 8.11 Two-Plane Cache Read                                                 | 45 |

|     | 8.12 Two-Plane Page Program                                               | 46 |

|     | 8.13 Two-Plane Copy Back Program                                          | 47 |

|     | 8.14 Two-Plane Cache Program                                              | 49 |

|     | 8.15 Two-Plane Block Erase                                                | 50 |

|     | 8.16 Ready/Busy#                                                          | 51 |

|     | 8.17 Data Protection and Power Up Sequence                                |    |

|     | 8.18 Write Protect Operation                                              | 53 |

| 9.  | INVALID BLOCK AND ERROR MANAGEMENT                                        | 55 |

|     | 9.1 Mask Out Initial Invalid Block(s)                                     | 55 |

|     | 9.2 Identifying Initial Invalid Block(s) and Block Replacement Management |    |

|     | 9.3 ERRor in Read or Write operation                                      |    |

|     | 9.4 Addressing for PROGRAM operation                                      | 62 |

|     | 9.5 System Interface Using CE# NOT Care operation                         |    |

| 10. |                                                                           |    |

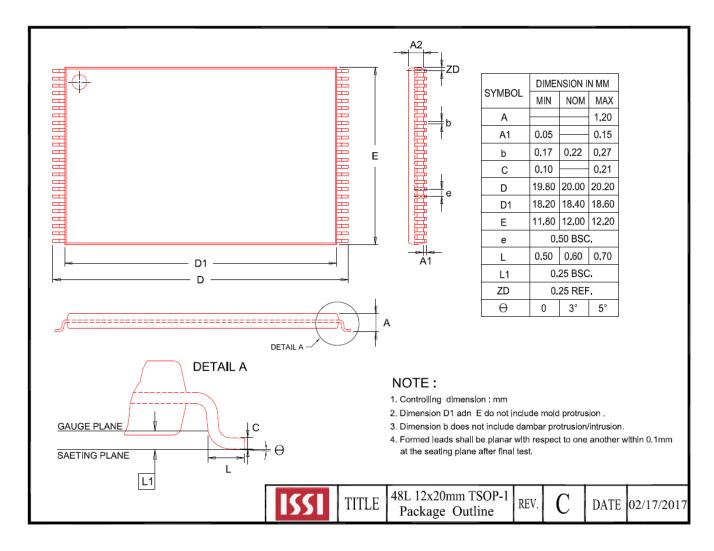

|     | 10.1 48-Pin TSOP (TYPE I) Package (T)                                     | 64 |

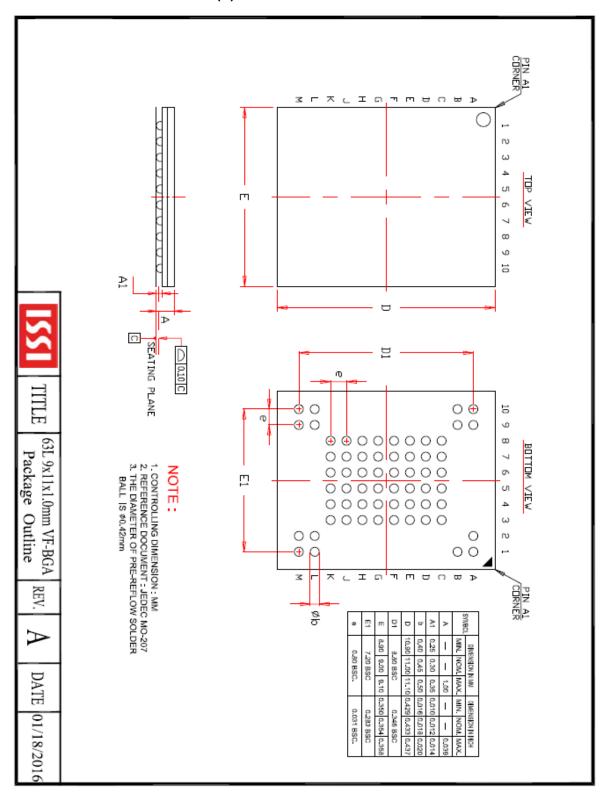

|     | 10.2 63-BALL VFBGA Package (B)                                            | 65 |

| 11  | OPDERING INFORMATION Valid Part Numbers                                   | 66 |

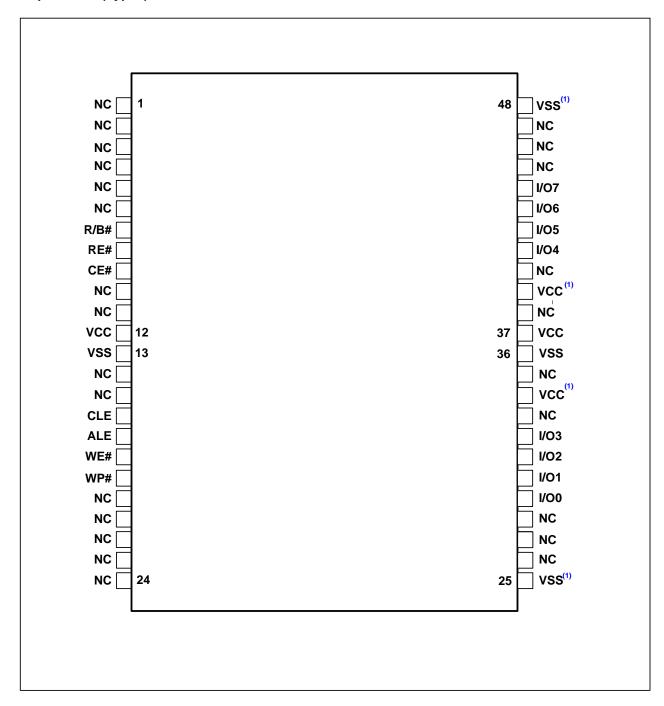

# 1. PIN CONFIGURATION

48-pin TSOP (Type I)

## Note:

1. These pins might not be bonded in the package; however it is recommended to connect these pins to the designated external sources for ONFI compatibility.

# 63-ball VFBGA

# Balls Down, Top View

| A1 A2 NC NC      |            |                    |            |            |            |            | A9<br>NC   | (A)<br>10)<br>NC |

|------------------|------------|--------------------|------------|------------|------------|------------|------------|------------------|

| (B1)<br>NC       |            |                    |            |            |            |            | (B9)<br>NC | B<br>10<br>NC    |

|                  | C3<br>WP#  | C4<br>ALE          | C5<br>VSS  | C6<br>CE#  | C7<br>WE#  | C8<br>R/B# |            |                  |

|                  | D3)<br>NC  | D4<br>RE#          | D5<br>CLE  | D6 NC      | D7)<br>NC  | D8<br>NC   |            |                  |

|                  | E3<br>NC   | (E4)<br>NC         | (E5)<br>NC | (E6)<br>NC | E7<br>NC   | E8<br>NC   |            |                  |

|                  | F3<br>NC   | (F4)<br>NC         | (F5)<br>NC | (F6)<br>NC | VSS (1)    | F8<br>NC   |            |                  |

|                  | (G3)<br>NC | VCC <sup>(1)</sup> | G5<br>NC   | (G6)<br>NC | (G7)<br>NC | (G8)<br>NC |            |                  |

|                  | H3)<br>NC  | H4<br>I/O0         | H5<br>NC   | (H6)<br>NC | H7<br>NC   | H8<br>VCC  |            |                  |

|                  | J3<br>NC   | J4<br>I/O1         | J5<br>NC   | J6<br>VCC  | J7<br>I/O5 | J8<br>I/O7 |            |                  |

|                  | K3<br>VSS  | K4<br>I/O2         | K5<br>I/O3 | K6<br>I/O4 | K7<br>I/O6 | K8<br>VSS  |            |                  |

| L1 (L2)<br>NC NC |            |                    |            |            |            |            | L9<br>NC   | L<br>10<br>NC    |

| M1 (M2)<br>NC NC |            |                    |            |            |            |            | M9)<br>NC  | M<br>10<br>NC    |

## Note:

1. These pins might not be bonded in the package; however it is recommended to connect these pins to the designated external sources for ONFI compatibility.

# 2. PIN DESCRIPTIONS

| Pin Name         | Pin Function                                                                                                                                                                                                                                                                                                                                |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I/O0 ~ I/O7 (X8) | DATA INPUTS/OUTPUTS  The I/O pins are used to input command, address and data, and to output data during read operations. The I/O pins float to high-z when the chip is deselected or when the outputs are disabled.                                                                                                                        |

| CLE              | COMMAND LATCH ENABLE The CLE input controls the activating path for commands sent to the internal command registers. Commands are latched into the command register through the I/O ports on the rising edge of the WE# signal with CLE high.                                                                                               |

| ALE              | ADDRESS LATCH ENABLE The ALE input controls the activating path for addresses sent to the internal address registers. Addresses are latched into the address register through the I/O ports on the rising edge of WE# with ALE high.                                                                                                        |

| CE#              | CHIP ENABLE The CE# input is the device selection control. When the device is in the Busy state, CE# high is ignored, and the device does not return to standby mode in program or erase operation. Regarding CE# control during read operation, refer to 'Page read' section of Device operation.                                          |

| RE#              | READ ENABLE The RE# input is the serial data-out control, and when it is active low, it drives the data onto the I/O bus. Data is valid tREA after the falling edge of RE# which also increments the internal column address counter by one.                                                                                                |

| WE#              | WRITE ENABLE The WE# input controls writes to the I/O ports. Commands, address and data are latched on the rising edge of the WE# pulse.                                                                                                                                                                                                    |

| WP#              | WRITE PROTECT The WP# pin provides inadvertent write/erase protection during power transitions. The internal high voltage generator is reset when the WP# pin is active low.                                                                                                                                                                |

| R/B#             | READY/BUSY OUTPUT The R/B# output indicates the status of the device operation. When low, it indicates that a program, erase or random read operation is in progress and returns to high state upon completion. It is an open drain output and does not float to high-z condition when the chip is deselected or when outputs are disabled. |

| VCC              | POWER VCC is the power supply for device.                                                                                                                                                                                                                                                                                                   |

| VSS              | GROUND                                                                                                                                                                                                                                                                                                                                      |

| N.C.             | NO CONNECTION Lead is not internally connected.                                                                                                                                                                                                                                                                                             |

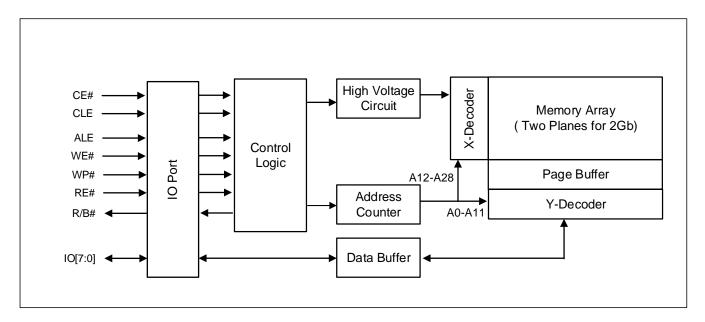

# 3. BLOCK DIAGRAM

Figure 3.1 Functional Block Diagram

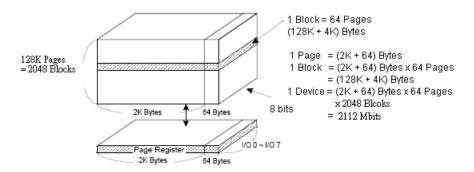

Figure 3.2 Array Organization

# Table 3.1 ARRAY Address (x8)

|                       | I/O 0           | I/O 1                 | I/O 2           | I/O 3           | I/O 4                 | I/O 5           | I/O 6           | I/O 7           | Address        |

|-----------------------|-----------------|-----------------------|-----------------|-----------------|-----------------------|-----------------|-----------------|-----------------|----------------|

| 1 <sup>st</sup> cycle | A <sub>0</sub>  | A <sub>1</sub>        | A <sub>2</sub>  | A <sub>3</sub>  | <b>A</b> <sub>4</sub> | A <sub>5</sub>  | A <sub>5</sub>  | A <sub>7</sub>  | Column Address |

| 2 <sup>nd</sup> cycle | A <sub>8</sub>  | <b>A</b> <sub>9</sub> | A <sub>10</sub> | A <sub>11</sub> | *L                    | *L              | *L              | *L              | Column Address |

| 3 <sup>rd</sup> cycle | A <sub>12</sub> | A <sub>13</sub>       | A <sub>14</sub> | A <sub>15</sub> | A <sub>16</sub>       | A <sub>17</sub> | A <sub>18</sub> | A <sub>19</sub> | Row Address    |

| 4 <sup>th</sup> cycle | A <sub>20</sub> | A <sub>21</sub>       | A <sub>22</sub> | A <sub>23</sub> | A <sub>24</sub>       | A <sub>25</sub> | A <sub>26</sub> | A <sub>27</sub> | Row Address    |

| 5 <sup>th</sup> cycle | A <sub>28</sub> | *L                    | *L              | *L              | *L                    | *L              | *L              | *L              | Row Address    |

#### Notes:

- 1. Column Address: Starting Address of the Register.

- 2. \*L must be set to "Low".

- 3. The device ignores any additional input of address cycles than required.

- 4. A<sub>18</sub> is for Plane Address setting.

## 4. OPERATION DESCRIPTION

The IS34/35ML02G081 is a 2Gbit memory organized as 128K rows (pages) by 2,112x8 columns. Spare 64x8 columns are located from column address of 2,048~2,111. A 2,112-byte data register is connected to memory cell arrays accommodating data transfer between the I/O buffers and memory during page read and page program operations. The program and read operations are executed on a page basis, while the erase operation is executed on a block basis. The memory array consists of 2,048 separately erasable 128K-byte blocks. It indicates that the bit-by-bit erase operation is prohibited on the IS34/35ML02G081.

The device has addresses multiplexed into 8 I/Os. This scheme dramatically reduces pin counts and allows system upgrades to future densities by maintaining consistency in system board design. Command, address and data are all written through I/O's by bringing WE# to low while CE# is low. Those are latched on the rising edge of WE#. Command Latch Enable (CLE) and Address Latch Enable (ALE) are used to multiplex command and address respectively, via the I/O pins. Some commands require one bus cycle. For example, Reset Command, Status Read Command, etc require just one cycle bus. Some other commands, like page read and block erase and page program, require two cycles: one cycle for setup and the other cycle for execution.

In addition to the enhanced architecture and interface, the device incorporates copy-back program feature from one page to another page without need for transporting the data to and from the external buffer memory.

## **Table 4.1 Command Set**

| Function                                   | 1 <sup>st</sup> Cycle | 2 <sup>nd</sup> Cycle | Acceptable Command during Busy |

|--------------------------------------------|-----------------------|-----------------------|--------------------------------|

| Read                                       | 00h                   | 30h                   |                                |

| Read for Copy-Back                         | 00h                   | 35h                   |                                |

| Read ID                                    | 90h                   | -                     |                                |

| Reset                                      | FFh                   | -                     | 0                              |

| Page Program                               | 80h                   | 10h                   |                                |

| Copy-Back Program                          | 85h                   | 10h                   |                                |

| Block Erase                                | 60h                   | D0h                   |                                |

| Random Data Input (1)                      | 85h                   | -                     |                                |

| Random Data Output (1)                     | 05h                   | E0h                   |                                |

| Read Status                                | 70h                   | -                     | 0                              |

| Read Status 2                              | F1h                   | -                     | 0                              |

| Two-Plane Read <sup>(3)</sup>              | 60h-60h               | 30h                   |                                |

| Two-Plane Read for Copy-Back               | 60h-60h               | 35h                   |                                |

| Two-Plane Random Data Output(1) (3)        | 00h-05h               | E0h                   |                                |

| Two-Plane Page Program <sup>(2)</sup>      | 80h-11h               | 81h-10h               |                                |

| Two-Plane Copy-Back Program <sup>(2)</sup> | 85h-11h               | 81h-10h               |                                |

| Two-Plane Block Erase                      | 60h-60h               | D0h                   |                                |

| Cache Program                              | 80h                   | 15h                   |                                |

| Cache Read                                 | 31h                   | -                     |                                |

| Read Start For Last Page Cache Read        | 3Fh                   | -                     |                                |

| Two-Plane Cache Read <sup>(3)</sup>        | 60h-60h               | 33h                   |                                |

| Two-Plane Cache Program <sup>(2)</sup>     | 80h-11h               | 81h-15h               |                                |

#### Notes:

- 1. Random Data Input/Output can be executed in a page.

- 2. Any command between 11h and 80h/81h/85h is prohibited except 70h/F1h and FFh.

- 3. Two-Plane Random Data Output must be used after Two-Plane Read operation or Two-Plane Cache Read operation.

# 5. ELECTRICAL CHARACTERISTICS

## 5.1 ABSOLUTE MAXIMUM RATINGS (1)

| Storage Temperature                                               | -65°C to +150°C                        |                 |  |

|-------------------------------------------------------------------|----------------------------------------|-----------------|--|

| Surface Mount Load Soldering Tomporature                          | Standard Package                       | 240°C 3 Seconds |  |

| Surface Mount Lead Soldering Temperature                          | Lead-free Package                      | 260°C 3 Seconds |  |

| Input Voltage with Respect to Ground on All Pins                  | -0.6V to +4.6V                         |                 |  |

| All I/O Voltage with Respect to Ground                            | All I/O Voltage with Respect to Ground |                 |  |

| Vcc                                                               | Vcc                                    |                 |  |

| Short Circuit Current                                             | 5mA                                    |                 |  |

| Electrostatic Discharge Voltage (Human Body Model) <sup>(2)</sup> | -2000V to +2000V                       |                 |  |

#### Notes:

- 1. Applied conditions greater than those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

- 2. ANSI/ESDA/JEDEC JS-001

## **5.2 RECOMMENDED OPERATING CONDITIONS**

| Part Number                                 | IS34/35ML02G081                       |

|---------------------------------------------|---------------------------------------|

| Operating Temperature (Industrial Grade)    | -40°C to 85°C                         |

| Operating Temperature (Extended Grade)      | -40°C to 105°C                        |

| Operating Temperature (Automotive Grade A1) | -40°C to 85°C                         |

| Operating Temperature (Automotive Grade A2) | -40°C to 105°C                        |

| V <sub>CC</sub> Power Supply                | 2.7V (VMIN) – 3.6V (VMAX); 3.3V (Typ) |

#### **5.3 DC CHARACTERISTICS**

(Under operating range)

|                           | Parameter                       | Symbol        | Test Conditions                               | Min     | Тур. | Max     | Unit |

|---------------------------|---------------------------------|---------------|-----------------------------------------------|---------|------|---------|------|

| Onenation                 | Page Read<br>with Serial Access | ICC1          | tRC=tRC <sub>Min</sub> ,<br>CE#=VIL, IOUT=0mA | -       | 15   |         |      |

| Operating<br>Current      | Program                         | ICC2          | -                                             | -       | 15   | 30 r    | mΑ   |

|                           | Erase                           | ICC3          | -                                             | -       | 15   |         | 1117 |

| Stand-by Cu               | rrent (TTL)                     | ISB1          | CE#=VIH, WP#=0V/VCC                           | -       | -    | 1       |      |

| Stand-by Cu               | irrent (CMOS)                   | ISB2          | CE#=VCC-0.2,<br>WP#=0V/VCC                    | -       | 10   | 50      |      |

| Input Leakage Current     |                                 | ILI           | VIN=0 to Vcc (max)                            | -       | ı    | +/-10   | uA   |

| Output Leak               | age Current                     | ILO           | VOUT=0 to Vcc (max)                           | -       | -    | +/-10   |      |

| Input High V              | oltage                          | VIH (1)       |                                               | 0.8xVCC | -    | Vcc+0.3 |      |

| Input Low Vo              | oltage, All inputs              | VIL (1)       |                                               | -0.3    | -    | 0.2xVCC |      |

| Output High Voltage Level |                                 | VOH           | IOH=-400 uA                                   | 2.4     | -    | -       | V    |

| Output Low Voltage Level  |                                 | VOL           | IOL=2.1mA                                     | -       | -    | 0.4     |      |

| Output Low                | Current (R/B#)                  | IOL<br>(R/B#) | VOL=0.4V                                      | 8       | 10   | -       | mA   |

#### Notes:

- 1. VIL can undershoot to -2.0V and VIH can overshoot to VCC + 2.0V for durations of 20 ns or less.

- 2. Typical value are measured at Vcc=3.3V, TA=25℃. Not 100% tested.

## **5.4 VALID BLOCK**

| Parameter       | Symbol | Min   | Тур. | Max   | Unit  |

|-----------------|--------|-------|------|-------|-------|

| IS34/35ML02G081 | NVB    | 2,008 | -    | 2,048 | Block |

#### Notes:

- 1. The device may include initial invalid blocks when first shipped. Additional invalid blocks may develop while being used. The number of valid blocks is presented with both cases of invalid blocks considered. Invalid blocks are defined as blocks that contain one or more bad bits which cause status failure during program and erase operation. Do not erase or program factory-marked bad blocks. Refer to the attached technical notes for appropriate management of initial invalid blocks.

- 2. The 1st block, which is placed on 00h block address, is guaranteed to be a valid block at the time of shipment and is guaranteed to be a valid block up to 1K program/erase cycles with 1bit/512Byte ECC.

## 5.5 AC MEASUREMENT CONDITION

| Symbol | Parameter                        | Min                      | Max | Units |

|--------|----------------------------------|--------------------------|-----|-------|

| CL     | Output Load                      | 1 TTL GATE and CL = 50pF |     | pF    |

| TR,TF  | Input Rise and Fall Times        |                          | 5   | ns    |

| VIN    | Input Pulse Voltages             | 0V to Vcc                |     | ٧     |

| VREFI  | Input Timing Reference Voltages  | 0.5V <sub>CC</sub>       |     | V     |

| VREFO  | Output Timing Reference Voltages | 0.5V <sub>CC</sub>       |     | V     |

#### Note:

1. Refer to 8.16 Ready/Busy#, R/B#'s Busy to Ready time is decided by pull up register (Rp) tied to R/B# pin.

# 5.6 AC PIN CAPACITANCE (TA = 25°C, VCC=3.3V, 1MHZ)

| Symbol           | Parameter                 | Test Condition        | Min | Тур | Max | Units |

|------------------|---------------------------|-----------------------|-----|-----|-----|-------|

| Cin              | Input Capacitance         | V <sub>IN</sub> = 0V  | -   | •   | 8   | pF    |

| C <sub>I/O</sub> | Input /Output Capacitance | V <sub>I/O</sub> = 0V | -   | -   | 8   | pF    |

## Note:

1. These parameters are characterized and not 100% tested.

## **5.7 MODE SELECTION**

| CLE | ALE              | CE# | WE# | RE# | WP#                               | Mode          |                         |  |  |  |  |

|-----|------------------|-----|-----|-----|-----------------------------------|---------------|-------------------------|--|--|--|--|

| Н   | L                | L   |     | Н   | X                                 | Read Mode     | Command Input           |  |  |  |  |

| L   | Н                | L   |     | Н   | Х                                 | Read Mode     | Address Input (5 clock) |  |  |  |  |

| Н   | L                | L   |     | Н   | Н                                 | Write Made    | Command Input           |  |  |  |  |

| L   | Н                | L   |     | Н   | Н                                 | Write Mode    | Address Input (5 clock) |  |  |  |  |

| L   | L                | L   |     | Н   | Н                                 | Data Input    |                         |  |  |  |  |

| L   | L                | L   | Н   |     | Х                                 | Data Output   |                         |  |  |  |  |

| Х   | Х                | Х   | Х   | Н   | Х                                 | During Read   | (Busy)                  |  |  |  |  |

| Х   | Х                | Х   | Х   | Х   | Н                                 | During Progra | am (Busy)               |  |  |  |  |

| Х   | Х                | Х   | Х   | Х   | Н                                 | During Erase  | (Busy)                  |  |  |  |  |

| Х   | X <sup>(1)</sup> | Х   | Х   | Х   | L                                 | Write Protect |                         |  |  |  |  |

| Х   | Х                | Н   | Х   | Х   | 0V/V <sub>CC</sub> <sup>(2)</sup> | Stand-by      |                         |  |  |  |  |

## Notes:

- X can be VIL or VIH.

WP# should be biased to CMOS high or CMOS low for standby.

## 5.8 ROGRAM/ERASE PERFORMANCNE

(Industrial:  $T_A$ =-40 to 85°C, Automotive, A1:  $T_A$ =-40 to 85°C, Vcc=2.7V ~ 3.6V)

| Parameter                                         | Symbol | Min | Тур | Max | Unit  |

|---------------------------------------------------|--------|-----|-----|-----|-------|

| Average Program Time                              | tPROG  | -   | 400 | 950 | us    |

| Dummy Busy Time for Cache Operation               | tCBSY  | -   | 3   | 950 | us    |

| Number of Partial Program Cycles in the Same Page | Nop    | -   | -   | 4   | cycle |

| Block Erase Time                                  | tBERS  | -   | 2   | 10  | ms    |

| Dummy Busy Time for Two-Plane Page Program        | tDBSY  | -   | 0.5 | 1   | us    |

#### Notes:

- 1. Typical program time is defined as the time within which more than 50% of the whole pages are programmed at 3.3V Vcc and 25°C temperature.

- tPROG is the average program time of all pages. Users should be noted that the program time variation from page to page is possible.

- 3. tCBSY max.time depends on timing between internal program completion and data-in.

## 5.9 AC CHARACTERISTICS FOR ADDRESS/ COMMAND/DATA INPUT

| Parameter                    | Symbol              | Min               | Max | Unit |

|------------------------------|---------------------|-------------------|-----|------|

| CLE Setup Time               | tCLS <sup>(1)</sup> | 12                | -   | ns   |

| CLE Hold Time                | tCLH                | 5                 | -   | ns   |

| CE# Setup Time               | tCS <sup>(1)</sup>  | 20                | -   | ns   |

| CE# Hold Time                | tCH                 | 5                 | -   | ns   |

| WE# Pulse Width              | tWP                 | 12                | -   | ns   |

| ALE Setup Time               | tALS <sup>(1)</sup> | 12                | -   | ns   |

| ALE Hold Time                | tALH                | 5                 | 1   | ns   |

| Data Setup Time              | tDS <sup>(1)</sup>  | 12                | -   | ns   |

| Data Hold Time               | tDH                 | 5                 | -   | ns   |

| Write Cycle Time             | tWC                 | 25                | -   | ns   |

| WE# High Hold Time           | tWH                 | 10                | -   | ns   |

| Address to Data Loading Time | tADL <sup>(2)</sup> | 70 <sup>(2)</sup> | -   | ns   |

#### Note:

- 1. The transition of the corresponding control pins must occur only once while WE# is held low.

- 2. tADL is the time from the WE rising edge of final address cycle to the WE# rising edge of first data cycle.

# 5.10 AC CHARACTERISTICS FOR OPERATION

| Parameter                                        | Symbol  | Min | Max   | Unit |

|--------------------------------------------------|---------|-----|-------|------|

| Data Transfer from Cell to Register              | tR      | -   | 25    | us   |

| ALE to RE# Delay                                 | tAR     | 10  | -     | ns   |

| CLE to RE# Delay                                 | tCLR    | 10  | -     | ns   |

| Ready to RE# Low                                 | tRR     | 20  | -     | ns   |

| RE# Pulse Width                                  | tRP     | 12  | -     | ns   |

| WE# High to Busy                                 | tWB     | -   | 100   | ns   |

| WP# Low to WE# Low (disable mode)                | 4\4\4   | 400 |       | 20   |

| WP# High to WE# Low (enable mode)                | tWW     | 100 | -     | ns   |

| Read Cycle Time                                  | tRC     | 25  | -     | ns   |

| RE# Access Time                                  | tREA    | -   | 20    | ns   |

| CE# Access Time                                  | tCEA    | -   | 25    | ns   |

| RE# High to Output Hi-Z                          | tRHZ    | -   | 100   | ns   |

| CE# High to Output Hi-Z                          | tCHZ    | -   | 30    | ns   |

| CE# High to ALE or CLE Don't care                | tCSD    | 0   |       | ns   |

| RE# High to Output Hold                          | tRHOH   | 15  | -     | ns   |

| RE# Low to Output Hold                           | tRLOH   | 5   |       | ns   |

| CE# High to Output Hold                          | tCOH    | 15  | -     | ns   |

| RE# High Hold Time                               | tREH    | 10  | -     | ns   |

| Output Hi-Z to RE# Low                           | tIR     | 0   | -     | ns   |

| RE# High to WE# Low                              | tRHW    | 100 | -     | ns   |

| WE# High to RE# Low                              | tWHR    | 60  | -     | ns   |

| Device Read                                      |         | -   | 5     | us   |

| Resetting Program                                | 4D0T    | -   | 10    | us   |

| Time Erase                                       | tRST    | -   | 500   | us   |

| during Ready                                     | [       | -   | 5 (1) | us   |

| Cache Busy in Read Cache (following 31h and 3Fh) | tDCBSYR | -   | 30    | us   |

Note: If reset command (FFh) is written at Ready state, the device goes into Busy for maximum 5us.

# 6. TIMING DIAGRAMS

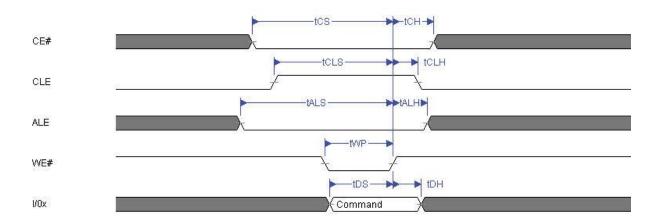

# **6.1 COMMAND LATCH CYCLE**

Figure 6.1 Command Latch Cycle

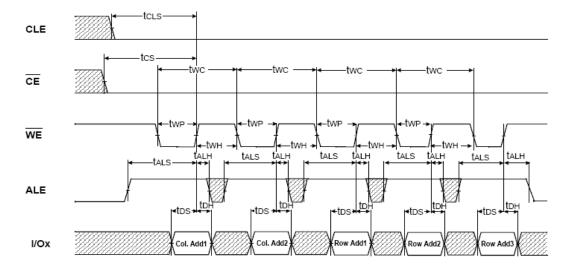

# **6.2 ADDRESS LATCH CYCLE**

Figure 6.2 Address Latch Cycle

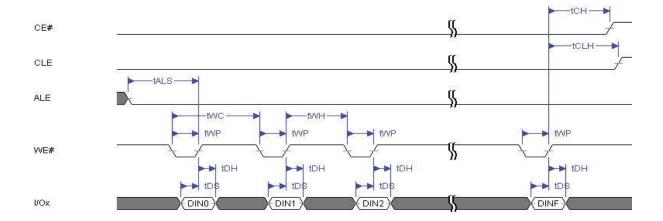

## **6.3 INPUT DATA LATCH CYCLE**

Figure 6.3 Input Data Latch Cycle

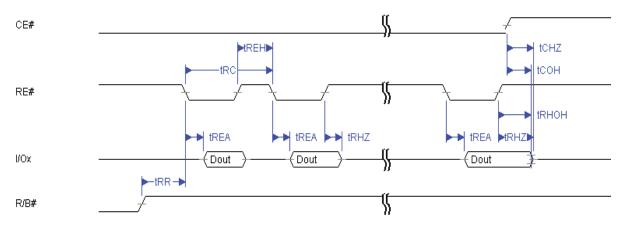

# 6.4 SERIAL ACCESS CYCLE AFTER READ (CLE=L, WE#=H, ALE=L)

#### Note:

- Dout transition is measured at ±200mV from steady state voltage at I/O with load.

- 2. trhoh starts to be valid when frequency is lower than 33MHz.

Figure 6.4 Serial Access Cycle after Read

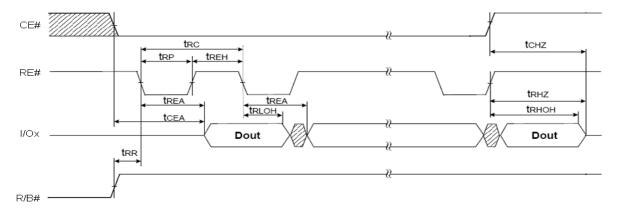

# 6.5 SERIAL ACCESS CYCLE AFTER READ (EDO TYPE CLE=L, WE#=H, ALE=L)

#### Note:

- 1. Transition is measured at +/-200mV from steady state voltage with load.

- This parameter is sample and not 100% tested. (tCHZ, tRHZ)

- tRLOH is valid when frequency is higher than 33MHZ. tRHOH starts to be valid

Figure 6.5 Serial Access Cycle after Read (EDO Type CLE=L, WE#=H, ALE=L)

## **6.6 STATUS READ CYCLE**

Figure 6.6 Status Read Cycle

# **6.7 READ OPERATION (ONE PAGE)**

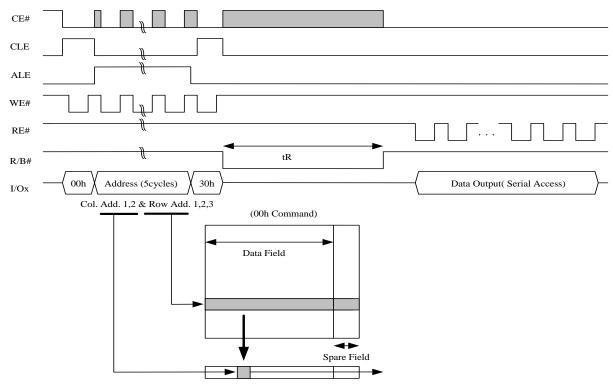

Figure 6.7 Read Operation (One Page)

# 6.8 READ OPERATION (INTERCEPTED BY CE#)

Figure 6.8 Read Operation (Intercepted by CE#)

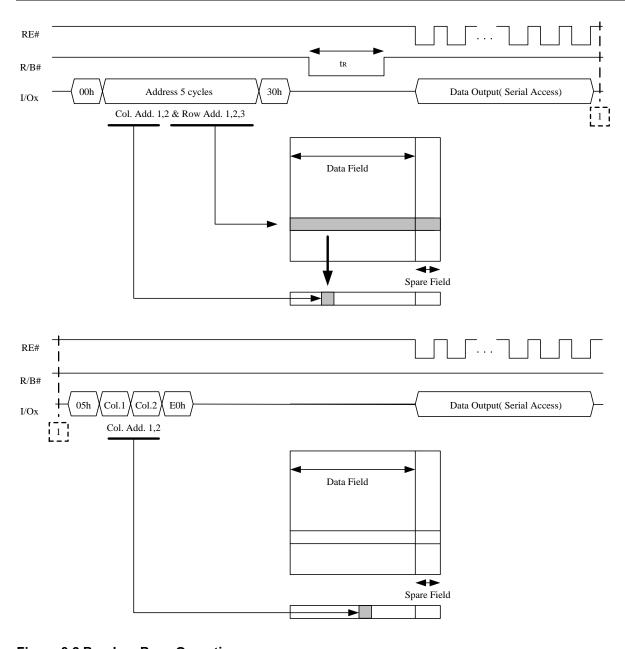

# **6.9 RANDOM DATA OUTPUT IN A PAGE**

Figure 6.9 Random Data Output in a Page

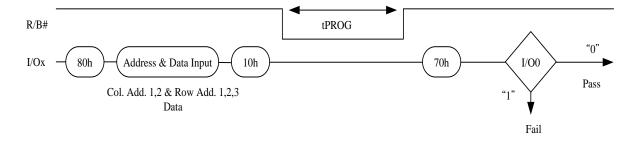

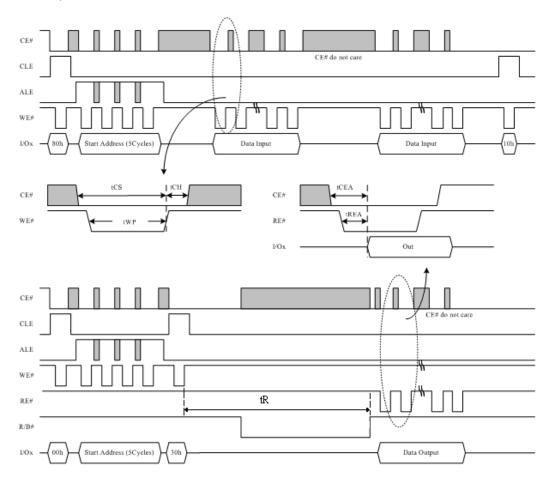

# **6.10 PAGE PROGRAM OPERATION**

**Figure 6.10 Page Program Operation**

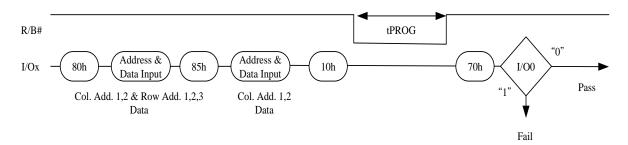

## 6.11 PAGE PROGRAM OPERATION WITH RANDOM DATA INPUT

Note: table is the time from the WE# rising edge of final address cycle to the WE# rising edge of the first data cycle.

Figure 6.11 Page Program Operation with Random Data Input

# 6.12 COPY-BACK OPERATION WITH RANDOM DATA INPUT

Figure 6.12 Copy-Back Operation with Random Data Input

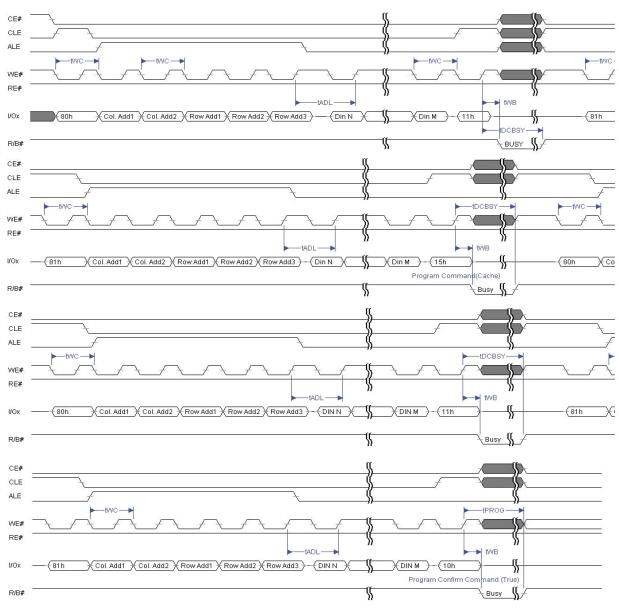

## **6.13 CACHE PROGRAM OPERATION**

Figure 6.13 Cache Program Operation

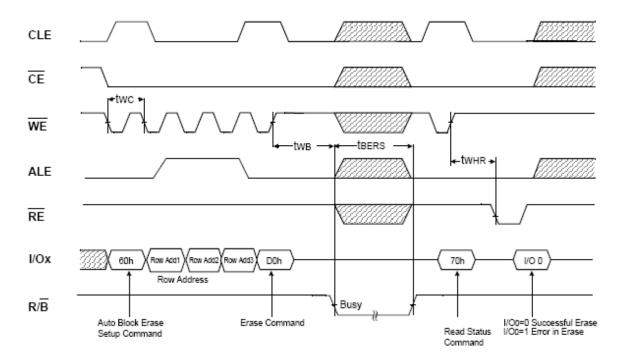

# **6.14 BLOCK ERASE OPERATION**

Figure 6.14. Block Erase Operation

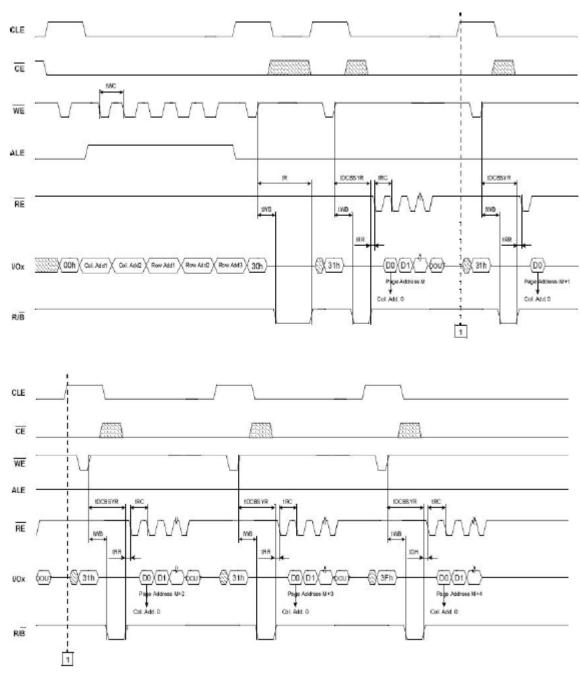

## **6.15 CACHE READ OPERATION**

Figure 6.15.Cache Read Operation

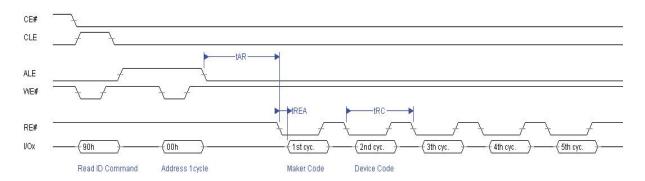

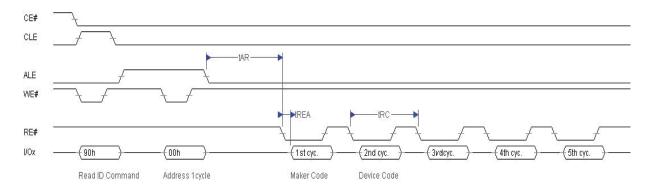

# **6.16 READ ID OPERATION**

Figure 6.16 Read ID Operation

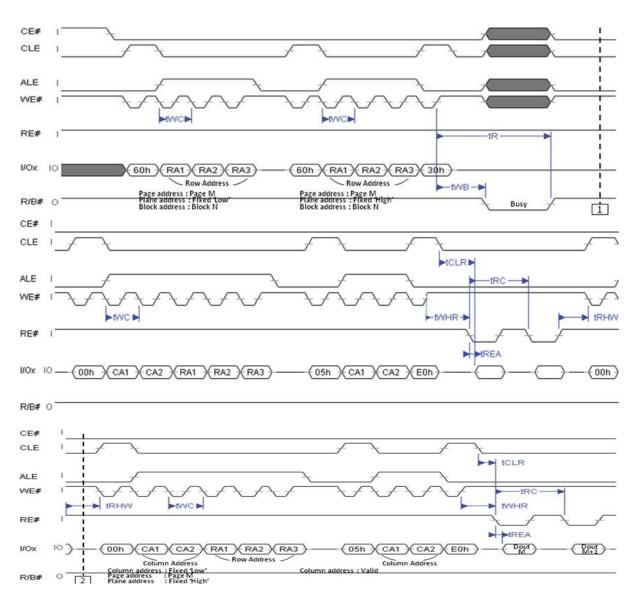

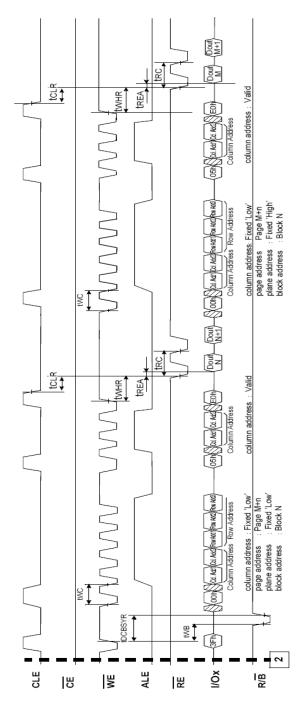

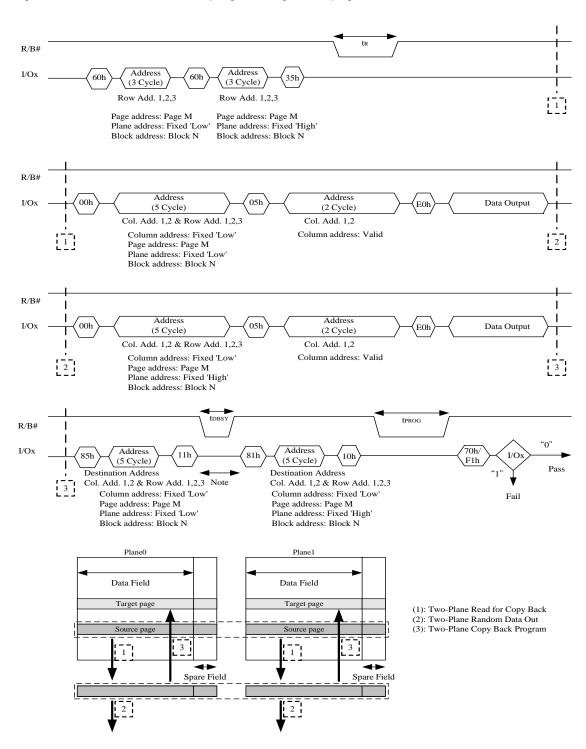

# 6.17 TWO-PLANE PAGE READ OPERATION WITH TWO-PLANE RANDOM DATA OUT

Figure 6.17 Two Plane Page Read Operation with Two-Plane Random Data Out

## 6.18 TWO-PLANE CACHE READ OPERATION

#### Notes:

- 1. The column address will be reset to 0 by the 3Fh command input.

- 2. Cache Read operation is available only within a block.

- 3. Make sure to terminate the operation with 3Fh command. If the operation is terminated by 31h command, monitor I/O6 (Ready/Busy) by issuing Status Read Command (70h) and make sure the previous page read operation is completed. If the page read operation is completed, issue FFh reset before next operation.

Figure 6.18 Two-Plane Cache Read Operation

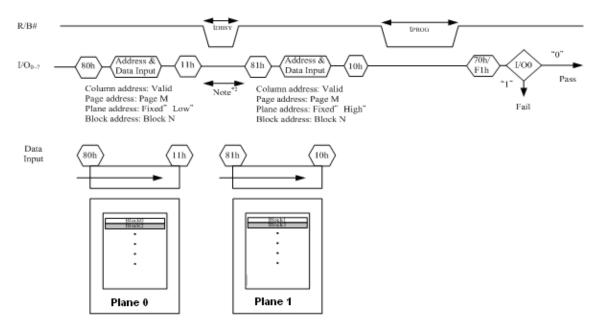

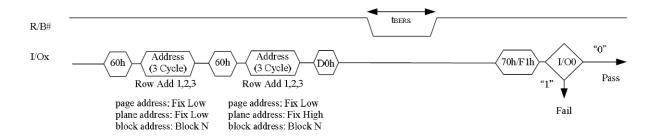

# **6.19 TWO-PLANE PAGE PROGRAM OPERATION**

Figure 6.19 Two-Plane Page Program Operation

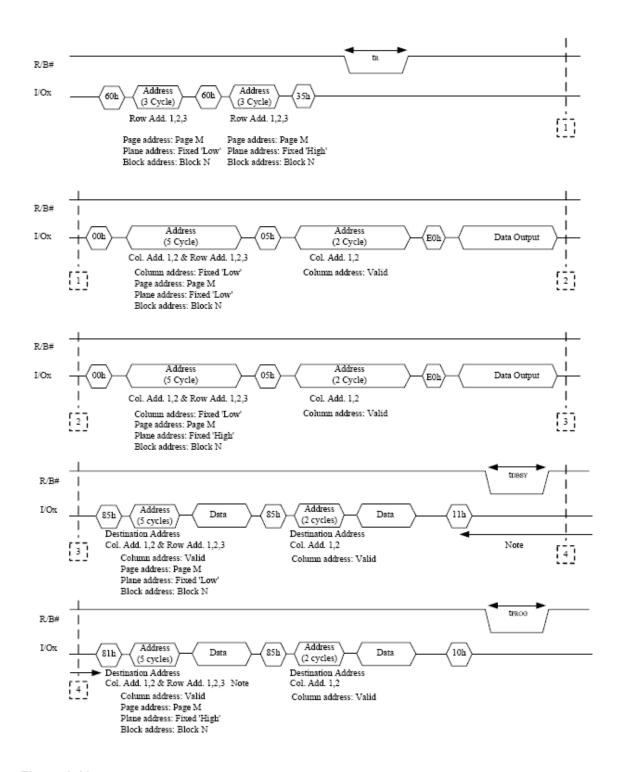

# 6.20 TWO-PLANE CACHE PROGRAM OPERATION

Figure 6.20 Two-Plane Cache Program Operation

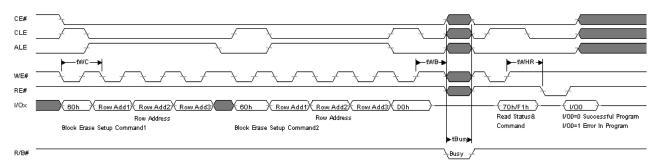

# 6.21 READ TWO PLANE BLOCK ERASE OPERATION

Figure 6.21 Two-Plane Block Erase Operation

# 7. ID Definition Table

# 90 ID: Access command = 90H

| Part No.            | 1 <sup>st</sup> Cycle<br>(Maker<br>Code) | 2 <sup>nd</sup> Cycle<br>(Device Code) | 3 <sup>rd</sup> Cycle | 4 <sup>th</sup> Cycle | 5 <sup>th</sup> Cycle | 6 <sup>th</sup> ~ 8 <sup>th</sup> Cycle |

|---------------------|------------------------------------------|----------------------------------------|-----------------------|-----------------------|-----------------------|-----------------------------------------|

| IS34/35ML02G081(X8) | C8h                                      | DAh                                    | 90h                   | 95h                   | 46h                   | 7Fh                                     |

|                      | Description                             |

|----------------------|-----------------------------------------|

| 1st Byte             | Maker Code                              |

| 2 <sup>nd</sup> Byte | Device Code                             |

| 3 <sup>rd</sup> Byte | Internal Chip Number, Cell Type, etc    |

| 4 <sup>th</sup> Byte | Page Size, Block Size, etc              |

| 5 <sup>th</sup> Byte | Plane Number, Plane Size, ECC Level     |

| 6th Byte             | JEDEC Maker Code Continuation Code, 7Fh |

| 7 <sup>th</sup> Byte | JEDEC Maker Code Continuation Code, 7Fh |

| 8 <sup>th</sup> Byte | JEDEC Maker Code Continuation Code, 7Fh |

# 3<sup>rd</sup> ID Data

| Item                   | Description   | 1/07 | I/O6 | I/O5 | I/O4 | I/O3 | I/O2 | I/O1 | I/O0 |

|------------------------|---------------|------|------|------|------|------|------|------|------|

| Internal Chip Number   | 1             |      |      |      |      |      |      | 0    | 0    |

|                        | 2             |      |      |      |      |      |      | 0    | 1    |

|                        | 4             |      |      |      |      |      |      | 1    | 0    |

|                        | 8             |      |      |      |      |      |      | 1    | 1    |

| Cell Type              | 2 Level Cell  |      |      |      |      | 0    | 0    |      |      |

|                        | 4 Level Cell  |      |      |      |      | 0    | 1    |      |      |

|                        | 8 Level Cell  |      |      |      |      | 1    | 0    |      |      |

|                        | 16 Level Cell |      |      |      |      | 1    | 1    |      |      |

| Number of              | 1             |      |      | 0    | 0    |      |      |      |      |

| Simultaneously         | 2             |      |      | 0    | 1    |      |      |      |      |

| Programmed Pages       | 4             |      |      | 1    | 0    |      |      |      |      |

|                        | 8             |      |      | 1    | 1    |      |      |      |      |

| Interleave Program     | Not Support   |      | 0    |      |      |      |      |      |      |

| Between Multiple Chips | Support       |      | 1    |      |      |      |      |      |      |

| Cache Program          | Not Support   | 0    |      |      |      |      |      |      |      |

|                        | Support       | 1    |      |      |      |      |      |      |      |

# 4th ID Data

| Item                 | Description | 1/07 | I/O6 | I/O5 | I/O4 | I/O3 | I/O2 | I/O1 | I/O0 |

|----------------------|-------------|------|------|------|------|------|------|------|------|

| Page Size            | 1KB         |      |      |      |      |      |      | 0    | 0    |

| (w/o redundant area) | 2KB         |      |      |      |      |      |      | 0    | 1    |

|                      | 4KB         |      |      |      |      |      |      | 1    | 0    |

|                      | 8KB         |      |      |      |      |      |      | 1    | 1    |

| Redundant Area Size  | 8           |      |      |      |      |      | 0    |      |      |

| (Byte/512Byte)       | 16          |      |      |      |      |      | 1    |      |      |

| Block Size           | 64KB        |      |      | 0    | 0    |      |      |      |      |

| (w/o redundant area) | 128KB       |      |      | 0    | 1    |      |      |      |      |

|                      | 256KB       |      |      | 1    | 0    |      |      |      |      |

|                      | 512KB       |      |      | 1    | 1    |      |      |      |      |

| Organization         | X8          |      | 0    |      |      |      |      |      |      |

|                      | X16         |      | 1    |      |      |      |      |      |      |

|                      | 45ns        | 0    |      |      |      | 0    |      |      |      |

| Carial Assass Time   | Reserved    | 0    |      |      |      | 1    |      |      |      |

| Serial Access Time   | 25ns        | 1    |      |      |      | 0    |      |      |      |

|                      | Reserved    | 1    |      |      |      | 1    |      |      |      |

# 5<sup>th</sup> ID Data

| Item                         | Description | 1/07 | I/O6 | I/O5 | I/O4 | I/O3 | I/O2 | I/O1 | I/O0 |

|------------------------------|-------------|------|------|------|------|------|------|------|------|

| ECC Level                    | 4bit/512B   |      |      |      |      |      |      | 0    | 0    |

|                              | 2bit/512B   |      |      |      |      |      |      | 0    | 1    |

|                              | 1bit/512B   |      |      |      |      |      |      | 1    | 0    |

|                              | Reserved    |      |      |      |      |      |      | 1    | 1    |

| Plane Number                 | 1           |      |      |      |      | 0    | 0    |      |      |

|                              | 2           |      |      |      |      | 0    | 1    |      |      |

|                              | 4           |      |      |      |      | 1    | 0    |      |      |

|                              | 8           |      |      |      |      | 1    | 1    |      |      |

| Plane Size(without Redundant | 64Kb        |      | 0    | 0    | 0    |      |      |      |      |

| Area)                        | 128Kb       |      | 0    | 0    | 1    |      |      |      |      |

|                              | 256Kb       |      | 0    | 1    | 0    |      |      |      |      |

|                              | 512Kb       |      | 0    | 1    | 1    |      |      |      |      |

|                              | 1Gb         |      | 1    | 0    | 0    |      |      |      |      |

|                              | 2Gb         |      | 1    | 0    | 1    |      |      |      |      |

|                              | 4Gb         |      | 1    | 1    | 0    |      |      |      |      |

|                              | 8Gb         |      | 1    | 1    | 1    |      |      |      |      |

| Reserved                     | Reserved    | 0    |      |      |      |      |      |      |      |

# 6th ~ 8th ID Data

| Item                               | Description | I/O7 | 1/06 | 1/05 | I/O4 | I/O3 | I/O2 | I/O1 | I/O0 |

|------------------------------------|-------------|------|------|------|------|------|------|------|------|

| JEDEC Maker Code Continuation Code | 7F          | 0    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

## 8. DEVICE OPERATION

#### **8.1 PAGE READ OPERATION**

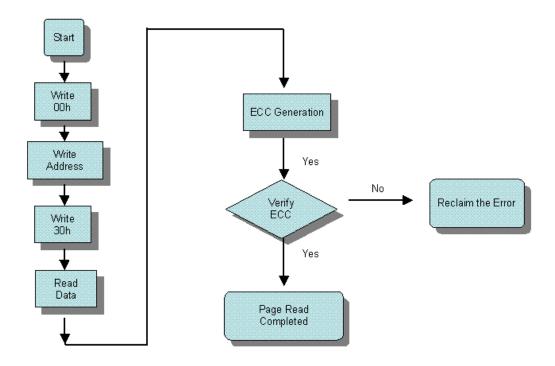

Upon initial device power up, the device defaults to Read mode. This operation is also initiated by writing 00h command, five-cycle address, and 30h command. After initial power up, the 00h command can be skipped because it has been latched in the command register. The 2,112Byte of data on a page are transferred to cache registers via data registers within 25us (tR). Host controller can detect the completion of this data transfer by checking the R/B# output. Once data in the selected page have been loaded into cache registers, each Byte can be read out in 25ns cycle time by continuously pulsing RE#. The repetitive high-to-low transitions of RE# clock signal make the device output data starting from the designated column address to the last column address.

The device can output data at a random column address instead of sequential column address by using the Random Data Output command. Random Data Output command can be executed multiple times in a page.

After power up, device is in read mode so 00h command cycle is not necessary to start a read operation.

A page read sequence is illustrated in Figure below, where column address, page address are placed in between commands 00h and 30h. After tR read time, the R/B# de-asserts to ready state. Read Status command (70h) can be issued right after 30h. Host controller can toggle RE# to access data starting with the designated column address and their successive bytes.

Figure 8.1 Read Operation

**Figure 8.2 Random Page Operation**

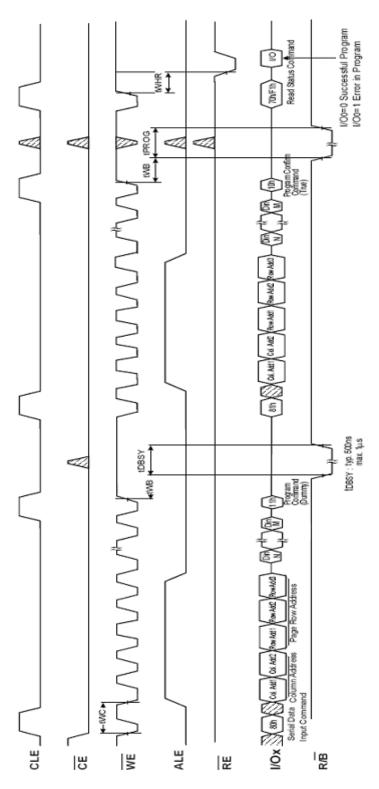

#### **8.2 PAGE PROGRAM**

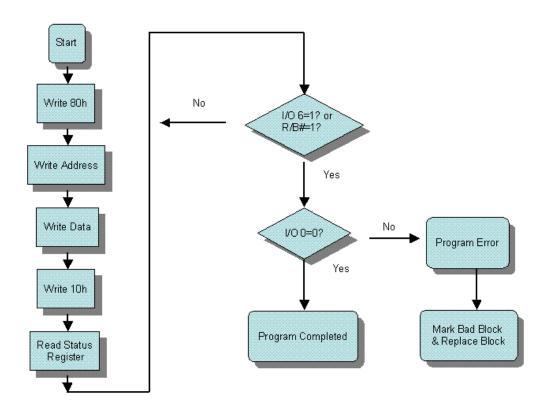

The device is programmed based on the unit of a page, and consecutive partial page programming on one page without intervening erase operation is strictly prohibited. Addressing of page program operations within a block should be in sequential order. A complete page program cycle consists of a serial data input cycle in which up to 2,112byteof data can be loaded into data register via cache register, followed by a programming period during which the loaded data are programmed into the designated memory cells.

The serial data input cycle begins with the Serial Data Input command (80h), followed by a five-cycle address input and then serial data loading. The bytes not to be programmed on the page do not need to be loaded. The column address for the next data can be changed to the address follows Random Data Input command (85h). Random Data Input command may be repeated multiple times in a page. The Page Program Confirm command (10h) starts the programming process. Writing 10h alone without entering data will not initiate the programming process. The internal write engine automatically executes the corresponding algorithm and controls timing for programming and verification, thereby freeing the host controller for other tasks. Once the program process starts, the host controller can detect the completion of a program cycle by monitoring the R/B# output or reading the Status bit (I/O6) using the Read Status command. Only Read Status and Reset commands are valid during programming. When the Page Program operation is completed, the host controller can check the Status bit (I/O0) to see if the Page Program operation is successfully done. The command register remains the Read Status mode unless another valid command is written to it.

A page program sequence is illustrated in Figure below, where column address, page address, and data input are placed in between 80h and 10h. After tPROG program time, the R/B# de-asserts to ready state. Read Status command (70h) can be issued right after 10h.

Figure 8.3 Program and Read Status Operation

Figure 8.4 Random Data Input In a Page

### **8.3 CACHE PROGRAM**

The Cache Program is an extension of Page Program, which is executed with 2,112 byte(x8) data registers, and is available only within a block. Since the device has 1 page of cache memory, serial data input may be executed while data stored in data register are programmed into memory cell.

After writing the first set of data up to 2,112 bytes(x8) into the selected cache registers, Cache Program command (15h) instead of actual Page Program (10h) is inputted to make cache registers free and to start internal program operation. To transfer data from cache registers to data registers, the device remains in Busy state for a short period of time (tcbsy) and has its cache registers ready for the next data-input while the internal programming gets started with the data loaded into data registers. Read Status command (70h) may be issued to find out when cache registers become ready by polling the Cache-Busy status bit (I/O6). Pass/fail status of only the previous page is available upon the return to Ready state. When the next set of data is inputted with the Cache Program command, tCBSY is affected by the progress of pending internal programming. The programming of the cache registers is initiated only when the pending program cycle is finished and the data registers are available for the transfer of data from cache registers. The status bit (I/O5) for internal Ready/Busy may be polled to identity the completion of internal programming. If the system monitors the progress of programming only with R/B#, the last page of the target programming sequence must be programmed with actual Page Program command (10h).

### NOTE:

- Since programming the last page does not employ caching, the program time has to be that of Page Program. However,

if the previous program cycle with the cache data has not finished, the actual program cycle of the last page is initiated

only after completion of the previous cycle, which can be expressed as the following formula.

- 2. tprogram time for the last page + Program time for the (last-1)th page (Program command cycle time + Last page data loading time)

Figure 8.5 Fast Cache Program (Available only within a Block)

#### 8.4 COPY-BACK PROGRAM

Copy-Back Program is designed to efficiently copy data stored in memory cells without time-consuming data reloading when there is no bit error detected in the stored data. The benefit is particularly obvious when a portion of a block is updated and the rest of the block needs to be copied to a newly assigned empty block. Copy-Back operation is a sequential execution of Read for Copy-Back and of Copy-Back Program with Destination address. A Read for Copy-Back operation with "35h" command and the Source address moves the whole 2,112byte data into the internal buffer. The host controller can detect bit errors by sequentially reading the data output. Copy-Back Program is initiated by issuing Page-Copy Data-Input command (85h) with Destination address. If data modification is necessary to correct bit errors and to avoid error propagation, data can be reloaded after the Destination address. Data modification can be repeated multiple times as shown in Figure below. Actual programming operation begins when Program Confirm command (10h) is issued. Once the program process starts, the Read Status command (70h) may be entered to read the status register. The host controller can detect the completion of a program cycle by monitoring the R/B# output, or the Status bit (I/O6) of the Status Register. When the Copy-Back Program is complete, the Status Bit (I/O0) may be checked. The command register remains Read Status mode until another valid command is written to it.

Figure 8.6 Page Copy-Back Program Operation

Figure 8.7 Page Copy-Back Program Operation with Random Data Input

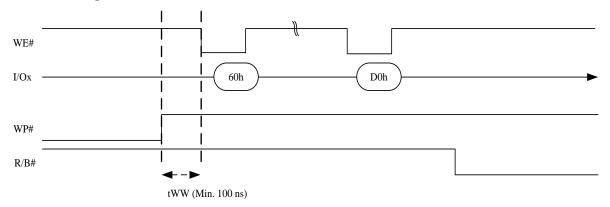

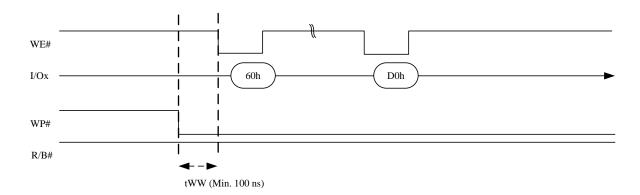

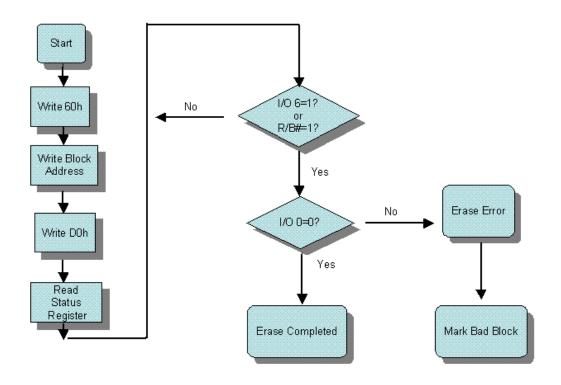

### **8.5 BLOCK ERASE**

The block-based Erase operation is initiated by an Erase Setup command (60h), followed by a three-cycle row address, in which only Plane address and Block address are valid while Page address is ignored. The Erase Confirm command (D0h) following the row address starts the internal erasing process. The two-step command sequence is designed to prevent memory content from being inadvertently changed by external noise.

At the rising edge of WE# after the Erase Confirm command input, the internal control logic handles erase and erase-verify. When the erase operation is completed, the host controller can check Status bit (I/O0) to see if the erase operation is successfully done. Figure below illustrates a block erase sequence, and the address input (the first page address of the selected block) is placed in between commands 60h and D0h. After tBERS erase time, the R/B# de-asserts to ready state. Read Status command (70h) can be issued right after D0h to check the execution status of erase operation.

Figure 8.8 Block Erase Operation

#### **8.6 READ STATUS**

A status register on the device is used to check whether program or erase operation is completed and whether the operation is completed successfully. After writing 70h/F1h command to the command register, a read cycle outputs the content of the status register to I/O pins on the falling edge of CE# or RE#, whichever occurs last. These two commands allow the system to poll the progress of each device in multiple memory connections even when R/B# pins are common-wired. RE# or CE# does not need to toggle for status change.

The command register remains in Read Status mode unless other commands are issued to it. Therefore, if the status register is read during a random read cycle, a read command (00h) is needed to start read cycles.

Table 8.1 Status Register Definition for 70h Command

| I/O   | Page Program          | Block Erase   | Cache Program      | Read          | Cache Read         | Definition                        |

|-------|-----------------------|---------------|--------------------|---------------|--------------------|-----------------------------------|

| I/O 0 | Pass/Fail             | Pass/Fail     | Pass/Fail(N)       | NA            | NA                 | Pass : 0<br>Fail : 1              |

| I/O 1 | NA                    | NA            | Pass/ Fail (N-1)   | NA            | NA                 | Don't cared                       |

| I/O 2 | NA<br>(Pass/Fail,OTP) | NA            | NA                 | NA            | NA                 | Don't cared                       |

| I/O 3 | NA                    | NA            | NA                 | NA            | NA                 | Don't cared                       |

| I/O 4 | NA                    | NA            | NA                 | NA            | NA                 | Don't cared                       |

| I/O 5 | NA                    | NA            | True<br>Ready/Busy | NA            | True<br>Ready/Busy | Busy : 0<br>Ready : 1             |

| I/O 6 | Ready/Busy            | Ready/Busy    | Ready/Busy         | Ready/Busy    | Ready/Busy         | Busy : 0<br>Ready : 1             |

| I/O 7 | Write Protect         | Write Protect | Write Protect      | Write Protect | Write Protect      | Protected :0<br>Not Protected : 1 |

Table 8.2 Status Register Definition for F1h Command

| I/O   | Page Program        | Block Erase         | Cache Program         | Read             | Cache Read         | Definition                         |

|-------|---------------------|---------------------|-----------------------|------------------|--------------------|------------------------------------|

| I/O 0 | Chip Pass/Fail      | Chip Pass/Fail      | Chip Pass/Fail(N)     | NA               | NA                 | Pass : 0<br>Fail : 1               |

| I/O 1 | Plane0<br>Pass/Fail | Plane0<br>Pass/Fail | Plane0 Pass/Fail(N)   | NA               | NA                 | Pass : 0<br>Fail : 1               |

| I/O 2 | Plane1<br>Pass/Fail | Plane1<br>Pass/Fail | Plane1 Pass/Fail(N)   | NA               | NA                 | Pass : 0<br>Fail : 1               |

| I/O 3 | NA                  | NA                  | Plane0 Pass/Fail(N-1) | NA               | NA                 | Pass : 0<br>Fail : 1               |

| I/O 4 | NA                  | NA                  | Plane1 Pass/Fail(N-1) | NA               | NA                 | Pass : 0<br>Fail : 1               |

| I/O 5 | NA                  | NA                  | True Ready/Busy       | NA               | True<br>Ready/Busy | Busy : 0<br>Ready : 1              |

| I/O 6 | Ready/Busy          | Ready/Busy          | Ready/Busy            | Ready/Busy       | Ready/Busy         | Busy : 0<br>Ready : 1              |

| I/O 7 | Write Protect       | Write Protect       | Write Protect         | Write<br>Protect | Write Protect      | Protected : 0<br>Not Protected : 1 |

#### Note:

- 1. I/Os defined NA are recommended to be masked out when Read Status is being executed.

- 2. N = current page, n-1 = previous page.

### 8.7 READ ID

The device contains a product identification mode, initiated by writing 90h to the command register, followed by an address input of 00h. Five read cycles sequentially output the manufacturer code (C8h), and the device code and 3<sup>rd</sup>, 4<sup>th</sup>, 5<sup>th</sup> cycle ID respectively. The command register remains in Read ID mode until further commands are issued to it.

Figure 8.9 Read ID Operation

**Table 8.3 ID definition Table**

| Part No.            | 1 <sup>st</sup> Cycle<br>(Maker Code) | 2 <sup>nd</sup> Cycle<br>(Device Code) | 3 <sup>rd</sup> Cycle | 4 <sup>th</sup> Cycle | 5 <sup>th</sup> Cycle |

|---------------------|---------------------------------------|----------------------------------------|-----------------------|-----------------------|-----------------------|

| IS34/35ML02G081(X8) | C8h                                   | DAh                                    | 90h                   | 95h                   | 46h                   |

### **8.8 RESET**

The device offers a reset feature, executed by writing FFh to the command register. When the device is in Busy state during random read, program or erase mode, the reset operation will abort these operations. The contents of memory cells being altered are no longer valid, as the data will be partially programmed or erased. The command register is cleared to wait for the next command, and the Status Register is cleared to value C0h when WP# is high. If the device is already in reset state a new reset command will be accepted by the command register. The R/B# pin changes to low for tRST after the Reset command is written. Refer to Figure below.

Figure 8.10 Reset Operation

**Table 8.4 Device Status Table**

|                | After Power-up         | After Reset              |

|----------------|------------------------|--------------------------|

| Operation Mode | 00h Command is latched | Waiting for next command |

### 8.9 CACHE READ

Cache Read is an extension of Page Read, and is available only within a block. The normal Page Read command (00h-30h) is always issued before invoking Cache Read. After issuing the Cache Read command (31h), read data of the designated page (page N) are transferred from data registers to cache registers in a short time period of tDCBSYR, and then data of the next page (page N+1) is transferred to data registers while the data in the cache registers are being read out. Host controller can retrieve continuous data and achieve fast read performance by iterating Cache Read operation. The Read Start for Last Page Cache Read command (3Fh) is used to complete data transfer from memory cells to data registers.

Figure 8.11 Read Operation with Cache Read

### 8.10 TWO-PLANE PAGE READ

Two-Plane Page Read is an extension of Page Read, for a single plane with 2,112 byte data registers. Since the device is equipped with two memory planes, activating the two sets of 2,112 byte data registers enables a random read of two pages. Two-Plane Page Read is initiated by repeating command 60h followed by three address cycles twice. In this case, only same page of same block can be selected from each plane.

After Read Confirm command(30h) the 4,224 bytes of data within the selected two page are transferred to the cache registers via data registers in less than 25us(tR). The system controller can detect the completion of data transfer (tR) by monitoring the output of R/B pin.

Once the data is loaded into the cache registers, the data output of first plane can be read out by issuing command 00h with five address cycles, command 05h with two column address and finally E0h. The data output of second plane can be read out using the identical command sequences.

Figure 8.12 Two-Plane Page Read

## **8.11 TWO-PLANE CACHE READ**

Figure 8.13 Two-Plane Cache Read

### **8.12 TWO-PLANE PAGE PROGRAM**

Two-Plane Page Program is an extension of Page Program, for a single plane with 2,112 byte data registers. Since the device is equipped with two memory planes, activating the two sets of 2112 byte data registers enables a simultaneous programming of two pages.

After writing the first set of data up to 2,112 byte into the selected data registers via cache registers, Dummy Page Program command (11h) instead of actual Page Program command (10h) is inputted to finish data-loading of the first plane. Since no programming process is involved, R/B remains in busy state for a short period of time (tDBSY). Read Status command (70h) may be issued to find out when the device returns to ready state by polling the R/B status bit (I/O 6). Then the next set of data for the other plane is inputted after 81h command and address sequences. After inputting data for the last page, actual True Page Program (10h) instead of dummy Page Program command (11h) must be followed to start the programming process. The operation of R/B and Read Status is the same as that of Page Program. Although two planes are programmed simultaneously, pass/fail is not available for each page when the program operation completes. Status bit of I/O 0 is set to "1" when any of the pages fails.

Figure 8.14 Two-Plane Page Program

### 8.13 TWO-PLANE COPY BACK PROGRAM

Two-Plane Copy-Back Program is an extension of Copy-Back Program, for a single plane with 2,112 byte data registers. Since the device is equipped with two memory planes, activating the two sets of 2,112 byte data registers enables a simultaneous programming of two pages.

Figure 8.15 Two-Plane Copy Back Program

Figure 8.16 Two-Plane Copy Back Program with Random Data Input

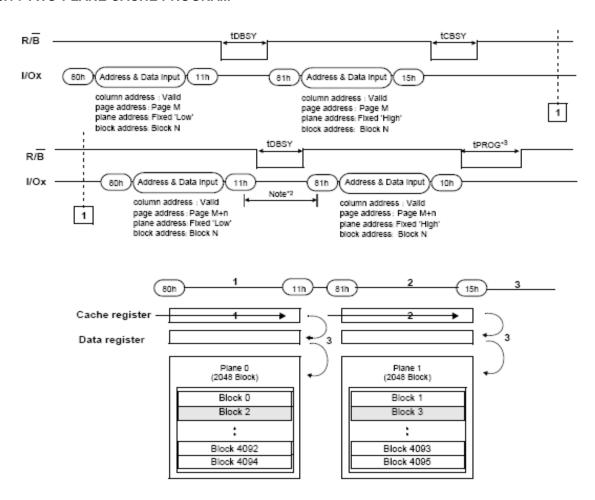

### 8.14 TWO-PLANE CACHE PROGRAM

Figure 8.17 Two-Plane Cache Program

# 8.15 TWO-PLANE BLOCK ERASE

Figure 8.18 Two-Plane Block Erase

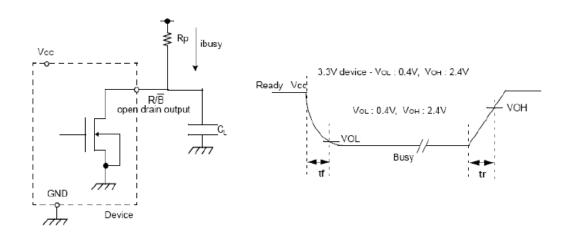

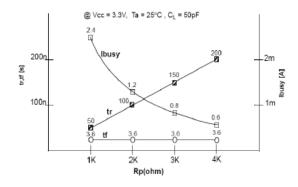

### 8.16 READY/BUSY#

The device has a R/B# output that provides a hardware method of indicating the completion of a page program, erase and random read completion. The R/B# pin is normally high but transition to low after program or erase command is written to the command register or random read is started after address loading. It returns to high when the internal controller has finished the operation. The pin is an opendrain driver thereby allowing two or more R/B# outputs to be Or-tied. Because pull-up resistor value is related to tr(R/B#) and current drain during busy (ibusy) , an appropriate value can be obtained with the following reference chart. Its value can be determined by the following guidance

RP vs tRHOH vs CL

### Rp value guidance

$$Rp(min, 3.3V part) = \frac{Vcc(Max.) - Vol(Max.)}{Iol + \Sigma IL} = \frac{3.2V}{8mA + \Sigma IL}$$

where  $I_L$  is the sum of the input currents of all devices tied to the R/B# pin.  $R_P$  (max) is determined by maximum permissible limit of tr

Figure 8.19 Ready/Busy# Pin Electrical Specifications

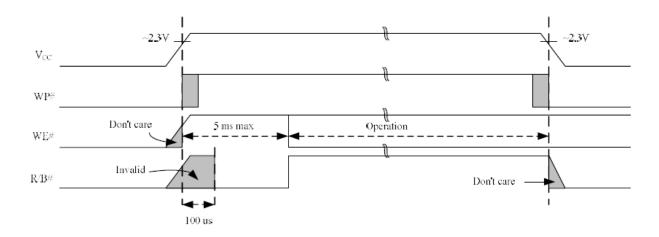

### 8.17 DATA PROTECTION AND POWER UP SEQUENCE

The timing sequence shown in the figure below is necessary for the power-on/off sequence.

The device internal initialization starts after the power supply reaches an appropriate level in the power on sequence. During the initialization the device R/B# signal indicates the Busy state as shown in the figure below. In this time period, the acceptable commands are 70h.

The WP# signal is useful for protecting against data corruption at power on/off.

Figure 8.20 AC Waveforms for Power Transition

# **8.18 WRITE PROTECT OPERATION**

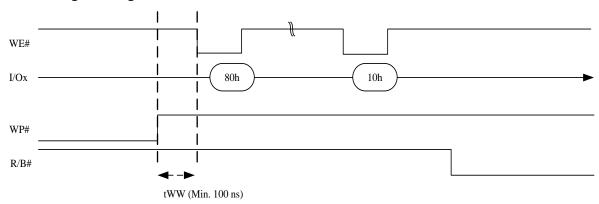

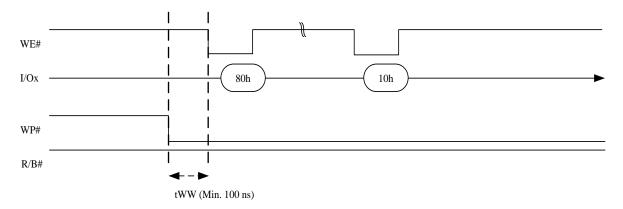

Enabling WP# during erase and program busy is prohibited. The erase and program operations are enabled and disabled as follows:

## **Enable Programming**

Note: WP# keeps "High" until programming finish

# **Disable Programming**

# **Enable Erasing**

NOTE: WP# keeps "High" until erasing finish

# **Disable Erasing**

Figure 8.21 Enable/Disable Programming and Enable Erasing

## 9. INVALID BLOCK AND ERROR MANAGEMENT

### 9.1 MASK OUT INITIAL INVALID BLOCK(S)

Initial invalid blocks are defined as blocks that contain one or more initial invalid bits whose reliability is not guaranteed by ISSI. The information regarding the initial invalid block(s) is called the initial invalid block information. Devices with initial invalid block(s) have the same quality level as devices with all valid blocks and have the same AC and DC characteristics. An initial invalid block(s) does not affect the performance of valid block(s) because it is isolated from the bit line and the common source line by a select transistor. The system design must be able to mask out the initial invalid block(s) via address mapping.

The 1st block, which is placed on 00h block address, is guaranteed to be a valid block up to 1K program/erase cycles with 1bit/512Byte ECC.

### 9.2 IDENTIFYING INITIAL INVALID BLOCK(S) AND BLOCK REPLACEMENT MANAGEMENT

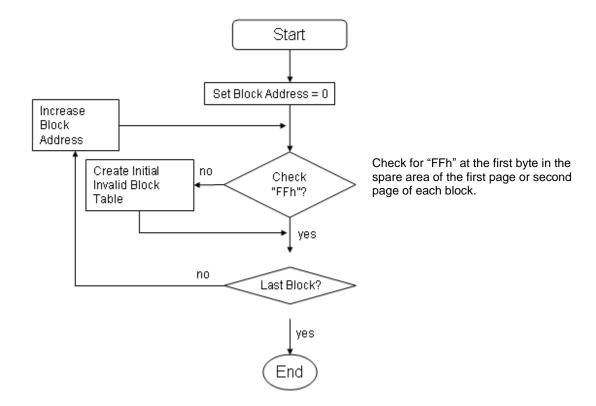

Unpredictable behavior may result from programming or erasing the defective blocks. Figure below illustrates an algorithm for searching factory-mapped defects, and the algorithm needs to be executed prior to any erase or program operations.

A host controller has to scan the data at the first byte in the spare area of the first page or second page of each block from block 0 to the last block using page read command.

Any block where the 1<sup>st</sup> byte in the spare area of the first or second page does not contain "FFh" is an invalid block.

Do not erase or program factory-marked bad blocks. The host controller must be able to recognize the initial invalid block information and to create a corresponding table to manage block replacement upon erase or program error when additional invalid blocks develop with Flash memory usage.

Figure 9.1 Algorithm for Bad Block Scanning

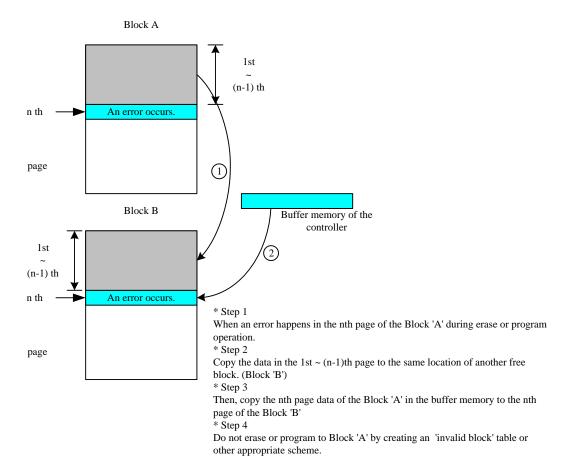

#### 9.3 ERROR IN READ OR WRITE OPERATION

Within its lifetime, additional invalid blocks may develop with NAND Flash memory. Refer to the qualification report for the actual data. The following possible failure modes should be considered to implement a highly reliable system. In the case of status read failure after erase or program, block replacement should be done. Because program status fail during a page program does not affect the data of the other pages in the same block, block replacement can be executed with a page-sized buffer by finding an erased empty block and reprogramming the current target data and copying the rest of the replaced block. In case of Read, ECC must be employed. To improve the efficiency of memory space, it is recommended that the read or verification failure due to single bit error be reclaimed by ECC without any block replacement. The additional block failure rate does not include those reclaimed blocks.

|                          | Failure Mode    | Detection and Countermeasure Sequence         |  |

|--------------------------|-----------------|-----------------------------------------------|--|

| Write Erase failure      |                 | Read Status after Erase → Block Replacement   |  |

|                          | Program failure | Read Status after Program → Block Replacement |  |

| Read Up to 1 bit failure |                 | Verify ECC → ECC Correction                   |  |

**Note**: Error Correcting Code → RS Code or BCH Code etc.

Example: 1bit correction / 512 Byte

Figure 9.2 Program Flow Chart

Figure 9.3 Erase Flow Chart

Figure 9.4 Read Flow Chart

Figure 9.5 Blcok Replacement

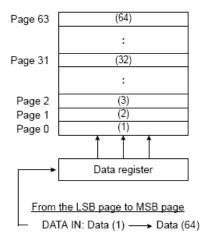

### 9.4 ADDRESSING FOR PROGRAM OPERATION

Within a block, the page must be programmed consecutively from the LSB (Least Significant Bit) page of the block to MSB (Most Significant Bit) pages of the block. Random page address programming is prohibited. In this case, the definition of LSB page is the LSB among the pages to be programmed. Therefore, LSB page doesn't need to be page 0.

Figure 9.6 Addressing for Program Operation

### 9.5 SYSTEM INTERFACE USING CE# NOT CARE OPERATION

For an easier system interface, CE# may be inactive during the data-loading or serial access as shown below. The internal 2,112byte data registers are utilized as separate buffers for this operation and the system design gets more flexible. In addition, for voice or audio applications that use slow cycle time on the order of  $\mu$ -seconds, de-activating CE# during the data-loading and serial access would provide significant savings in power consumption.

Figure 9.7 Program/Read-Operation with CE# Not-Care Operation

### **Address Information**

| Davisa          | Data        | 1/0         | Address      |              |              |              |             |

|-----------------|-------------|-------------|--------------|--------------|--------------|--------------|-------------|

| Device          | Data In/Out | I/Ox        | Col.<br>Add1 | Col.<br>Add2 | Row<br>Add1  | Row<br>Add2  | Row<br>Add3 |

| IS34/35ML02G081 | 2,112Byte   | I/O 0~I/O 7 | A0 ~ A7      | A8 ~ A11     | A12 ~<br>A19 | A20 ~<br>A27 | A28         |

# **10. PACKAGE TYPE INFORMATION**

## 10.1 48-PIN TSOP (TYPE I) PACKAGE (T)

## 10.2 63-BALL VFBGA PACKAGE (B)

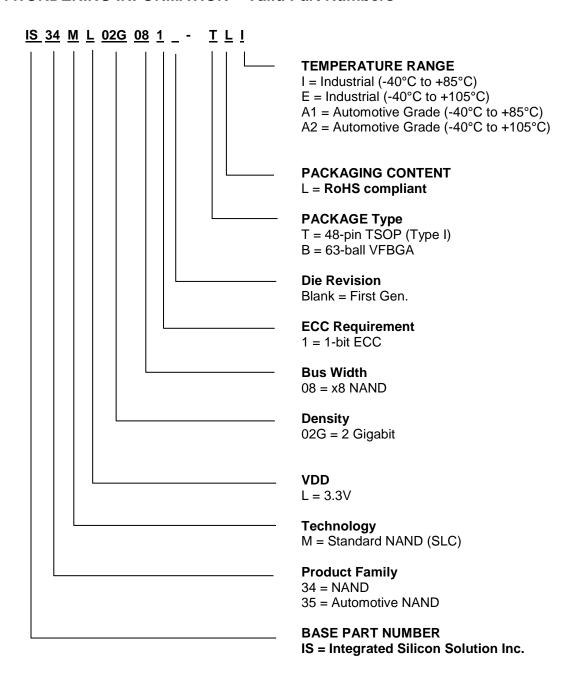

## 11. ORDERING INFORMATION - Valid Part Numbers

| VDD  | Density | Bus  | Temp. Grade                    | Order Part Number              | Package              |               |

|------|---------|------|--------------------------------|--------------------------------|----------------------|---------------|

|      |         | b X8 | Industrial                     | IS34ML02G081-TLI               | 48-pin TSOP (Type I) |               |

|      |         |      |                                | IS34ML02G081-BLI               | 63-ball VFBGA        |               |

|      |         |      |                                | IS34ML02G081-TLE               | 48-pin TSOP (Type I) |               |

| 3.3V | 2Gb     |      |                                | IS34ML02G081-BLE               | 63-ball VFBGA        |               |

|      | 200     |      |                                | IS35ML02G081-TLA1              | 48-pin TSOP (Type I) |               |

|      |         |      | <i>'</i>                       | Automotive (A1) <sup>(1)</sup> | IS35ML02G081-BLA1    | 63-ball VFBGA |

|      |         |      | Automotive (A2) <sup>(1)</sup> | IS35ML02G081-TLA2              | 48-pin TSOP (Type I) |               |

|      |         |      |                                | IS35ML02G081-BLA2              | 63-ball VFBGA        |               |

## Note:

<sup>1.</sup> Automotive Grade meets AEC-Q100 requirements with PPAP. Temp Grades: A1= -40 to 85°C, A2= -40 to 105°C

OOO «ЛайфЭлектроникс" "LifeElectronics" LLC

ИНН 7805602321 КПП 780501001 P/C 40702810122510004610 ФАКБ "АБСОЛЮТ БАНК" (ЗАО) в г.Санкт-Петербурге К/С 3010181090000000703 БИК 044030703

Компания «Life Electronics» занимается поставками электронных компонентов импортного и отечественного производства от производителей и со складов крупных дистрибьюторов Европы, Америки и Азии.

С конца 2013 года компания активно расширяет линейку поставок компонентов по направлению коаксиальный кабель, кварцевые генераторы и конденсаторы (керамические, пленочные, электролитические), за счёт заключения дистрибьюторских договоров

### Мы предлагаем:

- Конкурентоспособные цены и скидки постоянным клиентам.

- Специальные условия для постоянных клиентов.

- Подбор аналогов.

- Поставку компонентов в любых объемах, удовлетворяющих вашим потребностям.

- Приемлемые сроки поставки, возможна ускоренная поставка.

- Доставку товара в любую точку России и стран СНГ.

- Комплексную поставку.

- Работу по проектам и поставку образцов.

- Формирование склада под заказчика.

- Сертификаты соответствия на поставляемую продукцию (по желанию клиента).

- Тестирование поставляемой продукции.

- Поставку компонентов, требующих военную и космическую приемку.

- Входной контроль качества.

- Наличие сертификата ISO.

В составе нашей компании организован Конструкторский отдел, призванный помогать разработчикам, и инженерам.

Конструкторский отдел помогает осуществить:

- Регистрацию проекта у производителя компонентов.

- Техническую поддержку проекта.

- Защиту от снятия компонента с производства.

- Оценку стоимости проекта по компонентам.

- Изготовление тестовой платы монтаж и пусконаладочные работы.

Тел: +7 (812) 336 43 04 (многоканальный) Email: org@lifeelectronics.ru