## 11.3 Gbps Differential VCSEL Driver With Output Waveform Shaping

## **FEATURES**

- Up to 11.3 Gbps Operation

- 2-Wire Digital Interface

- Digitally Selectable Modulation Current up to 24 mApp Differential

- Digitally Selectable Bias Current up to 20 mA

- Automatic Power Control (APC) Loop

- Supports Transceiver Management System (TMS)

- Programmable Input Equalizer

- Output Waveform Control

- Includes Laser Safety Features

- Analog Temperature Sensor Output

- Selectable Monitor Photodiode Current Range

- Output Polarity Select

- Single 3.3V Supply

- Operating Temperature –40°C to 85°C

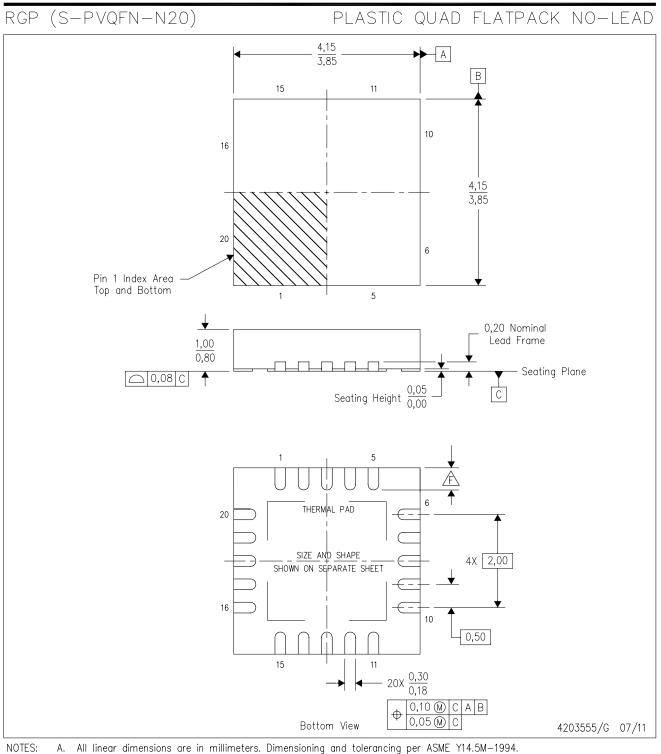

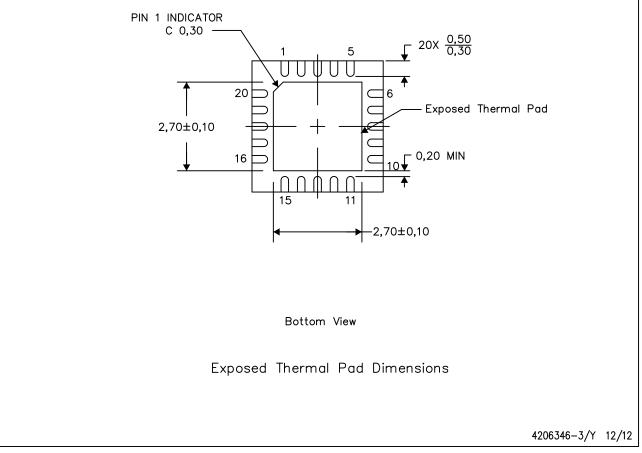

- Surface Mount Small Footprint  $4mm \times 4mm$  20 Pin RoHS compliant QFN Package

## APPLICATIONS

- 10 Gigabit Ethernet Optical Transmitters

- 8x and 10x Fibre Channel Optical Transmitters

- SONET OC-192/SDH STM-64 Optical Transmitters

- SFP+ and XFP Transceiver Modules

- XENPAK, XPAK, X2 and 300-pin MSA Transponder Modules

## DESCRIPTION

The ONET8501V is a high-speed, 3.3V laser driver designed to directly modulate VCSELs at data rates from 2 Gbps up to 11.3 Gbps.

The device provides a two-wire serial interface which allows digital control of the modulation and bias currents, eliminating the need for external components. Output waveform control, in the form of cross point control and independent over- and undershoot capability on the rising and falling edges is also available to improve VCSEL edge speeds and the optical eye diagram. An optional input equalizer can be used for equalization of up to 300mm (12 inch) of microstrip or stripline transmission line on FR4 printed circuit boards.

The ONET8501V includes an integrated automatic power control (APC) loop as well as circuitry to support laser safety and transceiver management systems. The VCSEL driver is characterized for operation from  $-40^{\circ}$ C to 85°C ambient temperatures and is available in a small footprint 4mm × 4mm 20 pin RoHS compliant QFN package.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

## **ONET8501V**

SLLS837B-JUNE 2007-REVISED SEPTEMBER 2007

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

## **BLOCK DIAGRAM**

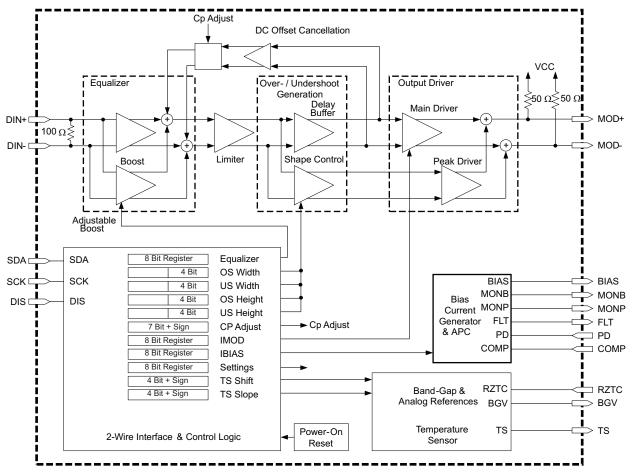

A simplified block diagram of the ONET8501V is shown in Figure 1.

The VCSEL driver consists of an equalizer, a limiter, a waveform shaping block with over- and undershoot control, an output driver, power-on reset circuitry, a 2-wire serial interface including a control logic block, a modulation current generator and a bias current generator with automatic power control loop, and an analog reference block.

Figure 1. Simplified Block Diagram of the ONET8501V

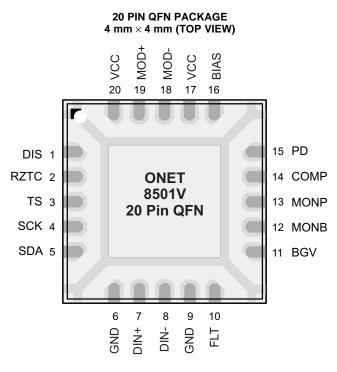

#### PACKAGE

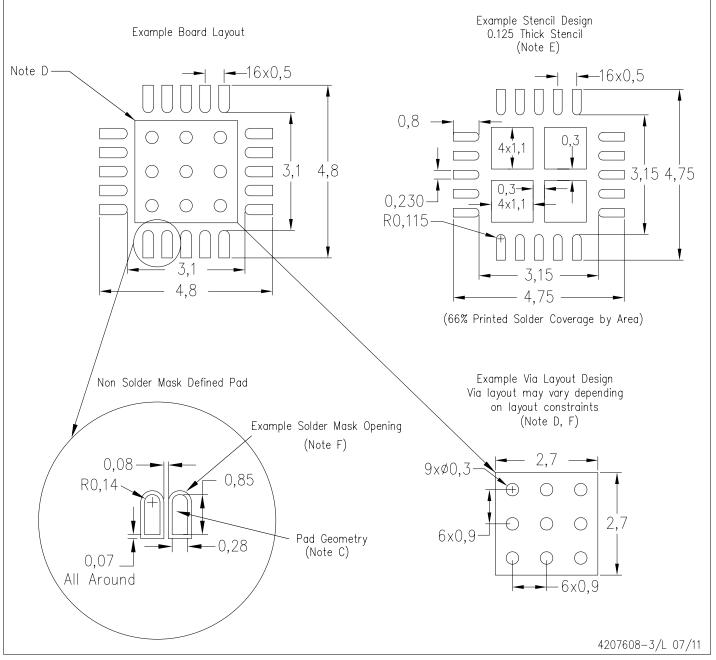

The ONET8501V is packaged in a small footprint  $4mm \times 4mm$  20 pin RoHS compliant QFN package with a lead pitch of 0,5 mm. The pin out is shown below.

#### **TERMINAL FUNCTIONS**

| TERM                 | MINAL |              |                                                                                                                                                                                                                                                                              |  |  |  |  |  |

|----------------------|-------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| PIN NAME TYPE<br>NO. |       | TYPE         | DESCRIPTION                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| 1                    | DIS   | Digital-in   | Disables bias, modulation and peaking currents when set to high state. Toggle to reset a fault condition. Recommend shorting pin to GND if disable feature is not used.                                                                                                      |  |  |  |  |  |

| 2                    | RZTC  | Analog       | Connect external zero TC 28.7k $\Omega$ resistor to ground (GND). Used to generate a defined zero TC reference current for internal DACs.                                                                                                                                    |  |  |  |  |  |

| 3                    | TS    | Analog-out   | Temperature sensor output.                                                                                                                                                                                                                                                   |  |  |  |  |  |

| 4                    | SCK   | Digital -in  | 2-wire interface serial clock. Includes a pull-up resistor to VCC.                                                                                                                                                                                                           |  |  |  |  |  |

| 5                    | SDA   | Digital -in  | 2-wire interface serial data input. Includes a pull-up resistor to VCC.                                                                                                                                                                                                      |  |  |  |  |  |

| 6, 9, EP             | GND   | Supply       | Circuit ground. Exposed die pad (EP) must be grounded.                                                                                                                                                                                                                       |  |  |  |  |  |

| 7                    | DIN+  | Analog-in    | Non-inverted data input. On-chip differentially 100Ω terminated to DIN–. Must be AC coupled.                                                                                                                                                                                 |  |  |  |  |  |

| 8                    | DIN-  | Analog-in    | Inverted data input. On-chip differentially $100\Omega$ terminated to DIN+. Must be AC coupled.                                                                                                                                                                              |  |  |  |  |  |

| 10                   | FLT   | Digital-out  | Fault detection flag. LVCMOS output with source and sink capability.                                                                                                                                                                                                         |  |  |  |  |  |

| 11                   | BGV   | Anolog-out   | Buffered bandgap voltage with 1.16V output. This is a replica of the bandgap voltage at RZTC. For best matching, use the same $28.7k\Omega$ resistor to GND as used at RZTC.                                                                                                 |  |  |  |  |  |

| 12                   | MONB  |              | Bias current monitor. Sources a 3.5% replica of the bias current. Connect an external resistor to ground (GND). If the voltage at this pin exceeds 1.16V a fault is triggered. Typically choose a resistor to give MONB voltage of 0.8V at the maximum desired bias current. |  |  |  |  |  |

| 13                   | MONP  | - Analog-out | Photodiode current monitor. Sources a 27% replica of the photodiode current when PDR = 10, a 54% replica when PDR = 01, and a 270% replica when PDR=00. Connect an external resistor (5k $\Omega$ typical) to ground (GND).                                                  |  |  |  |  |  |

| 14                   | COMP  |              | Compensation pin used to control the bandwidth of the APC loop. Connect a 0.01µF capacitor to ground.                                                                                                                                                                        |  |  |  |  |  |

| 15                   | PD    | Analog       | Photodiode input. Pin can source or sink current dependent on register setting.                                                                                                                                                                                              |  |  |  |  |  |

| 16                   | BIAS  | , and og     | Sinks average bias current for VCSEL in both APC and open loop modes. Connect to laser cathode through an inductor. BLM15HG102SN1D recommended.                                                                                                                              |  |  |  |  |  |

| 17, 20               | VCC   | Supply       | 3.3V ± 10% supply voltage                                                                                                                                                                                                                                                    |  |  |  |  |  |

#### **TERMINAL FUNCTIONS (continued)**

| TERMINAL<br>PIN NAME TYPE<br>NO. |                 |           |                                                                                                                                                  |  |  |  |

|----------------------------------|-----------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                  |                 | TYPE      | DESCRIPTION                                                                                                                                      |  |  |  |

| 18                               | MOD-<br>CML-out |           | Inverted modulation current output. On-chip $50\Omega$ back-terminated to VCC. I <sub>MOD</sub> flows into this pin when input data is low.      |  |  |  |

| 19                               | MOD+            | (current) | Non-inverted modulation current output. On-chip $50\Omega$ back-terminated to VCC. I <sub>MOD</sub> flows into this pin when input data is high. |  |  |  |

### ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

over operating free-air temperature range (unless otherwise noted)

|                                                                                                                                                                                                                                                                                                                             |                                                                                                                 | VALUE      | UNIT     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|------------|----------|

| V <sub>CC</sub>                                                                                                                                                                                                                                                                                                             | Supply voltage <sup>(2)</sup>                                                                                   | -0.3 to 4  | V        |

| V <sub>DIS</sub> , V <sub>RZTC</sub> , V <sub>TS</sub> , V <sub>SCK</sub> ,<br>V <sub>SDA</sub> , V <sub>FLT</sub> , V <sub>BGV</sub> , V <sub>MONB</sub> ,<br>V <sub>MONP</sub> , V <sub>CAPC</sub> , V <sub>PD</sub> , V <sub>BIAS</sub><br>V <sub>DIN+</sub> , V <sub>DIN-</sub> , V <sub>MOD+</sub> , V <sub>MOD-</sub> | Voltage at DIS, RZTC, TS, SCK, SDA, FLT, BGV, MONB, MONP, CAPC, PD, BIAS, DIN+, DIN–, MOD+, MOD– <sup>(2)</sup> | -0.3 to 4  | V        |

| I <sub>DIN-</sub> , I <sub>DIN+</sub>                                                                                                                                                                                                                                                                                       | Maximum current at input pins                                                                                   | 25         | mA       |

| I <sub>MOD+</sub> , I <sub>MOD-</sub>                                                                                                                                                                                                                                                                                       | Maximum current at output pins                                                                                  | 30         | mA       |

| ESD                                                                                                                                                                                                                                                                                                                         | ESD rating at all pins                                                                                          | 2          | kV (HBM) |

| T <sub>J,max</sub>                                                                                                                                                                                                                                                                                                          | Maximum junction temperature                                                                                    | 125        | °C       |

| T <sub>STG</sub>                                                                                                                                                                                                                                                                                                            | Storage temperature range                                                                                       | -65 to 150 | °C       |

| T <sub>A</sub>                                                                                                                                                                                                                                                                                                              | Characterized free-air operating temperature range                                                              | -40 to 85  | °C       |

(1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability

(2) All voltage values are with respect to network ground terminal

## **RECOMMENDED OPERATING CONDITIONS**

over operating free-air temperature range (unless otherwise noted)

|                   |                                       |                                                       | MIN  | TYP  | MAX  | UNIT             |

|-------------------|---------------------------------------|-------------------------------------------------------|------|------|------|------------------|

| V <sub>CC</sub>   | Supply voltage                        |                                                       | 2.95 | 3.3  | 3.6  | V                |

| VIH               | Digital input high voltage            | DIS, SCK, SDA                                         | 2    |      |      | V                |

| VIL               | Digital input low voltage             | DIS, SCK, SDA                                         |      |      | 0.8  | V                |

|                   | Bias output headroom voltage          | V <sub>BIAS</sub> – GND                               | 300  |      |      | mV               |

|                   |                                       | High step size mode, min. step size = 5 µA            |      | 25   |      | μA               |

|                   |                                       | High step size mode, max. step size = 5 µA            |      | 1280 |      |                  |

|                   |                                       | Medium step size mode, min. step size = $2.5 \mu A$   |      | 12.5 |      |                  |

|                   | Photodiode current range              | Medium step size mode, max. step size = $2.5 \mu$ A   |      | 640  |      |                  |

|                   |                                       | Low step size mode, min. step size = $0.5 \mu A$      |      | 2.5  |      |                  |

|                   |                                       | Low step size mode, max. step size = 0.5 µA           |      | 128  |      |                  |

| R <sub>RZTC</sub> | Zero TC resistor value <sup>(1)</sup> | 1.16 V bandgap bias across resistor, E96, 1% accuracy | 28.4 | 28.7 | 29   | kΩ               |

| VIN               | Differential input voltage swing      |                                                       | 100  |      | 1200 | mV <sub>pp</sub> |

| t <sub>R-IN</sub> | Input rise time                       | 20%-80%                                               |      | 30   | 55   | ps               |

| t <sub>F-IN</sub> | Input fall time                       | 20%-80%                                               |      | 30   | 55   | ps               |

| T <sub>A</sub>    | Operating free-air temperature        |                                                       | -40  |      | 85   | °C               |

(1) Changing the value will alter the DAC ranges.

## **DC ELECTRICAL CHARACTERISTICS**

Over recommended operating conditions, all values are for open-loop operation, I<sub>MODC</sub> = 12 mA, I<sub>BIASC</sub> = 6 mA, and  $R_{RZTC}$  = 28.7 k $\Omega$ , unless otherwise noted

|                        | PARAMETER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | TEST CONDITIONS                                                                                                                    | MIN  | TYP  | MAX  | UNIT |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| V <sub>CC</sub>        | Supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                    | 2.95 | 3.3  | 3.6  | V    |

|                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | $I_{MODC}$ = 12 mA, $I_{BIASC}$ = 6 mA, including $I_{MODC},$ No waveform shaping, EQENA = 0                                       |      | 50   | 70   |      |

|                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | $I_{MODC}$ = 12 mA, $I_{BIASC}$ = 6 mA, including $I_{MODC},$ No waveform shaping, EQENA = 1                                       |      | 55   | 75   |      |

| I <sub>VCC</sub>       | Supply current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | $I_{MODC}$ = 12 mA, $I_{BIASC}$ = 6 mA, including $I_{MODC}$ , Single sided max output waveform shaping at MOD+ or MOD–, EQENA = 1 |      | 75   | 90   | mA   |

|                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | $I_{MODC}$ = 12 mA, $I_{BIASC}$ = 6 mA, including $I_{MODC}$ . Double sided max output waveform shaping at MOD+ or MOD–, EQENA = 1 |      | 82   | 100  |      |

|                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Disabled (DIS=HIGH) or ENA=LOW, EQENA = 0                                                                                          |      | 24   |      |      |

| R <sub>IN</sub>        | Data input resistance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Differential between DIN+ / DIN-                                                                                                   | 80   | 100  | 120  | Ω    |

| R <sub>OUT</sub>       | Supply voltage2.953.33.6Supply voltage $I_{NODC} = 12 \text{ mA}, I_{BLASC} = 6 \text{ mA}, including I_{MODC}, No waveformshaping, EQENA = 15070Supply currentI_{NODC} = 12 \text{ mA}, I_{BLASC} = 6 \text{ mA}, including I_{MODC}, No waveformshaping, EQENA = 15575I_{NODC} = 12 \text{ mA}, I_{BLASC} = 6 \text{ mA}, including I_{MODC}, Single sided maxoutput waveform shaping at MOD+ or MOD-, EQENA = 182100Disabled (DIS=HIGH) or ENA-LOW, EQENA = 1Disabled (DIS=HIGH) or ENA-LOW, EQENA = 182100Disabled (DIS=HIGH) or ENA-LOW, EQENA = 0241010Diata output resistanceSingle-ended to VCC405060Digital input currentSCK, SDA, pull up to VCC(1)-101010Digital output hydrageFLT, pull-up to VCC.1001010Digital output dign voltageFLT, pull-up to VCC. ISINK = 1000 µA(2)2.4100Minimum bias currentDAC set to maximum, open and closed loop17200.4Photodiode reverse bias voltageAPC active, IPD = max1.32.3100Photodiode current monitor ratioSource or sink (11)100100100100Minimum bias currentDAC set to maximum, open and closed loop172.42.52.5Temperature sensor ovoltage range-4O*C to 120*C junction temperature. With Mid scale calibration(1).52.52.5Temperature sensor ovoltage range-4O*C to 120*C junction temperature. With Mid scale calibration(1).2.42$ | Ω                                                                                                                                  |      |      |      |      |

|                        | Digital input current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | SCK, SDA, pull up to VCC <sup>(1)</sup>                                                                                            | -10  |      | 10   | μA   |

|                        | Digital input current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | DIS, pull down to GND <sup>(1)</sup>                                                                                               | -10  |      | 10   | μA   |

| V <sub>OH</sub>        | Digital output high voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | FLT, pull-up to V <sub>CC</sub> , $I_{SOURCE} = 1000 \ \mu A^{(2)}$                                                                | 2.4  |      |      | V    |

| V <sub>OL</sub>        | Digital output low voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | FLT, pull-up to V <sub>CC</sub> , $I_{SINK}$ = 1000 $\mu A^{(2)}$                                                                  |      |      | 0.4  | V    |

| I <sub>BIAS-DIS</sub>  | Bias current during disable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                    |      |      | 100  | μA   |

| IBIAS-MIN              | Minimum bias current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | See <sup>(3)</sup>                                                                                                                 |      |      | 200  | μA   |

| I <sub>BIAS-MAX</sub>  | Maximum bias current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | DAC set to maximum, open and closed loop                                                                                           | 17   | 20   |      | mA   |

| V <sub>PD</sub>        | Photodiode reverse bias voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | APC active, I <sub>PD</sub> = max                                                                                                  | 1.3  | 2.3  |      | V    |

|                        | Photodiode fault current level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Percent of target I <sub>PD</sub> <sup>(1)</sup>                                                                                   |      | 150% |      |      |

| V <sub>TS</sub>        | Temperature sensor voltage range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -40°C to 120°C junction temperature. With Mid scale calibration <sup>(1)</sup>                                                     | 0.5  |      | 2.5  | V    |

|                        | Temperature sensor accuracy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | With mid scale calibration <sup>(1)</sup>                                                                                          |      | ±4   |      | °C   |

| I <sub>TS</sub>        | Temperature sensor drive current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Source or sink <sup>(1)</sup>                                                                                                      |      | 100  |      | μA   |

|                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | $I_{MONP} / I_{PD}$ with control bit PDR = 10                                                                                      | 20%  | 27%  | 32%  |      |

|                        | Photodiode current monitor ratio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                    | 40%  | 54%  | 65%  |      |

|                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | $I_{MONP} / I_{PD}$ with control bit PDR = 00                                                                                      | 200% | 270% | 350% |      |

|                        | Bias current monitor ratio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                    |      |      |      |      |

| V <sub>CC-RST</sub>    | VCC reset threshold voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                    | 2.4  | 2.5  | 2.8  | V    |

| V <sub>CC-RSTHYS</sub> | VCC reset threshold voltage hysteresis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                    |      | 100  |      | mV   |

| V <sub>MONB-FLT</sub>  | Fault voltage at MONB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Fault occurs if voltage at MONB exceeds value                                                                                      | 1.1  | 1.16 | 1.2  | V    |

Specified by simulation over process, supply and temperature variation External pull up resistor according to timing requirements (1)

(2) (3) The bias current can be set below the specified minimum according to the corresponding register setting, however in closed loop operation settings below the specified value may trigger a fault.

## AC ELECTRICAL CHARACTERISTICS

Over recommended operating conditions with 50 $\Omega$  output load, open loop operation,  $I_{MODC}$  = 12 mA,  $I_{BIAS}$  = 6 mA, and  $R_{RZTC}$  = 28.7 k $\Omega$ , unless otherwise noted. Typical operating condition is at  $V_{CC}$  = 3.3V and  $T_A$  = 25°C

|                       | PARAMETER                         | TEST CONDITIONS                                                                                                                                                                          | MIN TYP | MAX | UNIT              |

|-----------------------|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----|-------------------|

|                       |                                   | 0.01 GHz < f < 3.9 GHz                                                                                                                                                                   | -16     |     |                   |

| SDD11                 | Differential input return gain    | 3.9 GHz < f < 11.1 GHz                                                                                                                                                                   | (1)     |     | dB                |

|                       |                                   | 11.1 GHz < f < 20 GHz                                                                                                                                                                    | -3      |     |                   |

| SCD11                 | Differential to common mode       | f < 8.25 GHz                                                                                                                                                                             | -35     |     |                   |

|                       | conversion gain                   | 8.25 GHz < f < 20 GHz                                                                                                                                                                    | -28     |     | dB                |

| t <sub>R-OUT</sub>    | Output rise time                  | $20\%-80\%,t_{R-IN}<40$ ps, 100 $\Omega$ differential load, no waveform shaping, EQENA = 0, 100 mVpp differential input voltage                                                          | 24      | 30  | 50                |

| t <sub>F-OUT</sub>    | Output fall time                  | $20\%-80\%,$ tr-IN < 40 ps, 100 $\Omega$ differential load, no waveform shaping, EQENA = 0, 100 mVpp differential input voltage                                                          | 24      | 30  | ps                |

| I <sub>MOD-MAX</sub>  | Maximum modulation current        | Output stage tail current                                                                                                                                                                | 16 24   |     | mA                |

| I <sub>MOD-STEP</sub> | Modulation current step size full |                                                                                                                                                                                          | 100     |     |                   |

|                       | Modulation current step size half | Modulation current smaller than 6 mA                                                                                                                                                     | 50      |     | μA                |

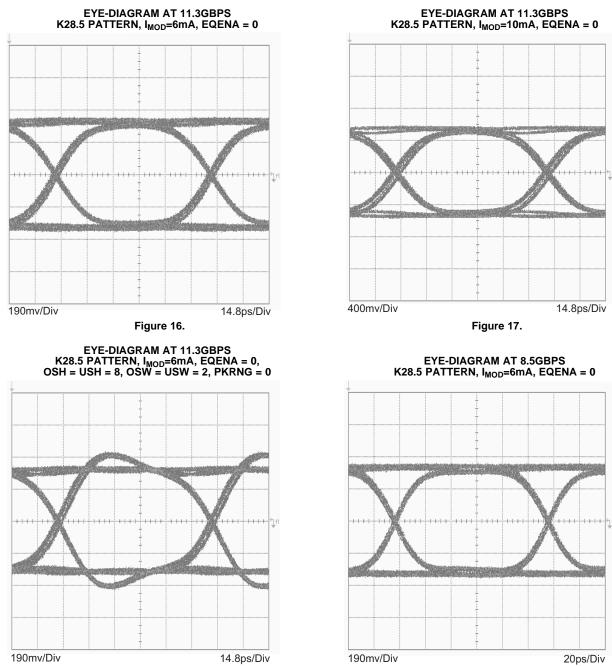

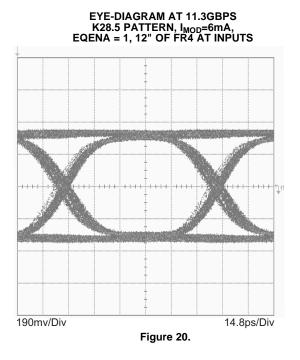

|                       |                                   | EQENA = 0, K28.5 pattern at 11.3 Gbps, no waveform shaping, 100 mVpp, 600 mVpp, 1200 mVpp differential input voltage                                                                     | 3.5     | 9   |                   |

| DJ                    | Deterministic output jitter       | EQENA = 1, K28.5 pattern at 11.3 Gbps, maximum equalization<br>with 12" transmission line at the input, no waveform shaping,<br>200 mVpp, 600 mVpp, 1200 mVpp differential input voltage | 8.5     | 15  | ps <sub>p-p</sub> |

|                       | Maximum output peaking width      |                                                                                                                                                                                          | 120     |     |                   |

|                       | Minimum output peaking width      | – Maximum peaking height <sup>(2)</sup>                                                                                                                                                  | 30      |     | ps                |

|                       |                                   | Referred to output stage tail current, high range                                                                                                                                        | 10      |     |                   |

|                       | Maximum output peaking height     | Referred to output stage tail current, low range                                                                                                                                         | 5       |     | mA                |

|                       |                                   | Referred to output stage tail current, high range                                                                                                                                        | 0.66    |     |                   |

|                       | Output peaking height step size   | Referred to output stage tail current, low range                                                                                                                                         | 0.33    |     | mA                |

|                       | Cross point range                 | 600 mVpp differential input                                                                                                                                                              | 30–70%  |     |                   |

| RJ                    | Random output jitter              | 50Ω load, EQENA = 0, 100 mVpp differential input voltage                                                                                                                                 | 0.4     | 0.6 | ps <sub>RMS</sub> |

| T <sub>APC</sub>      | APC time constant                 | $C_{APC}$ 0.01 $\mu F,  I_{PD}$ = 100 $\mu A,  PD$ coupling ratio CR = $40^{(2)}$                                                                                                        | 200     |     | μs                |

| t <sub>OFF</sub>      | Transmitter disable time          | Rising edge of DIS to $I_{BIAS} \le 0.1 \times I_{BIAS-NOMINAL}^{(2)}$                                                                                                                   | 1       | 5   | μs                |

| t <sub>ON</sub>       | Disable negate time               | Falling edge of DIS to $I_{BIAS} \ge 0.9 \times I_{BIAS-NOMINAL}$ <sup>(2)</sup>                                                                                                         |         | 1   | ms                |

| t <sub>INIT1</sub>    | Power-on to initialize            | Power-on to registers ready to be loaded                                                                                                                                                 | 0.2     | 1   | ms                |

| t <sub>INIT2</sub>    | Initialize to transmit            | Register load STOP command to part ready to transmit valid data <sup>(2)</sup>                                                                                                           |         | 2   | ms                |

| t <sub>RESET</sub>    | DIS pulse width                   | Time DIS must held high to reset part <sup>(2)</sup>                                                                                                                                     | 100     |     | ns                |

| t <sub>FAULT</sub>    | Fault assert time                 | Time from fault condition to FLT high <sup>(2)</sup>                                                                                                                                     |         | 50  | μs                |

(1) Differential Return Gain given by SDD11 =  $-14 + 13.33 \log_{10}(f/5.5)$ , f in GHz

(2) Assured by simulation over process, supply and temperature variation

## DETAILED DESCRIPTION

#### EQUALIZER

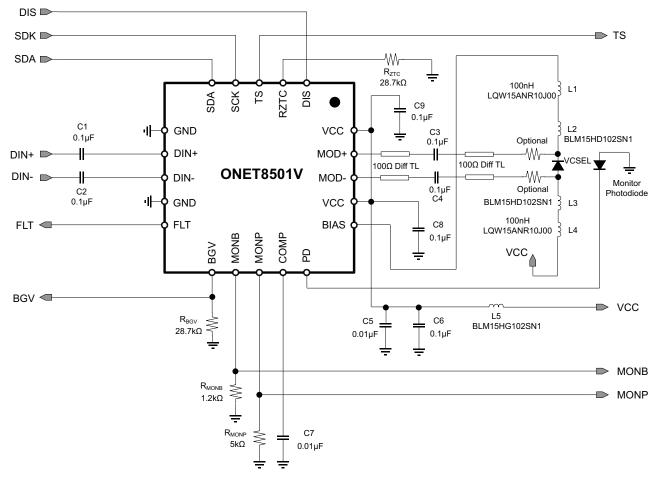

The data signal can be applied to an input equalizer by means of the input signal pins DIN+/DIN–, which provide on-chip differential  $100\Omega$  line-termination. The equalizer is enabled by setting the EQENA = 1 (bit 1 of register 0). Equalization of up to 300mm (12") of microstrip or stripline transmission line on FR4 printed circuit boards can be achieved. The amount of equalization is digitally controlled by the two-wire interface and control logic block and depends on the register settings EQADJ[0..7] (register 3). The equalizer can also be turned off and bypassed by setting EQENA = 0. For details about the equalizer settings, see Table 16.

### LIMITER

By limiting the output signal of the equalizer to a fixed value, the limiter removes any overshoot after the input equalization and provides the input signal for the output signal waveform shaping.

#### **OUTPUT SIGNAL WAVEFORM SHAPING**

The output signal waveform shaping provides two paths for the data signal. The delay buffer ensures that both paths have the same transit time. The over- and undershoot peaking width and height are controlled through the two wire interface and the peak driver linearly amplifies the signal. The resultant waveform shaped signal is then added to the output of the main driver. The overshoot width is controlled by register 5 settings OSW[0..3] and the overshoot height is controlled by register 6 settings OSH[0..3]. The undershoot width is controlled by register 7 settings USW[0..3] and the undershoot height is controlled by register 8 settings OSH[0..3].

The peaking current is disabled by setting both over- and undershoot height registers to zero. The peaking current is also disabled when the DIS pin is set to a high level or during a fault condition if the fault detection enable register flag FLTEN is set (bit 3 of register 0).

#### HIGH-SPEED OUTPUT DRIVER

The modulation current is sunk from the common emitter node of the output driver differential pair by means of a modulation current generator, which is digitally controlled by the 2-wire serial interface.

The collector nodes of the output stages are connected to the output pins MOD+/ MOD-, which include on-chip 2  $\times 50\Omega$  back-termination to VCC. The 50 $\Omega$  back-termination together with an optional off chip series resistor helps to sufficiently suppress signal distortion caused by double reflections for VCSEL diodes with impedances from 50 $\Omega$  through 110 $\Omega$ . The polarity of the output can be selected with the output polarity switch POL (bit 4 of register 9).

#### **MODULATION CURRENT GENERATOR**

The modulation current generator provides the current for the current modulator described above. The circuit is digitally controlled by the 2-wire interface block.

An 8-bit wide control bus, MODC[0..7] (register 1), is used to set the desired modulation current. Furthermore, four modulation current ranges can be selected by means of MODRNG1 (bit 1 of register 13) and MODRNG0 (bit 0 of register 13).

The modulation current can be disabled by setting the DIS input pin to a high level. The modulation current is also disabled in a fault condition if the fault detection enable register flag FLTEN is set (bit 3 of register 0).

#### DC OFFSET CANCELLATION AND CROSS POINT CONTROL

The ONET8501V has DC offset cancellation to compensate for internal offset voltages. The offset cancellation can be disabled by setting OCDIS = 1 (bit 2 of register 9). Disabling the offset cancellation enables the output crossing point to be adjusted from 35% to 65% of the output eye diagram. The crossing point can be moved toward the one level be setting CPSGN = 1 (bit 7 of register 4) and it can be moved toward the zero level by setting CPSGN = 0. The percentage of shift depends upon the register settings CPADJ[0..6] (register 4).

## **BIAS CURRENT GENERATION AND APC LOOP**

The bias current generation and APC loop are controlled by means of the 2-wire interface. In open loop operation, selected by setting OLENA = 1 (bit 4 of register 0) the bias current is set directly by the 8-bit wide control word BIASC[0..7] (register 2). In automatic power control mode, selected by setting OLENA = 0, the bias current depends on the register settings BIASC[0..7] and the coupling ratio (CR) between the VCSEL bias current and the photodiode current. CR =  $I_{BIAS-VCSEL}/I_{PD}$ .

Three photodiode current ranges can be selected by means of the PDRNG[1..0] bits (register 0). The photodiode range should be chosen to keep the laser bias control DAC, BIASC[0..7], close to the center of its range. This keeps the laser bias current set point resolution high.

For details regarding the bias current setting in open- as well as in closed-loop mode, see Table 16.

In closed-loop mode, the photodiode polarity bit, PDPOL (bit 0 of register 0), must be set for common-anode or common-cathode configuration to ensure proper operation.

### ANALOG REFERENCE AND TEMPERATURE SENSOR

The ONET8501V VCSEL driver is supplied by a single 3.3V10% supply voltage connected to the VCC pins. This voltage is referred to ground (GND).

On-chip bandgap voltage circuitry generates a reference voltage, independent of the supply voltage, from which all other internally required voltages and bias currents are derived.

An external zero temperature coefficient resistor must be connected from the RZTC pin of the device to ground (GND). This resistor is used to generate a precise, zero-TC current which is required as a reference current for the on-chip DACs.

In order to minimize the module component count, the ONET8501V provides an on-chip temperature sensor. The output voltage of the temperature sensor is available at the TS pin. Due to the die temperature of the 8501V and for high accuracy applications, the use of an external temperature sensor may be required. However, in order to improve the part-to-part accuracy of the sensor, the offset voltage and temperature slope can be adjusted through the 2-wire interface. The offset voltage can be adjusted by means of the TSSH[0..3] bits (register 10) and the direction of the offset can be set by the sign bit TSHSGN (bit 4 of register 10). The temperature slope can be adjusted by means of the TSSL[0..3] bits (register 11) and the sign bit TSLSGN (bit 4 of register 11).

The temperature sensor can be disabled by setting TSDIS = 1 (bit 1 of register 9).

#### **POWER-ON RESET**

The ONET8501V has power on reset circuitry which ensures that all registers are reset to zero during startup. After the power-on to initialize time ( $t_{INIT1}$ ), the internal registers are ready to be loaded. The part is ready to transmit data after the initialize to transmit time ( $t_{INIT2}$ ), assuming that the chip enable bit ENA is set to 1 and the disable pin DIS is low.

The ONET8501V can be disabled using either the ENA control register bit or the disable pin DIS. In both cases the internal registers are not reset. After the disable pin DIS is set low and/or the enable bit ENA is set back to 1, the part returns to its prior output settings.

## 2-WIRE INTERFACE AND CONTROL LOGIC

The ONET8501V uses a 2-wire serial interface for digital control. The two circuit inputs, SDA and SCK, are driven, respectively, by the serial data and serial clock from a microcontroller, for example. Both inputs include  $500k\Omega$  pull-up resistors to VCC. For driving these inputs, an open drain output is recommended.

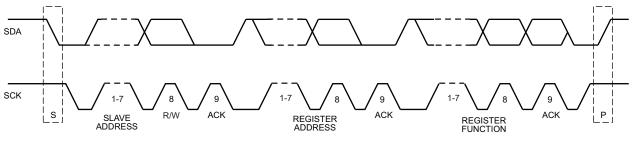

The 2-wire interface allows write access to the internal memory map to modify control registers and read access to read out the control signals. The ONET8501V is a slave device only which means that it cannot initiate a transmission itself; it always relies on the availability of the SCK signal for the duration of the transmission. The master device provides the clock signal as well as the START and STOP commands. The protocol for a data transmission is as follows:

- 1. START command

- 2. 7 bit slave address (0001000) followed by an eighth bit which is the data direction bit (R/W). A zero indicates a WRITE and a 1 indicates a READ.

- 3. 8 bit register address

- 4. 8 bit register data word

- 5. STOP command

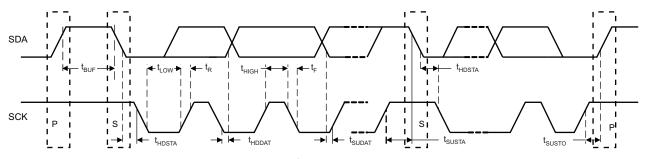

Regarding timing, the ONET8501V is I<sup>2</sup>C compatible. The typical timing is shown in Figure 2 and a complete data transfer is shown in Figure 3. Parameters for Figure 2 are defined in Table 1.

#### Bus Idle: Both SDA and SCK lines remain HIGH

**Start Data Transfer:** A change in the state of the SDA line, from HIGH to LOW, while the SCK line is HIGH, defines a START condition (S). Each data transfer is initiated with a START condition.

**Stop Data Transfer:** A change in the state of the SDA line from LOW to HIGH while the SCK line is HIGH defines a STOP condition (P). Each data transfer is terminated with a STOP condition; however, if the master still wishes to communicate on the bus, it can generate a repeated START condition and address another slave without first generating a STOP condition.

**Data Transfer:** Only one data byte can be transferred between a START and a STOP condition. The receiver acknowledges the transfer of data.