# Single/Dual Digital Potentiometer with SPI<sup>TM</sup> Interface

#### Features

- · 256 taps for each potentiometer

- Potentiometer values for 10 kΩ, 50 kΩ and 100 kΩ

- · Single and dual versions

- SPI<sup>™</sup> serial interface (mode 0,0 and 1,1)

- ±1 LSB max INL & DNL

- Low power CMOS technology

- 1 µA maximum supply current in static operation

- Multiple devices can be daisy-chained together (MCP42XXX only)

- Shutdown feature open circuits of all resistors for maximum power savings

- Hardware shutdown pin available on MCP42XXX only

- Single supply operation (2.7V 5.5V)

- Industrial temperature range: -40°C to +85°C

- Extended temperature range: -40°C to +125°C

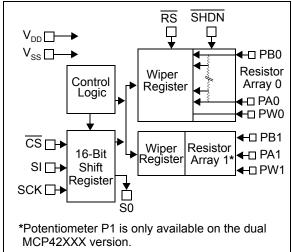

#### **Block Diagram**

#### Description

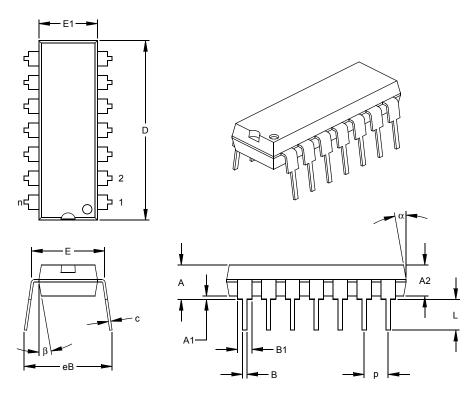

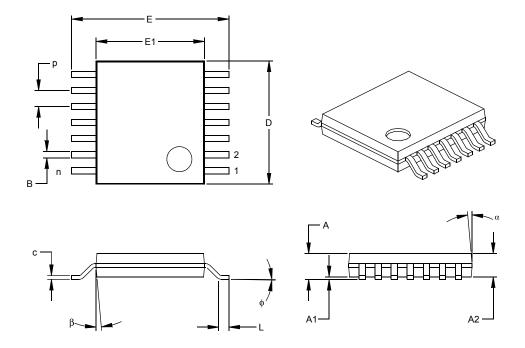

The MCP41XXX and MCP42XXX devices are 256position, digital potentiometers available in 10 k $\Omega$ , 50 k $\Omega$  and 100 k $\Omega$  resistance versions. The MCP41XXX is a single-channel device and is offered in an 8-pin PDIP or SOIC package. The MCP42XXX contains two independent channels in a 14-pin PDIP, SOIC TSSOP package. The wiper position of the or MCP41XXX/42XXX varies linearly and is controlled via an industry-standard SPI interface. The devices consume <1 µA during static operation. A software shutdown feature is provided that disconnects the "A" terminal from the resistor stack and simultaneously connects the wiper to the "B" terminal. In addition, the dual MCP42XXX has a SHDN pin that performs the same function in hardware. During shutdown mode, the contents of the wiper register can be changed and the potentiometer returns from shutdown to the new value. The wiper is reset to the mid-scale position (80h) upon power-up. The  $\overline{RS}$  (reset) pin implements a hardware reset and also returns the wiper to mid-scale. The MCP42XXX SPI interface includes both the SI and SO pins, allowing daisy-chaining of multiple devices. Channel-to-channel resistance matching on the MCP42XXX varies by less than 1%. These devices operate from a single 2.7 - 5.5V supply and are specified over the extended and industrial temperature ranges.

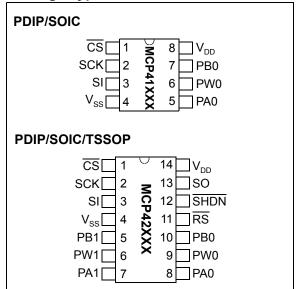

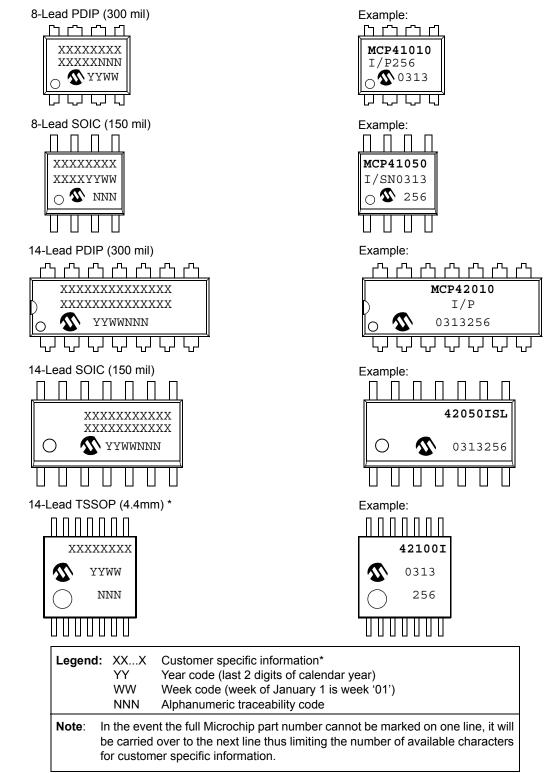

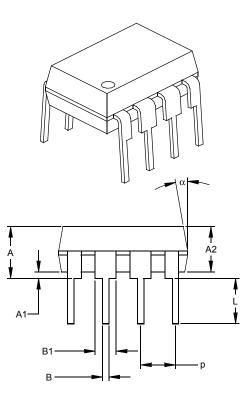

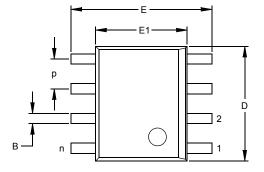

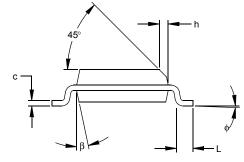

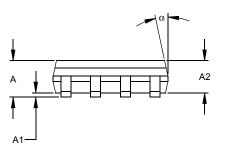

#### Package Types

## 1.0 ELECTRICAL CHARACTERISTICS

### DC CHARACTERISTICS: 10 k $\Omega$ VERSION

Electrical Characteristics: Unless otherwise indicated,  $V_{DD}$  = +2.7V to 5.5V,  $T_A$  = -40°C to +85°C (TSSOP devices are only specified at +25°C and +85°C). Typical specifications represent values for  $V_{DD}$  = 5V,  $V_{SS}$  = 0V,  $V_B$  = 0V,  $T_A$  = +25°C.

| Parameters                                      | Sym                                | Min                    | Тур          | Max             | Units  | Conditions                                                                                                                                            |

|-------------------------------------------------|------------------------------------|------------------------|--------------|-----------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rheostat Mode                                   |                                    |                        |              |                 |        |                                                                                                                                                       |

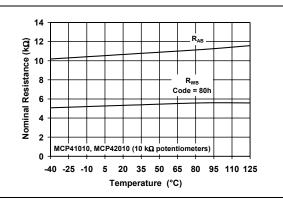

| Nominal Resistance                              | R                                  | 8                      | 10           | 12              | kΩ     | T <sub>A</sub> = +25°C (Note 1)                                                                                                                       |

| Rheostat Differential Non Linearity             | R-DNL                              | -1                     | ±1/4         | +1              | LSB    | Note 2                                                                                                                                                |

| Rheostat Integral Non Linearity                 | R-INL                              | -1                     | ±1/4         | +1              | LSB    | Note 2                                                                                                                                                |

| Rheostat Tempco                                 | $\Delta R_{AB} / \Delta T$         | _                      | 800          | _               | ppm/°C |                                                                                                                                                       |

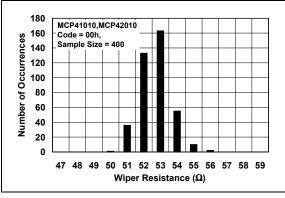

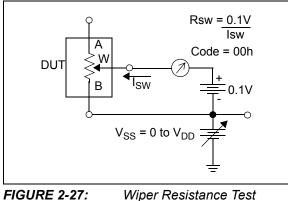

| Wiper Resistance                                | R <sub>W</sub>                     | _                      | 52           | 100             | Ω      | $V_{DD}$ = 5.5V, $I_{W}$ = 1 mA, code 00h                                                                                                             |

|                                                 | R <sub>W</sub>                     | _                      | 73           | 125             | Ω      | $V_{DD}$ = 2.7V, $I_{W}$ = 1 mA, code 00h                                                                                                             |

| Wiper Current                                   | IW                                 | -1                     | _            | +1              | mA     |                                                                                                                                                       |

| Nominal Resistance Match                        | $\Delta R/R$                       | _                      | 0.2          | 1               | %      | <b>MCP42010 only</b> , P0 to P1; T <sub>A</sub> = +25°C                                                                                               |

| Potentiometer Divider                           |                                    |                        |              |                 |        |                                                                                                                                                       |

| Resolution                                      | Ν                                  | 8                      |              |                 | Bits   |                                                                                                                                                       |

| Monotonicity                                    | Ν                                  | 8                      | _            | _               | Bits   |                                                                                                                                                       |

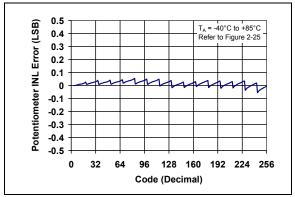

| Differential Non-Linearity                      | DNL                                | -1                     | ±1/4         | +1              | LSB    | Note 3                                                                                                                                                |

| Integral Non-Linearity                          | INL                                | -1                     | ±1/4         | +1              | LSB    | Note 3                                                                                                                                                |

| Voltage Divider Tempco                          | $\Delta V_W / \Delta T$            | _                      | 1            | _               | ppm/°C | Code 80h                                                                                                                                              |

| Full Scale Error                                | V <sub>WFSE</sub>                  | -2                     | -0.7         | 0               | LSB    | Code FFh, V <sub>DD</sub> = 5V, see Figure 2-25                                                                                                       |

|                                                 | V <sub>WFSE</sub>                  | -2                     | -0.7         | 0               | LSB    | Code FFh, V <sub>DD</sub> = 3V, see Figure 2-25                                                                                                       |

| Zero Scale Error                                | V <sub>WZSE</sub>                  | 0                      | +0.7         | +2              | LSB    | Code 00h, V <sub>DD</sub> = 5V, see Figure 2-25                                                                                                       |

|                                                 | V <sub>WZSE</sub>                  | 0                      | +0.7         | +2              | LSB    | Code 00h, V <sub>DD</sub> = 3V, see Figure 2-25                                                                                                       |

| Resistor Terminals                              |                                    |                        |              |                 |        |                                                                                                                                                       |

| Voltage Range                                   | V <sub>A,B,W</sub>                 | 0                      |              | V <sub>DD</sub> |        | Note 4                                                                                                                                                |

| Capacitance (C <sub>A</sub> or C <sub>B</sub> ) |                                    | _                      | 15           | _               | pF     | f = 1 MHz, Code = 80h, see Figure 2-30                                                                                                                |

| Capacitance                                     | Cw                                 | _                      | 5.6          | _               | pF     | f = 1 MHz, Code = 80h, see Figure 2-30                                                                                                                |

| Dynamic Characteristics (All dynamic            | characteristi                      | cs use V <sub>DD</sub> | o = 5V)      |                 |        |                                                                                                                                                       |

| Bandwidth -3dB                                  | BW                                 |                        | 1            |                 | MHz    | V <sub>B</sub> = 0V, Measured at Code 80h,<br>Output Load = 30 PF                                                                                     |

| Settling Time                                   | t <sub>S</sub>                     | -                      | 2            | _               | μS     | $V_A = V_{DD}, V_B = 0V, \pm 1\%$ Error Band, Transition<br>from Code 00h to Code 80h, Output Load = 30 pF                                            |

| Resistor Noise Voltage                          | e <sub>NWB</sub>                   | _                      | 9            | _               | nV/√Hz | V <sub>A</sub> = Open, Code 80h, f =1 kHz                                                                                                             |

| Crosstalk                                       | CT                                 | -                      | -95          | _               | dB     | V <sub>A</sub> = V <sub>DD</sub> , V <sub>B</sub> = 0V (Note 5)                                                                                       |

| Digital Inputs/Outputs (CS, SCK, SI, SC         | 0) See Figure                      | 2-12 for R             | S and SHI    | ON pin ope      | ration |                                                                                                                                                       |

| Schmitt Trigger High-Level Input Voltage        | V <sub>IH</sub>                    | $0.7V_{DD}$            |              |                 | V      |                                                                                                                                                       |

| Schmitt Trigger Low-Level Input Voltage         | V <sub>IL</sub>                    |                        |              | $0.3V_{DD}$     | V      |                                                                                                                                                       |

| Hysteresis of Schmitt Trigger Inputs            | V <sub>HYS</sub>                   | _                      | $0.05V_{DD}$ | _               |        |                                                                                                                                                       |

| Low-Level Output Voltage                        | V <sub>OL</sub>                    | -                      | -            | 0.40            | V      | I <sub>OL</sub> = 2.1 mA, V <sub>DD</sub> = 5V                                                                                                        |

| High-Level Output Voltage                       | V <sub>OH</sub>                    | V <sub>DD</sub> - 0.5  | _            | _               | V      | I <sub>OH</sub> = -400 μA, V <sub>DD</sub> = 5V                                                                                                       |

| Input Leakage Current                           | I <sub>LI</sub>                    | -1                     | _            | +1              | μA     | $\overline{\text{CS}}$ = V <sub>DD</sub> , V <sub>IN</sub> = V <sub>SS</sub> or V <sub>DD</sub> , includes V <sub>A</sub> $\overline{\text{SHDN}}$ =0 |

| Pin Capacitance (All inputs/outputs)            | C <sub>IN</sub> , C <sub>OUT</sub> |                        | 10           |                 | pF     | V <sub>DD</sub> = 5.0V, T <sub>A</sub> = +25°C, f <sub>c</sub> = 1 MHz                                                                                |

| Power Requirements                              |                                    |                        |              |                 |        |                                                                                                                                                       |

| Operating Voltage Range                         | V <sub>DD</sub>                    | 2.7                    | _            | 5.5             | V      |                                                                                                                                                       |

| Supply Current, Active                          | I <sub>DDA</sub>                   |                        | 340          | 500             | μA     | V <sub>DD</sub> = 5.5V, <del>CS</del> = V <sub>SS</sub> , f <sub>SCK</sub> = 10 MHz,<br>SO = Open, Code FFh <b>(Note 6)</b>                           |

| Supply Current, Static                          | I <sub>DDS</sub>                   | _                      | 0.01         | 1               | μA     | $\overline{\text{CS}}$ , $\overline{\text{SHDN}}$ , $\overline{\text{RS}}$ = V <sub>DD</sub> = 5.5V, SO = Open (Note 6)                               |

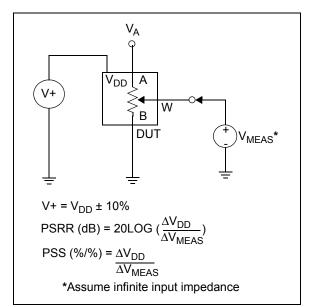

| Power Supply Sensitivity                        | PSS                                | —                      | 0.0015       | 0.0035          | %/%    | $V_{DD} = 4.5V - 5.5V$ , $V_A = 4.5V$ , Code 80h                                                                                                      |

|                                                 | PSS                                | _                      | 0.0015       | 0.0035          | %/%    | V <sub>DD</sub> = 2.7V - 3.3V, V <sub>A</sub> = 2.7V, Code 80h                                                                                        |

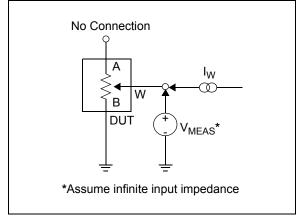

Note 1:  $V_{AB} = V_{DD}$ , no connection on wiper.

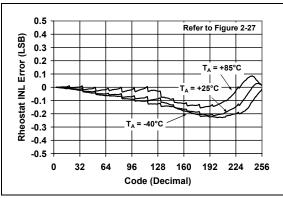

2: Rheostat position non-linearity R-INL is the deviation from an ideal value measured between the maximum resistance and the minimum resistance wiper positions. R-DNL measures the relative step change from the ideal between successive tap positions.  $I_W = 50 \ \mu A$  for  $V_{DD} = 3V$  and  $I_W = 400 \ \mu A$  for  $V_{DD} = 5V$  for 10 k $\Omega$  version. See Figure 2-26 for test circuit.

3: INL and DNL are measured at  $V_W$  with the device configured in the voltage divider or potentiometer mode.  $V_A = V_{DD}$  and  $V_B = 0V$ . DNL specification limits of ±1 LSB max are specified monotonic operating conditions. See Figure 2-25 for test circuit.

4: Resistor terminals A,B and W have no restrictions on polarity with respect to each other. Full-scale and zero-scale error were measured using Figure 2-25.

5: Measured at V<sub>W</sub> pin where the voltage on the adjacent V<sub>W</sub> pin is swinging full-scale.

6: Supply current is independent of current through the potentiometers.

#### DC CHARACTERISTICS: 50 kΩ VERSION

| +85°C). Typical specifications represent v<br>Parameters | Sym                                | Min                     | Тур                 | Max                | Units             | Conditions                                                                                                                                                                                    |

|----------------------------------------------------------|------------------------------------|-------------------------|---------------------|--------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                          | Sym                                | IAIIII                  | iyp                 | WIAX               | Units             | Conditions                                                                                                                                                                                    |

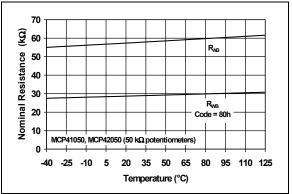

| Rheostat Mode Nominal Resistance                         | R                                  | 35                      | 50                  | 65                 | kΩ                | T <sub>A</sub> = +25°C (Note 1)                                                                                                                                                               |

|                                                          |                                    |                         |                     |                    | LSB               | Α                                                                                                                                                                                             |

| Rheostat Differential Non-Linearity                      | R-DNL                              | -1                      | ±1/4                | +1                 |                   | Note 2                                                                                                                                                                                        |

| Rheostat Integral Non-Linearity                          | R-INL                              | -1                      | ±1/4                | +1                 | LSB               | Note 2                                                                                                                                                                                        |

| Rheostat Tempco<br>Wiper Resistance                      | ΔR <sub>AB</sub> /ΔT               |                         | 800<br>125          | 175                | ppm/°C            | $V_{1} = 5.5V_{1} = 1.00$ code 00b                                                                                                                                                            |

| wiper Resistance                                         | RW                                 |                         | 125                 | 250                | Ω<br>Ω            | $V_{DD} = 5.5V$ , $I_W = 1$ mA, code 00h                                                                                                                                                      |

| Wiper Current                                            | R <sub>W</sub>                     |                         |                     | +1                 | mA                | $V_{DD}$ = 2.7V, $I_W$ = 1 mA, code 00h                                                                                                                                                       |

| •                                                        |                                    | -1                      |                     | 1                  | 111A<br>%         | MCD42050 and $P0 to P1:T = +25^{\circ}C$                                                                                                                                                      |

| Nominal Resistance Match Potentiometer Divider           | ∆R/R                               |                         | 0.2                 | 1                  | 70                | <b>MCP42050 only</b> , P0 to P1;T <sub>A</sub> = +25°C                                                                                                                                        |

| Resolution                                               | N                                  | 8                       |                     |                    | Bits              |                                                                                                                                                                                               |

|                                                          | N                                  | 8                       |                     |                    |                   |                                                                                                                                                                                               |

| Monotonicity<br>Differential Non-Linearity               | DNL                                | -1                      | <br>±1/4            | +1                 | Bits<br>LSB       | Note 3                                                                                                                                                                                        |

|                                                          | INL                                | -1                      | ±1/4<br>±1/4        | +1                 | LSB               | Note 3                                                                                                                                                                                        |

| Integral Non-Linearity                                   |                                    | -1                      | ±1/4                | +1                 |                   |                                                                                                                                                                                               |

| Voltage Divider Tempco                                   | $\Delta V_W / \Delta T$            | _                       |                     |                    | ppm/°C            | Code 80h                                                                                                                                                                                      |

| Full-Scale Error                                         | V <sub>WFSE</sub>                  | -1                      | -0.25               | 0                  | LSB               | Code FFh, $V_{DD}$ = 5V, see Figure 2-25                                                                                                                                                      |

| Zana Oacia Eman                                          | V <sub>WFSE</sub>                  | -1                      | -0.35               | 0                  | LSB               | Code FFh, $V_{DD}$ = 3V, see Figure 2-25                                                                                                                                                      |

| Zero-Scale Error                                         | V <sub>WZSE</sub>                  | 0                       | +0.25               | +1                 | LSB               | Code 00h, $V_{DD}$ = 5V, see Figure 2-25                                                                                                                                                      |

| De siste a Terreiro de                                   | V <sub>WZSE</sub>                  | 0                       | +0.35               | +1                 | LSB               | Code 00h, $V_{DD}$ = 3V, see Figure 2-25                                                                                                                                                      |

| Resistor Terminals                                       | N/                                 | 0                       |                     | M                  | 1                 |                                                                                                                                                                                               |

| Voltage Range                                            | $V_{A,B,W}$                        | 0                       |                     | $V_{DD}$           |                   | Note 4                                                                                                                                                                                        |

| Capacitance (C <sub>A</sub> or C <sub>B</sub> )          |                                    |                         | 11                  |                    | pF                | f =1 MHz, Code = 80h, see Figure 2-30                                                                                                                                                         |

| Capacitance                                              | C <sub>W</sub>                     | —                       | 5.6                 | _                  | pF                | f =1 MHz, Code = 80h, see Figure 2-30                                                                                                                                                         |

| Dynamic Characteristics (All dynamic                     |                                    | ics use v <sub>DE</sub> | -                   |                    |                   |                                                                                                                                                                                               |

| Bandwidth -3dB                                           | BW                                 | —                       | 280                 | -                  | MHz               | V <sub>B</sub> = 0V, Measured at Code 80h,<br>Output Load = 30 PF                                                                                                                             |

| Settling Time                                            | t <sub>S</sub>                     | —                       | 8                   | —                  | μS                | $V_A = V_{DD}$ , $V_B = 0V$ , ±1% Error Band, Transition from Code 00h to Code 80h, Output Load = 30 pF                                                                                       |

| Resistor Noise Voltage                                   | e <sub>NWB</sub>                   | —                       | 20                  | _                  | nV/√Hz            | V <sub>A</sub> = Open, Code 80h, f =1 kHz                                                                                                                                                     |

| Crosstalk                                                | CT                                 | _                       | -95                 | _                  | dB                | V <sub>A</sub> = V <sub>DD</sub> , V <sub>B</sub> = 0V (Note 5)                                                                                                                               |

| Digital Inputs/Outputs (CS, SCK, SI, SC                  | ) See Figure                       | 2-12 for R              | S and SHE           | ON pin ope         | ration.           | •                                                                                                                                                                                             |

| Schmitt Trigger High-Level Input Voltage                 | VIH                                | 0.7V <sub>DD</sub>      | —                   | _                  | V                 |                                                                                                                                                                                               |

| Schmitt Trigger Low-Level Input Voltage                  | V <sub>IL</sub>                    | —                       | _                   | 0.3V <sub>DD</sub> | V                 |                                                                                                                                                                                               |

| Hysteresis of Schmitt Trigger Inputs                     | V <sub>HYS</sub>                   | —                       | 0.05V <sub>DD</sub> |                    |                   |                                                                                                                                                                                               |

| Low-Level Output Voltage                                 | V <sub>OL</sub>                    | _                       | _                   | 0.40               | V                 | I <sub>OL</sub> = 2.1 mA, V <sub>DD</sub> = 5V                                                                                                                                                |

| High-Level Output Voltage                                | V <sub>OH</sub>                    | V <sub>DD</sub> - 0.5   | _                   | _                  | V                 | I <sub>OH</sub> = -400 μA, V <sub>DD</sub> = 5V                                                                                                                                               |

| Input Leakage Current                                    | ILI                                | -1                      | _                   | +1                 | μA                | $\overline{\text{CS}} = \text{V}_{\text{DD}}, \text{V}_{\text{IN}} = \text{V}_{\text{SS}} \text{ or } \text{V}_{\text{DD}}, \text{ includes } \text{V}_{\text{A}} \overline{\text{SHDN}} = 0$ |

| Pin Capacitance (All inputs/outputs)                     | C <sub>IN</sub> , C <sub>OUT</sub> | _                       | 10                  | _                  | pF                | $V_{DD} = 5.0V, T_A = +25^{\circ}C, f_c = 1 \text{ MHz}$                                                                                                                                      |

| Power Requirements                                       | - 110/ - 001                       | 1                       | -                   |                    | 1 P.              |                                                                                                                                                                                               |

| Operating Voltage Range                                  | V <sub>DD</sub>                    | 2.7                     | _                   | 5.5                | V                 |                                                                                                                                                                                               |

| Supply Current, Active                                   | I <sub>DDA</sub>                   |                         | 340                 | 500                | μA                | V <sub>DD</sub> = 5.5V,                                                                                                                                                                       |

| Supply Current, Static                                   |                                    | _                       | 0.01                | 1                  | μA                | $\overline{\text{CS}}$ , $\overline{\text{SHDN}}$ , $\overline{\text{RS}} = V_{\text{DD}} = 5.5V$ , $SO = Open$ (Note 6)                                                                      |

| Power Supply Sensitivity                                 | PSS                                | _                       | 0.0015              | 0.0035             | μ <u>γ</u><br>%/% | $V_{DD} = 4.5V - 5.5V$ , $V_A = 4.5V$ , Code 80h                                                                                                                                              |

| cappij constituty                                        |                                    |                         | 0.0010              | 0.0000             | , 31 70           | $V_{DD} = 2.7V - 3.3V, V_A = 2.7V, Code 80h$                                                                                                                                                  |

Note 1:

$V_{AB} = V_{DD}$ , no connection on wiper. Rheostat position non-linearity R-INL is the deviation from an ideal value measured between the maximum resistance and the minimum resistance wiper positions. R-DNL measures the relative step change from the ideal between successive tap positions. I<sub>W</sub> = V<sub>DD</sub>/R for 2: +3V or +5V for 50 k $\!\Omega$  version. See Figure 2-26 for test circuit.

INL and DNL are measured at  $V_W$  with the device configured in the voltage divider or potentiometer mode.  $V_A = V_{DD}$  and  $V_B = 0$ V. DNL 3: specification limits of ±1 LSB max are specified monotonic operating conditions. See Figure 2-25 for test circuit.

4: Resistor terminals A,B and W have no restrictions on polarity with respect to each other. Full-scale and zero-scale error were measured using Figure 2-25.

Measured at  $V_W$  pin where the voltage on the adjacent  $V_W$  pin is swinging full scale. 5:

6: Supply current is independent of current through the potentiometers.

### DC CHARACTERISTICS: 100 kΩ VERSION

| Parameters                               | Sym                                | Min                     | Тур                 | Max             | Units   | Conditions                                                                                                                                            |

|------------------------------------------|------------------------------------|-------------------------|---------------------|-----------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rheostat Mode                            |                                    |                         |                     |                 |         | •                                                                                                                                                     |

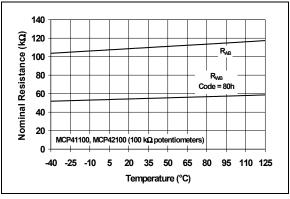

| Nominal Resistance                       | R                                  | 70                      | 100                 | 130             | kΩ      | T <sub>A</sub> = +25°C (Note 1)                                                                                                                       |

| Rheostat Differential Non-Linearity      | R-DNL                              | -1                      | ±1/4                | +1              | LSB     | Note 2                                                                                                                                                |

| Rheostat Integral Non-Linearity          | R-INL                              | -1                      | ±1/4                | +1              | LSB     | Note 2                                                                                                                                                |

| Rheostat Tempco                          | $\Delta R_{AB} / \Delta T$         | _                       | 800                 | _               | ppm/°C  |                                                                                                                                                       |

| Wiper Resistance                         | R <sub>W</sub>                     | _                       | 125                 | 175             | Ω       | $V_{DD}$ = 5.5V, $I_W$ = 1 mA, code 00h                                                                                                               |

|                                          | R <sub>W</sub>                     | _                       | 175                 | 250             | Ω       | $V_{DD}$ = 2.7V, $I_W$ = 1 mA, code 00h                                                                                                               |

| Wiper Current                            | IW                                 | -1                      | _                   | +1              | mA      |                                                                                                                                                       |

| Nominal Resistance Match                 | $\Delta R/R$                       | _                       | 0.2                 | 1               | %       | MCP42010 only, P0 to P1;T <sub>A</sub> = +25°C                                                                                                        |

| Potentiometer Divider                    |                                    |                         |                     |                 |         | •                                                                                                                                                     |

| Resolution                               | Ν                                  | 8                       | _                   | _               | Bits    |                                                                                                                                                       |

| Monotonicity                             | Ν                                  | 8                       | _                   | _               | Bits    |                                                                                                                                                       |

| Differential Non-Linearity               | DNL                                | -1                      | ±1/4                | +1              | LSB     | Note 3                                                                                                                                                |

| Integral Non-Linearity                   | INL                                | -1                      | ±1/4                | +1              | LSB     | Note 3                                                                                                                                                |

| Voltage Divider Tempco                   | $\Delta V_W / \Delta T$            | _                       | 1                   | _               | ppm/°C  | Code 80h                                                                                                                                              |

| Full-Scale Error                         | V <sub>WFSE</sub>                  | -1                      | -0.25               | 0               | LSB     | Code FFh, V <sub>DD</sub> = 5V, see Figure 2-25                                                                                                       |

|                                          | V <sub>WFSE</sub>                  | -1                      | -0.35               | 0               | LSB     | Code FFh, V <sub>DD</sub> = 3V, see Figure 2-25                                                                                                       |

| Zero-Scale Error                         | V <sub>WZSE</sub>                  | 0                       | +0.25               | +1              | LSB     | Code 00h, V <sub>DD</sub> = 5V, see Figure 2-25                                                                                                       |

|                                          | V <sub>WZSE</sub>                  | 0                       | +0.35               | +1              | LSB     | Code 00h, V <sub>DD</sub> = 3V, see Figure 2-25                                                                                                       |

| Resistor Terminals                       |                                    |                         |                     |                 |         |                                                                                                                                                       |

| Voltage Range                            | V <sub>A,B,W</sub>                 | 0                       | -                   | V <sub>DD</sub> |         | Note 4                                                                                                                                                |

| Capacitance (CA or CB)                   |                                    | —                       | 11                  |                 | pF      | f =1 MHz, Code = 80h, see Figure 2-30                                                                                                                 |

| Capacitance                              | C <sub>W</sub>                     | —                       | 5.6                 |                 | pF      | f =1 MHz, Code = 80h, see Figure 2-30                                                                                                                 |

| Dynamic Characteristics (All dynamic     | characteristi                      | ics use V <sub>DE</sub> | <sub>0</sub> = 5V.) |                 |         |                                                                                                                                                       |

| Bandwidth -3dB                           | BW                                 | —                       | 145                 |                 | MHz     | V <sub>B</sub> = 0V, Measured at Code 80h,<br>Output Load = 30 PF                                                                                     |

| Settling Time                            | t <sub>S</sub>                     | —                       | 18                  |                 | μS      | $V_A = V_{DD}, V_B = 0V, \pm 1\%$ Error Band, Transition<br>from Code 00h to Code 80h, Output Load = 30 pF                                            |

| Resistor Noise Voltage                   | e <sub>NWB</sub>                   | —                       | 29                  | _               | nV/√Hz  | V <sub>A</sub> = Open, Code 80h, f =1 kHz                                                                                                             |

| Crosstalk                                | CT                                 | —                       | -95                 |                 | dB      | $V_{A} = V_{DD}, V_{B} = 0V$ (Note 5)                                                                                                                 |

| Digital Inputs/Outputs (CS, SCK, SI, SC  | )) See Figure                      | e 2-12 for R            | S and SHE           | ON pin ope      | ration. |                                                                                                                                                       |

| Schmitt Trigger High-Level Input Voltage | V <sub>IH</sub>                    | $0.7V_{DD}$             |                     |                 | V       |                                                                                                                                                       |

| Schmitt Trigger Low-Level Input Voltage  | V <sub>IL</sub>                    | —                       | —                   | $0.3V_{DD}$     | V       |                                                                                                                                                       |

| Hysteresis of Schmitt Trigger Inputs     | V <sub>HYS</sub>                   | —                       | $0.05V_{DD}$        |                 |         |                                                                                                                                                       |

| Low-Level Output Voltage                 | V <sub>OL</sub>                    | _                       | _                   | 0.40            | V       | I <sub>OL</sub> = 2.1 mA, V <sub>DD</sub> = 5V                                                                                                        |

| High-Level Output Voltage                | V <sub>OH</sub>                    | V <sub>DD</sub> - 0.5   | _                   | _               | V       | I <sub>OH</sub> = -400 μA, V <sub>DD</sub> = 5V                                                                                                       |

| Input Leakage Current                    | ILI                                | -1                      | _                   | +1              | μA      | $\overline{\text{CS}}$ = V <sub>DD</sub> , V <sub>IN</sub> = V <sub>SS</sub> or V <sub>DD</sub> , includes V <sub>A</sub> $\overline{\text{SHDN}}$ =0 |

| Pin Capacitance (All inputs/outputs)     | C <sub>IN</sub> , C <sub>OUT</sub> | —                       | 10                  | _               | pF      | V <sub>DD</sub> = 5.0V, T <sub>A</sub> = +25°C, f <sub>c</sub> = 1 MHz                                                                                |

| Power Requirements                       |                                    | •                       |                     |                 | •       | •                                                                                                                                                     |

| Operating Voltage Range                  | V <sub>DD</sub>                    | 2.7                     | —                   | 5.5             | V       |                                                                                                                                                       |

| Supply Current, Active                   | I <sub>DDA</sub>                   | —                       | 340                 | 500             | μA      | V <sub>DD</sub> = 5.5V, <del>CS</del> = V <sub>SS</sub> , f <sub>SCK</sub> = 10 MHz,<br>SO = Open, Code FFh <b>(Note 6)</b>                           |

| Supply Current, Static                   | I <sub>DDS</sub>                   | _                       | 0.01                | 1               | μA      | $\overline{CS}$ , $\overline{SHDN}$ , $\overline{RS}$ = V <sub>DD</sub> = 5.5V, SO = Open (Note 6)                                                    |

| Power Supply Sensitivity                 | PSS                                | _                       | 0.0015              | 0.0035          | %/%     | $V_{DD} = 4.5V - 5.5V, V_A = 4.5V, Code 80h$                                                                                                          |

|                                          | PSS                                | i                       | 0.0015              | 0.0035          | %/%     | $V_{DD} = 2.7V - 3.3V, V_A = 2.7V, Code 80h$                                                                                                          |

Note 1:

$V_{AB} = V_{DD}$ , no connection on wiper. Rheostat position non-linearity R-INL is the deviation from an ideal value measured between the maximum resistance and the minimum resistance wiper positions. R-DNL measures the relative step change from the ideal between successive tap positions.  $I_W = 50 \ \mu$ A for  $V_{DD} = 3V$  and  $I_W = 400 \ \mu$ A for  $V_{DD} = 5V$  for 10 k $\Omega$  version. See Figure 2-26 for test circuit. INL and DNL are measured at  $V_W$  with the device configured in the voltage divider or potentiometer mode.  $V_A = V_{DD}$  and  $V_B = 0V$ . DNL specification limits of ±1 LSB max are specified monotonic operating conditions. See Figure 2-25 for test circuit. 2:

3:

Resistor terminals A,B and W have no restrictions on polarity with respect to each other. Full-scale and zero-scale error were measured 4: using Figure 2-25.

Measured at  $V_W$  pin where the voltage on the adjacent  $V_W$  pin is swinging full-scale. 5:

6: Supply current is independent of current through the potentiometers.

#### Absolute Maximum Ratings †

| V <sub>DD</sub>                                      | 7.0V                          |

|------------------------------------------------------|-------------------------------|

| All inputs and outputs w.r.t. $V_{SS} \ldots \ldots$ | 0.6V to V <sub>DD</sub> +1.0V |

| Storage temperature                                  | 60°C to +150°C                |

| Ambient temp. with power applied                     | 60°C to +125°C                |

| ESD protection on all pins                           | ≥ 2 kV                        |

**† Notice:** Stresses above those listed under "maximum ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

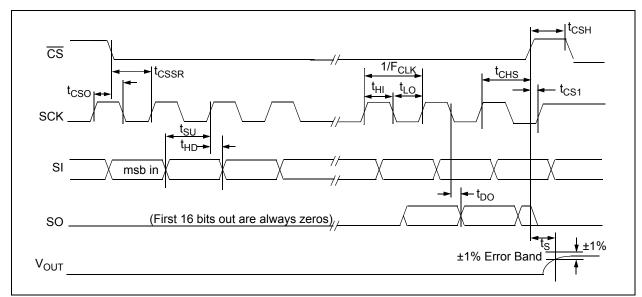

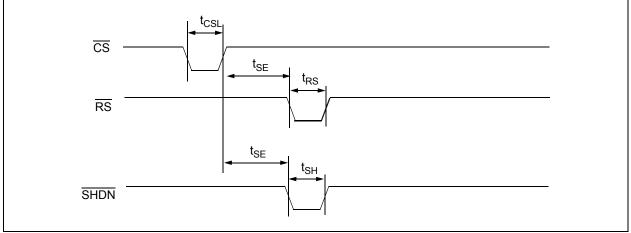

## AC TIMING CHARACTERISTICS

| Parameter                                  | Sym               | Min. | Тур. | Max. | Units | Conditions                      |

|--------------------------------------------|-------------------|------|------|------|-------|---------------------------------|

| Clock Frequency                            | F <sub>CLK</sub>  | _    | —    | 10   | MHz   | V <sub>DD</sub> = 5V (Note 1)   |

| Clock High Time                            | t <sub>HI</sub>   | 40   | -    | _    | ns    |                                 |

| Clock Low Time                             | t <sub>LO</sub>   | 40   | -    | _    | ns    |                                 |

| CS Fall to First Rising CLK Edge           | t <sub>CSSR</sub> | 40   | -    | _    | ns    |                                 |

| Data Input Setup Time                      | t <sub>SU</sub>   | 40   | -    | _    | ns    |                                 |

| Data Input Hold Time                       | t <sub>HD</sub>   | 10   | -    | _    | ns    |                                 |

| SCK Fall to SO Valid Propagation Delay     | t <sub>DO</sub>   |      | -    | 80   | ns    | C <sub>L</sub> = 30 pF (Note 2) |

| SCK Rise to CS Rise Hold Time              | t <sub>CHS</sub>  | 30   | —    | _    | ns    |                                 |

| SCK Rise to CS Fall Delay                  | t <sub>CS0</sub>  | 10   | -    | _    | ns    |                                 |

| CS Rise to CLK Rise Hold                   | t <sub>CS1</sub>  | 100  | -    | _    | ns    |                                 |

| CS High Time                               | t <sub>CSH</sub>  | 40   | —    | _    | ns    |                                 |

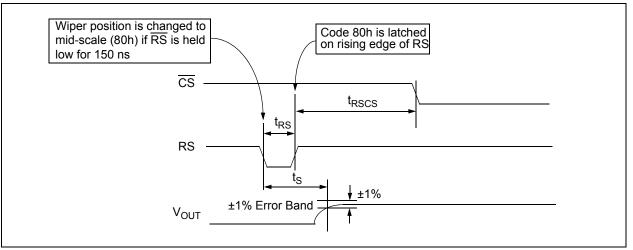

| Reset Pulse Width                          | t <sub>RS</sub>   | 150  | _    | _    | ns    | Note 2                          |

| RS Rising to CS Falling Delay Time         | t <sub>RSCS</sub> | 150  | _    | _    | ns    | Note 2                          |

| CS rising to RS or SHDN falling delay time | t <sub>SE</sub>   | 40   | —    | —    | ns    | Note 3                          |

| CS low time                                | t <sub>CSL</sub>  | 100  | _    | —    | ns    | Note 3                          |

| Shutdown Pulse Width                       | t <sub>SH</sub>   | 150  | —    |      | ns    | Note 3                          |

Note 1: When using the device in the daisy-chain configuration, maximum clock frequency is determined by a combination of propagation delay time ( $t_{DO}$ ) and data input setup time ( $t_{SU}$ ). Max. clock frequency is therefore ~ 5.8 MHz based on SCK rise and fall times of 5 ns,  $t_{HI}$  = 40 ns,  $t_{DO}$  = 80 ns and  $t_{SU}$  = 40 ns.

2: Applies only to the MCP42XXX devices.

3: Applies only when using hardware pins to exit software shutdown mode, MCP42XXX only.

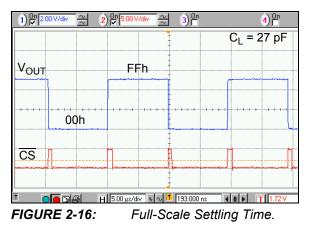

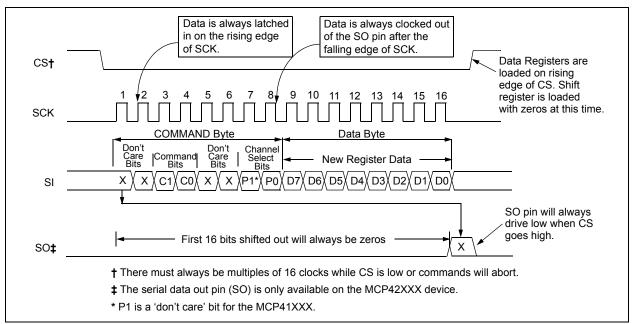

FIGURE 1-1: Detailed Serial interface Timing.

FIGURE 1-3: Software Shutdown Exit Timing.

### 2.0 TYPICAL PERFORMANCE CURVES

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore outside the warranted range.

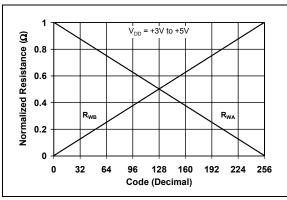

**FIGURE 2-1:** Normalized Wiper to End Terminal Resistance vs. Code.

FIGURE 2-2: Potentiometer INL Error vs. Code.

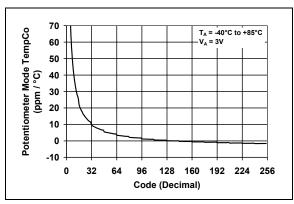

FIGURE 2-3: Potentiometer Mode Tempco vs. Code.

**FIGURE 2-4:** Nominal Resistance 10  $k\Omega$  vs. Temperature.

**FIGURE 2-5:** Nominal Resistance 50  $k\Omega$  vs. Temperature.

FIGURE 2-6: vs. Temperature.

Nominal Resistance 100 k $\Omega$

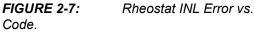

FIGURE 2-8: Rheostat Mode Tempco vs. Code.

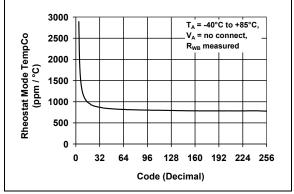

FIGURE 2-9:Static Current vs.Temperature.

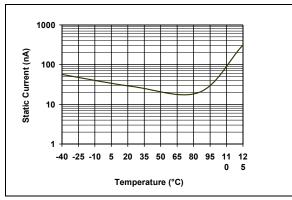

*FIGURE 2-10:* Active Supply Current vs. Temperature.

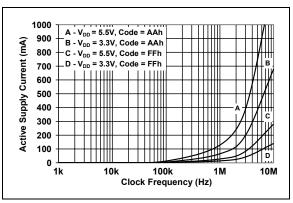

FIGURE 2-11: Active Supply Current vs. Clock Frequency.

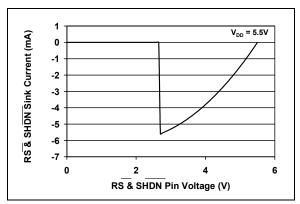

FIGURE 2-12: Reset & Shutdown Pins Current vs. Voltage.

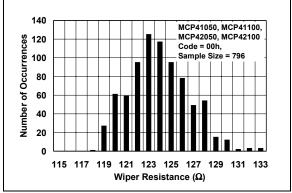

**FIGURE 2-14:** 50 k $\Omega$ , 100 k $\Omega$  Device Wiper Resistance Histogram.

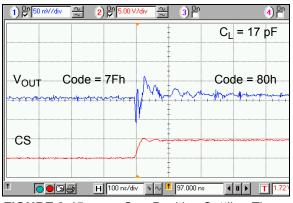

FIGURE 2-15:

One Position Settling Time.

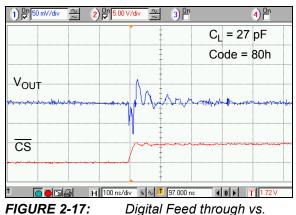

FIGURE 2-17: Digital Feed through v Time.

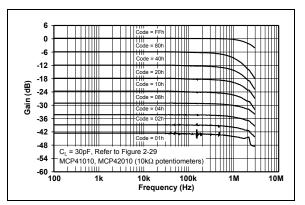

**FIGURE 2-18:** Gain vs. Frequency for 10  $k\Omega$  Potentiometer.

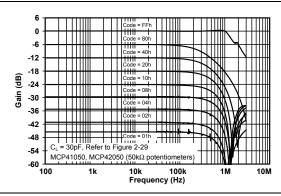

**FIGURE 2-19:** Gain vs. Frequency for  $50k\Omega$  Potentiometer.

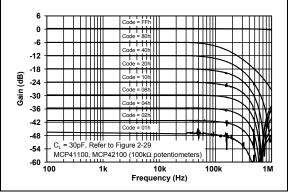

**FIGURE 2-20:** Gain vs. Frequency for  $100k\Omega$  Potentiometer.

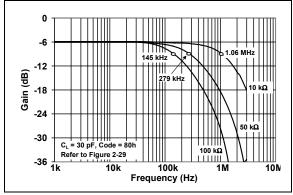

FIGURE 2-21: -3 dB Bandwidths.

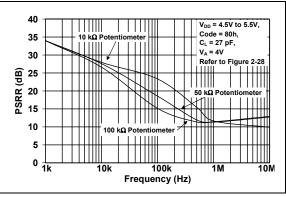

FIGURE 2-22: Power Supply Rejection Ratio vs. Frequency.

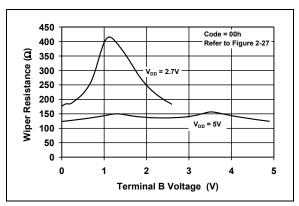

**FIGURE 2-23:** 10  $k\Omega$  Wiper Resistance vs. Voltage.

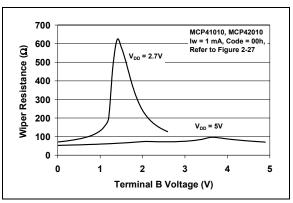

**FIGURE 2-24:** 50 k $\Omega$  & 100 k $\Omega$  Wiper Resistance vs. Voltage.

#### 2.1 Parametric Test Circuits

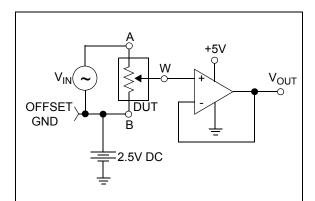

FIGURE 2-25: Potentiometer Divider Non-Linearity Error Test Circuit (DNL, INL).

**FIGURE 2-26:** Resistor Position Non-Linearity Error Test Circuit (Rheostat operation DNL, INL).

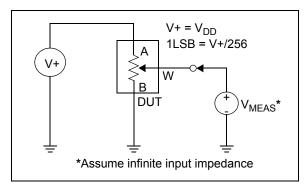

FIGURE 2-27: Circuit.

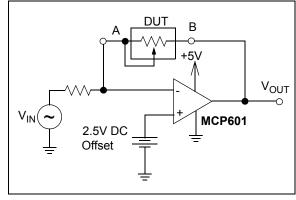

FIGURE 2-29: Gain vs. Frequency Test Circuit.

FIGURE 2-30:

Capacitance Test Circuit.

## 3.0 PIN DESCRIPTIONS

### 3.1 PA0, PA1

Potentiometer Terminal A Connection.

### 3.2 PB0, PB1

Potentiometer Terminal B Connection.

### 3.3 PW0, PW1

Potentiometer Wiper Connection.

### 3.4 Chip Select (CS)

This is the SPI port chip select pin and is used to execute a new command after it has been loaded into the shift register. This pin has a Schmitt Trigger input.

### 3.5 Serial Clock (SCK)

This is the SPI port clock pin and is used to clock-in new register data. Data is clocked into the SI pin on the rising edge of the clock and out the SO pin on the falling edge of the clock. This pin is gated to the  $\overline{CS}$  pin (i.e., the device will not draw any more current if the SCK pin is toggling when the  $\overline{CS}$  pin is high). This pin has a Schmitt Trigger input.

### 3.6 Serial Data Input (SI)

This is the SPI port serial data input pin. The command and data bytes are clocked into the shift register using this pin. This pin is gated to the  $\overline{CS}$  pin (i.e., the device will not draw any more current if the SI pin is toggling when the  $\overline{CS}$  pin is high). This pin has a Schmitt Trigger input.

#### 3.7 Serial Data Output (SO) (MCP42XXX devices only)

This is the SPI port serial data output pin used for daisy-chaining more than one device. Data is clocked out of the SO pin on the falling edge of clock. This is a push-pull output and **does not** go to a high-impedance state when  $\overline{CS}$  is high. It will drive a logic-low when  $\overline{CS}$  is high.

### 3.8 Reset (RS) (MCP42XXX devices only)

The Reset pin will set all potentiometers to mid-scale (Code 80h) if this pin is brought low for at least 150 ns. This pin should not be toggled low when the  $\overline{CS}$  pin is low. It is possible to toggle this pin when the  $\overline{SHDN}$  pin is low. In order to minimize power consumption, this pin has an active pull-up circuit. The performance of this circuit is shown in Figure 2-12. This pin will draw negligible current at logic level '0' and logic level '1'. Do not leave this pin floating.

#### 3.9 Shutdown (SHDN) (MCP42XXX devices only)

The Shutdown pin has a Schmitt Trigger input. Pulling this pin low will put the device in a power-saving mode where A terminal is opened and the B and W terminals are connected for all potentiometers. This pin should not be toggled low when the  $\overline{CS}$  pin is low. In order to minimize power consumption, this pin has an active pull-up circuit. The performance of this circuit is shown in Figure 2-12. This pin will draw negligible current at logic level '0' and logic level '1'. Do not leave this pin floating.

| Pin # | Name            | Function                        |  |

|-------|-----------------|---------------------------------|--|

| 1     | CS              | Chip Select                     |  |

| 2     | SCK             | Serial Clock                    |  |

| 3     | SI              | Serial Data Input               |  |

| 4     | $V_{\rm SS}$    | Ground                          |  |

| 5     | PA0             | Terminal A Connection For Pot 0 |  |

| 6     | PW0             | Wiper Connection For Pot 0      |  |

| 7     | PB0             | Terminal B Connection For Pot 0 |  |

| 8     | $V_{\text{DD}}$ | Power                           |  |

#### TABLE 3-1: MCP41XXX Pins

#### TABLE 3-2: MCP42XXX Pins

| Pin # | Name            | Function                        |

|-------|-----------------|---------------------------------|

| 1     | CS              | Chip Select                     |

| 2     | SCK             | Serial Clock                    |

| 3     | SI              | Serial Data Input               |

| 4     | $V_{\text{SS}}$ | Ground                          |

| 5     | PB1             | Terminal B Connection For Pot 1 |

| 6     | PW1             | Wiper Connection For Pot 1      |

| 7     | PA1             | Terminal A Connection For Pot 1 |

| 8     | PA0             | Terminal A Connection For Pot 0 |

| 9     | PW0             | Wiper Connection For Pot 0      |

| 10    | PB0             | Terminal B Connection For Pot 0 |

| 11    | RS              | Reset Input                     |

| 12    | SHDN            | Shutdown Input                  |

| 13    | SO              | Data Out for Daisy-Chaining     |

| 14    | $V_{DD}$        | Power                           |

### 4.0 APPLICATIONS INFORMATION

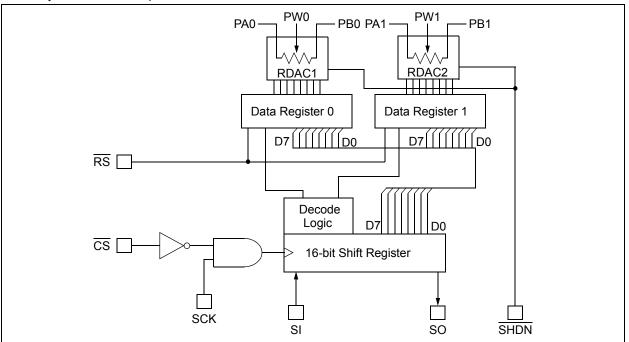

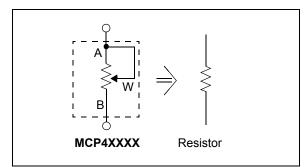

The MCP41XXX/42XXX devices are 256 position single and dual digital potentiometers that can be used in place of standard mechanical pots. Resistance values of 10 k $\Omega$ , 50 k $\Omega$  and 100 k $\Omega$  are available. As shown in Figure 4-1, each potentiometer is made up of a variable resistor and an 8-bit (256 position) data register that determines the wiper position. There is a nominal wiper resistance of 52 $\Omega$  for the 10 k $\Omega$  version, 125 $\Omega$  for the 50 k $\Omega$  and 100 k $\Omega$  versions. For the dual devices, the channel-to-channel matching variation is less than 1%. The resistance between the wiper and either of the resistor endpoints varies linearly according to the value stored in the data register. Code 00h effectively connects the wiper to the B terminal. At

power-up, all data registers will automatically be loaded with the mid-scale value (80h). The serial interface provides the means for loading data into the shift register, which is then transferred to the data registers. The serial interface also provides the means to place individual potentiometers in the shutdown mode for maximum power savings. The SHDN pin can also be used to put all potentiometers in shutdown mode and the RS pin is provided to set all potentiometers to mid-scale (80h).

**FIGURE 4-1:** Block diagram showing the MCP42XXX dual digital potentiometer. Data register 0 and data register 1 are 8-bit registers allowing 256 positions for each wiper. Standard SPI pins are used with the addition of the Shutdown (SHDN) and Reset ( $\overline{RS}$ ) pins. As shown, reset affects the data register and wipers, bringing them to mid-scale. Shutdown disconnects the A terminal and connects the wiper to B, without changing the state of the data registers.

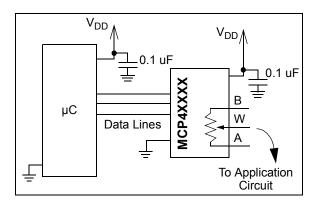

When laying out the circuit for your digital potentiometer, bypass capacitors should be used. These capacitors should be placed as close as possible to the device pin. A bypass capacitor value of 0.1  $\mu$ F is recommended. Digital and analog traces should be separated as much as possible on the board, with no traces running underneath the device or the bypass capacitor. Extra precautions should be taken to keep traces with high-frequency signals (such as clock lines) as far as possible from analog traces. Use of an analog ground plane is recommended in order to keep the ground potential the same for all devices on the board.

#### 4.1 Modes of Operation

Digital potentiometer applications can be divided into two categories: rheostat mode and potentiometer, or voltage divider, mode.

#### 4.1.1 RHEOSTAT MODE

In the rheostat mode, the potentiometer is used as a two-terminal resistive element. The unused terminal should be tied to the wiper, as shown in Figure 4-2. Note that reversing the polarity of the A and B terminals will not affect operation.

**FIGURE 4-2:** Two-terminal or rheostat configuration for the digital potentiometer. Acting as a resistive element in the circuit, resistance is controlled by changing the wiper setting.

Using the device in this mode allows control of the total resistance between the two nodes. The total measured resistance would be the least at code 00h, where the wiper is tied to the B terminal. The resistance at this code is equal to the wiper resistance, typically 52 $\Omega$  for the 10 k $\Omega$  MCP4X010 devices, 125 $\Omega$  for the 50 k $\Omega$  (MCP4X050), and 100 k $\Omega$  (MCP4X100) devices. For the 10 k $\Omega$  device, the LSB size would be 39.0625 $\Omega$  (assuming 10 k $\Omega$  total resistance). The resistance would then increase with this LSB size until the total measured resistance at code FFh would be 9985.94 $\Omega$ . The wiper will never directly connect to the A terminal of the resistor stack.

In the 00h state, the total resistance is the wiper resistance. To avoid damage to the internal wiper circuitry in this configuration, care should be taken to ensure the current flow never exceeds 1 mA.

For dual devices, the variation of channel-to-channel matching of the total resistance from A to B is less than 1%. The device-to-device matching, however, can vary up to 30%. In the rheostat mode, the resistance has a positive temperature coefficient. The change in wiper-to-end terminal resistance over temperature is shown in Figure 2-8. The most variation over temperature will occur in the first 6% of codes (code 00h to 0Fh) due to the wiper resistance coefficient affecting the total resistance. The remaining codes are dominated by the total resistance tempco  $R_{AB}$ , typically 800 ppm/°C.

#### 4.1.2 POTENTIOMETER MODE

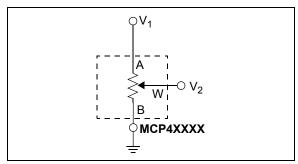

In the potentiometer mode, all three terminals of the device are tied to different nodes in the circuit. This allows the potentiometer to output a voltage proportional to the input voltage. This mode is sometimes called voltage divider mode. The potentiometer is used to provide a variable voltage by adjusting the wiper position between the two endpoints as shown in Figure 4-3. Note that reversing the polarity of the A and B terminals will not affect operation.

#### FIGURE 4-3: divider mode.

Three terminal or voltage

In this configuration, the ratio of the internal resistance defines the temperature coefficient of the device. The resistor matching of the  $R_{WB}$  resistor to the  $R_{AB}$  resistor performs with a typical temperature coefficient of 1 ppm/°C (measured at code 80h). At lower codes, the wiper resistance temperature coefficient will dominate. Figure 2-3 shows the effect of the wiper. Above the lower codes, this figure shows that 70% of the states will typically have a temperature coefficient of less than 5 ppm/°C. 30% of the states will typically have a ppm/°C of less than 1.

#### 4.2 Typical Applications

#### 4.2.1 PROGRAMMABLE SINGLE-ENDED AMPLIFIERS

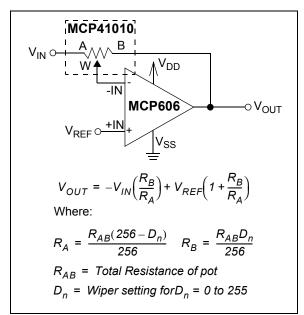

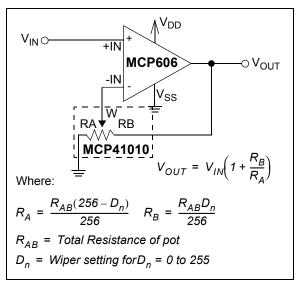

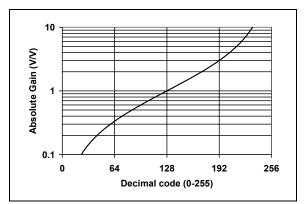

Potentiometers are often used to adjust system reference levels or gain. Programmable gain circuits using digital potentiometers can be realized in a number of different ways. An example of a single-supply, inverting gain amplifier is shown in Figure 4-4. Due to the high input impedance of the amplifier, the wiper resistance is not included in the transfer function. For a single-supply, non-inverting gain configuration, the circuit in Figure 4-5 can be used.

*FIGURE 4-4:* Single-supply, programmable, inverting gain amplifier using a digital potentiometer.

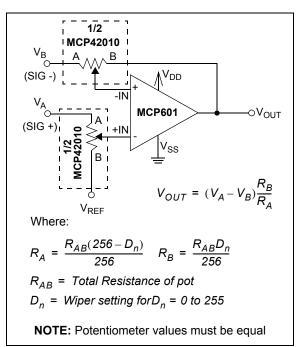

In order for these circuits to work properly, care must be taken in a few areas. For linear operation, the analog input and output signals must be in the range of V<sub>SS</sub> to V<sub>DD</sub> for the potentiometer and input and output rails of the op-amp. The circuit in Figure 4-4 requires a virtual ground or reference input to the non-inverting input of the amplifier. Refer to Application Note 682, "Using Single-Supply Operational Amplifiers in Embedded Systems" (DS00682), for more details. At power-up or reset (RS), the resistance is set to mid-scale, with R<sub>A</sub> and R<sub>B</sub> matching. Based on the transfer function for the circuit, the gain is -1 V/V. As the code is increased and the wiper moves towards the A terminal, the gain increases. Conversely, when the wiper is moved towards the B terminal, the gain decreases. Figure 4-6 shows this relationship. Notice the pseudo-logarithmic gain around decimal code 128. As the wiper approaches either terminal, the step size in the gain calculation increases dramatically. Due to the mismatched ratio of RA and RB at the extreme high and low codes, small increments in wiper position can dramatically affect the gain. As shown in Figure 4-3, recommended gains lie between 0.1 and 10 V/V.

*FIGURE 4-6:* Gain vs. Code for inverting and differential amplifier circuits.

## 4.2.2 PROGRAMMABLE DIFFERENTIAL AMPLIFIER

An example of a differential input amplifier using digital potentiometers is shown in Figure 4-7. For the transfer function to hold, both pots must be programmed to the same code. The resistor-matching from channel-to-channel within a dual device can be used as an advantage in this circuit. This circuit will also show stable operation over temperature due to the low potentiometer temperature coefficient. Figure 4-6 also shows the relationship between gain and code for this circuit. As the wiper approaches either terminal, the step size in the gain calculation increases dramatically. This circuit is recommended for gains between 0.1 and 10 V/V.

*FIGURE 4-7:* Single Supply programmable differential amplifier using digital potentiometers.

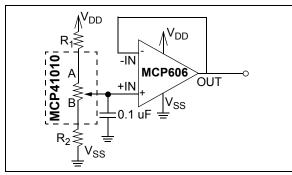

#### 4.2.3 PROGRAMMABLE OFFSET TRIM

For applications requiring only a programmable voltage reference, the circuit in Figure 4-8 can be used. This circuit shows the device used in the potentiometer mode along with two resistors and a buffered output. This creates a circuit with a linear relationship between voltage-out and programmed code. Resistors R<sub>1</sub> and R<sub>2</sub> can be used to increase or decrease the output voltage step size. The potentiometer in this mode is stable over temperature. The operation of this circuit over temperature is shown in Figure 2-3. The worst performance over temperature will occur at the lower codes due to the dominating wiper resistance. R<sub>1</sub> and R<sub>2</sub> can also be used to affect the boundary voltages, thereby eliminating the use of these lower codes.

**FIGURE 4-8:** By changing the values of  $R_1$  and  $R_2$ , the voltage output resolution of this programmable voltage reference circuit is affected.

#### 4.3 Calculating Resistances

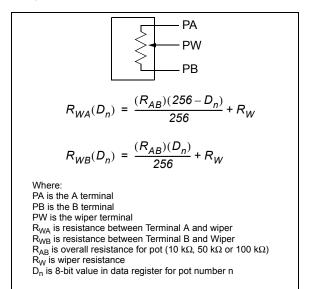

When programming the digital potentiometer settings, the following equations can be used to calculate the resistances. Programming code 00h effectively brings the wiper to the B terminal, leaving only the wiper resistance. Programming higher codes will bring the wiper closer to the A terminal of the potentiometer. The equations in Figure 4-9 can be used to calculate the terminal resistances. Figure 4-10 shows an example calculation using a 10 k $\Omega$  potentiometer.

**FIGURE 4-9:** Potentiometer resistances are a function of code. It should be noted that, when using these equations for most feedback amplifier circuits (see Figure 4-4 and Figure 4-5), the wiper resistance can be omitted due to the high impedance input of the amplifier.

PA Example:

R = 10 kΩ

PW Code = C0h = 192d

PB

$$R_{WA}(D_n) = \frac{(R_{AB})(256 - D_n)}{256} + R_W$$

$$R_{WA}(C0h) = \frac{(10k\Omega)(256 - 192)}{256} + 52\Omega$$

$$R_{WA}(C0h) = 2552\Omega$$

$$R_{WB}(D_n) = \frac{(R_{AB})(D_n)}{256} + R_W$$

$$R_{WB}(C0h) = \frac{(10k\Omega)(192)}{256} + 52\Omega$$

$$R_{WB}(C0h) = 7552\Omega$$

Note: All values shown are typical and actual results will vary.

FIGURE 4-10: Example Resistance calculations.

### 5.0 SERIAL INTERFACE

Communications from the controller to the MCP41XXX/42XXX digital potentiometers is accomplished using the SPI serial interface. This interface allows three commands:

- 1. Write a new value to the potentiometer data register(s).

- 2. Cause a channel to enter low power shutdown mode.

- 3. NOP (No Operation) command.

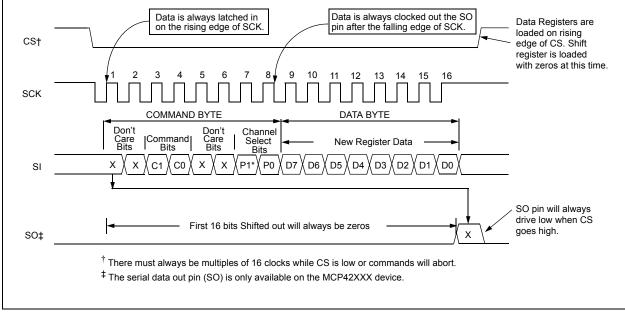

Executing any command is accomplished by setting  $\overline{CS}$  low and then clocking-in a command byte followed by a data byte into the <u>16-bit</u> shift register. The command is executed when  $\overline{CS}$  is raised. Data is clockedin on the rising edge of clock and out the SO pin on the falling edge of the clock (see Figure 5-1). The device will track the number of clocks (rising edges) while  $\overline{CS}$  is low and will abort all commands if the number of clocks is not a multiple of 16.

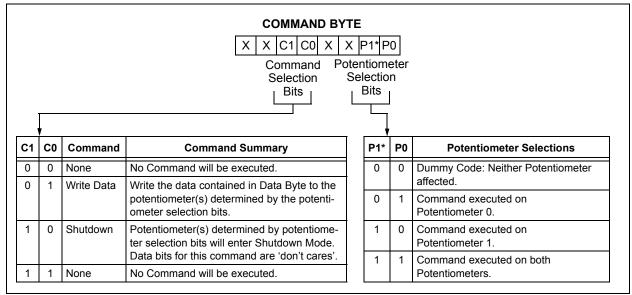

#### 5.1 Command Byte

The first byte sent is always the command byte, followed by the data byte. The command byte contains two command select bits and two potentiometer select bits. Unused bits are 'don't care' bits. The command select bits are summarized in Figure 5-2. The command select bits C1 and C0 (bits 4:5) of the command byte determine which command will be executed. If the command bits are both 0's or 1's, then a NOP command will be executed once all 16 bits have been loaded. This command is useful when using the daisychain configuration. When the command bits are 0,1, a write command will be executed with the 8 bits sent in the data byte. The data will be written to the potentiometer(s) determined by the potentiometer select bits. If the command bits are 1,0, then a shutdown command will be executed on the potentiometers determined by the potentiometer select bits.

For the MCP42XXX devices, the potentiometer select bits P1 and P0 (bits 0:1) determine which potentiometers are to be acted upon by the command. A corresponding '1' in the position signifies that the command for that potentiometer will get executed, while a '0' signifies that the command will not effect that potentiometer (see Figure 5-2).

### 5.2 Writing Data Into Data Registers

When new data is written into one or more of the potentiometer data registers, the write command is followed by the data byte for the new value. The command select bits C1, C0 are set to 0,1. The potentiometer selection bits P1 and P0 allow new values to be written to potentiometer 0, potentiometer 1 (or both) with a single command. A '1' for either P1 or P0 will cause the data to be written to the respective data register and a '0' for P1 or P0 will cause no change. See Figure 5-2 for the command format summary.

#### 5.3 Using The Shutdown Command

The shutdown command allows the user to put the application circuit into a power-saving mode. In this mode, the A terminal is open-circuited and the B and W terminals are shorted together. The command select bits C1, C0 are set to 1,0. The potentiometer selection bits P1 and P0 allow each potentiometer to be shutdown independently. If either P1 or P0 are high, the respective potentiometer will enter shutdown mode. A '0' for P1 or P0 will have no effect. The eight data bits following the command byte still need to be transmitted for the shutdown command, but they are 'don't care' bits. See Figure 5-2 for command format summary. Once a particular potentiometer has entered the shutdown mode, it will remain in this mode until:

• A new value is written to the potentiometer data register, provided that the SHDN pin is high. The device will remain in the shutdown mode until the rising edge of the CS is detected, at which time the device will come out of shutdown mode and the new value will be written to the data register(s). If the SHDN pin is low when the new value is received, the registers will still be set to the new value, but the device will remain in shutdown mode. This scenario assumes that a valid command was received. If an invalid command was received, the command will be ignored and the device will remain in the shutdown mode.

It is also possible to use the hardware shutdown pin and reset pin to remove a device from software shutdown. To do this, a low pulse on the chip select line must first be sent. For multiple devices, sharing a single SHDN or RESET line allows you to pick an individual device on that chain to remove from software shutdown mode. See Figure 1-3 for timing. With a preceding chip select pulse, either of these situations will also remove a device from software shutdown:

- A falling edge is seen on the RS pin and held low for at least 150 ns, provided that the SHDN pin is high. If the SHDN pin is low, the registers will still be set to mid-scale, but the device will remain in shutdown mode. This condition assumes that CS is high, as bringing the RS pin low while CS is low is an invalid state and results are indeterminate.

- A rising edge on the SHDN pin is seen after being low for at least 100 ns, provided that the CS pin is high. Toggling the SHDN pin low while CS is low is an invalid state and results are indeterminate.

- The device is powered-down and back up.

**Note:** The hardware SHDN pin will always put the device in shutdown regardless of whether a potentiometer has already been put in the shutdown mode using the software command.

FIGURE 5-2: Command Byte Format.

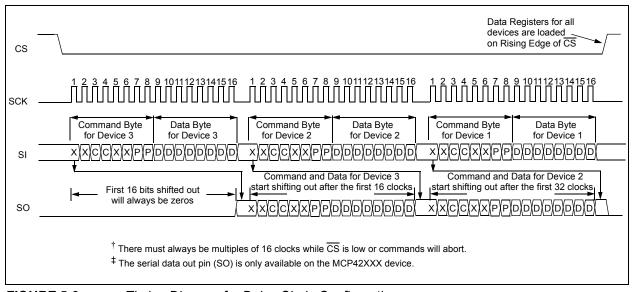

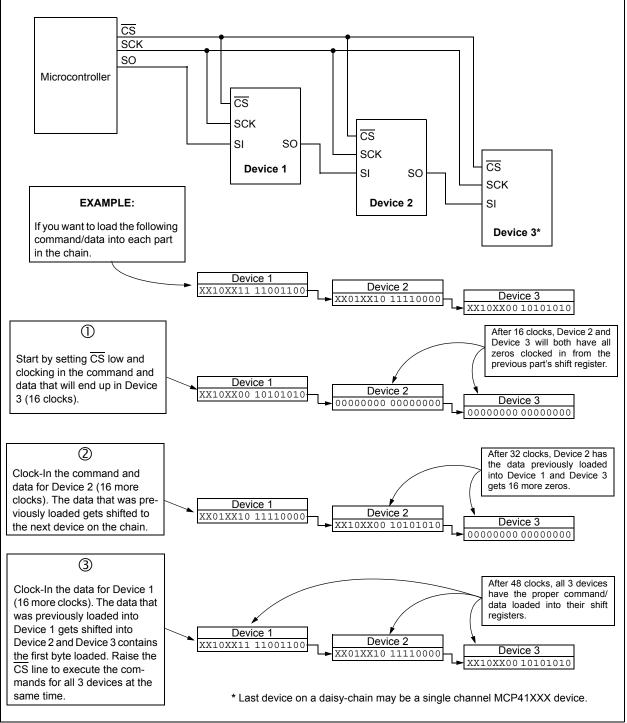

#### 5.4 Daisy-Chain Configuration

Multiple MCP42XXX devices can be connected in a daisy-chain configuration, as shown in Figure 5-4, by connecting the SO pin from one device to the SI pin on the next device. The data on the SO pin is the output of the 16-bit shift register. The daisy-chain configuration allows the system designer to communicate with several devices without using a separate  $\overline{CS}$  line for each device. The example shows a daisy-chain configuration with three devices, although any number of devices (with or without the same resistor values) can be configured this way. While it is not possible to use a MCP41XXX at the beginning or middle of a daisy-chain (because it does not provide the serial data out (SO) pin), it is possible to use the device at the end of a chain. As shown in the timing diagram in Figure 5-3, data will be clocked-out of the SO pin on the falling edge of the clock. The SO pin has a CMOS push-pull output and will drive low when  $\overline{CS}$  goes high. SO will **not** go to a high-impedance state when  $\overline{CS}$  is held high.

When using the daisy-chain configuration, the maximum clock speed possible is reduced to  $\sim$ 5.8 MHz, because of the propagation delay of the data coming out of the SO pin.