Motor Drivers for Printers

# Three-phase Brushless Motor Pre-drivers for Paper Feed

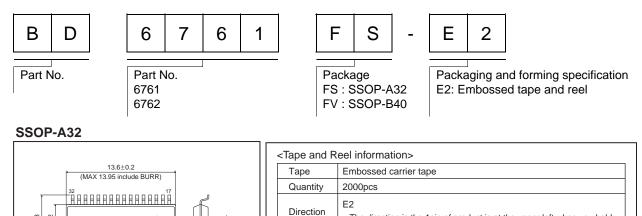

## BD6761FS,BD6762FV

No.10016EAT01

#### Description

This product is the motor predriver for high-side/low-side N-channel MOS-FET drive, which has the built-in booster (step-up) circuit. BD6761FS uses the drive type controlled by the servo signal input from outside and BD6762FV incorporates a servo circuit (Speed discriminator + PLL servo).

#### Features

- 1) Predriver for high-side/low-side N-channel MOS-FET

- 2) Built-in booster (step-up) circuit

- 3) Built-in FG and hysteresis amplifiers

- 4) Built-in current limit circuit

- 5) Built-in thermal shutdown circuit

- 6) Built-in forward/reverse rotation switching circuit (BD6761FS, FD6762FV)

- 7) Built-in short brake circuit (BD6761FS, BD6762FV)

- 8) Built-in low voltage protection circuit (BD6761FS, BD6762FV)

- 9) Built-in speed lock detection circuit (BD6762FV)

- 10) Built-in motor lock protection circuit (BD6762FV)

- 11) Built-in start-stop circuit (BD6762FV)

- 12) Built-in servo circuit (Speed discriminator + PLL) (BD6762FV)

- 13) Built-in frequency multiplication circuit (BD6762FV)

- 14) 180°, direct PWM drive (BD6761FS)

- 15) 120°, slope switchable direct PWM drive (BD6762FV)

#### Applications

Main motor for paper feed of the laser beam printer and PPC

#### ●Absolute Maximum Ratings (Ta=25°C)

| Parameter                   | Symbol | Rat                 | – Unit               |      |

|-----------------------------|--------|---------------------|----------------------|------|

| Parameter                   | Symbol | BD6761FS            | BD6762FV             | Onit |

| Applied voltage             | VCC    | 36                  | 36                   | V    |

| Applied voltage             | VG     | 36                  | 36                   | V    |

| Pin input voltage           | Vin    | VREG                | VREG                 | V    |

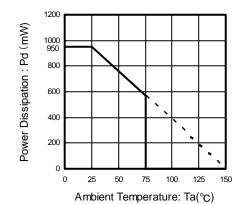

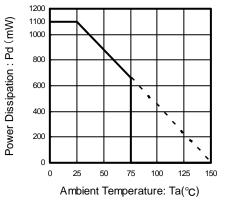

| Power dissipation           | Pd     | 950 <sup>(‰1)</sup> | 1100 <sup>(‰2)</sup> | mW   |

| Operating temperature range | TOPR   | -35 ~ +75           | -25 ~ +75            | °C   |

| Storage temperature range   | TSTG   | -40 ~ +150          | -40 ~ +150           | °C   |

| Junction temperature        | Tjmax  | 150                 | 150                  | C°   |

$1 \text{ Reduced by 7.6 mW}^{\circ}$  over 25°°C, when mounted on a glass epoxy board (70 mm  $\times$  70 mm  $\times$  1.6 mm).  $2 \text{ Reduced by 8.8 mW}^{\circ}$  over 25°C, when mounted on a glass epoxy board (70 mm  $\times$  70 mm  $\times$  1.6 mm).

#### Line up Matrix

| -                          | BD6761FS | BD6762FV          | Unit |

|----------------------------|----------|-------------------|------|

| Power supply voltage (VCC) | 16~28    | 16~28             | V    |

| Drive type                 | 180°     | 120° / 120° slope | —    |

| Servo                      | No       | Yes               | —    |

●Electrical Characteristics BD6761FS (Unless otherwise specified, Ta=25°C, VCC=24.0V)

| Demonster                    | Querra la cal |       | Limits |       | 1.114   |                              |

|------------------------------|---------------|-------|--------|-------|---------|------------------------------|

| Parameter                    | Symbol        | Min.  | Тур.   | Max.  | Unit    | Conditions                   |

| Overall                      |               |       |        |       | 1       |                              |

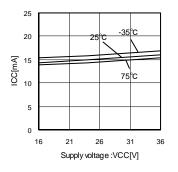

| Circuit current              | ICC           | 10    | 15     | 20    | mA      |                              |

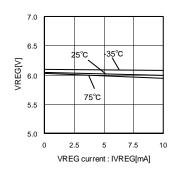

| VREG voltage                 | VREG          | 5.5   | 6      | 6.5   | V       | IVREG=-1mA                   |

| Hall amp                     |               |       |        |       |         |                              |

| Input bias current           | IHA           | _     | 0.7    | 3.0   | μA      |                              |

| In-phase input voltage range | VHAR          | 1.5   | _      | 4.1   | V       |                              |

| Input level                  | VINH          | 30    | _      | 250   | mVpp    | Single-phase Hall amplitude  |

| PWM                          |               |       |        |       |         | 5 1 1                        |

| High CFE voltage             | VHPCFE        | 3.0   | 3.5    | 4.0   | V       |                              |

| Low CFE voltage              | VLPCFE        | 2.1   | 2.5    | 2.9   | V       |                              |

| CFE oscillating frequency    | FCFE          | 12    | 15     | 18    | kHz     | RFE=50kΩ, CFE=1000pF         |

| PWM on duty offset           | DPWM          | -1.5  | 0      | 1.5   | %       |                              |

| Torque amplifier             | Di iiii       | 1.0   | Ŭ      | 1.0   | 70      |                              |

| High CPOUT input current     | ICPOUTH       | _     | 0      | 1     | μA      |                              |

| Low CPOUT input current      | ICPOUTL       | -1    | 0      | _     | μΑ      |                              |

| Current limit                |               | -1    | 0      |       | μΛ      |                              |

| Current detection voltage 1  | VCL1          | 0.391 | 0.435  | 0.479 | V       | For current sense amplifier  |

| Current detection voltage 2  | VCL1<br>VCL2  | 0.432 | 0.433  | 0.528 | V       | For current limit comparator |

| VCL2-VCL1                    |               | 40    | 45     | 50    | mV      | For current limit comparator |

| FG Amp                       | AVCL          | 40    | 40     | 50    | mv      |                              |

| Input bias current           | IBFG          | -1    | _      | 1     | μA      |                              |

| Input offset voltage         | VBFG          | -10   |        | 10    |         |                              |

|                              |               |       | -      |       | mV<br>V |                              |

| High output voltage          | VHFG          | 4.5   | 5.0    | VREG  | V       | IHFGOUT=-0.75mA              |

| Low output voltage           | VLFG          | -     | 1.0    | 1.5   |         | ILFGOUT=2mA                  |

| Low FGS output voltage       | VLFGS         | -     | 0.1    | 0.3   | V       | ILFGSOUT=3mA                 |

| Open loop gain               | GVFG          | 45    | 54     |       | dB      | f=3kHz                       |

| Bias voltage                 | VBIASFG       | 2.7   | 3.0    | 3.3   | V       |                              |

| Hysteresis width             | VHYS          | 100   | 180    | 250   | mV      |                              |

| F/R                          |               |       |        |       |         | <b>F</b> ( <b>D</b> , a) (   |

| High input current           | IFRL          | 30    | 60     | 90    | μA      | F/R=6V                       |

| Low input current            | IFRH          | -10   | 0      | 10    | μA      | F/R=0V                       |

| High input level             | VIHFR         | 2.2   | -      | VREG  | V       | Reverse rotation             |

| Low input level              | VILFR         | 0     | —      | 0.8   | V       | Forward rotation             |

| ACC and DEC                  |               |       |        | 1     |         |                              |

| High ACC input current       | IACCH         | 30    | 60     | 90    | μA      | ACC=6V                       |

| Low ACC input current        | IACCL         | -10   | 0      | 10    | μA      | ACC=0V                       |

| High DEC input current       | IDECH         | 30    | 60     | 90    | μA      | DEC=6V                       |

| Low DEC input current        | IDECL         | -10   | 0      | 10    | μA      | DEC=0V                       |

| Accelerating current         | ISS           | -260  | -200   | -140  | μA      | RCP=13.5kΩ, ACC=L            |

| Decelerating current         | ISO           | 140   | 200    | 260   | μA      | RCP=13.5kΩ, DEC=L            |

| High ACC input level         | VIHACC        | 2.2   | _      | VREG  | V       |                              |

| Low ACC input level          | VILACC        | 0     | -      | 0.8   | V       |                              |

| High DEC input level         | VIHDEC        | 2.2   | —      | VREG  | V       |                              |

| Low DEC input level          | VILDEC        | 0     | —      | 0.8   | V       |                              |

| High-side output             |               |       | 1      | 1     |         |                              |

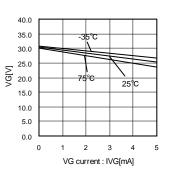

| High-side voltage            | VHG           | Vcc+5 | Vcc+6  | Vcc+7 | V       |                              |

| Pull-down resistor           | RHD           | 70    | 100    | 130   | kΩ      |                              |

| Low-side output              |               |       |        |       |         |                              |

| Low-side voltage             | VLG           | 9.5   | 10.5   | 11.5  | V       |                              |

| Pull-down resistor           | RLD           | 70    | 100    | 130   | kΩ      |                              |

| Booster                      |               |       |        |       |         |                              |

| Boost voltage                | VG            | Vcc+5 | Vcc+6  | Vcc+7 | V       |                              |

| CP1 oscillating frequency    | FCP1          | 35    | 62.5   | 85    | kHz     |                              |

BD6762FV (Unless otherwise specified, Ta=25°C, VCC=24V)

| BD6762FV (Unless otherwise speci        |              | Limits    |           |      |       | Conditions                 |  |

|-----------------------------------------|--------------|-----------|-----------|------|-------|----------------------------|--|

| Parameter                               | Symbol       | Min.      | Тур.      | Max. | Unit  | Conditions                 |  |

| Overall                                 |              |           |           |      |       |                            |  |

| Circuit current 1                       | ICCS         | 5.1       | 7.6       | 10.2 | mA    | ST/SP=OPEN                 |  |

| Circuit current 2                       | ICC          | 10        | 17        | 25   | mA    | ST/SP=GND                  |  |

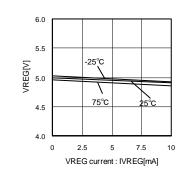

| VREG voltage                            | VREG         | 4.5       | 5         | 5.5  | V     | IVREG=-1mA                 |  |

| Low voltage protection level            | VUVON        | 9.5       | 11.5      | 13.5 | V     |                            |  |

| Low voltage protection hysteresis level | VUVHYS       | 0.4       | 0.5       | 0.6  | V     |                            |  |

| Hall amp                                | 1            | ŀ         |           |      | 1     |                            |  |

| Input bias current                      | IBH          | _         | 1         | 3    | μA    |                            |  |

| In-phase input voltage range            | VHAR         | 0         | -         | 3    | V     |                            |  |

| Input level                             | VINH         | 50        | _         | _    | mVp-p |                            |  |

| PWM                                     |              |           | 11        |      |       |                            |  |

| High CFE voltage                        | VCFEH        | 2.6       | 2.9       | 3.2  | V     |                            |  |

| Low CFE voltage                         | VCFEL        | 1.2       | 1.4       | 1.6  | V     |                            |  |

| CFE oscillating frequency               | FCFE         | 13        | 16        | 19   | kHz   | RFE=20K, CFE=1000pF        |  |

| REF voltage                             | VRFE         | 0.75      | 0.95      | 1.15 | V     | - , ····r·                 |  |

| FG amp                                  |              |           |           |      | -     |                            |  |

| Input bias current                      | IFGM         | -1        | _         | 1    | μA    |                            |  |

| Input offset voltage                    | VFGOF        | -10       | _         | 10   | mV    |                            |  |

| High output voltage                     | VFGOH        | 3.5       | 4.0       | _    | V     | I=-0.5mA                   |  |

| Low output voltage                      | VFGOL        | -         | 1.0       | 1.5  | V     | I=0.5mA                    |  |

| Low FGS output voltage                  | VFGSL        | _         | 0.1       | 0.3  | V     | I=2mA                      |  |

| Open loop gain                          | GFG          | 45        | 54        | -    | dB    | f=3kHz                     |  |

| Bias voltage                            | VBFG         | 2.25      | 2.50      | 2.75 | V     |                            |  |

| Hysteresis width                        | VFGHYS       | 100       | 180       | 250  | mV    |                            |  |

| Integration amp                         | vi onito     | 100       | 100       | 200  | IIIV  |                            |  |

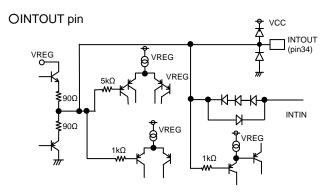

| Di clamp voltage 1                      | VDI1         | 1.5       | 2.1       | 2.7  | V     | INTIN=0.1mA                |  |

| Di clamp voltage 2                      | VDI1<br>VDI2 | 0.5       | 0.7       | 0.9  | V     | INTOUT=0.1mA               |  |

| Bias voltage                            | VBERR        | 2.25      | 2.50      | 2.75 | V     | INTIN=INTOUT               |  |

| Speed discriminator                     | VDERN        | 2.25      | 2.50      | 2.75 | v     |                            |  |

| High output voltage                     | VDOH         | VREG-0.3  | VREG-0.1  |      | V     | I=-0.1mA                   |  |

| Low output voltage                      | VDOH         | -         | 0.1       | 0.3  | V     | I=-0.1mA                   |  |

| PLL                                     | VDOL         | _         | 0.1       | 0.3  | V     | I=0.IIIIA                  |  |

|                                         |              |           | VREG-0.15 | _    | V     | I=-0.1mA                   |  |

| High output voltage                     | VPOH         | VREG-0.40 |           |      |       |                            |  |

| Low output voltage                      | VPOL         | _         | 0.15      | 0.45 | V     | I=0.1mA                    |  |

| Lock detection                          |              |           | 0.45      | 0.0  |       |                            |  |

| Low output voltage                      | VLDL         | _         | 0.15      | 0.3  | V     | I=2mA                      |  |

| Lock protection                         |              | 40        |           | 07   |       |                            |  |

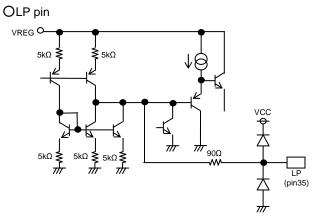

| CLK cycle for protection circuit        | TLP          | 13        | 20        | 27   | msec  | LP=0.1µF                   |  |

| VCO                                     | 5011         | 0.0       |           | 0.5  |       |                            |  |

| CLK input frequency range               | FCLK         | 0.2       | -         | 2.5  | kHz   | Designed value (VCO alone) |  |

| High-level CLK input voltage            | VCKH         | 2.2       | -         | VREG | V     |                            |  |

| Low-level CLK input voltage             | VCKL         | 0         | -         | 0.8  | V     |                            |  |

| High-level CLK input current            | ICKH         | -10       | —         | 10   | μA    |                            |  |

| Low-level CLK input current             | ICKL         | -140      | -100      | -60  | μA    |                            |  |

BD6762FV (Unless otherwise specified, Ta=25°C, VCC=24 V)

| BD6762FV (Unless otherwise specif  |        |         | Limits  |         |      |                       |

|------------------------------------|--------|---------|---------|---------|------|-----------------------|

| Parameter                          | Symbol | Min.    | Тур.    | Max.    | Unit | Conditions            |

| Start/Stop                         |        |         |         |         |      |                       |

| High-level ST/SP input voltage     | VSTH   | 2.2     | —       | VREG    | V    | STOP                  |

| Low-level ST/SP input voltage      | VSTL   | 0       | —       | 0.8     | V    | START                 |

| High-level ST/SP input current     | ISTH   | -10     | 0       | 10      | μA   |                       |

| Low-level ST/SP input current      | ISTL   | -70     | -50     | -30     | μA   |                       |

| Forward rotation/Reverse rotation  |        |         |         |         |      |                       |

| High-level FR input voltage        | VFRH   | 2.2     | —       | VREG    | V    | Reverse rotation      |

| Low-level FR input voltage         | VFRL   | 0       | —       | 0.8     | V    | Forward rotation      |

| High-level FR input current        | IFRH   | -10     | 0       | 10      | μA   |                       |

| Low-level FR input current         | IFRL   | -70     | -50     | -30     | μA   |                       |

| 120°/Slope switching               |        |         |         |         |      |                       |

| High-level 120/slope input voltage | VANH   | 2.2     | —       | VREG    | V    | 120°                  |

| Low-level 120/slope input voltage  | VANL   | 0       | _       | 0.8     | V    | 120° slope            |

| High-level 120/slope input current | IANH   | -10     | 0       | 10      | μA   |                       |

| Low-level 120/slope input current  | IANL   | -70     | -50     | -30     | μA   |                       |

| Short brake                        |        |         |         |         |      |                       |

| High-level SB input voltage        | VSBH   | 2.2     | —       | VREG    | V    | Short brake operation |

| Low-level SB input voltage         | VSBL   | 0       | —       | 0.8     | V    | Short brake clear     |

| High-level SB input current        | ISBH   | -10     | 0       | 10      | μA   |                       |

| Low-level SB input current         | ISBL   | -70     | -50     | -30     | μA   |                       |

| Current limit                      |        |         |         |         |      |                       |

| Current detection voltage          | VCL    | 0.23    | 0.26    | 0.29    | V    |                       |

| Booster                            |        |         |         |         |      |                       |

| CP1 oscillating frequency          | FCP1   | 75      | 125     | 175     | kHz  |                       |

| VG step-up voltage                 | VG     | VCC+5.7 | VCC+6.7 | VCC+7.7 | V    |                       |

| High-side output                   |        |         |         |         |      |                       |

| High output voltage 1              | VHHG1  | VCC+5.8 | VCC+6.8 | VCC+7.8 | V    | VG=31V                |

| High output voltage 2              | VHHG2  | VCC+3.8 | VCC+4.8 | VCC+5.8 | V    | lo=-1mA               |

| Low output voltage 1               | VHLG1  | _       | 0.1     | 0.3     | V    |                       |

| Low output voltage 2               | VHLG2  | _       | 0.5     | 1.0     | V    | lo=5mA                |

| Clamp voltage                      | VHCL   | 10      | 11      | 12      | V    |                       |

| Low-side output                    |        |         |         |         |      |                       |

| High output voltage 1              | VLHG1  | 9.8     | 10.8    | 11.8    | V    |                       |

| High output voltage 2              | VLHG2  | 9.0     | 10.0    | 11.0    | V    | lo=-5mA               |

| Low output voltage 1               | VLLG1  | _       | 0.1     | 0.3     | V    |                       |

| Low output voltage 2               | VLLG2  | —       | 0.3     | 0.5     | V    | lo=5mA                |

## Reference Data

25

20

15

10

5

0

16

Power Dissipation Reduction

21

26

Supply voltage :VCC[V]

Fig.4 Circuit current (BD6762FV)

ICC[mA]

Fig.1 Circuit current (BD6761FS)

-25°C

75 C

31

36

Fig. 2 VREG Voltage (BD6761FS)

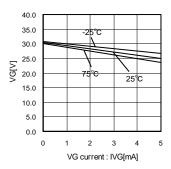

Fig. 3 VG Voltage (BD6761FS)

Fig.5 VREG Voltage (BD6762FV)

Fig.6 VG Voltage (BD6762FV)

Fig.7 BD6761FS Power Dissipation Reduction Reduced by 7.6 mW/°C over 25°C, when mounted on a glass epoxy board (70 mm  $\times$  70 mm  $\times$  1.6 mm).

Fig.8 BD6762FV Power Dissipation Reduction Reduced by 8.8 mW/°C over 25°C, when mounted on a glass epoxy board (70 mm × 70 mm × 1.6 mm)/°Cで軽減。

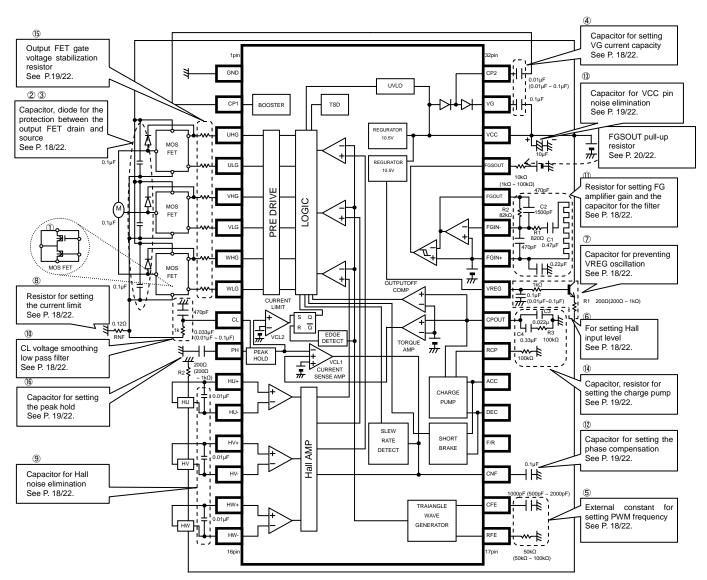

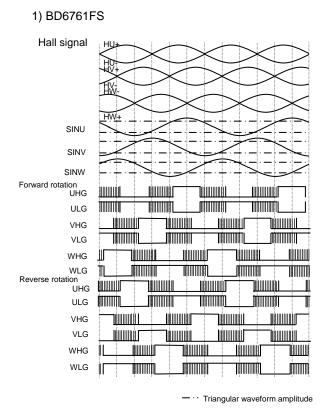

#### Block Diagram, Application Circuit Diagram, and Pin Function 1)BD6761FS

### Fig.9 BD6761FS Block Diagram

| No. | Pin<br>name | Function                       | No. | Pin<br>name | Function                               |

|-----|-------------|--------------------------------|-----|-------------|----------------------------------------|

| 1   | GND         | GND pin                        | 17  | RFE         | CFE current control pin                |

| 2   | CP1         | CP1 pin                        | 18  | CFE         | PWM frequency control pin              |

| 3   | UHG         | U-phase high-side FET gate pin | 19  | CNF         | Phase compensation pin                 |

| 4   | ULG         | U-phase low-side FET gate pin  | 20  | F/R         | Forward/reverse rotation switching pin |

| 5   | VHG         | V-phase high-side FET gate pin | 21  | DEC         | Deceleration signal input pin          |

| 6   | VLG         | V-phase low-side FET gate pin  | 22  | ACC         | Acceleration signal input pin          |

| 7   | WHG         | W-phase high-side FET gate pin | 23  | RCP         | CPOUT current control pin              |

| 8   | WLG         | W-phase low-side FET gate pin  | 24  | CPOUT       | Charge pump output /                   |

| 9   | CL          | Motor current detection pin    | 24  | CFUUI       | Torque control signal input pin        |

| 10  | PH          | Peak hold pin                  | 25  | VREG        | VREG pin                               |

| 11  | HU+         | Hall signal input pin          | 26  | FGIN+       | FG input + pin                         |

| 12  | HU-         | Hall signal input pin          | 27  | FGIN-       | FG input - pin                         |

| 13  | HV+         | Hall signal input pin          | 28  | FGOUT       | FG output pin                          |

| 14  | HV-         | Hall signal input pin          | 29  | FGSOUT      | FGS output pin                         |

| 15  | HW+         | Hall signal input pin          | 30  | VCC         | VCC pin                                |

| 16  | HW-         | Hall signal input pin          | 31  | VG          | Boost pin                              |

|     |             |                                | 32  | CP2         | CP2 pin                                |

# BD6761FS,BD6762FV

## **Technical Note**

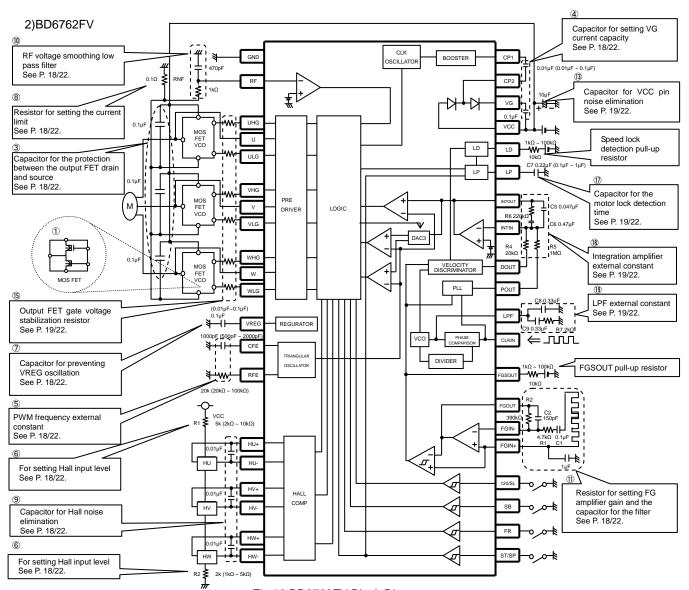

Fig.10 BD6762FV Block Diagram

| No. | Pin name | Function                                                         | No. | Pin name | Function                                 |

|-----|----------|------------------------------------------------------------------|-----|----------|------------------------------------------|

| 1   | GND      | GND pin                                                          | 21  | ST/SP    | Start/Stop pin                           |

| 2   | RF       | Motor current detection pin                                      | 22  | FR       | Forward/reverse rotation switching pin   |

| 3   | UHG      | U-phase high-side FET gate pin                                   | 23  | SB       | Short brake pin                          |

| 4   | U        | Protection pin for U-phase high-side<br>FET GS breakdown voltage | 24  | 120/SL   | 120°/slope switching pin                 |

| 5   | ULG      | U-phase low-side FET gate pin                                    | 25  | FGIN+    | FG amplifier input + pin                 |

| 6   | VHG      | V-phase high-side FET gate pin                                   | 26  | FGIN-    | FG amplifier input - pin                 |

| 7   | V        | Protection pin for V-phase high-side<br>FET GS breakdown voltage | 27  | FGOUT    | FG amplifier output pin                  |

| 8   | VLG      | V-phase low-side FET gate pin                                    | 28  | FGSOUT   | FGS output pin                           |

| 9   | WHG      | W-phase high-side FET gate pin                                   | 29  | CLKIN    | Reference CLK input pin                  |

| 10  | W        | Protection pin for W-phase high side<br>FET GS breakdown voltage | 30  | LPF      | VCO system loop filter connection pin    |

| 11  | WLG      | W-phase low-side FET gate pin                                    | 31  | POUT     | PLL output pin                           |

| 12  | VREG     | Internal power supply 5 V output pin                             | 32  | DOUT     | Speed discriminator output pin           |

| 13  | CFE      | PWM frequency control pin                                        | 33  | INTIN    | Integration amplifier input pin          |

| 14  | RFE      | CEF charge/discharge current control pin                         | 34  | INTOUT   | Integration amplifier output pin         |

| 15  | HU+      | Hall signal input pin                                            | 35  | LP       | Motor lock protection time setting pin   |

| 16  | HU-      | Hall signal input pin                                            | 36  | LD       | Motor rotation number lock detection pin |

| 17  | HV+      | Hall signal input pin                                            | 37  | VCC      | VCC pin                                  |

| 18  | HV-      | Hall signal input pin                                            | 38  | VG       | Step-up voltage output pin               |

| 19  | HW+      | Hall signal input pin                                            | 39  | CP2      | Capacitor connection pin (to CP1)        |

| 20  | HW-      | Hall signal input pin                                            | 40  | CP1      | Capacitor connection pin (to CP2)        |

BD6762FV pin Function

# ●I/O Logic 1)BD6761FS

Forward rotation (F/R=Low)

| -orward rotation |          |               |     |              |     |       |          |     |     |  |  |

|------------------|----------|---------------|-----|--------------|-----|-------|----------|-----|-----|--|--|

|                  | Inp      | ut conditi    | ons |              |     | Outpu | it state |     |     |  |  |

| Dia Ma           | 15       | 17            | 19  | 3            | 5   | 7     | 4        | 6   | 8   |  |  |

| Pin No.          | HU+      | HV+           | HW+ | UHG          | VHG | WHG   | ULG      | VLG | WLG |  |  |

| Condition 1      | L        | М             | Н   | Н            | Н   | L     | L        | L   | Н   |  |  |

| Condition 2      | L        | Н             | Н   | Н            | PWM | L     | L        | PWM | Н   |  |  |

| Condition 3      | L        | Н             | М   | Н            | L   | L     | L        | Н   | Н   |  |  |

| Condition 4      | L        | Н             | L   | Н            | L   | PWM   | L        | Н   | PWM |  |  |

| Condition 5      | М        | Н             | L   | Н            | L   | Н     | L        | Н   | L   |  |  |

| Condition 6      | Н        | Н             | L   | PWM          | L   | Н     | PWM      | Н   | L   |  |  |

| Condition 7      | Н        | М             | L   | L            | L   | Н     | Н        | Н   | L   |  |  |

| Condition 8      | Н        | L             | L   | L            | PWM | н     | Н        | PWM | L   |  |  |

| Condition 9      | Н        | L             | М   | L            | Н   | Н     | Н        | L   | L   |  |  |

| Condition 10     | Н        | L             | Н   | L            | Н   | PWM   | Н        | L   | PWM |  |  |

| Condition 11     | М        | L             | Н   | L            | Н   | L     | Н        | L   | Н   |  |  |

| Condition 12     | L        | L             | Н   | PWM          | Н   | L     | PWM      | L   | Н   |  |  |

| Reverse rotation | (F/R=Hig | h)            |     |              |     |       |          |     |     |  |  |

|                  | Inp      | out condition | ons | Output state |     |       |          |     |     |  |  |

| Pin No.          | 15       | 17            | 19  | 3            | 5   | 7     | 4        | 6   | 8   |  |  |

| FILLING.         | HU+      | HV+           | HW+ | UHG          | VHG | WHG   | ULG      | VLG | WLG |  |  |

| Condition 1      | L        | М             | Н   | L            | L   | Н     | Н        | Н   | L   |  |  |

| Condition 2      | L        | Н             | Н   | L            | PWM | Н     | Н        | PWM | L   |  |  |

| Condition 3      | L        | Н             | М   | L            | Н   | Н     | Н        | L   | L   |  |  |

| Condition 4      | L        | Н             | L   | L            | Н   | PWM   | Н        | L   | PWM |  |  |

| Condition 5      | М        | Н             | L   | L            | Н   | L     | Н        | L   | Н   |  |  |

| Condition 6      | Н        | Н             | L   | PWM          | Н   | L     | PWM      | L   | Н   |  |  |

| Condition 7      | Н        | М             | L   | Н            | Н   | L     | L        | L   | Н   |  |  |

| Condition 8      | Н        | L             | L   | Н            | PWM | L     | L        | PWM | Н   |  |  |

| Condition 9      | Н        | L             | М   | Н            | L   | L     | L        | Н   | Н   |  |  |

| Condition 10     | н        | L             | н   | н            | L   | PWM   | L        | н   | PWM |  |  |

| Condition 11     | М        | L             | Н   | Н            | L   | Н     | L        | Н   | L   |  |  |

| Condition 12     | L        | L             | Н   | PWM          | L   | Н     | PWM      | Н   | L   |  |  |

|                  |          |               |     |              |     |       |          |     |     |  |  |

<Input conditions> Hall input voltage H: 3.05V M: 3.0V L: 2.95V

<Output criteria> High-side FET gate voltage L≦1V, VG-1V≦H Low-side FET gate voltage  $L \leq 1V$ ,  $9V \leq H$

ACC, DEC

|             | Input co | nditions | Output state |             |  |  |

|-------------|----------|----------|--------------|-------------|--|--|

| Pin No.     | 21       | 22       | 24           | Short brake |  |  |

| FIII NO.    | DEC      | ACC      | CPOUT        | Short brake |  |  |

| Condition 1 | Н        | H OPEN   |              | OFF         |  |  |

| Condition 2 | Н        | L        | Н            | OFF         |  |  |

| Condition 3 | L        | Н        | L            | OFF         |  |  |

| Condition 4 | L        | L        | L            | ON          |  |  |

<Input conditions>

ACC, DEC input conditions H : 2.2V

L : 0.8V

<Output criteria> •CPOUT

RCP=13.5k $\Omega$ , CPOUT=3V High: Current outflow more than 140µA from CPOUT pin Low: Current inflow more than 140µA to CPOUT pin OPEN: CPOUT pin current -10µA $\leq$ ICPOUT $\leq$ 10µA

Short brake function

On state

High-side FET gate voltage≦1V

Low-side FET gate voltage≧9V

### 2)BD6762FV

Forward rotation (F/R=Low), 120° (120/SL=High)

|             | Inni | ut condit | ione  | Output state |                |     |     |          |     |        |   |    |

|-------------|------|-----------|-------|--------------|----------------|-----|-----|----------|-----|--------|---|----|

|             | inpo |           | 10115 | Hig          | High-side gate |     |     | w-side g | ate | Output |   |    |

| Pin No.     | 15   | 17        | 19    | 3            | 6              | 9   | 5   | 8        | 11  | 4      | 7 | 10 |

| FIITNO.     | HU+  | HV+       | HW+   | UHG          | VHG            | WHG | ULG | VLG      | WLG | U      | V | W  |

| Condition 1 | L    | L         | н     | L            | Н              | L   | L   | L        | Н   | М      | Н | L  |

| Condition 2 | Н    | L         | Н     | L            | Н              | L   | Н   | L        | L   | L      | Н | М  |

| Condition 3 | Н    | L         | L     | L            | L              | Н   | Н   | L        | L   | L      | М | Н  |

| Condition 4 | Н    | Н         | L     | L            | L              | Н   | L   | Н        | L   | М      | L | Н  |

| Condition 5 | L    | Н         | L     | Н            | L              | L   | L   | Н        | L   | Н      | L | М  |

| Condition 6 | L    | Н         | Н     | Н            | L              | L   | L   | L        | Н   | Н      | М | L  |

| Reverse rotation | (F/R=High), 120° | (120 | /SL=High) |

|------------------|------------------|------|-----------|

|                  |                  |      |           |

|             | Inn             | ut condi | tion |     | Output state |      |               |     |     |        |   |    |  |

|-------------|-----------------|----------|------|-----|--------------|------|---------------|-----|-----|--------|---|----|--|

|             | Input condition |          |      | Hig | h-side g     | jate | Low-side gate |     |     | Output |   |    |  |

| Pin No.     | 15              | 17       | 19   | 3   | 6            | 9    | 5             | 8   | 11  | 4      | 7 | 10 |  |

| FILLINO.    | HU+             | HV+      | HW+  | UHG | VHG          | WHG  | ULG           | VLG | WLG | U      | V | W  |  |

| Condition 1 | L               | L        | Н    | L   | L            | н    | L             | Н   | L   | М      | L | Н  |  |

| Condition 2 | Н               | L        | Н    | Н   | L            | L    | L             | Н   | L   | Н      | L | М  |  |

| Condition 3 | Н               | L        | L    | Н   | L            | L    | L             | L   | Н   | Н      | М | L  |  |

| Condition 4 | Н               | Н        | L    | L   | Н            | L    | L             | L   | Н   | М      | Н | L  |  |

| Condition 5 | L               | Н        | L    | L   | Н            | L    | Н             | L   | L   | L      | Н | М  |  |

| Condition 6 | L               | Н        | Н    | L   | L            | Н    | Н             | L   | L   | L      | М | Н  |  |

| ST/SP        | Mode           |  |

|--------------|----------------|--|

| OPEN or High | Standby        |  |

| L            | Operating mode |  |

<Input condition>

| Hall input voltage | Н | : | 2.0V |

|--------------------|---|---|------|

|                    | Μ | : | 1.5V |

|                    | L | : | 1.0V |

| HU-, HV-, HW-      |   | : | Μ    |

<Output criteria>

High-side FET gate voltage: L $\leq$ output (U, V, W) + 1V, VG - 1V $\leq$ HLow-side FET gate voltage: L $\leq$ 1V, 9V $\leq$ H

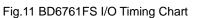

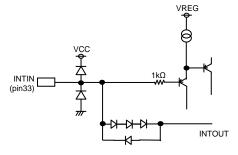

### Timing Chart

2) BD6762FV

#### Hall signal HU+ HU-HV-HV+ HW-HW+ 120° UH UL VH VL THE WН WL 120° slope UH UL Ν И Ν И Ν Г VH Ń И Ņ Ζ Ņ VL Ņ wн Ń Ń И Ν Ν WL

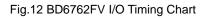

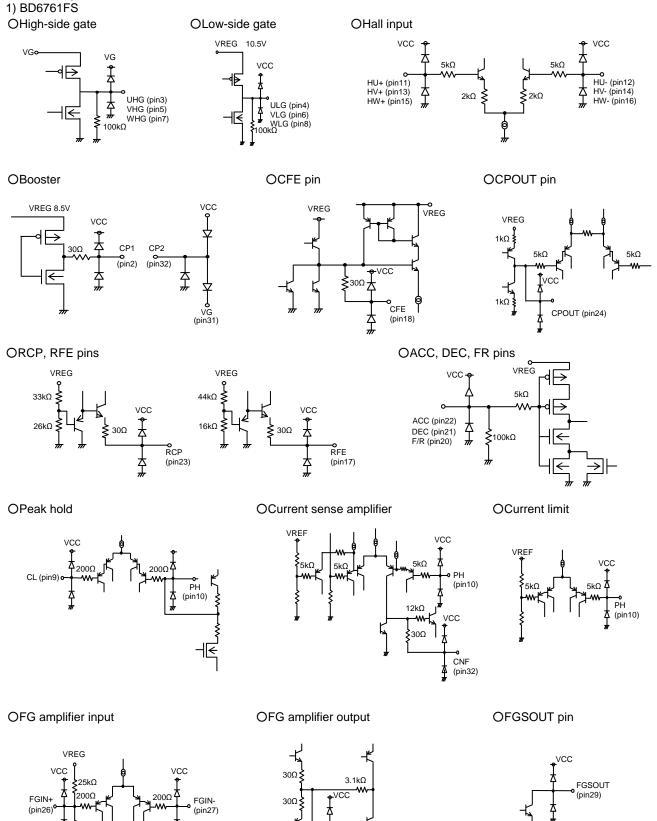

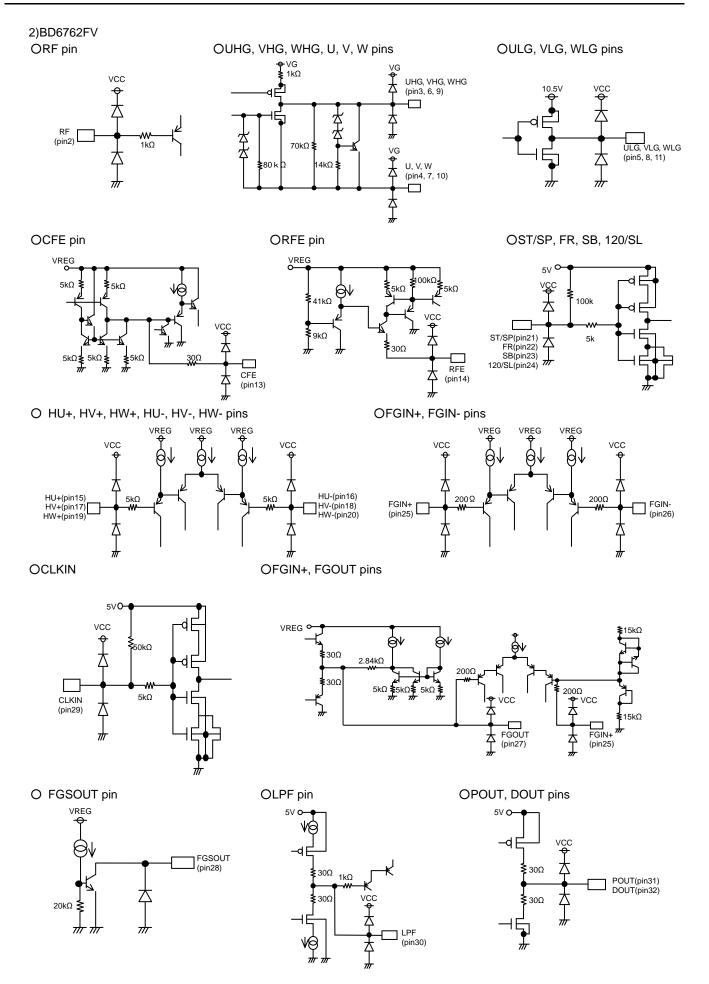

### ●I/O Circuit Diagram

5kQ

FGOUT

## O INTIN pin

OLD pin

O VG, CP2, CP1 pins

#### IC Operation

1) Hall input and output

For the hall input signal, the wave is shaped by the hall amplifier to generate the drive signal. This drive signal is amplified in the predriver block and the gate voltage is output for N-channel MOS FET.

2) PWM operation

PWM oscillating frequency is determined by the triangular waveform frequency which is decided by the external constant. This triangular waveform voltage and the listed voltage in the following chart are compared to perform PWM drive.

|          | Rfe, RFE | Cfe, CFE | Cfe, CFE pin<br>charge/discharge current I | Frequency<br>(Typ.) | Comparison voltage                          |

|----------|----------|----------|--------------------------------------------|---------------------|---------------------------------------------|

| BD6761FS | 50kΩ     | 1000pF   | 1.6V/R                                     | 16.5kHz             | Drive signal shaped by the hall amplifier   |

| BD6762FV | 20kΩ     | 1000pF   | VRFE/R                                     | 16kHz               | Integration amplifier output<br>pin voltage |

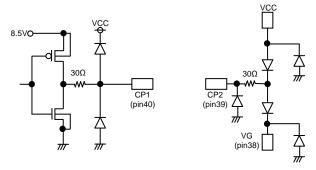

#### 3) Booster circuit (step-up circuit) (common)

BD6761FS (Frequency = 62.5 kHz) and BD6762FV (Frequency = 125 kHz) generate the triangular waveform when the internal oscillator generates free-run oscillation and the rectangular waveform is generated at CP1. When a capacitor is connected between CP1 and CP2, and VG and GND, the step-up voltage is generated at VG pin. In this case, set VCC so that VG does not exceed the absolute maximum ratings (36 V).

| Triangular waveform oscillating<br>frequency |          | Charge pump voltage (VG pin |  |

|----------------------------------------------|----------|-----------------------------|--|

|                                              |          | voltage)                    |  |

| BD6761FS                                     | 62.5 kHz | VCC+6V                      |  |

| BD6762FV                                     | 125 kHz  | VCC+6.7V                    |  |

#### 4) FG amplifier (common)

Set the FG amplifier gain so that the FGOUT pin is within the range of high and low output voltage and the amplitude is higher than the hysteresis width (250 mV: max) of the HYS amplifier.

FGSOUT pin uses an open collector format. Use in the condition as it is pulled up to the power supply with the resistor. At this time, pay attention so that the voltage higher than 36 V is not applied to the FGSOUT pin.

#### 5) ACC, DEC circuits (BD6761FS)

When a resistor is connected to the RCP pin and the low voltage is input to the ACC pin, the current flows out from the CPOUT pin. When the low signal is input to the DEC pin, the current flows in to the CPOUT pin. Furthermore, when the ACC pin and DEC pin both set to low, the current flows in to the CPOUT pin. This current can be converted to the voltage by connecting a filter between the CPOUT and GND pins.

The voltage generated at the CPOUT pin controls the PWM's on-duty and maintains the constant motor rotation by inputting the controlled signal to ACC and DEC pins.

#### 6) Current limit operation

When the CL voltage (BD6761FS) and RF voltage (BD6762FV) become the current limit voltage, the current limit circuit operates and works to limit PWM on\_dutty. It also turns off the current limit circuit (current limit clear) at the peak of PWM triangular waveform and makes the current flow again. Output current lomax at this time are shown in the table.

|                             | Current limit current |  |  |

|-----------------------------|-----------------------|--|--|

| BA6761FS                    | Iomax=0.48/RNF [A]    |  |  |

| BA6762FV Iomax=0.26/RNF [A] |                       |  |  |

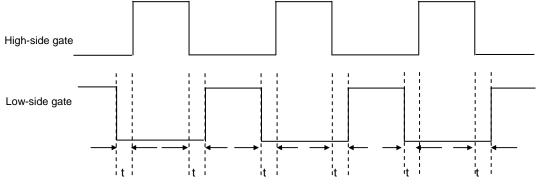

Output simultaneous on prevention circuit (BD6761FS, BD6762FV) 7)

When the low-side gate voltage becomes high while the high-side gate voltage is low, or when the high-side gate voltage becomes high while the low-side gate voltage is low, the simultaneous on prevention time is provided with t=3.2 µs (TYP value). When the input capacity of external FET is C and the gate connection resistor is R, set R to satisfy the following equation so that the simultaneous on prevention time as mentioned above is not exceeded.

$$C \leq \frac{1.8\mu}{10 \times (24 + R)}$$

Check that the simultaneous on is not made in the actual operation and then set C and R.

Fig.13 High/Low-side Simultaneous On Prevention Timing Chart

8) Short brake (BD6761FS and BD6762FV)

BD6761FS operates the short brake action with the ACC and DEC pins set to low, and BD6762FV does with the SB pin set to OPEN or high. At the time of short brake, the high-side gate is turned off and the low-side is turned on. At the time of short brake operating, the current flows to the output FET, which is decided by the motor's counter electromotive voltage and coil impedance. Since this current flows via path which does not run through the overcurrent protection (current limit) detection resistor, the overcurrent protection does not operate as IC operating. Therefore, the current more than the overcurrent protection set current may flow to the output FET, pay attention so that it does not exceed the output FET rating.

9) Forward/reverse rotation circuit (BD6761FS and BD6762FV)

Forward /reverse rotation of motor can be switched according to the FR pin input conditions. Logics of the hall input and output conditions according to the FR pin input conditions are shown in the I/O conditions table (P.10). If the FR pin is switched during the motor rotation, since the simultaneous on prevention circuit in IC operates, the feed through current does not flow. However, since the motor current flows in the direction to the power source due to the electromotive force, the voltage may be raised if the power source does not have the power supply voltage absorption ability. Examine the capacitor characteristics between the power supply and ground sufficiently and then pay attention so that the power supply voltage and step-up voltage do not exceed the absolute maximum ratings. When the physical measures are taken such as increasing the capacitor value which is connected between the power supply and ground, check the characteristics enough prior to use.

10) Start/stop circuit (BD6762FV)

When the ST/SP pin is in the sate of OPEN or high, IC becomes standby. In the case of standby, some circuits operation are turned off to reduce the current consumption.

When the ST/SP pin is in the state of low, IC becomes operating.

11) Low voltage protection circuit (BD6761FS and BD6762FV)

This IC builds in the low voltage protection circuit. When VCC becomes lower than 11.5 V (Typ.), the high-side and low-side gates are both turned off to make the coil turn off. Protection off voltage is 12.0 V (Typ.) and hysteresis width is 0.5 V (Typ.).Since the motor locking protection detection circuit operates in BD6762FV during the low voltage protection operation, if the low voltage protection operating time becomes longer than the motor locking protection detection time, the operation moves to the motor locking protection operation after the low voltage protection operation.

12) Built-in 120° slope PWM logic (BD6762FV)

It is possible to perform 120° drive by setting 120/SL pin to OPEN or making high. 120° slope drive is possible by setting the 120/SL pin to OPEN or making high. Low noise design is realized by reducing the electromagnetic sound generated at the time of phase switching by means of gradually changing the output PWM on-duty during 120° slope energization. However, at the time of startup or the hall input frequency is lower than about 3 Hz (Typ. value), it becomes 120° drive. When the hall input frequency is more than about 3 Hz (Typ. value) and the rise of hall U-phase is detected 7 times, it switches to the 120° slope drive.

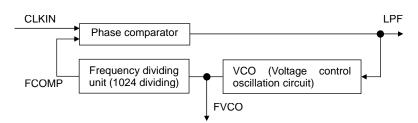

#### 13) Servo circuit (BD6762FV)

- Frequency multiplication circuit (Dividing period) (BD6762FV)

- This IC builds in the frequency multiplication circuit.

Servo circuit is composed of the feedback loop as shown in the diagram and flows in/out the current ( $22 \mu A$ : Typ.) to the LPF pin (30 pin) by detecting the phase difference between the CLKIN pin (29 pin) and the frequency dividing unit output FCOMP. The phase difference signal output to the LPF pin (30 pin) is smoothed by the filter which is connected at the IC external of the LPF pin (30 pin) and this voltage is input to the VCO (Voltage control oscillation circuit) to decide the frequency for the internal signal FVCO. Since the dividing ratio of this frequency dividing unit is set to 1024, the relation of

#### FVCO[Hz]=1024 · FCOMP[Hz]

can be obtained, and the FCOMP and CLKIN have the same frequency according to the feedback loop as shown in the following diagram, therefore the multiplied frequency of 1024 times of FCOMP or CLKIN is acquired as the FVCO frequency.

Speed discriminator (BD6762FV)

The FGSOUT signal (28 pin) which detects the motor rotation speed and the reference clock in IC are compared and the acceleration/deceleration signal is output to the DOUT pin (32 pin). Reference clock is the signal (FVCO) that the CLKIN signal (29 pin) is multiplied by 1024. When the FG period is short to the reference clock period, it is determined that the motor revolution speed is too fast and the difference from the reference clock period is output to the DOUT pin as the deceleration command. When the FG period is long, the difference is output as an accelerating command.

PLL (BD6762FV)

Phases of the FGSOUT (28 pin) signal which detected the motor revolution speed and the CLKIN (29 pin) input from the external are compared, and if the FG phase leads to CLKIN (28 pin), the difference is output as the deceleration command. If the FG phase lags, the difference is output as the acceleration command.

Integration amplifier (BD6762FV)

Speed error of the reference clock which is obtained in the speed discriminator block and the FG signal, and the phase difference signal of the CLKIN acquired in PLL block and the FG are integrated together and smoothed to become the DC voltage. This smoothed signal determines the PWM on-duty.

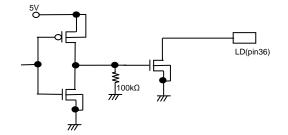

14) Speed lock detection circuit (BD6762FV)

When the motor speed is within  $\pm 6.25\%$  range to the CLKIN signal (29 pin), L is output to the LD pin (36 pin) output. Since the LD pin (36 pin) has the open/drain output format, use as it is pulled up to the power supply with the resistor (100k $\Omega$ ). At this time, pay attention so that the voltage more than 36 V is not applied to the LD pin.

15) Motor locking protection (BD6762FV)

Motor locking protection circuit judges he motor is in the locking condition when the motor speed is not in the lock range (preset value:  $\pm 6.25\%$ ) and the motor locking detection time  $T_{LP}$  elapsed, the high-side and low-side output gates are both turned off.Motor locking protection can be cleared by making the condition Low after setting the ST/SP pin or the SB pin to OPEN or making high. Motor locking detection time  $T_{LP}$  is determined by the capacitor C7 which is connected to the LP pin and the count number CLP (preset value: 96) of the internal counter.

T<sub>LP</sub>=2×10<sup>5</sup>×C7×CLP [S]

### •Selecting application components

| Selecting application components                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Design method                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Design example                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| ①Output FET<br>This IC is the predriver for high-side and low-side N-channel<br>MOS FET drive. Select the FET with the required current<br>capacity to drive the motor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Recommended FET RDS035L03 (A)                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| ②Diodes (BD67861FS)<br>Diodes are required to protect between the gate and source of<br>output FET.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Recommended diode 1SS355<br>Insert the diode in the direction from high-side<br>FET source to the gate side (in the forward direction).                                                                                                                                                                                                                                                                                                                                   |

| ③Protection capacitor between the output FET drain and source<br>Check the operation so that the voltage between the output FET<br>drain and source does not exceed the absolute maximum<br>ratings due to the fluctuation of VCC at the time of PWM driving<br>and then set the value.                                                                                                                                                                                                                                                                                                                                                                       | A value of $0.01\mu$ to $0.1\mu$ F is recommended.<br>A value of $0.1\mu$ F is appropriate for the capacitance.<br>Insert the capacitor between the output FET drain and<br>source. (Position at the close point to FET as much as<br>possible.)                                                                                                                                                                                                                          |

| (4)VB current capacitance capacitor<br>Current capacity from VG changes according to the capacitance<br>to be connected. However, if the capacitance is too large, the<br>following action is delayed when VCC starts up, and the<br>magnitude relation becomes VCC > VG which should be VCC <<br>VG usually and the large current may flow in internal block<br>circuits and result in damaging the circuits. When VG is directly<br>supplied from the external block without using the internal<br>circuits, disconnect the capacitor between CP1 and CP2, and<br>connect the 20k $\Omega$ resistor (for noise reduction) between CP1<br>and ground to use. | A value of 0.01μF is appropriate for the capacitor<br>between CP1 and CP2<br>(A value of 0.01μF 0.1μF is recommended.)<br>A value of 0.1μF is appropriate for the capacitor<br>between VG and VCC.                                                                                                                                                                                                                                                                        |

| ⑤PWM frequency<br>PWM frequency can be adjusted by the capacitance and<br>resistance to connect. When the frequency is high, the heat<br>generation increases due to switching loss. When the frequency<br>is low, it enters audible range. Check the operation with the<br>actual product and determine the constant.                                                                                                                                                                                                                                                                                                                                        | The following constants are appropriate.<br>BD6761FS Cfe=1000pF, Rfe=50kΩ, fo=16.5kHz(TYP.)<br>BD6762FV Cfe=1000pF, Rfe=20kΩ, fo=16.0kHz(TYP.)                                                                                                                                                                                                                                                                                                                            |

| (6)Hall input level<br>The current value to feed to the hall element changes by<br>changing the resistance and the amplitude level of hall element<br>can be adjusted.<br>Amplitude level increases when the resistance value is chosen<br>smaller by considering the noise affect, but pay attention also to<br>the hall input voltage range. BD6761FS (1.5V to 4.1V) and<br>BD6762FV (0V to 3V)                                                                                                                                                                                                                                                             | Connect to the transistor base via $1k\Omega$ resistor (base current limit) from the VREG pin. Connect the transistor collector to VCC, the emitter to the hall element via R1. Connect the ground side of hall element to the ground via R2.<br>A value of $200\Omega$ to $1k\Omega$ is recommended. A value of $200\Omega$ is appropriate, respectively. When connecting to the VCC side directly with R1, values of R1=5k $\Omega$ and R2=2k $\Omega$ are appropriate. |

| ⑦VREG<br>VREG which is the internal voltage output pin drives the circuits<br>in IC. Connect the capacitor to stabilize it.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | A value of $0.01\mu$ F to $0.1\mu$ F is recommended. A value of $0.1\mu$ is appropriate.                                                                                                                                                                                                                                                                                                                                                                                  |

| Ourrent limit<br>The current flowing to FET can be controlled by setting the<br>resistance value. Determine the constant according to the motor<br>specifications.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Following equation shows the current value.<br>BD6761FS lomax=0.48/RNF [A]<br>BD6762FV lomax=0.26/RNF [A]                                                                                                                                                                                                                                                                                                                                                                 |

| (9)Hall input noise<br>Insert capacitors between the hall phases in order to eliminate<br>the hall input noise due to the effect by the pattern routing<br>design.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | A value of $0.01\mu$ F is appropriate for the capacitor to be<br>installed between the hall phases.<br>A value of $0.01\mu$ F to $0.1\mu$ F is recommended.                                                                                                                                                                                                                                                                                                               |

| ①CL (RF) voltage smoothing low pass filter<br>Smooth the CL (RF) voltage which has PWM noise through the<br>low pass filter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | A value of C = 470pF and R=1k $\Omega$ is appropriate for the<br>low pass filter.<br>For the external constant, since the impedance is high,<br>make sure to design the pattern with the shortest circuit<br>route so that the circuit is hard to be affected by noise.                                                                                                                                                                                                   |

| <ul> <li>(1)FG AMP constant setting         FG AMP gain: GFG is the ratio of R1 and R2 calculated by the         following equation.         GFG=20log R2/R1 [dB]         Set up the gain so that the FGOUT amplitude is large enough to         the hysteresis level of the hysteresis comparator and it cannot         be clamped by the high and low output voltages         (VFGOH and VFGOL).     </li> </ul>                                                                                                                                                                                                                                            | R1 and C1 form a high pass filter and R2 and C2 form a<br>low pass filter. Each cut off frequency; fMPF and fLPF<br>is determined by the following equation.<br>fMPF=1/2 $\pi$ R1C1, fLPF=1/2 $\pi$ R2C2<br>Set the value so that the main signal from PG by the<br>motor is not attenuated but the unnecessary noise can<br>be attenuated.                                                                                                                               |

| Design method                                                                                                                         | Design example                                                               |

|---------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| Phase compensation capacitor (BD6761FS)                                                                                               | A value of 0.001µF to 0.1µF is recommended.                                  |

| Phase compensation is performed in the output of the CS                                                                               | A value of 0.001µF is appropriate for BA6680FS.                              |

| amplifier. The capacitance value should be selected according                                                                         | A value of $0.1\mu$ F is appropriate for BD6761FS.                           |

| to the servo constant, and proper motor operation should be                                                                           |                                                                              |

| confirmed. When the capacitance is large, the I/O response                                                                            |                                                                              |

| becomes bad. When it is small, the output becomes easy to                                                                             |                                                                              |

| oscillate.                                                                                                                            |                                                                              |

| WCC pin                                                                                                                               | A value of value $1\mu$ F to $10\mu$ F is recommended.                       |

| Set up the capacitance for the stabilization and noise reduction                                                                      | A value of 10µF is appropriate.                                              |

| on the power line.                                                                                                                    |                                                                              |

| <pre></pre>                                                                                                                           | Recommended value                                                            |

| Filter composed of C3, C4 and R3 smoothes the current pulses                                                                          | C3: $0.01\mu$ F to $0.1\mu$ F; a value of $0.01\mu$ F is appropriate.        |

| output from the CPOUT pin and converts it to DC.                                                                                      | C4: $0.033\mu$ F to $0.33\mu$ F; a value of $0.1\mu$ F is appropriate.       |

| This impedance Z is shown by the following equation.                                                                                  | R3 : $30k\Omega$ to $300k\Omega$ ; a value of $100k\Omega$ is appropriate.   |

|                                                                                                                                       |                                                                              |

| $Z = R3 \times \frac{C_4}{C3+C4} \times \frac{S+\omega_2}{S\left(1+\frac{S}{\omega_1}\right)}$                                        |                                                                              |

| $C3+C4$ $S \mid 1+\frac{S}{3} \mid$                                                                                                   |                                                                              |

| When the pole frequency is set to fP1 and fP2, they are:                                                                              |                                                                              |

| $fP1=\omega_1/2\pi = 1/2\pi (C3//C4)R3$                                                                                               |                                                                              |

| $fP2=\omega_2/2\pi = 1/2\pi C4R3$                                                                                                     |                                                                              |

| (5)Output FET gate voltage stabilization resistor                                                                                     | Establish R so that the simultaneous on prevention time                      |

| When the noise is generated at the time of external MOSFET                                                                            | is not exceeded as shown in 7). Output simultaneous of                       |

| on/off due to the rise and fall speed of the IC output, insert the                                                                    | prevention circuit in P.17/24 Operating Explanation.                         |

| resistor between the IC output and external MOSFET gate.                                                                              | A value of $R = 0\Omega$ is appropriate.                                     |

| resistor between the IC output and external MOSFET gate.                                                                              | A value of $R = 0\Omega$ is appropriate.                                     |

| BPeak hold setting capacitor (BD6761FS)                                                                                               | A value of 0.33µF is appropriate.                                            |

| Charges the peak hold on the voltage at the current detection                                                                         | A value of 0.35µF is appropriate.                                            |

| pin CL.                                                                                                                               |                                                                              |

| OMotor locking detection time setting capacitor (BD6762FV)                                                                            | A value of 0.22µF is appropriate.                                            |

|                                                                                                                                       | A value of 0.22µr is appropriate.                                            |

| Motor locking detection time $T_{LP}$ is determined by the capacitor                                                                  |                                                                              |

| C7 which is connected to the LP pin and the count number CLP                                                                          |                                                                              |

| (Preset value: 96) of the internal counter. The $T_{LP}$ is shown by                                                                  |                                                                              |

| the following equation.<br>TLP=2×10⁵×C7×96                                                                                            |                                                                              |

|                                                                                                                                       | Decommonded volue                                                            |

| Integration amplifier constant setting (BD6762FV) Speed dispriminates side surrant value ID is shown bull 1.2 5/D4.                   | Recommended value                                                            |

| Speed discriminator side current value ID is shown by $ I_D =2.5/R4$                                                                  | R4: 10kΩ to 40kΩ; a value of 20 kΩ is appropriate.                           |

| and the PLL side current value IP is shown by IP = 2.5/R5.                                                                            | R5: $300k\Omega$ to $3M\Omega$ ; a value of $1 M\Omega$ is appropriate.      |

| Therefore, the current $I_{IN}$ which flows in the integration AMP                                                                    | R6: $100k\Omega$ to $500k\Omega$ ; a value of 220 k $\Omega$ is appropriate. |

| input pin INTIN is shown by $I_{IN}=I_D+I_P$ .                                                                                        | C5: $0.01\mu$ F to $0.1\mu$ F; a value of $0.047\mu$ F is appropriate        |

| The larger the $I_{IN}$ is, the higher the integration amplifier gain                                                                 | C6: $0.033\mu$ F to $1.0\mu$ F; a value of $0.47\mu$ F is appropriate        |

| becomes.                                                                                                                              |                                                                              |

| Gains of the speed discriminator and PLL can be set by                                                                                |                                                                              |

| adjusting R4 and R5.                                                                                                                  |                                                                              |

| Gain G is shown by the following equation.                                                                                            |                                                                              |

| $G = \frac{R6}{R4 //R5} \times \frac{C6}{C5+C6} \times \frac{S+\omega_2}{S\left(1+\frac{S}{U_{H}}\right)}$                            |                                                                              |

| $G = \frac{G}{R4 / R5} \times \frac{C5+C6}{C5+C6} \times \frac{G}{C5+C6}$                                                             |                                                                              |

| $S\left[1+\frac{\omega_{1}}{\omega_{1}}\right]$                                                                                       |                                                                              |

| When the pole frequency is get to (D4 and (D0, there are                                                                              |                                                                              |

| When the pole frequency is set to fP1 and fP2, they are:                                                                              |                                                                              |

| $fP1=\omega_1/2\pi = 1/2\pi (C5//C6) \times R6$                                                                                       |                                                                              |

| $fP2=\omega_2/2\pi = 1/2\pi C6R6$                                                                                                     |                                                                              |

| (19LPF external constant (BD6762FV)                                                                                                   | Recommended value                                                            |

| Filter composed of C8, C9 and R7 smoothes the current pulses                                                                          | C8: $0.1\mu$ F to $0.6\mu$ F; a value of $0.33\mu$ F is appropriate.         |

| output from the LPF pin and converts it to DC.                                                                                        | C9: $0.1\mu$ F to $0.6\mu$ F; a value of $0.33\mu$ F is appropriate.         |

| This impedance Z is shown by the following equation.                                                                                  | R7: $0.5k\Omega$ to $10k\Omega$ ; a value of $2k\Omega$ is appropriate.      |

| C9 S+ω <sub>2</sub>                                                                                                                   |                                                                              |

| $Z = R7 \times \frac{C9}{C8 + C9} \times \frac{S + \omega_2}{S \left(1 + \frac{S}{\omega_1}\right)}$                                  |                                                                              |

| $S   1 + \frac{S}{1}  $                                                                                                               |                                                                              |

|                                                                                                                                       |                                                                              |

| ζ ω <sub>1</sub> Σ                                                                                                                    |                                                                              |

| When the pole frequency is set to fP1 and fP2, they are:<br>$fP1=\omega_1/2\pi = 1/2\pi$ (C8//C9)R7 $fP2=\omega_2/2\pi = 1/2\pi$ C9R7 |                                                                              |

\*\*Setting values in these materials are only for reference. Actual set may change its characteristics due to the boards layout, wiring and components type to use. Please perform the sufficient verification using the actual product for the field operation.

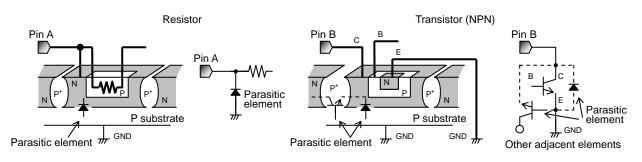

#### Notes for use

#### (1) Absolute maximum ratings

This product is subject to a strict quality management regime during its manufacture. Use of the IC in excess of absolute maximum ratings such as the applied voltage or operating temperature range may result in IC damage. Assumptions should not be made regarding the state of the IC (short mode or open mode) when such damage is suffered. A physical safety measure such as a fuse should be implemented when use of the IC in a special mode where the absolute maximum ratings may be exceeded is anticipated.

#### (2) Connecting the power supply connector backward

Connecting the power supply connector backwards may result in damage to the IC. For the protection of the IC from reversed connections, provide an appropriate measure, such as the insertion of an external diode each between the power supply and the power supply pin of the IC and between the motor coils.

(3) Power supply lines