# PN7462 family NFC Cortex-M0 microcontroller Rev. 4.5 — 14 April 2020

**Product data sheet COMPANY PUBLIC**

# **General description**

The PN7462 family is a family of 32-bit Arm Cortex-M0-based NFC microcontrollers offering high performance and low power consumption. It has a simple instruction set and memory addressing along with a reduced code size compared to existing architectures. PN7462 family offers an all in one solution, with features such as NFC, supporting all NFC Forum modes, microcontroller, optional contact smart card reader, and software in a single chip. It operates at CPU frequencies of up to 20 MHz.

Table 1. Comparison of the PN7462 family members

|                                 |               | 1 147 402 Talling |               |             |             |             |             |

|---------------------------------|---------------|-------------------|---------------|-------------|-------------|-------------|-------------|

|                                 | PN7462AUHN    | PN7462AUEV        | PN7412AUHN    | PN7362AUHN  | PN7362AUEV  | PN7360AUHN  | PN7360AUEV  |

| Contact<br>smart card<br>reader | Class A, B, C | No                | Class A, B, C | No          | No          | No          | No          |

| ISO/IEC<br>7816 UART            | Yes           | Yes               | Yes           | No          | No          | No          | No          |

| Contactless interface           | Yes           | Yes               | No            | Yes         | Yes         | Yes         | Yes         |

| Available<br>Flash<br>memory    | 160 kB        | 160 kB            | 160 kB        | 160 kB      | 160 kB      | 80 kB       | 80 kB       |

| SRAM data<br>memory             | 12 kB         | 12 kB             | 12 kB         | 12 kB       | 12 kB       | 12 kB       | 12 kB       |

| General<br>purposes I/<br>O     | 12 up-to 21   | 14 up-to 21       | 12 up-to 21   | 14 up-to 21 | 14 up-to 21 | 14 up-to 21 | 14 up-to 21 |

| Package<br>type                 | HVQFN64       | VFBGA64           | HVQFN64       | HVQFN64     | VFBGA64     | HVQFN64     | VFBGA64     |

Having the differences listed in the table above, all products within the PN7462 family are equipped with 12 kB of SRAM data memory and 4 kB EEPROM. All products within the family also include one host interface with either high-speed mode I<sup>2</sup>C-bus, SPI, USB or high-speed UART, and two master interfaces, SPI and Fast-mode Plus I<sup>2</sup>C-bus. Four general-purpose counter/timers, a random number generator, one CRC coprocessor and up to 21 general-purpose I/O pins.

The PN7462 family NFC microcontroller offers a one chip solution to build contactless, or contact and contactless applications. It is equipped with a highly integrated high-power output NFC-IC for contactless communication at 13.56 MHz enabling EMV-compliance on RF level, without additional external active components.

By integrating a contact ISO/IEC 7816 interface on a single chip, the PN7462AUHN provides a solution for dual interface smart card readers. Whereas the PN7412AUHN offers a solution for a contact reader only. The PN7462AUHN and PN7412AUHN contact

interfaces offer a high level of security for the card by performing current limiting, short-circuit detection, ESD protection as well as supply supervision. On PN7462AUHN, PN7412AUHN and PN7462AUEV, an additional UART output is also implemented to address applications where more than one contact card slot is needed. It enables an easy connection to multiple smart card slot interfaces like TDA8026.

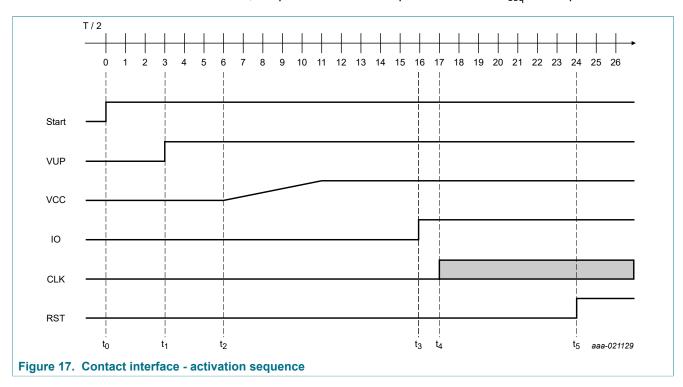

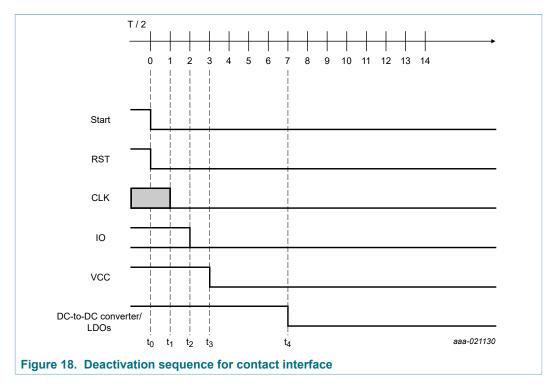

PN7462AUHN and PN7412AUHN provide thermal and short-circuit protection on all card contacts. It also provides automatic activation and deactivation sequences initiated by software or hardware.

#### 2 Features and benefits

#### 2.1 Integrated contact interface frontend

This chapter applies to the products with contact interface only.

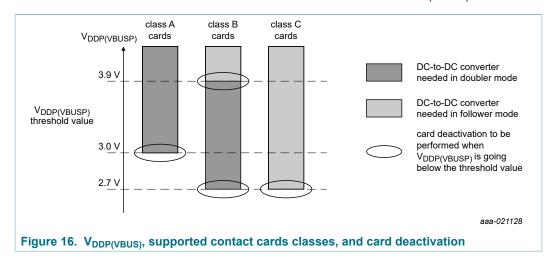

- Class A, B, and C cards can work on 1.8 V, 3 V, and 5 V supply

- Specific ISO UART, variable baud rate through frequency or division ratio programming, error management at character level for T = 0, and extra guard time register

- DC-to-DC converter for class A support starting at 3 V, and class B support starting at 2.7 V

- Thermal and short-circuit protection on contact cards

- Automatic activation and deactivation sequence, initiated by software or by hardware in case of short-circuit, card removal, overheating, and V<sub>DD</sub> or V<sub>DD</sub> drop-out

- Enhanced ESD protection (> 12 kV)

- ISO/IEC 7816 compliant

- Compliance with EMV contact protocol specification

- Clock generation up to 13.56 MHz

- · Synchronous card support

- Possibility to extend the number of contact interfaces, with the addition of slot extenders such as TDA8026

#### 2.2 Integrated ISO/IEC 7816-3&4 UART interface

This chapter applies to the products with Integrated ISO/IEC 7816 UART interface only.

The PN7462 family offers the possibility to extend the number of contact interfaces available. It uses an I/O auxiliary interface to connect a slot extension (TDA8035 - 1 slot, TDA8020 - 2 slots, and TDA8026 - 5 slots).

- Class A (5 V), class B (3 V), and class C (1.8 V) smart card supply

- Protection of smart card

- Three protected half-duplex bidirectional buffered I/O lines (C4, C7, and C8)

- Compliant with ISO/IEC 7816 and EMVCo standards

#### 2.3 Integrated contactless interface frontend

This chapter applies to the products with integrated contactless interface only.

- High RF output power frontend IC for transfer speed up to 848 kbit/s

- NFC IP1 and NFC IP2 support

- Full NFC Forum tag support (type 1, type 2, type 3, type 4A, type 4B and type 5)

- · P2P active and passive, target, and initiator

- · Card emulation ISO14443 type A

- ISO/IEC 14443 type A and type B

- MIFARE products using Crypto 1

- ISO/IEC 15693, and ISO/IEC 18000-3 mode 3

- Low-power card detection

- Dynamic Power Control (DPC)

PN7462\_FAM

All information provided in this document is subject to legal disclaimers.

- Adaptive Wave Control (AWC)

- Adaptive Range Control (ARC)

- Compliance with EMV contactless protocol specification

- Processor core

- Arm Cortex: 32-bit M0 processor

- Built-in Nested Vectored Interrupt Controller (NVIC)

- Non-maskable interrupt

- 24-bit system tick timer

- Running frequency of up to 20 MHz

- Clock management to enable low power consumption

- Memory

- Flash: 160 kB / 80 kB

- SRAM: 12 kB

- EEPROM: 4 kB

- 40 kB boot ROM included, including USB mass storage primary boot loader for code download

- Debug option

- Serial Wire Debug (SWD) interface

- Peripherals

- Host interface:

- USB 2.0 full speed with USB 3.0 hub connection capability

- HSUART for serial communication, supporting standards speeds from 9600 bauds to 115200 bauds, and faster speed up to 1.288 Mbit/s

- SPI with half-duplex and full duplex capability with speeds up to 7 Mbit/s

- I<sup>2</sup>C supporting standard mode, fast mode, and high-speed mode with multiple address supports

- Master interface:

- SPI with half-duplex capability from 1 Mbit/s to 6.78 Mbit/s

- I<sup>2</sup>C supporting standard mode, fast mode, fast mode plus, and clock stretching

- Up to 21 General-Purpose I/O (GPIO) with configurable pull-up/pull-down resistors

- GPIO1 to GPIO12 can be used as edge and level sensitive interrupt sources

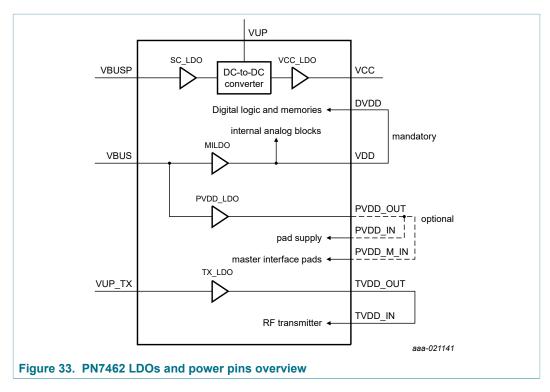

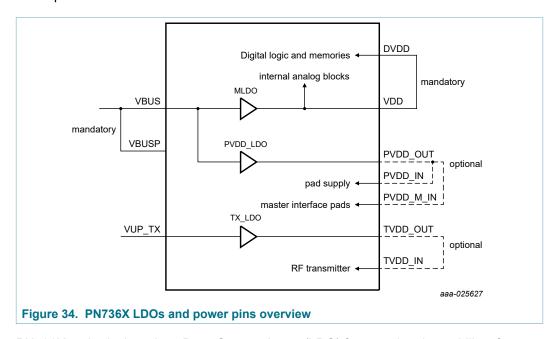

- Power

- Two reduced power modes: standby mode and hard power-down mode

- Supports suspend mode for USB host interface

- Processor wake-up from hard power-down mode, standby mode, suspend mode via host interface, GPIOs, RF field detection

- Integrated PMU to adjust internal regulators automatically, to minimize the power consumption during all possible power modes

- Power-on reset

- RF supply: external, or using an integrated LDO (TX LDO, configurable with 3 V, 3.3 V, 3.6 V, 4.5 V, and 4.75 V)

- Pad voltage supply: external 3.3 V or 1.8 V, or using an integrated LDO (3.3 V supply)

- Timers

- Four general-purpose timers

PN7462\_FAM

All information provided in this document is subject to legal disclaimers.

- Programmable Watchdog Timer (WDT)

- CRC coprocessor

- Random number generator

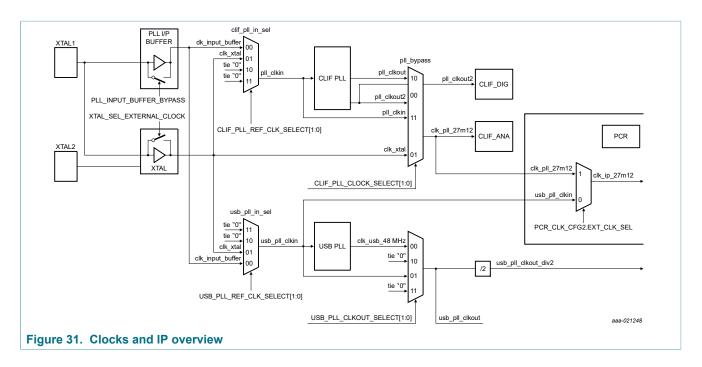

- Clocks

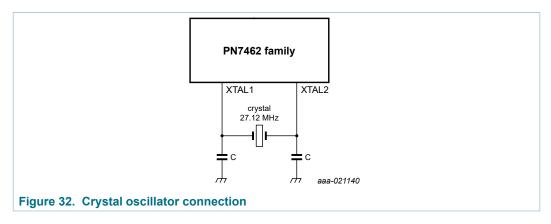

- Crystal oscillator at 27.12 MHz

- Dedicated PLL at 48 MHz for the USB

- Integrated HFO 20 MHz and LFO 365 kHz

- General

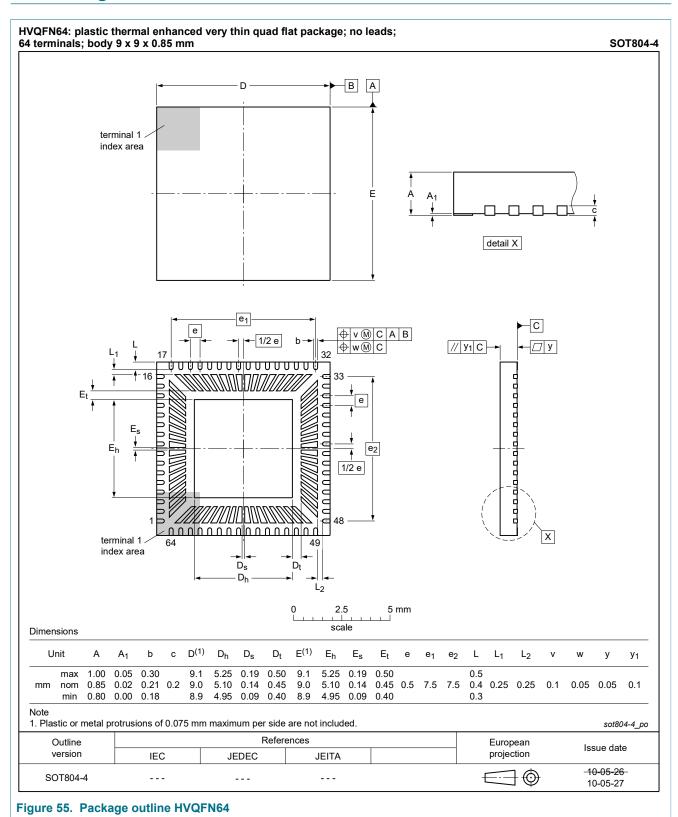

- HVQFN64 package

- VFBGA64 package

- Temperature range: -40 °C to +85 °C

# 3 Applications

- · Physical access control

- Gaming

- USB NFC reader, including dual interface smart card readers

- Home banking, payment readers EMVCo compliant

- · High integration devices

- NFC applications

## 4 Quick reference data

#### Table 2. Quick reference data

Operating range: -40 °C to +85 °C unless specified; contact interface:  $V_{DDP(VBUSP)} = V_{DDP(VBUS)}$ ; contactless interface: internal LDO not used

| Symbol                 | Parameter                        | Conditions                                                                                   | Min  | Тур | Max  | Unit |

|------------------------|----------------------------------|----------------------------------------------------------------------------------------------|------|-----|------|------|

| V <sub>DDP(VBUS)</sub> | power supply voltage on pin VBUS | card emulation, passive target (PLM)                                                         | 2.3  | -   | 5.5  | V    |

|                        |                                  | all RF modes; class B and class<br>C contact interface support                               | 2.7  | -   | 5.5  | V    |

|                        |                                  | all RF modes; class A, class B and class C contact interface support                         | 3    | -   | 5.5  | V    |

| $V_{DD(PVDD)}$         | PVDD supply voltage              | 1.8 V                                                                                        | 1.65 | 1.8 | 1.95 | V    |

|                        |                                  | 3.3 V                                                                                        | 3    | 3.3 | 3.6  | V    |

| I <sub>DDP(VBUS)</sub> | power supply current on pin VBUS | in hard power-down mode; T = 25 °C; V <sub>DDP(VBUS)</sub> = 5.5 V; RST_N = 0                | -    | 12  | 18   | μΑ   |

|                        |                                  | stand by mode; T = 25 °C;<br>V <sub>DDP(VBUS)</sub> = 3.3 V; external<br>PVDD LDO used       | -    | 18  | -    | μΑ   |

|                        |                                  | stand by mode; T = 25 °C;<br>V <sub>DDP(VBUS)</sub> = 5.5 V; internal<br>PVDD LDO used       | -    | 55  | -    | μΑ   |

|                        |                                  | suspend mode, USB interface; V <sub>DDP(VBUS)</sub> = 5.5 V; external PVDD supply; T = 25 °C | -    | 120 | 250  | μΑ   |

| I <sub>DD(TVDD)</sub>  | TVDD supply current              | on pin TVDD_IN; maximum supported operating current by the contactless interface             | -    | -   | 250  | mA   |

| P <sub>max</sub>       | maximum power dissipation        |                                                                                              | -    | -   | 1050 | mW   |

| T <sub>amb</sub>       | ambient temperature              | JEDEC PCB                                                                                    | -40  | -   | +85  | °C   |

# 5 Ordering information

The table below lists the ordering information of the PN7462 family.

Table 3. Ordering information

| Type number | Package |                                                                                                                                                                                                |           |

|-------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

|             | Name    | Description                                                                                                                                                                                    | Version   |

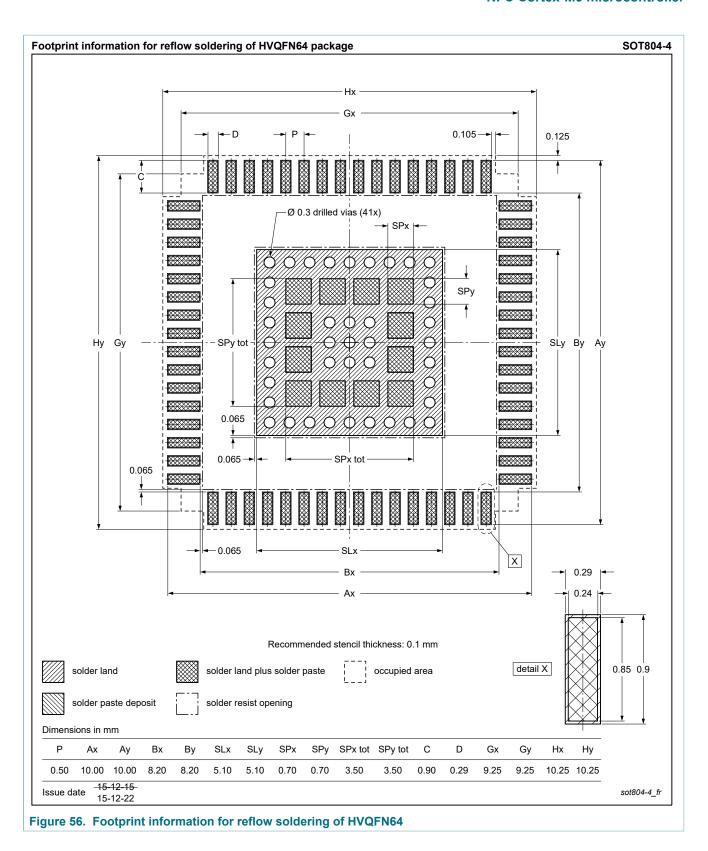

| PN7462AUHN  | HVQFN64 | 160 kB memory; contact interface; ISO/IEC 7816-3&4 UART interface; plastic thermal enhanced very thin quad flat package; no leads; 64 terminals; body 9 × 9 × 0.85 mm                          | SOT804-4  |

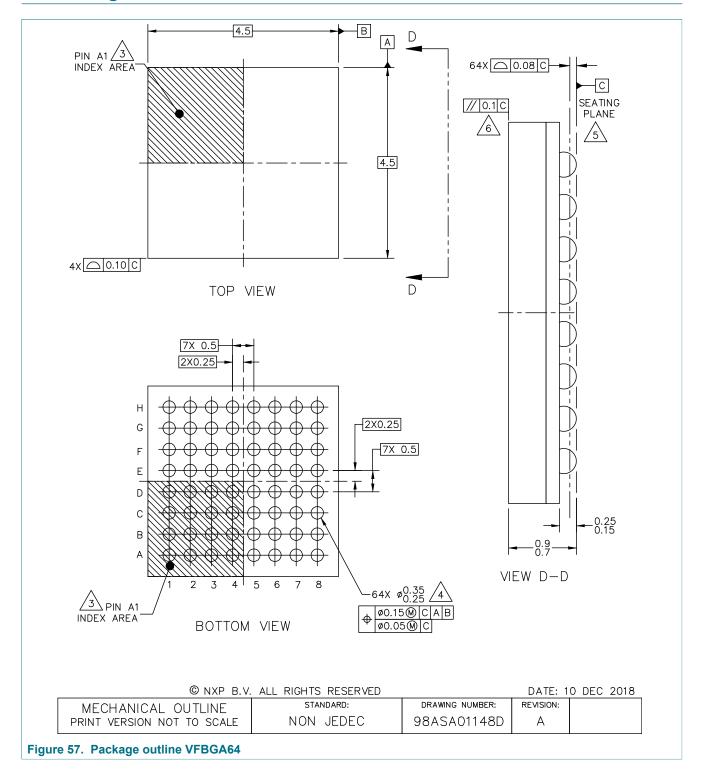

| PN7462AUEV  | VFBGA64 | 160 kB memory; no contact interface; ISO/IEC 7816-3&4 UART interface; plastic very thin fine-pitch ball grid array package; 64 balls; 4.5 mm x 4.5 mm x 0.80 mm                                | SOT1307-2 |

| PN7412AUHN  | HVQFN64 | 160 kB memory; contact interface; ISO/IEC 7816-3&4 UART interface; no contactless interface plastic thermal enhanced very thin quad flat package; no leads; 64 terminals; body 9 × 9 × 0.85 mm | SOT804-4  |

| PN7362AUHN  | HVQFN64 | 160 kB memory; no contact interface; no ISO/IEC 7816-3&4 UART interface; plastic thermal enhanced very thin quad flat package; no leads; 64 terminals; body 9 × 9 × 0.85 mm                    | SOT804-4  |

| PN7362AUEV  | VFBGA64 | 160 kB memory; no contact interface; no ISO/IEC 7816-3&4 UART interface; plastic very thin fine-pitch ball grid array package; 64 balls; 4.5 mm x 4.5 mm x 0.80 mm                             | SOT1307-2 |

| PN7360AUHN  | HVQFN64 | 80 kB memory; no contact interface; no ISO/IEC 7816-3&4 UART interface; plastic thermal enhanced very thin quad flat package; no leads; 64 terminals; body 9 × 9 × 0.85 mm                     | SOT804-4  |

| PN7360AUEV  | VFBGA64 | 80 kB memory; no contact interface; no ISO/IEC 7816-3&4 UART interface; plastic very thin fine-pitch ball grid array package; 64 balls; 4.5 mm x 4.5 mm x 0.80 mm                              | SOT1307-2 |

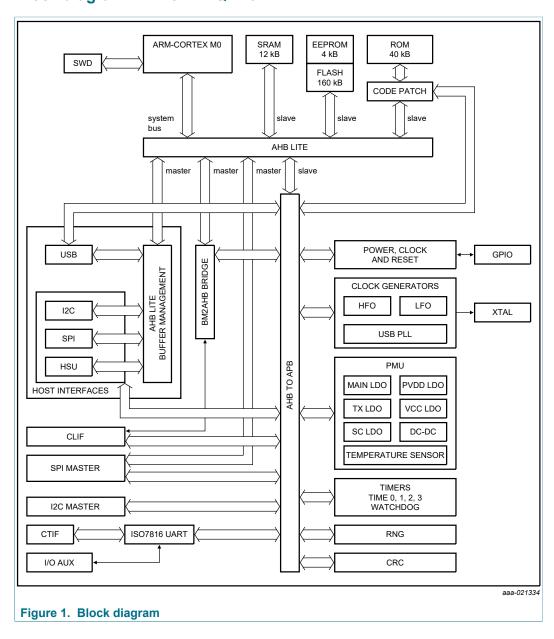

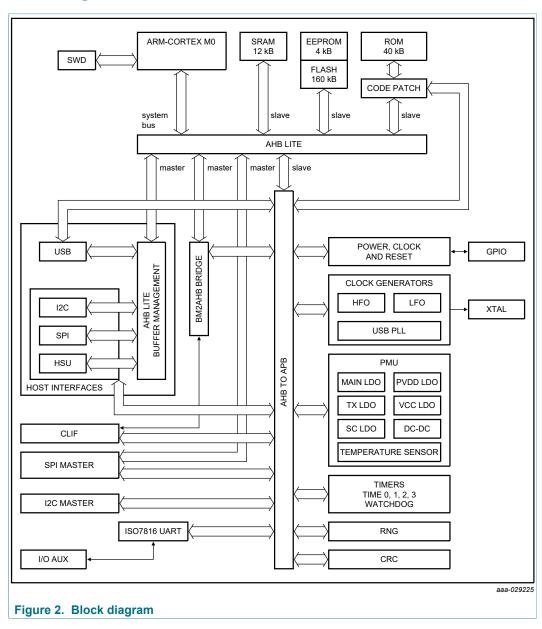

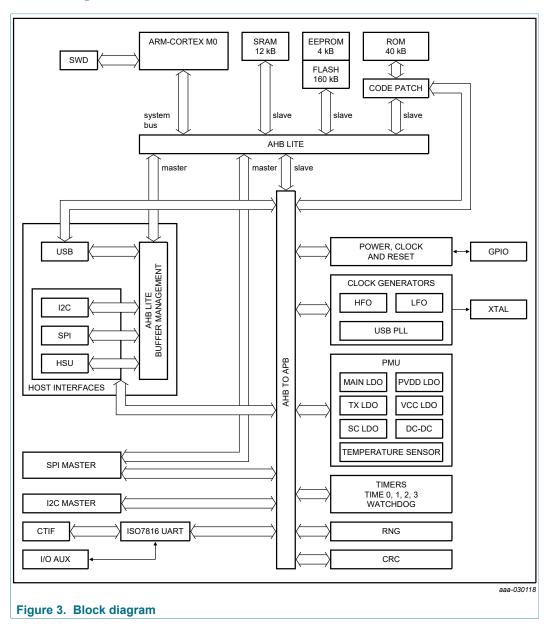

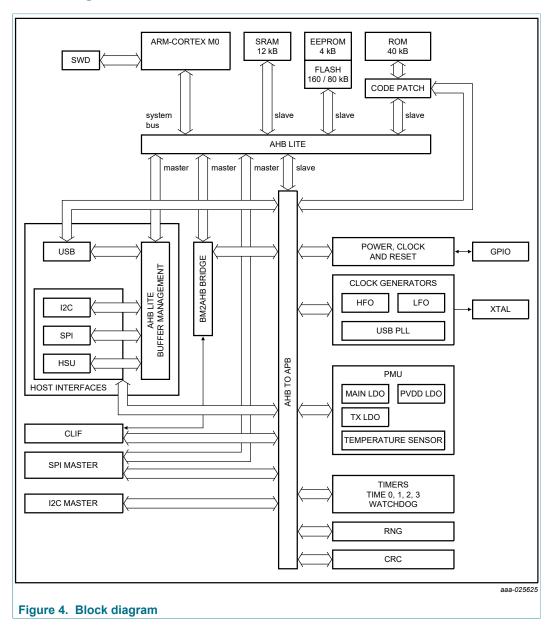

# 6 Block diagram

## 6.1 Block diagram PN7462 HVQFN64

# 6.2 Block diagram PN7462 VFBGA64

# 6.3 Block diagram PN7412 HVQFN64

# 6.4 Block diagram PN736X

# 7 Pinning information

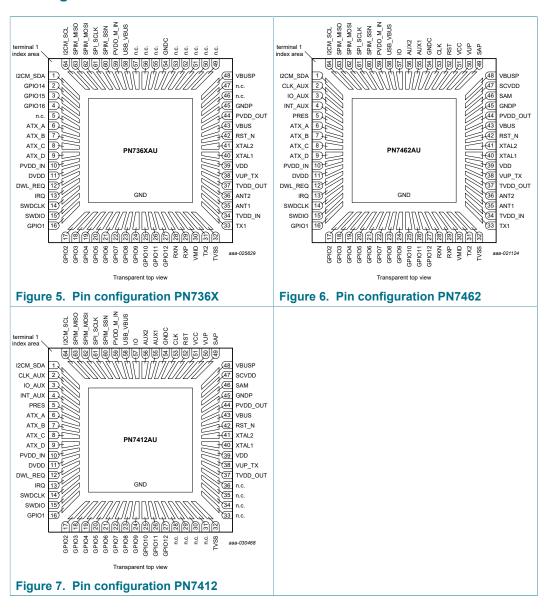

#### 7.1 Pinning HVQFN64

Important note: the inner leads below the package are internally connected to the PIN. Special care needs to be taken during the design so that no conductive part is present under these PINs, which could cause short cuts.

# 7.2 Pin description HVQFN64

Table 4. Pin description

| Pin | Symbol PN736X | Description PN736X                                                                                 | Symbol<br>PN7462 | Description PN7462                                                                                 | Symbol PN7412 | Description PN7412                                                                                 |

|-----|---------------|----------------------------------------------------------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------|---------------|----------------------------------------------------------------------------------------------------|

| 1   | I2CM_<br>SDA  | I <sup>2</sup> C-bus serial data I/O<br>master/GPIO13                                              | I2CM_<br>SDA     | I <sup>2</sup> C-bus serial data I/O master/GPIO13                                                 | I2CM_<br>SDA  | I <sup>2</sup> C-bus serial data I/O<br>master/GPIO13                                              |

| 2   | CLK_<br>AUX   | GPIO14                                                                                             | CLK_<br>AUX      | auxiliary card contact clock/<br>GPIO14                                                            | CLK_<br>AUX   | auxiliary card contact clock/<br>GPIO14                                                            |

| 3   | IO_AUX        | GPIO15                                                                                             | IO_AUX           | auxiliary card contact I/O/<br>GPIO15                                                              | IO_AUX        | auxiliary card contact I/O/<br>GPIO15                                                              |

| 4   | INT_<br>AUX   | GPIO16                                                                                             | INT_<br>AUX      | auxiliary card contact interrupt/GPIO16                                                            | INT_<br>AUX   | auxiliary card contact interrupt/GPIO16                                                            |

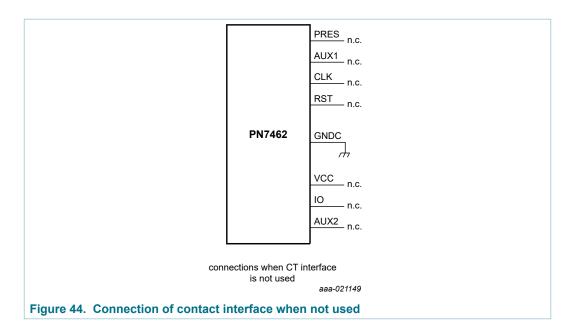

| 5   | n.c.          | not connected                                                                                      | PRES             | card presence                                                                                      | PRES          | card presence                                                                                      |

| 6   | ATX_A         | SPI slave select input<br>(NSS_S)/I <sup>2</sup> C-bus serial<br>clock input (SCL_S)/<br>HSUART RX | ATX_A            | SPI slave select input<br>(NSS_S)/I <sup>2</sup> C-bus serial<br>clock input (SCL_S)/<br>HSUART RX | ATX_A         | SPI slave select input<br>(NSS_S)/I <sup>2</sup> C-bus serial<br>clock input (SCL_S)/<br>HSUART RX |

| 7   | ATX_B         | SPI slave data input<br>(MOSI_S)/I <sup>2</sup> C-bus serial<br>data I/O (SDA_S)/HSUART<br>TX      | ATX_B            | SPI slave data input<br>(MOSI_S)/I <sup>2</sup> C-bus serial<br>data I/O (SDA_S)/HSUART<br>TX      | ATX_B         | SPI slave data input<br>(MOSI_S)/I <sup>2</sup> C-bus serial<br>data I/O (SDA_S)/HSUART<br>TX      |

| 8   | ATX_C         | USB D+/SPI slave data<br>output (MISO_S)/I <sup>2</sup> C-bus<br>address bit0 input/HSUART<br>RTS  | ATX_C            | USB D+/SPI slave data<br>output (MISO_S)/I <sup>2</sup> C-bus<br>address bit0 input/HSUART<br>RTS  | ATX_C         | USB D+/SPI slave data<br>output (MISO_S)/I <sup>2</sup> C-bus<br>address bit0 input/HSUART<br>RTS  |

| 9   | ATX_D         | USB D-/SPI clock input<br>(SCK_S)/I <sup>2</sup> C-bus address<br>bit1 input/HSUART CTS            | ATX_D            | USB D-/SPI clock input<br>(SCK_S)/I <sup>2</sup> C-bus address<br>bit1 input/HSUART CTS            | ATX_D         | USB D-/SPI clock input<br>(SCK_S)/I <sup>2</sup> C-bus address<br>bit1 input/HSUART CTS            |

| 10  | PVDD_<br>IN   | pad supply voltage input                                                                           | PVDD_<br>IN      | pad supply voltage input                                                                           | PVDD_<br>IN   | pad supply voltage input                                                                           |

| 11  | DVDD          | digital core logic supply voltage input                                                            | DVDD             | digital core logic supply voltage input                                                            | DVDD          | digital core logic supply voltage input                                                            |

| 12  | DWL_<br>REQ   | entering in download mode                                                                          | DWL_<br>REQ      | entering in download mode                                                                          | DWL_<br>REQ   | entering in download mode                                                                          |

| 13  | IRQ           | interrupt request output                                                                           | IRQ              | interrupt request output                                                                           | IRQ           | interrupt request output                                                                           |

| 14  | SWDC<br>LK    | SW serial debug line clock                                                                         | SWDC<br>LK       | SW serial debug line clock                                                                         | SWDC<br>LK    | SW serial debug line clock                                                                         |

| 15  | SWDIO         | SW serial debug line input/<br>output                                                              | SWDIO            | SW serial debug line input/<br>output                                                              | SWDIO         | SW serial debug line input/<br>output                                                              |

| 16  | GPIO1         | general-purpose I/O/SPI<br>master select2 output                                                   | GPIO1            | general-purpose I/O/SPI<br>master select2 output                                                   | GPIO1         | general-purpose I/O/SPI<br>master select2 output                                                   |

| 17  | GPIO2         | general-purpose I/O                                                                                | GPIO2            | general-purpose I/O                                                                                | GPIO2         | general-purpose I/O                                                                                |

| 18  | GPIO3         | general-purpose I/O                                                                                | GPIO3            | general-purpose I/O                                                                                | GPIO3         | general-purpose I/O                                                                                |

| 19  | GPIO4         | general-purpose I/O                                                                                | GPIO4            | general-purpose I/O                                                                                | GPIO4         | general-purpose I/O                                                                                |

| 20  | GPIO5         | general-purpose I/O                                                                                | GPIO5            | general-purpose I/O                                                                                | GPIO5         | general-purpose I/O                                                                                |

| 21  | GPIO6         | general-purpose I/O                                                                                | GPIO6            | general-purpose I/O                                                                                | GPIO6         | general-purpose I/O                                                                                |

PN7462\_FAM

All information provided in this document is subject to legal disclaimers.

# PN7462 family

# NFC Cortex-M0 microcontroller

| Pin | Symbol<br>PN736X | Description PN736X                                                                    | Symbol<br>PN7462 | Description PN7462                                                                             | Symbol<br>PN7412 | Description PN7412                           |

|-----|------------------|---------------------------------------------------------------------------------------|------------------|------------------------------------------------------------------------------------------------|------------------|----------------------------------------------|

| 22  | GPIO7            | general-purpose I/O                                                                   | GPIO7            | general-purpose I/O                                                                            | GPIO7            | general-purpose I/O                          |

| 23  | GPIO8            | general-purpose I/O                                                                   | GPIO8            | general-purpose I/O                                                                            | GPIO8            | general-purpose I/O                          |

| 24  | GPIO9            | general-purpose I/O                                                                   | GPIO9            | general-purpose I/O                                                                            | GPIO9            | general-purpose I/O                          |

| 25  | GPIO10           | general-purpose I/O                                                                   | GPIO10           | general-purpose I/O                                                                            | GPIO10           | general-purpose I/O                          |

| 26  | GPIO11           | general-purpose I/O                                                                   | GPIO11           | general-purpose I/O                                                                            | GPIO11           | general-purpose I/O                          |

| 27  | GPIO12           | general-purpose I/O                                                                   | GPIO12           | general-purpose I/O                                                                            | GPIO12           | general-purpose I/O                          |

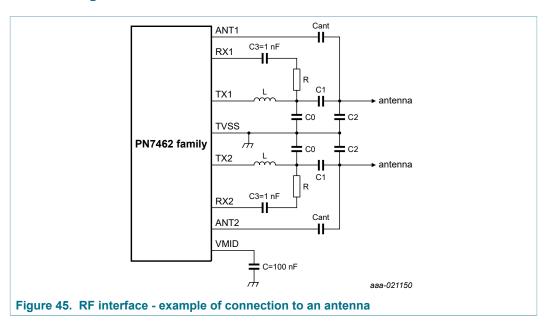

| 28  | RXN              | receiver input                                                                        | RXN              | receiver input                                                                                 | n.c.             | See UM10858 for connection details           |

| 29  | RXP              | receiver input                                                                        | RXP              | receiver input                                                                                 | n.c.             | See UM10858 for connection details           |

| 30  | VMID             | receiver reference voltage input                                                      | VMID             | receiver reference voltage input                                                               | n.c.             | See UM10858 for connection details           |

| 31  | TX2              | antenna driver output                                                                 | TX2              | antenna driver output                                                                          | n.c.             | keep unconnected                             |

| 32  | TVSS             | ground for antenna power supply                                                       | TVSS             | ground for antenna power supply                                                                | TVSS             | ground for antenna power supply              |

| 33  | TX1              | antenna driver output                                                                 | TX1              | antenna driver output                                                                          | n.c.             | keep unconnected                             |

| 34  | TVDD_<br>IN      | antenna driver supply voltage input                                                   | TVDD_<br>IN      | antenna driver supply voltage input                                                            | n.c.             | Connect to GND                               |

| 35  | ANT1             | antenna connection for load modulation in card emulation and P2P passive target modes | ANT1             | antenna connection for<br>load modulation in card<br>emulation and P2P passive<br>target modes | n.c.             | See UM10858 for connection details           |

| 36  | ANT2             | antenna connection for load modulation in card emulation and P2P passive target modes | ANT2             | antenna connection for<br>load modulation in card<br>emulation and P2P passive<br>target modes | n.c.             | See UM10858 for connection details           |

| 37  | TVDD_<br>OUT     | antenna driver supply, output of TX_LDO                                               | TVDD_<br>OUT     | antenna driver supply, output of TX_LDO                                                        | TVDD_<br>OUT     | antenna driver supply, output of TX_LDO      |

| 38  | VUP_<br>TX       | supply of the contactless TX_LDO                                                      | VUP_<br>TX       | supply of the contactless TX_LDO                                                               | VUP_<br>TX       | supply of the contactless TX_LDO             |

| 39  | VDD              | 1.8 V regulator output for digital blocks                                             | VDD              | 1.8 V regulator output for digital blocks                                                      | VDD              | 1.8 V regulator output for digital blocks    |

| 40  | XTAL1            | 27.12 MHz clock input for crystal                                                     | XTAL1            | 27.12 MHz clock input for crystal                                                              | XTAL1            | 27.12 MHz clock input for crystal            |

| 41  | XTAL2            | 27.12 MHz clock input for crystal                                                     | XTAL2            | 27.12 MHz clock input for crystal                                                              | XTAL2            | 27.12 MHz clock input for crystal            |

| 42  | RST_N            | reset pin                                                                             | RST_N            | reset pin                                                                                      | RST_N            | reset pin                                    |

| 43  | VBUS             | main supply voltage input of microcontroller                                          | VBUS             | main supply voltage input of microcontroller                                                   | VBUS             | main supply voltage input of microcontroller |

| 44  | PVDD_<br>OUT     | output of PVDD_LDO for pad voltage supply                                             | PVDD_<br>OUT     | output of PVDD_LDO for pad voltage supply                                                      | PVDD_<br>OUT     | output of PVDD_LDO for pad voltage supply    |

| 45  | GNDP             | Ground                                                                                | GNDP             | Ground                                                                                         | GNDP             | Ground                                       |

| Pin        | Symbol<br>PN736X | Description PN736X                                        | Symbol<br>PN7462 | Description PN7462                                          | Symbol<br>PN7412 | Description PN7412                                          |

|------------|------------------|-----------------------------------------------------------|------------------|-------------------------------------------------------------|------------------|-------------------------------------------------------------|

| 46         | n.c.             | not connected                                             | SAM              | DC-to-DC converter connection                               | SAM              | DC-to-DC converter connection                               |

| 47         | n.c.             | not connected                                             | SCVDD            | input LDO for DC-to-DC converter                            | SCVDD            | input LDO for DC-to-DC converter                            |

| 48         | VBUSP            | Connected to VBUS                                         | VBUSP            | main supply for the contact interface                       | VBUSP            | main supply for the contact interface                       |

| 49         | n.c.             | not connected                                             | SAP              | DC-to-DC converter connection                               | SAP              | DC-to-DC converter connection                               |

| 50         | n.c.             | not connected                                             | VUP              | reserved; connected to GND through a decoupling capacitance | VUP              | reserved; connected to GND through a decoupling capacitance |

| 51         | n.c.             | not connected                                             | VCC              | card supply output of contact interface                     | VCC              | card supply output of contact interface                     |

| 52         | n.c.             | not connected                                             | RST              | reset pin of contact interface                              | RST              | reset pin of contact interface                              |

| 53         | n.c.             | not connected                                             | CLK              | clock pin of contact interface                              | CLK              | clock pin of contact interface                              |

| 54         | GNDC             | connected to the ground                                   | GNDC             | connected to the ground                                     | GNDC             | connected to the ground                                     |

| 55         | n.c.             | not connected                                             | AUX1             | C4 card I/O pin of contact interface                        | AUX1             | C4 card I/O pin of contact interface                        |

| 56         | n.c.             | not connected                                             | AUX2             | C8 card I/O pin of contact interface                        | AUX2             | C8 card I/O pin of contact interface                        |

| 57         | n.c.             | not connected                                             | Ю                | card I/O                                                    | Ю                | card I/O                                                    |

| 58         | USB_<br>VBUS     | used for USB VBUS detection                               | USB_<br>VBUS     | used for USB VBUS detection                                 | USB_<br>VBUS     | used for USB VBUS detection                                 |

| 59         | PVDD_<br>M_IN    | pad supply voltage input for master interfaces            | PVDD_<br>M_IN    | pad supply voltage input for master interfaces              | PVDD_<br>M_IN    | pad supply voltage input for master interfaces              |

| 60         | SPIM_<br>SSN     | SPI master select 1 output/<br>GPIO17                     | SPIM_<br>SSN     | SPI master select 1 output/<br>GPIO17                       | SPIM_<br>SSN     | SPI master select 1 output/<br>GPIO17                       |

| 61         | SPI_<br>SCLK     | SPI master clock output/<br>GPIO18                        | SPI_<br>SCLK     | SPI master clock output/<br>GPIO18                          | SPI_<br>SCLK     | SPI master clock output/<br>GPIO18                          |

| 62         | SPIM_<br>MOSI    | SPI master data output/<br>GPIO19                         | SPIM_<br>MOSI    | SPI master data output/<br>GPIO19                           | SPIM_<br>MOSI    | SPI master data output/<br>GPIO19                           |

| 63         | SPIM_<br>MISO    | SPI master data input/<br>GPIO20                          | SPIM_<br>MISO    | SPI master data input/<br>GPIO20                            | SPIM_<br>MISO    | SPI master data input/<br>GPIO20                            |

| 64         | I2CM_<br>SCL     | I <sup>2</sup> C-bus serial clock output<br>master/GPIO21 | I2CM_<br>SCL     | I <sup>2</sup> C-bus serial clock output<br>master/GPIO21   | I2CM_<br>SCL     | I <sup>2</sup> C-bus serial clock output<br>master/GPIO21   |

| Die<br>pad | GND              | Ground                                                    | GND              | Ground                                                      | GND              | Ground                                                      |

# 7.3 Pinning VFBGA64

# 7.4 Pin description VFBGA64

Table 5. Pin description

| Pin | Symbol<br>PN736X | Description PN736X                                                                       | Symbol<br>PN7462 | Description PN7462                                                                       |

|-----|------------------|------------------------------------------------------------------------------------------|------------------|------------------------------------------------------------------------------------------|

| A1  | I2CM_SDA         | I <sup>2</sup> C-bus serial data I/O master/GPIO13                                       | I2CM_SDA         | I <sup>2</sup> C-bus serial data I/O master/GPIO13                                       |

| A2  | SPIM_MISO        | SPI master data input/GPIO20                                                             | SPIM_MISO        | SPI master data input/GPIO20                                                             |

| A3  | PVDD_M_IN        | pad supply voltage input for master interfaces                                           | PVDD_M_IN        | pad supply voltage input for master interfaces                                           |

| A4  | VBUSP            | Connected to VBUS                                                                        | VBUSP            | Connected to VBUS                                                                        |

| A5  | VBUS             | main supply voltage input of microcontroller                                             | VBUS             | main supply voltage input of microcontroller                                             |

| A6  | PVSS             | Pad ground                                                                               | PVSS             | Pad ground                                                                               |

| A7  | PVDD_OUT         | output of PVDD_LDO for pad voltage supply                                                | PVDD_OUT         | output of PVDD_LDO for pad voltage supply                                                |

| A8  | XTAL2            | 27.12 MHz clock input for crystal                                                        | XTAL2            | 27.12 MHz clock input for crystal                                                        |

| B1  | INT_AUX          | GPIO16                                                                                   | INT_AUX          | auxiliary card contact interrupt/GPIO16                                                  |

| B2  | ATX_A            | SPI slave select input (NSS_S)/I <sup>2</sup> C-bus serial clock input (SCL_S)/HSUART RX | ATX_A            | SPI slave select input (NSS_S)/I <sup>2</sup> C-bus serial clock input (SCL_S)/HSUART RX |

| В3  | SPIM_MOSI        | SPI master data output/GPIO19                                                            | SPIM_MOSI        | SPI master data output/GPIO19                                                            |

| B4  | SPIM_SSN         | SPI master select 1 output/GPIO17                                                        | SPIM_SSN         | SPI master select 1 output/GPIO17                                                        |

| B5  | USB_VBUS         | used for USB VBUS detection                                                              | USB_VBUS         | used for USB VBUS detection                                                              |

| В6  | PVSS             | Pad ground                                                                               | PVSS             | Pad ground                                                                               |

| В7  | PVSS             | Pad ground                                                                               | PVSS             | Pad ground                                                                               |

| В8  | XTAL1            | 27.12 MHz clock input for crystal                                                        | XTAL1            | 27.12 MHz clock input for crystal                                                        |

| C1  | CLK_AUX          | GPIO14                                                                                   | CLK_AUX          | auxiliary card contact clock/GPIO14                                                      |

| C2  | ATX_B            | SPI slave data input (MOSI_S)/I <sup>2</sup> C-bus serial data I/O (SDA_S)/HSUART TX     | ATX_B            | SPI slave data input (MOSI_S)/I <sup>2</sup> C-bus serial data I/O (SDA_S)/HSUART TX     |

| Pin | Symbol<br>PN736X | Description PN736X                                                                              | Symbol<br>PN7462 | Description PN7462                                                                              |

|-----|------------------|-------------------------------------------------------------------------------------------------|------------------|-------------------------------------------------------------------------------------------------|

| C3  | I2CM_SCL         | I <sup>2</sup> C-bus serial clock output master/<br>GPIO21                                      | I2CM_SCL         | I <sup>2</sup> C-bus serial clock output master/<br>GPIO21                                      |

| C4  | SPI_SCLK         | SPI master clock output/GPIO18                                                                  | SPI_SCLK         | SPI master clock output/GPIO18                                                                  |

| C5  | DVSS             | Digital ground                                                                                  | DVSS             | Digital ground                                                                                  |

| C6  | PVSS             | Pad ground                                                                                      | PVSS             | Pad ground                                                                                      |

| C7  | RST_N            | reset pin                                                                                       | RST_N            | reset pin                                                                                       |

| C8  | VDD              | 1.8 V regulator output for digital blocks                                                       | VDD              | 1.8 V regulator output for digital blocks                                                       |

| D1  | PVDD_IN          | pad supply voltage input                                                                        | PVDD_IN          | pad supply voltage input                                                                        |

| D2  | ATX_C            | USB D+/SPI slave data output<br>(MISO_S)/I <sup>2</sup> C-bus address bit0 input/<br>HSUART RTS | ATX_C            | USB D+/SPI slave data output<br>(MISO_S)/I <sup>2</sup> C-bus address bit0 input/<br>HSUART RTS |

| D3  | IRQ              | interrupt request output                                                                        | IRQ              | interrupt request output                                                                        |

| D4  | IO_AUX           | GPIO15                                                                                          | IO_AUX           | auxiliary card contact I/O/GPIO15                                                               |

| D5  | DVSS             | Digital ground                                                                                  | DVSS             | Digital ground                                                                                  |

| D6  | PVSS             | Pad ground                                                                                      | PVSS             | Pad ground                                                                                      |

| D7  | PVSS             | Pad ground                                                                                      | PVSS             | Pad ground                                                                                      |

| D8  | VUP_TX           | supply of the contactless TX_LDO                                                                | VUP_TX           | supply of the contactless TX_LDO                                                                |

| E1  | DVDD             | digital core logic supply voltage input                                                         | DVDD             | digital core logic supply voltage input                                                         |

| E2  | ATX_D            | USB D-/SPI clock input (SCK_S)/I <sup>2</sup> C-bus address bit1 input/HSUART CTS               | ATX_D            | USB D-/SPI clock input (SCK_S)/I <sup>2</sup> C-bus address bit1 input/HSUART CTS               |

| E3  | GPIO1            | general-purpose I/O/SPI master select2 output                                                   | GPIO1            | general-purpose I/O/SPI master select2 output                                                   |

| E4  | GPIO5            | general-purpose I/O                                                                             | GPIO5            | general-purpose I/O                                                                             |

| E5  | DVSS             | Digital ground                                                                                  | DVSS             | Digital ground                                                                                  |

| E6  | AVSS             | Analog ground                                                                                   | AVSS             | Analog ground                                                                                   |

| E7  | ANT2             | antenna connection for load modulation in card emulation and P2P passive target modes           | ANT2             | antenna connection for load modulation in card emulation and P2P passive target modes           |

| E8  | TVDD_OUT         | antenna driver supply, output of TX_LDO                                                         | TVDD_OUT         | antenna driver supply, output of TX_LDO                                                         |

| F1  | DWL_REQ          | entering in download mode                                                                       | DWL_REQ          | entering in download mode                                                                       |

| F2  | SWDIO            | SW serial debug line input/output                                                               | SWDIO            | SW serial debug line input/output                                                               |

| F3  | GPIO6            | general-purpose I/O                                                                             | GPIO6            | general-purpose I/O                                                                             |

| F4  | GPIO9            | general-purpose I/O                                                                             | GPIO9            | general-purpose I/O                                                                             |

| F5  | GPIO12           | general-purpose I/O                                                                             | GPIO12           | general-purpose I/O                                                                             |

| F6  | AVSS             | Analog ground                                                                                   | AVSS             | Analog ground                                                                                   |

| F7  | ANT1             | antenna connection for load modulation in card emulation and P2P passive target modes           | ANT1             | antenna connection for load modulation in card emulation and P2P passive target modes           |

| F8  | TVDD_IN          | antenna driver supply voltage input                                                             | TVDD_IN          | antenna driver supply voltage input                                                             |

# PN7462 family

# NFC Cortex-M0 microcontroller

| Pin | Symbol PN736X | Description PN736X               | Symbol<br>PN7462 | Description PN7462               |

|-----|---------------|----------------------------------|------------------|----------------------------------|

| G1  | SWDCLK        | SW serial debug line clock       | SWDCLK           | SW serial debug line clock       |

| G2  | GPIO4         | general-purpose I/O              | GPIO4            | general-purpose I/O              |

| G3  | GPIO7         | general-purpose I/O              | GPIO7            | general-purpose I/O              |

| G4  | GPIO8         | general-purpose I/O              | GPIO8            | general-purpose I/O              |

| G5  | GPIO10        | general-purpose I/O              | GPIO10           | general-purpose I/O              |

| G6  | GPIO11        | general-purpose I/O              | GPIO11           | general-purpose I/O              |

| G7  | AVSS          | Analog ground                    | AVSS             | Analog ground                    |

| G8  | TX1           | antenna driver output            | TX1              | antenna driver output            |

| H1  | GPIO3         | general-purpose I/O              | GPIO3            | general-purpose I/O              |

| H2  | GPIO2         | general-purpose I/O              | GPIO2            | general-purpose I/O              |

| НЗ  | VMID          | receiver reference voltage input | VMID             | receiver reference voltage input |

| H4  | RXN           | receiver input                   | RXN              | receiver input                   |

| H5  | RXP           | receiver input                   | RXP              | receiver input                   |

| H6  | TVSS          | Antenna driver ground            | TVSS             | Antenna driver ground            |

| H7  | TX2           | antenna driver output            | TX2              | antenna driver output            |

| H8  | TVSS          | Antenna driver ground            | TVSS             | Antenna driver ground            |

# 8 Functional description

#### 8.1 Arm Cortex-M0 microcontroller

The PN7462 family is an Arm Cortex-M0-based 32-bit microcontroller, optimized for low-cost designs, high energy efficiency, and simple instruction set.

The CPU operates on an internal clock, which can be configured to provide frequencies such as 20 MHz, 10 MHz, and 5 MHz.

The peripheral complement of the PN7462 family includes a 160 kB flash memory, a 12 kB SRAM, and a 4 kB EEPROM. It also includes one configurable host interface (Fast-mode Plus and high-speed I<sup>2</sup>C, SPI, HSUART, and USB), two master interfaces (Fast-mode Plus I<sup>2</sup>C, SPI), 4 timers, 12 general-purpose I/O pins, one ISO/IEC 7816 contact card interface (PN7462AUHN only), one ISO/IEC 7816-3&4 UART (PN7462AUHN and PN7462AUEV only) and one 13.56 MHz NFC interface.

#### 8.2 Memories

#### 8.2.1 On-chip flash programming memory

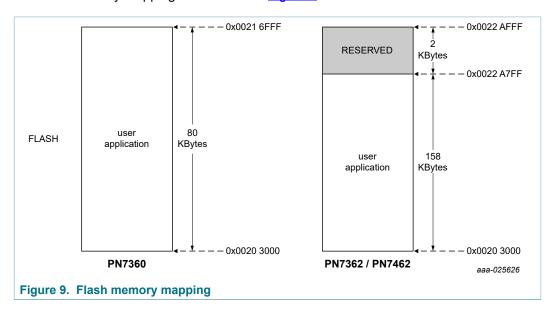

The PN7462 family contains 160 / 80 kB on-chip flash program memory depending on the version. The flash can be programmed using In-System Programming (ISP) or In-Application Programming (IAP) via the on-chip boot loader software.

The flash memory is divided into two instances of 80 kB each, with each sector consisting of individual pages of 64 bytes.

#### 8.2.1.1 Memory mapping

The flash memory mapping is described in Figure 9.

#### 8.2.2 **EEPROM**

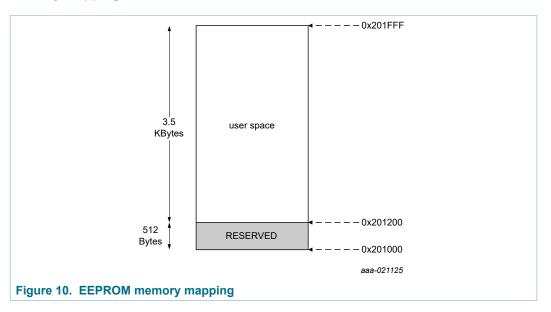

The PN7462 family embeds 4 kB of on-chip byte-erasable and byte-programmable EEPROM data memory.

The EEPROM can be programmed using In-System Programming (ISP).

#### 8.2.2.1 Memory mapping

#### 8.2.3 **SRAM**

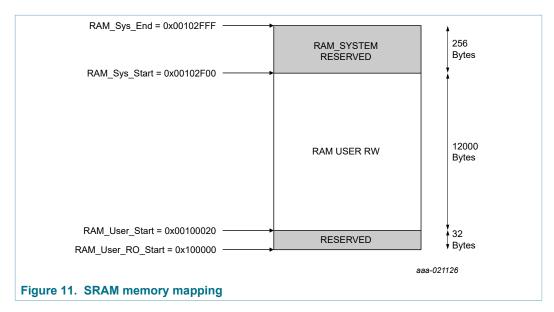

The PN7462 family contains a total of 12 kB on-chip static RAM memory.

#### 8.2.3.1 Memory mapping

The SRAM memory mapping is shown in Figure 11.

PN7462\_FAM

All information provided in this document is subject to legal disclaimers.

#### 8.2.4 ROM

The PN7462 family contains 40 kB of on-chip ROM memory. The on-chip ROM contains boot loader, USB mass storage primary download, and the following Application Programming Interfaces (APIs):

- In-Application Programming (IAP) support for flash

- Lifecycle management of debug interface, code write protection of flash memory and USB mass storage primary download

- USB descriptor configuration

- · Configuration of timeout and source of pad supply

#### 8.2.5 Memory map

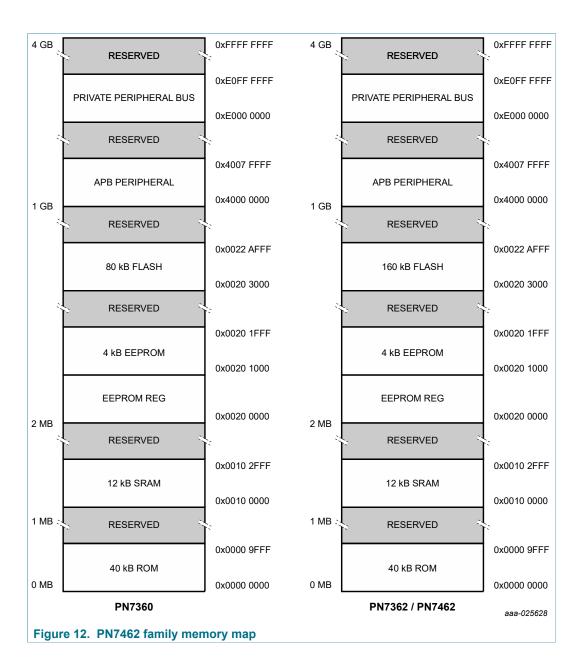

The PN7462 family incorporates several distinct memory regions. <u>Figure 12</u> shows the memory map, from the user program perspective, following reset.

The APB peripheral area is 512 kB in size, and is divided to allow up to 32 peripherals. Only peripherals from 0 to 15 are accessible. Each peripheral allocates 16 kB, which simplifies the address decoding for the peripherals. APB memory map is described in Figure 13 and Figure 14.

aaa-021127

aaa-028697

| APB ID   | APB IF name   | Connected IP                   | 0x4004 8000 |

|----------|---------------|--------------------------------|-------------|

| 16 to 31 | Rese          | 0x4004 0000                    |             |

| 15       | Rese          | erved                          | 0x4003 C000 |

| 14       | Rese          | erved                          | 0x4003 8000 |

| 13       | SPIMASTER_APB | SPI Master IF                  | 0x4003 4000 |

| 12       | I2CMASTER_APB | I2C Master IF                  | 0x4003 0000 |

| 11       | Rese          | erved                          | 0x4002 C000 |

| 10       | USB_APB       | HostIF (USB) IP                | 0x4002 8000 |

| 9        | PCR_APB       | PowerClockResetModule IP       | 0x4002 4000 |

| 8        | HOST_APB      | HostIF (I2C/SPI/HSU/BufMgt) IP | 0x4002 0000 |

| 7        | TIMERS_APB    | Timer IP                       | 0x4001 C000 |

| 6        | RNG_APB       | RNG IP                         | 0x4001 8000 |

| 5        | Rese          | erved                          | 0x4001 4000 |

| 4        | CLOCKGEN_APB  | Clock Gen module               | 0x4001 0000 |

| 3        | CRC_APB       | CRC IP                         | 0x4000 C000 |

| 2        | PMU_APB       | PMU modules                    | 0x4000 8000 |

| 1        | CL_APB        | Contactless IP                 | 0x4000 4000 |

| 0        | Rese          | erved                          | 0x4000 0000 |

Figure 13. APB memory map PN736X

| APB ID   | APB IF name   | Connected IP                   | 0x4004 8000 |

|----------|---------------|--------------------------------|-------------|

| 16 to 31 | Rese          | 0x4004 0000                    |             |

| 15       | Rese          | erved                          | 0x4003 C000 |

| 14       | Rese          | erved                          | 0x4003 8000 |

| 13       | SPIMASTER_APB | SPI Master IF                  | 0x4003 4000 |

| 12       | I2CMASTER_APB | I2C Master IF                  | 0x4003 0000 |

| 11       | Rese          | erved                          | 0x4002 C000 |

| 10       | USB_APB       | HostIF (USB) IP                | 0x4002 8000 |

| 9        | PCR_APB       | PowerClockResetModule IP       | 0x4002 4000 |

| 8        | HOST_APB      | HostIF (I2C/SPI/HSU/BufMgt) IP | 0x4002 0000 |

| 7        | TIMERS_APB    | Timer IP                       | 0x4001 C000 |

| 6        | RNG_APB       | RNG IP                         | 0x4001 8000 |

| 5        | CTUART_APB    | Contact UART IP                | 0x4001 4000 |

| 4        | CLOCKGEN_APB  | Clock Gen module               | 0x4001 0000 |

| 3        | CRC_APB       | CRC IP                         | 0x4000 C000 |

| 2        | PMU_APB       | PMU modules                    | 0x4000 8000 |

| 1        | CL_APB        | Contactless IP                 | 0x4000 4000 |

| 0        | Rese          | erved                          | 0x4000 0000 |

Figure 14. APB memory map PN7462

aaa-030119

| APB ID   | APB IF name   | Connected IP                   | 0x4004 8000 |

|----------|---------------|--------------------------------|-------------|

| 16 to 31 | Rese          | 0x4004 0000                    |             |

| 15       | Rese          | erved                          | 0x4003 C000 |

| 14       | Rese          | erved                          | 0x4003 8000 |

| 13       | SPIMASTER_APB | SPI Master IF                  | 0x4003 4000 |

| 12       | I2CMASTER_APB | I2C Master IF                  | 0x4003 0000 |

| 11       | Rese          | erved                          | 0x4002 C000 |

| 10       | USB_APB       | HostIF (USB) IP                | 0x4002 8000 |

| 9        | PCR_APB       | PowerClockResetModule IP       | 0x4002 4000 |

| 8        | HOST_APB      | HostIF (I2C/SPI/HSU/BufMgt) IP | 0x4002 0000 |

| 7        | TIMERS_APB    | Timer IP                       | 0x4001 C000 |

| 6        | RNG_APB       | RNG IP                         | 0x4001 8000 |

| 5        | CTUART_APB    | Contact UART IP                | 0x4001 4000 |

| 4        | CLOCKGEN_APB  | Clock Gen module               | 0x4001 0000 |

| 3        | CRC_APB       | CRC IP                         | 0x4000 C000 |

| 2        | PMU_APB       | PMU modules                    | 0x4000 8000 |

| 1        | Reserved      |                                | 0x4000 4000 |

| 0        | Rese          | 0x4000 0000                    |             |

Figure 15. APB memory map PN7412

# 8.3 Nested Vectored Interrupt Controller (NVIC)

Cortex-M0 includes a Nested Vectored Interrupt Controller (NVIC). The tight coupling to the CPU allows for low interrupt latency and efficient processing of late arriving interrupts.

#### 8.3.1 NVIC features

- System exceptions and peripheral interrupts control

- Support 32 vectored interrupts

- · Four interrupt priority levels with hardware priority level masking

- One Non-Maskable Interrupt (NMI) connected to the watchdog interrupt

- Software interrupt generation

#### 8.3.2 Interrupt sources

The following table lists the interrupt sources available in the PN7462 family microcontroller.

Table 6. Interrupt sources

| EIRQ# | Source        | Description                                                    |  |

|-------|---------------|----------------------------------------------------------------|--|

| 0     | timer 0/1/2/3 | general-purpose timer 0/1/2/3 interrupt                        |  |

| 1     | -             | reserved                                                       |  |

| 2     | CLIF          | NFC interface module interrupt                                 |  |

| 3     | EECTRL        | EEPROM controller                                              |  |

| 4     | -             | reserved                                                       |  |

| 5     | -             | reserved                                                       |  |

| 6     | host IF       | TX or RX buffer from I <sup>2</sup> C, SPI, HSU, or USB module |  |

| EIRQ#              | Source                  | Description                                                                                                                                                                            |  |  |

|--------------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 7                  | contact IF              | ISO7816 contact module interrupt                                                                                                                                                       |  |  |

| 8                  | -                       | reserved                                                                                                                                                                               |  |  |

| 9                  | PMU                     | power management unit (temperature sensor, over current, overload, and VBUS level)                                                                                                     |  |  |

| 10                 | SPI master              | TX or RX buffer from SPI master module                                                                                                                                                 |  |  |

| 11                 | I <sup>2</sup> C master | TX or RX buffer from I <sup>2</sup> C master module                                                                                                                                    |  |  |

| 12                 | PCR                     | high temperature from temperature sensor 0 and 1; interrupt to CPU from PCR to indicate wake-up from suspend mode; out of standby; out of suspend; event on GPIOs configured as inputs |  |  |

| 13                 | PCR                     | interrupt common GPIO1 to GPIO12                                                                                                                                                       |  |  |

| 14                 | PCR                     | interrupt (rise/fall/both-edge/level-high/level-low interrupt as programmed) GPIO1                                                                                                     |  |  |

| 15                 | PCR                     | interrupt (rise/fall/both-edge/level-high/level-low interrupt as programmed) GPIO2                                                                                                     |  |  |

| 16                 | PCR                     | interrupt (rise/fall/both-edge/level-high/level-low interrupt as programmed) GPIO3                                                                                                     |  |  |

| 17                 | PCR                     | interrupt (rise/fall/both-edge/level-high/level-low interrupt as programmed) GPIO4                                                                                                     |  |  |

| 18                 | PCR                     | interrupt (rise/fall/both-edge/level-high/level-low interrupt as programmed) GPIO5                                                                                                     |  |  |

| 19                 | PCR                     | interrupt (rise/fall/both-edge/level-high/level-low interrupt as programmed) GPIO6                                                                                                     |  |  |

| 20                 | PCR                     | interrupt (rise/fall/both-edge/level-high/level-low interrupt as programmed) GPIO7                                                                                                     |  |  |

| 21                 | PCR                     | interrupt (rise/fall/both-edge/level-high/level-low interrupt as programmed) GPIO8                                                                                                     |  |  |

| 22                 | PCR                     | interrupt (rise/fall/both-edge/level-high/level-low interrupt as programmed) GPIO9                                                                                                     |  |  |

| 23                 | PCR                     | interrupt (rise/fall/both-edge/level-high/level-low interrupt as programmed) GPIO10                                                                                                    |  |  |

| 24                 | PCR                     | interrupt (rise/fall/both-edge/level-high/level-low interrupt as programmed) GPIO11                                                                                                    |  |  |

| 25                 | PCR                     | interrupt (rise/fall/both-edge/level-high/level-low interrupt as programmed) GPIO12                                                                                                    |  |  |

| 26                 | -                       | reserved                                                                                                                                                                               |  |  |

| 27                 | -                       | reserved                                                                                                                                                                               |  |  |

| 28                 | -                       | reserved                                                                                                                                                                               |  |  |

| 29                 | -                       | reserved                                                                                                                                                                               |  |  |

| 30                 | -                       | reserved                                                                                                                                                                               |  |  |

| 31                 | -                       | reserved                                                                                                                                                                               |  |  |

| NMI <sup>[1]</sup> | WDT                     | watchdog interrupt is connected to the non-maskable interrupt pin                                                                                                                      |  |  |

[1] The NMI is not available on an external pin.

#### 8.4 GPIOs

The PN7462 family has up to 21 general-purpose I/O (GPIO) with configurable pull-up and pull-down resistors, up to 9 of those GPIOs are multiplexed with SPI master, I<sup>2</sup>C-bus master and AUX pins (if available).

Pins can be dynamically configured as inputs or outputs. GPIO read/write are made by the FW using dedicated registers that allow reading, setting, or clearing inputs. The value of the output register can be read back, as well as the current state of the input pins.

#### 8.4.1 GPIO features

- · Dynamic configuration as input or output

- 3.3 V and 1.8 V signaling

- Programmable weak pull-up and weak pull-down

- Independent interrupts for GPIO1 to GPIO12

- Interrupts: edge or level sensitive

- GPIO1 to GPIO12 can be programmed as wake-up sources

- Programmable spike filter (3 ns)

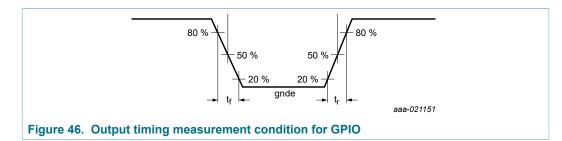

- Programmable slew rate (3 ns and 10 ns)

- · Hysteresis receiver with disable option

#### 8.4.2 **GPIO** configuration

The GPIO configuration is done through the PCR module (power, clock, and reset).

#### 8.4.3 **GPIO** interrupts

GPIO1 to GPIO12 can be programmed to generate an interrupt on a level, a rising or falling edge or both.

#### 8.5 CRC engine 16/32 bits

The PN7462 family has a configurable 16/32-bit parallel CRC coprocessor.

The 16-bit CRC is compliant to X.25 (CRC-CCITT, ISO/IEC 13239) standard with a generator polynomial of:

$$g(x) = x^{16} + x^{12} + x^5 + 1$$

The 32-bit CRC is compliant to the ethernet/AAL5 (IEEE 802.3) standard with a generator polynomial of:

$$a(x) = x^{32} + x^{26} + x^{23} + x^{22} + x^{16} + x^{12} + x^{11} + x^{10} + x^{8} + x^{7} + x^{5} + x^{4} + x^{2} + x + 1$$

CRC calculation is performed in parallel, meaning that one CRC calculation is performed in one clock cycle. The standard CRC 32 polynomial is compliant with FIPS140-2.

Note: No final XOR calculation is performed.

PN7462 FAM

All information provided in this document is subject to legal disclaimers.

Following are the CRC engine features:

- · Configurable CRC preset value

- · Selectable LSB or MSB first

- CRC 32 calculation based on 32-bit, 16-bit, and 8-bit words

- CRC16 calculation based on 32-bit, 16-bit, and 8-bit words

- · Supports bit order reverse

#### 8.6 Random Number Generator (RNG)

The PN7462 family integrates a random number generator. It consists of an analog True Random Number Generator (TRNG), and a digital Pseudo Random Number Generator (PRNG). The TRNG is used for loading a new seed in the PRNG.

The random number generator features:

- · 8-bit random number

- Compliant with FIPS 140-2

- · Compliant with BSI AIS20 and SP800-22

#### 8.7 Master interfaces

#### 8.7.1 I<sup>2</sup>C master interface

#### 8.7.1.1 I<sup>2</sup>C features

The I<sup>2</sup>C master interface supports the following features:

- Standard I<sup>2</sup>C-compliant bus interface with open-drain pins

- Standard-mode, fast mode, and fast mode plus (up to 1 Mbit/s).

- Support I<sup>2</sup>C master mode only.

- · Programmable clocks allowing versatile rate control.

- Clock stretching

- 7-bit and 10-bit I<sup>2</sup>C slave addressing

- LDM/STM instruction support

- Maximum data frame size up to 1024 bytes

#### 8.7.2 SPI interface

The PN7462 family contains one SPI master controller and one SPI slave controller.

The SPI master controller transmits the data from the system RAM to the SPI external slaves. Similarly, it receives data from the SPI external slaves and stores them into the system RAM. It can compute a CRC for received frames and automatically compute and append CRC for outgoing frames (optional feature).

#### 8.7.2.1 SPI features

The SPI master interface provides the following features:

- SPI master interface: synchronous, half-duplex

- Supports Motorola SPI frame formats only (SPI block guide V04.0114 (Freescale) specification)

- · Maximum SPI data rate of 6.78 Mbit/s

PN7462\_FAM

All information provided in this document is subject to legal disclaimers.

- Multiple data rates such as 1, 1.51, 2.09, 2.47, 3.01, 4.52, 5.42 and 6.78 Mbit/s

- · Up to two slaves select with selectable polarity

- · Programmable clock polarity and phase

- · Supports 8-bit transfers only

- Maximum frame size: 511 data bytes payload + 1 CRC byte

- · Optional 1 byte CRC calculation on all data of TX and RX buffer

- · AHB master interface for data transfer

#### 8.8 Host interfaces

The PN7462 family embeds four different interfaces for host connection: USB, HSUART,  $I^2C$ , and SPI.

The four interfaces share the buffer manager and the pins; see Table 7.

Table 7. Pin description for host interface

| Name  | SPI    | I <sup>2</sup> C      | USB | HSU       |

|-------|--------|-----------------------|-----|-----------|

| ATX_A | NSS_S  | SCL_S                 | -   | HSU_RX    |

| ATX_B | MOSI_S | SDA_S                 | -   | HSU_TX    |

| ATX_C | MISO_S | I <sup>2</sup> C_ADR0 | DP  | HSU_RTS_N |

| ATX_D | SCK_S  | I <sup>2</sup> C_ADR1 | DM  | HSU_CTS_N |

The interface selection is done by configuring the Power Clock Reset (PCR) registers.

Note: The host interface pins should not be kept floating.

#### 8.8.1 High-speed UART

The PN7462 family has a high-speed UART which can operate in slave mode only.

- Following are the HSUART features:

- Standard bit-rates are 9600, 19200, 38400, 57600, 115200, and up to 1.288 Mbit/s

- Supports full duplex communication

- Supports only one operational mode: start bit, 8 data bits (LSB), and stop bits

- The number of "stop bits" programmable for RX and TX is 1 stop bit or 2 stop bits

- Configurable length of EOF (1-bit to 122-bits)

Table 8. HSUART baudrates

| Bit rate (kBd) |

|----------------|

| 0.6            |

| 9.2            |

| 8.4            |

| 57.6           |

| 15.2           |

| 30.4           |

| 60.8           |

| 21.6           |

| 288 K          |

PN7462\_FAM

All information provided in this document is subject to legal disclaimers.

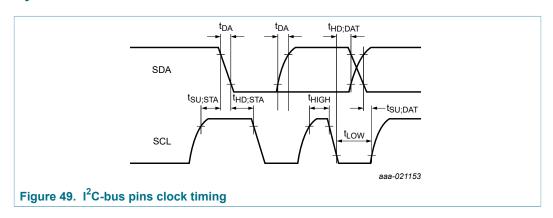

#### 8.8.2 I<sup>2</sup>C host interface controller

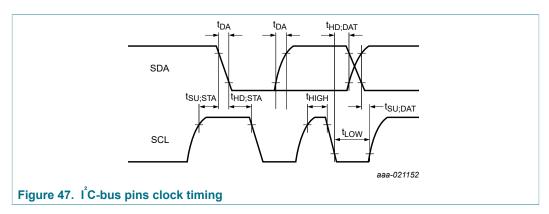

The I<sup>2</sup>C-bus is bidirectional and uses only two wires: a Serial Clock Line (SCL) and a Serial Data Line (SDA). I<sup>2</sup>C standard mode (100 kbit/s), fast mode (400 kbit/s and up to 1 Mbit/s), and high-speed mode (3.4 Mbit/s) are supported.

#### 8.8.2.1 I<sup>2</sup>C host interface features

The PN7462 family I<sup>2</sup>C slave interface supports the following features:

- Support slave I<sup>2</sup>C bus

- Standard mode, fast mode (extended to 1 Mbit/s support), and high-speed modes

- Supports 7-bit addressing mode only

- Selection of the I<sup>2</sup>C address done by two pins

- It supports multiple addresses

- The upper bits of the I<sup>2</sup>C slave address are hard-coded. The value corresponds to the NXP identifier for I<sup>2</sup>C blocks. The value is 0101 0XXb.

- · General call (software reset only)

- Software reset (in standard mode and fast mode only)

Table 9. I<sup>2</sup>C interface addressing

| I <sup>2</sup> C_ADR1 | I <sup>2</sup> C_ADR0 | I <sup>2</sup> C address (R/W = 0, write) | $I^2C$ address (R/W = 0, read) |

|-----------------------|-----------------------|-------------------------------------------|--------------------------------|

| 0                     | 0                     | 0 × 28                                    | 0 × 28                         |

| 0                     | 1                     | 0 × 29                                    | 0 × 29                         |

| 1                     | 0                     | 0 × 2A                                    | 0 × 2A                         |

| 1                     | 1                     | 0 × 2B                                    | 0 × 2B                         |

#### 8.8.3 SPI host/Slave interface

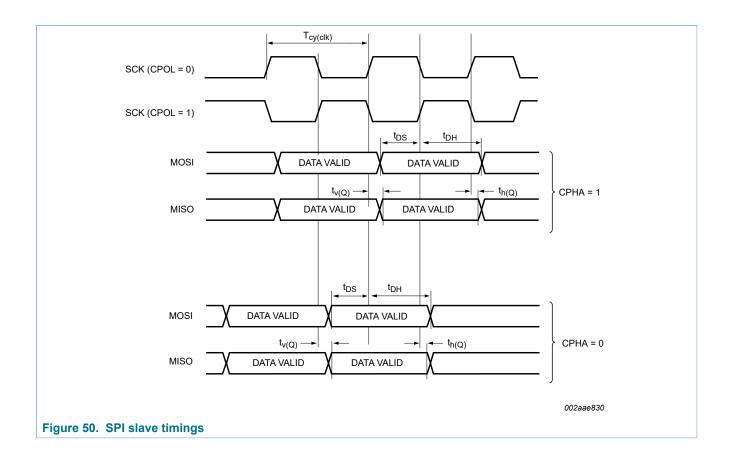

The PN7462 family host interface can be used as SPI slave interface.

The SPI slave controller operates on a four wire SSI: Master In Slave Out (MISO), Master Out Slave In (MOSI), Serial Clock (SCK), and Not Slave Select (NSS). The SPI slave select polarity is fixed to positive polarity.

#### 8.8.3.1 SPI host interface features

The SPI host/slave interface has the following features:

- SPI speeds up to 7 Mbit/s

- Slave operation only

- 8-bit data format only

- · Programmable clock polarity and phase

- SPI slave select polarity selection fixed to positive polarity

- Half-duplex in HDLL mode

- · Full-duplex in native mode

If no data is available, the MISO line is kept idle by making all the bits high (0xFF). Toggling the NSS line indicates a new frame.

**Note**: Programmable echo-back operation is not supported.

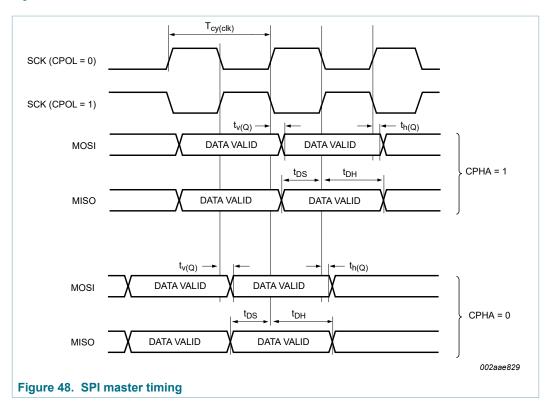

#### Table 10. SPI configuration

#### connection

CPHA switch: Clock phase: Defines the sampling edge of MOSI data

- CPHA = 1: Data are sampled on MOSI on the even clock edges of SCK, after NSS goes low

- CPHA = 0: Data are sampled on MOSI on the odd clock edges of SCK, after NSS goes low

CPOL switch: Clock polarity

- IFSEL1 = 0: The clock is idle low, and the first valid edge of SCK is a rising one

- IFSEL1 = 0: The clock is idle high, and the first valid edge of SCK is a falling one

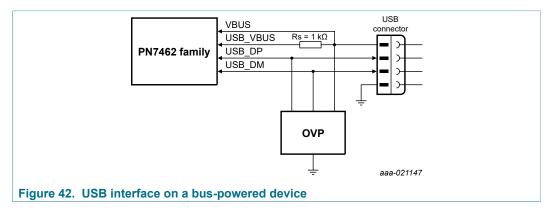

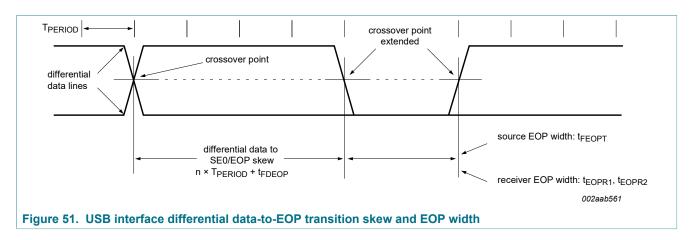

#### 8.8.4 USB interface

The Universal Serial Bus (USB) is a 4-wire bus that supports communication between a host and up to 127 peripherals. The host controller allocates the USB bandwidth to attached devices through a token-based protocol. The bus supports hot-plugging and dynamic configuration of devices. The host controller initiates all transactions. The PN7462 family USB interface consists of a full-speed device controller with on-chip PHY (physical layer) for device functions.

#### 8.8.4.1 Full speed USB device controller

The PN7462 family embeds a USB device peripheral, compliant with USB 2.0 specification, full speed. It is interoperable with USB 3.0 host devices.

The device controller enables 12 Mbit/s data exchange with a USB host controller. It consists of a register interface, serial interface engine, and endpoint buffer memory. The serial interface engine decodes the USB data stream and writes data to the appropriate endpoint buffer.

The status of a completed USB transfer or error condition is indicated via status registers. If enabled, an interrupt is generated.

Following are the USB interface features:

- Fully compliant with USB 2.0 specification (full speed)

- · Dedicated USB PLL available

- Supports 14 physical (7 logical) endpoints including one control endpoint

- Each non-control endpoint supports bulk, interrupt, or isochronous endpoint types

- · Single or double buffering allowed

- · Support wake-up from suspend mode on USB activity and remote wake-up

- · Soft-connect supported

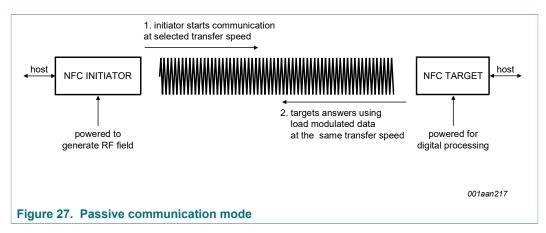

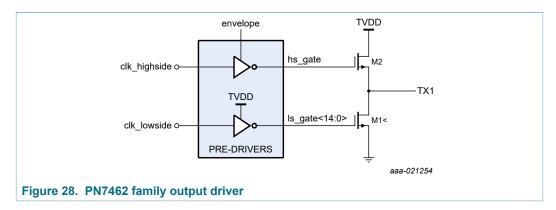

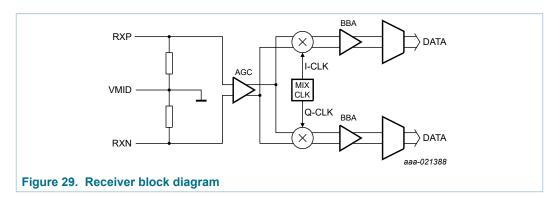

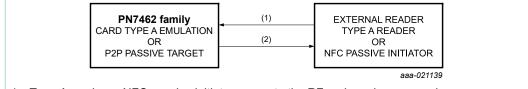

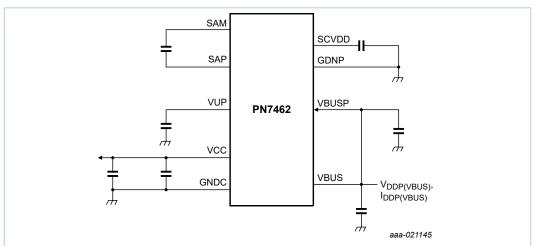

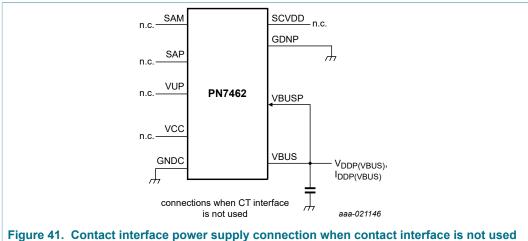

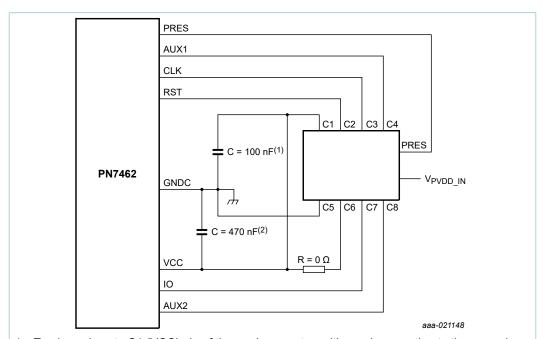

#### 8.9 Contact interface