### **Datasheet**

DS000522

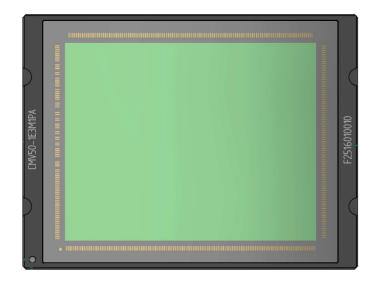

# **CMV50000**

**47.5MP CMOS Machine Vision Image Sensor**

v2-00 • 2019-Feb-01

## **Content Guide**

| 1                                             | General Description3                |

|-----------------------------------------------|-------------------------------------|

| 1.1<br>1.2<br>1.3                             | Key Benefits & Features             |

| 2                                             | Ordering Information5               |

| 3                                             | Pin Assignment6                     |

| 3.1<br>3.2                                    | Pin Diagram6 Pin Description6       |

| 4                                             | Absolute Maximum Ratings 11         |

| 5                                             | Electrical Characteristics12        |

| 6                                             | Typical Operating Characteristics14 |

| 6.1<br>6.2                                    | Electro-Optical Characteristics     |

| 7                                             | Functional Description19            |

| 7.1<br>7.2<br>7.3<br>7.4<br>7.5<br>7.6<br>7.7 | Sensor Architecture                 |

| 7.8               | Additional Features9            |

|-------------------|---------------------------------|

| 8                 | Register Description10          |

| 8.1<br>8.2        | Register Overview               |

| 9                 | Application Information 12      |

| 9.1<br>9.2<br>9.3 | Color Filter                    |

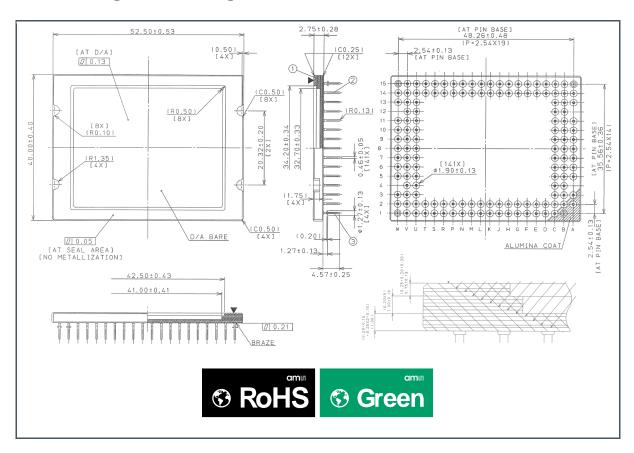

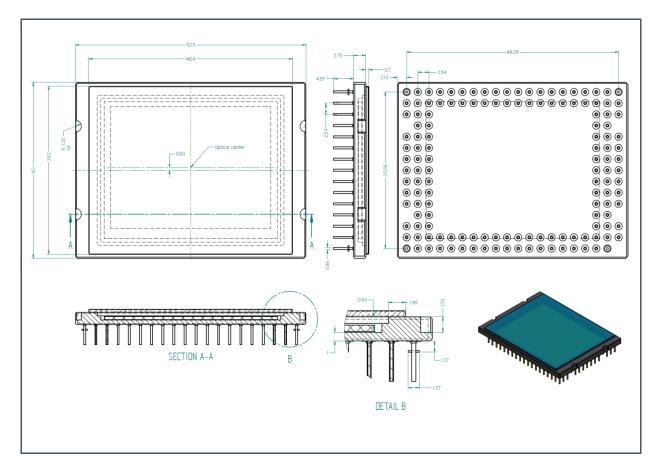

| 10                | Package Drawings & Markings. 13 |

| 11                | Packing Information13           |

| 12                | Soldering Information 13        |

| 13                | Revision Information 13         |

| 14                | Legal Information               |

## 1 General Description

The CMV50000 is a high speed CMOS image sensor with 7920 × 6004 effective pixels (47.5Mp) developed for machine vision and video applications. The image array consists of 4.6µm pipelined 8T global shutter pixels which allow exposure during read out, while performing true CDS (Correlated Double Sampling) operation. The image sensor also integrates a programmable analog gain amplifier and offset regulation. The image sensor has 22 digital sub-LVDS data output channels. Each output channel runs up to 830 Mbit/s, which results in a frame rate of 30 fps at full resolution. Higher frame rates can be achieved in row-windowing mode or row-subsampling mode. These modes are all programmable using the SPI interface. All internal exposure and read out timings are generated by a programmable on-chip sequencer. External triggering and exposure programming is also possible. Extended optical dynamic range can be achieved by a dual exposure HDR mode.

### 1.1 Key Benefits & Features

The benefits and features of CMV50000, 47.5MP CMOS Machine Vision Image Sensor, are listed below:

Figure 1: Added Value of Using CMV50000

| Benefits                                   | Features                                                                                             |

|--------------------------------------------|------------------------------------------------------------------------------------------------------|

| Designed for high performance applications | Resolution of 7920x6004 at 30 frames per second                                                      |

| Capture fast moving objects                | 8T global shutter pixel with true Correlated Double Sampling (true-CDS)                              |

| Use in low light conditions                | Low noise (8.8e) and high sensitivity (QE=60%), with on-chip noise reduction.                        |

| Use in bright light conditions             | In binning mode the full well capacity reaches 58000e <sup>-</sup> with an SNR of 47.6dB and DR=68dB |

| Standard optics can be used                | 35mm Full Frame optical format                                                                       |

| Easy to operate                            | On-chip digital sequencer which handles all the sensor controls, over SPI                            |

## 1.2 Applications

- Machine vision

- Video/Broadcast

- Security

- High-end inspection

- Aerial mapping

- Document scanning

- ITS

- Scientific

- 3D imaging

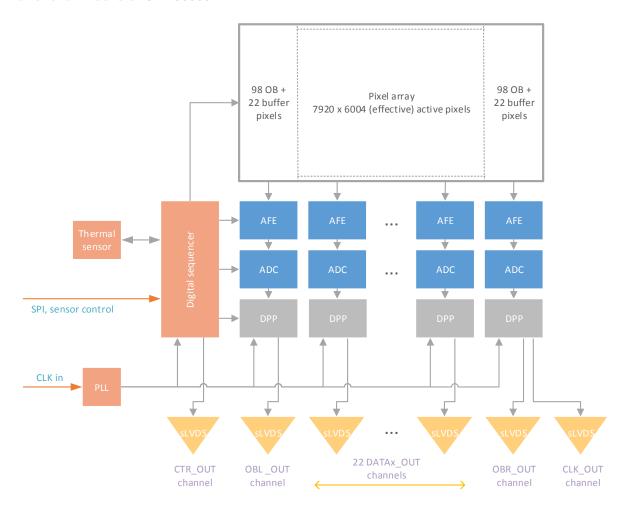

## 1.3 Block Diagram

The functional blocks of this device are shown below:

Figure 2 : Functional Blocks of CMV50000

## 2 Ordering Information

| Ordering Code      | Package | Chroma | Options | Delivery Quantity |

|--------------------|---------|--------|---------|-------------------|

| CMV50000ES-1E3M1PA | PGA     | Mono   |         | 10 Pcs / Tray     |

| CMV50000ES-1E3C1PA | PGA     | Color  |         | 10 Pcs / Tray     |

## 3 Pin Assignment

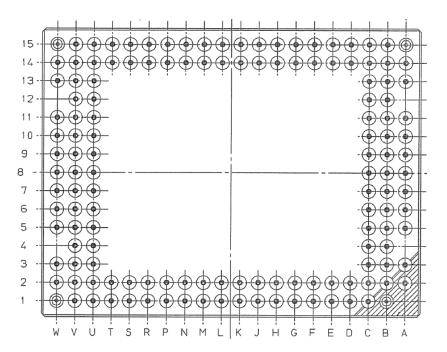

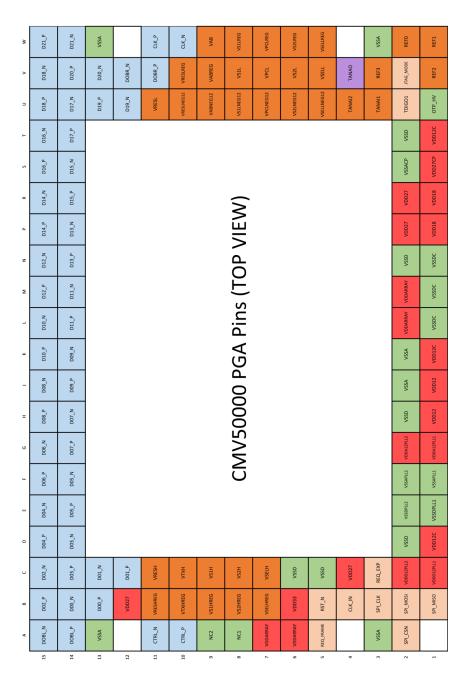

## 3.1 Pin Diagram

Figure 3:

Pin Numbering (bottom view)

## 3.2 Pin Description

Figure 4:

Pin Description of CMV50000

| Pin Number | Pin Name  | Pin Type      | Description                   |  |

|------------|-----------|---------------|-------------------------------|--|

| A2         | SPI_CSN   | Digital input | SPI Chip Select               |  |

| A3         | VSSA      | Analog ground | Analog ground                 |  |

| A5         | REQ_FRAME | Digital input | Request frame (stop exposure) |  |

| A6         | VDDARRAY  | Analog supply | Pixel array supply            |  |

| A7         | VDDARRAY  | Analog supply | Pixel array supply            |  |

| A8         | NC1       | Analog        | Do Not Connect                |  |

| A9         | NC2       | Analog        | Do Not Connect                |  |

| Pin Number | Pin Name   | Pin Type       | Description                       |

|------------|------------|----------------|-----------------------------------|

| A10        | CTRL_P     | sub-LVDS       | Control channel output            |

| A11        | CTRL_N     | sub-LVDS       | Control channel output            |

| A13        | VSSA       | Analog ground  | Main analog ground                |

| A14        | DOBL_P     | sub-LVDS       | Left Optical Black output         |

| A15        | DOBL_N     | sub-LVDS       | Left Optical Black output         |

| B1         | SPI_MISO   | Digital output | SPI Master In/Slave Out data      |

| B2         | SPI_MOSI   | Digital input  | SPI Master Out/Slave In data      |

| B3         | SPI_CLK    | Digital input  | SPI clock                         |

| B4         | CLK_IN     | Digital input  | Sensor input clock                |

| B5         | RST_N      | Digital input  | Asynchronous hard reset input pin |

| B6         | VDD33      | Analog supply  | On-chip regulators supply         |

| B7         | VSELHREG   | Analog         | On-chip regulator output          |

| B8         | VS2HREG    | Analog         | On-chip regulator output          |

| B9         | VS1HREG    | Analog         | On-chip regulator output          |

| B10        | VTXHREG    | Analog         | On-chip regulator output          |

| B11        | VRESHREG   | Analog         | On-chip regulator output          |

| B12        | VDD27      | Analog supply  | Main analog supply                |

| B13        | D00_P      | sub-LVDS       | Channel 0 output                  |

| B14        | D00_N      | sub-LVDS       | Channel 0 output                  |

| B15        | D02_P      | sub-LVDS       | Channel 2 output                  |

| C1         | VDDD12PLL1 | Digital supply | Digital supply for PLL1           |

| C2         | VDDD12PLL2 | Digital supply | Digital supply for PLL2           |

| C3         | REQ_EXP    | Digital input  | Request exposure (start exposure) |

| C4         | VDD27      | Analog supply  | Main analog supply                |

| C5         | VSSD       | Digital ground | Digital ground                    |

| C6         | VSSD       | Digital ground | Digital ground                    |

| C7         | VSELH      | Analog         | Bias                              |

| C8         | VS2H       | Analog         | Bias                              |

| C9         | VS1H       | Analog         | Bias                              |

| C10        | VTXH       | Analog         | Bias                              |

| C11        | VRESH      | Analog         | Bias                              |

| C12        | D01_P      | sub-LVDS       | Channel 1 output                  |

| C13        | D01_N      | sub-LVDS       | Channel 1 output                  |

| C14        | D03_P      | sub-LVDS       | Channel 3 output                  |

| C15        | D02_N      | sub-LVDS       | Channel 2 output                  |

| Pin Number | Pin Name   | Pin Type       | Description                 |  |

|------------|------------|----------------|-----------------------------|--|

| D1         | VDD12C     | Digital supply | Logic supply for ADC        |  |

| D2         | VSSD       | Digital ground | Main digital ground         |  |

| D14        | D03_N      | sub-LVDS       | Channel 3 output            |  |

| D15        | D04_P      | sub-LVDS       | Channel 4 output            |  |

| E1         | VSSDPLL1   | Digital ground | Digital ground for PLL1     |  |

| E2         | VSSDPLL2   | Digital ground | Digital ground for PLL2     |  |

| E14        | D05_P      | sub-LVDS       | Channel 0 output            |  |

| E15        | D04_N      | sub-LVDS       | Channel 0 output            |  |

| F1         | VSSAPLL1   | Analog ground  | Analog ground for PLL1      |  |

| F2         | VSSAPLL2   | Analog ground  | Analog ground for PLL2      |  |

| F14        | D05_N      | sub-LVDS       | Channel 5 output            |  |

| F15        | D06_P      | sub-LVDS       | Channel 6 output            |  |

| G1         | VDDA12PLL1 | Analog supply  | Analog supply for PLL1      |  |

| G2         | VDDA12PLL2 | Analog supply  | Analog supply for PLL2      |  |

| G14        | D07_P      | sub-LVDS       | Channel 7 output            |  |

| G15        | D06_N      | sub-LVDS       | Channel 6 output            |  |

| H1         | VDD12      | Digital supply | Logic supply for core logic |  |

| H2         | VSSD       | Digital ground | Main digital ground         |  |

| H14        | D07_N      | sub-LVDS       | Channel 7 output            |  |

| H15        | D08_P      | sub-LVDS       | Channel 8 output            |  |

| J1         | VDD12      | Digital supply | Logic supply for core logic |  |

| J2         | VSSA       | Analog ground  | Main analog ground          |  |

| J14        | D09_P      | sub-LVDS       | Channel 9 output            |  |

| J15        | D08_N      | sub-LVDS       | Channel 8 output            |  |

| K1         | VDD12C     | Digital supply | Logic supply for ADC        |  |

| K2         | VSSA       | Analog ground  | Main analog ground          |  |

| K14        | D09_N      | sub-LVDS       | Channel 9 output            |  |

| K15        | D10_P      | sub-LVDS       | Channel 10 output           |  |

| L1         | VSSDC      | Digital ground | Digital ground for ADC      |  |

| L2         | VDDARRAY   | Analog supply  | Pixel array supply          |  |

| L14        | D11_P      | sub-LVDS       | Channel 11 output           |  |

| L15        | D10_N      | sub-LVDS       | Channel 10 output           |  |

| M1         | VSSDC      | Digital ground | Digital ground for ADC      |  |

| M2         | VDDARRAY   | Analog supply  | Pixel array supply          |  |

| M14        | D11_N      | sub-LVDS       | Channel 11 output           |  |

| Pin Number | Pin Name   | Pin Type       | Description                   |  |

|------------|------------|----------------|-------------------------------|--|

| M15        | D12_P      | sub-LVDS       | Channel 12 output             |  |

| N1         | VSSDC      | Digital ground | Digital ground                |  |

| N2         | VSSD       | Digital ground | Digital ground                |  |

| N14        | D13_P      | sub-LVDS       | Channel 13 output             |  |

| N15        | D12_N      | sub-LVDS       | Channel 12 output             |  |

| P1         | VDD18      | Digital supply | I/O supply for CMOS and I/O's |  |

| P2         | VDD27      | Analog supply  | Main analog supply            |  |

| P14        | D13_N      | sub-LVDS       | Channel 13 output             |  |

| P15        | D14_P      | sub-LVDS       | Channel 14 output             |  |

| R1         | VDD18      | Digital supply | I/O supply for CMOS and I/O's |  |

| R2         | VDD27      | Analog supply  | Main analog supply            |  |

| R14        | D15_P      | sub-LVDS       | Channel 15 output             |  |

| R15        | D14_N      | sub-LVDS       | Channel 14 output             |  |

| S1         | VDD27CP    | Analog supply  | Connect to VDD27              |  |

| S2         | VSSACP     | Analog ground  | Analog ground                 |  |

| S14        | D15_N      | sub-LVDS       | Channel 15 output             |  |

| S15        | D16_P      | sub-LVDS       | Channel 16 output             |  |

| T1         | VDD12C     | Digital supply | Logic supply for ADC          |  |

| T2         | VSSD       | Digital ground | Main digital ground           |  |

| T14        | D17_P      | sub-LVDS       | Channel 17 output             |  |

| T15        | D16_N      | sub-LVDS       | Channel 16 output             |  |

| U1         | EXTRA1     | Analog ground  | Connect to analog ground      |  |

| U2         | TDIGO1     | Digital output | Digital test output           |  |

| U3         | TANAI1     | Analog         | Do Not Connect                |  |

| U4         | TANAI2     | Analog         | Do Not Connect                |  |

| U5         | VSELLNEG12 | Analog         | On-chip regulator output      |  |

| U6         | VS2LNEG12  | Analog         | On-chip regulator output      |  |

| U7         | VPCLNEG12  | Analog         | On-chip regulator output      |  |

| U8         | VS1LNEG12  | Analog         | On-chip regulator output      |  |

| U9         | VABNEG12   | Analog         | On-chip regulator output      |  |

| U10        | VRESLNEG12 | Analog         | On-chip regulator output      |  |

| U11        | VRESL      | Analog         | Bias                          |  |

| U12        | D19_N      | sub-LVDS       | Channel 19 output             |  |

| U13        | D19_P      | sub-LVDS       | Channel 19 output             |  |

| U14        | D17_N      | sub-LVDS       | Channel 17 output             |  |

| Pin Number | Pin Name  | Pin Type      | Description                                            |

|------------|-----------|---------------|--------------------------------------------------------|

| U15        | D18_P     | sub-LVDS      | Channel 18 output                                      |

| V1         | REF2      | Analog        | Do Not Connect                                         |

| V2         | JTAG_MODE | Digital input | JTAG Mode select. Connect to VSSD if JTAG is not used. |

| V3         | REF3      | Analog        | Bias                                                   |

| V4         | TANAO     | Analog        | Do Not Connect                                         |

| V5         | VSELL     | Analog        | Bias                                                   |

| V6         | VS2L      | Analog        | Bias                                                   |

| V7         | VPCL      | Analog        | Bias                                                   |

| V8         | VS1L      | Analog        | Bias                                                   |

| V9         | VABREG    | Analog        | On-chip regulator output                               |

| V10        | VRESLREG  | Analog        | On-chip regulator output                               |

| V11        | DOBR_P    | sub-LVDS      | Right Optical Black output                             |

| V12        | DOBR_N    | sub-LVDS      | Right Optical Black output                             |

| V13        | D20_N     | sub-LVDS      | Channel 20 output                                      |

| V14        | D20_P     | sub-LVDS      | Channel 20 output                                      |

| V15        | D18_N     | sub-LVDS      | Channel 18 output                                      |

| W1         | REF1      | Analog        | Do Not Connect                                         |

| W2         | REF0      | Analog        | Bias                                                   |

| W3         | VSSA      | Analog ground | Analog ground                                          |

| W5         | VSELLREG  | Analog        | On-chip regulator output                               |

| W6         | VS2LREG   | Analog        | On-chip regulator output                               |

| W7         | VPCLREG   | Analog        | On-chip regulator output                               |

| W8         | VS1LREG   | Analog        | On-chip regulator output                               |

| W9         | VAB       | Analog        | Bias                                                   |

| W10        | CLK_N     | sub-LVDS      | Clock output                                           |

| W11        | CLK_P     | sub-LVDS      | Clock output                                           |

| W13        | VSSA      | Analog ground | Main analog ground                                     |

| W14        | D21_N     | sub-LVDS      | Channel 21 output                                      |

| W15        | D21_P     | sub-LVDS      | Channel 21 output                                      |

## 4 Absolute Maximum Ratings

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated under "Operating Conditions" is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Figure 5:

Absolute Maximum Ratings of CMV50000

| Symbol             | Parameter                          | Min   | Max | Unit | Comments                  |

|--------------------|------------------------------------|-------|-----|------|---------------------------|

| Electrical Pa      | arameters                          |       |     |      |                           |

| I <sub>SCR</sub>   | Input Current (latch-up immunity)  | ±1    | 00  | mA   | JEDEC JESD78D Nov<br>2011 |

| Electrostation     | c Discharge                        |       |     |      |                           |

| ESD <sub>HBM</sub> | Electrostatic Discharge HBM        | ±2000 |     | V    | JEDEC JS-001-2014         |

| ESD <sub>CDM</sub> | Electrostatic Discharge CDM        | ±2    | 50  | V    | JEDEC JS-002-2014         |

| Temperature        | e Ranges and Storage Conditions    |       |     |      |                           |

| TJ                 | Operating Junction Temperature     | -30   | 70  | °C   |                           |

| T <sub>STRG</sub>  | Storage Temperature Range          | -30   | 70  | °C   |                           |

| R <sub>HNC</sub>   | Relative Humidity (non-condensing) | 30    | 60  | %    | Storage condition         |

## **5** Electrical Characteristics

All limits are guaranteed. The parameters with Min and Max values are guaranteed with production tests or SQC (Statistical Quality Control) methods.

Figure 6: Electrical Characteristics of CMV50000

| Symbol               | Parameter                                                             | Conditions           | Min         | Tyre                      | Max         | Unit |

|----------------------|-----------------------------------------------------------------------|----------------------|-------------|---------------------------|-------------|------|

| Symbol               | Parameter                                                             | Conditions           | Min         | Тур                       | Max         | Unit |

| Power Suppli         | ies                                                                   |                      |             |                           |             |      |

| VDD12                | Logic Supply Voltage of digital core, PLL                             |                      | 1.10        | 1.20                      | 1.30        | V    |

| VDD12C               | Logic Supply Voltage of ADC                                           |                      | 1.10        | 1.20                      | 1.30        | V    |

| VDD18                | I/O Supply Voltage for sub-LVDS, CMOS I/O's                           |                      | 1.70        | 1.80                      | 1.90        | V    |

| VDD27                | Main Analog Supply Voltage;<br>Supply Voltage for negative regulators |                      | 2.60        | 2.70                      | 2.80        | V    |

| VDDARRAY             | Pixel Array Supply Voltage                                            |                      | 2.60        | 2.70                      | 2.80        | V    |

| VDD33                | Internal Regulator Supply Voltage                                     |                      | 3.20        | 3.30                      | 3.40        | V    |

| IDD12                | Supply Current                                                        | Idle<br>Running      |             | 350<br>375                |             | mA   |

| IDD12C               | Supply Current                                                        | Idle<br>Running      |             | 10<br>410                 |             | mA   |

| IDD18                | Supply Current                                                        | Idle<br>Running      |             | 130<br>115                |             | mA   |

| IDD27                | Supply Current                                                        | Idle<br>Running      |             | 550<br>550                |             | mA   |

| IDDARRAY             | Supply Current                                                        | Idle<br>Running      |             | 130<br>130 <sup>(1)</sup> |             | mA   |

| IDD33                | Supply Current                                                        | Idle<br>Running      |             | 20<br>20                  |             | mA   |

| Ptot                 | Total Power Consumption                                               | Idle<br>Running      |             | 2.5<br>3.0                |             | W    |

| Digital I/O          |                                                                       |                      |             |                           |             |      |

| V <sub>IH</sub>      | High level input voltage                                              |                      | 0.7 × VDD18 |                           | VDD18 +0.5  | V    |

| V <sub>IL</sub>      | Low level input voltage                                               |                      | -0.5        |                           | 0.3 × VDD18 | V    |

| V <sub>OH</sub>      | High level output voltage                                             | I <sub>OH</sub> =4mA | VDD18 -0.15 |                           | -           | V    |

| V <sub>OL</sub>      | Low level output voltage                                              | I <sub>OL</sub> =4mA | -           |                           | 0.15        | V    |

| Cı                   | Input load                                                            |                      | -           |                           | 10          | pF   |

| Co                   | Output load                                                           |                      | -           |                           | 20          | pF   |

| T <sub>tran</sub>    | Input transition time                                                 |                      | 0.1         |                           | 5.0         | ns   |

| f <sub>CLK_IN</sub>  | CLK_IN frequency                                                      |                      | 6           |                           | 96          | MHz  |

| DC <sub>CLK_IN</sub> | CLK_IN duty cycle                                                     |                      | 40          |                           | 60          | %    |

| Symbol               | Parameter                  | Conditions | Min                         | Тур | Max | Unit   |

|----------------------|----------------------------|------------|-----------------------------|-----|-----|--------|

| f <sub>SPI_CLK</sub> | SPI input clock frequency  |            | -                           |     | 10  | MHz    |

| t <sub>setup</sub>   | SPI setup time             |            | 0.25 x T <sub>SPI_CLK</sub> |     | -   | ns     |

| t <sub>hold</sub>    | SPI hold time              |            | 0                           |     | -   | ns     |

| t <sub>REQ</sub>     | REQ_FRAME/EXP pulse width  |            | 2 × T <sub>CLK_PIX</sub>    |     | -   | ns     |

| Sub-LVDS             | Interface                  |            |                             |     |     |        |

| V <sub>CM</sub>      | Common mode voltage        |            | 0.8                         | 0.9 | 1.0 | V      |

| V <sub>OD</sub>      | Differential voltage swing |            | 100                         | 150 | 200 | mV     |

| Ro                   | Output impedance (2)       |            | 40                          |     | 240 | Ohm    |

| D <sub>R0</sub>      | Impedance mismatch         |            |                             |     | 10  | %      |

| DC                   | Clock duty cycle           |            | 45                          | 50  | 55  | %      |

| f                    | Operating frequency        |            | 60                          |     | 415 | MHz    |

| I <sub>OD</sub>      | Drive current              |            | 1                           | 1.5 | 2   | mA     |

| ΔIOD                 | IOD variation over Temp.   |            |                             |     | 15  | %      |

| I <sub>DC</sub>      | DC current consumption     |            |                             | 3.7 |     | mA     |

| I <sub>AC</sub>      | AC current consumption     |            |                             | 7.2 |     | μA/MHz |

<sup>(1)</sup> VDDARRAY draws high peak currents (>1A) during GLOB. Enough decoupling is needed to suppress these peaks.

<sup>(2)</sup> Unused sub-LVDS channels must be terminated the same way as the used channels.

## **6 Typical Operating Characteristics**

### 6.1 Electro-Optical Characteristics

Below are the typical electro-optical specifications of the CMV50000. These are typical values for the whole operating temperature range.

Figure 7: Electro-Optical Characteristics of CMV50000

| Parameter                   | Value                        | Remark                                                                                                               |  |  |

|-----------------------------|------------------------------|----------------------------------------------------------------------------------------------------------------------|--|--|

| Effective pixels            | 7920 × 6004                  |                                                                                                                      |  |  |

| Pixel pitch                 | 4.6 × 4.6 μm²                |                                                                                                                      |  |  |

| Optical format              | 35mm full frame              |                                                                                                                      |  |  |

| Pixel type                  | Global shutter with true CDS | Allows fixed pattern noise correction and reset (kTC) noise canceling by true correlated double sampling (true-CDS). |  |  |

| Shutter type                | Pipelined global shutter     | Exposure of next image during readout of the previous image.                                                         |  |  |

| Full well charge            | 14500 e <sup>-</sup>         | Normal mode                                                                                                          |  |  |

|                             | 58000 e <sup>-</sup>         | Binning mode                                                                                                         |  |  |

| Conversion gain             | 0.27 DN/e <sup>-</sup>       | Normal mode, unity gain                                                                                              |  |  |

|                             | 0.068 DN/ e <sup>-</sup>     | Binning mode, unity gain                                                                                             |  |  |

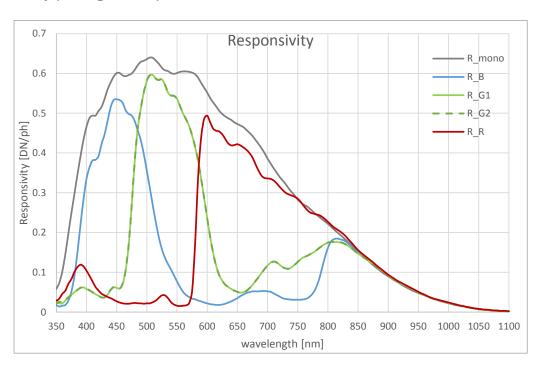

| Responsivity                | 0.16 DN/photon               | @ 510nm (with micro-lenses)                                                                                          |  |  |

|                             | 0.25 A/W                     |                                                                                                                      |  |  |

| Temporal noise              | 8.8 e <sup>-</sup>           | Normal mode                                                                                                          |  |  |

|                             | 22 e <sup>-</sup>            | Binning mode                                                                                                         |  |  |

| Dynamic range               | 64 dB                        | Normal mode                                                                                                          |  |  |

|                             | 68 dB                        | Binning mode                                                                                                         |  |  |

| SNR <sub>MAX</sub>          | 41.6 dB                      | Normal mode                                                                                                          |  |  |

|                             | 47.6dB                       | Binning mode                                                                                                         |  |  |

| Shutter efficiency<br>1/PLS | 1/18000                      | At 520nm, f/8.                                                                                                       |  |  |

| DC                          | 0.24 e <sup>-</sup> /s       | @ 20°C sensor temperature                                                                                            |  |  |

|                             | 66.2 e <sup>-</sup> /s       | @ 60°C sensor temperature                                                                                            |  |  |

|                             |                              | Dark Current doubles every 5.1°C increase                                                                            |  |  |

| DCNU                        | 0.72 e <sup>-</sup> /s       | @ 20°C sensor temperature                                                                                            |  |  |

|                             | 14.2 e <sup>-</sup> /s       | @ 60°C sensor temperature                                                                                            |  |  |

|                             |                              | DC Non-Uniformity doubles every 10°C increase                                                                        |  |  |

| DSNU                        | 24.5 e <sup>-</sup>          | Dark Signal Non Uniformity (FPN)                                                                                     |  |  |

|                             |                              | <0.2%rms of saturation                                                                                               |  |  |

| PRNU                        | < 1.0% RMS                   | Photo Response Non Uniformity                                                                                        |  |  |

|                             |                              | RMS of signal                                                                                                        |  |  |

| Parameter              | Value                 | Remark                                                                            |  |  |

|------------------------|-----------------------|-----------------------------------------------------------------------------------|--|--|

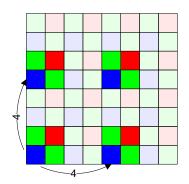

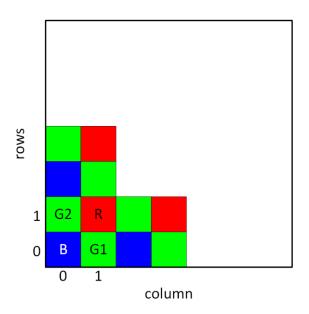

| Color filters          | Optional              | RGB Bayer pattern                                                                 |  |  |

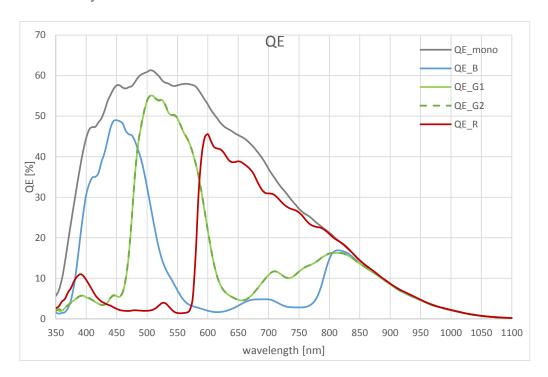

| QE                     | 58 / 61 / 53 / 14.5 % | Quantum Efficiency (with micro-lenses)<br>@ 450 / 510 / 600 / 850nm (mono device) |  |  |

|                        | 49 / 55 / 45 %        | @ 450 / 510 / 600nm (color device)                                                |  |  |

| Sub-LVDS outputs       | 22 Data               | Each data output running @ 830 Mbit/s.                                            |  |  |

|                        | 1 Control<br>1 Clock  | Less outputs selectable at reduced frame rate                                     |  |  |

| Frame rate             | 30 fps                | Using 830 Mbit/s sub-LVDS in pixel-based output                                   |  |  |

|                        |                       | Higher frame rate possible in row windowing mode.                                 |  |  |

| Timing generation      | On-chip               | Possibility to control exposure time through external pin.                        |  |  |

| PGA                    | Yes                   | x1, x1.33, x2, x4 analog gain settings                                            |  |  |

| Programmable registers | Sensor parameters     | Window coordinates, Timing parameters, Gain & offset, Exposure time,              |  |  |

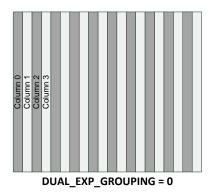

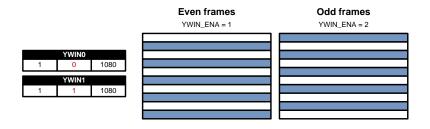

| HDR mode               | Interleaved           | 2 exposure times for odd/even columns                                             |  |  |

| ADC                    | 12 bit                | Column ADC                                                                        |  |  |

| Interface              | sub-LVDS; 830 Mbit/s  | Serial output data + synchronization signals                                      |  |  |

| I/O logic levels       | sub-LVDS = 1.2 V      |                                                                                   |  |  |

|                        | Dig. I/O = 1.8 V      |                                                                                   |  |  |

| Cover glass            | D263T eco             | Double sided AR coating                                                           |  |  |

|                        |                       | R<1.5 % abs, 400 - 900nm, per surface, AOI=15°                                    |  |  |

| Mass                   | 20gr                  |                                                                                   |  |  |

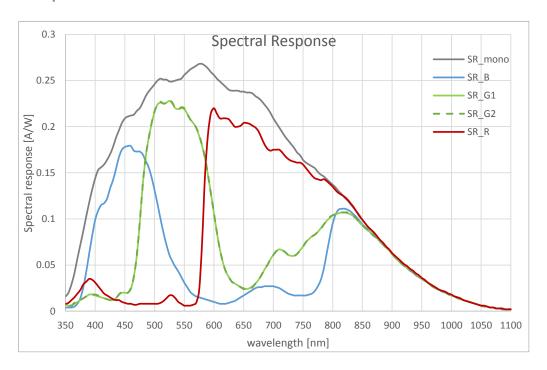

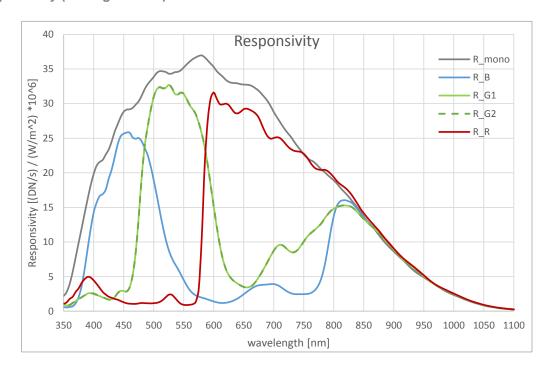

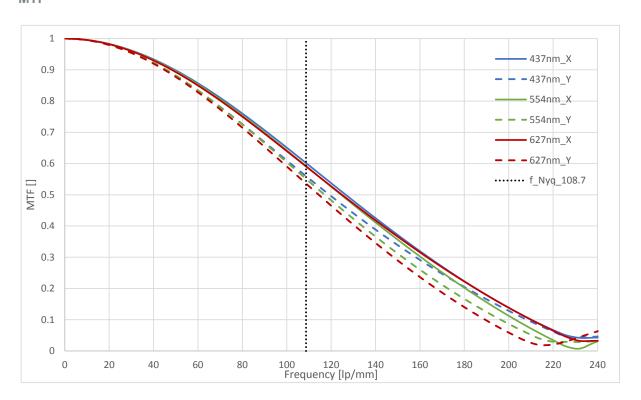

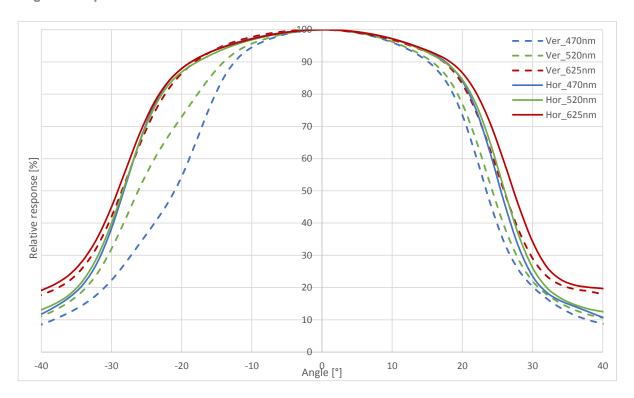

## 6.2 Spectral Characteristics

Figure 8 : Quantum Efficiency

Figure 9 : Responsivity (Analog Gain x4)

Figure 10 : Spectral Response

Figure 11 : Responsivity (Analog Gain x4)

Figure 12 : MTF

Figure 13 : Angular Response

## 7 Functional Description

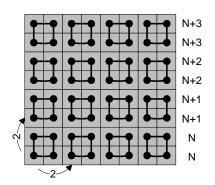

#### 7.1 Sensor Architecture

Figure 2 shows a high-level representation of the chip architecture for the CMV50000 sensor. The drawing shows the active pixel array and the periphery around it that enables the control and readout of the pixels.

The core of the image sensor is made up from the pixel array, which is driven from two sides by 2 instances of the row logic and drivers. The pixel control signals are created globally by the global drivers and distributed to the sides of the sensor. The pixel data is read out row by row using a data path consisting of an analog front-end (AFE), analog-to-digital converter (ADC) and a digital data post-processing (DPP) block.

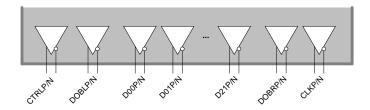

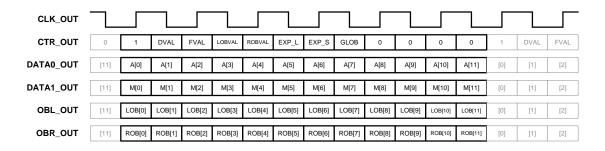

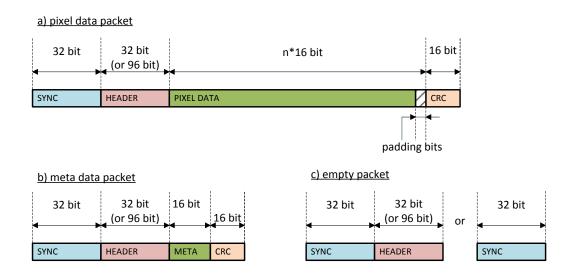

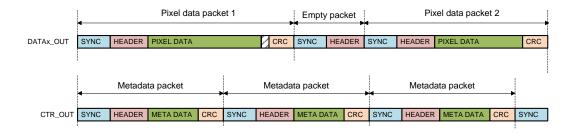

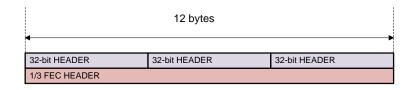

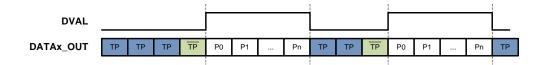

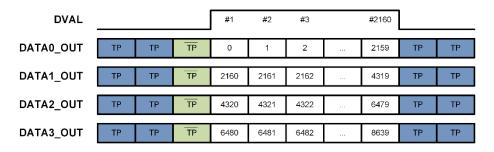

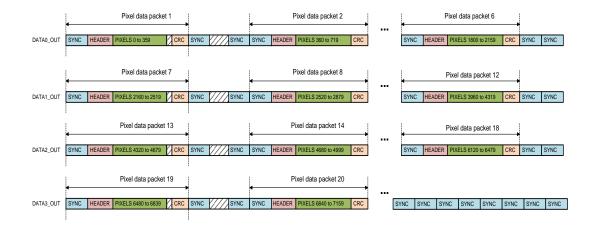

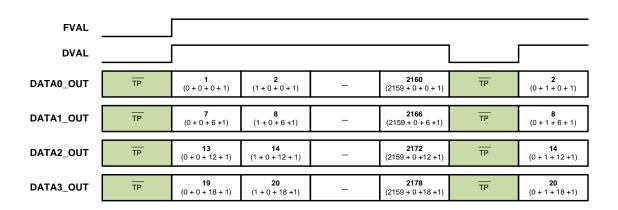

The converted data is sent, pixel by pixel, to a set of sub-LVDS drivers. An additional control (CTR) channel provides synchronization information about the data on the data channels, while a specific CLK channel can be used to sample the data channels.

The data path is organized in kernels of 360 columns. Between kernels, control signals are repeated. There is one sub-LVDS driver for every kernel. At the left and right side of the pixel array, an additional kernel of OB pixels is added.

An on-chip sequencer controls the sensor operation and contains a register bank that is programmable over an SPI interface. There is also an on-chip temperature sensor available. A low-frequency CMOS input clock is transformed using an on-chip PLL to a set of high-frequency signals used in the sensor.

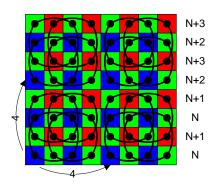

#### 7.1.1 Pixel Array

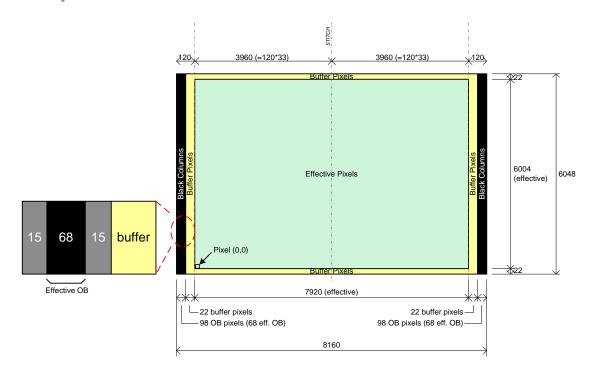

Figure 14 shows the complete pixel array.

Figure 14: Pixel Array

The pixel array can be split up in 3 parts: Optical black (OB) pixels (left and right side), buffer pixels (around effective array perimeter) and effective pixels. Only the 68 effective OB pixels are used for internal row clamping, which improves row noise and allows setting a pre-defined black level. The buffer pixels form a guard ring around the effective pixels. The buffer pixels are optically active, but are not guaranteed to meet the optical specifications. The 98 OB and 22 buffer pixels are read out via the sub-LVDS OB-L/R outputs.

The full resolution of the pixel array is  $8160 \times 6048$  pixels. This results in an effective resolution of  $7920 \times 6004$  pixels or 47.5Mpixels. The effective array is 36.4mm  $\times 27.6$ mm which is slightly larger than the 35mm full frame optical format (= 36mm  $\times 24$ mm; which would correspond to a window of  $7826 \times 5217$ ).

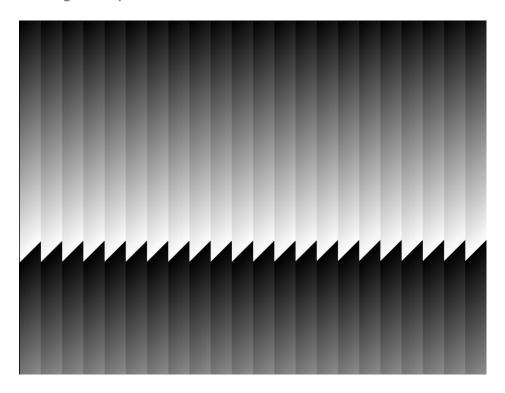

Because of the large sensor area, a wafer process called mask stitching is done. The vertical stitch line is located exactly in the middle of the array. Therefor a small offset between the pixels left and right of the stitch line might be present.

Micro-lenses are placed on the pixels for improved quantum efficiency and fill factor.

#### 7.1.2 Analog Front End

The analog front end consists of the PGA (programmable gain amplifier) and circuitry to prepare the signal for ADC conversion

#### 7.1.3 ADC

The column ADC converts the analog pixel value to a 12-bit value.

#### 7.1.4 DPP

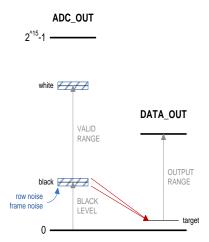

The DPP blocks perform digital operations on the visible pixel data: digital offset, digital gain, row noise correction.

#### 7.1.5 Sub-LVDS Outputs

The sensor has 22 sub-LVDS data channels to output the processed data. Each data channel outputs the data of 360 columns. Readout modes using less parallel channels at reduced framerate are supported as well.

#### 7.1.6 Sequencer

The on-chip sequencer will generate all required control signals to operate the sensor from only a few external control clocks. This sequencer can be activated and programmed through the SPI interface.

- Among the different features that the sequencer has implemented are the following:

- SPI protocol and register banks management.

- Exposure and frame timing generation based on external inputs or internal settings.

- Dual exposure HDR mode.

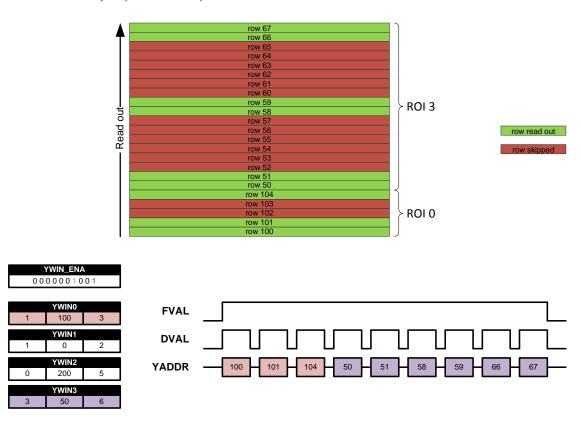

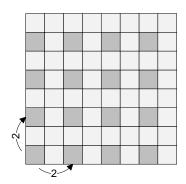

- Y-windowing, subsampling and binning

#### 7.1.7 SPI Interface

The SPI interface is used to load the sequencer registers with settings to configure the image sensor. Features like windowing, subsampling, gain and offset are programmed using this interface. The settings in the on-chip registers can also be read back for test and debug of the surrounding system.

#### 7.1.8 Temperature Sensor

An on-chip thermal sensor is included. The temperature data is read out through the SPI interface.

#### 7.1.9 PLL

Various clock frequencies are required internally to operate the sensor. These are derived from a single input frequency using an on-chip PLL. Through configuration over SPI, a range of input clock frequencies is supported.

The 3 main internal clocks are CLK\_ADC, CLK\_SER and CLK\_PIX:

- CLK\_ADC is the PLL output clock and is equal to the data rate (830MHz for 830Mbit/s).

- CLK\_SER is 1:2 of CLK\_ADC and equal to the sub-LVDS output clock.

- CLK\_PIX is the pixel clock and has a ratio of 1:12 of CLK\_ADC.

#### **7.1.10 OTP Memory**

A non-volatile, one time programmable memory is included on-chip. This is programmed with unique device ID and temperature sensor calibration data which the user can use.

### 7.2 Operating the Sensor

This section explains how to connect and power the sensor, as well as basic recipes of how to configure the sensor in a certain operation mode.

#### 7.2.1 Power Supplies

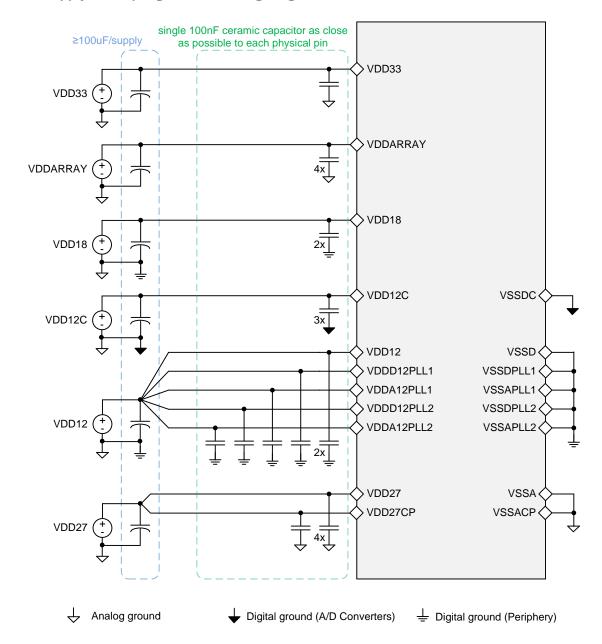

#### **External Power Supplies**

To power the sensor, six externally generated supplies are required as listed in Figure 6. A distinction is made between digital supplies (VDD12, VDD12C, VDD18) and analog supplies (VDD27, VDDARRAY, VDD33). Avoid using switching power supplies when possible, especially for the analog supplies.

Sufficient bulk (at the regulators) and local (at the sensor pins) decoupling is needed. In case of multiple pins for the same supply, local decoupling must be foreseen for each pin (e.g. four capacitors for the four VDDARRAY pins). Separate ground planes must be provided to minimize coupling.

For optimal noise performance, it is advised to keep the analog and digital ground nets separated and connect them together as close as possible to the external supply regulators.

Figure 15:

Power Supply Decoupling and Grounding Diagram

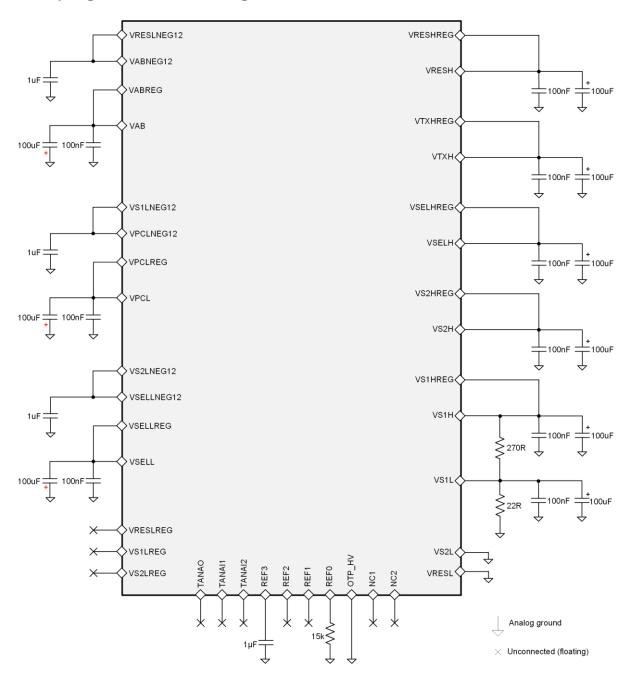

#### Biasing (on-chip regulators)

Operating the pixel array requires multiple different biasing supply levels. These supply levels can be generated using on-chip regulators. The chip contains 2 types of regulators, for positive supply levels and negative supply levels. The regulator output voltages are controlled using the SPI interface.

The supply regulators are internally not connected to the actual image sensor. Connections have to be made on PCB level (from a VxxREG pin to a Vyy pin). Also, each supply regulator requires to be

decoupled by a 100µF and 100nF capacitor. The negative supply regulators also require a decoupling of 1µF on a separate output pin (which will settle to -1.2V).

Next figure shows the positive and negative voltage regulator as well as the bias connections.

Figure 16:

On-Chip Regulators Connection Diagram

For the 100nF and  $1\mu$ F capacitors, ceramic types can be used. Capacitances of  $100\mu$ F can be electrolytic types (beware of the polarity on the negative supplies!). The maximal specified ESR and ESL of these  $100\mu$ F capacitors are  $0.1\Omega$  and 10nH respectively.

A resistor network is necessary between VS1H and VS1L (±5% tolerance).

To obtain an accurate current bias reference in the sensor, an external bias resistor of 15kOhm (±5%) must be placed between REF0 and ground. No decoupling is required in parallel with this resistor. A maximal capacitance of 1nF on this node is allowed.

After power-up of the sensor, the recommended register settings will set the correct supply levels for these regulators (see section 7.4). Next table gives an overview of the available supply regulators, the connection to the bias pin and the required voltage on that pin.

Figure 17: Bias Voltages

| Regulator Pin | Туре                   | Bias Pin   | Voltage<br>(V) |

|---------------|------------------------|------------|----------------|

| VRESHREG      | Positive               | VRESH      | 3.2            |

| VTXHREG       | Positive               | VTXH       | 3.0            |

| VS1HREG       | Positive               | VS1H       | 3.0            |

| VS2HREG       | Positive               | VS2H       | 3.0            |

| VSELHREG      | Positive               | VSELH      | 3.0            |

| VABREG        | Negative               | VAB        | -0.8           |

| VPCLREG       | Negative               | VPCL       | -0.3           |

| VSELLREG      | SELLREG Negative VSELL |            | -0.6           |

| -             | Positive               | VS1L       | 0.25           |

| -             | Ground                 | VS2L       | 0              |

| -             | Ground                 | VRESL      | 0              |

| VRESLREG      | Negative               | -          | 0              |

| VS1LREG       | Negative               | -          | 0              |

| VS2LREG       | Negative               | -          | 0              |

| VRESLNEG12    | Negative               | VABNEG12   | -1.2           |

| VS1LNEG12     | Negative               | VPCLNEG12  | -1.2           |

| VS2LNEG12     | Negative               | VSELLNEG12 | -1.2           |

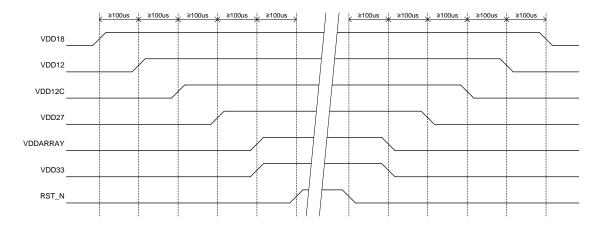

#### 7.2.2 Power-Up/Down Sequence

To avoid peak currents and guarantee a proper power-up/down of the sensor, following supply order and timing must be applied.

Figure 18: Supply Power-Up and Power-Down Sequences

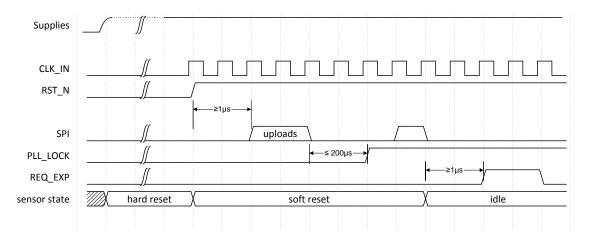

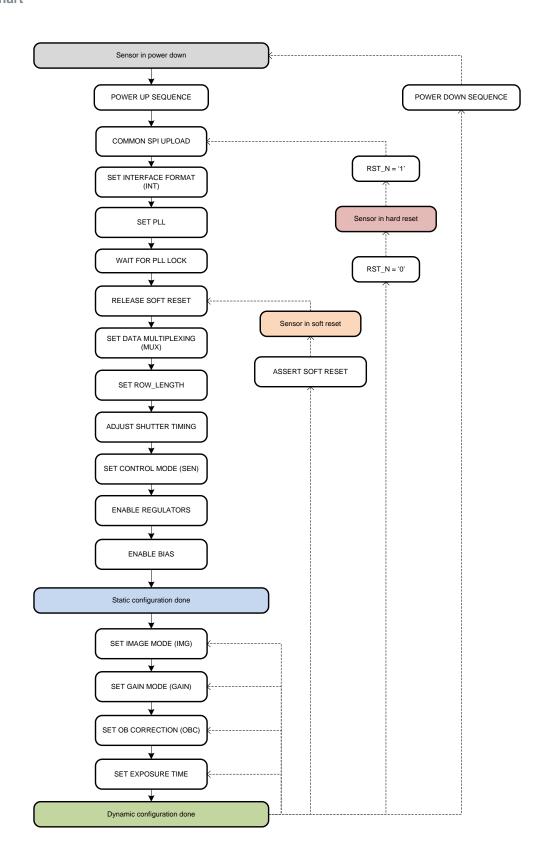

#### 7.2.3 Startup Sequence

After the supply power-up sequence, the general sequence below must be followed to configure and start operating the sensor. Deviating from the order or timing can lead to the sensor being in an unknown or unstable state.

The sensor hard reset pin, RST\_N, must be asserted ('0') during the supply ramp-up to initialize the sensor in the hard reset state. By releasing RST\_N ('1'), the sensor moves to soft reset state. CLK\_IN can be started during either the hard reset or during soft reset state. During the soft reset state, the recommended SPI uploads must be executed (see section 7.4). One of them enables the PLL. After maximally 200µs, the PLL will lock. After the PLL has locked the sensor can be moved from soft reset state to idle state through a short SPI upload.

In idle state, the sensor waits for an exposure request to begin grabbing, for example with REQ\_EXP pin (depending on the configured sensor control mode).

As indicated in the figure, a non-overlap of 1 µs must be respected between each sensor state change and the next action.

Figure 19:

Power-Up Sequence (not to scale)

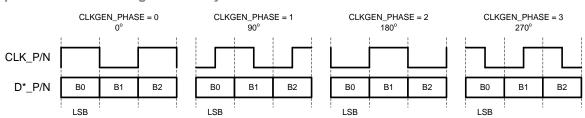

#### 7.2.4 Clocking

The sensor has two CMOS clock inputs: SPI\_CLK and CLK\_IN. SPI\_CLK is part of the SPI interface used to configure the sensor. All other internal sensor clocks are derived from two PLLs running on CLK\_IN.

Refer to section 5 for the electrical specifications of the input clocks and to section 7.1.9 for the configuration procedure of the PLL.

#### 7.2.5 SPI and Register Access

The sensor operation must be configured by uploading register settings. These static register values control the behavior of the sequencer on the chip, but also of all the analog and mixed-signal blocks. To write and read register settings the SPI interface is used.

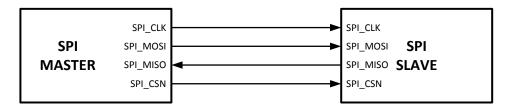

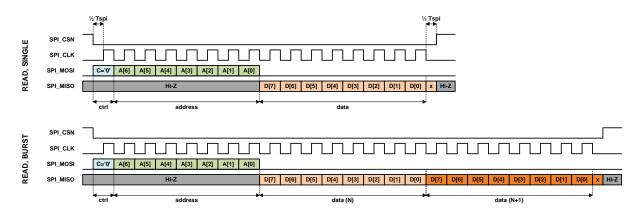

The SPI (Serial Peripheral Interface) consists of four wires, as shown in Figure 21. The CMV50000 image sensor always operates as the SPI slave. A single SPI access always consists of:

- Transfer of a control bit from master to slave to specify transfer direction (read or write)

- Transfer of 7-bit register address from master to slave

- Transfer of 8-bit data from master to slave (write operation) or from slave to master (read operation)

Figure 20: SPI Signal Overview

| Pin Name | Direction     | Purpose                                      |  |  |

|----------|---------------|----------------------------------------------|--|--|

| SPI_CSN  | Sensor Input  | Active-low chip select                       |  |  |

| SPI_CLK  | Sensor Input  | Rising-edge triggered clock for SPI protocol |  |  |

| SPI_MOSI | Sensor Input  | Data moving from master to slave             |  |  |

| SPI_MISO | Sensor Output | Data moving from slave to master             |  |  |

Data is written to the registers of the SPI slave over the SPI\_MOSI wire. The data written to the programming registers can also be read out over this same SPI interface, using the SPI\_MISO wire. SPI\_CSN is an active-low chip select that enables the SPI slave. The details of the timing and data format are described below.

Figure 21: SPI Connection Diagram

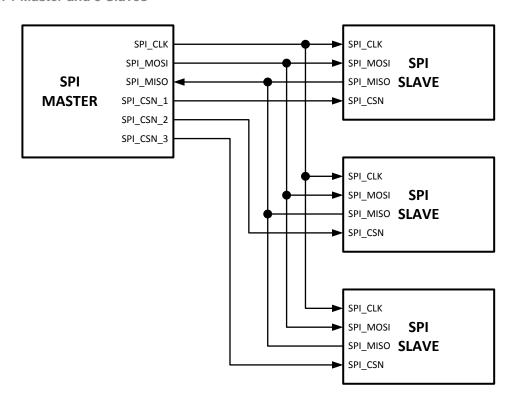

When using multiple CMV image sensors, the SPI\_CLK and SPI\_MOSI can be shared among them. The SPI\_CSN operates as a chip select for each of the slaves. The SPI\_MISO can also be shared on a bus because it is tri-stated when it is not used. This configuration of one master and multiple slaves is shown in Figure 22.

Figure 22: SPI with 1 Master and 3 Slaves

An SPI access always consists of the transfer of the following bits (in this order), as given in Figure 23:

Figure 23: SPI Bits Transfer Sequence

| Phase | # Bits | Via      | Purpose                                                               |

|-------|--------|----------|-----------------------------------------------------------------------|

| CTRL  | 1      | SPI_MISO | Control bit indicating SPI access direction (1 for write, 0 for read) |

| ADDR  | 7      | SPI_MISO | Address (0-127) of register to be accessed                            |

| DATA  | N*8    | SPI_MISO | Data written to N consecutive register addresses, starting at ADDR    |

|       |        | SPI_MOSI | Data read from N consecutive register addresses, starting at ADDR     |

Via a burst mode, it's possible to write/read multiple consecutive register addresses with a single address upload.

The state of SPI\_CLK whenever SPI\_CSN is high is ignored, though it is advised to stop the clock to save unnecessary power consumption.

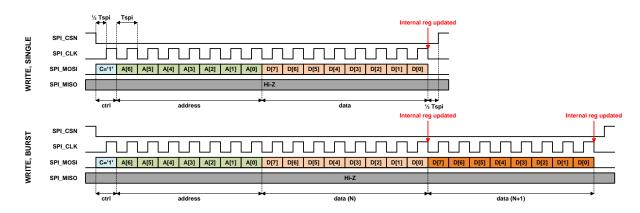

#### **SPI Write**

The SPI\_MOSI data is sampled by the CMV image sensor on the rising edge of the SPI\_CLK. The SPI\_CSN signal shall be low for ½ a SPI\_CLK period before the first data bit is sampled. SPI\_CSN shall remain low for ½ a SPI\_CLK period after the last falling edge of SPI\_CLK. The first bit transferred is a control bit indicating a write operation ('1'). Both the subsequent address (A<6:0>) and data (D<7:0>) are sent MSB-first.

When writing multiple sequential registers (e.g. 100, 101, 102 ...), the write burst mode can be used. The address is that of the 1<sup>st</sup> register to be written to and the sequencer will automatically shift to the next register after 8 data bits. SPI\_CSN shall stay low the entire time.

The actual register value is updated with the new value on the falling edge of SPI\_CLK on every D[0] bit. I.e. SPI\_CLK shall go low at the end of D[0] for the write sequence to be completed. The timing of both write modes is illustrated below.

Figure 24: SPI Write Timing

#### **SPI Read**

The timing of the SPI read sequence is similar to the SPI write sequence. The main differences are the control bit and the use of SPI\_MISO. An SPI read is indicated by setting the control bit to '0'. After the control bit, the address of the register to read shall be transmitted MSB first. At the end of the LSB of the address, the data is launched on the SPI\_MISO pin on the falling edge of the SPI\_CLK. This means that the data can be sampled by the SPI master on the rising edge of the SPI\_CLK. The data D<7:0> is transmitted MSB first on SPI\_MISO. When not transmitting data, the SPI\_MISO output is in high-Z state.

Sequential SPI register addresses can also be read out in burst mode by keeping SPI\_CSN low and clocking out additional bytes. The timing of both read modes is illustrated below.

Figure 25: SPI Read Timing

#### **Register Banks**

The sensor's configuration registers are organized in four banks. Each bank contains 127 8-bit registers.

To select a certain register bank, the register at address 0 is used. This register is accessible regardless of the currently selected register bank, of course.

Figure 26: Bank Selection Register

| Register Name | Bit Name | Bank | Addr | Pos   | Description                                      |

|---------------|----------|------|------|-------|--------------------------------------------------|

| BANK_SEL      | BANK_SEL | N/A  | 0    | [1:0] | 0: Bank 0<br>1: Bank 1<br>2: Bank 2<br>3: Bank 3 |

The value of BANK\_SEL selects which register bank the current SPI access will have an effect on. An example is given below. 'Addr' is the address of the register being written to or read from and 'D' is the data being written.

Figure 27:

Bank Selection Example Sequence

| # | Action              | Effect                                                                       |  |  |

|---|---------------------|------------------------------------------------------------------------------|--|--|

| 1 | WRITE(Addr=0, D=0)  | Set BANK_SEL to 0 (Point to BANK 0)                                          |  |  |

| 2 | WRITE(Addr=12, D=3) | BANK_SEL points to bank 0 Write value 3 to NROF_FRAMES register              |  |  |

| 3 | WRITE(Addr=79,D=1)  | BANK_SEL points to bank 0 Write value of 1 to 8 lowest bits of TRAINING_WORD |  |  |

| # | Action                                  | Effect                                                                                                                          |  |  |  |  |

|---|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 4 | WRITE(Addr=80,D=2)                      | BANK_SEL points to bank 0 Write value of 2 to highest bits of TRAINING_WORD Completes full 14-bit register: TRAINING_WORD = 513 |  |  |  |  |

| 5 | WRITE(Addr=79, D=8;1;3)<br>burst upload | BANK_SEL points to bank 0 Write 8 to LSBs of TRAINING_WORD Write 1 to MSBs of TRAINING_WORD Write 3 to TEST_LVDS                |  |  |  |  |

| 6 | WRITE(Addr=0, D=0)                      | Set BANK_SEL to 0 (Point to BANK 0)                                                                                             |  |  |  |  |

| 7 | READ(Addr=81)                           | Reads TEST_LVDS (result = 3)                                                                                                    |  |  |  |  |

#### **Register Categories**

The registers are grouped into various categories, based on when they may or may not be updated. The category for every individual register can be found in section 8. The table below explains the details of the various categories.

Figure 28: Register Categories

| Category | Description                                                                                                                                                                                                             |  |  |  |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| -        | Registers without category can be changed at any time, but might directly influence the sensor execution.                                                                                                               |  |  |  |

| SYNC     | Registers are internally synchronized to start of frame (at the start of the GLOB state), so an entire frame is always read with the same SYNC configuration. This means that the registers may be updated at any time. |  |  |  |

| FRAME    | Registers controlling the frame and exposure timing. These are only checked at the rising edge of REQ_EXP and may be updated at any time during operation.                                                              |  |  |  |

| DC       | Can only be changed when sensor is in IDLE state, or in soft reset state.                                                                                                                                               |  |  |  |

| RST      | Only to be changed when sensor is in soft reset state.                                                                                                                                                                  |  |  |  |

| RO       | Read-only register. All write operations are ignored.                                                                                                                                                                   |  |  |  |

Reading from a register is always allowed. When reading registers of category 'SYNC', the last previously uploaded value is read. This is NOT necessarily the same as the active frame-synchronized value.

Figure 29: Frame Sync

| Reg. Name         | Bank | Addr | Bits | Def. | Description                           |

|-------------------|------|------|------|------|---------------------------------------|

| DISABLE_FRAMESYNC | 0    | 1    | [0]  | 0    | 0: Enable<br>1: Disable               |

| PARAM_HOLD        | 0    | 2    | [0]  | 0    | 0: Frame sync<br>1: During SPI upload |

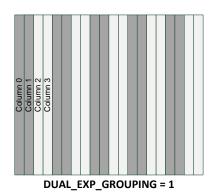

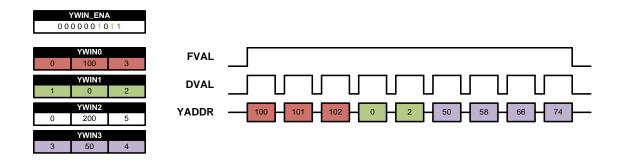

The upload of 'SYNC' type registers can be constrained with the following registers:

If **DISABLE\_FRAMESYNC** is set to '1', frame synchronization is disabled. Any uploads will take effect immediately.

Frame synchronization only happens if **PARAM\_HOLD** is '0'. When uploading a bunch of SYNC-type registers together (for example, change a number of different YWIN settings), it's advised to set **PARAM\_HOLD** to '1' during the entire upload. This prevents a frame from being started with only half of the required updates in case the frame start happened when the entire upload had not completed.

#### 7.2.6 Soft Reset

Figure 30: Soft Reset Register

| Reg. name                | В | Addr | Bits | Description          |

|--------------------------|---|------|------|----------------------|

| CMD_REGS. CMD_RST_SOFT_N | 0 | 3    | [0]  | Use calculated value |

The sensor has an asynchronous reset input pin (RST\_N) and an asynchronous reset register (CMD\_RST\_SOFT\_N). Both are active-low.

When combined, they have the following function:

- RST\_N: Reset the entire sensor when low. This is considered a hard reset.

- CMD\_RST\_SOFT\_N: Reset the entire sensor, except the SPI interface and register bank when low. This is considered a soft reset.

As long as RST\_N is high, all registers retain their value when CMD\_RST\_SOFT\_N is low.

The procedures to assert and release soft reset are described in detail in section 7.4.2.

#### 7.2.7 Controlling Exposure and Readout

This section explains the different ways the exposure of a frame can be started and ended. First some important concepts of the frame timing model are explained.

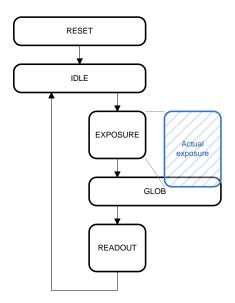

#### **Basic Frame Timing**

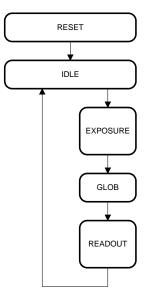

During operation, the sensor can be in any of the following states:

- RESET: asynchronous sensor reset is low, disabling the sensor entirely

- IDLE: sensor is not doing anything while waiting for external requests

- EXPOSURE: light is being integrated in the pixels

- GLOB: closing global shutter by sampling all integrated pixel values

- READOUT: reading out the acquired frame plus meta data and mandatory overhead

The sensor always exits a general sensor RESET condition in the IDLE state. This means that the sensor always acts as a slave, responding to external controls.

A distinction can be made between two basic frame timing operations (sequential and pipelined operation), as detailed in the following two sections.

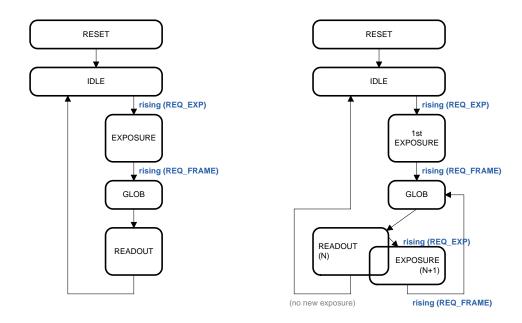

#### **Sequential Operation**

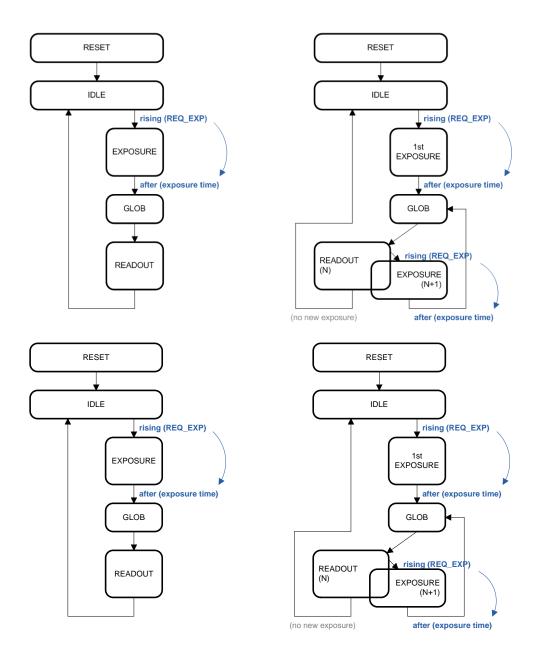

In sequential operation, the sensor goes through a sequential succession of EXPOSURE - GLOB - READOUT to grab a single image, as indicated in the figure below. When a cycle like this has been completed, the sensor is again in an IDLE state, waiting for new commands.

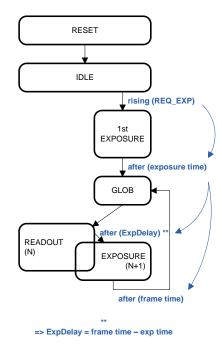

Figure 31:

**State Chart: Sequential Operation**

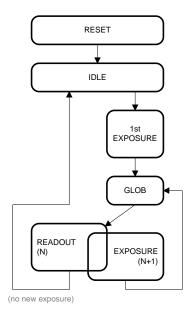

#### **Pipelined Operation**

The main property of pipelined operation is that the sensor can be in the EXPOSURE state and READOUT state at the same time. This basically means that the readout of frame N can be busy while

the EXPOSURE state of frame N+1 has already started. The EXPOSURE can fully or partially overlap with a READOUT state.

Figure 32:

**State Chart: Pipelined Operation**

When exiting IDLE state, the first EXPOSURE period starts. Just like in the sequential operation, this flows into a GLOB state, which in its turn starts the READOUT of a frame. Depending on the sensor control or configuration (see 7.2.7 and 7.2.8 for details and options), a new EXPOSURE may start when the READOUT is still busy.

At the end of the READOUT period, there are two options:

- No new EXPOSURE got started. The sensor will return to IDLE.

- A new EXPOSURE did get started. The sensor will wait until this new EXPOSURE finishes, before moving back to GLOB, which will always trigger a new READOUT.

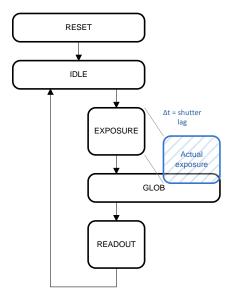

#### **Shutter Lag**

Figure 33: No Shutter Lag Register

| Reg. Name      | В | Addr | Bits | Def. | Description                      |

|----------------|---|------|------|------|----------------------------------|

| NO_SHUTTER_LAG | 0 | 117  | [0]  | 0    | 0: Shutter lag 1: No shutter lag |

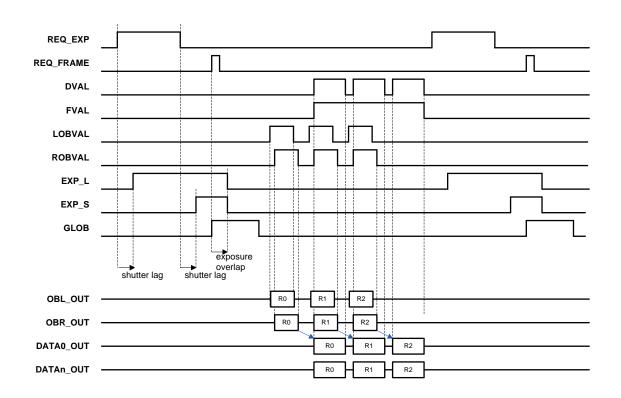

By default, the sensor always has a shutter lag. This effectively means that there is a delay between the start and end of **EXPOSURE state** and the start and end of the **actual exposure** (actual exposure = time where sensor is actually capturing and integrating light). This is illustrated in the figure below.

Figure 34: State Diagram: Sequential Operation with Shutter Lag

The distinction is important because:

- The EXPOSURE state is the direct response of external control (through sensor I/O requests or register settings),

- Yet it is the actual exposure that really matters to the user

In the remainder of the document, when the concept of exposure or exposure time is mentioned, it will always be about the **EXPOSURE state**, unless stated otherwise. The reader should always bear in mind that the **actual exposure** is delayed in time with respect to this EXPOSURE state due to the shutter lag mechanism.

In Figure 34 the shutter lag is shown under sequential operating conditions only, but note however that the shutter lag is present in all operation modes.

The shutter lag is always present at the end of the EXPOSURE period: part of the actual exposure time will always extend into the GLOB state (sometimes called "exposure overlap"). The shutter lag at the beginning of the EXPOSURE periods is introduced artificially to compensate for this exposure overlap.

If the shutter lag at the start of EXPOSURE is not allowed in certain applications, it can be disabled by setting register **NO\_SHUTTER\_LAG** high. This means that the actual exposure will start together with the start of the EXPOSURE state (practically: "immediately after an exposure request"). The

disadvantage of this is obviously that the length of the actual exposure time is not the same as the length of the EXPOSURE state (the "exposure overlap" needs to be added).

Figure 35:

State Diagram: Sequential Operation, no Shutter Lag at Start

## 7.2.8 Sensor Control Modes

Figure 36: Control Mode Register

| Reg. Name | Bank | Addr | Bits  | Def. | Description                             |

|-----------|------|------|-------|------|-----------------------------------------|

| CTRL_MODE | 0    | 9    | [2:0] | 0    | 0: Full external 1: Programmed external |

|           |      |      |       |      | 2: Triggered internal                   |

|           |      |      |       |      | 3: Streaming                            |

The travel through the state diagrams of Figure 34 and Figure 35 can be externally controlled with the sensor inputs REQ\_EXP and REQ\_FRAME and a bunch of register settings (which will be detailed in further sections). This can be done in a number of different modes (each varying slightly in behavior and level of dependency on I/O control versus register configuration).

The control mode is set with the CTRL\_MODE register, as listed in Figure 37.

Figure 37: Control Modes

| CTRL MODE | Name                | External Control                                       | Internal Control                                                  |

|-----------|---------------------|--------------------------------------------------------|-------------------------------------------------------------------|

| 0         | Full external       | Start of exposure. End of exposure (starting readout). | Readout details.                                                  |

| 1         | Programmed external | Start of exposure.                                     | Length of exposure. Readout details.                              |

| 2         | Triggered internal  | A finite sequence of 1 or more consecutive frames.     | Length of exposure. Frame rate. Sequence length. Readout details. |

| 3         | Streaming           | An infinite sequence of consecutive frames.            | Length of exposure. Frame rate. Readout details.                  |

Each of these control modes is introduced in one of the following sections.

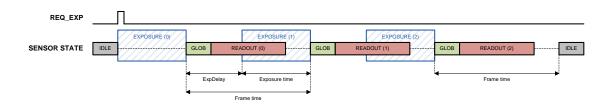

#### **Control Mode 0: Full External**

In the Full External control mode, the exposure timing is fully controlled with the sensor input pins:

- A rising edge on REQ\_EXP moves the sensor to the EXPOSURE state

- A rising edge on REQ\_FRAME moves the sensor to the GLOB state, which will be automatically followed by READOUT.

The length of the EXPOSURE state will exactly match the time between the rising edges of both triggers.

In the figure below, the state diagrams of sequential and pipelined operation are annotated with the external control events.

Figure 38:

State Diagram: Full External Mode

The length of the GLOB state, as well as the length of the READOUT period depends on a number of register settings.

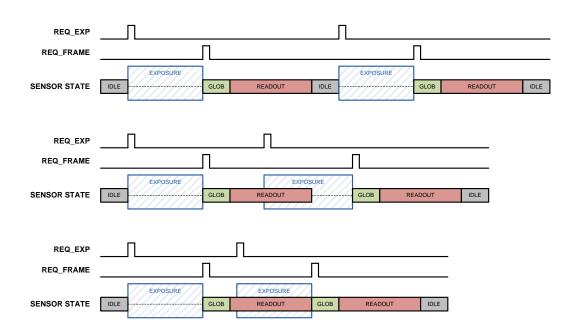

The state diagram is expanded into a timing diagram for a few situations in the figure below.

Figure 39 : Timing Diagram: Full External Mode

The figure shows how the Full External control mode can be used to (from top to bottom):

- Operate the sensor in Sequential Operation mode.

- Operate the sensor in *Pipelined Operation* mode, with the parallel exposure extending beyond the readout phase.

- Operate the sensor in *Pipelined Operation* mode, with the parallel exposure ending together with the readout phase (gives maximum frame rate).

Except for the invalid timings listed in Figure 40, the requests on REQ\_EXP and REQ\_FRAME can be freely placed anywhere by the external controller. This will result in the most flexible external control possible with this sensor (start and end exposure at any possible time, freely vary exposure time from frame to frame, interrupt frames being read to start a new readout...).

Figure 40: Full External Mode: Invalid Control Timing

| #     | Invalid Control Timing                              | Sensor Response                                                                                                                                 |

|-------|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| FE_i0 | REQ_EXP during GLOB                                 | Will disrupt the GLOB execution, causing the READOUT that naturally follows the GLOB phase to contain corrupted data.                           |

| FE_i1 | REQ_FRAME during GLOB                               | Will initiate a new GLOB, followed by READOUT. Image data in this READOUT will be corrupt.                                                      |

| FE_i2 | 2 consecutive REQ_FRAME, without REQ_EXP in between | Second REQ_FRAME will initiate GLOB followed by READOUT. Since there has not been EXPOSURE, the image data in the second frame will be corrupt. |

| FE_i3 | REQ_FRAME when sensor is IDLE                       | Same as above: READOUT without EXPOSURE results in corrupted image.                                                                             |

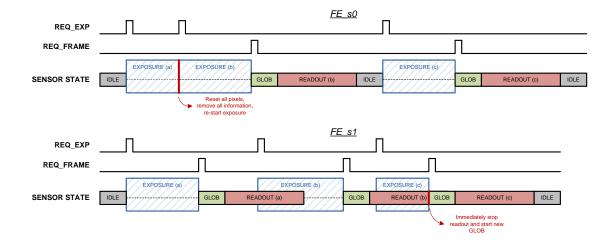

The table below lists some special cases that are not part of the table above and are therefore not illegal (though they each do have some consequences)

Figure 41: Full External Mode: Special Control Timing

| #     | Special Control Timing      | Sensor Response                                                                                                                                                                                                                                                          |

|-------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FE_s0 | REQ_EXP during<br>EXPOSURE  | Will initiate a new EXPOSURE, erasing all previously integrated information. The next REQ_FRAME will initiate a GLOB+READOUT that will contain image data of only the second EXPOSURE.                                                                                   |

| FE_s1 | REQ_FRAME during<br>READOUT | Will immediately interrupt the active READOUT to start a new GLOB, followed by a new READOUT. The image information of the first READOUT which had not been read will be forever lost. The new READOUT will be complete and correct (if not violating FE_i2, Figure 40). |

The figure below shows an example of the cases listed in Figure 41.

Figure 42 :

Timing Diagram: Special Control Timing in Full External Mode

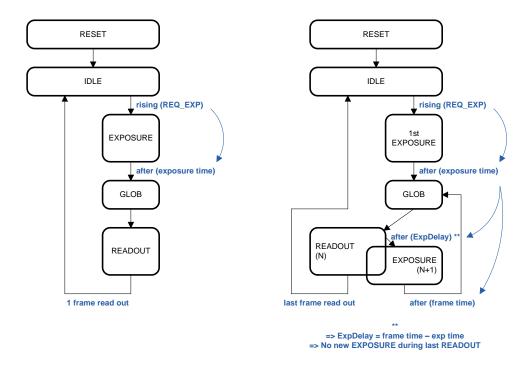

## **Control Mode 1: Programmed External**

This control mode is quite similar to the *Full External* mode, with the exception that the transition from EXPOSURE to GLOB state is not triggered by a pulse on REQ\_FRAME sensor input. Instead the sensor ends the EXPOSURE period and moves to GLOB after a programmable time, set by register upload. This behavior is illustrated in the figure below.

Figure 43 : State Diagram: Programmed External Mode

Expanding this to a timing diagram gives similar timings to the ones shown in Figure 39 with REQ\_FRAME continuously low.

Since this mode is so similar to the *Full External* mode, also the lists of invalid and special control timing are quite similar.

Figure 44:

Programmed External Mode: Invalid and Special Control Timing

| #     | Invalid Control Timing            | Sensor Response        |

|-------|-----------------------------------|------------------------|

| PE_i0 | REQ_EXP during GLOB               | Same response as FE_i0 |

| PE_i1 | EXPOSURE time expires during GLOB | Same response as FE_i1 |

| #     | Special Control Timing               | Sensor Response        |

|-------|--------------------------------------|------------------------|

| PE_s0 | REQ_EXP during EXPOSURE              | Same response as FE_s0 |

| PE_s1 | EXPOSURE time expires during READOUT | Same response as FE_s1 |

| PE_s2 | Any pulse on REQ_FRAME               | Will be ignored        |

## **Control Mode 2: Triggered Internal**

Both external control modes have in common that every external request results in exactly one sensor response:

- In Full External mode:

- Each REQ\_EXP initiates 1 EXPOSURE period

- Each REQ\_FRAME initiates 1 GLOB period, followed by READOUT

- In Programmed External mode:

- Each REQ\_EXP initiates the complete readout of 1 frame (EXPOSURE, GLOB and READOUT).

This means that in those two modes, the frame rate is fully controlled externally by timing the requests.

In the *Triggered Internal* mode, a single request is followed by a programmable number of frames, at a frame rate also set by register upload.

Figure 45 : State Diagram: Triggered Internal Mode

When exiting IDLE mode, the behavior is identical to Programmed External mode: a rising edge on REQ\_EXP will initiate the EXPOSURE state, which ends after a register defined exposure time. When the exposure time expires, a GLOB state is started, followed by READOUT.

The behavior during the READOUT phase depends on the number of frames that were requested (also set by register) and the amount of frames that have already been read during the active sequence:

- Last READOUT of requested sequence:

- Finish active READOUT and move back to IDLE state

- All other READOUT:

- Restart EXPOSURE for the next frame. EXPOSURE is started at the correct moment to make it finish exactly 'frame time' later than the GLOB period was started.

- The end of this EXPOSURE will initiate a new GLOB phase.

- Because a GLOB period immediately follows the EXPOSURE period, there will be exactly 'frame time' delay between two consecutive frames.

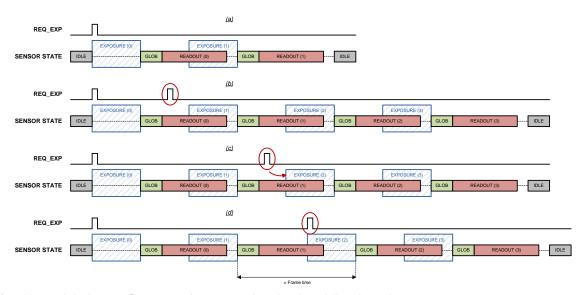

An example (with 3 frames requested) is shown in the figure below.

Figure 46:

**Timing Diagram: Triggered Internal Mode**

In the example, the programmed 'frame time' is longer than the sum of GLOB length and READOUT length. This situation is allowed and provides an easy mechanism to fine-tune frame rate.

In the most extreme case, the programmed frame time exactly matches the minimum length of the GLOB and READOUT phases together. This will start a new GLOB period as soon as the previous READOUT is finished, which results in the maximum frame rate for given GLOB and READOUT settings.

Because this mode is internally controlled based on register settings, there are no invalid control timing conditions. Invalid register settings do exist (for example: frame time shorter than GLOB+READOUT length), but these are specified in the relevant sections describing those registers later in this document.

The table below lists the special timing conditions of this mode.

Figure 47:

Triggered Internal Mode: Special Control Timing

| #     | Special Control Timing                                     | Sensor Response                                                                                                                                                                |

|-------|------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TI_s0 | REQ_EXP <i>before</i> last READOUT of sequence has started | Will do nothing else than increase the sequence length (add the number of frames of the new request to the total length of this sequence, with a maximum total of 255 frames). |

| TI_s1 | REQ_EXP <i>after</i> last READOUT of sequence has started  | Will initiate a new 'first' EXPOSURE, followed by a complete new sequence. Depending on the timing of the new request, the frame rate may be temporally change. See below.     |

| TI_s2 | Any pulse on REQ_FRAME                                     | Will be ignored                                                                                                                                                                |

The behavior in case of TI\_s1 depends on the relation between (1) the programmed exposure time of the new request and (2) the time remaining to complete the active frame (see last 'Frame time' in Figure 46).

- If (1) < (2):</li>

- The start of the new EXPOSURE will be delayed.

- It will be started at the correct moment so its end will coincide with the end of the active frame.

- The frame rate will not change: the first GLOB of the new sequence will be exactly 'frame time' after the last GLOB of the active sequence.

- If (1) > (2)

- The new EXPOSURE will start immediately.

- Because (1) is larger than (2), this EXPOSURE will end after the last frame would have finished.

- This causes a temporary drop in frame rate.

The figure below shows the following cases (in all cases, the requested sequence is 2 frames long):

Figure 48 : Timing Diagram: Special Control Timing in Triggered Internal Mode

- (a) Normal timing → Capture 2 frames and go back to idle when done

- (b) TI\_s0 → New request before last frame is active; extend sequence length to 4

- (c)  $TI_s1$ , (1) < (2)  $\rightarrow$  New EXPOSURE delayed to guarantee programmed frame rate

- (d) TI\_s1, (1) > (2) → Temporary frame rate decrease to guarantee complete exposure time

## **Programmed External vs Triggered Internal**