# Standalone USB Type-C<sup>TM</sup> controller with high voltage protections

#### **Features**

- Type-C attach and cable orientation detection

- Power role support: source / sink / DRP

- · Configurable start-up profiles

- Integrated power switch for V<sub>CONN</sub> supply:

- Programmable current limit up to 600 mA

- Overcurrent, overvoltage and thermal protections

- Undervoltage lockout

- I<sup>2</sup>C interface and interrupt (optional connection to MCU)

- Integrated V<sub>BUS</sub> voltage monitoring

- Integrated V<sub>BUS</sub> and V<sub>CONN</sub> discharge path

- Short-to-VBUS protection on CC pins (22 V) and VBUS pins (28 V)

- · Dead-battery mode support

- Accessory mode support

- High and/or low voltage power supply:

- V<sub>SYS</sub> = [3.0 V; 5.5 V]

- V<sub>DD</sub> = [4.1 V; 22 V]

- ESD: 4 kV HBM 1.5 kV CDM

- Temperature range: -40 °C up to 105 °C

- Certification test ID: 1000100

# Product status link STUSB1600

| Dev         | ice summary                                                                         |

|-------------|-------------------------------------------------------------------------------------|

| Order code  | STUSB1600AQTR                                                                       |

| Description | Standalone USB Type-<br>C <sup>TM</sup> controller with high<br>voltage protections |

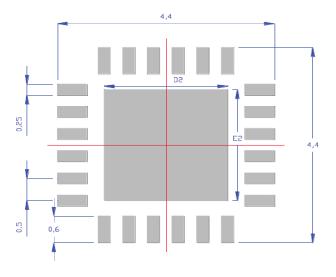

| Package     | QFN24 EP 4x4 mm                                                                     |

| Marking     | 1600A                                                                               |

# **Applications**

- Smart plugs, wall adapters, chargers

- Power hubs and docking stations

- · Smartphones and tablets

- Gaming and PNDs

- Displays

- Wearable and Internet of Things (IoT)

- Cameras, camcorders, MP3 players

- Any Type-C source or sink device

## **Description**

The STUSB1600 is an IC controller, fully compliant with the USB Type-C cable and connector specification (rev. 1.2), which addresses 5 V USB Type-C port management both on the host and/or device side. It is designed for a broad range of applications and can handle the following USB Type-C functions: attach detection, plug orientation detection, host to device connection, VCONN support, and  $V_{BUS}$  configuration. Thanks to its 20 V technology, it implements high voltage protection features against short-circuits to  $V_{BUS}$  up to 28 V. The device supports dead battery mode and is fully customizable thanks to an integrated non-volatile memory.

# 1 Functional description

The STUSB1600 is a USB Type-C controller IC. It is designed to interface with the Type-C receptacle both on host and/or device sides. It is used to establish and manage the source-to-sink connection between two USB Type-C host and device ports.

The STUSB1600 major role is to:

- 1. Detect the connection between two USB Type-C ports (attach detection)

- 2. Establish a valid source-to-sink connection

- 3. Determine the attached device mode: source, sink or accessory

- 4. Resolve cable orientation and twist connections to establish USB data routing (MUX control)

- 5. Configure and monitor V<sub>BUS</sub> power path

- 6. Manage V<sub>BUS</sub> power capability: USB Default, Type-C medium or Type-C high current mode

- 7. Configure V<sub>CONN</sub> when required

The STUSB1600 also provides:

- 1. Low power standby mode

- 2. Dead-battery mode

- 3. I<sup>2</sup>C interface and interrupt (optional connection to MCU)

- 4. Start-up configuration customization: static through NVM or/and dynamic through I<sup>2</sup>C

- 5. High voltage protection

- 6. Accessory modes detection

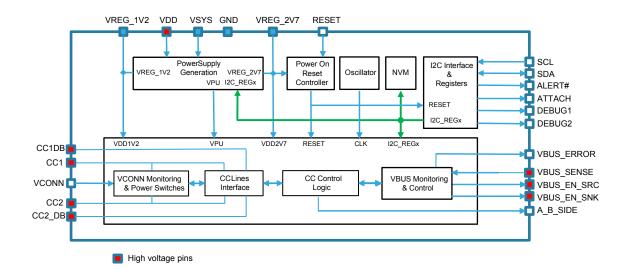

# 1.1 Block overview

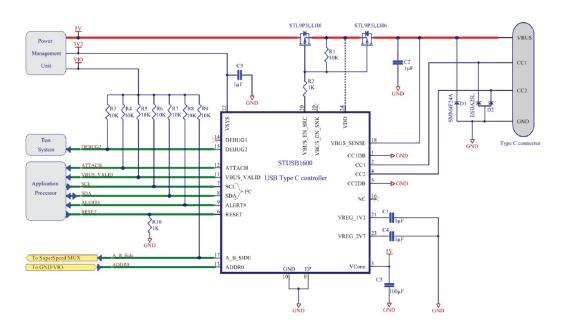

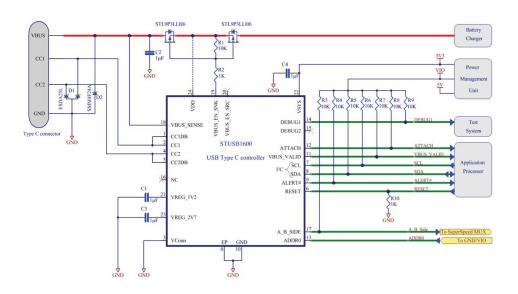

Figure 1. Functional block diagram

DS11503 - Rev 4 page 2/66

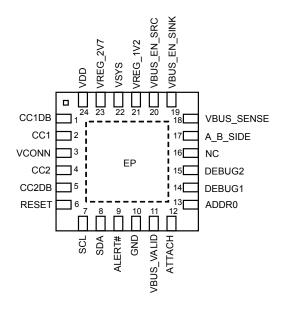

# 2 Inputs / outputs

# 2.1 Pinout

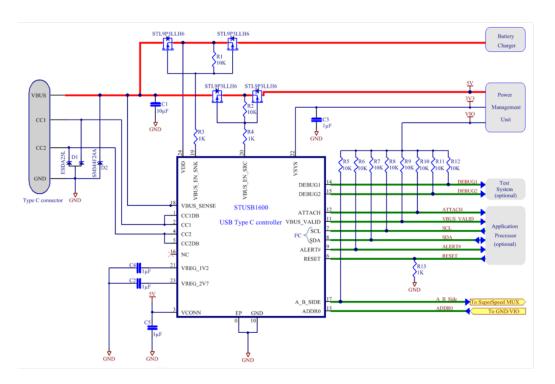

Figure 2. STUSB1600 pin connections

DS11503 - Rev 4 page 3/66

# 2.2 Pin list

**Table 1. Pin functions list**

| Pin | Name        | Туре   | Description                                                                        | Typical connection                               |  |

|-----|-------------|--------|------------------------------------------------------------------------------------|--------------------------------------------------|--|

| 1   | CC1DB       | HV AIO | Dead-battery enable on CC1 pin                                                     | CC1 pin if used or ground                        |  |

| 2   | CC1         | HV AIO | Type-C configuration channel 1                                                     | Type-C receptacle A5                             |  |

| 3   | VCONN       | PWR    | Power input for active plug                                                        | 5 V power source                                 |  |

| 4   | CC2         | HV AIO | Type-C Configuration Channel 2                                                     | Type-C receptacle B5                             |  |

| 5   | CC2DB       | HV AIO | Dead-battery enable on CC2 pin                                                     | CC2 pin if used or ground                        |  |

| 6   | RESET       | DI     | Reset input (active high)                                                          |                                                  |  |

| 7   | SCL         | DI     | I <sup>2</sup> C clock input                                                       | To I <sup>2</sup> C master, ext. pull-up         |  |

| 8   | SDA         | DI/OD  | I <sup>2</sup> C data input/output – active low open-drain                         | To I <sup>2</sup> C master, ext. pull-up         |  |

| 9   | ALERT#      | OD     | I <sup>2</sup> C interrupt – active low open-drain                                 | To I <sup>2</sup> C master, ext. pull-up         |  |

| 10  | GND         | GND    | Ground                                                                             | Ground                                           |  |

| 11  | VBUS_VALID  | OD     | V <sub>BUS</sub> detection, active low open-drain                                  | To MCU if any, ext. pull-up                      |  |

| 12  | ATTACH      | OD     | Attachment detection, active low open-drain                                        | To MCU if any, ext. pull-up                      |  |

| 13  | ADDR0       | DI     | I <sup>2</sup> C device address setting (see Section 4 I <sup>2</sup> C interface) | Static                                           |  |

| 14  | DEBUG1      | OD     | Debug accessory device detection in sink power role, active low open-drain         | To MCU if any, ext. pull-up                      |  |

| 15  | DEBUG2      | OD     | Debug accessory device detection in source power role, active low open-drain       | To MCU if any, ext. pull-up                      |  |

| 16  | NC          | -      | -                                                                                  | Floating                                         |  |

| 17  | A_B_SIDE    | OD     | Cable orientation, active low open-drain                                           | USB SuperSpeed mux select – Ext. pull-up         |  |

| 18  | VBUS_SENSE  | HV AI  | V <sub>BUS</sub> voltage monitoring and discharge path                             | From V <sub>BU</sub> s                           |  |

| 19  | VBUS_EN_SNK | HV OD  | V <sub>BUS</sub> sink power path enable, active low opendrain                      | To switch or power system, ext. pull-up          |  |

| 20  | VBUS_EN_SRC | HV OD  | V <sub>BUS</sub> source power path enable, active low open-drain                   | To switch or power system, ext. pull-up          |  |

| 21  | VREG_1V2    | PWR    | 1.2 V internal regulator output                                                    | 1 μF typ. decoupling capacitor                   |  |

| 22  | VSYS        | PWR    | Power supply from system                                                           | From power system, connect to ground if not used |  |

| 23  | VREG_2V7    | PWR    | 2.7 V internal regulator output                                                    | 1 μF typ. decoupling capacitor                   |  |

| 24  | VDD         | HV PWR | Power supply from USB power line                                                   | From V <sub>BUS</sub>                            |  |

|     | EP          | GND    | Exposed pad is connected to ground                                                 | To ground                                        |  |

DS11503 - Rev 4 page 4/66

Table 2. Legend

| Туре | Description       |  |  |

|------|-------------------|--|--|

| D    | Digital           |  |  |

| Α    | Analog            |  |  |

| 0    | Output pad        |  |  |

| I    | Input pad         |  |  |

| IO   | Bidirectional pad |  |  |

| OD   | Open-drain output |  |  |

| PD   | Pull-down         |  |  |

| PU   | Pull-up           |  |  |

| HV   | HIGH VOLTAGE      |  |  |

| PWR  | Power             |  |  |

| GND  | Ground            |  |  |

# 2.3 Pin description

#### 2.3.1 CC1 / CC2

CC1 and CC2 are the configuration channel pins used for the connection and attachment detection, plug orientation determination and system configuration management across USB Type-C cable.

# 2.3.2 CC1DB / CC2DB

CC1DB and CC2DB are used for dead-battery mode when the STUSB1600 is configured in sink power role or dual power role. This mode is enabled by connecting CC1DB and CC2DB respectively to CC1 and CC2. Thanks to this connection, the pull-down terminations on the CC pins are present by default even if the device is not supplied (see Section 3.5 Dead-battery mode).

Note: CC1DB and CC2DB must be connected to ground when the STUSB1600 is configured in source power role or when the dead-battery mode is not supported.

# 2.3.3 VCONN

This power input is connected to a power source that can be a 5 V power supply, or a lithium battery. It is used to provide power supply to the local plug. It is internally connected to power switches that are protected against short-circuit and overvoltage. This does not require any protection on the input side. When a valid source-to-sink connection is determined and V<sub>CONN</sub> power switches are enabled, V<sub>CONN</sub> is provided by the source to the unused CC pin (see Section 3.3 VCONN supply).

# 2.3.4 **RESET**

Active high reset.

DS11503 - Rev 4 page 5/66

### 2.3.5 I<sup>2</sup>C interface pins

Table 3. I<sup>2</sup>C interface pin list

| Name   | Description                                                                    |  |  |  |

|--------|--------------------------------------------------------------------------------|--|--|--|

| SCL    | C clock, need external pull-up                                                 |  |  |  |

| SDA    | <sup>2</sup> C data, need external pull-up                                     |  |  |  |

| ALERT# | <sup>2</sup> C interrupt, need external pull-up                                |  |  |  |

| ADDR0  | I <sup>2</sup> C device address bit (see Section 4 I <sup>2</sup> C interface) |  |  |  |

#### 2.3.6 GND

Ground.

### 2.3.7 VBUS\_VALID

This pin is asserted during attachment when  $V_{BUS}$  is detected on VBUS\_SENSE pin and  $V_{BUS}$  voltage is within the valid operating range. The  $V_{BUS}$  valid state is also advertised in a dedicated I<sup>2</sup>C register bit (see Section 5.1 Register description).

# 2.3.8 ATTACH

This pin is asserted when a valid source-to-sink connection is established. It is also asserted when a connection to an accessory device is detected. The attachment state is also advertised in a dedicated I<sup>2</sup>C register bit (see Section 5.1 Register description).

### 2.3.9 DEBUG pins

These pins are asserted when a debug accessory device is detected according to the running power role.

Table 4. Debug pin list

| Name   | Description                                                                                                            |  |  |  |  |

|--------|------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| DEBUG1 | Asserted when Type-C FSM is in DebugAccessory.SNK state in sink power role                                             |  |  |  |  |

| DEBUG2 | Asserted when Type-C FSM is in UnorientedDebugAccessory. SRC or OrientedDebugAccessory.SRC states in source power role |  |  |  |  |

# 2.3.10 A\_B\_SIDE

This output pin provides cable orientation. It is used to establish USB SuperSpeed signal routing. The cable orientation is also advertised in a dedicated I<sup>2</sup>C register bit. (see Section 5.1 Register description). This signal is not required in case of USB 2.0 support.

Table 5, USB data MUX select

| Value | CC pin position                |

|-------|--------------------------------|

| HiZ   | CC1 pin is attached to CC line |

| 0     | CC2 pin is attached to CC line |

### 2.3.11 VBUS\_SENSE

This input pin is used to sense  $V_{BUS}$  presence, monitor  $V_{BUS}$  voltage and discharge  $V_{BUS}$  on USB Type-C receptacle side.

DS11503 - Rev 4 page 6/66

### 2.3.12 VBUS\_EN\_SNK

In sink power role, this pin allows the incoming  $V_{BUS}$  power to be enabled when the connection to a source is established and  $V_{BUS}$  is in the valid operating range. The open-drain output allows a PMOS transistor to be driven directly. The logic value of the pin is also advertised in a dedicated  $I^2C$  register bit (see Section 5.1 Register description).

### 2.3.13 VBUS\_EN\_SRC

In source power role, this pin allows the outgoing  $V_{BUS}$  power to be enabled when the connection to a sink is established and  $V_{BUS}$  is in the valid operating range. The open-drain output allows a PMOS transistor to be driven directly. The logic value of the pin is also advertised in a dedicated  $I^2C$  register bit (see Section 5.1 Register description).

#### 2.3.14 VREG\_1V2

This pin is used only for external decoupling of 1.2 V internal regulator. The recommended decoupling capacitor:  $1 \mu F$  typ. (0.5  $\mu F$  min.; 10  $\mu F$  max.).

#### 2.3.15 VSYS

This is the low power supply from the system, if any. It can be connected directly to a single cell lithium battery or to the system power supply delivering 3.3 V or 5 V. It is recommended to connect the pin to ground when it is not used.

### 2.3.16 VREG\_2V7

This pin is used only for external decoupling of 2.7 V internal regulator. The recommended decoupling capacitor:  $1 \mu F$  typ. (0.5  $\mu F$  min.; 10  $\mu F$  max.).

#### 2.3.17 VDD

This is the main power supply for applications powered by V<sub>BUS</sub>.

In source power role, this pin can be used to sense the voltage level of the main power supply providing  $V_{BUS}$ . It allows UVLO and OVLO thresholds to be considered independently on VDD pin as additional conditions to enable the  $V_{BUS}$  power path through VBUS\_EN\_SRC pin (see Section 3.2.3 VBUS power path assertion). When UVLO threshold detection is enabled, the VDD pin must be connected to the main power supply to establish the connection and to assert the  $V_{BUS}$  power path.

DS11503 - Rev 4 page 7/66

# 3 Features description

### 3.1 CC interface

The STUSB1600 controls the connection to the configuration channel (CC) pins, CC1 and CC2, through two main blocks, the CC lines interface block and the CC control logic block.

The CC line interface block is used to:

- Configure the termination mode on the CC pins relative to the power mode supported, i.e. pull-up for source power role and pull-down for sink power role

- · Monitor the CC pin voltage values relative to the attachment detection thresholds

- Configure  $V_{CONN}$  on the unconnected CC pin when required

- · Protect the CC pins against overvoltage

The CC control logic block is used to:

- Execute the Type-C FSM relative to the Type-C power mode supported

- Determine the electrical state for each CC pin relative to the detected thresholds

- Evaluate the conditions relative to the CC pin states and V<sub>BUS</sub> voltage value to transition from one state to another in the Type-C FSM

- Detect and establish a valid source-to-sink connection

- Determine the attached device mode: source, sink or accessory

- Determine cable orientation to allow external routing of the USB data

- Manage V<sub>BUS</sub> power capability: USB default, Type-C medium or Type-C high current mode

- Handle hardware faults

The CC control logic block implements the Type-C FSMs corresponding to the following Type-C power modes:

- · Source power role with accessory support

- Sink power role with accessory support

- Sink power role without accessory support

- Dual power role with accessory support

- Dual power role with accessory and Try.SRC support

- Dual power role with accessory and Try.SNK support

The default Type-C power mode is selected through NVM programming (see Section 6 Start-up configuration) and can be changed by software during operation through I<sup>2</sup>C interface (see Section 5.1 Register description).

# 3.2 V<sub>BUS</sub> power path control

### 3.2.1 V<sub>BUS</sub> monitoring

The V<sub>BUS</sub> monitoring block supervises (from the VBUS\_SENSE pin) the V<sub>BUS</sub> voltage on the USB Type-C receptacle side.

It is used to check that V<sub>BUS</sub> is within a valid voltage range:

- To establish a valid source-to-sink connection according to USB Type-C standard specifications

- To enable safely the V<sub>BUS</sub> power path through VBUS\_EN\_SRC pin or VBUS\_EN\_SNK pin depending on the power role

It allows detection of unexpected  $V_{BUS}$  voltage conditions such as: undervoltage or overvoltage relative to the valid  $V_{BUS}$  voltage range. When such conditions occurs, the STUSB1600 behaves as follows:

At attachment, it prevents the source-to-sink connection and the V<sub>BUS</sub> power path assertion

DS11503 - Rev 4 page 8/66

After attachment, it deactivates the source-to-sink connection and disables the V<sub>BUS</sub> power path. In source

power role, the device goes into error recovery state. In sink power role the device goes into unattached

state

The valid  $V_{BUS}$  voltage range is defined from  $V_{BUS}$  nominal voltage by a high threshold voltage and a low threshold voltage whose nominal values are respectively  $V_{BUS}+5\%$  and  $V_{BUS}-5\%$ . The nominal threshold limits can be shifted by a fraction of  $V_{BUS}$  from +1% to +15% for the high threshold voltage and from -1% to -15% for the low threshold voltage. It means the threshold limits can vary from  $V_{BUS}+5\%$  to  $V_{BUS}+20\%$  for the high limit and from  $V_{BUS}-5\%$  to  $V_{BUS}-20\%$  for the low limit.

The threshold limits are preset by default in the NVM with different shift coefficients depending on whether the device operates in source power role or sink power role (see Section 8.3 Electrical and timing characteristics). The threshold limits can be changed independently through NVM programming (see Section 6 Start-up configuration) and also by software during attachment through I<sup>2</sup>C interface (see Section 5.1 Section 4.4: Register description).

## 3.2.2 V<sub>BUS</sub> discharge

The monitoring block handles also the internal V<sub>BUS</sub> discharge path connected to the VBUS\_SENSE pin. The discharge path is activated at detachment, or when the device goes into the error recovery state whatever the power role (see Section 3.7 Hardware fault management).

The  $V_{BUS}$  discharge path is enabled by default in the NVM and can be disabled through NVM programming only (see Section 6 Start-up configuration). The discharge time duration is also preset by default in the NVM (see Section 8.3 Electrical and timing characteristics). The discharge time duration can be modified through NVM programming (see Section 6 Start-up configuration) and also by software through the I<sup>2</sup>C interface (see Section 5.1 Register description).

### 3.2.3 V<sub>BUS</sub> power path assertion

The STUSB1600 can control the assertion of the  $V_{BUS}$  power path on USB Type-C port, directly or indirectly, through VBUS\_EN\_SRC pin and VBUS\_EN\_SNK pins according to the system power role.

The following tables summarize the configurations of the STUSB1600 and the operation conditions that determine the electrical value of VBUS\_EN\_SRC pin and VBUS\_EN\_SNK pins during the system operation.

DS11503 - Rev 4 page 9/66

Table 6. Conditions for  $V_{\mbox{\scriptsize BUS}}$  power path assertion in source power role

|             | Electrical | Ope                                                                          | ration conditions                                                                                                                                           |                                                                                                                                                                                                                                       |                                                                                  |

|-------------|------------|------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| Pin         | value      | Type-C attached state                                                        | VDD pin monitoring                                                                                                                                          | VBUS_SENSE pin monitoring                                                                                                                                                                                                             | Comment                                                                          |

|             | 0          | Attached.SRC or UnorientedDebug Accessory.SRC or OrientedDebug Accessory.SRC | V <sub>DD</sub> > V <sub>DDUVLO</sub> if UVLO threshold detection enabled and/or  V <sub>DD</sub> < V <sub>DDOVLO</sub> if OVLO threshold detection enabled | V <sub>BUS</sub> < V <sub>MONUSBH</sub> and V <sub>BUS</sub> > V <sub>MONUSBL</sub> if V <sub>BUS</sub> voltage range detection enabled or V <sub>BUS</sub> > V <sub>THUSB</sub> if V <sub>BUS</sub> voltage range detection disabled | The signal is asserted only if all the valid operation conditions are met        |

| VBUS_EN_SRC | HiZ        | Any other state                                                              | V <sub>DD</sub> <v<sub>DDUVLO if UVLO threshold detection enabled and/or V<sub>DD</sub> &gt;V<sub>DDOVLO</sub> if OVLO threshold detection enabled</v<sub>  | V <sub>BUS</sub> > V <sub>MONUSBH</sub> or V <sub>BUS</sub> < V <sub>MONUSBL</sub> if V <sub>BUS</sub> voltage range detection enabled or V <sub>BUS</sub> < V <sub>THUSB</sub> if V <sub>BUS</sub> voltage range detection disabled  | The signal is de-asserted when at least one non-valid operation condition is met |

As specified in the USB Type-C standard specification, the attached state "Attached.SRC" is reached only if the voltage on  $V_{BUS}$  receptacle side is at vSafe0V condition when a connection is detected.

DS11503 - Rev 4 page 10/66

|             | Electrical | C                                            | peration condition    | ns                                                                                                                                                                                                                                    |                                                                                  |

|-------------|------------|----------------------------------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| Pin         | value      | Type-C attached state                        | VDD pin<br>monitoring | VBUS_SENSE pin monitoring                                                                                                                                                                                                             | Comment                                                                          |

|             | 0          | Attached.SNK<br>or<br>DebugAccessory.<br>SNK | Not applicable        | V <sub>BUS</sub> < V <sub>MONUSBH</sub> and V <sub>BUS</sub> > V <sub>MONUSBL</sub> if V <sub>BUS</sub> voltage range detection enabled or V <sub>BUS</sub> > V <sub>THUSB</sub> if V <sub>BUS</sub> voltage range detection disabled | The signal is asserted only if all the valid operation conditions are met        |

| VBUS_EN_SNK | HiZ        | Any other state                              | Not applicable        | VBUS > VMONUSBH  or  VBUS < VMONUSBL if VBUS voltage range detection enabled  or  VBUS < VTHUSB if VBUS voltage range detection disabled                                                                                              | The signal is de-asserted when at least one non-valid operation condition is met |

Table 7. Conditions for V<sub>BUS</sub> power path assertion in sink power role

"Type-C attached state" refers to the Type-C FSM states as defined in the USB Type-C standard specification and as described in I<sup>2</sup>C register CC\_OPERATION\_STATUS (see Section 5.1 Register description).

"VDD pin monitoring" is valid in source power role only. The activation of the UVLO and OVLO threshold detections can be done through NVM programming (see Section 6 Start-up configuration) and also by software through I<sup>2</sup>C interface (see Section 5.1 Register description). When UVLO and/or OVLO threshold detection is activated, VBUS\_EN\_SRC pin is asserted only if the device is attached and the valid threshold conditions on VDD are met. Once VBUS\_EN\_SRC pin is asserted, the V<sub>BUS</sub> monitoring is done on VBUS\_SENSE pin instead of VDD pin.

"VBUS\_SENSE pin monitoring" relies by default on the valid  $V_{BUS}$  voltage range defined by a high limit  $V_{MONUSBH}$  and a low limit  $V_{MONUSBL}$ . The voltage range conditions can be disabled to consider UVLO threshold detection instead. The monitoring conditions of  $V_{BUS}$  voltage can be changed through NVM programming (see Section 6 Start-up configuration) and also by software through  $I^2C$  interface (see Section 5.1 Register description).

See Section 8.3 Electrical and timing characteristics for the threshold voltage description and value on VDD and VBUS\_SENSE pins.

# 3.3 V<sub>CONN</sub> supply

#### 3.3.1 V<sub>CONN</sub> input voltage

$V_{CONN}$  is a regulated supply used to power circuits in the plug of USB3.1 full-featured cables and other accessories.  $V_{CONN}$  nominal operating voltage is 5.0 V  $\pm$  5%.

# 3.3.2 V<sub>CONN</sub> application conditions

The  $V_{CONN}$  pin of the STUSB1600 is connected to each CC pin (CC1 and CC2) across independent power switches.

The STUSB1600 applies  $V_{CONN}$  only to the CC pin not connected to the CC wire when all below conditions are met:

DS11503 - Rev 4 page 11/66

- The device is configured in source power role or dual power role

- V<sub>CONN</sub> power switches are enabled

- A valid connection to a sink is achieved

- Ra presence is detected on the unwired CC pin

- A valid power source is applied on V<sub>CONN</sub> pin with respect to a predefined UVLO threshold

The STUSB1600 does not provide V<sub>CONN</sub> when it works in sink power role.

# 3.3.3 V<sub>CONN</sub> monitoring

The  $V_{CONN}$  monitoring block detects if  $V_{CONN}$  power supply is available on the VCONN pin. It is used to check that  $V_{CONN}$  voltage is above a predefined undervoltage lockout (UVLO) threshold to allow  $V_{CONN}$  power switches to be enabled.

The default value of the UVLO threshold is 4.65 V typical for powered cables operating at 5 V. It can be changed by software to 2.65 V typical to support  $\text{V}_{\text{CONN}}$ -powered accessories that are operating down to 2.7 V (see Section 5.1 Register description).

# 3.3.4 V<sub>CONN</sub> discharge

The behavior of Type-C FSMs is extended with an internal V<sub>CONN</sub> discharge path capability on CC pins in source power mode only. The discharge path is activated during 250 ms from sink detachment detection. This feature is disabled by default and can be activated through NVM programming (see Section 6 Start-up configuration) and also by software through I<sup>2</sup>C interface (see Section 5.1 Register description).

# 3.3.5 V<sub>CONN</sub> control and status

The supplying conditions of  $V_{CONN}$  across the STUSB1600 are managed through the  $I^2C$  interface. Different  $I^2C$  registers and bits are used specifically for this purpose (see Section 5.1 Register description).

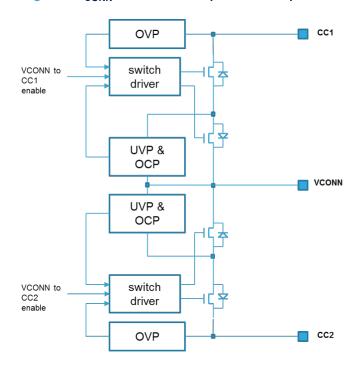

### 3.3.6 VCONN power switches

#### **Features**

The STUSB1600 integrates two current limited high-side power switches with protections that tolerate high voltage up to 22 V on the CC pins.

Each V<sub>CONN</sub> power switch presents the following features:

- · Soft-start to limit inrush current

- Constant current mode overcurrent protection

- · Adjustable current limit

- Thermal protection

- Undervoltage and overvoltage protection

- Reverse current and reverse voltage protections

DS11503 - Rev 4 page 12/66

Figure 3. V<sub>CONN</sub> to CC1 and CC2 power switch protections

# **Current limit programming**

The current limit can be set within the range 100 mA to 600 mA by step of 50 mA. The default current limit is programmed through NVM programming (see Section 6 Start-up configuration) and can be changed by software through I<sup>2</sup>C interface (see Section 5.1 Register description). At power-on or after a reset, the current limit takes the default value preset in the NVM.

#### **Fault management**

The table below summarizes the different fault conditions that could occur during the operation of the switch and the associated responses. An I<sup>2</sup>C alert is generated when a fault condition happens (see Section 5.1 Register description).

**Fault conditions** Fault types **Expected actions** CC output pin shorted to ground via Power switch limits the current and reduces the output voltage. I<sup>2</sup>C Short-circuit very low resistive path causing rapid alert is asserted immediately thanks to VCONN\_SW\_OCP\_FAULT current surge bits CC output pin connected to a load Power switch limits the current and reduces the output voltage. I<sup>2</sup>C Overcurrent that sinks current above alert is asserted immediately thanks to VCONN\_SW\_OCP\_FAULT programmed limit Power switch is disabled immediately until the temperature falls Junction temperature exceeding 145 below 145 ° minus hysteresis of 15 °C. I<sup>2</sup>C alert is asserted Overheating immediately thanks to THERMAL\_FAULT bit. The STUSB1600 goes °C due to any reason into transient error recovery state Power switch is disabled immediately until the input voltage rises V<sub>CONN</sub> input voltage drops below Undervoltage above the UVLO threshold. I<sup>2</sup>C alert is asserted immediately thanks UVLO threshold minus hysteresis to VCONN\_PRESENCE bit

Table 8. Fault management conditions

DS11503 - Rev 4 page 13/66

| Fault types     | Fault conditions                                                                                                             | Expected actions                                                                                                                                                                |  |  |

|-----------------|------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Overvoltage     | CC output pin voltage exceeds maximum operating limit of 6.0 V                                                               | Power switch is opened immediately until the voltage falls below the voltage limit. I <sup>2</sup> C alert is asserted immediately thanks to VCONN_SW_OVP_FAULT bits            |  |  |

| Reverse current | CC output pin voltage exceeds V <sub>CONN</sub> input voltage when the power switch is turned off                            | The reverse biased body diode of the back-to-back MOS switches is naturally disabled preventing current to flow from the CC output pin to the input                             |  |  |

| Reverse voltage | CC output pin voltage exceeds V <sub>CONN</sub> input voltage of more than 0.35 V for 5 V when the power switch is turned on | Power switch is opened immediately until the voltage difference falls below the voltage limit. I <sup>2</sup> C alert is asserted immediately thanks to VCONN_SW_RVP_FAULT bits |  |  |

# 3.4 Low power standby mode

The STUSB1600 proposes a standby mode to reduce the device power consumption when no device is connected to the USB Type-C port. It is disabled by default and can be activated through NVM programming (see Section 6 Start-up configuration).

When activated, the STUSB1600 enters standby mode at power-up, or after a reset, after a reset or after a disconnection. In this mode, the CC interface and the voltages monitoring blocks are turned off. Only a monitoring circuitry is maintained active on the CC pins to detect a connection. When the connection is detected, all the internal circuits are turned on to allow normal operations.

The standby mode does not operate when the device is configured in sink power role with accessory support (see Section 6 Start-up configuration).

# 3.5 Dead-battery mode

The dead-battery mode allows systems powered by a battery to be supplied by  $V_{BUS}$  when the battery is discharged and to start the battery charging process. It is also used in systems that are powered through  $V_{BUS}$  only.

This mode is only supported in sink power role and dual power role configurations. It operates only if the CC1DB and CC2DB pins are connected respectively to the CC1 and CC2 pins. Thanks to these connections, the STUSB1600 presents a pull-down termination on its CC pins and advertises itself as a sink even if the device is not supplied.

When a source system connects to a USB Type-C port with the STUSB1600 configured in dead-battery mode, it can detect the pull-down termination, establish the source-to-sink connection, and provide the  $V_{BUS}$ . The STUSB1600 is then supplied thanks to the VDD pin connected to the  $V_{BUS}$  on the USB Type-C receptacle side. The STUSB1600 can finalize the source-to-sink connection and enable the power path on the  $V_{BUS}$  thanks to the VBUS EN SNK pin which allows the system to be powered.

# 3.6 High voltage protection

The STUSB1600 can be used safely in systems or connected to systems that handle high voltage on the  $V_{BUS}$  power path. The device integrates an internal circuitry on the CC pins that tolerates high voltages and ensures a protection up to 22 V in case of unexpected short-circuit with  $V_{BUS}$  or in case of connection to a device supplying high voltage on  $V_{BUS}$ .

# 3.7 Hardware fault management

The STUSB1600 handles hardware fault conditions related to the device itself and to the  $V_{BUS}$  power path during the system operation.

When such conditions happens, the circuit goes into a transient error recovery state named ErrorRecovery in the Type-C FSM. The error recovery state is sufficient to force a detach event.

When entering this state, the device de-asserts the V<sub>BUS</sub> power path by disabling VBUS\_EN\_SRC pin and VBUS\_EN\_SNK pin, and it removes the terminations from the CC pins during few tens of milliseconds. Then it transits to the unattached state related to the configured power mode.

The STUSB1600 goes into error recovery state when at least one condition listed below is met:

DS11503 - Rev 4 page 14/66

- Whatever the power role:

- If an overtemperature is detected, the "THERMAL FAULT" bit set to 1b

- In source power role only:

- If an internal pull-up voltage on CC pins is below UVLO threshold (VPU VALID bit set to 0b)

- If an overvoltage is detected on the CC pins (VPU OVP FAULT bit set to 1b)

- If V<sub>BUS</sub> voltage is out of the valid voltage range during attachment (VBUS VALID bit set to 0b)

- If an undervoltage is detected on VDD pin during attachment when UVLO detection is enabled (VDD\_UVLO\_DISABLE bit set to 0b)

- If an overvoltage is detected on VDD pin during attachment when OVLO detection is enabled (VDD OVLO DISABLE bit set to 0b)

The I<sup>2</sup>C register bits above-mentioned give either the state of the hardware fault when it occurs, or the setting conditions to detect the hardware fault (see Section 5.1 Register description).

# 3.8 Accessory mode detection

The STUSB1600 supports the detection of audio accessory mode and debug accessory mode as defined in USB Type-C standard specification with the following Type-C power modes (see Section 6 Start-up configuration):

- · Source power role with accessory support

- Sink power role with accessory support

- Dual power role with accessory support

- Dual power role with accessory and Try.SRC support

- · Dual power role with accessory and Try.SNK support

### 3.8.1 Audio accessory mode detection

The STUSB1600 detects an audio accessory device when both CC1 and CC2 pins are pulled down to ground by Ra resistor from the connected device. The audio accessory detection is advertised through CC ATTACHED MODE bits of I<sup>2</sup>C register CC CONNECTION STATUS (see Section 5.1 Register description).

# 3.8.2 Debug accessory mode detection

The STUSB1600 detects a connection to a debug and test system (DTS) when it operates either in sink power role or in source power role. The debug accessory detection is advertised by DEBUG1 and DEBUG2 pins as well as through CC\_ATTACHED\_MODE bits of I<sup>2</sup>C register CC\_CONNECTION\_STATUS (see Section 5.1 Register description).

In sink power role, a debug accessory device is detected when both CC1 and CC2 pins are pulled up by Rp resistor from the connected device. The voltage levels on CC1 and CC2 pins give the orientation and the current capability as described in the table below. DEBUG1 pin is asserted to advertise the DTS detection and A\_B\_SIDE pin indicates the orientation of the connection. The current capability of the DTS is given through SINK\_POWER\_STATE bits of I<sup>2</sup>C register CC\_OPERATION\_STATUS (see Section 5.1 Register description).

Table 9. Orientation and current capability detection in sink power role

| # | CC1<br>(CC2)        | CC2<br>(CC1)        | Charging current configuration | A_B_SIDE pin<br>CC1/CC2<br>(CC2/CC1) | Current capability state SINK_POWER_STATE bit values    |

|---|---------------------|---------------------|--------------------------------|--------------------------------------|---------------------------------------------------------|

| 1 | Rp 3A               | Rp 1.5 A            | Default                        | HiZ (0)                              | PowerDefault.SNK (source supplies default USB current)  |

| 2 | Rp 1.5 A            | Rp default          | 1.5 A                          | HiZ (0)                              | Power1.5.SNK (source supplies 1.5 A USB Type-C current) |

| 3 | Rp 3 A              | Rp default          | 3.0 A                          | HiZ (0)                              | Power3.0.SNK (source supplies 3.0 A USB Type-C current) |

| 4 | Rp<br>def/1.5 A/3 A | Rp<br>def/1.5 A/3 A | Default                        | HiZ (HiZ)                            | PowerDefault.SNK (source supplies default USB current)  |

DS11503 - Rev 4 page 15/66

In source power role, a debug accessory device is detected when both CC1 and CC2 pins are pulled down to ground by Rd resistor from the connected device. The orientation detection is performed in two steps as described in the table below. DEBUG2 pin is asserted to advertise the DTS detection and the A\_B\_SIDE pin indicates the orientation of the connection. The orientation detection is advertised through TYPEC\_FSM\_STATE bits of I<sup>2</sup>C register CC\_OPERATION\_STATUS (see Section 5.1 Register description).

Table 10. Orientation detection in source power role

| # | CC1<br>(CC2) | CC2<br>(CC1) | Detection process                                                                                             | A_B_SIDE pin<br>CC1/CC2<br>(CC2/CC1) | Orientation detection state  TYPEC_FSM_STATE bit value |

|---|--------------|--------------|---------------------------------------------------------------------------------------------------------------|--------------------------------------|--------------------------------------------------------|

| 1 | Rd           | Rd           | 1 <sup>st</sup> step: debug accessory mode detected                                                           | HiZ (HiZ)                            | UnorientedDebugAccessory.SRC                           |

| 2 | Rd           | ≤Ra          | 2 <sup>nd</sup> step: orientation detected (DTS presents a resistance to GND with a value ≤Ra on its CC2 pin) | HiZ (0)                              | OrientedDebugAccessory.SRC                             |

DS11503 - Rev 4 page 16/66

# 4 I<sup>2</sup>C interface

# 4.1 Read and write operations

The I<sup>2</sup>C interface is used to configure, control and read the operation status of the device. It is compatible with the Philips I<sup>2</sup>C Bus® (version 2.1). The I<sup>2</sup>C is a slave serial interface based on two signals:

- SCL serial clock line: input clock used to shift data

- SDA serial data line: input/output bidirectional data transfers

A filter rejects the potential spikes on the bus data line to preserve data integrity.

The bidirectional data line supports transfers up to 400 kbit/s (fast mode). The data are shifted to and from the chip on the SDA line, MSB first.

The first bit must be high (START) followed by the 7-bit device address and the read/write control bit.

Two 7-bit device address are available for the STUSB1600 thanks to the external programming of DevADDR0 through ADDR0 pin setting, i.e. 0x28 or 0x29. It allows two STUSB1600 devices to be connected on the same I<sup>2</sup>C bus

Table 11. Device address format

| Bit7     | Bit6     | Bit5     | Bit4     | Bit3     | Bit2     | Bit1     | Bit0 |

|----------|----------|----------|----------|----------|----------|----------|------|

| DevADDR6 | DevADDR5 | DevADDR4 | DevADDR3 | DevADDR2 | DevADDR1 | DevADDR0 | R/W  |

| 0        | 1        | 0        | 1        | 0        | 0        | ADDR0    | 0/1  |

### Table 12. Register address format

| Bit7     | Bit6     | Bit5     | Bit4     | Bit3     | Bit2     | Bit1     | Bit0     |

|----------|----------|----------|----------|----------|----------|----------|----------|

| RegADDR7 | RegADDR6 | RegADDR5 | RegADDR4 | RegADDR3 | RegADDR2 | RegADDR1 | RegADDR0 |

# Table 13. Register data format

| Bit7  | Bit6  | Bit5  | Bit4  | Bit3  | Bit2  | Bit1  | Bit0  |

|-------|-------|-------|-------|-------|-------|-------|-------|

| DATA7 | DATA6 | DATA5 | DATA4 | DATA3 | DATA2 | DATA1 | DATA0 |

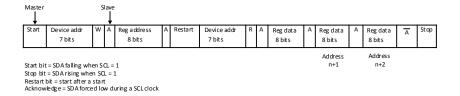

Figure 4. Read operation

DS11503 - Rev 4 page 17/66

Figure 5. Write operation

| Start                                | Device addr<br>7 bits | W | Α | Reg address<br>8 bits | Α | Reg data<br>8 bits | А | Reg data<br>8 bits | А | Reg data<br>8 bits | Α | St op |

|--------------------------------------|-----------------------|---|---|-----------------------|---|--------------------|---|--------------------|---|--------------------|---|-------|

| Start hit = SDA falling when SCI = 1 |                       |   |   |                       |   |                    |   | Address<br>n+1     |   | Address<br>n+2     |   |       |

Start bit = SDA falling when SCL = 1 Stop bit = SDA rising when SCL = 1 Restart bit = start after a start

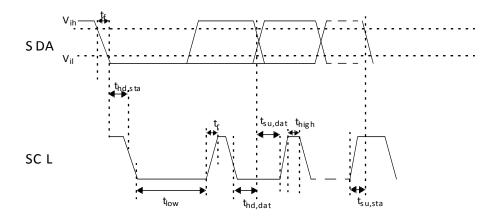

# 4.2 Timing specifications

The device uses a standard slave I<sup>2</sup>C channel at speed up to 400 kHz.

Table 14. I<sup>2</sup>C timing parameters -  $V_{DD}$  = 5 V

| Symbol              | Parameter                                        | Min.                    | Тур. | Max. | Unit |

|---------------------|--------------------------------------------------|-------------------------|------|------|------|

| F <sub>scl</sub>    | SCL clock frequency                              | 0                       | -    | 400  | kHz  |

| t <sub>hd,sta</sub> | Hold time (repeated) START condition             | 0.6                     | -    | -    | μs   |

| t <sub>low</sub>    | LOW period of the SCL clock                      | 1.3                     | -    | -    | μs   |

| t <sub>high</sub>   | HIGH period of the SCL clock                     | 0.6                     | -    | -    | μs   |

| t <sub>su,dat</sub> | Set-up time for repeated START condition         | 0.6                     | -    | -    | μs   |

| t <sub>hd,dat</sub> | Data hold time                                   | 0.04                    | -    | 0.9  | μs   |

| t <sub>su,dat</sub> | Data set-up time                                 | 100                     | -    | -    | μs   |

| t <sub>r</sub>      | Rise time of both SDA and SCL signals            | 20 + 0.1 C <sub>b</sub> | -    | 300  | ns   |

| t <sub>f</sub>      | Fall time of both SDA and SCL signals            | 20 + 0.1 C <sub>b</sub> | -    | 300  | ns   |

| t <sub>su,sto</sub> | Set-up time for STOP condition                   | 0.6                     | -    | -    | μs   |

| t <sub>buf</sub>    | Bus free time between a STOP and START condition | 1.3                     | -    | -    | μs   |

| C <sub>b</sub>      | Capacitive load for each bus line                | -                       | -    | 400  | pF   |

DS11503 - Rev 4 page 18/66

DS11503 - Rev 4 page 19/66

# 5 I<sup>2</sup>C register map

Table 15. Register access legend

| Access code | Expanded name  | Description                                    |

|-------------|----------------|------------------------------------------------|

| RO          | Read only      | Register can be read only                      |

| R/W         | Read /write    | Register can be read or written                |

| RC          | Read and clear | Register can be read and is cleared after read |

Table 16. STUSB1600 register map overview

| Address    | Register name              | Access | Description                                                                 |

|------------|----------------------------|--------|-----------------------------------------------------------------------------|

| 00h to 0Ah | Reserved                   | RO     | Do not use                                                                  |

| 0Bh        | ALERT_STATUS               | RC     | Alert register linked to transition registers                               |

| 0Ch        | OCh ALERT_STATUS_MASK_CTRL |        | Allows the interrupt mask on ALERT_STATUS register to be changed            |

| 0Dh        | CC_CONNECTION_STATUS_TRANS | RC     | Alerts about transition in CC_CONNECTION_STATUS register                    |

| 0Eh        | CC_CONNECTION_STATUS       | RO     | Gives status on CC connection                                               |

| 0Fh        | MONITORING_STATUS_TRANS    | RC     | Alerts about transition in MONITORING_STATUS register                       |

| 10h        | MONITORING_STATUS          | RO     | Gives status on V <sub>BUS</sub> and V <sub>CONN</sub> voltage monitoring   |

| 11h        | CC_OPERATION_STATUS        | RO     | Gives status on CC operation modes                                          |

| 12h        | h HW_FAULT_STATUS_TRANS    |        | Alerts about transition in HW_FAULT_STATUS register                         |

| 13h        | HW_FAULT_STATUS            | RO     | Gives status on hardware faults                                             |

| 14h to 17h | Reserved                   | RO     | Do not use                                                                  |

| 18h        | CC_CAPABILITY_CTRL         | R/W    | Allows the CC capabilities to be changed                                    |

| 19h to 1Dh | Reserved                   | RO     | Do not use                                                                  |

| 1Eh        | CC_VCONN_SWITCH_CTRL       | R/W    | Allows the current limit of V <sub>CONN</sub> power switches to be changed  |

| 1Fh        | Reserved                   | RO     | Do not use                                                                  |

| 20h        | VCONN_MONITORING_CTRL      | R/W    | Allows the monitoring conditions of V <sub>CONN</sub> voltage to be changed |

| 21h        | Reserved                   | RO     | Do not use                                                                  |

| 22h        | VBUS_MONITORING_RANGE_CTRL |        | Allows the voltage range for V <sub>BUS</sub> monitoring to be changed      |

| 23h        | RESET_CTRL                 | R/W    | Controls the device reset by software                                       |

| 24h        | Reserved                   | RO     | Do not use                                                                  |

| 25h        | VBUS_DISCHARGE_TIME_CTRL   | R/W    | Allows the V <sub>BUS</sub> discharge time to be changed                    |

DS11503 - Rev 4 page 20/66

| Address    | Register name            | Access | Description                                                                |

|------------|--------------------------|--------|----------------------------------------------------------------------------|

| 26h        | VBUS_DISCHARGE_STATUS    | RO     | Gives status on V <sub>BUS</sub> discharge path activation                 |

| 27h        | VBUS_ENABLE_STATUS       | RO     | Gives status on V <sub>BUS</sub> power path activation                     |

| 28h        | CC_POWER_MODE_CTRL       | R/W    | Allows the CC power mode to be changed                                     |

| 29h to 2Dh | Reserved                 | RO     | Do not use                                                                 |

| 2Eh        | PEh VBUS_MONITORING_CTRL |        | Allows the monitoring conditions of V <sub>BUS</sub> voltage to be changed |

| 2Fh        | Reserved                 | RO     | Do not use                                                                 |

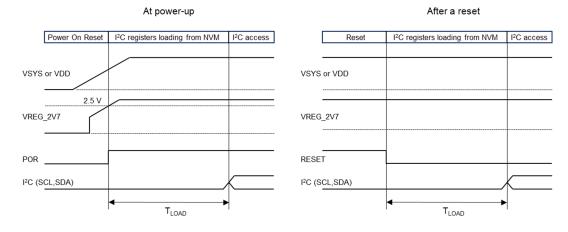

# 5.1 Register description

The reset column specified in the register descriptions below defines the default value of the registers at power-up or after a reset. The reset values with (NVM) index correspond to the user-defined parameters that can be customized by NVM re-programming if needed (see Section 6 Start-up configuration).

# 5.1.1 ALERT\_STATUS

Address: 0Bh Access: RC

Note: This register indicates an alert that has occurred.

Bit Field name Reset **Description** 7 0b Reserved Do not use 0b: cleared 6 CC\_CONNECTION\_STATUS\_AL 0b 1b: change occurred on CC CONNECTION STATUS TRANS register 5 MONITORING\_STATUS\_AL 0b 1b: change occurred on MONITORING\_STATUS\_TRANS register 0b: cleared 4 HW\_FAULT\_STATUS\_AL 0b 1b: change occurred on HW\_FAULT\_STATUS\_TRANS register Reserved 0000b Do not use 3:0

Table 17. ALERT\_STATUS register

When a bit value change occurs on one of the mentioned transition registers, it automatically sets the corresponding alert bit in ALERT\_STATUS register.

### 5.1.2 ALERT\_STATUS\_MASK\_CTRL

Address: 0Ch Access: R/W

Note: This register is used to mask event interrupt and prevent the assertion of the alert bit in the ALERT\_STATUS register when the corresponding bit defined below is set to 1.

DS11503 - Rev 4 page 21/66

Table 18. ALERT\_STATUS\_MASK\_CTRL register

| Bit | Field Name                                | Reset               | Description            |

|-----|-------------------------------------------|---------------------|------------------------|

| 7   | Reserved                                  | 1b                  | Do not use             |

| 6   | 6 CC_CONNECTION_STATUS_AL_MASK            |                     | 0b: interrupt unmasked |

|     | 00_001412011014_01741000_742_4477014      | 1b <sup>(NVM)</sup> | 1b: interrupt masked   |

| 5   | MONITORING STATUS AL MASK                 | 1b (NVM)            | 0b: interrupt unmasked |

|     | MONTO NINO _ O 17 NI O O _ 7 NE _ NINO NI | 10 \ /              | 1b: interrupt masked   |

| 4   | HW FAULT STATUS AL MASK                   | 1b (NVM)            | 0b: interrupt unmasked |

|     | TIV_I NOLI_OTNI OO_AL_WAOK                | 10 \ /              | 1b: interrupt masked   |

| 3:0 | Reserved                                  | 1111b               | Do not use             |

The condition to generate an active-low ALERT signal is: [ALERT\_STATUS bitwise AND (NOT ALERT\_STATUS\_MASK)] <> 0

# 5.1.3 CC\_CONNECTION\_STATUS\_TRANS

Address: 0Dh Access: RC

Note: This register indicates a bit value change has occurred in CC\_CONNECTION\_STATUS register.

Table 19. CC\_CONNECTION\_STATUS\_TRANS register

| Bit | Field name        | Reset    | Description                              |  |  |  |

|-----|-------------------|----------|------------------------------------------|--|--|--|

| 7:1 | Reserved          | 0000000b | Do not use                               |  |  |  |

| 0   | 0 CC_ATTACH_TRANS | 0b       | 0b: cleared                              |  |  |  |

|     |                   |          | 1b: transition occurred on CC_ATTACH bit |  |  |  |

DS11503 - Rev 4 page 22/66

# 5.1.4 CC\_CONNECTION\_STATUS

Address: 0Eh Access: RO

Note: This register gives the connection state of the CC pins and on associated operating modes of the device.

Table 20. CC\_CONNECTION\_STATUS register

| Bit | Field name          | Reset               | Description                                     |

|-----|---------------------|---------------------|-------------------------------------------------|

|     |                     |                     | 000b: no device attached                        |

|     |                     |                     | 001b: sink attached                             |

|     |                     |                     | 010b: source attached                           |

| 7:5 | CC_ATTACHED_MODE    | 000b                | 011b: debug accessory attached                  |

| 7.5 | CC_ATTACTIED_WODE   | 0000                | 100b: audio accessory attached                  |

|     |                     |                     | 101b: do not use                                |

|     |                     |                     | 110b: do not use                                |

|     |                     |                     | 111b: do not use                                |

| 4   | 4 DEVICE DOWED MODE | 0b <sup>(NVM)</sup> | 0b: operating in normal power mode              |

| 4   | DEVICE_POWER_MODE   | ODATA               | 1b: operating in standby power mode             |

| 3   | CC DOWED DOLE       | 0b                  | 0b: operating as a sink                         |

| 3   | CC_POWER_ROLE       | UD                  | 1b: operating as a source                       |

| 2   | Reserved            | 0b                  | Do not use                                      |

|     | OO MOONIN OURRING   |                     | 0b: V <sub>CONN</sub> is not supplied on CC pin |

| 1   | CC_VCONN_SUPPLY     | 0b                  | 1b: V <sub>CONN</sub> is supplied on CC pin     |

|     | CC ATTACH           | Oh                  | 0b: not attached                                |

| 0   | CC_ATTACH           | 0b                  | 1b: attached                                    |

The DEVICE\_POWER\_MODE bit indicates the power consumption mode of the device at start-up and during operation:

- In normal mode, all the internal circuits are turned on

- In standby mode the CC interface and the voltage monitoring blocks remain off until a connection is detected

The standby mode power is disabled by default and can be activated through NVM programming (see Section 6 Start-up configuration).

The CC\_POWER\_ROLE bit is relevant only when a connection is established and the device is attached.

DS11503 - Rev 4 page 23/66

# 5.1.5 MONITORING\_STATUS\_TRANS

Address: 0Fh Access: RC

Note: This register indicates a bit value change has occurred in MONITORING\_STATUS register.

Table 21. MONITORING\_STATUS\_TRANS register

| Bit | Field name           | Reset | Description                                              |

|-----|----------------------|-------|----------------------------------------------------------|

| 7:4 | Reserved             | 0000b | Do not use                                               |

| 3   | VBUS_VALID_TRANS     | 0b    | 0b: cleared 1b: transition occured on VBUS_VALID bit     |

| 2   | VBUS_VSAFE0V_TRANS   | 0b    | 0b: cleared 1b: transition occured on VBUS_VSAFE0V bit   |

| 1   | VBUS_PRESENCE_TRANS  | 0b    | 0b: cleared 1b: transition occured on VBUS_PRESENCE bit  |

| 0   | VCONN_PRESENCE_TRANS | 0b    | 0b: cleared 1b: transition occured on VCONN_PRESENCE bit |

# 5.1.6 MONITORING\_STATUS

Address: 10h Access: RO

Note: This register gives the current status of V<sub>BUS</sub> and V<sub>CONN</sub> voltage monitoring done respectively on

VBUS\_SENSE pin and VCONN pin.

Table 22. MONITORING\_STATUS register

| Bit | Field name     | Reset    | Description                                                                                                                              |

|-----|----------------|----------|------------------------------------------------------------------------------------------------------------------------------------------|

| 7:4 | Reserved 0000b |          | Do not use                                                                                                                               |

| 3   | VBUS_VALID     | 0b       | 0b: V <sub>BUS</sub> is outside valid V <sub>BUS</sub> voltage range 1b: V <sub>BUS</sub> is within valid V <sub>BUS</sub> voltage range |

| 2   | VBUS_VSAFE0V   | 1b       | 0b: V <sub>BUS</sub> is above V <sub>BUS</sub> VSafe0V threshold 1b: V <sub>BUS</sub> is below V <sub>BUS</sub> VSafe0V threshold        |

| 1   | VBUS_PRESENCE  | 0b       | 0b: V <sub>BUS</sub> is below V <sub>BUS</sub> UVLO threshold 1b: V <sub>BUS</sub> is above V <sub>BUS</sub> UVLO threshold              |

| 0   | VCONN_PRESENCE | 0b or 1b | 0b: V <sub>CONN</sub> is below V <sub>CONN</sub> UVLO threshold  1b: V <sub>CONN</sub> is above V <sub>CONN</sub> UVLO threshold         |

The default value of valid  $V_{BUS}$  voltage range can be changed in VBUS\_MONITORING\_RANGE\_CTRL register during the operation.

$V_{BUS}$  vSafe0V threshold is defined in VBUS\_MONITORING\_CTRL register. It is used in source power role as a Type-C FSM condition to establish a valid device attachment.

V<sub>BUS</sub> UVLO threshold is set by hardware.

V<sub>CONN</sub> UVLO threshold is defined in VCONN\_MONITORING\_CTRL register.

DS11503 - Rev 4 page 24/66

The reset value of VCONN\_PRESENCE bit is:

- 0b when V<sub>CONN</sub> is not supplied on VCONN pin, or when V<sub>CONN</sub> is supplied and voltage level is below UVLO threshold, or when V<sub>CONN</sub> threshold detection circuit is disabled.

- 1b when V<sub>CONN</sub> is supplied on VCONN pin and the voltage level is above UVLO threshold.

See Section 8.3 Electrical and timing characteristics for the threshold voltage description and value on VBUS\_SENSE and VCONN pins.

DS11503 - Rev 4 page 25/66

# 5.1.7 CC\_OPERATION\_STATUS

Address: 11h Access: RO

Note:

This register gives the current status of the device operating modes with respect to the Type-C FSM states as defined in the USB Type-C standard specification. This status is informative only and is not used to trigger any

Table 23. CC\_OPERATION\_STATUS register

| Bit | Field name           | Reset | Description                                                  |

|-----|----------------------|-------|--------------------------------------------------------------|

| 7   | 7 CC_PIN_ATTACHED 0b | Oh    | 0b: CC1 is attached                                          |

| /   |                      | OD    | 1b: CC2 is attached                                          |

| 6:5 | SINK_POWER_STATE     | 00b   | 00b: PowerDefault.SNK (source supplies default USB current)  |

|     |                      |       | 01b: Power1.5.SNK (source supplies 1.5 A USB Type-C current) |

|     |                      |       | 10b: Power3.0.SNK (source supplies 3.0 A USB Type-C current) |

|     |                      |       | 11b: do not use                                              |

DS11503 - Rev 4 page 26/66

| Bit | Field name      | Reset | Description                                                              |

|-----|-----------------|-------|--------------------------------------------------------------------------|

|     |                 |       | 00h: Unattached.SNK                                                      |

|     |                 |       | 01h: AttachWait.SNK                                                      |

|     |                 |       | 02h: Attached.SNK                                                        |

|     |                 |       | 03h: DebugAccessory.SNK                                                  |

|     |                 |       | 04h: reserved                                                            |

|     |                 |       | 05h: reserved                                                            |

|     |                 |       | 06h: reserved                                                            |

|     |                 |       | 07h: TryWait.SNK                                                         |

|     |                 |       | 08h: Unattached.SRC                                                      |

|     |                 |       | 09h: AttachWait.SRC                                                      |

|     |                 |       | 0Ah: Attached.SRC                                                        |

|     |                 |       | 0Bh: reserved                                                            |

|     |                 |       | 0Ch: Try.SRC                                                             |

|     |                 |       | 0Dh: Unattached.Accessory                                                |

|     |                 |       | 0Eh: AttachWait.Accessory                                                |

|     |                 | 00h   | 0Fh: AudioAccessory                                                      |

| 4:0 | TYPEC_FSM_STATE | or    | 10h: UnorientedDebugAccessory.SRC                                        |

|     |                 | 08h   | 11h: reserved                                                            |

|     |                 |       | 12h: reserved                                                            |

|     |                 |       | 13h: ErrorRecovery                                                       |

|     |                 |       | 14h: TryDebounce.SNK (intermediate state towards Try.SNK state)          |

|     |                 |       | 15h: Try.SNK                                                             |

|     |                 |       | 16h: reserved                                                            |

|     |                 |       | 17h: TryWait.SRC                                                         |

|     |                 |       | 18h: UnattachedWait.SRC (V <sub>CONN</sub> intermediate discharge state) |

|     |                 |       | 19h: OrientedDebugAccessory.SRC                                          |

|     |                 |       | 1Ah: reserved                                                            |

|     |                 |       | 1Bh: reserved                                                            |

|     |                 |       | 1Ch: reserved                                                            |

|     |                 |       | 1Dh: reserved                                                            |

|     |                 |       | 1Eh: reserved                                                            |

|     |                 |       | 1Fh: reserved                                                            |

The reset value of TYPEC\_FSM\_STATE bits is:

- 00h when device operates in sink power role (Unattached.SNK)

- 08h when device operates in source power role (Unattached.SRC)

The CC\_PIN\_ATTACHED bit indicates which CC pin is connected to the CC line. Its value is consistent with the logic level of the A\_B\_SIDE output pin providing cable orientation.

The SINK\_POWER\_STATE bits indicate the current level advertised by the source that the sink can consume when the device works in sink power role.

The TYPEC\_FSM\_STATE bits indicate the current state of the Type-C FSM corresponding to the power mode defined in CC\_POWER\_MODE\_CTRL register.

DS11503 - Rev 4 page 27/66

# 5.1.8 HW\_FAULT\_STATUS\_TRANS

Address: 12h Access: RC

Note:

This register indicates a bit value change has occurred in HW\_FAULT\_STATUS register. It also alerts when the overtemperature condition is met.

Table 24. HW\_FAULT\_STATUS\_TRANS register

| Bit | Field name               | Reset | Description                                                                   |

|-----|--------------------------|-------|-------------------------------------------------------------------------------|

| 7   | THERMAL_FAULT            | Ob    | 0b: cleared 1b: junction temperature is above temperature threshold of 145° C |

| 6   | Reserved                 | 0b    | Do not use                                                                    |

| 5   | VPU_OVP_FAULT_TRANS      | 0b    | 0b: cleared 1b: transition occured on VPU_OVP_FAULT bit                       |

| 4   | VPU_VALID_TRANS          | 0b    | 0b: cleared 1b: transition occured on VPU_VALID bit                           |

| 3   | Reserved                 | 0b    | Do not use                                                                    |

| 2   | VCONN_SW_RVP_FAULT_TRANS | 0b    | 0b: cleared 1b: transition occured on VCONN_SW_RVP_FAULT bits                 |

| 1   | VCONN_SW_OCP_FAULT_TRANS | 0b    | 0b: cleared 1b: transition occured on VCONN_SW_OCP_FAULT bits                 |

| 0   | VCONN_SW_OVP_FAULT_TRANS | 0b    | 0b: cleared 1b: transition occured on VCONN_SW_OVP_FAULT bits                 |

DS11503 - Rev 4 page 28/66

# 5.1.9 **HW\_FAULT\_STATUS**

Address: 13h Access: RO

Note:

This register provides information on hardware fault conditions related to the internal pull-up voltage in source power role and to the  $V_{CONN}$  power switches.

Table 25. HW\_FAULT\_STATUS register

| Bit | Field name             | Reset | Description                                                                                  |

|-----|------------------------|-------|----------------------------------------------------------------------------------------------|

| 7   | VPU_OVP_FAULT          | 0b    | 0b: voltage on CC pins is below OVP threshold of 6.0 V                                       |

| ,   | VPO_OVP_FAULT          | OD    | 1b: voltage on CC pins is above OVP threshold of 6.0 V                                       |

| 6   | VPU_VALID              | 1b    | 0b: pull-up voltage on CC pins is below UVLO threshold of 2.8 V                              |

|     |                        |       | 1b: pull-up voltage on CC pins is above UVLO threshold of 2.8 V (safe condition)             |

| 5   | VCONN SW DVD FAULT CC1 | 0b    | 0b: no reverse voltage on V <sub>CONN</sub> power switch connected to CC1                    |

| 3   | VCONN_SW_RVP_FAULT_CC1 | OD    | 1b: reverse voltage detected on V <sub>CONN</sub> power switch connected to CC1              |

| 4   | VCONN_SW_RVP_FAULT_CC2 | Ob    | 0b: no reverse voltage on V <sub>CONN</sub> power switch connected to CC2                    |

| 4   |                        |       | 1b: reverse voltage detected on V <sub>CONN</sub> power switch connected to CC2              |

| 3   | VCONN_SW_OCP_FAULT_CC1 | Ob    | 0b: no short-circuit or overcurrent on V <sub>CONN</sub> power switch connected to CC1       |

| 3   |                        |       | 1b: short-circuit or overcurrent detected on $V_{CONN}$ power switch connected to CC1        |

| 2   | VCONN SW OCD FAULT CC2 | 0b    | 0b: no short-circuit or overcurrent on V <sub>CONN</sub> power switch connected to CC2       |

| 2   | VCONN_SW_OCP_FAULT_CC2 | OD    | 1b: short-circuit or overcurrent detected on V <sub>CONN</sub> power switch connected to CC2 |

| 4   | VCONN CW OVE FAULT CC4 | Oh    | 0b: no overvoltage on V <sub>CONN</sub> power switch connected to CC1                        |

| 1   | VCONN_SW_OVP_FAULT_CC1 | 0b    | 1b: overvoltage detected on V <sub>CONN</sub> power switch connected to CC1                  |

| 0   | VCONN SW OVE FAULT CC2 | Ob    | 0b: no overvoltage on V <sub>CONN</sub> power switch connected to CC2                        |

| U   | VCONN_SW_OVP_FAULT_CC2 |       | 1b: overvoltage detected on V <sub>CONN</sub> power switch connected to CC2                  |

The VPU\_VALID and VPU\_OVP\_FAULT bits are related to the internal pull-up voltage applied on the CC pins when the device works in source power role. They inform about an internal supply issue that could prevent the device from detecting a valid connection to a distant device.

# 5.1.10 CC\_CAPABILITY\_CTRL

Address: 18h Access: R/W

Note:

When operating in source power role, this register allows the advertising of the current capability to be changed as defined in the USB Type-C standard specification and the V<sub>CONN</sub> supply capability.

DS11503 - Rev 4 page 29/66

Table 26. CC\_CAPABILITY\_CTRL register

| Bit | Field name             | Reset               | Description                                                  |

|-----|------------------------|---------------------|--------------------------------------------------------------|

|     |                        |                     | 00b: default USB current (500 mA or 900 mA)                  |

| 7:6 | CC CURRENT ADVERTISED  | 01b(NVM)            | 01b: 1.5 A USB Type-C current                                |

| 7.0 | CC_CORRENT_ADVERTISED  | O1D((VVW)           | 10b: 3.0 A USB Type-C current                                |

|     |                        |                     | 11b: do not use                                              |

| 5   | Reserved               | 1b                  | Do not use                                                   |

| 4   | CO VOCANA DIOCUADOS EN | 49.40               | 0b: V <sub>CONN</sub> discharge disabled on CC pin           |

| 4   | CC_VCONN_DISCHARGE_EN  | 0b <sup>(NVM)</sup> | 1b: V <sub>CONN</sub> discharge enabled for 250 ms on CC pin |

| 3:1 | Reserved               | 000b                | Do not use                                                   |

| 0   | CC VCONN CURRIN EN     | 1b <sup>(NVM)</sup> | 0b: V <sub>CONN</sub> supply capability disabled on CC pin   |

| 0   | CC_VCONN_SUPPLY_EN     |                     | 1b: V <sub>CONN</sub> supply capability enabled on CC pin    |

# 5.1.11 CC\_VCONN\_SWITCH\_CTRL

Address: 1Eh Access: R/W

Note: This register allows the default current limit of the power switches supplying V<sub>CONN</sub> on the CC pins to be

changed.

Table 27. CC\_VCONN\_SWITCH\_CTRL register

| Bit | Field name           | Reset       | Description             |

|-----|----------------------|-------------|-------------------------|

| 7:4 | Reserved             | 0000b       | Do not use              |

|     |                      |             | 0000b: 350 mA (default) |

|     |                      |             | 0001b: 300 mA           |

|     |                      |             | 0010b: 250 mA           |

|     |                      |             | 0011b: 200 mA           |

|     |                      |             | 0100b: 150 mA           |

| 3:0 | CC_VCONN_SWITCH_ILIM | 0000b (NVM) | 0101b: 100 mA           |

|     |                      |             | 0110b: 400 mA           |

|     |                      |             | 0111b: 450 mA           |

|     |                      |             | 1000b: 500 mA           |

|     |                      |             | 1001b: 550 mA           |

|     |                      |             | 1010b: 600 mA           |

# 5.1.12 VCONN\_MONITORING\_CTRL

Address: 20h Access: R/W

Note: This register allows the default voltage monitoring conditions for V<sub>CONN</sub> to be modified.

Table 28. VCONN\_MONITORING\_CTRL register

| Bit | Field name            | Reset | Description                                        |

|-----|-----------------------|-------|----------------------------------------------------|

| 7   | 7 VCONN_MONITORING_EN | 1b    | 0b: disables UVLO threshold detection on VCONN pin |

| 1   |                       |       | 1b: enables UVLO threshold detection on VCONN pin  |

DS11503 - Rev 4 page 30/66

| Bit | Field name           | Reset | Description                                                                                                                                        |

|-----|----------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| 6   | VCONN_UVLO_THRESHOLD | 0b    | 0b: selects high UVLO threshold (default) 1b: selects low UVLO threshold (case where V <sub>CONN</sub> -powered accessories operate down to 2.7 V) |

| 5   | Reserved             | 1b    | Do not use                                                                                                                                         |

| 4   | Reserved             | 0b    | Do not use                                                                                                                                         |

| 3:0 | Reserved             | 0000b | Do not use                                                                                                                                         |

Disabling the UVLO threshold detection on VCONN pin deactivates the  $V_{CONN}$  power path and sets VCONN\_PRESENCE bit to 0b in the MONITORING\_STATUS register.

See Section 8.3 Electrical and timing characteristics for the threshold voltage description and value on VCONN pin.

DS11503 - Rev 4 page 31/66

# 5.1.13 VBUS\_MONITORING\_RANGE\_CTRL

Address: 22h Access: R/W

Note: This register allows the low and high limits of the V<sub>BUS</sub> monitoring voltage range to be changed during

attachment.

Table 29. VBUS\_MONITORING\_RANGE\_CTRL register

| Bit | Field name            | Reset       | Description                                                                                                                                         |

|-----|-----------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:4 | SHIFT_HIGH_VBUS_LIMIT | 0000b (NVM) | Binary coded $V_{SHUSBH}$ coefficient to shift up the nominal high voltage limit from 1% (0001b) to 15% (1111b) of $V_{BUS}$ voltage by step of 1%  |