# 130-dB, 32-Bit High-Performance DAC with Integrated Headphone Driver and Impedance Detection

| System Features                                                                               | Direct Stream Digital (DSD <sup>®</sup> ) path                                                                                  |

|-----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Enhanced ΔΣ oversampling DAC architecture</li> </ul>                                 | <ul> <li>Patented DSD processor</li> </ul>                                                                                      |

| — 32-bit resolution                                                                           | <ul> <li>– On-chip 50-kHz filter to meet Scarlet Book Super</li> </ul>                                                          |

| <ul> <li>Up to 384-kHz sampling rate</li> </ul>                                               | Audio Compact Disk (SACD) recommendations                                                                                       |

| <ul> <li>Low clock jitter sensitivity</li> </ul>                                              | <ul> <li>Matched PCM and DSD analog output levels</li> </ul>                                                                    |

| — Auto mute detection                                                                         | <ul> <li>– Nondecimating volume control with 0.5-dB step size<br/>and soft ramp</li> </ul>                                      |

| <ul> <li>Integrated high performance, ground-centered stereo<br/>headphone outputs</li> </ul> | <ul> <li>DSD and Pulse-code modulation (PCM) mixing for<br/>alerts</li> </ul>                                                   |

| <ul> <li>— 130-dB dynamic range (A-weighted)</li> </ul>                                       | <ul> <li>Dedicated DSD and DoP pin interface</li> </ul>                                                                         |

| <ul> <li>— –108-dB total harmonic distortion + noise (THD+N)</li> </ul>                       | Serial audio input path                                                                                                         |

| <ul> <li>— 110-dB interchannel isolation</li> </ul>                                           | <ul> <li>Five selectable digital filter responses</li> </ul>                                                                    |

| <ul> <li>Headphone power output</li> </ul>                                                    | - ·                                                                                                                             |

| – 30 mW per channel into 32 $\Omega$                                                          | <ul> <li>Low-latency mode minimizes pre-echo</li> </ul>                                                                         |

| $-5$ mW per channel into 600 $\Omega$                                                         | <ul> <li>– 110 dB of stopband attenuation</li> </ul>                                                                            |

| Headphone detection                                                                           | <ul> <li>— Supports sample rates from 32 to 384 kHz</li> </ul>                                                                  |

| <ul> <li>Headphone detection</li> <li>Headphone DC and AC impedance measurement</li> </ul>    | <ul> <li>         — I<sup>2</sup>S, right-justified, left-justified, TDM, and<br/>DSD-over-PCM (DoP) interface     </li> </ul>  |

| <ul> <li>Headphone plug-in detection</li> </ul>                                               | - Master or slave operation                                                                                                     |

| <ul> <li>Popguard<sup>®</sup> technology eliminates pop noise</li> </ul>                      | — Volume control with 0.5-dB step size and soft ramp                                                                            |

| Integrated PLL                                                                                | — 44.1 kHz deemphasis and inverting feature                                                                                     |

| — Support for 11.2896-/22.5792-, 12.288-/24.576-, 9.6-/                                       | Alternate headphone input                                                                                                       |

| 19.2-, 12-/24-, and 13-/26-MHz system MCLK rates                                              | 40-pin QFN or 42-ball CSP package option                                                                                        |

| <ul> <li>Reference clock sourced from XTI/MCLK pin</li> </ul>                                 | Applications                                                                                                                    |

| <ul> <li>— System clock output</li> </ul>                                                     | 1                                                                                                                               |

| Mono mode support                                                                             | <ul> <li>Smart phones, tablets, portable media players, laptops,<br/>digital headphones, powered speakers, AVR, home</li> </ul> |

I<sup>2</sup>C control—up to 1 MHz

theater systems, Blu-ray/DVD/SACD players and pro audio

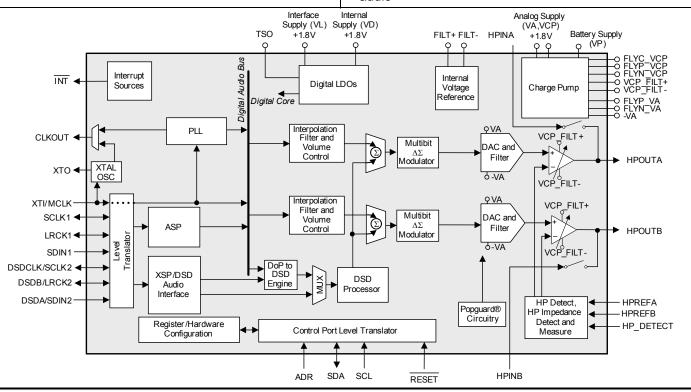

## **General Description**

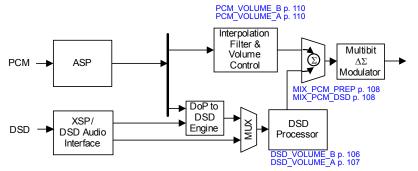

The CS43130 is a high-performance, 32-bit resolution, stereo audio DAC that supports up to 384-kHz sampling frequency with integrated low-noise ground-centered headphone amplifiers. The advanced 32-bit oversampled multibit modulator with mismatch shaping technology eliminates distortion due to on-chip component mismatch. Proprietary digital-interpolation filters support five selectable filter responses with pseudo-linear phase and ultralow latency to minimize pre-echos and ringing artifacts. Other features include volume control with 0.5-dB steps and digital deemphasis for 44.1-kHz sample rate.

The integrated ground-centered stereo headphone amplifiers are capable of delivering more than 30 mW into  $32-\Omega$  load or 5 mW into  $600-\Omega$  load per channel. Proprietary headphone impedance detection enables wide-band impedance detection for further digital post-processing. An internal stereo audio switch with true bypass supports an alternate analog input path for interfacing with external audio sources to minimize the overall bill-of-materials cost and PCB area.

The patented on-chip DSD processor preserves audio integrity by allowing signal processing such as volume control and 50-kHz Scarlet Book recommended filtering to be applied directly to the DSD stream without an intermediate decimation stage. Additional features like volume matching and channel mixing enable seamless transition between DSD and PCM playback paths.

The CS43130 accepts I<sup>2</sup>S, right-justified, left-justified, and TDM-format PCM data at sample rates from 32 to 384 kHz. The industry-standard high-speed I<sup>2</sup>C interface capable of up to 1-MHz operation provides easy configuration control. An integrated PLL allows for maximum clocking flexibility in any system. Popguard<sup>®</sup> technology eliminates output transients upon power-up or power-down events.

The CS43130 is available in a commercial-grade 42-ball WLCSP or 40-pin QFN package for operation from –10°C to +70°C.

## **Table of Contents**

| 1 | Pin Assignments and Descriptions                                                                                                                              |     |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| • | 1 1 40 Din OEN (Ton Down Through Dookage View)                                                                                                                | • 7 |

|   | 1.1 40-Pin QFN (Top-Down, Through-Package View)<br>1.2 42-Ball WLCSP (Top-down, Through-Package View)                                                         | . 4 |

|   | 1.2 42-Ball WLCSP (Top-down, Through-Package view)                                                                                                            | . ວ |

|   | 1.3 Pin Descriptions                                                                                                                                          | . 6 |

|   | 1.3 Pin Descriptions                                                                                                                                          | . 8 |

| 2 | Typical Connection Diagram                                                                                                                                    | 10  |

| 3 | Characteristics and Specifications                                                                                                                            | 11  |

|   | Table 3-1. Parameter Definitions         Table 3-2.           Table 3-2. Recommended Operating Conditions                                                     | 11  |

|   | Table 3-2 Recommended Operating Conditions                                                                                                                    | 11  |

|   | Table 3-3. Absolute Maximum Ratings         Table 3-4. Analog Output Characteristics (HV_EN = 1)         Table 3-5. Analog Output Characteristics (HV_EN = 0) | 12  |

|   | Table 3.4 Analog Output Characteristics (H)/ EN = 1)                                                                                                          | 12  |

|   | Table 2-4. Analog Output Characteristics $(\Pi V \_ E N = 1)$                                                                                                 | 12  |

|   | Table 5-5. Analog Output Characteristics $(\square V \_ \square N = 0)$                                                                                       | 13  |

|   | Table 3-6.    Headphone Load Measurement                                                                                                                      | 15  |

|   | Table 3-7. Alternate Headphone Path         Table 3-8. Combined DAC Digital, On-Chip Analog and                                                               | 16  |

|   | Table 3-8. Combined DAC Digital, On-Chip Analog and                                                                                                           |     |

|   | HPOUTx Filter Characteristics                                                                                                                                 | 16  |

|   | HPOUTx Filter Characteristics<br>Table 3-9. DAC High-Pass Filter (HPF) Characteristics<br>Table 3-10. DSD Combined Digital and On-Chip Analog                 | 18  |

|   | Table 3-10. DSD Combined Digital and On-Chip Analog                                                                                                           |     |

|   | Filter Response                                                                                                                                               | 18  |

|   | Table 3-11. Digital Interface Specifications and Characteristics                                                                                              | 19  |

|   | Table 3-12. CLKOUT Characteristics                                                                                                                            | 19  |

|   | Table 3-13. PLL Characteristics                                                                                                                               |     |

|   | Table 2-14. Crustel Characteristics                                                                                                                           | 20  |

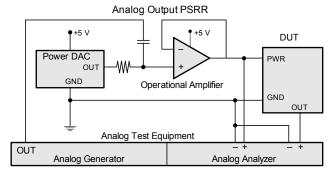

|   | Table 3-14. Crystal Characteristics         Table 3-15. Power-Supply Rejection Ratio (PSRR)                                                                   | 20  |

|   | Characteristics                                                                                                                                               | ~~  |

|   | Characteristics                                                                                                                                               | 20  |

|   | Table 3-16. DC Characteristics                                                                                                                                | 20  |

|   | Table 3-17. Power Consumption                                                                                                                                 |     |

|   | Table 3-18.         Serial-Port Interface Characteristics                                                                                                     | 21  |

|   | Table 3-19. DSD Switching Characteristic                                                                                                                      | 22  |

|   | Table 3-19. DSD Switching Characteristic         Table 3-20. I <sup>2</sup> C Slave Port Characteristics                                                      | 23  |

| 4 | Functional Description                                                                                                                                        | 24  |

|   | 4.1 Overview                                                                                                                                                  |     |

|   | 4.2 Analog Outputs                                                                                                                                            |     |

|   | 4.3 Class H Amplifier Output                                                                                                                                  |     |

|   | 4 4 Alternate Headphone Inputs                                                                                                                                | 32  |

|   | <ul><li>4.4 Alternate Headphone Inputs</li><li>4.5 Headphone Presence Detect and Output Load Detection</li></ul>                                              | 22  |

|   | 4.6 Clocking Architecture                                                                                                                                     | 36  |

|   | 4.6 Clocking Architecture                                                                                                                                     | 20  |

|   | 4.7 Clock Oulput and Fractional-N PLL                                                                                                                         | 39  |

|   | 4.8 Filtering Options                                                                                                                                         | 41  |

|   | 4.9 Audio Šerial Port (ASP)                                                                                                                                   | 42  |

|   | 4.10 DSD Interface                                                                                                                                            | 50  |

|   | 4.11 DSD and PCM Mixing                                                                                                                                       | 52  |

|   | 4.12 Standard Interrupts                                                                                                                                      | 52  |

|   | 4.13 Control Port Operation                                                                                                                                   | 53  |

|   |                                                                                                                                                               |     |

| 5 Applications                                      | . 56 |

|-----------------------------------------------------|------|

| 5.1 PLL Clocking                                    | 56   |

| 5.2 Dowor Soquencing                                | . 50 |

| 5.2 Power Sequencing                                | . 50 |

| 5.3 Crystal Tuning                                  | . 56 |

| 5.4 Alert Mixing Shutdown                           | . 57 |

| 5.5 Enable/Disable Nonoversampling Filter           | . 57 |

| 5.6 Enable/Disable Alternate Headphone Path (HPINx) | . 58 |

| 5.7 Headphone Power Down Sequences                  | 59   |

| 5.8 Headphone Power-Up Initialization               | 61   |

| 5.9 Headphone Power-Up Sequence                     | 62   |

| 5.9 Heauphone Fower-op Sequence                     | . 02 |

| 5.10 Example Sequences                              | . 04 |

| 5.11 Headphone Load Measurement                     | . 82 |

| 6 Register Quick Reference                          | . 91 |

| 7 Register Descriptions                             |      |

| 7.1 Global Registers                                | . 95 |

| 7.2 PLL Registers                                   | . 98 |

| 7.3 ASP and XSP Registers                           | 100  |

| 7 4 DSD Registers                                   | 106  |

| 7.4 DSD Registers                                   | 100  |

| 7.6 Interrupt Status and Mask Registers             | 115  |

| PCB L event Considerations                          | 404  |

| 8 PCB Layout Considerations                         | 121  |

| 8.1 Power Supply                                    | 121  |

| 8.2 Grounding                                       | 121  |

| 8.3 HPREFA and HPREFB Routing                       | 121  |

| 8.4 QFN Thermal Pad                                 | 121  |

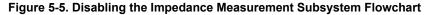

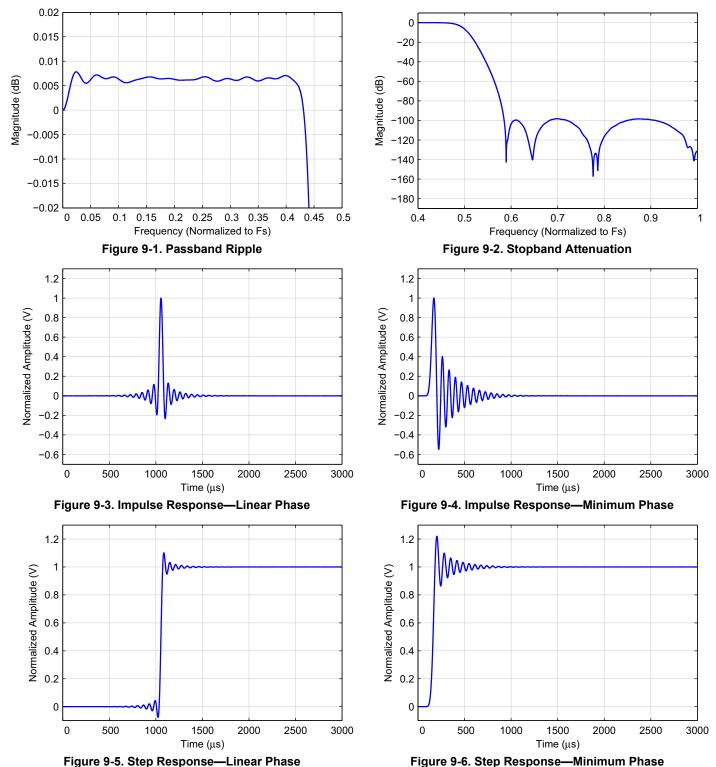

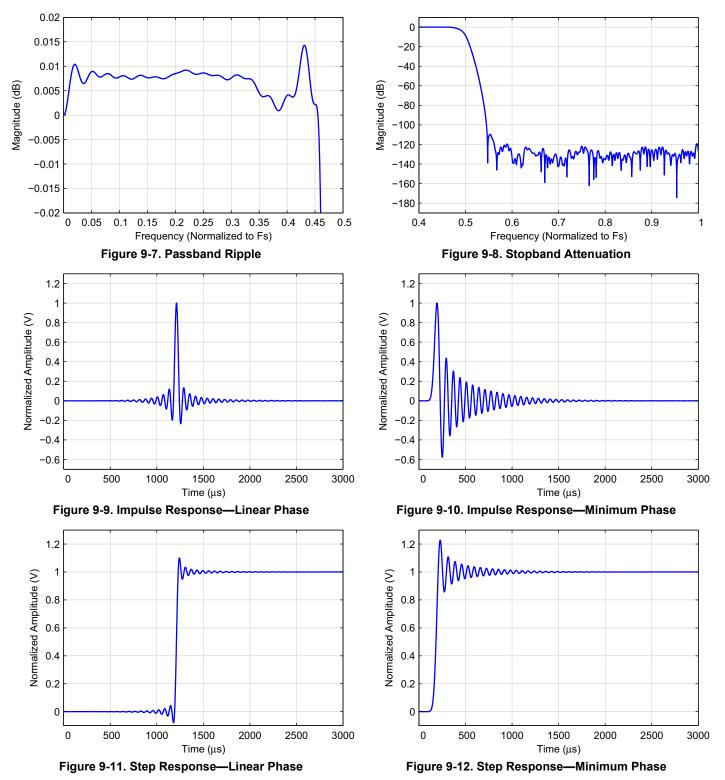

| 9 Performance Plots                                 | 122  |

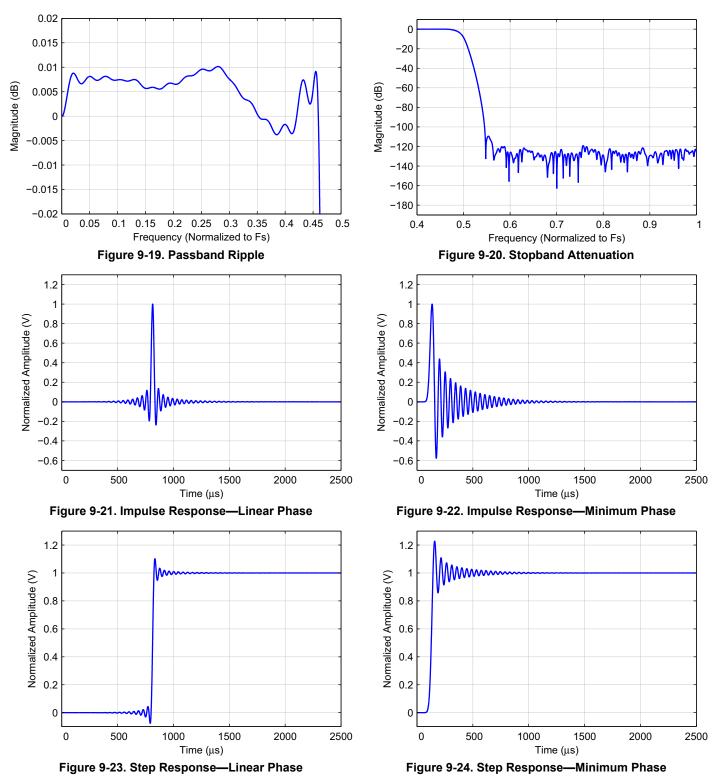

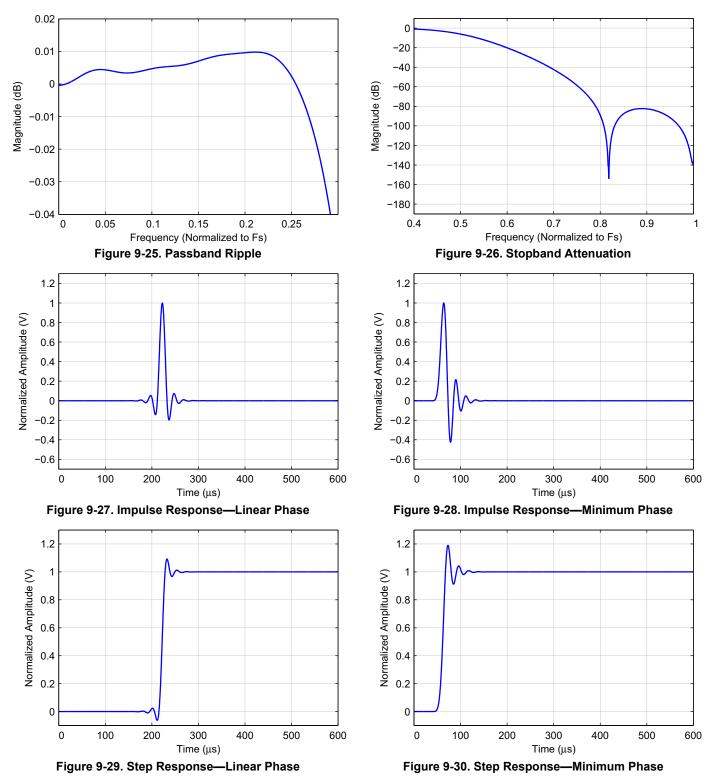

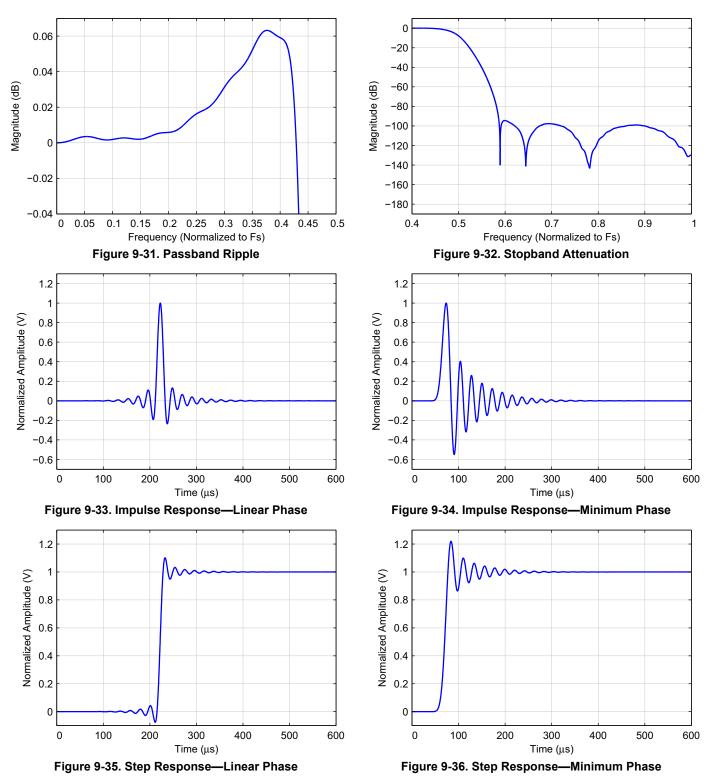

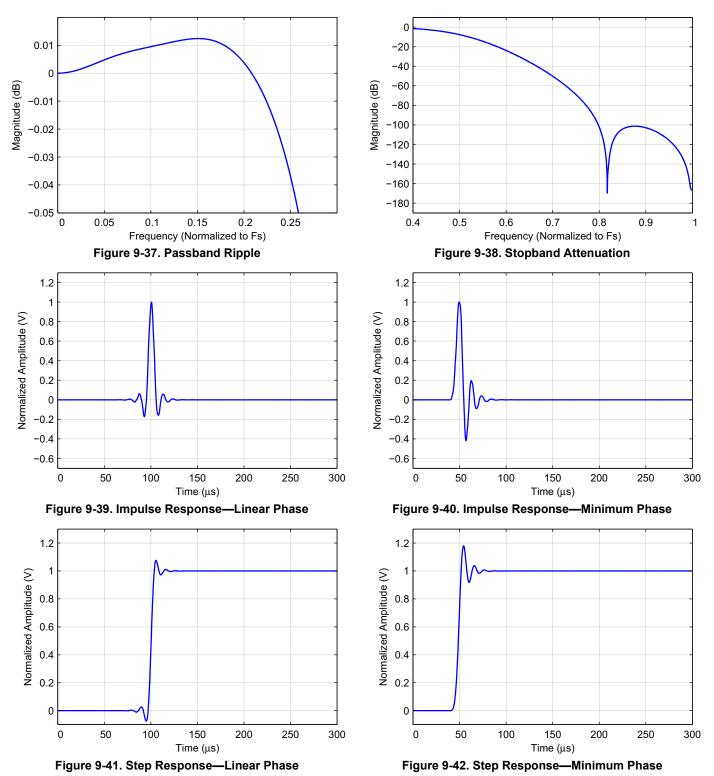

| 9.1 Digital Filter Response                         | 122  |

| 10 Package Dimensions                               |      |

| 10.1 40-Pin QFN Package Dimensions                  | 134  |

| 10.2 42-Ball WLCSP Package Dimensions               | 135  |

| 10.2 42-Dali WLCOF Fackage Dimensions               | 120  |

| 11 Thermal Characteristics                          |      |

| 12 Ordering Information                             | 130  |

| 13 References                                       | 136  |

| 14 Revision History                                 | 136  |

|                                                     |      |

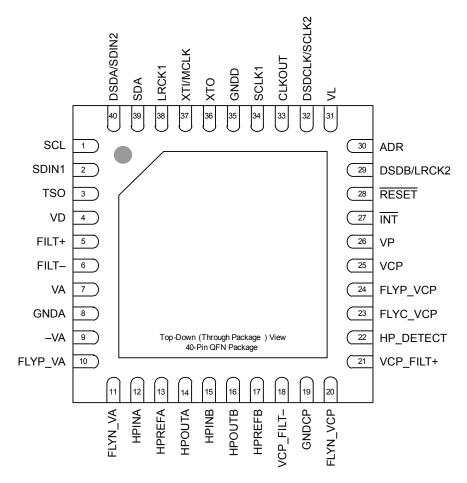

# 1 Pin Assignments and Descriptions

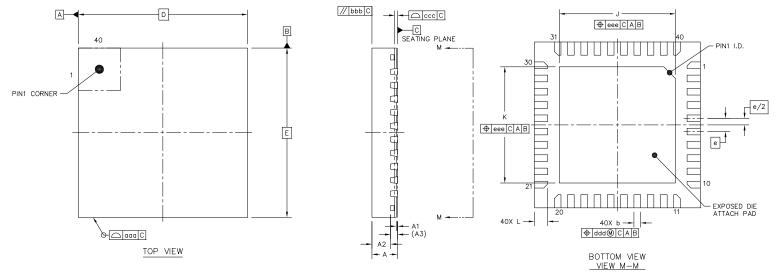

# 1.1 40-Pin QFN (Top-Down, Through-Package View)

Figure 1-1. Top-Down (Through-Package) View-QFN 40-Pin Diagram

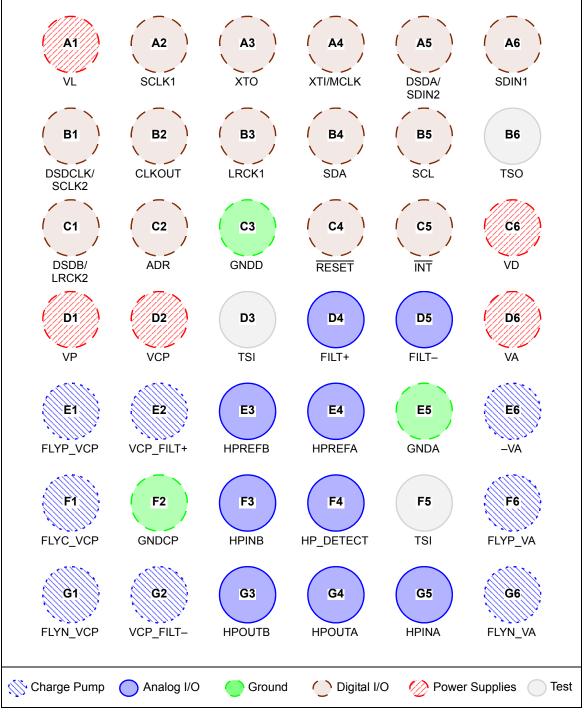

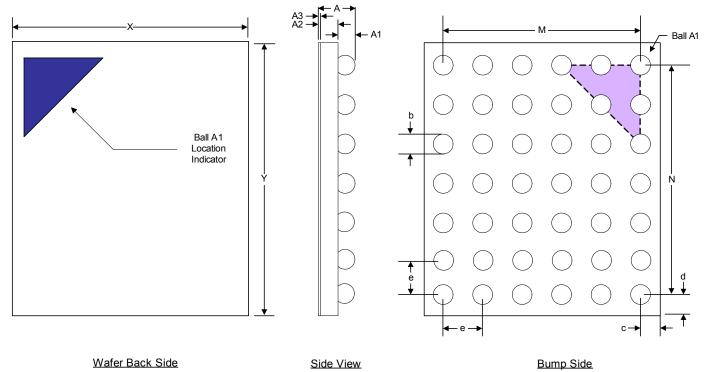

## 1.2 42-Ball WLCSP (Top-down, Through-Package View)

Figure 1-2. Top-Down (Through-Package) View—42-Ball WLCSP Package

# 1.3 Pin Descriptions

### Table 1-1. Pin Descriptions

| Pin Name         | QFN<br>Pin # | WLCSP<br>Ball | Power<br>Supply |     | Pin Description                                                                                                                                            | Internal<br>Connection | Digital I/O<br>Driver        | Digital I/O<br>Receiver        |

|------------------|--------------|---------------|-----------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------------------------|--------------------------------|

|                  |              |               |                 |     | Digital I/O                                                                                                                                                |                        |                              |                                |

| ADR              | 30           | C2            | VL              | Ι   | Address Bit (I <sup>2</sup> C). In I <sup>2</sup> C Mode, ADR is a chip address pin.                                                                       | —                      | —                            | —                              |

| CLKOUT           | 33           | B2            | VL              | 0   | <b>CLK Output.</b> Single-ended clock output sourced from PLL or buffered crystal.                                                                         | Weak<br>pull-down      | CMOS<br>output               | —                              |

| SCLK1            | 34           | A2            | VL              | I/O | Serial Audio Input Bit Clock 1. Serial bit clock for audio data on the SDIN pins.                                                                          | Weak<br>pull-down      | CMOS<br>output               | Hysteresis<br>on CMOS<br>input |

| LRCK1            | 38           | B3            | VL              | I/O | Serial Audio Input Left/Right Clock. Word-rate clock for the audio data on the SDIN pins.                                                                  | Weak<br>pull-down      | CMOS<br>output               | Hysteresis<br>on CMOS<br>input |

| SDIN1            | 2            | A6            | VL              | Ι   | Serial Audio Input Data Port. Audio data serial input pin 1.                                                                                               | Weak<br>pull-down      | _                            | Hysteresis<br>on CMOS<br>input |

| DSDA/<br>SDIN2   | 40           | A5            | VL              | Ι   | <b>DSD Data Input A/Serial Data In 2.</b> DSD audio or PCM audio data serial input pin 2.                                                                  | Weak<br>pull-down      | —                            | Hysteresis<br>on CMOS<br>input |

| DSDB/<br>LRCK2   | 29           | C1            | VL              |     | DSD Data Input B/Serial Audio Input Left/Right Clock 2. DSD audio data serial input pin or word rate clock for the audio data on the SDIN2 pin.            | Weak<br>pull-down      | CMOS<br>output               | Hysteresis<br>on CMOS<br>input |

| DSDCLK/<br>SCLK2 | 32           | B1            | VL              | I/O | <b>DSD Clock Input/Serial Audio Input Bit Clock 2.</b> DSD clock input. Serial bit clock for audio data on the SDIN2 pin.                                  | Weak<br>pull-down      | CMOS<br>output               | Hysteresis<br>on CMOS<br>input |

| INT              | 27           | C5            | VP              | 0   | <b>Interrupt.</b> When pulled up, works as system interrupt pin. Open drain, active low programmable.                                                      | —                      | CMOS<br>open-drain<br>output | _                              |

| RESET            | 28           | C4            | VP              | I   | System Reset. The device enters system reset when enabled.                                                                                                 | _                      | _                            | Hysteresis<br>on CMOS<br>input |

| SDA              | 39           | B4            | VL              | I/O | Serial Control Data I/O (I <sup>2</sup> C). In I <sup>2</sup> C Mode, SDA is the control I/O data line.                                                    | _                      | CMOS<br>open-drain<br>output | Hysteresis<br>on CMOS<br>input |

| SCL              | 1            | B5            | VL              | Ι   | <b>Software Clock (I<sup>2</sup>C).</b> Serial control interface clock used to clock control data bits into and out of the CS43130.                        | _                      | _                            | Hysteresis<br>on CMOS<br>input |

| XTI/MCLK         | 37           | A4            | VL              | I   | <b>Crystal/Oscillator Input/MCLK In.</b> Crystal or digital clock input for the master clock.                                                              | Weak<br>pull-down      | _                            | Hysteresis<br>on CMOS<br>input |

| XTO              | 36           | A3            | VL              | 0   | Crystal/Oscillator Output. Crystal output.                                                                                                                 | Weak<br>pull-down      | CMOS<br>output               | _                              |

|                  |              |               |                 |     | Analog I/O 🔵                                                                                                                                               |                        |                              |                                |

| FILT+            | 5            | D4            | VA              | 0   | Positive/Negative Voltage Reference. Positive/negative                                                                                                     | _                      | _                            | _                              |

| FILT-            | 6            | D5            |                 |     | reference voltage for DAC.                                                                                                                                 |                        |                              |                                |

| HP_<br>DETECT    | 22           | F4            | VP              | I   | <b>Headphone Detect.</b> Can be configured to be debounced on unplugged and plugged events before it is presented as a noninterrupt status bit (HPDETECT). | _                      | Hi-Z                         | _                              |

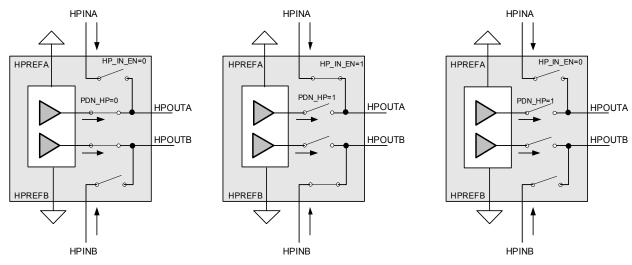

| HPINB            | 15           | F3            | VCP_            | Ι   | Headphone Audio Input. For interfacing low power audio source,                                                                                             | Weak                   |                              | _                              |

| HPINA            | 12           | G5            | FILT±           |     | an alternate analog input path for the headphone output. Refer to analog specification table for full-scale input level.                                   | pull-down              |                              |                                |

| HPOUTB           | 16           | G3            | VCP_            | 0   | Headphone Audio Output. Refer to analog specification table for                                                                                            | _                      | _                            |                                |

| HPOUTA           | 14           | G4            | FILT±           |     | full-scale output level.                                                                                                                                   |                        |                              |                                |

| HPREFB<br>HPREFA | 17<br>13     | E3<br>E4      | VCP_<br>FILT±   | I   | Headphone Output Reference. Reference for headphone amplifier and detect.                                                                                  | —                      | _                            | _                              |

|                  |              |               |                 |     | Power Supplies 🥢                                                                                                                                           |                        |                              |                                |

|                  |              |               |                 |     |                                                                                                                                                            |                        |                              |                                |

| Pin Name  | QFN<br>Pin # | WLCSP<br>Ball | Power<br>Supply         |     | Pin Description                                                                                                                                                                           | Internal<br>Connection | Digital I/O<br>Driver | Digital I/C<br>Receiver |

|-----------|--------------|---------------|-------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----------------------|-------------------------|

| VD        | 4            | C6            | N/A                     | I   | <b>Internal Digital Power.</b> Internal digital power supply, typically +1.8 V.                                                                                                           |                        |                       |                         |

| VA        | 7            | D6            | N/A                     | Ι   | Analog Power. Power supply for the internal analog section.                                                                                                                               | —                      | —                     | _                       |

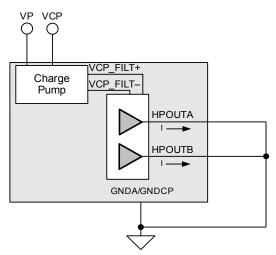

| VCP       | 25           | D2            | N/A                     | I   | <b>Charge Pump Supply.</b> Provides charge pump voltage to the headphone Class H analog output circuit.                                                                                   | _                      | _                     |                         |

| VP        | 26           | D1            | N/A                     | I   | <b>Battery supply</b> . Provides voltage to the headphone Class H circuit.                                                                                                                | _                      | _                     |                         |

|           |              |               |                         |     | Ground 🔴                                                                                                                                                                                  |                        |                       |                         |

| GNDD      | 35           | C3            | N/A                     | Ι   | <b>Digital and I/O Ground.</b> Ground for the I/O and core logic. GNDA, GNDCP, and GNDD must be connected to a common ground area under the chip.                                         | _                      | _                     | _                       |

| GNDA      | 8            | E5            | N/A                     | I   | <b>Analog Ground.</b> Ground reference for the internal analog section.<br>GNDA, GNDCP, and GNDD must be connected to a common<br>ground area under the chip.                             | _                      | _                     | _                       |

| GNDCP     | 19           | F2            | N/A                     | I   | <b>Charge Pump Ground.</b> Ground reference for the charge pump section. GNDA, GNDCP, and GNDD must be connected to a common ground area under the chip.                                  | _                      | _                     | _                       |

|           |              |               |                         |     | Charge Pump 🚫                                                                                                                                                                             |                        |                       |                         |

| VCP_FILT+ | 21           | E2            | VCP/                    | I/O |                                                                                                                                                                                           | —                      | _                     | —                       |

| VCP_FILT- | 18           | G2            | VP 1                    |     | the inverting charge pump that provides the positive/negative rail<br>for the analog output. When operating in external VCP_FILT<br>mode, these pins can directly take in supply voltage. |                        |                       |                         |

| –VA       | 9            | E6            | VA                      | 0   | VA Negative Charge Pump Output. Negative charge pump output for DAC rail. It is derived from VA.                                                                                          | _                      | —                     | _                       |

| FLYP_VA   | 10           | F6            | VA                      | 0   |                                                                                                                                                                                           | —                      | _                     | _                       |

| FLYN_VA   | 11           | G6            |                         |     | negative nodes for the DAC negative charge pump's flying capacitor.                                                                                                                       |                        |                       |                         |

| FLYP_VCP  | 24           | E1            | VCP/<br>VP 1            | 0   | <b>-VCP Charge Pump Cap Positive Node</b> . Positive node for the analog output negative charge pump's flying capacitor.                                                                  |                        | _                     | _                       |

| FLYC_VCP  | 23           | F1            | VCP/<br>VP <sup>1</sup> | 0   | -VCP Charge Pump Cap Center Node. Center node for the analog output negative charge pump's flying capacitor.                                                                              |                        | —                     | —                       |

| FLYN_VCP  | 20           | G1            | VCP_<br>FILT±           | 0   | <b>-VCP Charge Pump Cap Negative Node.</b> Negative node for the analog output negative charge pump's flying capacitor.                                                                   |                        | —                     | —                       |

|           |              |               |                         |     | Test                                                                                                                                                                                      |                        |                       |                         |

| TSO       | 3            | B6            | N/A                     | I/O | Test Output.                                                                                                                                                                              | —                      | —                     | —                       |

| TSI       | _            | D3, F5        |                         |     | Test Input.                                                                                                                                                                               |                        | _                     |                         |

#### Table 1-1. Pin Descriptions (Cont.)

1. The power supply is determined by ADPT\_PWR setting (see Section 4.3.1). VP is used if ADPT\_PWR = 001 (VP\_LDO Mode) or when necessary for ADPTPWR = 111 (Adapt-to-Signal Mode).

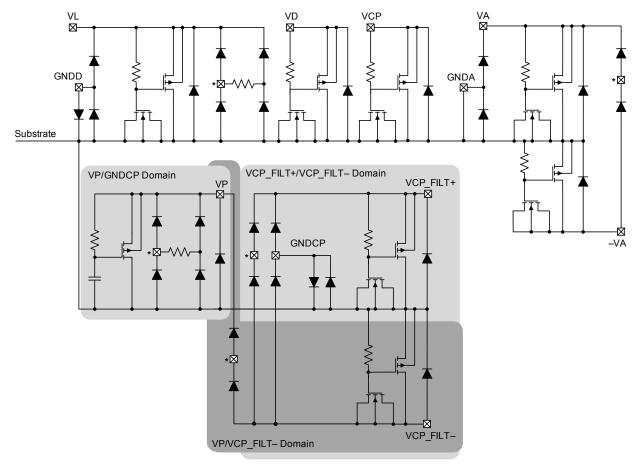

## 1.4 Electrostatic Discharge (ESD) Protection Circuitry

ESD-sensitive device. The CS43130 is manufactured on a CMOS process. Therefore, it is generically susceptible to damage from excessive static voltages. Proper ESD precautions must be taken while handling and storing this device. This device is qualified to current JEDEC ESD standards.

Fig. 1-3 provides a composite view of the ESD domains showing the ESD protection paths between each pad and the substrate (GND), as well as the interrelations between some domains. Note that this figure represents the structure for the internal protection devices and that additional protections can be implemented as part of the integration into the board.

Figure 1-3. Composite ESD Topology

Table 1-2 shows the individual ESD domains and lists the pins associated with each domain.

Table 1-2. ESD Domains

| ESD Domain | Signal Name<br>(See * in Topology Figures for Pad)                                                                    | Тороlоду  |

|------------|-----------------------------------------------------------------------------------------------------------------------|-----------|

| VL/GNDD    | ADR<br>DSDCLK/SCLK2<br>SCL<br>SDA<br>DSDB/LRCK2<br>DSDA/SDIN2<br>SDIN1<br>LRCK1<br>SCLK1<br>CLKOUT<br>XTI/MCLK<br>XTO | Substrate |

## Table 1-2. ESD Domains (Cont.)

| ESD Domain                                          | Signal Name<br>(See * in Topology Figures for Pad)                                                                       | Тороlоду                                                                              |

|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

| VA/–VA                                              | FLYN_VA<br>FLYP_VA<br>FILT+<br>FILT-                                                                                     | Substrate                                                                             |

| VP/GNDCP<br>VP/VCP_FILT-<br>VCP_FILT+/<br>VCP_FILT- | RESET<br>INT<br>FLYP_VCP<br>FLYC_VCP<br>HP_DETECT<br>FLYN_VCP<br>HPINA<br>HPOUTA<br>HPOUTA<br>HPOUTB<br>HPREFA<br>HPREFB | VP/GNDCP Domain<br>VCP_FILT+/VCP_FILT- Domain<br>VCP_FILT+<br>GNDCP<br>+<br>Substrate |

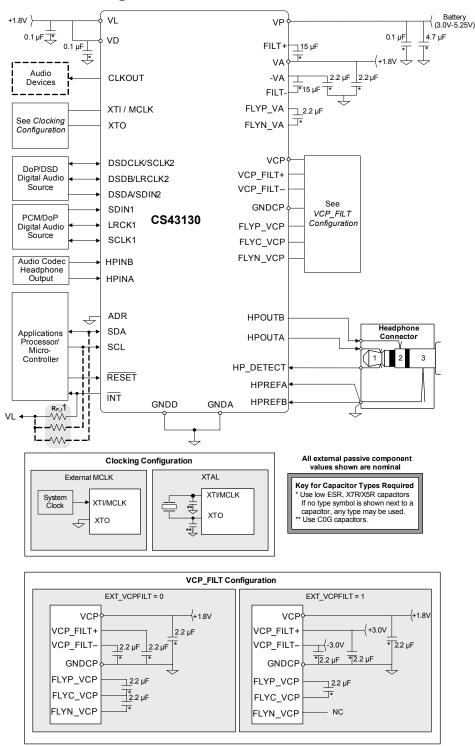

## 2 Typical Connection Diagram

#### Figure 2-1. Typical Connection Diagram

#### **Note:** 1. The value for $R_{P,I}$ can be determined by the interrupt pin specification in Table 3-11.

# **3** Characteristics and Specifications

Table 3-1 defines parameters as they are characterized in this section.

#### Table 3-1. Parameter Definitions

| Parameter                                       | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Dynamic range                                   | The ratio of the rms value of the signal to the rms sum of all other spectral components over the specified bandwidth. A signal-to-noise ratio measurement over the specified bandwidth made with a –60-dB signal; 60 dB is added to resulting measurement to refer the measurement to full scale. This technique ensures that distortion components are below the noise level and do not affect the measurement. This measurement technique has been accepted by the Audio Engineering Society, AES17–1991, and the Electronic Industries Association of Japan, EIAJ CP–307. Dynamic range is expressed in decibel units. |

| Gain drift                                      | The change in gain value with temperature, expressed in ppm/°C units.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Idle channel noise                              | The rms value of the signal with no input applied (properly back-terminated analog input, digital zero, or zero modulation input). Measured over the specified bandwidth.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Interchannel gain<br>mismatch                   | The gain difference between left and right channel pairs. Interchannel gain mismatch is expressed in decibel units.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Interchannel<br>phase mismatch                  | The phase difference between left and right channel pairs at 997-Hz sine wave input. Interchannel phase mismatch is expressed in degree units (with respect to 997-Hz sine wave input).                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Interchannel<br>isolation                       | A measure of cross talk between the left and right channel pairs. Interchannel isolation is measured for each channel at the converter's output with no signal to the input under test and a full-scale signal applied to the other channel. Interchannel isolation is expressed in decibel units.                                                                                                                                                                                                                                                                                                                         |

| Load resistance<br>and capacitance              | The recommended minimum resistance and maximum capacitance required for the internal op-amp's stability and signal integrity. The load capacitance effectively moves the band-limiting pole of the amp in the output stage. Increasing load capacitance beyond the recommended value can cause the internal op-amp to become unstable.                                                                                                                                                                                                                                                                                     |

| Output offset<br>voltage                        | The DC offset voltage present at the amplifier's output when its input signal is in a mute state. The offset exists due to CMOS process limitations and is proportional to analog volume settings. When measuring the offset out of the headphone amplifier, the headphone amplifier is ON.                                                                                                                                                                                                                                                                                                                                |

| Total harmonic<br>distortion + noise<br>(THD+N) | The ratio of the rms sum of distortion and noise spectral components across the specified bandwidth (typically 20 Hz–20 kHz) relative to the rms value of the signal. THD+N is measured at –1 and –20 dBFS for the analog input and at 0 and –20 dB for the analog output, as suggested in AES17–1991 Annex A. THD+N is expressed in decibel units.                                                                                                                                                                                                                                                                        |

| Turn-on time                                    | Turn-on time is measured from when the PDN_HP = 0 ACK signal is received to when the signal appears on the HP output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

### Table 3-2. Recommended Operating Conditions

GNDD = GNDA= GNDCP = 0 V, all voltages with respect to ground.

|                                                | Parameters           | 1                                                                                                         | Symbol                                                  | Minimum                                                      | Maximum                                                         | Units            |

|------------------------------------------------|----------------------|-----------------------------------------------------------------------------------------------------------|---------------------------------------------------------|--------------------------------------------------------------|-----------------------------------------------------------------|------------------|

| DC power supply                                | Analog               |                                                                                                           | VA                                                      | 1.66                                                         | 1.94                                                            | V                |

|                                                | Charge pump          |                                                                                                           | VCP                                                     | 1.66                                                         | 1.94                                                            | V                |

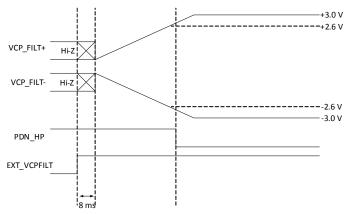

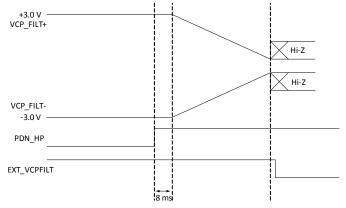

|                                                | Filtered charge pump | EXT_VCPFLT = 1                                                                                            | VCP_FILT+                                               | 2.85                                                         | 3.15                                                            | V                |

|                                                |                      |                                                                                                           | VCP_FILT-                                               | -3.15                                                        | -2.85                                                           | V                |

|                                                | Battery supply       | HV_EN = 0, EXT_VCPFILT = 0<br>HV_EN = 1, EXT_VCPFILT = 0<br>EXT_VCPFILT = 1                               |                                                         | 3.0<br>3.3<br>3.3                                            | 5.25<br>5.25<br>5.25                                            | V<br>V<br>V      |

|                                                | Digital Interface    |                                                                                                           | VL                                                      | 1.66                                                         | 1.94                                                            | V                |

|                                                | Digital Internal     |                                                                                                           | VD                                                      | 1.66                                                         | 1.94                                                            | V                |

| External voltage applied to pin <sup>2,3</sup> |                      | HP_DETECT pin<br>VCP_FILT± domain pins <sup>4</sup><br>VL domain pins<br>VA domain pins<br>VP domain pins | V <sub>VCPF</sub><br>V <sub>VL</sub><br>V <sub>VA</sub> | -0.3 - VCP_FILT-<br>-0.3 - VCP_FILT-<br>-0.3<br>-0.3<br>-0.3 | VP + 0.3<br>0.3 + VCP_FILT+<br>VL + 0.3<br>VA + 0.3<br>VP + 0.3 | V<br>V<br>V<br>V |

| Ambient temperatur                             | re                   |                                                                                                           | T <sub>A</sub>                                          | -10                                                          | +70                                                             | °C               |

1. Device functional operation is guaranteed within these limits. Functionality is not guaranteed or implied outside of these limits. Operation outside of these limits may adversely affect device reliability.

2. The maximum over/undervoltage is limited by the input current.

3. Table 1-1 lists the power supply domain in which each CS43130 pin resides.

4.VCP\_FILT± is specified in Table 3-16.

#### Table 3-3. Absolute Maximum Ratings

GNDD = GNDA= GNDCP = 0 V; all voltages with respect to ground.

| Parameters                                    |                                 | Symbol           | Minimum | Maximum | Units |

|-----------------------------------------------|---------------------------------|------------------|---------|---------|-------|

| DC power supply                               | Analog                          | VA               | -0.3    | 2.33    | V     |

|                                               | Battery                         | VP               | -0.3    | 6.3     | V     |

|                                               | Charge pump                     | VCP              | -0.3    | 2.33    | V     |

|                                               | Filtered charge pump (positive) | VCP_FILT+        | -0.3    | 3.3     | V     |

|                                               | Filtered charge pump (negative) | VCP_FILT-        | 0.3     | -3.3    | V     |

|                                               | Digital interface               | VL               | -0.3    | 2.33    | V     |

|                                               | Digital internal                | VD               | -0.3    | 2.33    | V     |

| Input current <sup>1</sup>                    |                                 | l <sub>in</sub>  | _       | ±10     | mA    |

| Ambient operating temperature (power applied) |                                 | T <sub>A</sub>   | -50     | +115    | °C    |

| Storage temperature                           |                                 | T <sub>stg</sub> | -65     | +150    | °C    |

**Caution:** Stresses beyond "Absolute Maximum Ratings" levels may cause permanent damage to the device. These levels are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in Table 3-2, "Recommended Operating Conditions" is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

1. Any pin except supplies and HPINx. Transient currents of up to ±100 mA on the analog input pins do not cause SCR latch-up.

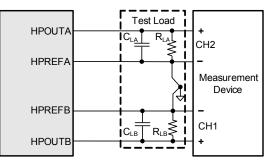

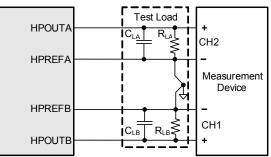

#### Table 3-4. Analog Output Characteristics (HV\_EN = 1) 1

Test conditions (unless otherwise specified): Fig. 2-1 shows CS43130 connections; input test signal is a 32-bit, full-scale 997-Hz sine wave (unless specified otherwise); GNDA = GNDCP = GNDD = 0 V; voltages are with respect to ground; HV\_EN = 1; ASP\_M/Sb = 1; typical, min/max performance data taken with VA = VCP = 1.8 V; VL = VD = 1.8 V; VP = 3.6 V; TA = +25°C; measurement bandwidth is 20 Hz–20 kHz; ASP\_SPRATE = 0001 (LRCK = 44.1-kHz mode); PDN\_XTAL = 0, MCLK\_INT = 1, and MCLK\_SRC\_SEL = 00 (crystal frequency f<sub>XTAL</sub> = 22.5792 MHz); Volume = 0 dB; when testing in DSD processor mode, DSD\_ZERODB = 1; when testing noise related specifications (dynamic range, THD+N, idle channel noise), no external impedance on HPREFx.

|                                                                            | PCM and DSD Process                                          | or Mode Parameter <sup>2,3,4</sup> |                                                      | Minimum                | Typical                                 | Maximum                           | Units                            |

|----------------------------------------------------------------------------|--------------------------------------------------------------|------------------------------------|------------------------------------------------------|------------------------|-----------------------------------------|-----------------------------------|----------------------------------|

| HPOUTx<br>R <sub>L</sub> = 10 kΩ<br>C <sub>L</sub> = 200 pF<br>OUT_FS = 11 | Dynamic range<br>(defined in Table 3-1)                      | 24-bit, 32-bit, DSD<br>16-bit      | A-weighted<br>Unweighted<br>A-weighted<br>Unweighted | 124<br>121<br>91<br>88 | 130<br>127<br>97<br>94                  | <br>                              | dB<br>dB<br>dB<br>dB             |

| Volume = 0 dB <sup>5</sup> ,<br>unless otherwise<br>specified              | THD+N<br>(defined in Table 3-1)                              | 24-bit, 32-bit, DSD<br>16-bit      | 0 dB<br>-20 dB<br>-60 dB<br>0 dB<br>-20 dB<br>-60 dB |                        | -108<br>-97<br>-67<br>-94<br>-74<br>-34 | -101<br><br>-61<br>-88<br><br>-28 | dB<br>dB<br>dB<br>dB<br>dB<br>dB |

|                                                                            | Idle channel noise<br>(A-weighted)<br>(defined in Table 3-1) | 24-bit, 32-bit, DSD                |                                                      | _                      | 0.55                                    | —                                 | μV                               |

|                                                                            | Full-scale output voltage                                    | 9                                  |                                                      | 4.66                   | 4.90                                    | 5.14                              | Vpp                              |

|                                                                            | Interchannel isolation 6(                                    | defined in Table 3-1)              | 217 Hz<br>1 kHz<br>20 kHz                            |                        | 110<br>95<br>68                         | —<br>—<br>—                       | dB<br>dB<br>dB                   |

| HPOUTx<br>$R_L = 600 \Omega$<br>$C_L = 200 pF$<br>$OUT_FS = 11$            | Dynamic range<br>(defined in Table 3-1)                      | 24-bit, 32-bit, DSD<br>16-bit      | A-weighted<br>Unweighted<br>A-weighted<br>Unweighted | 124<br>121<br>91<br>88 | 130<br>127<br>97<br>94                  |                                   | dB<br>dB<br>dB<br>dB             |

| Volume = 0 dB <sup>5</sup> ,<br>unless otherwise<br>specified              | THD+N<br>(defined in Table 3-1)                              | 24-bit, 32-bit, DSD<br>16-bit      | 0 dB<br>-20 dB<br>-60 dB<br>0 dB<br>-20 dB<br>-60 dB |                        | -108<br>-97<br>-67<br>-94<br>-74<br>-34 | -101<br>61<br>88<br>              | dB<br>dB<br>dB<br>dB<br>dB<br>dB |

|                                                                            | Idle channel noise<br>(A-weighted)<br>(defined in Table 3-1) | 24-bit, 32-bit, DSD                |                                                      | _                      | 0.55                                    | —                                 | μV                               |

|                                                                            | Full-scale output voltage                                    | 9                                  |                                                      | 4.66                   | 4.90                                    | 5.14                              | Vpp                              |

|                                                                            | Output power                                                 |                                    |                                                      | —                      | 5                                       | —                                 | mW                               |

|                                                                            | Interchannel isolation <sup>6</sup> (                        | defined in Table 3-1)              | 217 Hz<br>1 kHz<br>20 kHz                            |                        | 110<br>95<br>68                         |                                   | dB<br>dB<br>dB                   |

#### Table 3-4. Analog Output Characteristics (HV\_EN = 1) 1 (Cont.)

Test conditions (unless otherwise specified): Fig. 2-1 shows CS43130 connections; input test signal is a 32-bit, full-scale 997-Hz sine wave (unless specified otherwise); GNDA = GNDCP = GNDD = 0 V; voltages are with respect to ground; HV\_EN = 1; ASP\_M/Sb = 1; typical, min/max performance data taken with VA = VCP = 1.8 V; VL = VD = 1.8 V; VP = 3.6 V; TA = +25°C; measurement bandwidth is 20 Hz–20 kHz; ASP\_SPRATE = 0001 (LRCK = 44.1-kHz mode); PDN\_XTAL = 0, MCLK\_INT = 1, and MCLK\_SRC\_SEL = 00 (crystal frequency  $f_{XTAL}$  = 22.5792 MHz); Volume = 0 dB; when testing in DSD processor mode, DSD\_ZERODB = 1; when testing noise related specifications (dynamic range, THD+N, idle channel noise), no external impedance on HPREFx.

|                       | PCM and DSD Processor Mode Parameter <sup>2,3,4</sup> |            | Minimum | Typical | Maximum | Units  |

|-----------------------|-------------------------------------------------------|------------|---------|---------|---------|--------|

| Other characteristics | Interchannel gain mismatch (defined in Table 3-1)     |            | —       | ±0.1    | —       | dB     |

| for HPOUTx            | Interchannel phase mismatch (defined in Table 3-1)    |            | —       | ±0.05   | —       | ٥      |

|                       | Output offset voltage: Mute (defined in Table 3-1)    |            | _       | ±0.5    | ±1      | mV     |

|                       | Gain drift (defined in Table 3-1)                     |            | _       | ±100    | _       | ppm/°C |

|                       | Load resistance (RL)                                  |            | 600     | _       | _       | Ω      |

|                       | Load capacitance (CL)                                 |            | _       | _       | 1       | nF     |

|                       | Turn-on time (defined in Table 3-1)                   |            | _       | _       | 10      | ms     |

|                       | Click/pop during PDN_HP enable or disable             | A-weighted | _       | _       | -60     | dBV    |

1. This table also applies to external VCP\_FILT supply mode: CS43130 power up procedure is per description in Section 5.10.1; EXT\_VCPFILT = 1;

VCP\_FILT+ and VCP\_FILT- comply to Table 3-2 when EXT\_VCPFILT = 1; in this mode, HV\_EN setting becomes don't care.

2.One LSB of triangular PDF dither is added to PCM data.

3. Referred to the typical full-scale voltage. Applies to all THD+N and dynamic range values in the table.

4.DSD performance may be limited by the source recording. 0 dB-SACD = 50% modulation index.

5. The volume must be configured as indicated to achieve specified output characteristics.

6. Output test configuration. Symbolized component values are specified in the test conditions.

#### Table 3-5. Analog Output Characteristics (HV\_EN = 0) <sup>1</sup>

Test conditions (unless otherwise specified): Fig. 2-1 shows CS43130 connections; input test signal is a 32-bit, full-scale 997-Hz sine wave (unless specified otherwise); GNDA = GNDCP = GNDD = 0 V; voltages are with respect to ground; HV\_EN = 0; ASP\_M/Sb = 1; typical, min/max performance data taken with VA = VCP = 1.8 V; VL = VD = 1.8 V; VP = 3.6 V; TA =  $+25^{\circ}$ C; measurement bandwidth is 20 Hz–20 kHz; ASP\_SPRATE = 0001 (LRCK = 44.1-kHz mode); PDN\_XTAL = 0, MCLK\_INT = 1, and MCLK\_SRC\_SEL = 00 (crystal frequency f<sub>XTAL</sub> = 22.5792 MHz); Volume = 0 dB; when testing in DSD processor mode, DSD\_ZERODB = 1; when testing noise related specifications (dynamic range, THD+N, idle channel noise), no external impedance on HPREFx.

|                                                                                                                                                                                                                                                                                    | PCM and DSD Process                                          | or Mode Parameter 2,3,4 |                           | Minimum | Typical           | Maximum         | Units          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|-------------------------|---------------------------|---------|-------------------|-----------------|----------------|

| $\begin{array}{c} R_{L} = 10 \ k\Omega \\ C_{L} = 200 \ pF \\ OUT_{L}FS = 10 \\ Volume = 0 \ dB,^5 \\ unless otherwise \\ specified \\ \end{array} \\ \hline \begin{array}{c} THD+N \\ (defined) \\ \end{array} \\ \hline \\ Idle char \\ (defined) \\ \end{array} \\ \end{array}$ | Dynamic range<br>(defined in Table 3-1)                      | 24-bit, 32-bit, DSD     | A-weighted<br>Unweighted  |         | 128<br>125        | —               | dB<br>dB       |

|                                                                                                                                                                                                                                                                                    |                                                              | 16-bit                  | A-weighted<br>Unweighted  | 91      | 97<br>94          |                 | dB<br>dB       |

|                                                                                                                                                                                                                                                                                    | THD+N<br>(defined in Table 3-1)                              | 24-bit, 32-bit, DSD     | 0 dB<br>–20 dB<br>–60 dB  | —       | 109<br>95<br>65   | -103<br><br>-59 | dB<br>dB<br>dB |

|                                                                                                                                                                                                                                                                                    |                                                              | 16-bit                  | 0 dB<br>-20 dB<br>-60 dB  | _       | -94<br>-74<br>-34 | -88<br>         | dB<br>dB<br>dB |

|                                                                                                                                                                                                                                                                                    | Idle channel noise<br>(A-weighted)<br>(defined in Table 3-1) | 24-bit, 32-bit, DSD     |                           | _       | 0.55              | —               | μV             |

|                                                                                                                                                                                                                                                                                    | Full-scale output voltage                                    | 9                       |                           | 3.76    | 3.96              | 4.16            | Vpp            |

|                                                                                                                                                                                                                                                                                    | Interchannel isolation 6                                     | (defined in Table 3-1)  | 217 Hz<br>1 kHz<br>20 kHz | —       | 110<br>94<br>68   |                 | dB<br>dB<br>dB |

#### Table 3-5. Analog Output Characteristics (HV\_EN = 0) <sup>1</sup> (Cont.)

Test conditions (unless otherwise specified): Fig. 2-1 shows CS43130 connections; input test signal is a 32-bit, full-scale 997-Hz sine wave (unless specified otherwise); GNDA = GNDCP = GNDD = 0 V; voltages are with respect to ground; HV\_EN = 0; ASP\_M/Sb = 1; typical, min/max performance data taken with VA = VCP = 1.8 V; VL = VD = 1.8 V; VP = 3.6 V; TA = +25°C; measurement bandwidth is 20 Hz–20 kHz; ASP\_SPRATE = 0001 (LRCK = 44.1-kHz mode); PDN\_XTAL = 0, MCLK\_INT = 1, and MCLK\_SRC\_SEL = 00 (crystal frequency f<sub>XTAL</sub> = 22.5792 MHz); Volume = 0 dB; when testing in DSD processor mode, DSD\_ZERODB = 1; when testing noise related specifications (dynamic range, THD+N, idle channel noise), no external impedance on HPREFx.

|                                                             | PCM and DSD Process                                          | or Mode Parameter <sup>2,3,</sup> | 4                                      | Minimum          | Typical            | Maximum        | Units          |

|-------------------------------------------------------------|--------------------------------------------------------------|-----------------------------------|----------------------------------------|------------------|--------------------|----------------|----------------|

| HPOUTx;<br>R <sub>L</sub> = 600 Ω                           | Dynamic range (defined in Table 3-1)                         | 24-bit, 32-bit, DSD               | A-weighted<br>Unweighted               | 122<br>119       | 128<br>125         | _              | dB<br>dB       |

| $C_L^- = 200 \text{ pF}$<br>OUT_FS = 10<br>Volume = 0 dB.   |                                                              | 16-bit                            | A-weighted<br>Unweighted               | 91<br>88         | 97<br>94           | —              | dB<br>dB       |

| unless otherwise<br>specified                               | THD+N<br>(defined in Table 3-1)                              | 24-bit, 32-bit, DSD               | 0 dB<br>–20 dB                         | _                | -109<br>-95        | -103<br>       | dB<br>dB       |

|                                                             |                                                              | 16-bit                            | –60 dB<br>0 dB<br>–20 dB               | _                | 65<br>94<br>74     | -59<br>-88     | dB<br>dB<br>dB |

|                                                             |                                                              |                                   | -20 dB<br>-60 dB                       | _                | -34                |                | dB             |

|                                                             | Idle channel noise<br>(A-weighted)<br>(defined in Table 3-1) | 24-bit, 32-bit, DSD               |                                        | _                | 0.55               | _              | μV             |

|                                                             | Full-scale output voltage                                    | e                                 |                                        | 3.76             | 3.96               | 4.16           | Vpp            |

|                                                             | Output power                                                 |                                   |                                        | —                | 3.3                | —              | mW             |

|                                                             | Interchannel isolation <sup>6</sup>                          | (defined in Table 3-1)            | 217 Hz<br>1 kHz<br>20 kHz              |                  | 110<br>94<br>68    |                | dB<br>dB<br>dB |

| HPOUTx;<br>R <sub>L</sub> = 32 Ω<br>C <sub>L</sub> = 200 pF | Dynamic range<br>(defined in Table 3-1)                      | 24-bit, 32-bit, DSD<br>16-bit     | A-weighted<br>Unweighted<br>A-weighted | 119<br>116<br>91 | 125<br>122<br>97   | —              | dB<br>dB<br>dB |

| OUT_FS = 01<br>Volume = 0 dB,                               |                                                              | ТО-Ы                              | Unweighted                             | 88               | 97<br>94           | _              | dB             |

|                                                             | THD+N<br>(defined in Table 3-1)                              | 24-bit, 32-bit, DSD               | 0 dB<br>–20 dB<br>–60 dB               |                  | -106<br>-92<br>-62 | -96<br><br>-56 | dB<br>dB<br>dB |

|                                                             |                                                              | 16-bit                            | 0 dB<br>-20 dB<br>-60 dB               |                  | -94<br>-74<br>-34  | -88<br><br>-28 | dB<br>dB<br>dB |

|                                                             | Idle channel noise<br>(A-weighted)<br>(defined in Table 3-1) | 24-bit, 32-bit, DSD               |                                        | _                | 0.55               | _              | μV             |

|                                                             | Full-scale output voltage                                    | 9                                 |                                        | 2.68             | 2.81               | 2.96           | Vpp            |

|                                                             | Output power                                                 |                                   |                                        | _                | 30.8               | _              | mW             |

|                                                             | Interchannel isolation <sup>6</sup>                          | defined in Table 3-1)             | 217 Hz<br>1 kHz<br>20 kHz              |                  | 110<br>90<br>66    |                | dB<br>dB<br>dB |

| HPOUTx;<br>R <sub>L</sub> = 16 Ω<br>C <sub>L</sub> = 200 pF | Dynamic range<br>(defined in Table 3-1)                      | 24-bit, 32-bit<br>16-bit          | A-weighted<br>Unweighted<br>A-weighted | 113<br>110<br>89 | 119<br>116<br>95   |                | dB<br>dB<br>dB |

| OUT_FS = 00<br>Volume = 0 dB,                               |                                                              |                                   | Unweighted                             | 86               | 92                 | —              | dB             |

| unless otherwise specified                                  | THD+N<br>(defined in Table 3-1)                              | 24-bit, 32-bit, DSD               | 0 dB<br>–20 dB<br>–60 dB               | _                | -100<br>-86<br>-56 | -94<br><br>-50 | dB<br>dB<br>dB |

|                                                             |                                                              | 16-bit                            | 0 dB<br>-20 dB<br>-60 dB               |                  | -94<br>-74<br>-34  | -88<br>        | dB<br>dB<br>dB |

|                                                             | Idle channel noise<br>(A-weighted)<br>(defined in Table 3-1) | 24-bit, 32-bit, DSD               |                                        | _                | 0.55               | _              | μV             |

|                                                             | Full-scale output voltage                                    | 9                                 |                                        | 1.34             | 1.41               | 1.48           | Vpp            |

|                                                             | Output power                                                 |                                   |                                        | _                | 15.6               | _              | mW             |

|                                                             | Interchannel isolation <sup>6</sup>                          | (defined in Table 3-1)            | 217 Hz<br>1 kHz                        | _                | 110<br>83          | _              | dB<br>dB       |

|                                                             |                                                              |                                   | 20 kHz                                 | _                | 58                 | —              | dB             |

#### Table 3-5. Analog Output Characteristics (HV\_EN = 0) 1 (Cont.)

Test conditions (unless otherwise specified): Fig. 2-1 shows CS43130 connections; input test signal is a 32-bit, full-scale 997-Hz sine wave (unless specified otherwise); GNDA = GNDCP = GNDD = 0 V; voltages are with respect to ground; HV\_EN = 0; ASP\_M/Sb = 1; typical, min/max performance data taken with VA = VCP = 1.8 V; VL = VD = 1.8 V; VP = 3.6 V; TA = +25°C; measurement bandwidth is 20 Hz–20 kHz; ASP\_SPRATE = 0001 (LRCK = 44.1-kHz mode); PDN\_XTAL = 0, MCLK\_INT = 1, and MCLK\_SRC\_SEL = 00 (crystal frequency  $f_{XTAL}$  = 22.5792 MHz); Volume = 0 dB; when testing in DSD processor mode, DSD\_ZERODB = 1; when testing noise related specifications (dynamic range, THD+N, idle channel noise), no external impedance on HPREFx.

|                       | PCM and DSD Processor Mode Parameter <sup>2,3,4</sup> |            | Minimum | Typical | Maximum | Units  |

|-----------------------|-------------------------------------------------------|------------|---------|---------|---------|--------|

| Other characteristics | Interchannel gain mismatch (defined in Table 3-1)     |            | _       | ±0.1    | _       | dB     |

| for HPOUTx            | Interchannel phase mismatch (defined in Table 3-1)    |            | _       | ±0.05   | -       | degree |

|                       | Output offset voltage: Mute (defined in Table 3-1)    |            | _       | ±0.5    | ±1      | mV     |

|                       | Gain drift (defined in Table 3-1)                     |            | _       | ±100    | -       | ppm/°C |

|                       | Load resistance (RL)                                  |            | 16      | _       | _       | Ω      |

|                       | Load capacitance (CL)                                 |            | _       | _       | 1       | nF     |

|                       | Turn-on time (defined in Table 3-1)                   |            | _       | _       | 8       | ms     |

|                       | Audio latency after RESET released 7                  |            | _       | _       | 20      | ms     |

|                       | Click/pop during PDN_HP enable or disable             | A-weighted | _       | _       | -60     | dBV    |

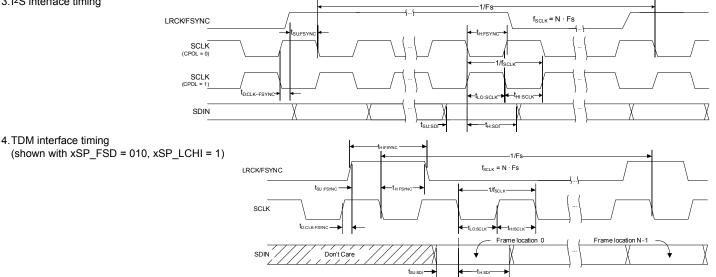

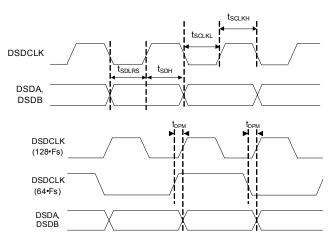

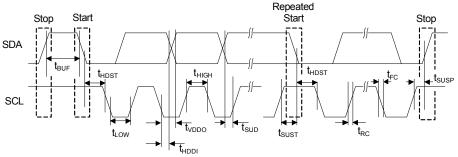

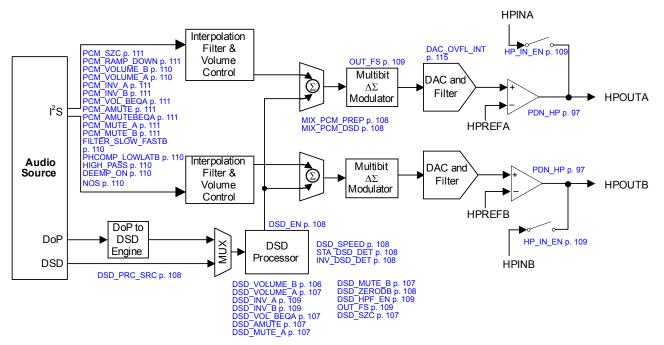

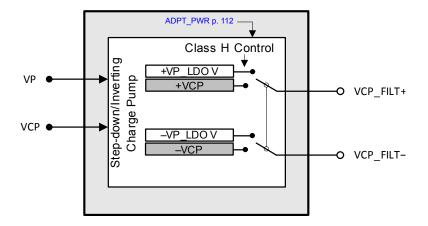

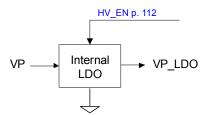

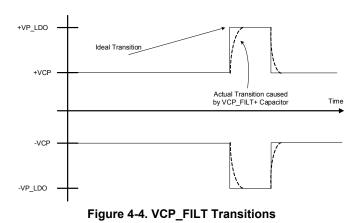

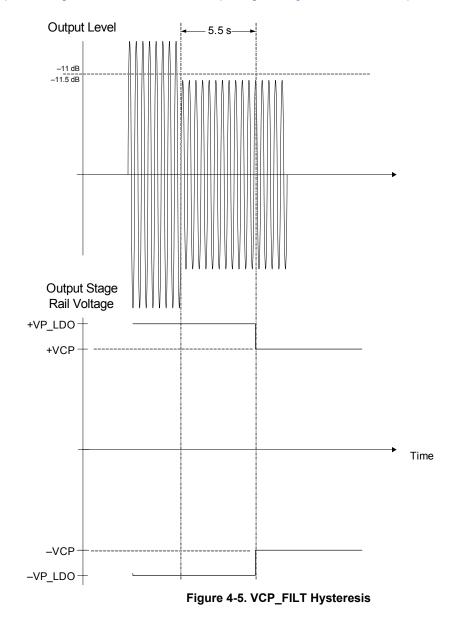

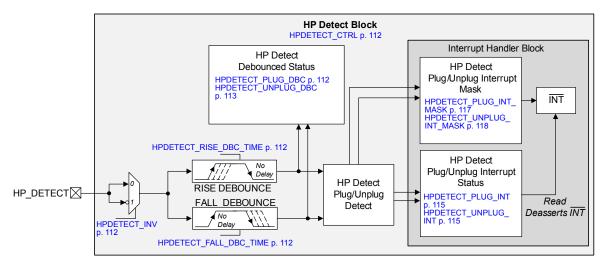

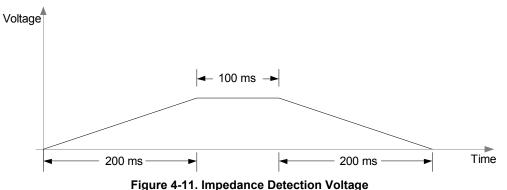

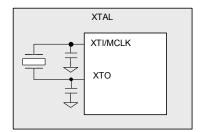

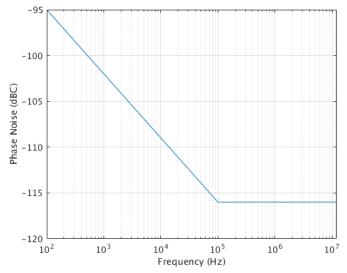

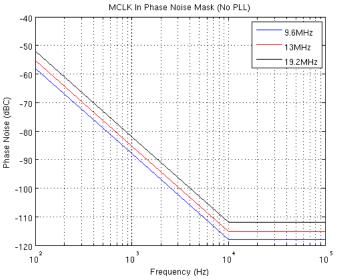

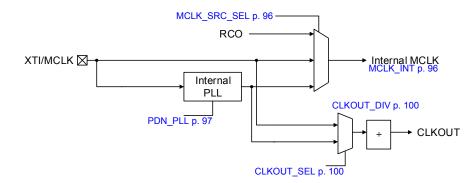

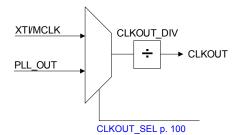

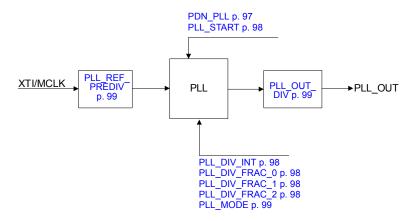

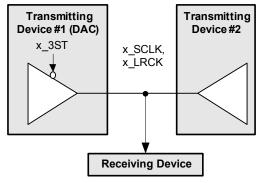

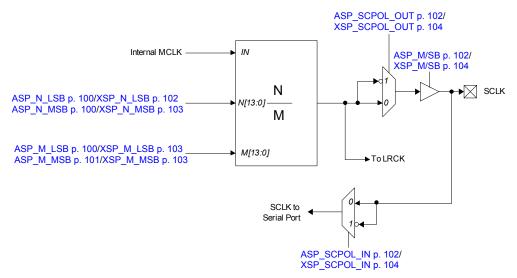

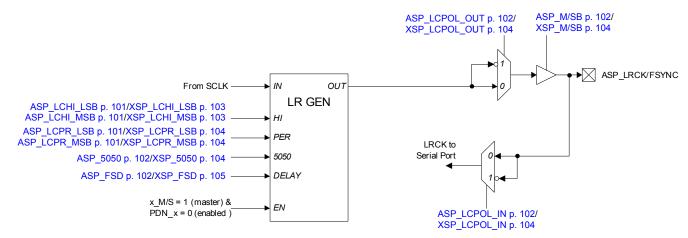

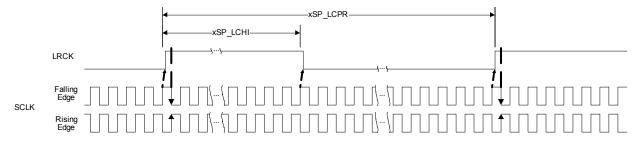

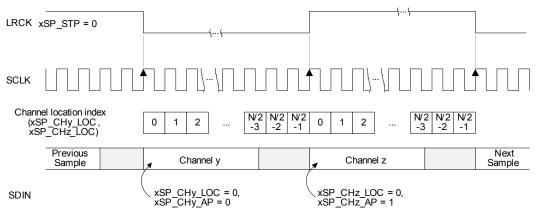

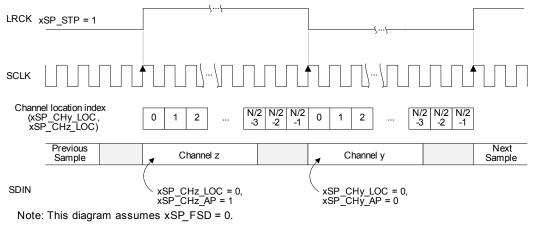

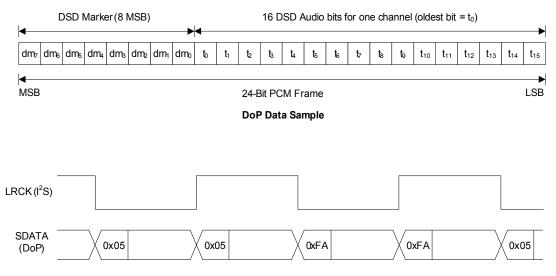

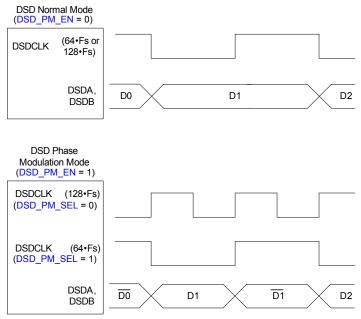

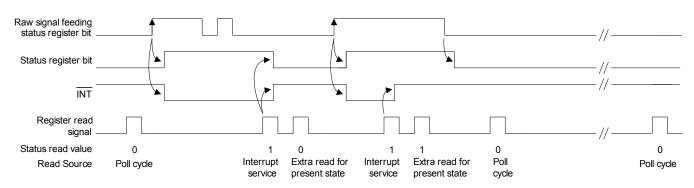

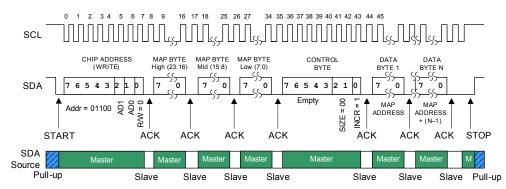

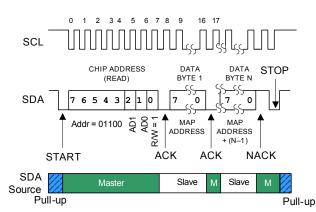

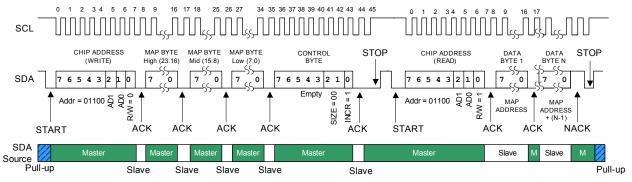

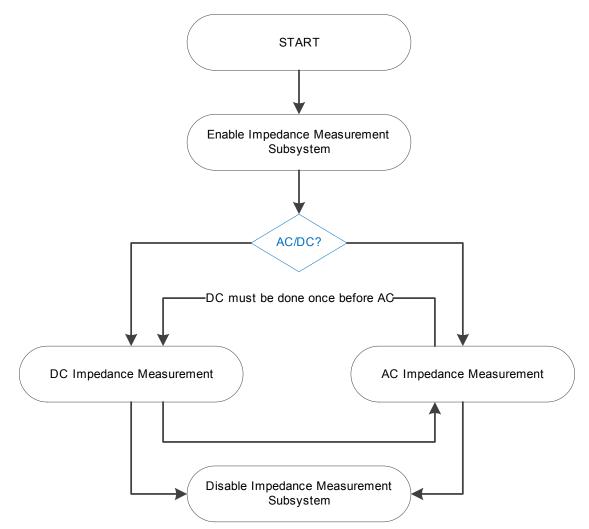

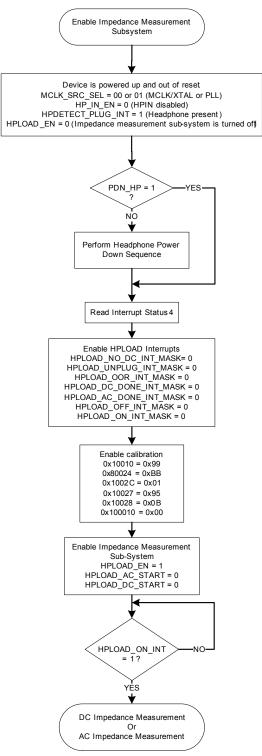

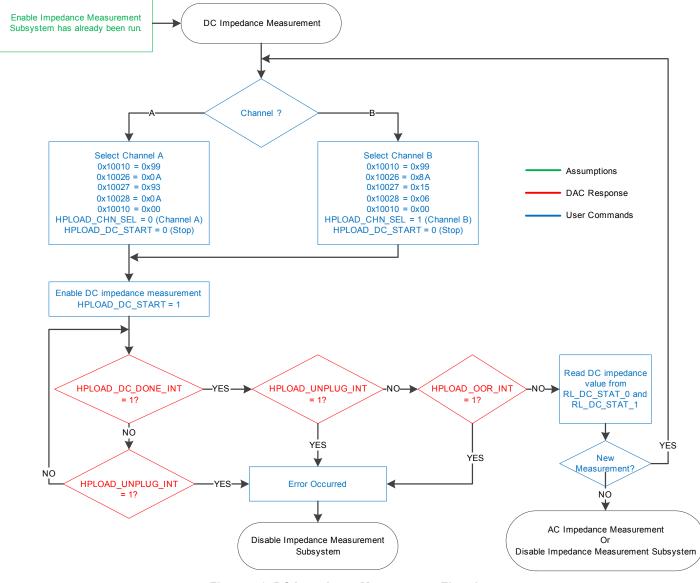

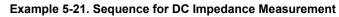

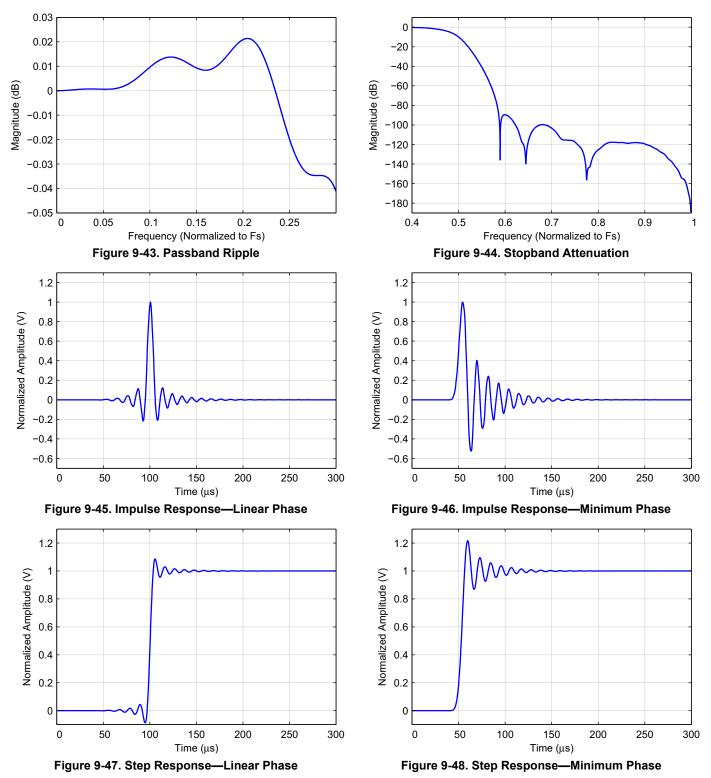

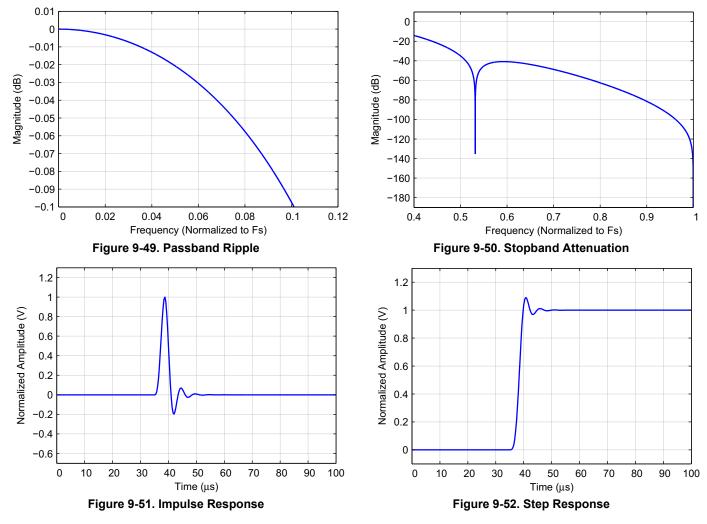

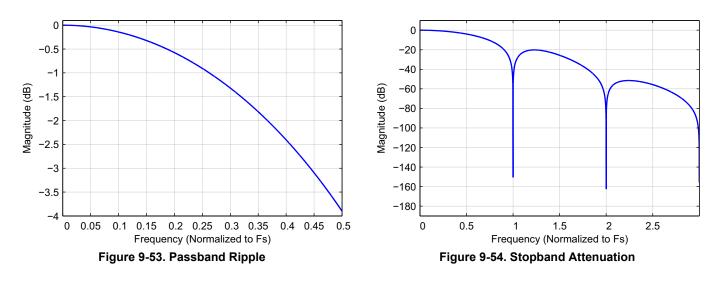

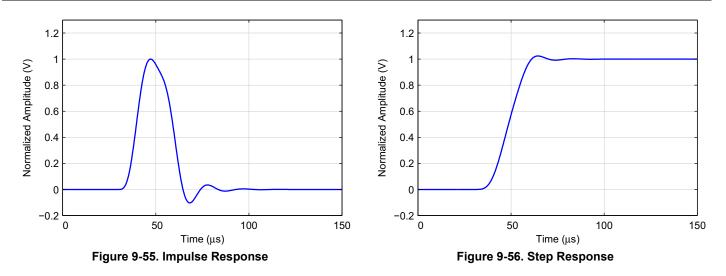

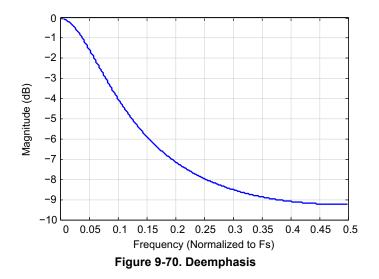

1. This table also applies to external VCP\_FILT supply mode: CS43130 power up procedure as described in Section 4.3.5; EXT\_VCPFILT=1; VCP\_ FILT+ and VCP\_FILT- comply to Table 3-2 when EXT\_VCPFILT = 1; in this mode, HV\_EN setting becomes don't care.