## LogiCORE IP Endpoint PIPE v1.8 for PCI Express

DS321 July 23, 2010

## Introduction

The LogiCORE<sup>TM</sup> IP Endpoint PIPE (PHY Interface) for PCI Express® 1-lane core is a high-bandwidth scalable and reliable serial interconnect intellectual property building block for use with the Spartan®-3, Spartan-3E, and Spartan-3A FPGAs in conjunction with an external PHY device. This solution, compliant with the *PCI Express Base Specification v1.1*, is a flexible low-cost chipset that can be used in a wide variety of high-volume applications including add-in cards, host bus adapters, and high-end server and graphics cards.

PCI Express offers a serial architecture that alleviates some of the limitations of parallel bus architectures by using clock data recovery (CDR) and differential signaling. Using CDR (as opposed to source synchronous clocking) lowers pin count, enables superior frequency scalability, and makes data synchronization easier. The layered architecture of PCI Express provides for future attachment to copper, optical, or emerging physical signaling media. PCI Express technology, adopted by the PCI-SIG as the next generation PCI, is backward-compatible to the existing PCI software model.

The Xilinx solutions for PCI Express set the industry standard for a high-performance and cost-efficient third-generation I/O solution by providing higher bandwidth per pin, low overhead, low latency, reduced signal integrity issues, and CDR architecture.

Xilinx Endpoint solutions for PCI Express are compatible with industry standard application form factors such as PCI Express Card Electromechanical (CEM) v1.1 and PCI Industrial Computer Manufacturers Group (PICMG) 3.4 specifications.

LogiCORE IP Facts Table **Core Specifics** Supported Spartan-3, Spartan-3E, Spartan-3A<sup>(2)</sup> Device Family<sup>(1)</sup> XC3S1000-4 Spartan-3 Minimum Device Spartan-3E XC3S500E-4 Requirement XC3S700A-4 Spartan-3A Resources<sup>(3)</sup> Block RAMs<sup>(4)</sup> LUTs Configuration FFs 4650-4790<sup>(5)</sup> 1-Lane 5880-8 6150(5) Endpoint PIPE NXP PX1011B-EL1 Supported PHY **Provided with Core** Product Specification Getting Started Guide Documentation User Guide Instantiation Template **Design Files** Netlist Example Design Verilog Test Bench Verilog Constraints File Specify Xilinx Constraints File Simulation Verilog and VHDL Model **Tested Design Tools** Mentor Graphics® ModelSim® PE/SE v6.5c and above Synopsys® VCS and VCS MX 2009.12 and **Design Entry** Tools above Cadence® Incisive Enterprise Simulator (IES) v9.2 and above Version of Simulator Tools Tested Simulation Synthesis Tools Synplicity® Synplify®, Xilinx XST (Verilog only) Support

Provided by Xilinx, Inc.

For a complete listing of supported devices, see the <u>release notes</u> for this core.

- 2. Spartan-3AN is not a supported device family.

- The precise number of slices depends on the user configuration of the interface and the level of resource sharing with adjacent logic.

- Based on 18K block RAMs (or 36K select appropriate size).

This range indicates resources used for a 2BAR\_7BAR

- 5. This range indicates resources used for a 2BAR-7BAR implementation.

© Copyright 2005-2010 Xilinx, Inc. XILINX, the Xilinx logo, Virtex, Spartan, ISE and other designated brands included herein are trademarks of Xilinx in the United States and other countries. All other trademarks are the property of their respective owners. PCI, PCI Express, PCIe, and PCI-X are trademarks of PCI-SIG.

www.xilinx.com

#### **Product Specification**

## **E** XILINX.

## Features

- High-performance, highly flexible, scalable, reliable, and general purpose I/O core

- Compliant with the PCI Express Base Specification v1.1

- Compatible with conventional PCI software model

- Fully compliant with PCI Express transaction ordering rules

- Six individually programmable/configurable BARs and expansion ROM BAR

- Supports MSI and INTX emulation

- 32-bit internal data path

- Supports removal of corrupt packets for error detection and recovery

- Compatible with PCI/PCI Express power management functions

- Active state power management (ASPM)

- Programmed power management (PPM)

- Used in conjunction with NXP PX1011B PCI Express standalone PHY to achieve high transceiver capability

- 2.5 Gbps line speed

- Elastic buffers and clock compensation

- Automatic clock and data recovery

- 8b/10b encode and decode

- Offers standardized easy-to-use Xilinx LocalLink interface

- Packet-based full-duplex communication

- Back-to-back transactions enable greater link bandwidth utilization

- Enables flow control of data and discontinuance of an in-process transaction in the transmit direction

- Enables flow control of data in the receive direction

- Automatically decodes and removes error forwarding packet indicator from received data

- Supports a maximum transaction payload of up to 512 bytes

- Fully configurable using the Xilinx CORE Generator<sup>™</sup> v12.2

- Design verified using a Xilinx proprietary test bench

# Applications

The Endpoint PIPE for PCI Express core architecture enables a broad range of computing and consumer communications target applications, emphasizing performance, cost, scalability, feature extensibility and mission-critical reliability. Typical applications include:

- Test equipment

- Consumer graphics boards

- Medical imaging equipment

- Data communications networks

- Telecommunications networks

- Broadband deployments

- Cross-connects

- Workstation and mainframe backbones

- Network interface cards

- Chip-to-chip and backplane interconnect

- Crossbar switches

- Wireless base stations

- High-bandwidth digital video

- High-bandwidth server applications

# **Functional Description**

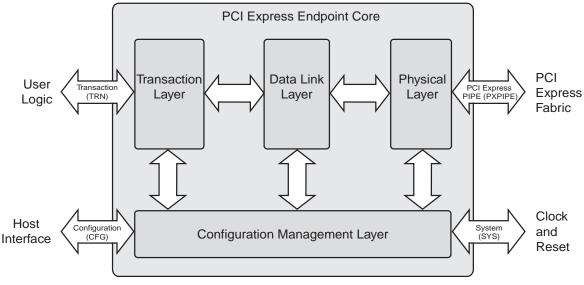

The Endpoint PIPE for PCI Express is organized into four main modules based on the three discrete logical layers defined by the *PCI Express Base Specification v1.1*. The logic modules, which manage all the system-level functions, include the following:

- Physical Layer Module (PLM)

- Data Link Layer Module (LLM)

- Transaction Layer Module (TLM)

- Configuration Management Module (CMM)

Each modules is further partitioned into the Receive and the Transmit sections. The Receive section processes the inbound information, and the Transmit section processes the outbound information. Figure 1 illustrates the main modules interfacing with one another and with the User Application using a set of four interfaces:

- System (SYS) interface

- PIPE (PXPIPE) interface

- Configuration (CFG) interface

- Transaction (TRN) interface

Figure 1: Top-level Functional Blocks and Interfaces

The core uses packets to exchange information between the various modules. Packets are formed in the Transaction and Data Link Layers to carry information from the transmitting component to the receiving component. Necessary information is added to the packet being transmitted, which is required to handle the packet at those layers. At the receiving end, each layer of the receiving element processes the incoming packet, strips the relevant information

and forwards the packet to the next layer. As a result, the received packets get transformed from their Physical Layer representation to their Data Link Layer representation and the Transaction Layer representation. The main logic modules comprising the Endpoint PIPE for PCI Express and their interfaces are described in the following sections.

### **Logic Modules**

The logic modules are responsible for handling the functionality related to each of the layers defined by the *PCI Express Base Specification v1.1*. The functions of these modules include generation and processing of Transaction Layer Packets (TLPs), flow control management, initialization and power management functions, data protection, error checking and retry functions, physical link interface initialization, maintenance and status tracking, serialization, de-serialization and other circuitry for interface operation. These modules and their functionality are described below.

### **Physical Layer Module**

The Physical Layer exchanges information with the Data Link Layer in an implementation-specific format. This layer is responsible for converting information received from the Data Link Layer into an appropriate format and transmitting it across the PXPIPE interface at a frequency and width compatible with the external PHY.

PXPIPE is the NXP PHY Specification, an extended version of the PIPE specification.

### **Data Link Layer Module**

The Data Link Layer acts as an intermediate stage between the Transaction Layer and the Physical Layer. Its primary responsibility is to provide a reliable mechanism for the exchange of TLPs between the two Components on a Link.

Services provided by the Data Link Layer include data exchange (TLPs), error detection and recovery, initialization services and the generation and consumption of Data Link Layer Packets (DLLPs). DLLPs are the mechanism used to transfer information between Data Link Layers of two directly connected Components on the Link. They are used for conveying information such as Flow Control and TLP acknowledgments.

### **Transaction Layer Module**

The upper layer of the PCI Express architecture is the Transaction Layer. The primary function of the Transaction Layer is to accept, buffer and disseminate TLPs. Packets are formed in the Transaction and Data Link Layers to carry the information from the transmitting component to the receiving component. TLPs are used to communicate transactions, such as read and write, as well as certain types of events. To maximize the efficiency of communication between devices, the Transaction Layer implements a pipelined, full split-transaction protocol; manages credit-based flow control of TLP which eliminates wasted Link bandwidth due to retries; and offers optional support for data poisoning.

### **Configuration Management Module**

This module supports generation and reception of System Management Messages by communicating with the other modules and the user application.

The Configuration Management module does the following:

- Implements Configuration Space registers which support:

- Legacy PCI2.3 configuration space

- PCI Express Capabilities (minimum required set)

- Supports Configuration Space accesses

- Power Management Functions

- Programmed Power Management (PPM)

- Active State Power Management (ASPM)

- Implements error reporting and status functionality

- Error tracking

- Error reporting

- Implements packet processing functions

- Receive

- Configuration Reads and Writes

- Transmit:

- Completions with or without data

- TLM Error Messaging

- User Error Messaging

- Power Management Messaging/Handshake

- Implements MSI and INTx interrupt emulation with support for Multi-Vector MSI

## **PCI Configuration Space**

This block provides a standard Type 0 configuration space. The Configuration Space consists of a 64 byte, Type 0 configuration space header, with an additional 192 bytes used for extended capabilities.

The following extended capabilities are provided in the interface:

- Express Capability Item

- Power Management Capability Item

- Message Signaled Interrupt Capability Item

- Device serial number extended capability structure

These capabilities, together with the standard Type 0 header shown in Table 1, support software driven *Plug and Play* initialization and configuration.

| 31                                                                                                                                           | 16                                     | 15                                      |                     | 0         |

|----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|-----------------------------------------|---------------------|-----------|

| Devi                                                                                                                                         | ce ID                                  | Vendor ID                               |                     | 000h      |

| Sta                                                                                                                                          | Status                                 |                                         | Command             |           |

|                                                                                                                                              | Class Code                             |                                         | Rev ID              | 008h      |

| BIST                                                                                                                                         | Header                                 | Lat Timer                               | Cache Ln            | 00Ch      |

|                                                                                                                                              | Base Addres                            | ss Register 0                           |                     | 010h      |

|                                                                                                                                              | Base Addres                            | ss Register 1                           |                     | 014h      |

|                                                                                                                                              | Base Addres                            | ss Register 2                           |                     | 018h      |

|                                                                                                                                              | Base Addres                            | ss Register 3                           |                     | 01Ch      |

|                                                                                                                                              | Base Addres                            | ss Register 4                           |                     | 020h      |

|                                                                                                                                              | Base Addres                            | ss Register 5                           |                     | 024h      |

|                                                                                                                                              | Cardbus C                              | CIS Pointer                             |                     | 028h      |

| Subsys                                                                                                                                       | stem ID                                | Subsystem                               | Vendor ID           | 02Ch      |

|                                                                                                                                              | Expansion ROM                          | A Base Address                          |                     | 030h      |

|                                                                                                                                              | Reserved                               |                                         | CapPtr              | 034h      |

|                                                                                                                                              | Rese                                   | erved                                   |                     | 038h      |

| Max Lat                                                                                                                                      | Min Gnt                                | Intr Pin                                | Intr Line           | 03Ch      |

| PM Ca                                                                                                                                        | pability                               | NxtCap                                  | PM Cap              | 040h      |

| Data                                                                                                                                         | BSE                                    | PMO                                     | CSR                 | 044h      |

| MSI C                                                                                                                                        | MSI Control                            |                                         | MSI Cap             | 048h      |

|                                                                                                                                              | Message Add                            | dress (Lower)                           |                     | 04Ch      |

|                                                                                                                                              | Message Ade                            | dress (Upper)                           |                     | 050h      |

| Rese                                                                                                                                         | erved                                  | Message Data                            |                     | 054h      |

| PE Ca                                                                                                                                        | pability                               | NxtCap                                  | PE Cap              | 058h      |

|                                                                                                                                              | PCI Express De                         | vice Capabilities                       |                     | 05Ch      |

| Device                                                                                                                                       | Status                                 | Device Control                          |                     | 060h      |

|                                                                                                                                              | PCI Express L                          | ink Capabilities                        |                     | 064h      |

| Link S                                                                                                                                       | Status                                 | Link Control                            |                     | 068h      |

| Reserved Legacy Configuration Space<br>(Read Access: Returns successful CpID w/ Data = 0x0000_0000<br>Write Access: Returns successful Cpl.) |                                        |                                         | 06Ch-0FFh           |           |

| Next Cap                                                                                                                                     |                                        |                                         | PCI Exp. Capability |           |

|                                                                                                                                              | PCI Express Device                     | Serial Number (1st)                     |                     | 104h      |

|                                                                                                                                              | PCI Express Device Serial Number (2nd) |                                         |                     |           |

|                                                                                                                                              |                                        | Configuration Space<br>eletion with UR) |                     | 10Ch-FFFh |

# Table 1: Configuration Space Header for PCI Express

### **Core Interfaces**

The Endpoint PIPE for PCI Express includes top-level signal interfaces that have sub-groups for the receive direction, transmit direction, and signals common to both directions.

### **System Interface**

The system interface (SYS) consists of the system reset signal, as described in Table 2.

#### Table 2: System Interface Signals

| Signal Name | Direction | Description                                                                                                                                  |

|-------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------|

| sys_reset_n |           | <b>System Reset:</b> An asynchronous, active low, reset signal from the root complex/system that puts the endpoint in a known initial state. |

The system reset signal is active low. The assertion of this signal causes a hard reset of the entire core, including the NXP PHY. This signal is an asynchronous input. In typical endpoint applications, a sideband reset signal is present and should be connection to sys\_reset\_n. For endpoint applications that do not have a sideband system reset signal, the initial hardware reset should be generated locally. In either case, subsequent resets may be communicated in-band using the PCI Express protocol.

Note that systems designed to the PCI Express electro-mechanical specification provide a sideband reset signal that uses 3.3V signaling levels—carefully read the FPGA device data sheet to understand the requirements for interfacing to such signals.

#### **NXP Standalone PHY**

The Endpoint PIPE for PCIe uses an external NXP PX1011B-EL1. The PIPE architecture is defined by Intel Corporation and is used as the interconnect between the Endpoint for PCI Express core and the NXP PHY. The NXP PHY (PXPIPE) is an extended version of the PIPE specification. Using another PHY with PIPE interface is incompatible. See the NXP PX1011B data sheet for more information and errata items related to the NXP PHY. For additional information, go to ics.nxp.com/products/pcie/phys/.

#### **PHY Pin Description**

The PXPIPE input and output signals are described in Table 3 through Table 7. Note that input/output is defined from the perspective of the FPGA—Output signals are *driven* by the FPGA, and Input signals are *received* by the FPGA.

Table 3: PXPIPE Transmit Data Interface Signals

| Symbol      | Direction | Description                                                                                                               |

|-------------|-----------|---------------------------------------------------------------------------------------------------------------------------|

| TXDATA[7:0] | Output    | 8-bit transmit data from the FPGA to the NXP PHY.                                                                         |

| TXDATAK     | Output    | Data/Control for the symbols of transmit data. A value of 0 indicates a data byte, a value of 1 indicates a control byte. |

#### Table 4: PXPIPE Receive Data Interface Signals

| Symbol      | Direction | Description                                                                                                              |

|-------------|-----------|--------------------------------------------------------------------------------------------------------------------------|

| RXDATA[7:0] | Input     | 8-bit receive data from the NXP PHY to the FPGA.                                                                         |

| RXDATAK     | Input     | Data/Control for the symbols of receive data. A value of 0 indicates a data byte, a value of 1 indicates a control byte. |

### Table 5: Clock and Reference Signals

| Symbol                     | Direction | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TXCLK                      | Output    | Source synchronous 250 MHz clock (from FPGA) for transmit clock from MAC input. All the data and the input signals to the PHY are synchronized to this clock.                                                                                                                                                                                                                                                                                                                          |

| RXCLK                      | Input     | Source synchronous 250 MHz clock (to FPGA) for received data bound for the MAC output.                                                                                                                                                                                                                                                                                                                                                                                                 |

| fast_train_simulation_only | Input     | Should only be asserted for simulation. Training counters are lowered when this input is asserted (set to "1") to allow the simulation to train faster. Do not assert this input when using the core in hardware. Doing so causes the core to fail link training.                                                                                                                                                                                                                      |

| two_plm_auto_config        | Input     | Used only for simulation; forces device to act as a down stream device for link training purposes. This signal should only be set to "1," if in simulation two Endpoint PIPE cores are connected back-to-back. When using the provided downstream port model for simulation, this signal should be set to "0" on the endpoint core under test. This signal should be set to "0" when using the core in hardware as an endpoint device. Any other setting in hardware is not supported. |

### Table 6: PXPIPE Command Interface Signals

| Symbol              | Direction | Description                                                                                                                                                                                                                                          |

|---------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TXDETECTRX_LOOPBACK | Output    | Enable the NXP PHY to begin a receiver detection operation or to begin loopback.                                                                                                                                                                     |

|                     |           | Forces NXP PHY Tx output to electrical idle when asserted in all power states.                                                                                                                                                                       |

| TXELECIDLE          | Output    | When deasserted while in P0 (as indicated by the PowerDown signals), indicates that there is valid data present on the TXDATA[7:0] and TXDATAK pins and that the data should be transmitted.                                                         |

|                     |           | When deasserted in P2 the signal has no function. It would be used to indicate that the PHY should begin transmitting beacon signaling however beacon is not supported in this version of the PHY.                                                   |

|                     |           | TXELECIDLE must always be asserted while in power states P0s and P1.                                                                                                                                                                                 |

| TXCOMPLIANCE        | Output    | When high, sets the running disparity to negative. Used when transmitting the compliance pattern.                                                                                                                                                    |

| RXPOLARITY          | Output    | Active high, signals the PHY to perform a polarity inversion on the receive data.                                                                                                                                                                    |

| RESETN              | Output    | Active low PHY reset from FPGA.                                                                                                                                                                                                                      |

| POWERDOWN[1:0]      | Output    | <ul> <li>Power up or down the transceiver. Power states:</li> <li>00 - P0, normal operation</li> <li>01 - P0s, low recovery time latency, power saving state</li> <li>10 - P1, longer recovery time (64us max) latency, lower power state</li> </ul> |

|                     |           | 11 - Reserved for P2, lowest power state                                                                                                                                                                                                             |

### Table 7: PXPIPE Status Interface Signals

| Symbol    | Direction | Description                                                                                                                       |

|-----------|-----------|-----------------------------------------------------------------------------------------------------------------------------------|

| RXVALID   | Input     | Indicates symbol lock and valid data on RxData and RxDataK.                                                                       |

| PHYSTATUS | Input     | Used to communicate completion of several NXP PHY functions including power management state transitions, and receiver detection. |

| Symbol        | Direction | Description                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RXELECIDLE    | Input     | Indicates receiver detection of an electrical idle. This is an asynchronous signal.                                                                                                                                                                                                                                                                                                                |

| RXSTATUS[2:0] | Input     | <ul> <li>Encodes receiver status and error codes for the received data stream and receiver detection.</li> <li>000 - Received data OK</li> <li>001 - 1 SKP added</li> <li>010 - 1 SKP removed</li> <li>011 - Receiver detected</li> <li>100 - 8B/10B decode error</li> <li>101 - Elastic Buffer overflow</li> <li>110 - Elastic Buffer underflow</li> <li>111 - Receive disparity error</li> </ul> |

| Table | 7: | PXPIPE | Status | Interface | Signals | (Cont'd) |

|-------|----|--------|--------|-----------|---------|----------|

|-------|----|--------|--------|-----------|---------|----------|

### **Transaction Interface**

The Transaction (TRN) interface provides a mechanism for the user design to generate and consume TLPs. The signal names and signal descriptions for this interface are shown in Table 8, Table 9, and Table 11.

#### **Common TRN Interface**

Table 8 lists the common TRN interface signal names and descriptions.

Table 8: Common Transaction Interface Signals

| Name         | Direction | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| trn_clk      | Output    | <b>Transaction Clock</b> : 62.50 MHz. Transaction and Configuration interface operations are referenced-to and synchronous-with the rising edge of this clock. trn_clk is unavailable when the core sys_reset_n is held asserted. trn_clk is guaranteed to be stable at the nominal operating frequency once the core deasserts trn_reset_n.                                                                                                                                                                                                                                                                   |

| trn_reset_n  | Output    | <b>Transaction Reset</b> : Active low. User logic interacting with the Transaction and Configuration interfaces must use trn_reset_n to return to their quiescent states. trn_reset_n is deasserted synchronously with respect to trn_clk, sys_reset_n is deasserted and is asserted asynchronously with sys_reset_n assertion. Note that trn_reset_n is not asserted for the core in-band reset events like <i>Hot Reset</i> or <i>Link Disable</i> . trn_reset_n is asserted due to loss of input receive clock from the external PHY device, which is used by the core's internal DCM, to generate trn_clk. |

| trn_lnk_up_n | Output    | <b>Transaction Link Up</b> : Active low. Transaction link-up is asserted when the core and the connected upstream link partner port are ready and able to exchange data packets. Transaction link-up is deasserted when the core and link partner are attempting to establish communication, and when communication with the link partner is lost due to errors on the transmission channel. When the core is driven to <i>Hot Reset</i> and <i>Link Disable</i> states by the link partner, trn_lnk_up_n is deasserted and all TLPs stored in the core are lost.                                              |

#### Transmit TRN Interface

Table 9 lists the transmit (Tx) TRN interface signal names and descriptions.

Table 9: Transmit Transaction Interface Signals

| Name         | Direction | Description                                                               |

|--------------|-----------|---------------------------------------------------------------------------|

| trn_tsof_n   | Input     | Transmit Start-of-Frame (SOF): Signals the start of a packet. Active low. |

| trn_teof_n   | Input     | Transmit End-of-Frame (EOF): Signals the end of a packet. Active low.     |

| trn_td[31:0] | Input     | Transmit Data: Packet data to be transmitted.                             |

www.xilinx.com

| Name             | Direction | Description                                                                                                                                                                                                                                       |

|------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| trn_terrfwd_n    | Input     | <b>Transmit Error Forward</b> : Marks the current packet in progress as error-poisoned.<br>May be asserted any time between SOF and EOF, inclusive. Active low.                                                                                   |

| trn_tsrc_rdy_n   | Input     | <b>Transmit Source Ready</b> : Indicates that the User Application is presenting valid data on <b>trn_td[31:0]</b> . Active low.                                                                                                                  |

| trn_tdst_rdy_n   | Output    | Transmit Destination Ready: Indicates that the core is ready to accept data on<br>trn_td[31:0]. Active low.The simultaneous assertion of trn_tsrc_rdy_n and trn_tdst_rdy_n marks the<br>successful transfer of one DWORD of data on trn_td[31:0]. |

| trn_tsrc_dsc_n   | Input     | <b>Transmit Source Discontinue</b> : Indicates that the User Application is aborting the current packet. Active low.                                                                                                                              |

| trn_tdst_dsc_n   | Output    | <b>Transmit Destination Discontinue</b> : Indicates that the core is aborting the current packet. Asserted when the physical link is going into reset. Active low.                                                                                |

| trn_tbuf_av[4:0] | Output    | <b>Transmit Buffers Available</b> : Number of transmit buffers available in the core. The maximum number is 8. Each transmit buffer can hold one packet with up to 512 bytes of payload.                                                          |

Table 9: Transmit Transaction Interface Signals

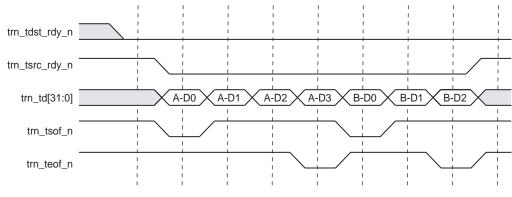

Figure 2 illustrates the transfer on the TRN interface of two TLPs to be transmitted on the PCI Express Link. Every valid transfer can be up to one double word (DWORD) of data.

Table 10 lists the transmit path clock cycle signals and event descriptions.

Table 10: Transmit Path Signaling Events

| Clock Cycle | Event Description                                                                                                                                                                                                    |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1           | The assertion of trn_tdst_rdy_n tells the user application that the core is ready to accept data.                                                                                                                    |

| 2           | The user application initiates the transfer with the assertion of trn_tsrc_rdy_n and trn_tsof_n. The combined assertion of trn_tsrc_rdy_n and trn_tdst_rdy_n marks a data transfer. Frame A DWORD D0 is transferred. |

| 3           | Frame A DWORD D1 is transferred.                                                                                                                                                                                     |

| 4           | Frame A DWORD D2 is transferred.                                                                                                                                                                                     |

| 5           | The end of Frame A is signaled with trn_teof_n. Frame A DWORD D3 is transferred.                                                                                                                                     |

| 6           | The user application signals the start of a new TLP with trn_tsof_n. Frame B DWORD D0 is transferred.                                                                                                                |

| 7           | Frame B DWORD D1 is transferred.                                                                                                                                                                                     |

| Clock Cycle | Event Description                                                                                                               |  |  |  |

|-------------|---------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 8           | The end of Frame B is signaled with trn_teof_n. Frame B DWORD D2 is transferred.                                                |  |  |  |

| 9           | The core keeps trn_tdst_rdy_n asserted to offer the user application the opportunity to start the transmission of the next TLP. |  |  |  |

### Table 10: Transmit Path Signaling Events

#### Receive TRN Interface

Table 11 lists the receive (Rx) TRN interface signal names and descriptions.

| Name                 | Direction | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| trn_rsof_n           | Output    | Receive Start-of-Frame (SOF): Signals the start of a packet. Active low.                                                                                                                                                                                                                                                                                                                                                                                                                          |

| trn_reof_n           | Output    | Receive End-of-Frame (EOF): Signals the end of a packet. Active low.                                                                                                                                                                                                                                                                                                                                                                                                                              |

| trn_rd[31:0]         | Output    | Receive Data: Packet data being received.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| trn_rerrfwd_n        | Output    | <b>Receive Error Forward:</b> Marks the current packet in progress as error-poisoned. Asserted by the core at EOF. Active low.                                                                                                                                                                                                                                                                                                                                                                    |

| trn_rsrc_rdy_n       | Output    | <b>Receive Source Ready:</b> Indicates that the core is presenting valid data on trn_rd[31:0]. Active low.                                                                                                                                                                                                                                                                                                                                                                                        |

| trn_rdst_rdy_n       | Input     | <b>Receive Destination Ready:</b> Indicates that the User Application is ready to accept data on trn_rd[31:0]. Active low.<br>The simultaneous assertion of trn_rsrc_rdy_n and trn_rdst_rdy_n marks the successful transfer of one DWORD of data on trn_rd[31:0].                                                                                                                                                                                                                                 |

| trn_rsrc_dsc_n       | Output    | <b>Receive Source Discontinue:</b> Indicates that the core is aborting the current packet. Asserted when the physical link is going into reset. Active low.                                                                                                                                                                                                                                                                                                                                       |

| trn_rnp_ok_n         | Input     | Receive Non-Posted OK: The User Application asserts this whenever it is ready<br>to accept a Non-Posted Request packet. This allows Posted and Completion<br>packets to bypass Non-Posted packets in the inbound queue if necessitated by the<br>User Application. Active low.When the User Application approaches a state where it is unable to service<br>                                                                                                                                      |

| trn_rbar_hit_n[6:0]  | Output    | Receive BAR Hit: Indicates BAR(s) targeted by the current receive transaction.         Active low.         trn_rbar_hit_n[0] => BAR0         trn_rbar_hit_n[1] => BAR1         trn_rbar_hit_n[2] => BAR2         trn_rbar_hit_n[3] => BAR3         trn_rbar_hit_n[4] => BAR4         trn_rbar_hit_n[5] => BAR5         trn_rbar_hit_n[6] => Expansion ROM Address         Note that if two BARs are configured into a single 64-bit address, both corresponding trn_rbar_hit_n bits are asserted. |

| trn_rfc_ph_av[7:0]   | Output    | <b>Receive Posted Header Flow Control Credits Available:</b> The number of Posted Header FC credits available to the remote link partner. <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                          |

| trn_rfc_pd_av[11:0]  | Output    | <b>Receive Posted Data Flow Control Credits Available:</b> The number of Posted Data FC credits available to the remote link partner. <sup>()</sup>                                                                                                                                                                                                                                                                                                                                               |

| trn_rfc_nph_av[7:0]  | Output    | <b>Receive Non-Posted Header Flow Control Credits Available:</b> The number of Non-Posted Header FC credits available to the remote link partner. <sup>()</sup>                                                                                                                                                                                                                                                                                                                                   |

| trn_rfc_npd_av[11:0] | Output    | <b>Receive Non-Posted Data Flow Control Credits Available:</b> The number of Non-Posted Data FC credits available to the remote link partner. <sup>()</sup>                                                                                                                                                                                                                                                                                                                                       |

## Table 11: Receive Transaction Interface Signals

| Name                  | Direction | Description                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| trn_rfc_cplh_av[7:0]  | Output    | <b>Receive Completion Header Flow Control Credits Available:</b> The number of Completion Header FC credits available to the remote link partner. <sup>(2)</sup> Note that this value and trn_rfc_cpld_av[11:0] are hypothetical quantities reflecting credit availability that would be advertised to the remote link partner if the core were not required to advertise infinite Completion credits. |

| trn_rfc_cpld_av[11:0] | Output    | <b>Receive Completion Data Flow Control Credits Available:</b> The number of Completion Data FC credits available to the remote link partner. <sup>()</sup>                                                                                                                                                                                                                                            |

Table 11: Receive Transaction Interface Signals (Cont'd)

1. Credit values given to the user are instantaneous quantities, not the cumulative (from time zero) values seen by the remote link partner.

Completion credit values given to the user reflect the actual state of the core's receive FIFO, even though the Base Specification v1.1 requires an endpoint to advertise infinite completion credits to its link partner regardless of actual receive capacity.

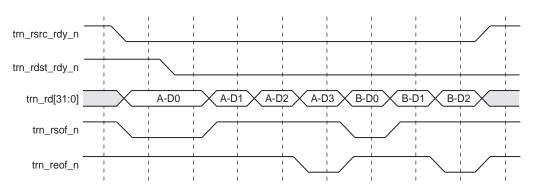

Figure 3 illustrates the transfer on the TRN interface of two TLPs received on the PCI Express Link.

Figure 3: Rx TRN Interface

Table 12 lists the receive path clock cycle signals and descriptions.

Table 12: Receive Path Signaling Events

| Clock Cycle | Event Description                                                                                                                                                                                                      |  |  |  |  |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1           | The core signals by the assertion of trn_rsrc_rdy_n that a valid TLP has been entirely received from the link. The core provides the first DWORD of the TLP and asserts trn_rsof_n to mark the start of the frame.     |  |  |  |  |

| 2           | The assertion of trn_rdst_rdy_n alerts the core that the user application is ready to accept data. The combined assertion of trn_rsrc_rdy_n and trn_rdst_rdy_n marks a data transfer. Frame A DWORD D0 is transferred. |  |  |  |  |

| 3           | Frame A DWORD D1 is transferred.                                                                                                                                                                                       |  |  |  |  |

| 4           | Frame A DWORD D2 is transferred.                                                                                                                                                                                       |  |  |  |  |

| 5           | The end of Frame A is signaled with trn_reof_n. Frame A DWORD D3 is transferred.                                                                                                                                       |  |  |  |  |

| 6           | The core signals the start of the second frame with trn_rsof_n. Frame B DWORD D0 is transferred.                                                                                                                       |  |  |  |  |

| 7           | Frame B DWORD D1 is transferred.                                                                                                                                                                                       |  |  |  |  |

| 8           | The end of Frame B is signaled with trn_reof_n. Frame B DWORD D2 is transferred.                                                                                                                                       |  |  |  |  |

| 9           | The core deasserts its trn_rsrc_rdy_n signal to indicate that there are no more pending TLPs to transfer.                                                                                                              |  |  |  |  |

#### **Configuration Interface**

The configuration (CFG) interface enables the user design to inspect the state of the Endpoint configuration space. The user provides a 10-bit configuration address which selects one of the 1024 configuration space double word

(DWORD) registers. The endpoint returns the state of the selected register over the 32-bit data output port. Table 13 describes the configuration interface signals.

| Table | 13: | Configuration | Interface Signals |

|-------|-----|---------------|-------------------|

|-------|-----|---------------|-------------------|

| Name                        | Direction | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| cfg_do[31:0]                | Output    | <b>Configuration Data Out</b> : This is a 32-bit data output port used to obtain read data from the configuration space inside the endpoint core.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                             |           | <b>Configuration Read Write Done:</b> This active-low read-write done signal indicates a successful completion of the user configuration register access operation.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| cfg_rd_wr_done_n            | Output    | For a user configuration register read operation, the signal validates the cfg_do[31:0] data-bus value.<br>For a user configuration register write operation, the assertion signals                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                             |           | completion of a successful write operation. Not supported for write operations.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| cfg_di[31:0]                | Input     | <b>Configuration Data In</b> : This is a 32-bit data input port used to provide write data to the configuration space inside the core. Not supported.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| cfg_dwaddr[9:0]             | Input     | <b>Configuration DWORD Address</b> : This is a 10-bit address input port used to provide a configuration register DWORD address during configuration register accesses.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| cfg_wr_en_n                 | Input     | <b>Configuration Write Enable</b> : This is the active low write enable for configuration register access. Not supported.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| cfg_rd_en_n                 | Input     | <b>Input Description:</b> Configuration Read Enable: This is the active low read enable for configuration register access.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| cfg_interrupt_n             | Input     | <b>Configuration Interrupt</b> : Active-low interrupt-request signal. The User Application may assert this to cause selected interrupt message-type to be transmitted by the core. The signal should be held low until cfg_interrupt_rdy_n is asserted.                                                                                                                                                                                                                                                                                                                                                    |

| cfg_interrupt_rdy_n         | Output    | <b>Configuration Interrupt Ready:</b> Active-low interrupt grant signal. The simultaneous assertion of cfg_interrupt_rdy_n and cfg_interrupt_n indicates that the core has successfully transmitted the requested interrupt message.                                                                                                                                                                                                                                                                                                                                                                       |

| cfg_interrupt_mmenable[2:0] | Output    | <b>Configuration Interrupt Multiple Message Enable:</b> This is the value of the Multiple Message Enable field. Values range from 000b to 101b. A value of 000b indicates that single vector MSI is enabled, while other values indicate the number of bits that may be used for multi-vector MSI.                                                                                                                                                                                                                                                                                                         |

| cfg_interrupt_msienable     | Output    | <b>Configuration Interrupt MSI Enabled:</b> Indicates that the Message Signaling Interrupt (MSI) messaging is enabled. If 0, then only Legacy (INTx) interrupts may be sent.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| cfg_interrupt_di[7:0]       | Input     | <b>Configuration Interrupt Data In</b> : For Message Signaling Interrupts (MSI), the portion of the Message Data that the Endpoint must drive to indicate MSI vector number, if Multi-Vector Interrupts are enabled. The value indicated by cfg_interrupt_mmenable[2:0] determines the number of lower-order bits of Message Data that the Endpoint provides; the remaining upper bits of cfg_interrupt_di[7:0] are not used. For Single-Vector Interrupts, cfg_interrupt_di[7:0] is not used. For Legacy interrupt messages (Assert_INTx, Deassert_INTx), this indicates the message type to send, where: |

|                             |           | ValueLegacy Interrupt00hINTA01hINTB02hINTC03hINTD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

Table 13: Configuration Interface Signals (Cont'd)

| Name                         | Direction | Description                                                                                                                                                                                                                                                                                                 |

|------------------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| cfg_interrupt_do[7:0]        | Output    | <b>Configuration Interrupt Data Out:</b> This is the value of the lowest 8 bits of the Message Data field in the Endpoint's MSI capability structure. This value is used in conjunction with cfg_interrupt_mmenable[2:0] to drive cfg_interrupt_di[7:0].                                                    |

| cfg_interrupt_assert_n       | Input     | Configuration Legacy Interrupt Assert/Deassert Select: Selects<br>between Assert and Deassert messages for Legacy interrupts when<br>cfg_interrupt_n is asserted. Not used for MSI interrupts.<br>ValueMessage Type<br>0Assert<br>1Deassert                                                                 |

| cfg_turnoff_ok_n             | Input     | <b>Configuration Turnoff OK</b> : This is the active low power turn-off ready signal. The User Application may assert this to notify the core that it is safe for power to be removed.                                                                                                                      |

| cfg_to_turnoff_n             | Output    | <b>Configuration To Turnoff:</b> This output signal notifies the user that a PME_TURN_Off message has been received and the CMM starts polling the cfg_turnoff_ok_n input coming in from the user. Once cfg_turnoff_ok_n is asserted, CMM sends a PME_To_Ack message to the upstream device.                |

| cfg_byte_en_n[3:0]           | Input     | <b>Configuration Byte Enable</b> : This is the active low byte enables for configuration register access signal. Not supported.                                                                                                                                                                             |

| cfg_err_ecrc_n               | Input     | <b>ECRC Error Report</b> : The user can assert this signal to report an ECRC error (end-to-end CRC).                                                                                                                                                                                                        |

| cfg_err_cpl_timeout_n        | Input     | <b>Configuration Error Completion Timeout</b> : The user can assert this signal to report a completion timed out.                                                                                                                                                                                           |

| cfg_err_cpl_abort_n          | Input     | <b>Configuration Error Completion Aborted</b> : The user can assert this signal to report that a completion was aborted.                                                                                                                                                                                    |

| cfg_err_cpl_unexpect_n       | Input     | <b>Configuration Error Completion Unexpected</b> : The user can assert this signal to report that an unexpected completion was received.                                                                                                                                                                    |

| cfg_err_posted_n             | Input     | <b>Configuration Error Posted</b> : This signal is used to further qualify any of the cfg_err_* input signals. When this input is asserted concurrently with one of the other signals, it indicates that the transaction which caused the error was a posted transaction.                                   |

| cfg_err_cor_n                | Input     | <b>Configuration Error Correctable Error</b> : The user can assert this signal to report that a correctable error was detected.                                                                                                                                                                             |

| cfg_err_ur_n                 | Input     | <b>Configuration Error Unsupported Request</b> : The user can assert this signal to report that an unsupported request was received.                                                                                                                                                                        |

| cfg_err_tlp_cpl_header[47:0] | Input     | <b>Configuration Error TLP Completion Header</b> : This input to the core accepts the header information from the user when an error is signaled. This information is required so that the core can issue a correct completion, if required.                                                                |

| cfg_bus_number[7:0]          | Output    | <b>Configuration Bus Number</b> : This output provides the assigned bus<br>number for the device. The User Application must use this information in<br>the Bus Number field of outgoing TLP requests. Default value after reset<br>is 00h. Refreshed whenever a Type 0 Configuration packet is received.    |

| cfg_device_number[4:0]       | Output    | <b>Configuration Device Number</b> : This output provides the assigned device number for the device. The User Application must use this information in the Device Number field of outgoing TLP requests. Default value after reset is 00000b. Refreshed whenever a Type 0 Configuration packet is received. |

| Name                       | Direction | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| cfg_function_number[2:0]   | Output    | <b>Configuration Function Number</b> : Provides the function number for the device. The User Application must use this information in the Function Number field of outgoing TLP request. Function number is hard-wired to 000b.                                                                                                                                                                                                                                                                 |

| cfg_status[15:0]           | Output    | <b>Configuration Status</b> : Status register from the Configuration Space Header.                                                                                                                                                                                                                                                                                                                                                                                                              |

| cfg_command[15:0]          | Output    | <b>Configuration Command</b> : Command register from the Configuration Space Header.                                                                                                                                                                                                                                                                                                                                                                                                            |

| cfg_dstatus[15:0]          | Output    | <b>Configuration Device Status</b> : Device status register from the PCI Express Extended Capability Structure.                                                                                                                                                                                                                                                                                                                                                                                 |

| cfg_dcommand[15:0]         | Output    | <b>Configuration Device Command</b> : Device control register from the PCI Express Extended Capability Structure.                                                                                                                                                                                                                                                                                                                                                                               |

| cfg_lstatus[15:0]          | Output    | <b>Configuration Link Status</b> : Link status register from the PCI Express Extended Capability Structure.                                                                                                                                                                                                                                                                                                                                                                                     |

| cfg_lcommand[15:0]         | Output    | <b>Configuration Link Command</b> : Link control register from the PCI Express Extended Capability Structure.                                                                                                                                                                                                                                                                                                                                                                                   |

| cfg_pm_wake_n              | Input     | <b>Configuration Power Management Wake</b> : A one-clock cycle active<br>low assertion on this signal enables the core to generate and send a<br>Power Management Wake event to the upstream link partner.<br><b>NOTE</b> : The user is required to assert this input only under stable link<br>conditions as reported on the cfg_pcie_link_state[2:0] bus. Assertion of<br>this signal when the PCI Express Link is under transition results in<br>incorrect behavior on the PCI Express Link. |