# High-Accuracy EPROM Programmable PLL Die for Crystal Oscillators

#### **Features**

- EPROM-programmable die for in-package programming of crystal oscillators

- High resolution PLL with 12-bit multiplier and 10-bit divider

- EPROM-programmable capacitor tuning array with shadow register

- Twice programmable die (CY2037A, CY2037B<sup>[1]</sup>, and CY2037-2)

- Simple 2-wire programming interface

- On-chip oscillator runs from 10 30 MHz fundamental tuned crystal

- EPROM-selectable TTL or CMOS duty cycle levels

- Operating frequency:

- □ 1 133 MHz at 5V

- □ 1 100 MHz at 3.3V

- □ 1 66.6 MHz at 2.7V

- Sixteen selectable post divide options, using PLL or reference oscillator output

- Programmable power down (PD#) or OE pin (CY2037A, CY2037B, and CY2037-2)

- Frequency select (CY2037-3)

- Programmable asynchronous or synchronous OE and power down (PD#) modes (CY2037A, CY2037B, and CY2037-2)

- Low jitter outputs typically:

- $\Box$  <  $\pm$  100 ps (pk-pk) at 5V and f>33 MHz  $\Box$  <  $\pm$  125 ps (pk-pk) at 3.3V and f>33 MHz

- 3.3V or 5V operation

- Small die

- Controlled rise and fall times and output slew rate

#### **Benefits**

- Enables quick turnaround of custom oscillators

- Lowers inventory costs through stocking of blank parts

- Enables synthesis of highly accurate and stable output clock frequencies with zero or low PPM

- Enables fine-tuning of output clock frequency by adjusting C<sub>Load</sub> of the crystal

- Enables reprogramming of programmed part to correct errors, and control excess inventory

- Enables programming of output frequency after packaging

- Lowers cost of oscillator because PLL may be programmed to a high frequency using a low frequency, low cost crystal

- Duty cycle centered at 1.4V or V<sub>DD</sub>/2

- Provides flexibility to service most TTL or CMOS applications

- Provides flexibility in output configurations and testing

- Enables low power operations or output enable functions

- Enables two frequency options for meeting different industry standards, that is, PAL/NTSC

- Provides flexibility for system applications through selectable instantaneous or synchronous change in outputs

- Suitable for most PC, consumer, and networking applications

- Lowers inventory costs because the same die services both applications

- Enables encapsulation in small size, surface mount packages

- Has lower EMI than oscillators

Table 1. Device Functionality: Output Frequencies

| Parameter | Description      | Condition                   | Min | Max | Unit |

|-----------|------------------|-----------------------------|-----|-----|------|

| Fo        | Output frequency | V <sub>DD</sub> = 4.5V–5.5V | 1   | 133 | MHz  |

|           |                  | V <sub>DD</sub> = 3.0V–3.6V | 1   | 100 | MHz  |

|           |                  | $V_{DD} = 2.7V - 3.0V$      | 1   | 66  | MHz  |

#### Note

<sup>1.</sup> CY2037A and CY2037B are identical. However, CY2037B is recommended for all new designs.

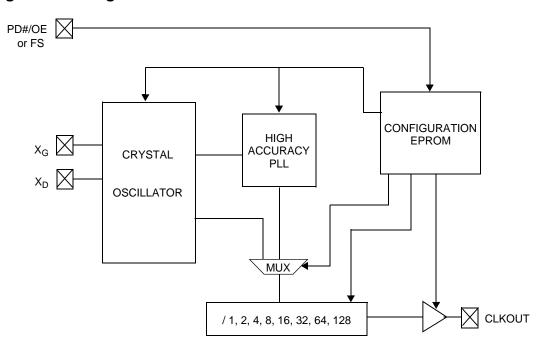

# **Logic Block Diagram**

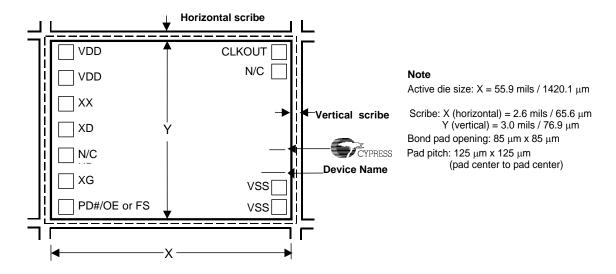

# **Die Pad Description**

# **Die Pad Summary**

| Name            | Die<br>Pad | X Coordinate<br>(μm) | Y Coordinate<br>(μm) | Description                                                                                                                                                                  |

|-----------------|------------|----------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $V_{DD}$        | 1, 2       | 124.7                | 855.6, 731           | Voltage supply                                                                                                                                                               |

| V <sub>SS</sub> | 8, 9       | 1291.35              | 99.6, 225.2          | Ground                                                                                                                                                                       |

| X <sub>D</sub>  | 4          | 124.7                | 481.8                | Crystal connection                                                                                                                                                           |

| X <sub>X</sub>  | 3          | 124.7                | 606.4                | No connect [2]                                                                                                                                                               |

| X <sub>G</sub>  | 6          | 124.7                | 232.6                | Crystal connection                                                                                                                                                           |

| PD#/OE<br>or FS | 7          | 124.7                | 108                  | CY2037A, CY2037B, and CY2037-2: EPROM-programmable power down or output enable pad CY2037-3: Frequency select. Serves as V <sub>PP</sub> in programming mode for all devices |

| CLKOUT          | 11         | 1282.45              | 901.8                | Clock output. Also serves as three-state input during programming.                                                                                                           |

| N/C             | 5, 10      | 124.7,1282.45        | 357.2, 769.4         | No connect (so do not bond to these pads)                                                                                                                                    |

#### Note

Document Number: 38-07354 Rev. \*E

$<sup>2. \ \ \, \</sup>text{For customers not bonding the } X_D \, \text{or } X_G \, \text{pad to external pins, an alternative bonding option would be shorting the } Xx \, \text{pad to the } X_D \, \text{pad.}$

#### **Functional Description**

CY2037 is an EPROM-programmable, high accuracy, PLL-based die designed for the crystal oscillator market. The die attaches directly to a low cost 10 - 30 MHz crystal and can be packaged into a 4-pin through-hole or surface mount packages. The oscillator devices may be stocked as blank parts and custom frequencies programmed in-package at the last stage before shipping. This enables fast-turn manufacture of custom and standard crystal oscillators without the need for dedicated, expensive crystals.

CY2037 contains an on-chip oscillator and a unique oscillator tuning circuit for fine-tuning of the output frequency. The crystal  $C_{load}$  may be selectively adjusted by programming a set of seven EPROM bits. This feature is used to compensate for crystal variations or to obtain a more accurate synthesized frequency.

CY2037 uses EPROM programming with a simple 2-wire, 4-pin interface that includes  $V_{SS}$  and  $V_{DD}$ . Clock outputs may be generated up to 133 MHz at 5V or up to 100 MHz at 3.3V. The entire configuration can be reprogrammed once, which allows the programmed inventory to be altered or reused.

CY2037 PLL die is designed for very high resolution. It has a 12-bit feedback counter multiplier and a 10-bit reference counter divider. This enables the synthesis of highly accurate and stable output clock frequencies with zero or low PPM error. The clock is further modified by eight output divider options of 1, 2, 4, 8, 16, 32, 64, and 128. The divider input can be selected as the PLL or crystal oscillator output, providing a total of 16 separate output options. For further flexibility, the ouput is selectable between TTL and CMOS duty cycle levels.

CY2037, CY2037B, and CY2037-2 also contain flexible power management controls. These parts include both power down (PD#) and OE features with integrated pull up resistors. The PD# and OE modes have an additional setting to determine timing (asynchronous or synchronous) with respect to the output signal. When PD# or OE modes are enabled, CLKOUT is pulled low by a weak pull down. The weak pull down is easily overdriven by another active CLKOUT for applications that require multiple CLKOUTs on a single signal path.

Controlled rise and fall times, unique output driver circuits, and innovative circuit layout techniques enable CY2037 to have low jitter and accurate outputs, making it suitable for most PC, networking, and consumer applications.

On the other hand, CY2037-3 contains a frequency select function in place of the power down and output enable modes. For example, consumer products often require frequency compatibility with different electrical standards around the world. With this frequency select feature, a product that incorporates CY2037-3 could be compatible with both NTSC for North American, and PAL for Europe by simply changing the FS line. The twice programmable feature is also absent in CY2037-3, because the second EPROM row is now being used for the alternate frequency.

#### **EPROM Configuration Block**

Table 2 summarizes the features that are configurable by EPROM. Refer "7C8038x/7C8034X Programming Specification" for further details. This specification can be obtained from your Cypress factory representative.

Table 2. EPROM Adjustable Features

| Adjustable Features                                   |                                             |  |  |  |  |

|-------------------------------------------------------|---------------------------------------------|--|--|--|--|

| _ Adjust                                              | Feedback Counter Value (P)                  |  |  |  |  |

| Frequency                                             | Reference Counter Value (Q)                 |  |  |  |  |

|                                                       | Output Divider Selection                    |  |  |  |  |

| Oscillator Tun                                        | Oscillator Tuning (Load Capacitance Values) |  |  |  |  |

| Duty Cycle Le                                         | Duty Cycle Levels (TTL or CMOS)             |  |  |  |  |

| Power Management Mode (OE or PD#)                     |                                             |  |  |  |  |

| Power Management Timing (Synchronous or Asynchronous) |                                             |  |  |  |  |

## **PLL Output Frequency**

CY2037 contains a high resolution PLL with 12-bit multiplier and 10-bit divider. The output frequency of the PLL is determined by the following formula:

$$F_{PLL} = \frac{2 \cdot (P+5)}{(Q+2)} \cdot F_{REF}$$

In this formula, P is the feedback counter value and Q is the reference counter value. P and Q are EPROM programmable values.

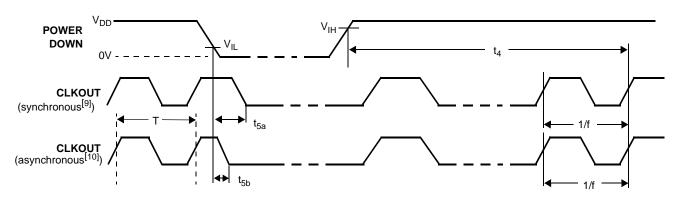

#### **Power Management Features** (except CY2037-3)

CY2037 contains EPROM-programmable PD# and OE functions. If power down is selected, all active circuitry on the chip is shut down when the control pin goes LOW. The oscillator and PLL circuits must relock when the part leaves the power down mode. If output enable mode is selected, the output is tri-stated and weakly pulled low when the control pin goes low. In this mode the oscillator and PLL circuits continue to operate, allowing a rapid return to normal operation when the control input is deasserted.

In addition, the PD# and OE modes can be programmed to occur synchronously or asynchronously with respect to the output signal. When the asynchronous setting is used, the power down or output disable occurs immediately (allowing for logic delays), regardless of the position in the clock cycle. However, when the synchronous setting is used, the part waits for a falling edge at the output before the power down or output enable signal is initiated, thus preventing output glitches. In asynchronous or synchronous setting, the output is always enabled synchronously by waiting for the next falling edge of the output.

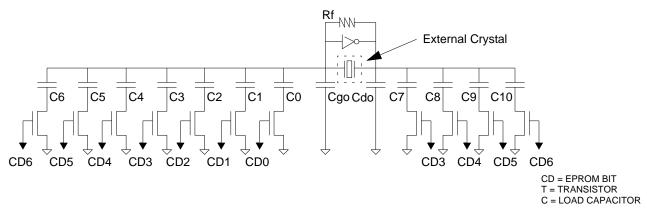

# **Crystal Oscillator Tuning Circuit**

CY2037 contains a unique tuning circuit to fine-tune the output frequency of the device. The tuning circuit consists of an array of eleven load capacitors on both sides of the oscillator drive inverter. The capacitor load values are EPROM-programmable and may be increased in small increments. As the capacitor load is increased the circuit is fine-tuned to a lower frequency. The capacitor load values vary from 0.17 pF to 8 pF for a 100:1 total control ratio. The tuning increments are shown in Table 3. Refer to "7C8038x/7C8034x Programming Specification" for further details.

Figure 1. Crystal Oscillator Tuning Circuit

**Table 3. Crystal Oscillator Parameter**

| Parameter       | Description                                                                      | Min        | Тур.   | Max        | Unit     |

|-----------------|----------------------------------------------------------------------------------|------------|--------|------------|----------|

| R <sub>f</sub>  | Feedback resistor, $V_{DD} = 4.5-5.5V$<br>Feedback resistor, $V_{DD} = 2.7-3.6V$ | 0.5<br>1.0 | 2<br>4 | 3.5<br>9.0 | MΩ<br>MΩ |

| Capacitors h    | nave ± 20% tolerance                                                             |            |        |            | •        |

| C <sub>g</sub>  | Gate capacitor                                                                   |            | 13     |            | pF       |

| C <sub>d</sub>  | Drain capacitor                                                                  |            | 9      |            | pF       |

| $C_0$           | Series cap                                                                       |            | 0.27   |            | pF       |

| C <sub>1</sub>  | Series cap                                                                       |            | 0.52   |            | pF       |

| C <sub>2</sub>  | Series cap                                                                       |            | 1.00   |            | pF       |

| C <sub>3</sub>  | Series cap                                                                       |            | 0.7    |            | pF       |

| C <sub>4</sub>  | Series cap                                                                       |            | 1.4    |            | pF       |

| C <sub>5</sub>  | Series cap                                                                       |            | 2.6    |            | pF       |

| C <sub>6</sub>  | Series cap                                                                       |            | 5.0    |            | pF       |

| C <sub>7</sub>  | Series cap                                                                       |            | 0.45   |            | pF       |

| C <sub>8</sub>  | Series cap                                                                       |            | 0.85   |            | pF       |

| C <sub>9</sub>  | Series cap                                                                       |            | 1.7    |            | pF       |

| C <sub>10</sub> | Series cap                                                                       |            | 3.3    |            | pF       |

#### CY2037A/CY2037B Versus CY2037-2

CY2037A and CY2037B contain a shadow register in addition to the EPROM register. The shadow register is an exact copy of the EPROM register and is the default register when the Valid bit is not set. It is useful when the prototype or production environment calls for measuring and adjusting the CLKOUT frequency several times. Multiple adjustments can be performed with the shadow register. After the required frequency is achieved the EPROM register is permanently programmed.

Some production flows do not require the use of the shadow register. If this is the case, then CY2037-2 is the chosen device and CY2037-2 has a disabled shadow register. CY2037-3 contains the shadow register.

#### Frequency Select Feature of CY2037-3

CY2037-3 contains a frequency select function in place of the powerdown and the output enable functions. With the frequency select feature, customers can switch two different frequencies that are configured in the two EPROM rows. Table 4 lists the definition of the frequency select pin (FS).

Table 4. Frequency Select Pin Decoding for CY2037-3

| FS Pin | Output Frequency               |

|--------|--------------------------------|

| 0      | From EPROM row 0 configuration |

| 1      | From EPROM row 1 configuration |

#### Inkless Die Pick Map (DPM) Format

Cypress ships inkless wafers to customers with an accompanying die pick map, which is used to determine the good die for assembly and programming. Customers can also access individual DPM files at their convenience through ftp.cypress.com with a valid user account login and password. Contact your local Cypress Field Application Engineer (FAE) or sales representative for a customer FTP account. The DPM files are named with the fab lot number and wafer number scribed on the wafer. The DPM files are transferred to the customer's FTP account when the factory ships out the wafers against their purchase order (PO).

[+] Feedback

Page 6 of 11

# **Absolute Maximum Ratings**

Exceeding maximum ratings may shorten the useful life of the device. User guidelines are not tested.  $\sp(3)$

Supply voltage ......-0.5 to +7.0V

| Input voltage –0.5V to V <sub>DD</sub> +0          | ).5 |

|----------------------------------------------------|-----|

| Storage temperature (non-condensing) 55°C to +150° | °С  |

| Junction temperature40°C to +100°                  | °C  |

| Static discharge voltage                           | VC  |

# **Operating Conditions**

| Parameter           | Description                                                                                           | Min  | Max      | Unit     |

|---------------------|-------------------------------------------------------------------------------------------------------|------|----------|----------|

| V <sub>DD</sub>     | Supply voltage (3.3V)                                                                                 | 2.7  | 3.6      | V        |

|                     | Supply voltage (5.0V)                                                                                 | 4.5  | 5.5      | V        |

| T <sub>AJ</sub> [4] | Operating temperature, Junction                                                                       | -10  | +100     | °C       |

| C <sub>TTL</sub>    | Max. capacitive load on outputs for TTL levels $V_{DD} = 4.5-5.5V$ , output frequency = 1 - 40 MHz    |      | 50       | pF       |

|                     | $V_{DD} = 4.5-5.5V$ , output frequency = 40 - 133 MHz                                                 |      | 25       | pF       |

| C <sub>CMOS</sub>   | Max. capacitive load on outputs for CMOS levels $V_{DD} = 4.5-5.5V$ , output frequency = 1 - 66.6 MHz |      | 50       | pF       |

|                     | V <sub>DD</sub> = 4.5–5.5V, output frequency = 66.6 - 133 MHz                                         |      | 25<br>30 | pF<br>pF |

|                     | $V_{DD} = 3.0-3.6V$ , output frequency = 1 - 40 MHz                                                   |      | 15       | pF       |

|                     | $V_{DD} = 3.0-3.6V$ , output frequency = 40 - 100 MHz                                                 |      | 15       | pF       |

|                     | V <sub>DD</sub> = 2.7–3.0V, output frequency = 1 - 66 MHz                                             |      |          |          |

| X <sub>REF</sub>    | Reference frequency, input crystal. Fundamental tuned crystals only                                   | 10   | 30       | MHz      |

| t <sub>PU</sub>     | Power up time for all VDDs to reach minimum specified voltage (power ramps must be monotonic)         | 0.05 | 50       | ms       |

### **Electrical Characteristics**

Over the Operating Range<sup>[5]</sup>

| Parameter                       | Description                              | Test Conditions                                                                                         | Min                                            | Тур.       | Max                       | Unit     |

|---------------------------------|------------------------------------------|---------------------------------------------------------------------------------------------------------|------------------------------------------------|------------|---------------------------|----------|

| V <sub>IL</sub>                 | Low level input voltage                  | $V_{DD} = 4.5V - 5.5V$<br>$V_{DD} = 2.7V - 3.6V$                                                        |                                                |            | 0.8<br>0.2V <sub>DD</sub> | V<br>V   |

| V <sub>IH</sub>                 | High level input voltage                 | $V_{DD} = 4.5V - 5.5V$<br>$V_{DD} = 2.7V - 3.6V$                                                        | 2.0<br>0.7V <sub>DD</sub>                      |            |                           | V<br>V   |

| V <sub>OL</sub>                 | Low level output voltage                 | $V_{DD} = 4.5V - 5.5V$ , $I_{OL} = 16 \text{ mA}$<br>$V_{DD} = 2.7V - 3.6V$ , $I_{OL} = 8 \text{ mA}$   |                                                |            | 0.4<br>0.4                | V<br>V   |

| V <sub>OHCMOS</sub>             | High level output voltage, CMOS levels   | $V_{DD} = 4.5V - 5.5V$ , $I_{OH} = -16$ mA<br>$V_{DD} = 2.7V - 3.6V$ , $I_{OH} = -8$ mA                 | V <sub>DD</sub> - 0.4<br>V <sub>DD</sub> - 0.4 |            |                           | V        |

| V <sub>OHTTL</sub>              | High level output voltage,<br>TTL levels | $V_{DD} = 4.5V - 5.5V, I_{OH} = -8 \text{ mA}$                                                          | 2.4                                            |            |                           | V        |

| I <sub>IL</sub>                 | Input low current                        | $V_{IN} = 0V$                                                                                           |                                                |            | 10                        | μА       |

| I <sub>IH</sub>                 | Input high current                       | $V_{IN} = V_{DD}$                                                                                       |                                                |            | 5                         | μА       |

| I <sub>DD</sub>                 | Power supply current,<br>Unloaded        | $V_{DD}$ = 4.5V - 5.5V, output frequency <= 133 MHz $V_{DD}$ = 2.7V - 3.6V, output frequency <= 100 MHz |                                                |            | 45<br>25                  | mA<br>mA |

| I <sub>DDS</sub> <sup>[6]</sup> | Standby current                          | V <sub>DD</sub> = 2.7V - 3.6V                                                                           |                                                | 10         | 50                        | μА       |

| R <sub>UP</sub>                 | Input pull up resistor                   | $V_{DD} = 4.5V - 5.5V, V_{IN} = 0V$<br>$V_{DD} = 4.5V - 5.5V, V_{IN} = 0.7V_{DD}$                       | 1.1<br>50                                      | 3.0<br>100 | 8.0<br>200                | MΩ<br>kΩ |

| I <sub>OE_CLKOUT</sub>          | CLKOUT pull down current                 | V <sub>DD</sub> = 5.0                                                                                   |                                                | 20         |                           | μА       |

- Stresses greater than listed can impair the life of the device.

This product is sold in die form so operating conditions are specified for the die, or junction temperature.

- 5. This part was characterized in a 20-pin SOIC package with external crystal, Electrical Characteristics can change with other package types.

- 6. If external reference is used, it is required to stop the reference (set reference to LOW) during power down.

# **Output Clock Switching Characteristics**

Over the Operating Range<sup>[7]</sup>

| Parameter       | Description                                                                         | Test Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Min                  | Тур                  | Max                                     | Unit                       |

|-----------------|-------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------------|-----------------------------------------|----------------------------|

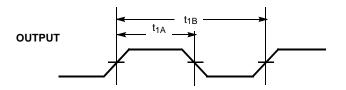

| t <sub>1w</sub> | Output duty cycle at 1.4V, $V_{DD} = 4.5-5.5V$ $t_{1w} = t_{1A} \div t_{1B}$        | 1 - 40 MHz, C <sub>L</sub> <=50 pF<br>40 - 66 MHz, C <sub>L</sub> <=15 pF<br>66 - 125 MHz, C <sub>L</sub> <=25 pF<br>125 - 133 MHz, C <sub>L</sub> <=15 pF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 45<br>45<br>40<br>40 |                      | 55<br>55<br>60<br>60                    | %<br>%<br>%                |

| t <sub>1x</sub> | Output duty cycle at $V_{DD}/2$ , $V_{DD} = 4.5-5.5V$ $t_{1x} = t_{1A} \div t_{1B}$ | 1 - 66.6 MHz, C <sub>L</sub> <=25 pF<br>66.6 - 125 MHz, C <sub>L</sub> <=25 pF<br>125 - 133 MHz, C <sub>L</sub> <=15 pF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                      |                      | 55<br>60<br>60                          | %<br>%<br>%                |

| t <sub>1y</sub> | Output duty cycle at $V_{DD}/2$ , $V_{DD} = 3.0-3.6$ $t_{1y} = t_{1A} \div t_{1B}$  | 1 - 40 MHz, C <sub>L</sub> <=30 pF<br>40 - 100 MHz, C <sub>L</sub> <=15 pF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 45<br>40             |                      | 55<br>60                                | %<br>%                     |

| t <sub>1z</sub> | Output duty cycle at $V_{DD}/2$ , $V_{DD} = 2.7-3.0$ $t_{1y} = t_{1A} \div t_{1B}$  | 1 - 40 MHz, C <sub>L</sub> <=15 pF<br>40 - 66.6 MHz, C <sub>L</sub> <=10 pF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 40<br>40             |                      | 60<br>60                                | %<br>%                     |

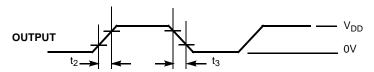

| t <sub>2</sub>  | Output clock rise time                                                              | $ \begin{array}{l} \text{Between } 0.8\text{V} - 2.0\text{V}, \text{V}_{\text{DD}} = 4.5\text{V} - 5.5\text{V}, \text{C}_{\text{L}} = 50 \text{ pF} \\ \text{Between } 0.8\text{V} - 2.0\text{V}, \text{V}_{\text{DD}} = 4.5\text{V} - 5.5\text{V}, \text{C}_{\text{L}} = 25 \text{ pF} \\ \text{Between } 0.8\text{V} - 2.0\text{V}, \text{V}_{\text{DD}} = 4.5\text{V} - 5.5\text{V}, \text{C}_{\text{L}} = 15 \text{ pF} \\ \text{Between } 0.2\text{V}_{\text{DD}} - 0.8\text{V}_{\text{DD}}, \text{V}_{\text{DD}} = 4.5\text{V} - 5.5\text{V}, \text{C}_{\text{L}} = 50 \text{ pF} \\ \text{Between } 0.2\text{V}_{\text{DD}} - 0.8\text{V}_{\text{DD}}, \text{V}_{\text{DD}} = 3.0\text{V} - 3.6\text{V}, \text{C}_{\text{L}} = 30 \text{ pF} \\ \text{Between } 0.2\text{V}_{\text{DD}} - 0.8\text{V}_{\text{DD}}, \text{V}_{\text{DD}} = 2.7\text{V} - 3.6\text{V}, \text{C}_{\text{L}} = 15 \text{ pF} \\ \end{array} $ |                      |                      | 1.8<br>1.2<br>0.9<br>3.4<br>4.0<br>2.4  | ns<br>ns<br>ns<br>ns<br>ns |

| t <sub>3</sub>  | Output clock fall time                                                              | Between $0.8V - 2.0V$ , $V_{DD} = 4.5V - 5.5V$ , $C_{L} = 50  pF$<br>Between $0.8V - 2.0V$ , $V_{DD} = 4.5V - 5.5V$ , $C_{L} = 25  pF$<br>Between $0.8V - 2.0V$ , $V_{DD} = 4.5V - 5.5V$ , $C_{L} = 15  pF$<br>Between $0.2V_{DD} - 0.8V_{DD}$ , $V_{DD} = 4.5V - 5.5V$ , $C_{L} = 50  pF$<br>Between $0.2V_{DD} - 0.8V_{DD}$ , $V_{DD} = 3.0V - 3.6V$ , $C_{L} = 30  pF$<br>Between $0.2V_{DD} - 0.8V_{DD}$ , $V_{DD} = 2.7V - 3.6V$ , $C_{L} = 15  pF$                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                      |                      | 1.8<br>1.2<br>0.9<br>3.4<br>4.0<br>2.4  | ns<br>ns<br>ns<br>ns<br>ns |

| t <sub>4</sub>  | Startup time out of power down                                                      | PD# pin LOW to HIGH <sup>[8]</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                      | 1                    | 2                                       | ms                         |

| t <sub>5a</sub> | Power down delay time (synchronous setting)                                         | PD# pin LOW to output LOW (T = period of output clk)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                      | T/2                  | T+10                                    | ns                         |

| t <sub>5b</sub> | Power down delay time (asynchronous setting)                                        | PD# pin LOW to output LOW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                      | 10                   | 15                                      | ns                         |

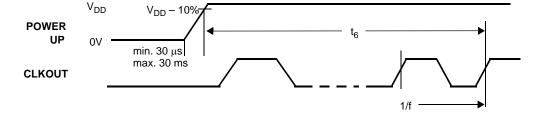

| t <sub>6</sub>  | Power up time                                                                       | From power on <sup>[8]</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                      | 1                    | 2                                       | ms                         |

| t <sub>7a</sub> | Output disable time (synchronous setting)                                           | OE pin LOW to output Hi-Z<br>(T = period of output clk)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                      | T/2                  | T+10                                    | ns                         |

| t <sub>7b</sub> | Output disable time (asynchronous setting)                                          | OE pin LOW to output Hi-Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                      | 10                   | 15                                      | ns                         |

| t <sub>8</sub>  | Output enable time (always synchronous enable)                                      | OE pin LOW to HIGH<br>(T = period of output clk)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                      | Т                    | 1.5T+2<br>5                             | ns                         |

| t <sub>9</sub>  | Peak-to-peak period jitter                                                          | $\begin{split} V_{DD} &= 4.5 \text{V} - 5.5 \text{V},  \text{Fo} > 33  \text{MHz},  \text{VCO} > 100  \text{MHz} \\ V_{DD} &= 2.7 \text{V} - 3.6 \text{V},  \text{Fo} > 33  \text{MHz},  \text{VCO} > 100  \text{MHz} \\ V_{DD} &= 2.7 \text{V} - 5.5 \text{V},  \text{Fo} < 33  \text{MHz} \end{split}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                      | ±100<br>±125<br>±250 | ±125<br>±200<br>1% of<br>F <sub>O</sub> | ps<br>ps<br>ps             |

#### Notes

<sup>7.</sup> Not all parameters measured in production testing.

8. Oscillator start time cannot be guaranteed for all crystal types. This specification is for operation with AT cut crystals with ESR < 70 ohms.</li>

# **Switching Waveforms**

Figure 2. Duty Cycle Timing  $(t_{1w,}t_{1x,}t_{1y},t_{1z})$

Figure 3. Output Rise/Fall Time

Figure 4. Power Down Timing (synchronous and asynchronous modes)

Figure 5. Power Up Timing

#### Notes

In synchronous mode the power down or output tri-state is not initiated until the next falling edge of the output clock.

In asynchronous mode the power down or output tri-state occurs within 25 ns regardless of position in the output clock cycle.

# Ordering Information[11]

| Ordering Code    | Status                                                 | Туре          | Wafer Thickness | Operating Range |

|------------------|--------------------------------------------------------|---------------|-----------------|-----------------|

| CY2037AWAF       | Obsolete                                               | Inked Wafer   | 14 ± 0.5 mils   | -10°C to +100°C |

| CY2037-2WAF      | Obsolete                                               | Inked Wafer   | 14 ± 0.5 mils   | −10°C to +100°C |

| CY2037-3WAF      | Obsolete                                               | Inked Wafer   | 14 ± 0.5 mils   | −10°C to +100°C |

| CY2037BWAF       | Obsolete                                               | Inked Wafer   | 14 ± 0.5 mils   | -10°C to +100°C |

| CY2037B-11WAF    | Obsolete                                               | Inked Wafer   | 11 ± 0.5 mils   | −10°C to +100°C |

| CY2037BWAF-IL    | Active                                                 | Inkless Wafer | 14 ± 0.5 mils   | −10°C to +100°C |

| CY2037B-11WAF-IL | Active                                                 | Inkless Wafer | 11 ± 0.5 mils   | −10°C to +100°C |

| CY2037-2WAF-IL   | Obsolete, CY2037BWAF-IL is recommended for new designs | Inkless Wafer | 14 ± 0.5 mils   | −10°C to +100°C |

| CY2037-3WAF-IL   | Obsolete                                               | Inkless Wafer | 14 ± 0.5 mils   | -10°C to +100°C |

Document Number: 38-07354 Rev. \*E Page 10 of 11

Notes

11. The only difference between the CY2037A/CY2037B, and the CY2037-2 is that the CY2037-2 has the shadow register disabled. CY2037-3 replaces the power down options with a frequency select and contains the shadow register.

#### **Document History Page**

|      | Document Title: CY2037 High-Accuracy EPROM Programmable PLL Die for Crystal Oscillators Document Number: 38-07354 |            |                    |                                                                                                                                                                       |  |  |  |

|------|-------------------------------------------------------------------------------------------------------------------|------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| REV. | ECN NO.                                                                                                           | Issue Date | Orig. of<br>Change | Description of Change                                                                                                                                                 |  |  |  |

| **   | 112248                                                                                                            | 03/01/02   | DSG                | Change from Spec number: 38-00679 to 38-07354                                                                                                                         |  |  |  |

| *A   | 121857                                                                                                            | 12/14/02   | RBI                | Power up requirements added to Operating Conditions Information                                                                                                       |  |  |  |

| *B   | 291092                                                                                                            | See ECN    | RGL                | Updated Min. Operating Temperature, Junction                                                                                                                          |  |  |  |

| *C   | 522769                                                                                                            | See ECN    | RGL                | Added CY2037B information. Updated absolute maximum Junction temperature specification. Updated Ordering information table. Added Die Pad description and coordinates |  |  |  |

| *D   | 804376                                                                                                            | See ECN    | RGL                | Minor Change: To post on web                                                                                                                                          |  |  |  |

| *E   | 2192266                                                                                                           | See ECN    | DPF/PYRS           | Added Inkless Die information.                                                                                                                                        |  |  |  |

© Cypress Semiconductor Corporation, 2002-2008. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any license under patent or other rights. Cypress products are not warranted nor intended to be used for medical, life support, life saving, critical control or safety applications, unless pursuant to an express written agreement with Cypress. Furthermore, Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Any Source Code (software and/or firmware) is owned by Cypress Semiconductor Corporation (Cypress) and is protected by and subject to worldwide patent protection (United States and foreign), United States copyright laws and international treaty provisions. Cypress hereby grants to licensee a personal, non-exclusive, non-transferable license to copy, use, modify, create derivative works of, and compile the Cypress Source Code and derivative works for the sole purpose of creating custom software and or firmware in support of licensee product to be used only in conjunction with a Cypress integrated circuit as specified in the applicable agreement. Any reproduction, modification, translation, or representation of this Source Code except as specified above is prohibited without the express written permission of Cypress.

Disclaimer: CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Cypress reserves the right to make changes without further notice to the materials described herein. Cypress does not assume any liability arising out of the application or use of any product or circuit described herein. Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress' product in a life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Use may be limited by and subject to the applicable Cypress software license agreement.

Document Number: 38-07354 Rev. \*E

Revised March 06, 2008

Page 11 of 11

Purchase of I2C components from Cypress or one of its sublicensed Associated Companies conveys a license under the Philips I2C Patent Rights to use these components in an I2C system, provided that the system conforms to the I2C Standard Specification as defined by Philips. All products and company names mentioned in this document may be the trademarks of their respective holders.

OOO «ЛайфЭлектроникс" "LifeElectronics" LLC

ИНН 7805602321 КПП 780501001 P/C 40702810122510004610 ФАКБ "АБСОЛЮТ БАНК" (ЗАО) в г.Санкт-Петербурге К/С 3010181090000000703 БИК 044030703

Компания «Life Electronics» занимается поставками электронных компонентов импортного и отечественного производства от производителей и со складов крупных дистрибьюторов Европы, Америки и Азии.

С конца 2013 года компания активно расширяет линейку поставок компонентов по направлению коаксиальный кабель, кварцевые генераторы и конденсаторы (керамические, пленочные, электролитические), за счёт заключения дистрибьюторских договоров

#### Мы предлагаем:

- Конкурентоспособные цены и скидки постоянным клиентам.

- Специальные условия для постоянных клиентов.

- Подбор аналогов.

- Поставку компонентов в любых объемах, удовлетворяющих вашим потребностям.

- Приемлемые сроки поставки, возможна ускоренная поставка.

- Доставку товара в любую точку России и стран СНГ.

- Комплексную поставку.

- Работу по проектам и поставку образцов.

- Формирование склада под заказчика.

- Сертификаты соответствия на поставляемую продукцию (по желанию клиента).

- Тестирование поставляемой продукции.

- Поставку компонентов, требующих военную и космическую приемку.

- Входной контроль качества.

- Наличие сертификата ISO.

В составе нашей компании организован Конструкторский отдел, призванный помогать разработчикам, и инженерам.

Конструкторский отдел помогает осуществить:

- Регистрацию проекта у производителя компонентов.

- Техническую поддержку проекта.

- Защиту от снятия компонента с производства.

- Оценку стоимости проекта по компонентам.

- Изготовление тестовой платы монтаж и пусконаладочные работы.

Тел: +7 (812) 336 43 04 (многоканальный) Email: org@lifeelectronics.ru