## General Description

The MAX520/MAX521 are quad/octal, 8-bit voltage-output digital-to-analog converters (DACs) with simple 2-wire serial interfaces that allow communication between multiple devices. They operate from a single +5V supply and their reference input range includes both supply rails.

The MAX521 includes rail-to-rail output buffer amplifiers for reduced system size and component count when driving loads. The MAX520's unbuffered voltage outputs reduce the device's total supply current to  $4\mu$ A and provide increased accuracy at low output currents.

The MAX520/MAX521 feature a serial interface and internal software protocol, allowing communication at data rates up to 400kbps. The interface, combined with the double-buffered input configuration, allows the DAC registers to be updated individually or simultaneously. In addition, the devices can be put into a low-power shutdown mode that reduces supply current to 4 $\mu$ A. Power-on reset ensures the DAC outputs are at 0V when power is initially applied.

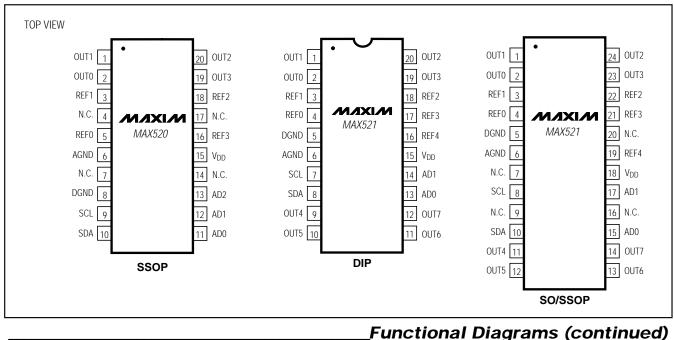

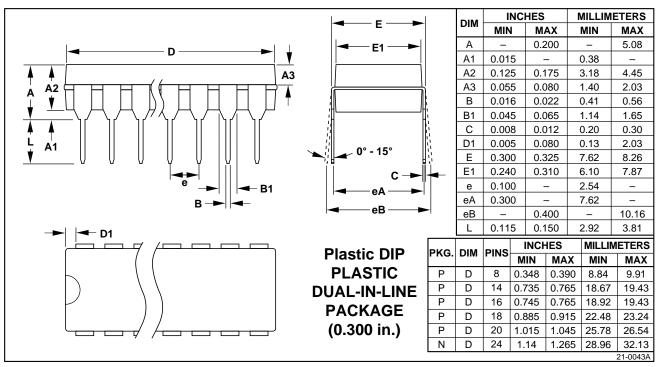

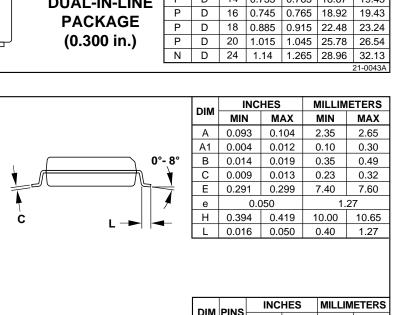

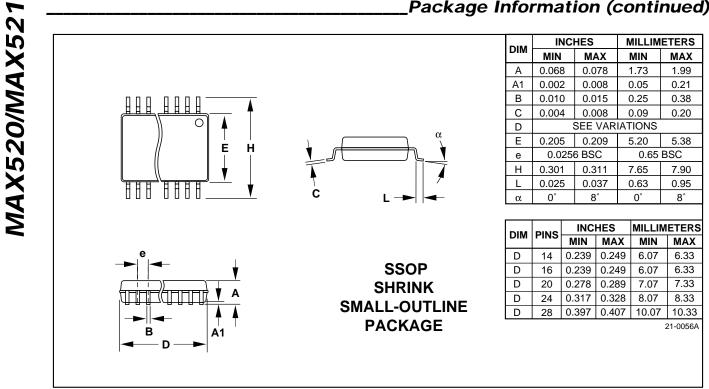

The MAX520 is available in 16-pin DIP and wide SO packages, as well as a space-saving 20-pin SSOP. The MAX521 comes in 20-pin DIP and 24-pin SO packages, as well as a space-saving 24-pin SSOP.

### **Applications**

Minimum Component Analog Systems Digital Offset/Gain Adjustment Industrial Process Control Automatic Test Equipment Programmable Attenuators

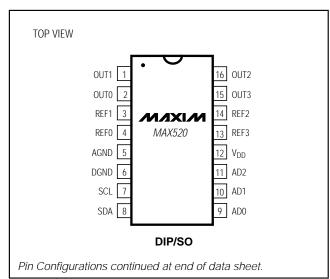

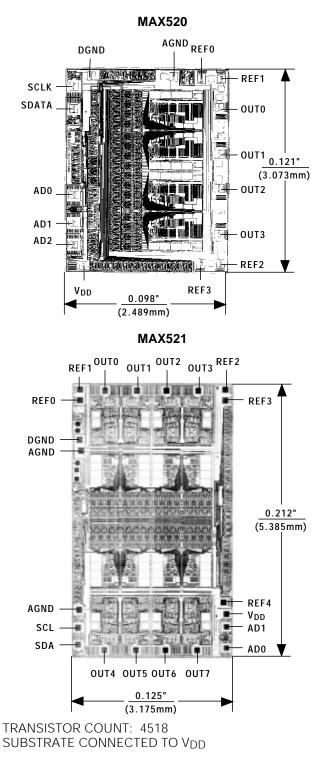

## Pin Configurations

##

\_Features

- Single +5V Supply

- Simple 2-Wire Serial Interface

- ✤ I<sup>2</sup>C Compatible

- Outputs Swing Rail to Rail: Unbuffered Outputs (MAX520) Buffered Outputs (MAX521)

- ♦ 1%-Accurate Trimmed Output Resistance (MAX520A)

- ♦ Ultra-Low 4µA Supply Current (MAX520)

- ♦ Individual DACs Have Separate Reference Inputs

- Power-On Reset Clears All Latches

- 4µA Power-Down Mode

### Ordering Information

| PART <sup>†</sup> | TEMP. RANGE                    | PIN-PACKAGE    | TUE<br>(LSB) |

|-------------------|--------------------------------|----------------|--------------|

| MAX520ACPE        | $0^{\circ}C$ to $+70^{\circ}C$ | 16 Plastic DIP | 1            |

| MAX520BCPE        | 0°C to +70°C                   | 16 Plastic DIP | 1            |

| MAX520ACWE        | 0°C to +70°C                   | 16 Wide SO     | 1            |

| MAX520BCWE        | $0^{\circ}C$ to $+70^{\circ}C$ | 16 Wide SO     | 1            |

#### Ordering Information continued at end of data sheet.

<sup>†</sup>MAX520 "A" grade parts include a 1%-accurate, factory-trimmed output resistance.

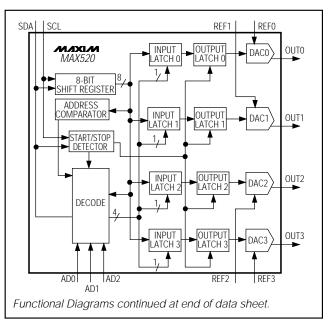

## **Functional Diagrams**

Maxim Integrated Products 1

For free samples & the latest literature: http://www.maxim-ic.com, or phone 1-800-998-8800

### **ABSOLUTE MAXIMUM RATINGS**

| VDD to DGND                  | -0.3V to +6V                     |

|------------------------------|----------------------------------|

| V <sub>DD</sub> to AGND      |                                  |

| OUT                          | 0.3V to (V <sub>DD</sub> + 0.3V) |

| REF                          | 0.3V to (V <sub>DD</sub> + 0.3V) |

| AD0, AD1, AD2                | 0.3V to (V <sub>DD</sub> + 0.3V) |

| SCL, SDA to DGND             | 0.3V to +6V                      |

| AGND to DGND                 | 0.3V to +0.3V                    |

| Maximum Current into Any Pin | 50mA                             |

|                              | 3000                             |

Continuous Power Dissipation ( $T_A = +70^{\circ}C$ )

16-Pin Plastic DIP (derate 10.53mW/°C above +70°C)...842mW 20-Pin Plastic DIP (derate 11.11mW/°C above +70°C)...889mW

16-Pin Wide SO (derate 9.52mW/°C above +70°C) .....762mW 24-Pin Wide SO (derate 11.76mW/°C above +70°C) ....941mW 20-Pin SSOP (derate 8.00mW/°C above +70°C) ......640mW 24-Pin SSOP (derate 8.00mW/°C above +70°C) ......640mW 16-Pin CERDIP (derate 10.00mW/°C above +70°C) ....800mW 20-Pin CERDIP (derate 11.11mW/°C above +70°C) ....889mW Operating Temperature Ranges

| MAX520_C/MAX521_C                   | 0°C to +70°C   |

|-------------------------------------|----------------|

| MAX520_E/MAX521_E                   | 40°C to +85°C  |

| MAX520_MJE/MAX521BMJP               | 55°C to +125°C |

| Storage Temperature Range           | 65°C to +150°C |

| Lead Temperature (soldering, 10sec) | +300°C         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **ELECTRICAL CHARACTERISTICS**

$(V_{DD} = 5V \pm 10\%, V_{REF} = 4V, R_L = \infty$  (MAX520),  $R_L = 10k\Omega$  (MAX521),  $C_L = 0pF$  (MAX520),  $C_L = 100pF$  (MAX521),  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25$ °C)

| PARAMETER                                | SYMBOL | CONDITIONS                        |          | MIN | TYP | MAX  | UNITS |

|------------------------------------------|--------|-----------------------------------|----------|-----|-----|------|-------|

| STATIC ACCURACY                          | 1      |                                   |          |     |     |      | 1     |

| Resolution                               |        |                                   |          | 8   |     |      | Bits  |

|                                          |        |                                   | MAX520_  |     |     | ±1   |       |

| Total Unadjusted Error                   | TUE    |                                   | MAX521A  |     |     | ±1.5 | LSB   |

|                                          |        |                                   | MAX521B  |     |     | ±2   |       |

| Differential Nonlinearity                | DNL    | Guaranteed mono                   | tonic    |     |     | ±1.0 | LSB   |

|                                          | ZCE    | Code = 00 hex                     | MAX520_  |     |     | 8    | mV    |

| Zero-Code Error                          |        |                                   | MAX521_C |     |     | 18   |       |

| Zero-Code Error                          |        |                                   | MAX521_E |     |     | 20   |       |

|                                          |        |                                   | MAX521BM |     |     | 20   |       |

| Zero-Code-Error Supply Rejection         |        | Code = 00 hex                     |          |     | ±1  |      | mV    |

| Zero-Code-Error Temperature Coefficient  |        | Code = 00 hex                     |          |     | ±10 |      | µV/°C |

|                                          |        |                                   | MAX520_  |     |     | 8    | mV    |

| Full Coole Error                         |        | Code = FF hex                     | MAX521_C |     |     | 18   |       |

| Full-Scale Error                         |        | Code = FF nex                     | MAX521_E |     |     | 20   |       |

|                                          |        |                                   | MAX521BM |     |     | 20   |       |

| Full-Scale-Error Supply Rejection        |        | Code = FF hex, $V_{DD}$ = 5V ±10% |          |     | ±1  |      | mV    |

| Full-Scale-Error Temperature Coefficient |        |                                   |          |     | ±10 |      | µV/°C |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = 5V \pm 10\%, V_{REF_} = 4V, R_L = \infty$  (MAX520),  $R_L = 10k\Omega$  (MAX521),  $C_L = 0pF$  (MAX520),  $C_L = 100pF$  (MAX521),  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ )

| PARAMETER                      | SYMBOL          | CONDITIONS                                                       |                 | MIN                 | TYP     | MAX  | UNITS              |          |

|--------------------------------|-----------------|------------------------------------------------------------------|-----------------|---------------------|---------|------|--------------------|----------|

| REFERENCE INPUTS               | 1               |                                                                  |                 |                     |         |      |                    |          |

| Input Voltage Range            |                 |                                                                  |                 |                     | 0       |      | V <sub>DD</sub>    | V        |

|                                |                 | Code =                                                           | MAX520_         |                     | 8       | 12   |                    |          |

| Input Resistance               | RIN             | 55 hex                                                           | MAX521_         | REF4                | 4       | 6    |                    | kΩ       |

|                                |                 | (Note 1)                                                         | IVIAA521_       | REF0-REF3           | 16      | 24   |                    |          |

| Input Current                  |                 | PD = 1                                                           |                 |                     |         |      | ±10                | μΑ       |

|                                |                 | Code =                                                           | MAX520_         | MAX520_             |         | 30   |                    |          |

| Input Capacitance              |                 | FF hex                                                           | MAX521_         | REF4                |         | 120  |                    | pF       |

|                                |                 | (Note 2)                                                         |                 | REF0-REF3           |         | 30   |                    |          |

| Channel-to-Channel Isolation   |                 | (Note 3)                                                         | MAX520_         |                     |         | -70  |                    | dB       |

|                                |                 |                                                                  | MAX521_         |                     |         | -60  |                    |          |

| AC Feedthrough                 |                 | (Note 4)                                                         |                 |                     |         | -70  |                    | dB       |

| DAC OUTPUTS                    |                 |                                                                  |                 |                     | I       |      |                    |          |

| Full-Scale Output Voltage      |                 |                                                                  |                 |                     | 0       |      | Vdd                | V        |

|                                |                 | MAX520A $T_A = +25^{\circ}C$                                     |                 | 15.8                | 16      | 16.2 |                    |          |

| Output Resistance (Note 5)     |                 | 101703207                                                        | $T_A = T_{MIN}$ | to T <sub>MAX</sub> | 15.6    | 16   | 16.4               | kΩ       |

|                                |                 | MAX520B                                                          |                 |                     | 8.4     |      | 16.4               | ]        |

|                                |                 | MAX521_, O<br>0mA to 2.5m                                        | UT_ = 4V,<br>A  |                     |         | 0.25 |                    |          |

| Output Load Regulation         |                 | MAX521_C/E, $V_{REF_} = V_{DD}$ ,<br>code = FF hex, 0µA to 500µA |                 |                     | 1.5     |      | LSB                |          |

|                                |                 | MAX521BM, $V_{REF_} = V_{DD}$ ,<br>code = FF hex, 0µA to 500µA   |                 |                     |         | 2.0  |                    |          |

| Output Leakage Current         |                 | MAX521_, C<br>PD = 1                                             | UT_ = 0V to '   | V <sub>DD</sub> ,   |         |      | ±10                | μΑ       |

| DIGITAL INPUTS SCL, SDA        |                 | 1                                                                |                 |                     |         |      |                    | 1        |

| Input High Voltage             | ViH             |                                                                  |                 |                     | 0.7VDD  |      |                    | V        |

| Input Low Voltage              | VIL             |                                                                  |                 |                     |         |      | 0.3V <sub>DD</sub> | V        |

| Input Current                  | IIN             | $0V \le V_{IN} \le V$                                            | DD              |                     |         |      | ±10                | μA       |

| Input Hysteresis               | VHYST           | (Note 5)                                                         |                 |                     | 0.05VDD |      |                    | V        |

| Input Capacitance              | CIN             | (Note 5)                                                         |                 |                     |         |      | 10                 | pF       |

| DIGITAL INPUTS AD0, AD1        |                 | 1 * *                                                            |                 |                     | 1       |      |                    | 1 .      |

| Input High Voltage             | VIH             |                                                                  |                 |                     | 2.4     |      |                    | V        |

| Input Low Voltage              | VIL             |                                                                  |                 |                     |         |      | 0.8                | V        |

| Input Leakage                  | I <sub>IN</sub> | $V_{IN} = 0V to V$                                               | / <sub>DD</sub> |                     |         |      | ±10                | μA       |

| DIGITAL OUTPUT SDA (Note 6)    | 1               |                                                                  |                 |                     | 1       |      |                    | <u> </u> |

|                                |                 | Isink = 3mA                                                      |                 |                     |         |      | 0.4                |          |

| Output Low Voltage             | Vol             | ISINK = 6mA                                                      |                 |                     |         |      | 0.6                | V        |

| Three-State Leakage Current    | IL              | $V_{IN} = OV \text{ to } V_{DD}$                                 |                 |                     |         |      | ±10                | μA       |

| Three-State Output Capacitance | Соит            | (Note 5)                                                         | 50              |                     |         |      | 10                 | pF       |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = 5V \pm 10\%, V_{REF} = 4V, R_L = \infty$  (MAX520),  $R_L = 10k\Omega$  (MAX521),  $C_L = 0pF$  (MAX520),  $C_L = 100pF$  (MAX521),  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ )

| PARAMETER                          | SYMBOL          | CONDITIONS                                                  |             | MIN | TYP | MAX | UNITS |  |

|------------------------------------|-----------------|-------------------------------------------------------------|-------------|-----|-----|-----|-------|--|

| DYNAMIC PERFORMANCE                | ł               |                                                             |             |     |     |     | 1     |  |

|                                    |                 |                                                             | MAX521_C    |     | 1.0 |     |       |  |

| Voltage Output Slew Rate           |                 | Positive and negative                                       | MAX521_E    |     | 0.7 |     | V/µs  |  |

|                                    |                 |                                                             | MAX521BM    |     | 0.5 |     |       |  |

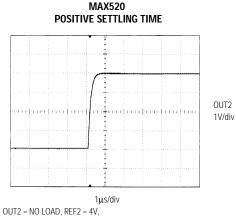

| Output Sattling Time               |                 | MAX520_, to 1/2LSB,                                         | no load     |     | 2   |     |       |  |

| Output Settling Time               |                 | MAX521_, to 1/2LSB, 10k $\Omega$ and 100pF load (Note 7)    |             |     | 6   |     | – µs  |  |

| Digital Feedthrough                |                 | Code = 00 hex, all digital inputs from $OV$ to $V_{DD}$     |             |     | 5   |     | nV-s  |  |

| Digital-Analog Glitch Impulse      |                 | Code 128 to 127                                             |             |     | 12  |     | nV-s  |  |

| Signal to Noise + Distortion Ratio | SINAD           | $V_{REF_}$ = 4Vp-p at 1kHz, $V_{DD}$ = 5V,<br>code = FF hex |             |     | 87  |     | dB    |  |

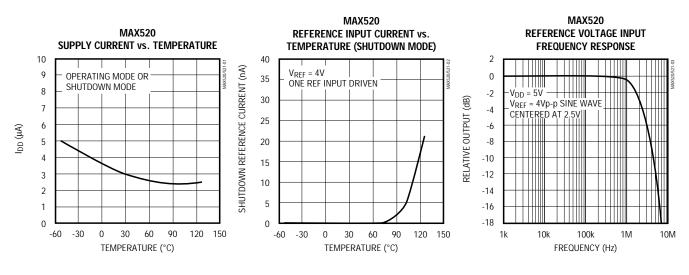

| Multiplying Bandwidth              |                 | V <sub>REF</sub> = 4Vp-p, 3dB k                             | oandwidth   |     | 1   |     | MHz   |  |

| Wideband Amplifier Noise           |                 | MAX521_                                                     |             |     | 60  |     | μVrms |  |

| POWER REQUIREMENTS                 | L               |                                                             |             |     |     |     |       |  |

| Supply Voltage                     | V <sub>DD</sub> |                                                             |             | 4.5 |     | 5.5 | V     |  |

|                                    |                 | Operating mode, out-                                        | MAX520_     |     | 4   | 20  | μA    |  |

| Supply Current                     | מסו             | put unloaded, all dig-<br>ital inputs 0V or V <sub>DD</sub> | MAX521_C    |     | 10  | 20  | — mA  |  |

| Supply Current                     | עטי             |                                                             | MAX521_E/BM |     | 10  | 24  |       |  |

|                                    |                 | Power-down mode (PD = 1)                                    |             |     | 4   | 20  | μA    |  |

**Note 1:** Input resistance is code dependent. The lowest input resistance occurs at code = 55 hex.

Note 2: Input capacitance is code dependent. The highest input capacitance occurs at code = FF hex.

**Note 3:** V<sub>REF\_</sub> = 4Vp-p, 10kHz. Channel-to-channel isolation is measured by setting the code of one DAC to FF hex and setting the code of all other DACs to 00 hex.

Note 4:  $V_{REF} = 4V_{P-p}$ , 10kHz, DAC code = 00 hex.

**Note 5:** Guaranteed by design.

Note 6: I<sup>2</sup>C-compatible mode.

Note 7: Output settling time is measured by taking the code from 00 hex to FF hex, and from FF hex to 00 hex.

### TIMING CHARACTERISTICS

$(V_{DD} = 5V \pm 10\%, T_A = T_{MIN}$  to T<sub>MAX</sub>, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.)

| PARAMETER                                          | SYMBOL               | CONDITIONS                       | MIN TYP    | MAX | UNITS |

|----------------------------------------------------|----------------------|----------------------------------|------------|-----|-------|

| Serial Clock Frequency                             | fscl                 |                                  | 0          | 400 | kHz   |

| Bus Free Time Between a STOP and a START Condition | tBUF                 |                                  | 1.3        |     | μs    |

| Hold Time, (Repeated) Start Condition              | t <sub>HD,</sub> sta |                                  | 0.6        |     | μs    |

| Low Period of the SCL Clock                        | tLOW                 |                                  | 1.3        |     | μs    |

| High Period of the SCL Clock                       | thigh                |                                  | 0.6        |     | μs    |

| Setup Time for a Repeated START Condition          | tsu, sta             |                                  | 0.6        |     | μs    |

| Data Hold Time                                     | thd, dat             | (Note 8)                         | 0          | 0.9 | μs    |

| Data Setup Time                                    | tsu, dat             |                                  | 100        |     | ns    |

| Rise Time of Both SDA and SCL Signals, Receiving   | tR                   | (Note 9)                         | 20 + 0.1Cb | 300 | ns    |

| Fall Time of Both SDA and SCL Signals, Receiving   | tF                   | (Note 9)                         | 20 + 0.1Cb | 300 | ns    |

| Fall Time of SDA Transmitting (Note 6)             | tF                   | I <sub>SINK</sub> ≤ 6mA (Note 9) | 20 + 0.1Cb | 250 | ns    |

| Setup Time for STOP Condition                      | tsu, sto             |                                  | 0.6        |     | μs    |

| Capacitive Load for Each Bus Line                  | Cb                   |                                  |            | 400 | pF    |

| Pulse Width of Spike Suppressed                    | tsp                  | (Notes 10, 11)                   | 0          | 50  | ns    |

**Note 8:** A master device must provide a hold time of at least 300ns for the SDA signal (referred to V<sub>IL</sub> of the SCL signal) in order to bridge the undefined region of SCL's falling edge.

**Note 9:** Cb = total capacitance of one bus line in pF.  $t_R$  and  $t_f$  measured between 0.3V<sub>DD</sub> and 0.7V<sub>DD</sub>.

Note 10: An input filter on the SDA and SCL input suppresses noise spikes less than 50ns.

Note 11: Guaranteed by design.

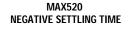

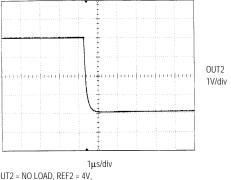

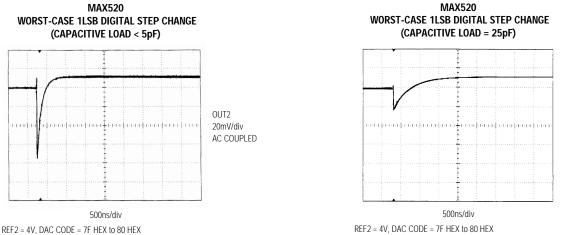

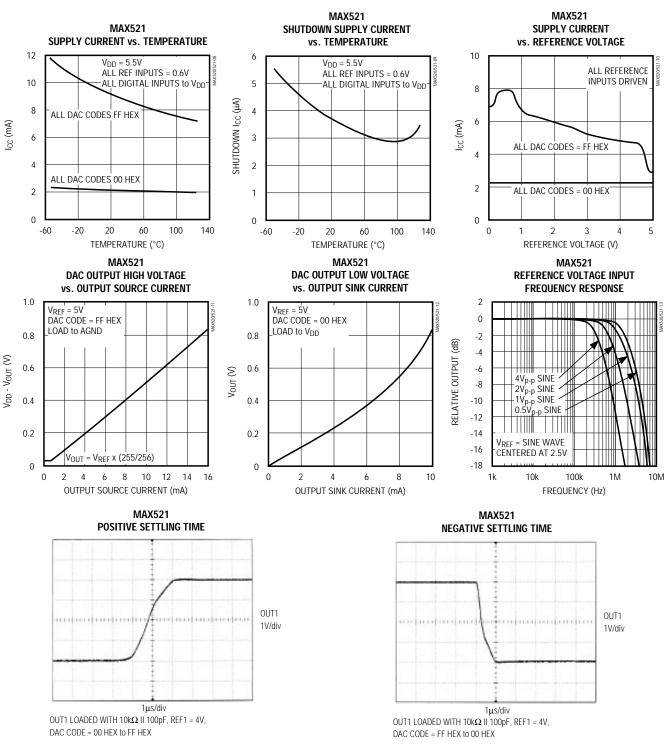

# **\_Typical Operating Characteristics**

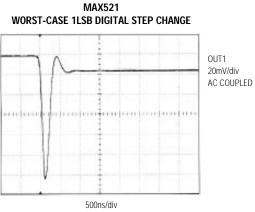

(V<sub>DD</sub> = 5V, DAC outputs unloaded,  $T_A$  = +25°C, unless otherwise noted.)

### \_Typical Operating Characteristics (continued)

( $V_{DD} = 5V$ , DAC outputs unloaded,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

OUT2 = NO LOAD, REF2 = 4V, DAC CODE = 00 HEX to FF HEX

OUT2 = NO LOAD, REF2 = 4V, DAC CODE = FF HEX to 00 HEX

OUT2 20mV/div AC COUPLED

# (V<sub>DD</sub> = 5V, DAC outputs unloaded, T<sub>A</sub> = +25°C, unless otherwise noted.)

**MAX520/MAX52**

### **Typical Operating Characteristics (continued)**

( $V_{DD} = 5V$ , DAC outputs unloaded,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

REF1 = 5V, DAC CODE = 80 HEX to 7F HEX

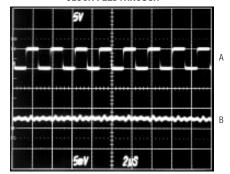

#### CLOCK FEEDTHROUGH

A = SCL, 400kHz, 5V/div B = OUT1, 5mV/div REF1 = 5V, DAC CODE = 7F HEX

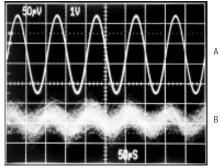

REFERENCE FEEDTHROUGH AT 10kHz

$\label{eq:alpha} \begin{array}{l} A = REF1, 1V/div (4V_{P.P}) \\ B = OUT1, 50 \mu V/div, UNLOADED \\ FILTER PASSBAND = 1 kHz to 100 kHz, DAC CODE = 00 HEX \end{array}$

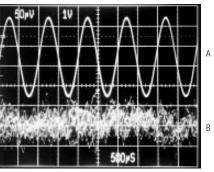

**REFERENCE FEEDTHROUGH AT 1kHz**

$\label{eq:alpha} \begin{array}{l} A=REF1, 1V/div~(4V_{P,P})\\ B=OUT1, 50\mu V/div, UNLOADED\\ \\ FILTER PASSBAND = 100Hz~to~10kHz, DAC~CODE = 00~HEX \end{array}$

**REFERENCE FEEDTHROUGH AT 100kHz**

A = REF1, 1V/div (4V<sub>P-P</sub>) B = OUT1, 50µV/div, UNLOADED FILTER PASSBAND = 10kHz to 1MHz, DAC CODE = 00 HEX

## \_Pin Description

|        | Р            | IN  |              |      |                                                 |

|--------|--------------|-----|--------------|------|-------------------------------------------------|

| М      | AX520        | N   | IAX521       | NAME | FUNCTION                                        |

| DIP/SO | SSOP         | DIP | SO/SSOP      |      |                                                 |

| 1      | 1            | 1   | 1            | OUT1 | DAC1 Voltage Output                             |

| 2      | 2            | 2   | 2            | OUTO | DAC0 Voltage Output                             |

| 3      | 3            | 3   | 3            | REF1 | Reference Voltage Input for DAC1                |

| 4      | 5            | 4   | 4            | REF0 | Reference Voltage Input for DAC0                |

| _      | 4, 7, 14, 17 |     | 7, 9, 16, 20 | N.C. | No Connect—not internally connected             |

| 6      | 8            | 5   | 5            | DGND | Digital Ground                                  |

| 5      | 6            | 6   | 6            | AGND | Analog Ground                                   |

| 7      | 9            | 7   | 8            | SCL  | Serial Clock Input                              |

| 8      | 10           | 8   | 10           | SDA  | Serial Data Input                               |

| _      | _            | 9   | 11           | OUT4 | DAC4 Voltage Output                             |

| _      | _            | 10  | 12           | OUT5 | DAC5 Voltage Output                             |

| _      | _            | 11  | 13           | OUT6 | DAC6 Voltage Output                             |

| _      | _            | 12  | 14           | OUT7 | DAC7 Voltage Output                             |

| 9      | 11           | 13  | 15           | AD0  | Address Input 0; sets IC's slave address        |

| 10     | 12           | 14  | 17           | AD1  | Address Input 1; sets IC's slave address        |

| 11     | 13           |     | _            | AD2  | Address Input 2; sets IC's slave address        |

| 12     | 15           | 15  | 18           | Vdd  | Power Supply, +5V                               |

| _      | —            | 16  | 19           | REF4 | Reference Voltage Input for DACs 4, 5, 6, and 7 |

| 13     | 16           | 17  | 21           | REF3 | Reference Voltage Input for DAC3                |

| 14     | 18           | 18  | 22           | REF2 | Reference Voltage Input for DAC2                |

| 15     | 19           | 19  | 23           | OUT3 | DAC3 Voltage Output                             |

| 16     | 20           | 20  | 24           | OUT2 | DAC2 Voltage Output                             |

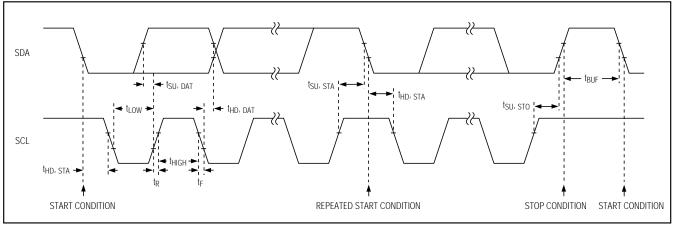

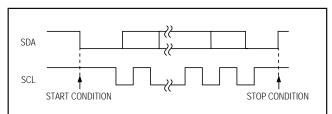

Figure 1. 2-Wire Serial-Interface Timing Diagram

### **Detailed Description**

#### Serial Interface

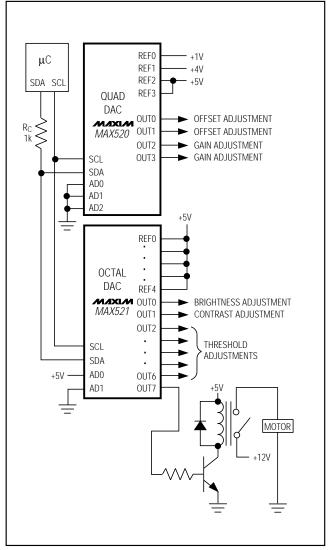

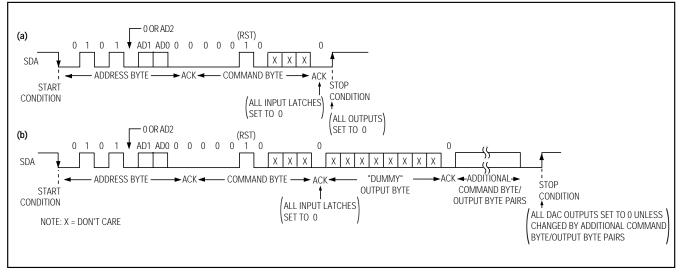

The MAX520/MAX521 use a simple 2-wire serial interface requiring only two I/O lines (2-wire bus) of a standard microprocessor (µP) port. Figure 1 shows the timing diagram for signals on the 2-wire bus. Figure 2 shows the typical application of the MAX520/MAX521. The 2-wire bus can have several devices (in addition to the MAX520/MAX521) attached. The two bus lines (SDA and SCL) must be high when the bus is not in use. When in use, the port bits are toggled to generate the appropriate signals for SDA and SCL. External pull-up resistors are not required on these lines. The MAX520/MAX521 can be used in applications where pull-up resistors are required (such as in I<sup>2</sup>C systems) to maintain compatibility with the existing circuitry.

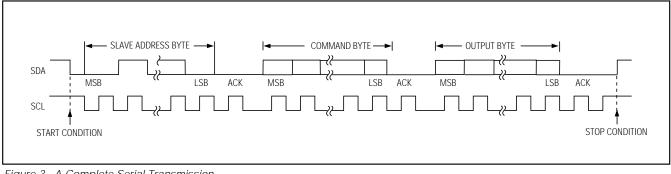

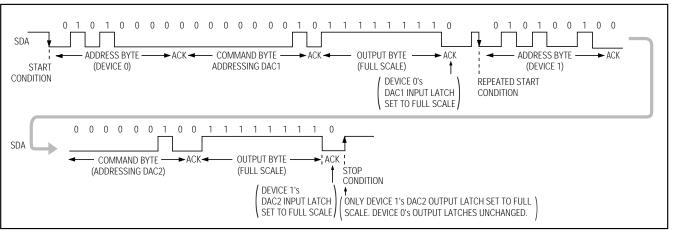

The MAX520/MAX521 are receive-only devices and must be controlled by a bus master device. They operate at SCL rates up to 400kHz. A master device sends information to the devices by transmitting their address over the bus and then transmitting the desired information. Each transmission consists of a START condition, the MAX520/MAX521's programmable slave-address, one or more command-byte/output-byte pairs (or a command byte alone, if it is the last byte in the transmission), and finally, a STOP condition (Figure 3).

The address byte and pairs of command and output bytes are transmitted between the START and STOP conditions. The SDA state is allowed to change only while SCL is low. SDA's state is sampled, and therefore must remain stable while SCL is high. The only exceptions to this are the START and STOP conditions. Data is transmitted in 8-bit bytes. Nine clock cycles are required to transfer the data bits to the MAX520/MAX521. Set SDA low during the 9th clock cycle as the MAX520/MAX521 pull SDA low during this time. R<sub>C</sub> (Figure 2) limits the current that flows during this time if SDA stays high for short periods of time.

///XI//

Figure 2. Typical Application Circuit

Figure 3. A Complete Serial Transmission

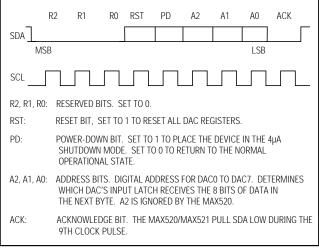

#### START and STOP Conditions

When the bus is not in use, both SCL and SDA must be high. A bus master signals the beginning of a transmission with a START condition by transitioning SDA from high to low while SCL is high (Figure 4). When the master has finished communicating with the slave, it issues a STOP condition by transitioning SDA from low to high while SCL is high. The bus is then free for another transmission.

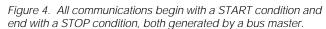

Slave Address

The MAX520/MAX521 each have a 7-bit-long slave address (Figure 5). The first four bits (MSBs) of the slave address have been factory programmed and are always 0101. In addition, the MAX521 has the next bit factory programmed to 0. The logic state of the address input pins (AD0, AD1, and AD2 of the MAX520; AD0 and AD1 of the MAX521) determine the least significant bits of the 7-bit slave address. These input pins may be connected to V<sub>DD</sub> or DGND, or they may be actively driven by TTL or CMOS logic levels. There are four possible slave addresses for the MAX521, and therefore a maximum of four such devices may be on the bus at one time. The MAX520 has eight possible slave addresses. The eighth bit (LSB) in the slave address byte should be low when writing to the MAX520/MAX521.

The MAX520/MAX521 monitor the bus continuously, waiting for a START condition followed by its slave address. When a device recognizes its slave address, it is ready to accept data.

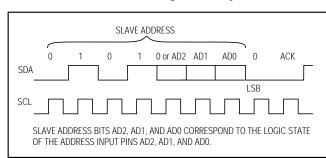

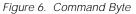

#### Command Byte and Output Byte

A command byte follows the slave address. Figure 6 shows the format for the command byte. A command byte is usually followed by an output byte unless it is the last byte in the transmission. If it is the last byte, all bits except PD and RST are ignored. If an output byte follows the command byte, A0–A2 of the command byte indicate the digital address of the DAC whose input data latch receives the digital output data. The data is transferred to the DAC's output latch during the STOP condition following the transmission. This allows all DACs to be updated and the new outputs to appear simultaneously (Figure 7).

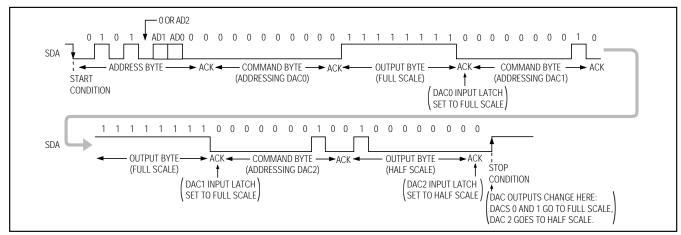

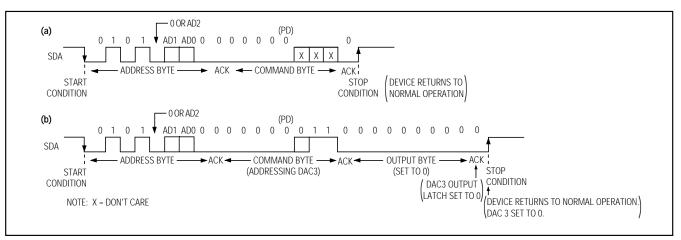

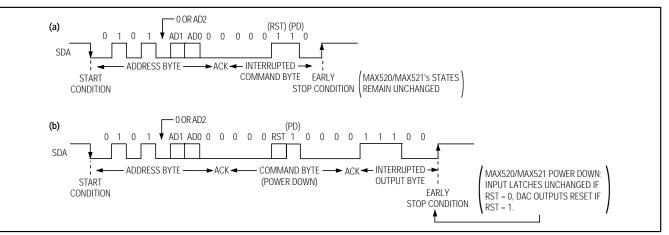

Setting the PD bit high powers down the MAX520/ MAX521 following a STOP condition (Figure 8a). If a command byte with PD set high is followed by an output byte, the addressed DAC's input latch will be updated and the data will be transferred to the DAC's output latch following the STOP condition (Figure 8b). If the transmission's last command byte has PD high, the voltage outputs will not reflect the newly entered data because the DAC will enter power-down mode when

Figure 5. Address Byte

the STOP condition is detected. When in power-down, the MAX521's DAC outputs float, and the MAX520's unbuffered outputs look like a 16k $\Omega$  resistor to AGND. In this mode, the supply current is a maximum of 20µA. A command byte with the PD bit low returns the MAX520/MAX521 to normal operation following a STOP condition, and the voltage outputs reflect the current output-latch contents (Figures 9a and 9b). Because each subsequent command byte overwrites the previous PD bit, only the last command byte of a transmission affects the power-down state.

Figure 7. Setting DAC Outputs

**//**/XI/M

Figure 10. Resetting DAC Outputs

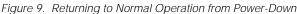

Setting the RST bit high clears all DAC input latches. The DAC outputs remain unchanged until a STOP condition is detected (Figure 10a). If a reset is issued, the following output byte is ignored. Subsequent pairs of command/output bytes overwrite the input latches (Figure 10b).

All changes made during a transmission affect the MAX520/MAX521's outputs only when the transmission ends and a STOP has been recognized. The R0, R1, and R2 bits are reserved bits that must be set to zero.

#### I<sup>2</sup>C Compatibility

The MAX520/MAX521 are fully compatible with existing I<sup>2</sup>C systems. SCL and SDA are high-impedance inputs; SDA has an open drain which pulls the data line low during the 9th clock pulse. Figure 11 shows a typical I<sup>2</sup>C application.

#### Additional START Conditions

It is possible to interrupt a transmission to a MAX520/ MAX521 with a new START (repeated start) condition (perhaps addressing another device), which leaves the input latches with data that has not been transferred to the output latches (Figure 12). Only the currently addressed device will recognize a STOP condition and transfer data to its output latches. If the device is left with data in its input latches, the data can be transferred to the output latches the next time the device is addressed, as long as it receives at least one command byte and a STOP condition.

Figure 11. Typical I<sup>2</sup>C Application Circuit

MAX520/MAX521

Figure 12. Repeated START Conditions

Figure 13. Early STOP Conditions

#### Early Stop Conditions

The addressed device recognizes a STOP condition at any point in a transmission. If the STOP occurs during a command byte, all previous uninterrupted command and output byte pairs are accepted, the interrupted command byte is ignored, and the transmission ends (Figure 13a). If the STOP occurs during an output byte, all previous uninterrupted command and output byte pairs are accepted, the final command byte's PD and RST bits are accepted, the interrupted output byte is ignored, and the transmission ends (Figure 13b).

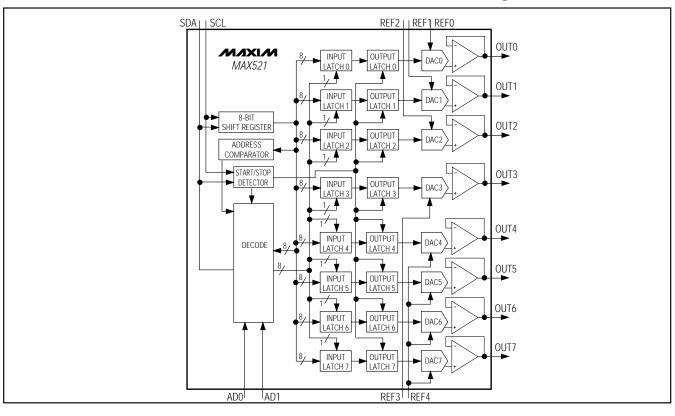

#### Analog Section DAC Operation

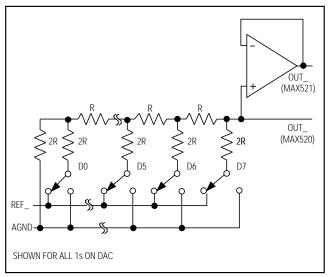

The MAX520 contains four matched voltage-output DACs, and the MAX521 contains eight. The DACs are inverted R-2R ladder networks that convert 8-bit digital

words into equivalent analog output voltages in proportion to the applied reference voltages. For both devices, DAC0–DAC3 each have separate reference inputs, while the MAX521's DAC4–DAC7 all share a common reference input. Figure 14 shows a simplified diagram of one DAC.

#### **Reference Inputs**

The MAX520/MAX521 can be used for multiplying applications. The reference accepts a OV to V<sub>DD</sub> voltage, both DC and AC signals. The voltage at each REF input sets the full-scale output voltage for its respective DAC(s). The reference voltage must be positive. The DAC's input impedance is code dependent, with the lowest value occurring when the input code is 55 hex or 0101 0101, and the maximum value occurring when the input code is 00 hex. Since the REF input resistance

Figure 14. DAC Simplified Circuit Diagram

(R<sub>IN</sub>) is code dependent, it must be driven by a circuit with low output impedance (no more than R<sub>IN</sub> ÷ 2000) to maintain output linearity. The REF input capacitance is also code dependent, with the maximum value occurring at code FF hex (typically 30pF for the MAX520/MAX521's REF0–REF3, and 120pF for the MAX521's REF4). The output voltage for any DAC can be represented by a digitally programmable voltage source as: V<sub>OUT</sub> = (N x V<sub>REF</sub>) / 256, where N is the numerical value of the DAC's binary input code. Table 1 shows the unipolar code.

| DAC CONTENTS | ANALOG OUTPUT                                                              |

|--------------|----------------------------------------------------------------------------|

| 1111111      | + V <sub>REF</sub> ( <u>255</u> )                                          |

| 10000001     | + V <sub>REF</sub> ( <u>129</u> )                                          |

| 1000000      | $+ V_{\text{REF}} \left(\frac{128}{256}\right) = \frac{V_{\text{REF}}}{2}$ |

| 0111111      | + V <sub>REF</sub> ( <u>127</u> )                                          |

| 00000001     | + $V_{\text{REF}} \left( \frac{1}{256} \right)$                            |

| 00000000     | OV                                                                         |

### Table 1. Unipolar Code Table

#### MAX520 Unbuffered DAC Outputs

The unbuffered DAC outputs (OUT0–OUT3) connect directly to the internal 16k $\Omega$  R-2R network. The outputs swing from 0V to VDD.

The MAX520 has no output buffer amplifiers, giving it very low supply current. The output-offset voltage is lower without the output buffer, and the output can also slew and settle faster if capacitive loading is minimized. Resistive loading should be very light for highest accuracy. Any output loading generates some gain error, increasing full-scale error. The R-2R ladder's output resistance is 16k $\Omega$ , so a 1µA output current creates a 16mV error. Linearity is not affected because the ladder output resistance changes with temperature are also very small.

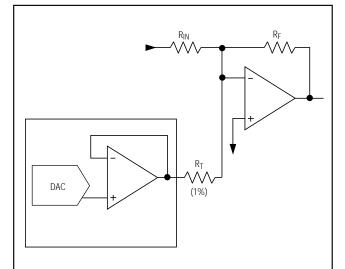

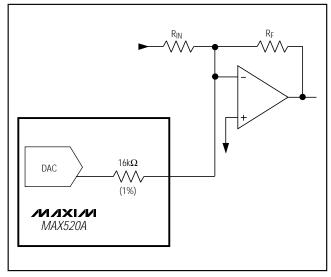

DACs are often used in trimming applications to replace hardware potentiometers. Figure 15a shows a typical application, which requires a buffered output so that a precise current can be injected into the summing node through precision resistor RT. For this application, the MAX520A features a precise  $\pm 1\%$  (T<sub>A</sub> =  $\pm 25^{\circ}$ C,  $\pm 2.5\%$  over temperature) factory-trimmed output resistance. Because the MAX520A's output resistance is precisely trimmed, there is no need for an internal buffer or external precision resistor (Figure 15b). For applications where the output resistance value is not critical, use the MAX520B.

All DACs exhibit output glitches during code transitions. An output filter is sometimes used to reduce these glitches in sensitive applications. The MAX520 simplifies output filtering because its internal resistive ladder network serves as the "R" in an RC filter. Simply connect a small capacitor from the DAC output to ground. See the *Typical Operating Characteristics* for oscilloscope photos of the worst-case 1LSB step change both without and with 25pF of capacitance on the MAX520's output.

#### MAX521 Output Buffer Amplifiers

The MAX521 voltage outputs (OUT0–OUT7) are internally buffered precision unity-gain followers that slew up to 1V/µs. The outputs can swing from 0V to V<sub>DD</sub>. With a 0V to 4V (or 4V to 0V) output transition, the amplifier outputs typically settle to 1/2LSB in 6µs when loaded with 10k $\Omega$  in parallel with 100pF. The buffer amplifiers are stable with any combination of resistive loads ≥2k $\Omega$  and capacitive loads ≤300pF.

Figure 15a. Typical Trimming Circuit

## Applications Information

#### Shutdown Mode

In shutdown mode, the MAX520/MAX521 reference inputs are disconnected from the R-2R ladder inputs, which saves power when the reference is not powered down. In addition, the MAX521's output buffers are disabled, greatly reducing the supply current. The MAX520's operating supply current does not change in shutdown mode. The *Command Byte and Output Byte* section describes how to enter and exit shutdown mode.

#### Power-Supply Bypassing and Ground Management

Bypass V<sub>DD</sub> with a 0.1 $\mu$ F capacitor, located as close to V<sub>DD</sub> and DGND as possible. The analog ground (AGND) and digital ground (DGND) pins should be connected in a "star" configuration to the highest quality ground available, which should be located as close to the MAX521 as possible.

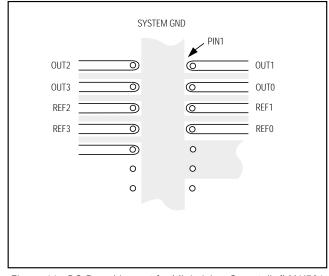

Careful PC board layout minimizes crosstalk among DAC outputs, reference inputs, and digital inputs. Figure 16 shows the suggested PC board layout to minimize crosstalk.

Figure 15b. MAX520A Trimming Circuit

Figure 16. PC Board Layout for Minimizing Crosstalk (MAX521 bottom view, DIP package)

## \_Pin Configurations (continued)

**MAX520/MAX521**

## Ordering Information (continued)

| $\mathbf{PART}^{\dagger}$ | TEMP. RANGE     | PIN-PACKAGE    | TUE<br>(LSB) |

|---------------------------|-----------------|----------------|--------------|

| MAX520ACAP                | 0°C to +70°C    | 20 SSOP        | 1            |

| MAX520BCAP                | 0°C to +70°C    | 20 SSOP        | 1            |

| MAX520AC/D                | 0°C to +70°C    | Dice*          | 1            |

| MAX520BC/D                | 0°C to +70°C    | Dice*          | 1            |

| MAX520AEPE                | -40°C to +85°C  | 16 Plastic DIP | 1            |

| MAX520BEPE                | -40°C to +85°C  | 16 Plastic DIP | 1            |

| MAX520AEWE                | -40°C to +85°C  | 16 Wide SO     | 1            |

| MAX520BEWE                | -40°C to +85°C  | 16 Wide SO     | 1            |

| MAX520AEAP                | -40°C to +85°C  | 20 SSOP        | 1            |

| MAX520BEAP                | -40°C to +85°C  | 20 SSOP        | 1            |

| MAX520AMJE                | -55°C to +125°C | 16 CERDIP      | 1            |

| MAX520BMJE                | -55°C to +125°C | 16 CERDIP      | 1            |

| MAX521ACPP                | 0°C to +70°C    | 20 Plastic DIP | 1            |

| MAX521BCPP                | 0°C to +70°C    | 20 Plastic DIP | 2            |

| MAX521ACWG                | 0°C to +70°C    | 24 Wide SO     | 1            |

| MAX521BCWG                | 0°C to +70°C    | 24 Wide SO     | 2            |

| MAX521ACAG                | 0°C to +70°C    | 24 SSOP        | 1            |

| MAX521BCAG                | 0°C to +70°C    | 24 SSOP        | 2            |

| MAX521BC/D                | 0°C to +70°C    | Dice*          | 2            |

| MAX521AEPP                | -40°C to +85°C  | 20 Plastic DIP | 1            |

| MAX521BEPP                | -40°C to +85°C  | 20 Plastic DIP | 2            |

| MAX521AEWG                | -40°C to +85°C  | 24 Wide SO     | 1            |

| MAX521BEWG                | -40°C to +85°C  | 24 Wide SO     | 2            |

| MAX521AEAG                | -40°C to +85°C  | 24 SSOP        | 1            |

| MAX521BEAG                | -40°C to +85°C  | 24 SSOP        | 2            |

| MAX521BMJP                | -55°C to +125°C | 20 CERDIP      | 2            |

\* Dice are specified at  $T_A = +25^{\circ}C$ , DC parameters only.

<sup>†</sup> MAX520 "A" grade parts include a 1%-accurate, factory-trimmed output resistance.

## \_Chip Topographies

MIXIM

## Package Information

Α

E H

в

0.101mm 0.004in.

| DIM | -    | INC   | HES   | MILLIM | ETERS    |

|-----|------|-------|-------|--------|----------|

| DIN | FINS | MIN   | MAX   | MIN    | MAX      |

| D   | 16   | 0.398 | 0.413 | 10.10  | 10.50    |

| D   | 18   | 0.447 | 0.463 | 11.35  | 11.75    |

| D   | 20   | 0.496 | 0.512 | 12.60  | 13.00    |

| D   | 24   | 0.598 | 0.614 | 15.20  | 15.60    |

| D   | 28   | 0.697 | 0.713 | 17.70  | 18.10    |

|     |      |       |       |        | 21-0042A |

**MAX520/MAX521**

百日日/日日日日

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 (408) 737-7600

Printed USA

© 1996 Maxim Integrated Products

**MAXIM** is a registered trademark of Maxim Integrated Products.

#### ООО "ЛайфЭлектроникс"

ИНН 7805602321 КПП 780501001 Р/С 40702810122510004610 ФАКБ "АБСОЛЮТ БАНК" (ЗАО) в г.Санкт-Петербурге К/С 3010181090000000703 БИК 044030703

Компания «Life Electronics» занимается поставками электронных компонентов импортного и отечественного производства от производителей и со складов крупных дистрибьюторов Европы, Америки и Азии.

С конца 2013 года компания активно расширяет линейку поставок компонентов по направлению коаксиальный кабель, кварцевые генераторы и конденсаторы (керамические, пленочные, электролитические), за счёт заключения дистрибьюторских договоров

Мы предлагаем:

- Конкурентоспособные цены и скидки постоянным клиентам.

- Специальные условия для постоянных клиентов.

- Подбор аналогов.

- Поставку компонентов в любых объемах, удовлетворяющих вашим потребностям.

- Приемлемые сроки поставки, возможна ускоренная поставка.

- Доставку товара в любую точку России и стран СНГ.

- Комплексную поставку.

- Работу по проектам и поставку образцов.

- Формирование склада под заказчика.

- Сертификаты соответствия на поставляемую продукцию (по желанию клиента).

- Тестирование поставляемой продукции.

- Поставку компонентов, требующих военную и космическую приемку.

- Входной контроль качества.

- Наличие сертификата ISO.

В составе нашей компании организован Конструкторский отдел, призванный помогать разработчикам, и инженерам.

Конструкторский отдел помогает осуществить:

- Регистрацию проекта у производителя компонентов.

- Техническую поддержку проекта.

- Защиту от снятия компонента с производства.

- Оценку стоимости проекта по компонентам.

- Изготовление тестовой платы монтаж и пусконаладочные работы.

Тел: +7 (812) 336 43 04 (многоканальный) Email: org@lifeelectronics.ru

#### www.lifeelectronics.ru