# L9654

## Quad squib driver and dual sensor interface ASIC for safety application

## Features

- 4 deployment drivers sized to deliver 1.2 A (min) for 2 ms (min) and 1.75 A (min) for 1ms (min).

- Independently controlled high-side and lowside MOS for diagnosis

- Analog output available for resistance

- Squib short to ground, short to battery and MOS diagnostic available on SPI register

- Capability to deploy the squib with 1.2 A (min.) or 1.75 A under 35 V load-dump condition and the low-side MOS is shorted to ground

- Capability to deploy the squib with 1.2 A (min.) at 6.9 V V<sub>RES</sub> and 1.75 A at 12 V V<sub>RES</sub>.

- Interface with 2 satellite sensors

- Programmable independent current trip points for each satellite channel

Datasheet - production data

- Support Manchester protocol for satellite sensors

- Supports for variable bit rate detection

- Independent current limit and fault timer shutdown protection for each satellite output

- Short to ground and short to battery detection and reporting for each satellite channel

- 5.5 MHz SPI interface

- Satellite message error detection

- Low voltage internal reset

- 2 kV ESD capability on all pins

- Package: 48 lead LQFP

- Technology: ST Proprietary BCD5s (0.57 μm)

## Description

L9654 is intended to deploy up to 4 squibs and to interface up to 2 satellites.

Squib drivers are sized to deploy 1.2 A (min.) for 2 ms (min.) during load dump and 1.75 A (min.) for 1 ms (min.) during load dump.

Diagnostic of squib driver and squib resistance measurement is controlled by micro controllers.

Satellite interfaces support Manchester decoder with variable bit rates.

| Order code | Package | Packing       |

|------------|---------|---------------|

| L9654      | LQFP48  | Tray          |

| L9654TR    | LQFP48  | Tape and reel |

#### Table 1. Device summary

# Contents

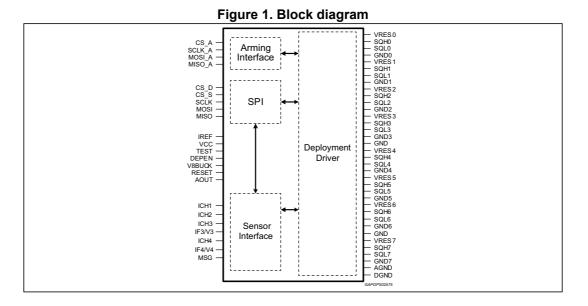

| 1 | Bloc  | k diagram and application schematic      | 7 |

|---|-------|------------------------------------------|---|

|   | 1.1   | Block diagram                            | 7 |

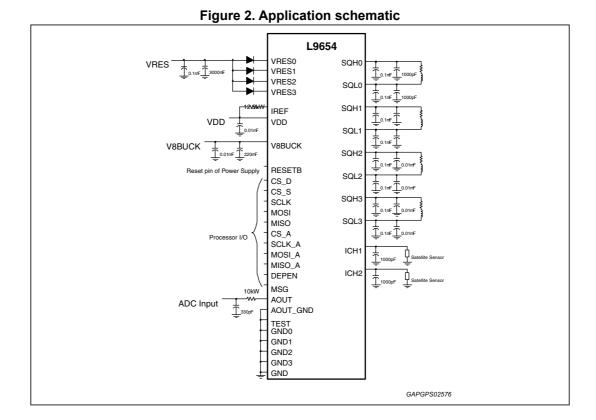

|   | 1.2   | Application schematic                    | 7 |

| 2 | Pin c | description                              | 8 |

|   | 2.1   | Thermal data                             | 9 |

| 3 | Elec  | trical specification                     | D |

|   | 3.1   | Maximum ratings                          | 0 |

|   | 3.2   | Absolute maximum ratings 10              | 0 |

|   | 3.3   | Electrical characteristics 1             | 1 |

|   |       | 3.3.1 DC characteristics                 | 1 |

|   |       | 3.3.2 AC characteristics                 | 4 |

| 4 | Fund  | ctional description                      | 8 |

|   | 4.1   | Overview                                 | 8 |

|   | 4.2   | Power on reset (POR)                     | 8 |

|   | 4.3   | RESETB                                   | 8 |

|   | 4.4   | MSG 18                                   | 8 |

|   | 4.5   | IREF                                     | 9 |

|   | 4.6   | Loss of ground                           | 9 |

|   | 4.7   | Deployment and reset                     | 9 |

|   | 4.8   | Serial peripheral interface (SPI)        | 9 |

|   |       | 4.8.1 Chip select (CS_A, CS_D, CS_S)     | 1 |

|   |       | 4.8.2 Serial clock (SCLK, SCLK_A)        | 1 |

|   |       | 4.8.3 Serial data output (MISO, MISO_A)2 | 1 |

|   |       | 4.8.4 Serial data input (MOSI, MOSI_A)   | 2 |

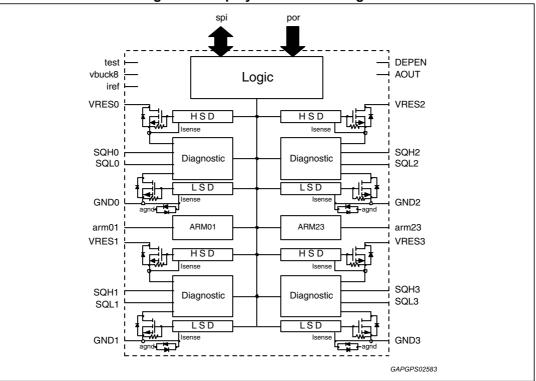

|   | 4.9   | Deployment drivers                       | 2 |

|   |       | 4.9.1 Arming interface                   | 3 |

|   | 4.10  | DEPEN                                    | 5 |

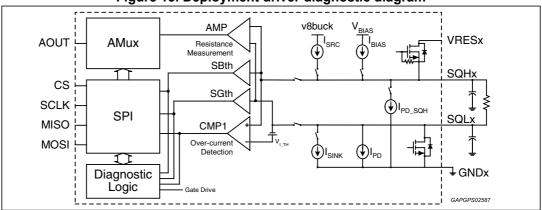

|   |       | 4.10.1 Deployment driver diagnostic      | 6 |

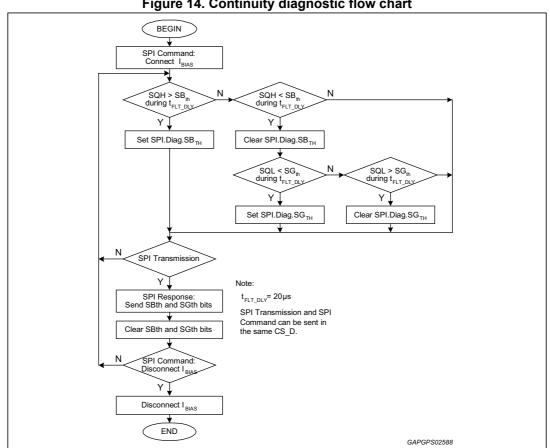

|   |       | 4.10.2 Continuity diagnostic             |   |

|   |       | 4.10.3 Short to battery                  | 7 |

|   |       |                                          |   |

|      | 4.10.4    | Short to ground and open circuit                   | . 27 |

|------|-----------|----------------------------------------------------|------|

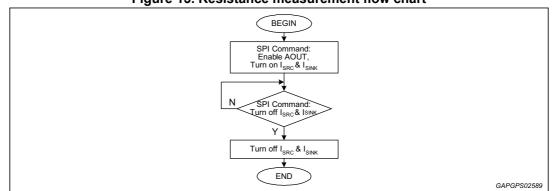

|      | 4.10.5    | Resistance measurement                             | . 27 |

|      | 4.10.6    | MOS diagnostics                                    | . 28 |

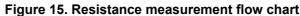

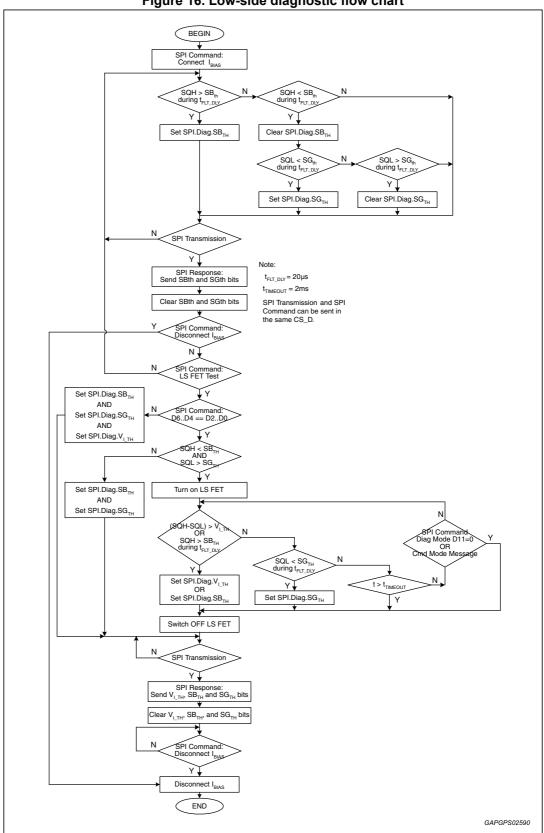

|      | 4.10.7    | Low-side MOS diagnostic                            | . 28 |

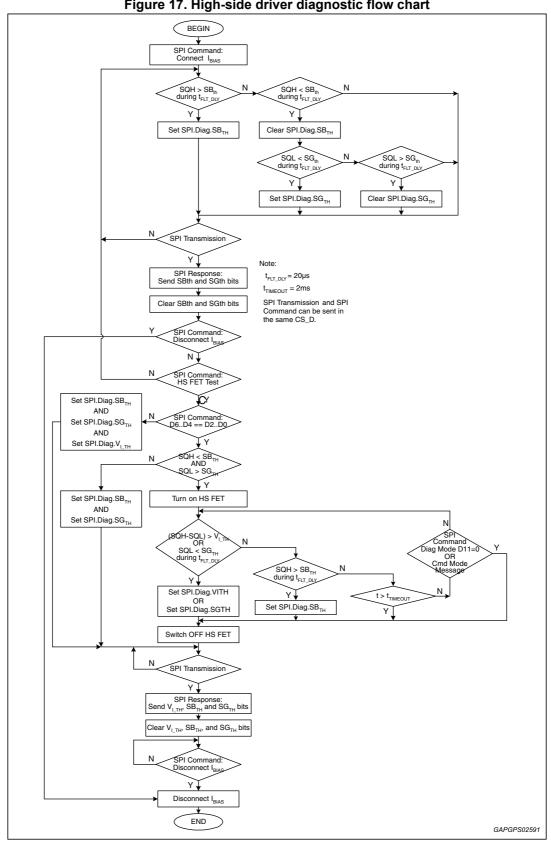

|      | 4.10.8    | High-side MOS diagnostic                           | . 30 |

|      | 4.10.9    | Loss of ground                                     | . 30 |

| 4.11 | Deployn   | nent driver SPI bit definition                     | 32   |

|      | 4.11.1    | Deployment driver MOSI bit definition              | . 32 |

|      | 4.11.2    | Deployment driver register mode                    | . 33 |

|      | 4.11.3    | Deployment driver command mode                     | . 34 |

|      | 4.11.4    | Deployment driver diagnostic mode                  | . 35 |

|      | 4.11.5    | Deployment driver monitor mode                     | . 37 |

|      | 4.11.6    | Deployment driver MISO bit definition              | . 39 |

|      | 4.11.7    | Deployment driver register mode response           | . 39 |

| 4.12 | MISO re   | egister mode response summary                      | 40   |

|      | 4.12.1    | Deployment driver command mode response            | . 41 |

|      | 4.12.2    | Deployment driver diagnostic mode response         | . 42 |

|      | 4.12.3    | Deployment driver status response                  | . 43 |

|      | 4.12.4    | Deployment driver SPI fault response               | . 44 |

| 4.13 | Arming    | SPI bit definition                                 | 44   |

|      | 4.13.1    | Arming MOSI_A bit definition                       | . 44 |

|      | 4.13.2    | ARM[0123]                                          | . 44 |

|      | 4.13.3    | ARM[0123]*                                         | . 44 |

|      | 4.13.4    | Arming MISO_A bit definition                       | . 45 |

|      | 4.13.5    | ARM[0123]                                          | . 45 |

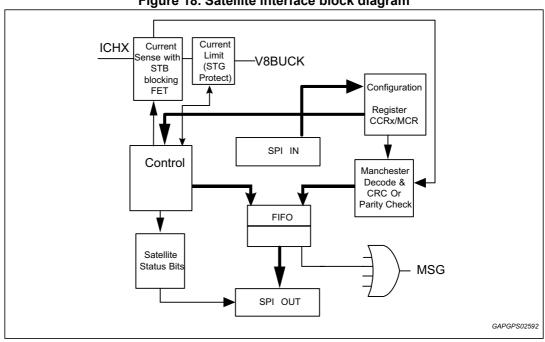

| 4.14 | Satellite | sensor interface                                   | 45   |

|      | 4.14.1    | Current sensor                                     | . 46 |

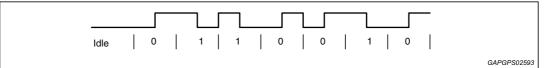

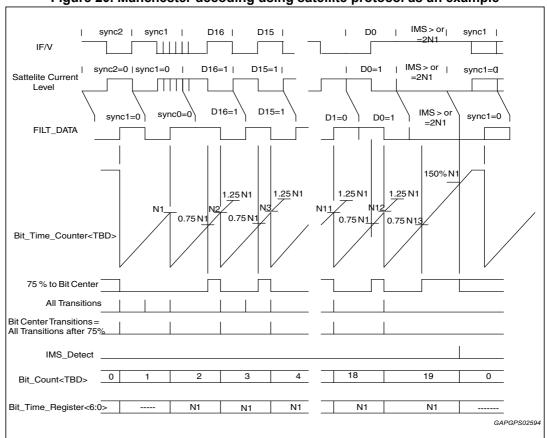

|      | 4.14.2    | Manchester decoding                                | . 46 |

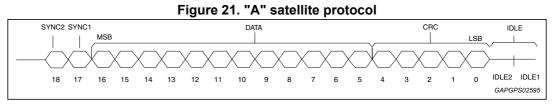

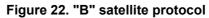

|      | 4.14.3    | Communication protocols                            | . 48 |

|      | 4.14.4    | "A" protocol                                       | . 48 |

|      | 4.14.5    | "B" variable length protocol                       | . 48 |

|      | 4.14.6    | FIFO buffer                                        | . 49 |

|      | 4.14.7    | Satellite continuity check                         | . 49 |

|      | 4.14.8    | Message waiting                                    | . 49 |

|      | 4.14.9    | Satellite serial data input (MOSI)                 | . 49 |

|      | 4.14.10   | Satellite MOSI bits definition                     | . 49 |

|      | 4.14.11   | Satellite module configuration register (CH1 only) | . 50 |

|      |           |                                                    |      |

|   | 4.14.12       Channel configuration registers (CCR1, CCR2, CCR3, CCR4) 51         4.14.13       SPI MISO bits layout for configuration report         55 |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5 | ackage information                                                                                                                                       |

| 6 | Revision history                                                                                                                                         |

# List of tables

| Table 1.               | Device summary                                            | 1    |

|------------------------|-----------------------------------------------------------|------|

| Table 2.               | Pin function                                              | 8    |

| Table 3.               | Thermal data                                              | 9    |

| Table 4.               | Maximum operating conditions                              | . 10 |

| Table 5.               | Absolute maximum ratings                                  | . 10 |

| Table 6.               | DC specification general.                                 |      |

| Table 7.               | DC specification: deployment drivers                      |      |

| Table 8.               | Satellite interface DC specifications                     |      |

| Table 9.               | AC specification: deployment drivers                      |      |

| Table 10.              | AC specifications: satellite                              |      |

| Table 11.              | SPI timing                                                |      |

| Table 12.              | SPI transmission during a deployment                      |      |

| Table 13.              | Deployment driver SPI response                            |      |

| Table 14.              | MOSI bit layout                                           |      |

| Table 15.              | MOSI mode bits definition.                                |      |

| Table 16.              | MOSI register mode message definition.                    |      |

| Table 17.              | Pulse stretch timer table                                 | . 00 |

| Table 18.              | MOSI command mode message definition.                     |      |

| Table 10.              | MOSI diagnostic mode message definition.                  |      |

| Table 19.<br>Table 20. |                                                           |      |

| Table 20.<br>Table 21. | Channel selection decoding                                |      |

|                        | MOSI monitor mode message definition.                     |      |

| Table 22.              | MISO bit layout                                           |      |

| Table 23.              | MISO mode bits definition.                                |      |

| Table 24.              | MISO register mode response definition.                   |      |

| Table 25.              | MISO register mode response summary                       |      |

| Table 26.              | MISO command mode response definition.                    |      |

| Table 27.              | MISO diagnostic mode response definition                  |      |

| Table 28.              | MISO status response definition                           |      |

| Table 29.              | MISO SPI fault response                                   |      |

| Table 30.              | Arming MOSI_A bit definition                              |      |

| Table 31.              | Arming MISO_A bit definition                              |      |

| Table 32.              | Satellite MOSI bits layout                                |      |

| Table 33.              | MOSI satellite interface registers map                    | . 50 |

| Table 34.              | Master configuration register definition (CH1 only)       | . 50 |

| Table 35.              | Channel configuration register definition.                |      |

| Table 36.              | Current ranges supported are given in following table     | . 52 |

| Table 37.              | Satellite/decoder control                                 |      |

| Table 38.              | "B" protocol configuration                                | . 53 |

| Table 39.              | Bit time selection.                                       |      |

| Table 40.              | Mode select                                               |      |

| Table 41.              | SPI mode selects reply for satellite channels             |      |

| Table 42.              | Satellite MISO bits definition.                           |      |

| Table 43.              | SPI MISO bits layout when reporting FIFO data.            |      |

| Table 44.              | MISO Manchester message data definition                   |      |

| Table 45.              | Status bits definition                                    |      |

| Table 46.              | Satellites fault codes definition supporting "A" protocol |      |

| Table 47.              | Satellites fault codes definition supporting "B" protocol | . 56 |

| Table 48.              | Document revision history.                                |      |

|                        | Doounion roution filotory                                 | . 55 |

# List of figures

| Figure 1.  | Block diagram                                              | . 7 |

|------------|------------------------------------------------------------|-----|

| Figure 2.  | Application schematic                                      | . 7 |

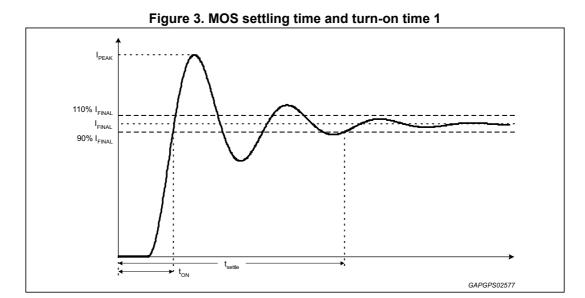

| Figure 3.  | MOS settling time and turn-on time 1                       | 15  |

| Figure 4.  | MOS settling time and turn-on time 2                       | 15  |

| Figure 5.  | SPI timing diagram                                         | 17  |

| Figure 6.  | SPI timing measurement.                                    | 17  |

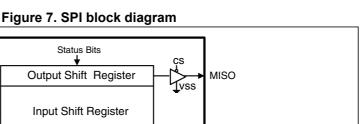

| Figure 7.  | SPI block diagram                                          | 20  |

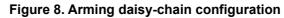

| Figure 8.  | Arming daisy-chain configuration                           | 20  |

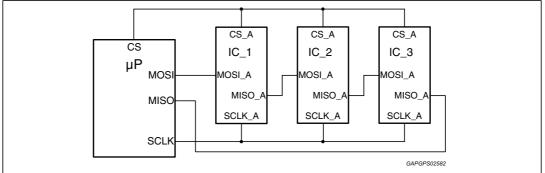

| Figure 9.  | Arming SPI transmission.                                   | 21  |

| Figure 10. | Deployment drivers diagram.                                | 22  |

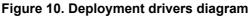

| Figure 11. | Deployment sequence                                        |     |

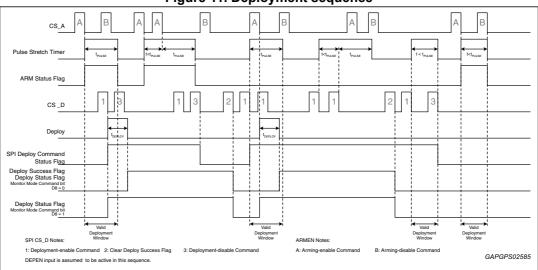

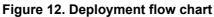

| Figure 12. | Deployment flow chart                                      |     |

| Figure 13. | Deployment driver diagnostic diagram                       | 26  |

| Figure 14. | Continuity diagnostic flow chart                           | 27  |

| Figure 15. | Resistance measurement flow chart                          |     |

| Figure 16. | Low-side diagnostic flow chart                             | 29  |

| Figure 17. | High-side driver diagnostic flow chart                     | 31  |

| Figure 18. | Satellite interface block diagram                          |     |

| Figure 19. | Manchester decoding                                        | 46  |

| Figure 20. | Manchester decoding using satellite protocol as an example |     |

| Figure 21. | "A" satellite protocol                                     |     |

| Figure 22. | "B" satellite protocol                                     |     |

| Figure 23. | LQFP48 mechanical data and package dimensions.             | 57  |

# **1** Block diagram and application schematic

## 1.1 Block diagram

## 1.2 Application schematic

DocID14218 Rev 3

# 2 Pin description

| Pin # | Pin name | Description                                                       | I/O type | Reset state |

|-------|----------|-------------------------------------------------------------------|----------|-------------|

| 1     | MISO_A   | Arming SPI data out                                               | Output   | Hi-Z        |

| 2     | NC       | No connect                                                        | -        | -           |

| 3     | RESETB   | Reset pin                                                         | Input    | Pullup      |

| 4     | GND      | Signal ground (analog & digital)                                  | -        | -           |

| 5     | VDD      | VDD supply voltage                                                | Input    | -           |

| 6     | NC       | No connect                                                        | -        | -           |

| 7     | CS_A     | SPI chip select for arming interface                              | Input    | Pulldown    |

| 8     | CS_S     | SPI chip select for satellite interface                           | Input    | Pulldown    |

| 9     | CS_D     | SPI Chip select for deployment driver                             | Input    | Pulldown    |

| 10    | DEPEN    | Deployment enable                                                 | Input    | Pulldown    |

| 11    | MOSI     | SPI data in                                                       | Input    | Hi-Z        |

| 12,13 | NC       | No connect                                                        | -        | -           |

| 14    | MOSI_A   | Arming SPI data in                                                | Input    | Hi-Z        |

| 15    | SCLK_A   | Arming SPI clock                                                  | Input    | Hi-Z        |

| 16    | SCLK     | SPI clock                                                         | Input    | Hi-Z        |

| 17    | GND2     | Power ground for loop channel 2                                   | -        | -           |

| 18    | SQL2     | Low-side driver output for channel 2                              | Output   | Pulldown    |

| 19    | SQH2     | High-side driver output for channel 2                             | Output   | Hi-Z        |

| 20    | VRES2    | Reserve voltage for loop channel 2                                | Input    | -           |

| 21    | VRES3    | Reserve voltage for loop channel 3                                | Input    | -           |

| 22    | SQH3     | High-side driver output for channel 3                             | Output   | Hi-Z        |

| 23    | SQL3     | Low-side driver output for channel 3                              | Output   | Pulldown    |

| 24    | GND3     | Power ground for loop channel 3                                   | -        | -           |

| 25    | TEST     | Test pin                                                          | Input    | Pulldown    |

| 26    | NC       | No connect                                                        | -        | -           |

| 27    | V8BUCK   | Supply Voltage for Satellite Interface and Resistance Measurement | Input    | -           |

| 28    | NC       | No connect                                                        | -        | -           |

| 29    | ICH2     | Current sense output for channel 2                                | Output   | Hi-Z        |

| 30    | NC       | No connect                                                        | -        | -           |

| 31    | ICH1     | Current sense output for channel 1                                | Output   | Hi-Z        |

| 32    | NC       | No connect                                                        | -        | -           |

| 33    | IREF     | External current reference resistor                               | Output   | -           |

Table 2. Pin function

DocID14218 Rev 3

| Pin # | Pin name | Description                           | I/O type | Reset state |

|-------|----------|---------------------------------------|----------|-------------|

| 34    | AOUT_GND | Ground reference for AOUT             | -        | -           |

| 35    | AOUT     | Analog output for loop diagnostics    | Output   | Hi-Z        |

| 36    | NC       | No connect                            | -        | -           |

| 37    | GND1     | Power ground for loop channel 1       | -        | -           |

| 38    | SQL1     | Low-side driver output for channel 1  | Output   | Pulldown    |

| 39    | SQH1     | High-side driver output for channel 1 | Output   | Hi-Z        |

| 40    | VRES1    | Reserve voltage for loop channel 1    | Input    | -           |

| 41    | VRES0    | Reserve voltage for loop channel 0    | Input    | -           |

| 42    | SQH0     | High-side driver output for channel 0 | Output   | Hi-Z        |

| 43    | SQL0     | Low-side driver output for channel 0  | Output   | Pulldown    |

| 44    | GND0     | Power ground for loop channel 0       | -        | -           |

| 45    | NC       | No connect                            | -        | -           |

| 46    | MSG      | Message waiting                       | Output   | Pulldown    |

| 47    | MISO     | SPI data out                          | Output   | Hi-Z        |

| 48    | NC       | No connect                            | -        | -           |

Table 2. Pin function (continued)

## 2.1 Thermal data

#### Table 3. Thermal data

| Symbol                | Parameter                              | Value. | Unit |

|-----------------------|----------------------------------------|--------|------|

| R <sub>th j-amb</sub> | Thermal resistance junction-to-ambient | 68     | °C/W |

# 3 Electrical specification

## 3.1 Maximum ratings

The device may not operate properly if maximum operating condition is exceeded.

| Symbol             | Parameter                                                                                          | Value                         | Unit |

|--------------------|----------------------------------------------------------------------------------------------------|-------------------------------|------|

| V <sub>DD</sub>    | Supply voltage                                                                                     | 4.9 to 5.1                    | V    |

| V <sub>8BUCK</sub> | V8BUCK voltage                                                                                     | 7 to 8.5                      | V    |

| V <sub>RES</sub>   | VRES voltage (VRES0, VRES1, VRES2, VRES3)                                                          | 35                            | V    |

| VI                 | Discrete input voltage (RESETB, DEPEN, CS_A, CS_D, CS_S, SCLK, SCLK_A, MOSI, MOSI_A, MISO, MISO_A) | 0.3 to (V <sub>DD</sub> +0.3) | V    |

| Тj                 | Junction temperature                                                                               | -40 to 150                    | °C   |

#### Table 4. Maximum operating conditions

## 3.2 Absolute maximum ratings

Maximum ratings are absolute ratings; exceeding any one of these values may cause permanent damage to the integrated circuit.

| Symbol             | Parameter                                                                                          | Value       | Unit |

|--------------------|----------------------------------------------------------------------------------------------------|-------------|------|

| V <sub>DD</sub>    | Supply voltage                                                                                     | -0.3 to 5.5 | V    |

| V <sub>8BUCK</sub> | V8BUCK voltage                                                                                     | 0.3 to 40   | V    |

| V <sub>RES</sub>   | VRES voltage (VRES0, VRES1, VRES2, VRES3)                                                          | 0.3 to 40   | V    |

| SQ <sub>L-H</sub>  | Squib high and low-side drivers (SQH0, SQH1, SQH2, SQH3, SQL0, SQL1, SQL2, SQL3)                   | 0.3 to 40   | V    |

| VI                 | Discrete input voltage (RESETB, DEPEN, CS_A, CS_D, CS_S, SCLK, SCLK_A, MOSI, MOSI_A, MISO, MISO_A) | -0.3 to 5.5 | V    |

| ICHx               | Satellite input voltage (ICH1, ICH2, ICH3, ICH4)                                                   | -3 to 40    | V    |

| -                  | Analog/digital outputs voltage (AOUT, IREF, MSG, IF3V3, IF4V4)                                     | -0.3 to 5.5 | V    |

| Тj                 | Maximum steady-state junction temperature                                                          | 150         | °C   |

| T <sub>amb</sub>   | Ambient temperature                                                                                | -40 to 95   | °C   |

| T <sub>stg</sub>   | Storage temperature                                                                                | -65 to 150  | °C   |

#### Table 5. Absolute maximum ratings

L9654

## 3.3 Electrical characteristics

## 3.3.1 DC characteristics

$V_{RES}$  = 6.5 to 35 V,  $V_{DD}$  = 4.9 to 5.1 V,  $V_{8BUCK}$  = 7.0 V to 8.5 V,  $T_{amb}$  = -40°C to +95°C.

| Symbol                            | Parameter                                     | Test condition                                 | Min.                 | Тур | Max. | Unit |

|-----------------------------------|-----------------------------------------------|------------------------------------------------|----------------------|-----|------|------|

| V <sub>RST</sub> <sup>(1)</sup>   | Internal voltage reset V <sub>DD</sub>        | V <sub>DD</sub> drops until deployment drivers | 4.0                  | -   | 4.5  | v    |

| V <sub>RST_L</sub> <sup>(2)</sup> | internal voltage reset v <sub>DD</sub>        | are disabled                                   | 2.1                  | -   | 3.0  | v    |

|                                   |                                               | Normal operation; I <sub>CH1-2</sub> = 0 A     | 4.5                  | -   | 7.0  |      |

| I                                 | I <sub>DD</sub> Input current V <sub>DD</sub> | Short to $-0.3V$ on SQH; $I_{CH1-2} = 0 A$     | 4.2                  | -   | 7.9  | mA   |

| 'DD                               |                                               | Short to $-0.3V$ on SQL; $I_{CH1-2} = 0A$      | 4.2                  | -   | 7.9  |      |

|                                   |                                               | Deployment; I <sub>CH1-2</sub> = 0A            | 4.2                  | -   | 7.9  |      |

| $R_{IREF_H}$                      | Resistance threshold I <sub>REF</sub>         | -                                              | 20.0                 | -   | 60.0 | kΩ   |

| $R_{IREF_{L}}$                    | Resistance in eshold IREF                     | -                                              | 2.0                  | -   | 9.0  | kΩ   |

| V <sub>IH_RESETB</sub>            |                                               | -                                              | -                    | -   | 2.0  | V    |

| V <sub>IL_RESETB</sub>            | Input voltage threshold<br>RESETB             | -                                              | 0.8                  | -   |      | V    |

| V <sub>HYS</sub>                  |                                               | -                                              | 100                  | -   | 400  | mV   |

| $V_{\text{IH}\_\text{DEPEN}}$     | Input voltage threshold                       | -                                              | -                    | -   | 2.0  | V    |

| $V_{IL\_DEPEN}$                   | DEPEN                                         | -                                              | 0.8                  | -   | -    | V    |

| I <sub>PD</sub>                   | Input pull-down current<br>DEPEN              | $V_{IN} = V_{IL}$ to $V_{DD}$                  | 10                   | -   | 50   | μA   |

| V <sub>IH_TEST</sub>              | Input voltage threshold TEST                  | -                                              | -                    | -   | 3.6  | V    |

| V <sub>IL_TEST</sub>              | Input voltage threshold TEST                  | -                                              | 0.8                  | -   | -    | V    |

| I <sub>TEST</sub>                 | Input pull-down current TEST                  | TEST = 5 V                                     | 1.0                  | -   | 2.5  | mA   |

| I <sub>PU</sub>                   | Input pull-up current RESETB                  | RESETB = V <sub>IH</sub> to GND                | 10                   | -   | 60   | μA   |

| I <sub>V8BUCK</sub>               | Current consumption<br>V8BUCK                 | -                                              | 25                   | -   | 40   | μA   |

| V <sub>IH</sub>                   | Input voltage threshold MOSI,                 | Input Logic = 1                                | -                    | -   | 2.0  | V    |

| V <sub>IL</sub>                   | MOSI_A, ŠCLK, SCLK_A,                         | Input Logic = 0                                | 0.8                  | -   | -    | V    |

| V <sub>HYS</sub>                  | CS_S, CS_D, CS_A                              | -                                              | 100                  | -   | 400  | mV   |

| 1 .                               | Input leakage current MOSI,                   | $V_{IN} = V_{DD}$                              |                      | -   | 1    | μA   |

| I <sub>LKG</sub>                  | MOSI_A, SCLK, SCLK_A                          | V <sub>IN</sub> = 0 to V <sub>IH</sub>         | -1                   | -   | -    | μA   |

| I <sub>PD</sub>                   | Input pulldown current<br>CS_S, CS_D, CS_A    | $V_{IN} = V_{IL}$ to $V_{DD}$                  | 10                   | -   | 50   | μA   |

| V <sub>OH</sub>                   | Output voltage MISO,                          | I <sub>OH</sub> = -800 μA                      | V <sub>DD</sub> -0.8 | -   | -    | V    |

| V <sub>OL</sub>                   | MISO_A, MSG                                   | I <sub>OL</sub> = 1.6 mA                       | -                    | -   | 0.4  | V    |

|                                   | Tri-state current MISO,                       | MISO = VDD                                     | -                    | -   | 1    | μA   |

| I <sub>HI_Z</sub>                 | MISO_A,                                       | MISO = 0 V                                     | -1                   | -   | -    | μA   |

## Table 6. DC specification general

1.  $V_{RST}$  shall have a POR de-glitch timer.

2.  $V_{RST\ L}$  shall have no timer.

$V_{RES}$  = 6.5 to 40 V,  $V_{DD}$  = 4.9 to 5.1 V,  $V_{8BUCK}$  = 7.0 V to 8.5 V,  $T_{amb}$  = -40 °C to +95 °C.

| Symbol                 | Parameter                                    | Test conditions                                                                                      | Min.                    | Тур | Max. | Units           |

|------------------------|----------------------------------------------|------------------------------------------------------------------------------------------------------|-------------------------|-----|------|-----------------|

| V <sub>OH</sub>        | Output voltage AOUT                          | High Saturation Voltage; I <sub>AOUT</sub> = -500µA                                                  | V <sub>DD</sub> -<br>04 | -   | -    | V               |

| V <sub>OL</sub>        |                                              | Low Saturation Voltage; I <sub>AOUT</sub> = +500µA                                                   | -                       | -   | 0.3  | V               |

| I                      | Tri-state current AOUT                       | AOUT = V <sub>DD</sub>                                                                               | -                       | -   | 1    | μA              |

| Ι <sub>Ζ</sub>         |                                              | AOUT = 0V                                                                                            | -1                      | -   | -    | μA              |

| I <sub>LKG</sub>       | Leakage current SQH                          | V8BUCK = V <sub>DD</sub> = 0, V <sub>RES</sub> = 36 V,<br>V <sub>SQH</sub> = 0 V                     | -                       | -   | 50   | μA              |

| I <sub>STG</sub>       |                                              | V8BUCK = 18V; V <sub>DD</sub> = 5V; V <sub>SQH</sub> = -0.3V                                         | -5                      | -   | -    | mA              |

| I <sub>LKG</sub>       | Bias current VRES <sup>(1)</sup>             | V8BUCK = 18 V; V <sub>DD</sub> = 5 V;<br>V <sub>RES</sub> = 36V; SQH shorted to SQL                  | -                       | -   | 10   | μA              |

| I <sub>LKG</sub>       |                                              | V8BUCK = V <sub>DD</sub> = 0, V <sub>SQL</sub> = 18 V                                                | -10                     | -   | 10   | μA              |

| I <sub>STG</sub>       | Leakage current SQL                          | V8BUCK = 18 V; V <sub>DD</sub> = 5V; V <sub>SQL</sub> = -0.3 V                                       | -5                      | -   | -    | mA              |

| I <sub>STB</sub>       |                                              | V8BUCK = 18 V; V <sub>DD</sub> = 5 V;<br>V <sub>SQL</sub> = 18 V                                     | -                       | -   | 5    | mA              |

| I <sub>PD</sub>        | Pull-down current SQL                        | V <sub>SQL</sub> = 1.8 V to V <sub>DD</sub>                                                          | 900                     | -   | 1300 | μA              |

| I <sub>PD_SQH</sub>    | Pull-down current SQH                        | V <sub>SQH</sub> = SBTH to V <sub>RES</sub>                                                          | 900                     | -   | 1300 | μA              |

| V <sub>BIAS</sub>      | Diagnostics bias voltage                     | I <sub>SQH</sub> = -1.5 mA (nominal: 2.0 V)                                                          | 1.80                    | -   | 2.20 | V               |

| I <sub>BIAS</sub>      | Diagnostics bias current                     | V <sub>SQH</sub> = 0V                                                                                | -7                      | -   | -    | I <sub>PD</sub> |

| V <sub>STB</sub>       | Short to battery threshold                   | (Nominal 3.0 V)                                                                                      | 2.70                    | -   | 3.30 | V               |

| V <sub>STG</sub>       | Short to ground threshold                    | (Nominal 1.0 V)                                                                                      | 0.90                    | -   | 1.10 | V               |

| V <sub>I_th</sub>      | MOS test load voltage detection              | -                                                                                                    | 100                     | -   | 300  | mV              |

| I <sub>SRC</sub>       | Resistance<br>measurement current<br>source  | V <sub>DD</sub> = 5.0 V; V8BUCK = 7.0 V to 26.5 V                                                    | 38                      | -   | 42   | mA              |

| I <sub>SINK</sub>      | Resistance measurement current sink          | -                                                                                                    | 45                      | -   | 55   | mA              |

| R <sub>DSon</sub>      | Total high and low-side<br>MOS On resistance | High-side MOS + Low-side<br>MOS V <sub>RES</sub> = 6.9 V; I = 1.2 A @95 °C                           | -                       | -   | 2.0  | Ω               |

| R <sub>DSon</sub>      | High-side MOS on resistance                  | V <sub>RES</sub> = 35 V; I <sub>VRES</sub> = 1.2 A;<br>T <sub>amb</sub> = 95 °C                      | -                       | -   | 0.8  | Ω               |

| R <sub>DSon</sub>      | Low-side MOS on resistance                   | V <sub>RES</sub> = 35 V; I <sub>VRES</sub> = 1.2 A;<br>T <sub>amb</sub> = 95 °C                      | -                       | -   | 1.2  | Ω               |

| I <sub>DEPL_12A</sub>  | Dealeiment                                   | MOSI Register mode bit D10="0"<br>R <sub>LOAD</sub> = 1.7 $\Omega$ ; V <sub>RES</sub> = 6.9 to 35 V  | 1.20                    | -   | 1.47 | А               |

| I <sub>DEPL_175A</sub> | - Deploiment current                         | MOSI Register mode Bit D10="1"<br>R <sub>LOAD</sub> = 1.7 $\Omega$ ; ; V <sub>RES</sub> = 12 to 35 V | 1.75                    | -   | 2.14 | Α               |

| I <sub>LIM</sub>       | Low-side MOS current limit                   | R <sub>LOAD</sub> = 1.75 Ω                                                                           | 2.15                    | -   | 3.5  | Α               |

| R <sub>L RANGE</sub>   | Load resistance range <sup>(2)</sup>         |                                                                                                      | 0                       | -   | 10.0 | Ω               |

| Table 7. DC specification: deployment d |

|-----------------------------------------|

|-----------------------------------------|

1. Not applicable during a diagnostic.

2. Test conditions for load resistance measurements

| $V_{DD} = 4.9$ to 5.1 V | /, V <sub>8BUCK</sub> = 7.0 V to 8.5 | 5 V, T <sub>amb</sub> = -40 °C to +95 °C. |

|-------------------------|--------------------------------------|-------------------------------------------|

| Symbol | Parameter                               | Test conditions                                                                           | Min      | Тур | Мах      | Unit |

|--------|-----------------------------------------|-------------------------------------------------------------------------------------------|----------|-----|----------|------|

|        |                                         | High-side short to -0.3 V                                                                 | (-)75    | -   | (-)150   | mA   |

| I Lim  | Lim Current limit                       | High-side short to Battery                                                                | -        | -   | 5        | mA   |

| '      |                                         | V8BUCK =Vcc=0<br>measured @ V8BUCK                                                        | -        | -   | 5        | mA   |

| Vhda   | Lligh aide veltage dren                 | I=50 mA @105°C; V8BUCK=7.0V                                                               | -        | -   | 1        | V    |

| Vhdp   | High-side voltage drop                  | I=25 mA @105°C; V8BUCK=7.0V                                                               | -        | -   | 0.5      | V    |

|        |                                         | SPI channel configuration                                                                 |          |     |          |      |

|        | tr Low to high transition current       | Bit <2:0≥111                                                                              | 54.00    | -   | 66.00    | mA   |

|        |                                         | Bit <2:0≥110                                                                              | 43.65    | -   | 53.35    | mA   |

|        |                                         | Bit <2:0≥101                                                                              | 35.10    | -   | 42.90    | mA   |

| ltr    |                                         | Bit <2:0≥100                                                                              | 28.80    | -   | 34.20    | mA   |

|        |                                         | Bit <2:0≥011                                                                              | 24.85    | -   | 29.15    | mA   |

|        |                                         | Bit <2:0≥010                                                                              | 20.25    | -   | 24.75    | mA   |

|        |                                         | Bit <2:0≥001                                                                              | 17.10    | -   | 20.90    | mA   |

|        |                                         | Bit <2:0≥000                                                                              | 14.85    | -   | 18.15    | mA   |

| lhyst  | Current threshold hysteresis            | Sink current = Ithr at the output<br>(ICHX).<br>Ihyst=trip point high – trip point<br>low | 0.05*Itr | -   | 0.15*Itr | mA   |

| Vos    | Short to BAT feedback current           | V(ICHX)-V8BUCK<50 mV                                                                      | -        | -   | 25       | mA   |

| Olkg   | Output leakage current ICH <sub>X</sub> | V=18 V @ pin under test                                                                   | -        | -   | 1        | μA   |

### Table 8. Satellite interface DC specifications

## 3.3.2 AC characteristics

$V_{RES}$  = 6.5 to 35 V,  $V_{DD}$  = 4.9 to 5.1 V,  $V_{8BUCK}$  = 7.0 V to 8.5 V,  $T_{amb}$  = -40 °C to +95 °C.

| Symbol                  | Parameter                                           | Test conditions                                                                                  | Min  | Тур | Мах  | Unit               |

|-------------------------|-----------------------------------------------------|--------------------------------------------------------------------------------------------------|------|-----|------|--------------------|

| t <sub>POR</sub>        | POR de-glitch timer                                 | Timer for V <sub>RST</sub>                                                                       | 10   | -   | 25   | μs                 |

| T <sub>GLITCH</sub>     | De-glitch timer                                     | -                                                                                                | 5    | -   | 20   | μs                 |

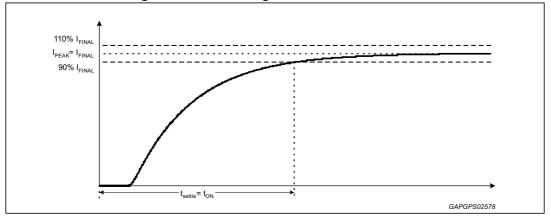

| I <sub>ON</sub>         | Diagnostic current                                  | DEPEN pins asserted ;Measured at 150 $\mu$ s from falling edge CS_D or CS_A; See <i>Figure 4</i> | 0.90 | -   |      | I <sub>FINAL</sub> |

| t <sub>PULSE</sub>      | Pulse stretch timer                                 | See Table 17                                                                                     | 0    | -   | 60   | ms                 |

| t <sub>P_ACC</sub>      | Pulse stretch timer accuracy                        | -                                                                                                | -20  | -   | 20   | %                  |

| t <sub>DEPLOY-2ms</sub> | Deployment time                                     | V <sub>RES</sub> = 6.9 to 35 V <sup>(1)</sup>                                                    | 2    | -   | 2.5  | ms                 |

| t <sub>DEPLOY-1ms</sub> | Deployment time                                     | V <sub>RES</sub> = 12 to 35 V <sup>(1)</sup>                                                     | 1    | -   | 1.25 | ms                 |

| t <sub>FLT_DLY</sub>    | Fault detection filter <sup>(2)</sup>               | -                                                                                                | 10   | -   | 50   | μs                 |

| I <sub>SLEW</sub>       | Rmeas current di/dt                                 | 10 % - 90 % of I <sub>SRC</sub>                                                                  | 2    | -   | 8    | mA/µs              |

| t <sub>R_DLY</sub>      | Rmeas current delay                                 | From the falling edge of CS to 10% of $\rm I_{SRC}$                                              |      | -   | 15   | μs                 |

| t <sub>R_WAIT</sub>     | Rmeas wait time <sup>(2)</sup>                      | Wait time before AOUT voltage is stable for ADC reading                                          | -    | -   | 100  | μs                 |

| t <sub>TIMEOUT</sub>    | MOS diagnostic on-time                              | -                                                                                                | -    | -   | 2.5  | ms                 |

| t <sub>ILIM</sub>       | SQL high current protection timer                   | -                                                                                                | 90   | -   | 110  | μs                 |

| tprop_dly               | LS/HS MOS turn off propagation delay <sup>(2)</sup> | Time is measured from the valid<br>LS/HS MOS fault to the LS/HS turn<br>off                      | -    | -   | 10   | μs                 |

| Table 9. AC | specification: | : deployment driv | /ers |

|-------------|----------------|-------------------|------|

|-------------|----------------|-------------------|------|

1. Application Information; Test is not performed at high voltage.

2. Design Information Only

Figure 4. MOS settling time and turn-on time 2

$V_{DD}$  = 4.9 to 5.1 V;  $V_{8BUCK}$  = 7.0 V to 8.5 V,  $T_{amb}$  = -40 °C to +95 °C

| Symbol                                                                     | Parameter                                                                                                                                         | Test conditions                                                                                                                                                                                         | Min                     | Тур    | Max                      | Unit         |

|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--------|--------------------------|--------------|

| Osc                                                                        | Internal oscillator frequency                                                                                                                     | Tested with 12.5 K 1% Iref resistor                                                                                                                                                                     | 4.45                    | -      | 5.55                     | MHz          |

| Mdf                                                                        | De-glitch filter as a function of protocol speed                                                                                                  | $\begin{array}{l} \mbox{Manchester Protocol Excluding} \\ \mbox{Osc tolerance} \\ \mbox{Bit} < 8:7 \ge 00 \\ \mbox{Bit} < 8:7 \ge 01 \\ \mbox{Bit} < 8:7 \ge 10 \\ \mbox{Bit} < 8:7 \ge 11 \end{array}$ | 11.76<br>%*Bit-<br>Time | -      | 23.53<br>% *Bit-<br>Time | μs           |

|                                                                            |                                                                                                                                                   | Channel configurations                                                                                                                                                                                  |                         |        |                          | _            |

|                                                                            | Minimum frequency operating<br>range<br>Bitr (Incoming messages fall<br>within this operating range is<br>guaranteed to be accepted by<br>the IC) | Bit<8:7≥ 00<br>Test at frq = 52.33 kHz<br>Test at frq =13.32 kHz                                                                                                                                        | 13.32                   | -      | 52.33                    | kHz          |

| Bitr                                                                       |                                                                                                                                                   | Bit<8:7≥01<br>Test at frq =110.74 kHz<br>Test at frq = 26.32 kHz                                                                                                                                        | 26.32                   | -      | 110.74                   | kHz          |

|                                                                            |                                                                                                                                                   | Bit<8:7≥10<br>Test at frq =164.20 kHz<br>Test at frq = 43.50 kHz                                                                                                                                        | 43.50                   | -      | 164.20                   | kHz          |

|                                                                            |                                                                                                                                                   | Bit<8:7≥11<br>Test at frq =250.63 kHz<br>Test at frq = 62.66 kHz                                                                                                                                        | 62.66                   | -      | 250.63                   | kHz          |

|                                                                            |                                                                                                                                                   | Channel configurations                                                                                                                                                                                  |                         |        |                          |              |

|                                                                            | Maximum frequency operating range                                                                                                                 | Bit<8:7≥ 00<br>Test at frq>59.14 kHz<br>Test at frq <11.99 kHz                                                                                                                                          | 11.99                   | -      | 59.14                    | kHz          |

| Bitr                                                                       |                                                                                                                                                   | Bit<8:7≥01<br>Test at frq>128.37 kHz<br>Test at frq <23.57 kHz                                                                                                                                          | 23.57                   | -      | 128.37                   | kHz          |

| outside this operating range is<br>guaranteed to be rejected by<br>the IC) | Bit<8:7≥10<br>Test at frq>194.93 kHz<br>Test at frq <38.71 kHz                                                                                    | 38.71                                                                                                                                                                                                   | -                       | 194.93 | kHz                      |              |

|                                                                            | Bit<8:7≥11<br>Test at frq>309.6 kHz<br>Test at frq <55.37 kHz                                                                                     | 55.37                                                                                                                                                                                                   | -                       | 309.6  | kHz                      |              |

| Idle                                                                       | Idle time                                                                                                                                         | Manchester                                                                                                                                                                                              | 2                       | -      |                          | Bit<br>Times |

| Flt                                                                        | Output fault timer                                                                                                                                | I_sensor>I_lim                                                                                                                                                                                          | 300                     | -      | 500                      | μs           |

| Table 10. AC | specifications: | satellite |

|--------------|-----------------|-----------|

|--------------|-----------------|-----------|

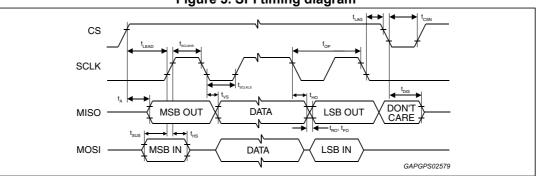

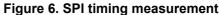

$V_{RES}$  = 6.5 to 35 V,  $V_{DD}$  = 4.9 to 5.1V.  $V_{8BUCK}$  = 7.0 V to 8.5 V,  $T_{amb}$  = -40 °C to +95 °C All SPI timing is performed with a 200 pF load on MISO unless otherwise noted.

| Symbol              | Parameter                                                                                                                                                                                                                                                               | Min                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Тур                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Мах                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| fop                 | Transfer frequency                                                                                                                                                                                                                                                      | dc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5.50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| t <sub>SCK</sub>    | SCLK, SCLK_A Period                                                                                                                                                                                                                                                     | 181                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| t <sub>LEAD</sub>   | Enable Lead Time                                                                                                                                                                                                                                                        | 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| t <sub>LAG</sub>    | Enable Lag Time                                                                                                                                                                                                                                                         | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| t <sub>SCLKHS</sub> | SCLK, SCLK_A High Time                                                                                                                                                                                                                                                  | 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| t <sub>SCLKLS</sub> | SCLK, SCLK_A Low Time                                                                                                                                                                                                                                                   | 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| t <sub>SUS</sub>    | MOSI, MOSI_A Input Setup Time                                                                                                                                                                                                                                           | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| t <sub>HS</sub>     | MOSI, MOSI_A Input Hold Time                                                                                                                                                                                                                                            | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| t <sub>A</sub>      | MISO, MISO_A Access Time                                                                                                                                                                                                                                                | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                       |