# **GS2970A**

## 3Gb/s, HD, SD SDI Receiver Complete with SMPTE Audio and Video Processing

### **Key Features**

- Operation at 2.970Gb/s, 2.970/1.001Gb/s, 1.485Gb/s, 1.485/1.001Gb/s and 270Mb/s

- Supports SMPTE ST 425 (Level A and Level B), SMPTE ST 424, SMPTE ST 292, SMPTE ST 259-C and DVB-ASI

- Integrated Reclocker

- Integrated low phase noise VCO

- Serial digital reclocked, or non-reclocked loop-through output

- Integrated audio de-embedder for 8 channels of 48kHz audio

- Integrated audio clock generator

- Ancillary data extraction

- Optional conversion from SMPTE ST 425 Level B to Level A for 1080p 50/59.94/60 4:2:2 10-bit inputs

- Parallel data bus selectable as either 20-bit or 10-bit

- Comprehensive error detection and correction features

- Output H, V, F or CEA 861 timing signals

- 1.2V digital core power supply, 1.2V and 3.3V analog power supplies, and selectable 1.8V or 3.3V I/O power supply

- GSPI host interface

- -20°C to +85°C operating temperature range

- Low power operation (typically 350mW)

- Small 11mm x 11mm 100-ball BGA package

- Pb-free and RoHS compliant

## **Applications**

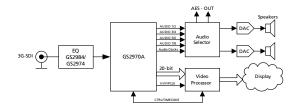

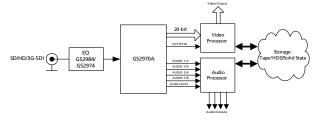

Application: Single Link (3G-SDI) to Dual Link (HD-SDI) Converter

Application: 1080p50/60 Monitor

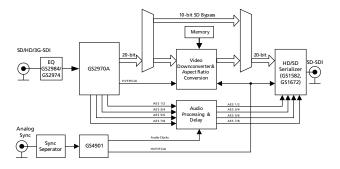

Application: Multi-format Downconverter

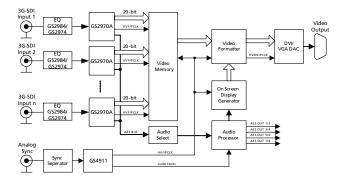

Application: Multi-input Video Monitoring System

Application: Multi-format Audio De-embedder Module

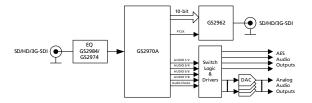

Application: Multi-format Digital VTR/Video Server

### **Description**

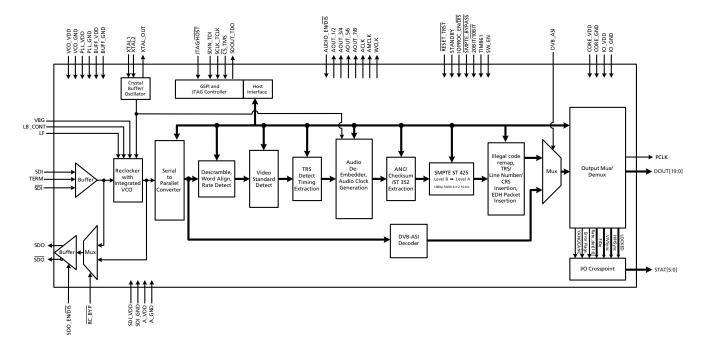

The GS2970A is a multi-rate SDI Receiver which includes complete SMPTE processing, as per SMPTE ST 425, SMPTE ST 292 and SMPTE ST 259-C. The SMPTE processing features can be bypassed to support signals with other coding schemes.

The device features an Integrated Reclocker with an internal VCO and a wide Input Jitter Tolerance (IJT) of 0.7UI.

A serial digital loop-through output is provided, which can be configured to output either reclocked or non-reclocked serial digital data. The serial digital output can be connected to an external cable driver.

The device operates in one of four basic modes: SMPTE mode, DVB-ASI mode, Data-Through mode or Standby mode.

In SMPTE mode (the default operating mode), the GS2970A performs full SMPTE processing, and features a number of data integrity checks and measurement capabilities.

The device also supports ancillary data extraction, and can provide entire ancillary data packets through host-accessible registers. It also provides a variety of other packet detection and error handling features. All of these processing features are optional, and may be individually enabled or disabled through register programming.

Both SMPTE ST 425 Level A and Level B inputs are supported with optional conversion from Level B to Level A for 1080p 50/59.94/60 4:2:2 10-bit inputs.

In DVB-ASI mode, sync word detection, alignment and 8b/10b decoding is applied to the received data stream.

In Data-Through mode all forms of SMPTE and DVB-ASI processing are disabled, and the device can be used as a simple serial to parallel converter.

The device can also operate in a lower power Standby mode. In this mode, no signal processing is carried out and the parallel output is held static.

Parallel data outputs are provided in 20-bit or 10-bit format for 3Gb/s, HD and SD video rates, with a variety of mapping options. As such, this parallel bus can interface directly with video processor ICs, and output data can be multiplexed onto 10 bits for a low pin count interface.

Up to eight channels (two audio groups) of serial digital audio may be extracted from the video data stream, in accordance with SMPTE ST 272-C and SMPTE ST 299.

The output audio formats supported by the device include AES/EBU and I<sup>2</sup>S, and two other industry standard serial digital formats. A variety of audio processing features are provided to ease implementation. Audio clocks are internally generated and provided by the device.

# **Functional Block Diagram**

**GS2970A Functional Block Diagram**

## **Revision History**

| Version | ECO    | PCN | Date           | Changes and/or Modifications                                                                                                               |

|---------|--------|-----|----------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| 3       | 014961 | -   | August 2013    | Clarified IOPROC_EN/DIS register configuration throughout Section 4. Added note to Section 4.20. Updated SMPTE format throughout document. |

| 2       | 158084 | -   | September 2012 | Changes throughout the document.                                                                                                           |

| 1       | 154875 | _   | September 2010 | Removed three duplicated pages from Table 4.21.1 Video Core Registers.                                                                     |

| 0       | 154391 | _   | July 2010      | New Document.                                                                                                                              |

# **Contents**

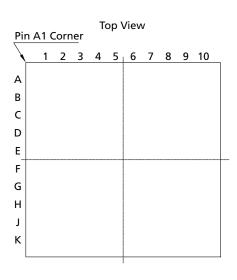

| 1. Pin Out                                                            | 9  |

|-----------------------------------------------------------------------|----|

| 1.1 Pin Assignment                                                    | 9  |

| 1.2 Pin Descriptions                                                  | 9  |

| 2. Electrical Characteristics                                         | 17 |

| 2.1 Absolute Maximum Ratings                                          | 17 |

| 2.2 Recommended Operating Conditions                                  | 17 |

| 2.3 DC Electrical Characteristics                                     | 18 |

| 2.4 AC Electrical Characteristics                                     | 20 |

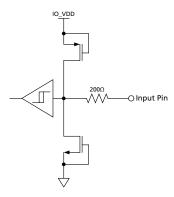

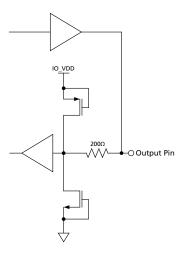

| 3. Input/Output Circuits                                              | 26 |

| 4. Detailed Description                                               | 29 |

| 4.1 Functional Overview                                               | 29 |

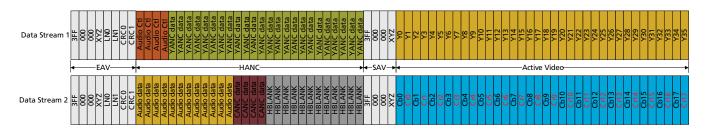

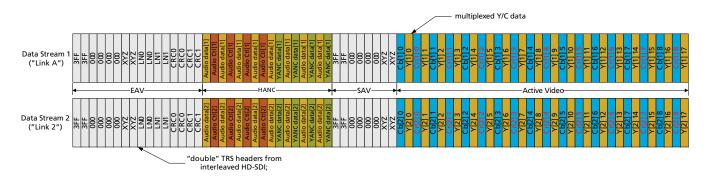

| 4.2 SMPTE ST 425 Mapping - 3G Level A and Level B Formats             | 29 |

| 4.2.1 Level A Mapping                                                 | 29 |

| 4.2.2 Level B Mapping                                                 | 30 |

| 4.3 Serial Digital Input                                              | 30 |

| 4.4 Serial Digital Loop-Through Output                                | 30 |

| 4.5 Serial Digital Reclocker                                          | 31 |

| 4.5.1 PLL Loop Bandwidth                                              | 31 |

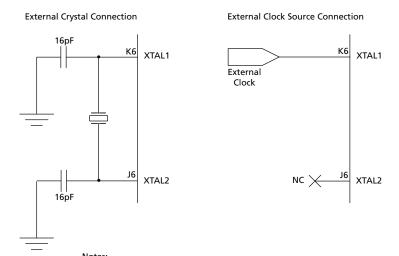

| 4.6 External Crystal/Reference Clock                                  | 32 |

| 4.7 Lock Detect                                                       | 34 |

| 4.7.1 Asynchronous Lock                                               | 34 |

| 4.7.2 Signal Interruption                                             | 35 |

| 4.8 SMPTE Functionality                                               | 35 |

| 4.8.1 Descrambling and Word Alignment                                 | 35 |

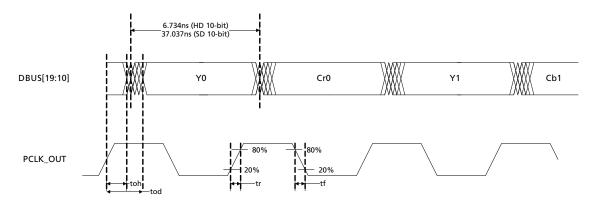

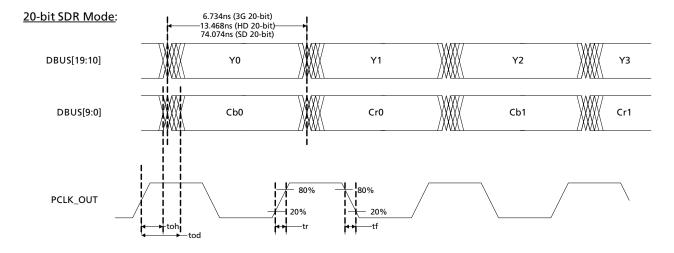

| 4.9 Parallel Data Outputs                                             | 36 |

| 4.9.1 Parallel Data Bus Buffers                                       | 36 |

| 4.9.2 Parallel Output in SMPTE Mode                                   | 39 |

| 4.9.3 Parallel Output in DVB-ASI Mode                                 | 39 |

| 4.9.4 Parallel Output in Data-Through Mode                            | 39 |

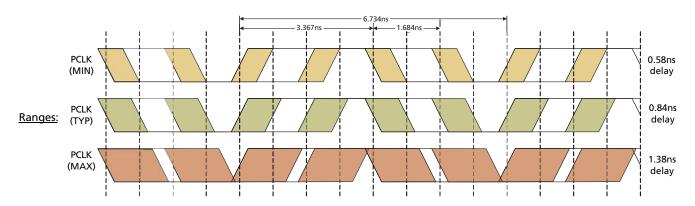

| 4.9.5 Parallel Output Clock (PCLK)                                    | 39 |

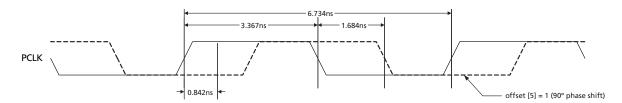

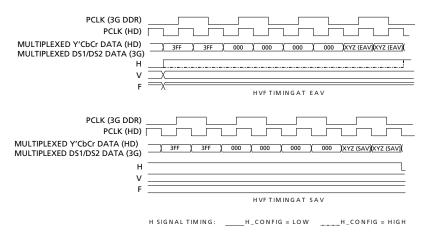

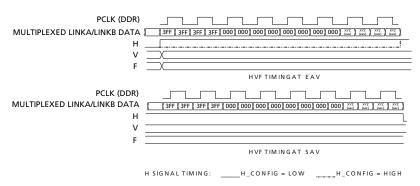

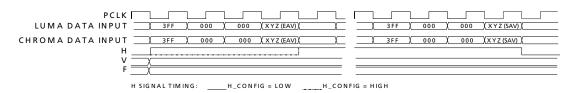

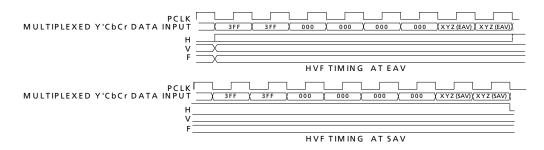

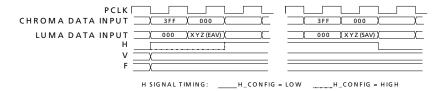

| 4.9.6 DDR Parallel Clock Timing                                       | 40 |

| 4.10 Timing Signal Generator                                          | 42 |

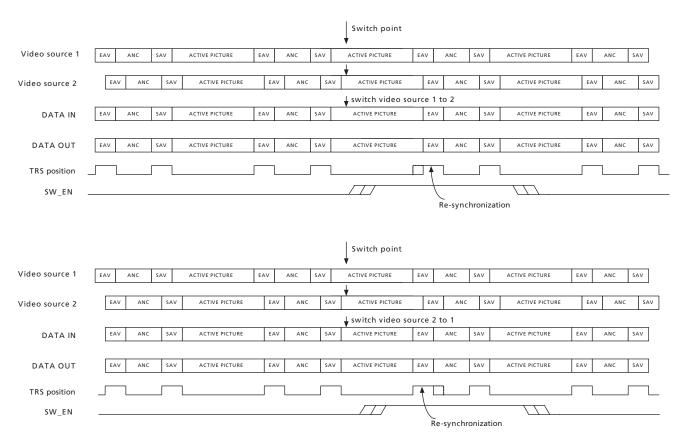

| 4.10.1 Manual Switch Line Lock Handling                               | 43 |

| 4.10.2 Automatic Switch Line Lock Handling                            | 44 |

| 4.10.3 Switch Line Lock Handling During Level B to Level A Conversion | 44 |

| 4.11 Programmable Multi-function Outputs                              | 46 |

| 4.12 H:V:F Timing Signal Generation                                   | 47 |

| 4.12.1 CEA-861 Timing Generation                                      | 49 |

| 4.13 Automatic Video Standards Detection                              | 56 |

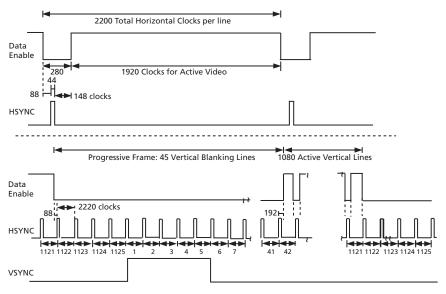

| 4.13.1 2K Support                                                     | 60 |

| 4.14 Data Format Detection & Indication                               | 60 |

| 4.15 EDH Detection                                                    | 62 |

| 4.15.1 EDH Packet Detection                                           | 62 |

| 4.15.2 EDH Flag Detection                             | 62  |

|-------------------------------------------------------|-----|

| 4.16 Video Signal Error Detection & Indication        | 63  |

| 4.16.1 TRS Error Detection                            | 64  |

| 4.16.2 Line Based CRC Error Detection                 | 65  |

| 4.16.3 EDH CRC Error Detection                        | 65  |

| 4.16.4 HD & 3G Line Number Error Detection            | 65  |

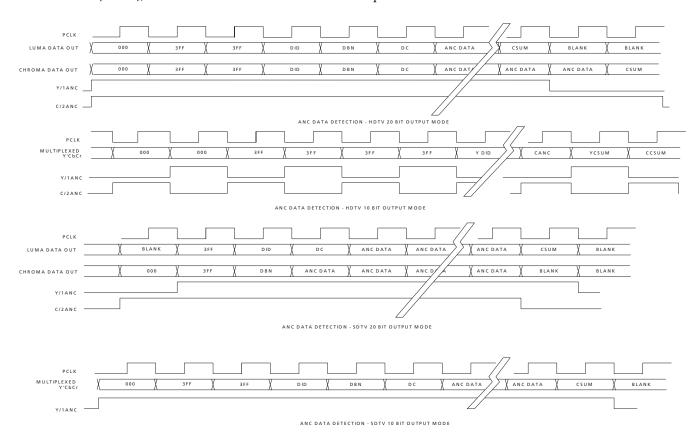

| 4.17 Ancillary Data Detection & Indication            | 66  |

| 4.17.1 Programmable Ancillary Data Detection          | 67  |

| 4.17.2 SMPTE ST 352 Payload Identifier                | 68  |

| 4.17.3 Ancillary Data Checksum Error                  | 69  |

| 4.17.4 Video Standard Error                           | 70  |

| 4.18 Signal Processing                                | 71  |

| 4.18.1 TRS Correction & Insertion                     |     |

| 4.18.2 Line Based CRC Correction & Insertion          | 72  |

| 4.18.3 Line Number Error Correction & Insertion       | 72  |

| 4.18.4 ANC Data Checksum Error Correction & Insertion |     |

| 4.18.5 EDH CRC Correction & Insertion                 |     |

| 4.18.6 Illegal Word Re-mapping                        |     |

| 4.18.7 TRS and Ancillary Data Preamble Remapping      |     |

| 4.18.8 Ancillary Data Extraction                      |     |

| 4.18.9 Level B to Level A Conversion                  | 79  |

| 4.19 Audio De-embedder                                | 80  |

| 4.19.1 Serial Audio Data I/O Signals                  | 80  |

| 4.19.2 Serial Audio Data Format Support               | 82  |

| 4.19.3 Audio Processing                               | 86  |

| 4.19.4 Error Reporting                                | 93  |

| 4.20 GSPI - HOST Interface                            | 94  |

| 4.20.1 Command Word Description                       | 95  |

| 4.20.2 Data Read or Write Access                      | 95  |

| 4.20.3 GSPI Timing                                    | 96  |

| 4.21 Host Interface Register Maps                     | 98  |

| 4.21.1 Video Core Registers                           | 98  |

| 4.21.2 SD Audio Core Registers                        | 112 |

| 4.21.3 HD and 3G Audio Core Registers                 | 126 |

| 4.22 JTAG Test Operation                              | 141 |

| 4.23 Device Power-up                                  | 143 |

| 4.24 Device Reset                                     | 143 |

| 4.25 Standby Mode                                     | 143 |

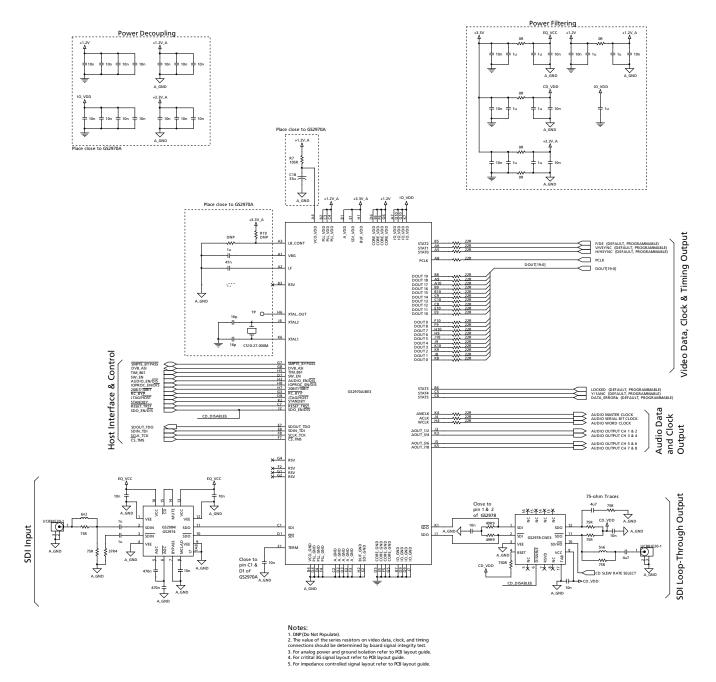

| 5. Application Reference Design                       | 144 |

| 5.1 Typical Application Circuit                       | 144 |

| 6. References & Relevant Standards                    | 145 |

| 7. Package & Ordering Information                     | 146 |

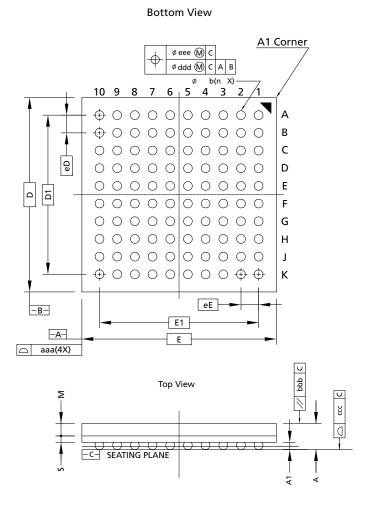

| 7.1 Package Dimensions                                | 146 |

| 7.2 Packaging Data                                    | 147 |

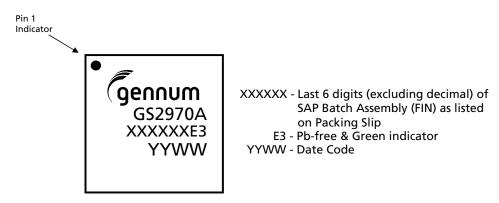

| 7.3 Marking Diagram                                   | 147 |

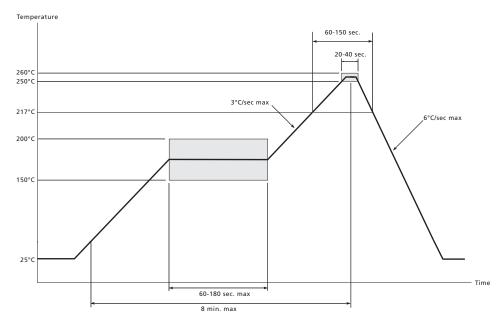

| 7.4 Solder Reflow Profiles                            | 148 |

| 7.5 Ordering Information                              | 148 |

# **List of Figures**

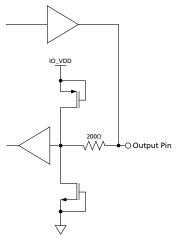

| Figure 3-1: Digital Input Pin with Schmitt Trigger                                  | 26 |

|-------------------------------------------------------------------------------------|----|

| Figure 3-2: Bidirectional Digital Input/Output Pin                                  | 26 |

| Figure 3-3: Bidirectional Digital Input/Output Pin with programmable drive strength | 27 |

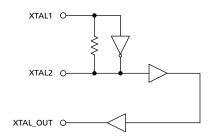

| Figure 3-4: XTAL1/XTAL2/XTAL-OUT                                                    | 27 |

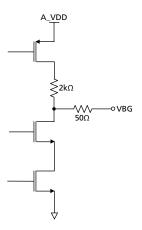

| Figure 3-5: VBG                                                                     | 27 |

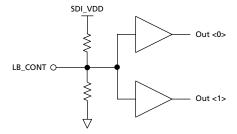

| Figure 3-6: LB_CONT                                                                 | 28 |

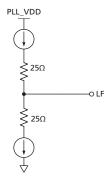

| Figure 3-7: Loop Filter                                                             | 28 |

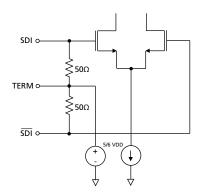

| Figure 3-8: SDI/SDI and TERM                                                        | 28 |

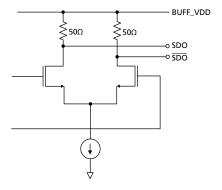

| Figure 3-9: SDO/SDO                                                                 | 28 |

| Figure 4-1: Level A Mapping                                                         |    |

| Figure 4-2: Level B Mapping                                                         | 30 |

| Figure 4-3: 27MHz Clock Sources                                                     | 33 |

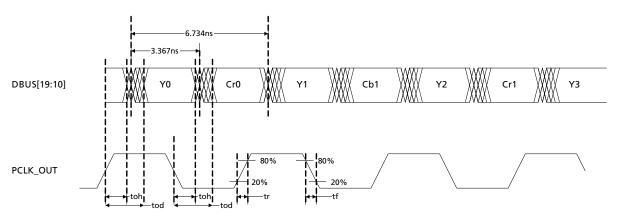

| Figure 4-4: PCLK to Data and Control Signal Output Timing - SDR Mode 1              | 36 |

| Figure 4-5: PCLK to Data and Control Signal Output Timing - SDR Mode 2              |    |

| Figure 4-6: PCLK to Data and Control Signal Output Timing - DDR Mode                |    |

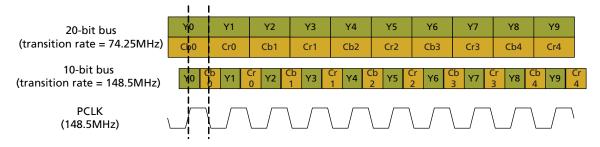

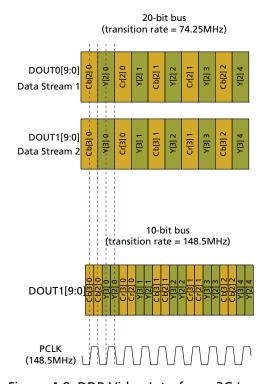

| Figure 4-7: DDR Video Interface - 3G Level A                                        |    |

| Figure 4-8: DDR Video Interface - 3G Level B                                        |    |

| Figure 4-9: Delay Adjustment Ranges                                                 |    |

| Figure 4-10: Switch Line Locking on a Non-Standard Switch Line                      |    |

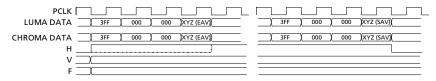

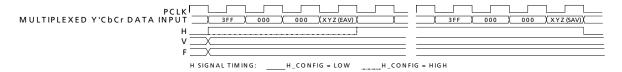

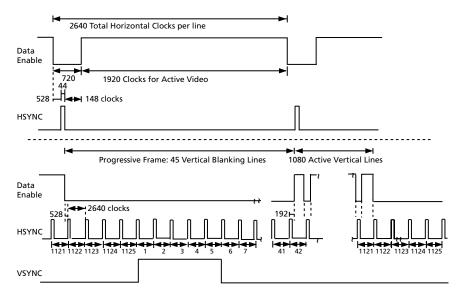

| Figure 4-11: H:V:F Output Timing - 3G Level A and HDTV 20-bit Mode                  |    |

| Figure 4-12: H:V:F Output Timing - 3G Level A and HDTV 10-bit Mode                  |    |

| 3Ğ Level B 20-bit Mode, each 10-bit stream                                          |    |

| Figure 4-13: H:V:F Output Timing - 3G Level B 10-bit Mode                           |    |

| Figure 4-14: H:V:F Output Timing - HD 20-bit Output Mode                            |    |

| Figure 4-15: H:V:F Output Timing - HD 10-bit Output Mode                            |    |

| Figure 4-16: H:V:F Output Timing - SD 20-bit Output Mode                            |    |

| Figure 4-17: H:V:F Output Timing - SD 10-bit Output Mode                            |    |

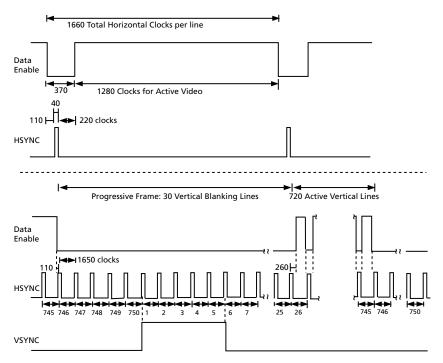

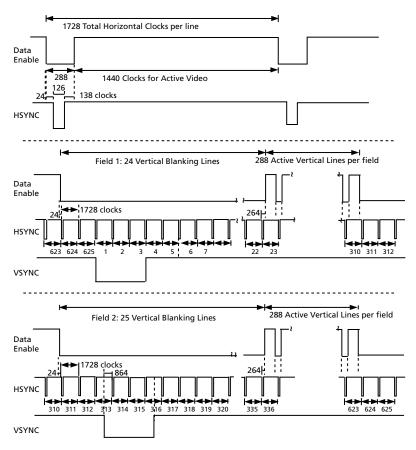

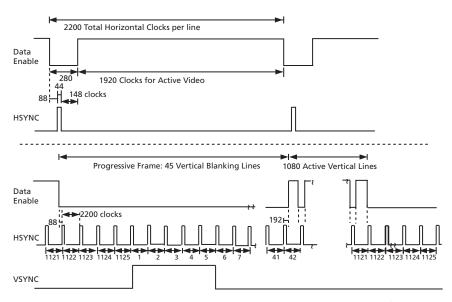

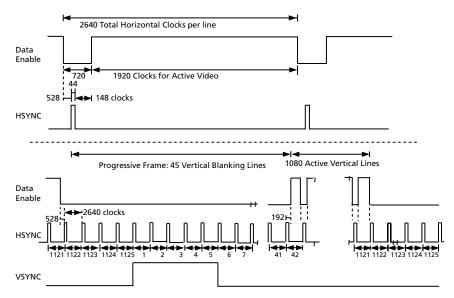

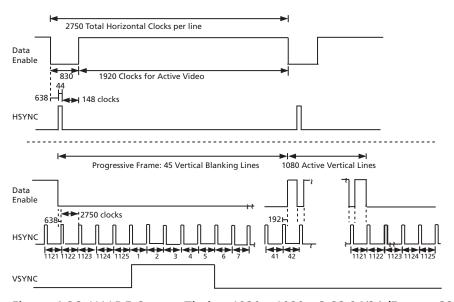

| Figure 4-18: H:V:DE Output Timing 1280 x 720p @ 59.94/60 (Format 4)4                |    |

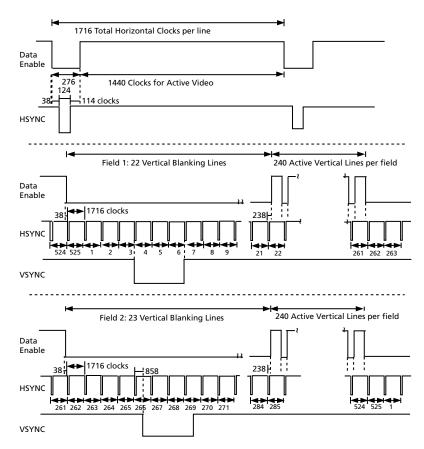

| Figure 4-19: H:V:DE Output Timing 1920 x 1080i @ 59.94/60 (Format 5)                |    |

| Figure 4-20: H:V:DE Output Timing 720 (1440) x 480i @ 59.94/60 (Format 6&7)         |    |

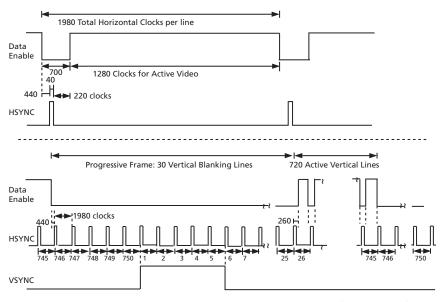

| Figure 4-21: H:V:DE Output Timing 1280 x 720p @ 50 (Format 19)                      |    |

| Figure 4-22: H:V:DE Output Timing 1920 x 1080i @ 50 (Format 20)                     |    |

| Figure 4-23: H:V:DE Output Timing 720 (1440) x 576 @ 50 (Format 21 & 22)            |    |

| Figure 4-24: H:V:DE Output Timing 1920 x 1080p @ 59.94/60 (Format 16)               |    |

| Figure 4-25: H:V:DE Output Timing 1920 x 1080p @ 50 (Format 31)                     |    |

| Figure 4-26: H:V:DE Output Timing 1920 x 1080p @ 23.94/24 (Format 32)               |    |

| Figure 4-27: H:V:DE Output Timing 1920 x 1080p @ 25 (Format 33)                     |    |

| Figure 4-28: H:V:DE Output Timing 1920 x 1080p @ 29.97/30 (Format 34)               |    |

| Figure 4-29: 2K Feature Enhancement                                                 |    |

| Figure 4-30: Y/1ANC and C/2ANC Signal Timing                                        |    |

| Figure 4-31: Ancillary Data Extraction - Step A                                     |    |

| Figure 4-32: Ancillary Data Extraction - Step B                                     |    |

| Figure 4-33: Ancillary Data Extraction - Step C                                     |    |

| Figure 4-34: Ancillary Data Extraction - Step D                                     |    |

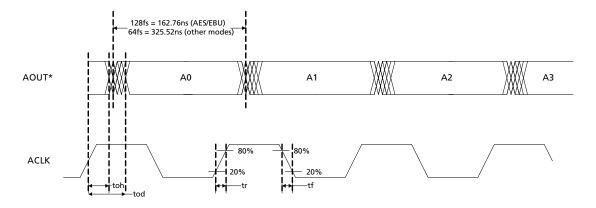

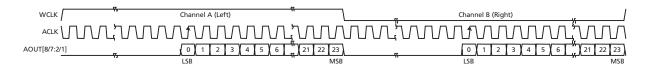

| Figure 4-35: ACLK to Data Signal Output Timing                                      |    |

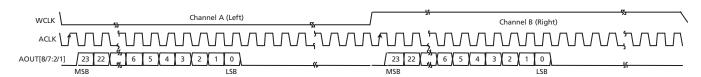

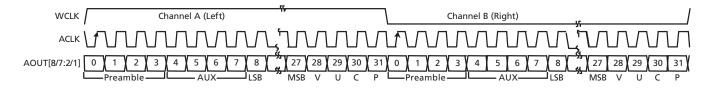

| Figure 4-36: I <sup>2</sup> S Audio Output Format                                   |    |

| Figure 4-37: AES/EBU Audio Output Format                                            |    |

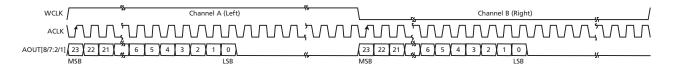

| Figure 4-38: Serial Audio, Left Justified, MSB First                                |    |

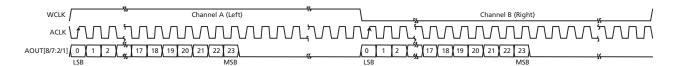

| Figure 4-39: Serial Audio, Left Justified, LSB First                                |    |

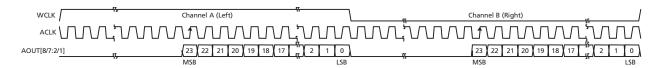

| Figure 4-40: Serial Audio, Right Justified, MSB First                               |    |

| Figure 4-41: Serial Audio, Right Justified, LSB First                               | 83 |

| Figure 4-42: AES/EBU Audio Output to Bit Clock Timing                   | 83  |

|-------------------------------------------------------------------------|-----|

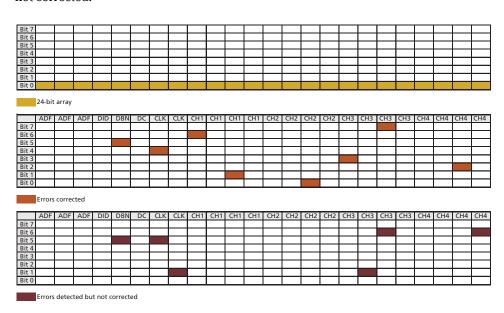

| Figure 4-43: ECC 24-bit Array and Examples                              | 86  |

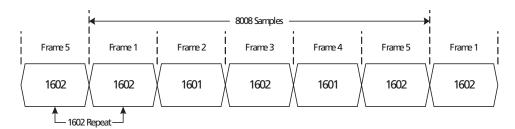

| Figure 4-44: Sample Distribution over 5 Video Frames (525-line Systems) | 88  |

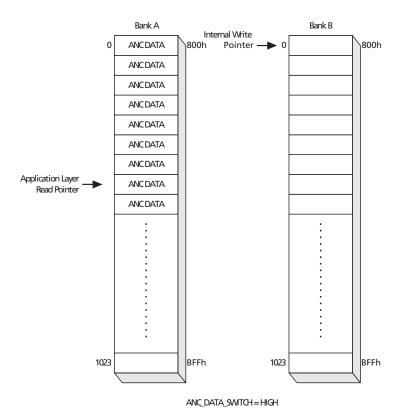

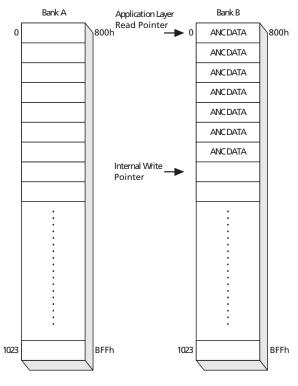

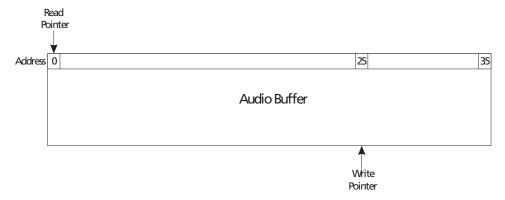

| Figure 4-45: Audio Buffer After Initial 26 Sample Write                 | 88  |

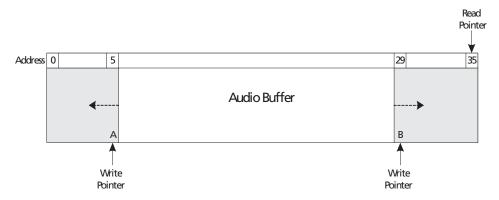

| Figure 4-46: Audio Buffer Pointer Boundary Checking                     | 89  |

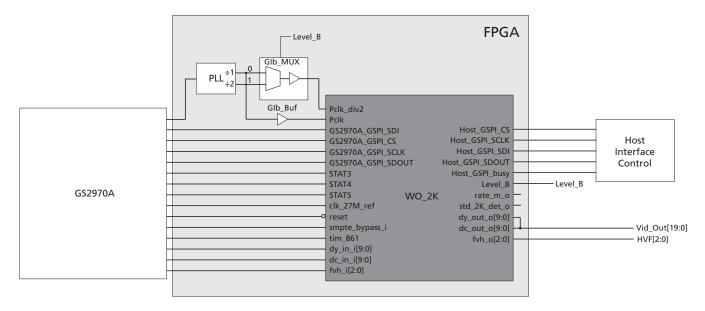

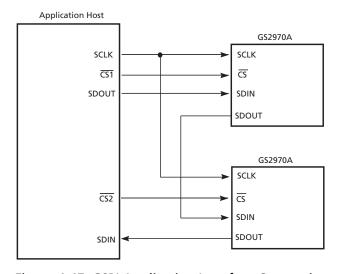

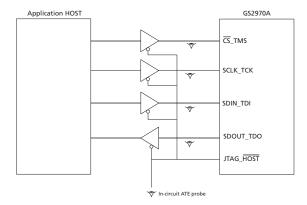

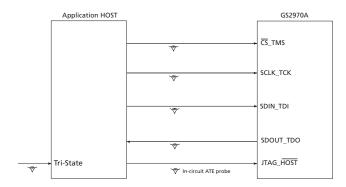

| Figure 4-47: GSPI Application Interface Connection                      | 94  |

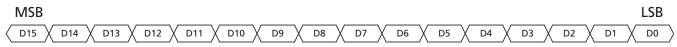

| Figure 4-48: Command Word Format                                        | 95  |

| Figure 4-49: Data Word Format                                           | 95  |

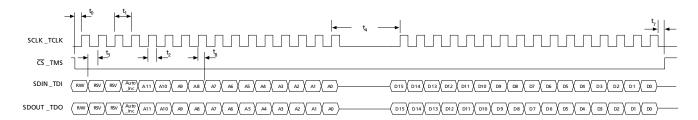

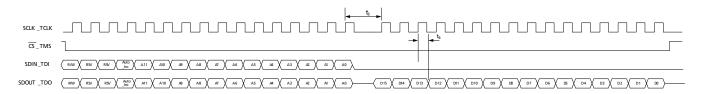

| Figure 4-50: Write Mode                                                 |     |

| Figure 4-51: Read Mode                                                  |     |

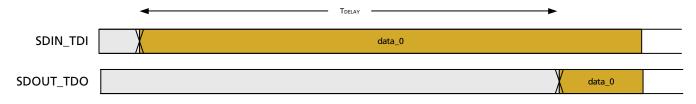

| Figure 4-52: GSPI Time Delay                                            |     |

| Figure 4-53: In-Circuit JTAG                                            |     |

| Figure 4-54: System JTAG                                                | 142 |

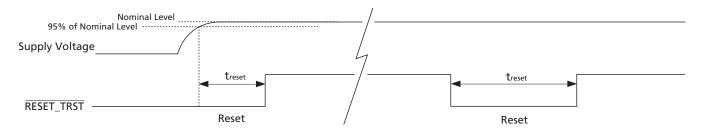

| Figure 4-55: Reset Pulse                                                | 143 |

| Figure 5-1: Typical Application Circuit                                 | 144 |

| Figure 7-1: Package Dimensions                                          | 146 |

| Figure 7-2: GS2970A Marking Diagram                                     | 147 |

| Figure 7-3: Pb-free Solder Reflow Profile                               | 148 |

|                                                                         |     |

# **List of Tables**

| Table 1-1: Pin Descriptions                                                 | . 9 |

|-----------------------------------------------------------------------------|-----|

| Table 2-1: Absolute Maximum Ratings 1                                       | 17  |

| Table 2-2: Recommended Operating Conditions 1                               | 17  |

| Table 2-3: DC Electrical Characteristics                                    | 18  |

| Table 2-4: AC Electrical Characteristics                                    | 20  |

| Table 4-1: Serial Digital Output                                            | 31  |

| Table 4-2: PLL Loop Bandwidth                                               | 32  |

| Table 4-3: Input Clock Requirements                                         | 33  |

| Table 4-4: Lock Detect Conditions                                           | 34  |

| Table 4-5: GS2970A Output Video Data Format Selections                      | 38  |

| Table 4-6: GS2970A PCLK Output Rates                                        | 40  |

| Table 4-7: Switch Line Position for Digital Systems                         | 45  |

| Table 4-8: Output Signals Available on Programmable Multi-Function Pins     | 46  |

| Table 4-9: Supported CEA-861 Formats                                        | 49  |

| Table 4-10: CEA861 Timing Formats 5                                         | 50  |

| Table 4-11: Supported Video Standard Codes                                  |     |

| Table 4-12: Data Format Register Codes                                      | 61  |

| Table 4-13: Error Status Register and Error Mask Register                   | 64  |

| Table 4-14: SMPTE ST 352 Packet Data                                        | 69  |

| Table 4-15: IOPROC_1 and IOPROC_2 Register Bits                             | 71  |

| Table 4-16: Serial Audio Pin Descriptions                                   | 80  |

| Table 4-17: Audio Output Formats                                            | 82  |

| Table 4-18: Audio Data Packet Detect Register                               | 84  |

| Table 4-19: Audio Group DID Host Interface Settings                         | 85  |

| Table 4-20: Audio Data and Control Packet DID Setting Register              | 85  |

| Table 4-21: Audio Buffer Pointer Offset Settings                            | 89  |

| Table 4-22: Audio Channel Mapping Codes                                     | 90  |

| Table 4-23: Audio Sample Word Lengths                                       | 91  |

| Table 4-24: Audio Channel Status Information Registers                      | 92  |

| Table 4-25: Audio Channel Status Block for Regenerate Mode Default Settings | 92  |

7 of 149

| Table 4-26: Audio Mute Control Bits                                     | 93    |

|-------------------------------------------------------------------------|-------|

| Table 4-27: GSPI Time Delay                                             | 96    |

| Table 4-28: GSPI Timing Parameters (50% levels; 3.3V or 1.8V operation) | 97    |

| Table 4-29: Video Core Configuration and Status Registers               | 98    |

| Table 4-30: SD Audio Core Configuration and Status Registers            | . 112 |

| Table 4-31: HD and 3G Audio Core Configuration and Status Registers     | . 126 |

| Table 4-32: ANC Extraction FIFO Access Registers                        | . 141 |

| Table 6-1: SMPTE Standards References                                   | . 145 |

| Гable 7-1: Packaging Data                                               | . 147 |

| Table 7-2: GS2970A Ordering Information                                 | . 148 |

# 1. Pin Out

# 1.1 Pin Assignment

|   | 1            | 2              | 3                | 4           | 5            | 6            | 7                      | 8                 | 9      | 10     |

|---|--------------|----------------|------------------|-------------|--------------|--------------|------------------------|-------------------|--------|--------|

| Α | VBG          | LF             | LB_CONT          | VCO_<br>VDD | STAT0        | STAT1        | IO_VDD                 | PCLK              | DOUT18 | DOUT17 |

| В | A_VDD        | PLL_<br>VDD    | RSV              | VCO_<br>GND | STAT2        | STAT3        | IO_GND                 | DOUT19            | DOUT16 | DOUT15 |

| С | SDI          | A_GND          | PLL_<br>VDD      | PLL_<br>VDD | STAT4        | STAT5        | RESET<br>_TRST         | DOUT12            | DOUT14 | DOUT13 |

| D | SDI          | A_GND          | A_GND            | PLL_<br>GND | CORE<br>_GND | CORE<br>_VDD | SW_EN                  | JTAG/<br>HOST     | IO_GND | IO_VDD |

| Е | SDI_VDD      | SDI_GND        | A_GND            | PLL_<br>GND | CORE<br>_GND | CORE<br>_VDD | SDOUT_<br>TDO          | SDIN_<br>TDI      | DOUT10 | DOUT11 |

| F | TERM         | RSV            | A_GND            | PLL_<br>GND | CORE<br>_GND | CORE<br>_VDD | CS_<br>TMS             | SCLK_<br>TCK      | DOUT8  | DOUT9  |

| G | RSV          | RSV            | RC_BYP           | RSV         | CORE<br>_GND | CORE<br>_VDD | SMPTE_<br>BYPASS       | DVB_ASI           | IO_GND | IO_VDD |

| Н | BUFF_<br>VDD | BUFF_<br>GND   | AUDIO_<br>EN/DIS | WCLK        | TIM_861      | XTAL_<br>OUT | <u>20bit/</u><br>10bit | IOPROC_<br>EN/DIS | DOUT6  | DOUT7  |

| J | SDO          | SDO_<br>EN/DIS | AOUT_1/2         | ACLK        | AOUT_5/6     | XTAL2        | IO_GND                 | DOUT1             | DOUT4  | DOUT5  |

| K | SDO          | STANDBY        | AOUT_3/4         | AMCLK       | AOUT_7/8     | XTAL1        | IO_VDD                 | DOUT0             | DOUT2  | DOUT3  |

# **1.2 Pin Descriptions**

**Table 1-1: Pin Descriptions**

| Pin<br>Number | Name    | Туре         | Description                                                                                                                                                                                                                 |

|---------------|---------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1            | VBG     | Analog Input | Band Gap voltage filter connection.                                                                                                                                                                                         |

| A2            | LF      | Analog Input | Loop Filter component connection.                                                                                                                                                                                           |

| A3            | LB_CONT | Analog Input | Connection for loop bandwidth control resistor.                                                                                                                                                                             |

| A4            | VCO_VDD | Input Power  | POWER pin for the VCO. Connect to a 1.2V $\pm$ 5% analog supply followed by a RC filter (see 5.1 Typical Application Circuit). A 105 $\Omega$ 1% resistor must be used in the RC filter circuit. VCO_VDD is nominally 0.7V. |

Table 1-1: Pin Descriptions (Continued)

| Pin<br>Number       | Name        | Туре        | Description                                                   |                                                                           |

|---------------------|-------------|-------------|---------------------------------------------------------------|---------------------------------------------------------------------------|

|                     |             |             | MULTI-FUNCTIONAL OUTPU                                        | T PORT.                                                                   |

|                     |             |             |                                                               | ogic parameters in the DC Electrical c level threshold and compatibility. |

|                     |             |             | Each of the STAT[0:5] pins ca<br>one of the following signals | n be configured individually to output<br>:                               |

|                     |             |             | Signal                                                        | Default                                                                   |

|                     |             |             | H/HSYNC                                                       | STAT0                                                                     |

|                     |             |             | V/VSYNC                                                       | STAT1                                                                     |

| A5, A6, B5,         | STAT[0:5]   | Output      | F/DE                                                          | STAT2                                                                     |

| B6, C5, C6          | 517 (1[0:5] |             | LOCKED                                                        | STAT3                                                                     |

|                     |             |             | Y/1ANC                                                        | STAT4                                                                     |

|                     |             |             | C/2ANC                                                        | <del>-</del>                                                              |

|                     |             |             | DATA ERROR                                                    | STAT5                                                                     |

|                     |             |             | VIDEO ERROR                                                   | _                                                                         |

|                     |             |             | AUDIO ERROR                                                   | _                                                                         |

|                     |             |             | EDH DETECTED                                                  | _                                                                         |

|                     |             |             | CARRIER DETECT                                                | _                                                                         |

|                     |             |             | RATE_DET0                                                     | _                                                                         |

|                     |             |             | RATE_DET1                                                     | -                                                                         |

| A7, D10,<br>G10, K7 | IO_VDD      | Input Power | POWER connection for digit digital.                           | al I/O. Connect to 3.3V or 1.8V DC                                        |

|                     |             | Output      | PARALLEL DATA BUS CLOCK                                       |                                                                           |

|                     |             |             |                                                               | ogic parameters in the DC Electrical c level threshold and compatibility. |

|                     |             |             | 3G 10-bit or 20-bit mode                                      | PCLK @ 148.5 or 148.5/1.001MHz                                            |

| A8                  | PCLK        |             | HD 10-bit mode                                                | PCLK @ 148.5 or 148.5/1.001MHz                                            |

|                     |             |             | HD 20-bit mode                                                | PCLK @ 74.25 or 74.25/1.001MHz                                            |

|                     |             |             | SD 10-bit mode                                                | PCLK @ 27MHz                                                              |

|                     |             |             | SD 20-bit mode                                                | PCLK @ 13.5MHz                                                            |

Table 1-1: Pin Descriptions (Continued)

| Pin<br>Number                                      | Name                                             | Туре         | Description                                                                                                                                             |                                                                                                                                                                                                                                                                                                                             |  |

|----------------------------------------------------|--------------------------------------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                                    | DOUT18, 17, 19,<br>16, 15, 12, 14, 13,<br>10, 11 | Output       | PARALLEL DATA BUS  Please refer to the Output Logic parameters in the DC Electrical  Characteristics table for logic level threshold and compatibility. |                                                                                                                                                                                                                                                                                                                             |  |

| A9, A10, B8,<br>B9, B10,C8,<br>C9, C10, E9,<br>E10 |                                                  |              | 20-bit mode<br>20bit/10bit = HIGH                                                                                                                       | SMPTE mode (SMPTE_BYPASS = HIGH and DVB_ASI = LOW):  Luma data output for SD and HD data rates; Data Stream 1 for 3G data rate  DVB-ASI mode (SMPTE_BYPASS = LOW and DVB_ASI = HIGH):  Not defined  Data-Through mode (SMPTE_BYPASS = LOW) and DVB_ASI = LOW):  Data output                                                 |  |

|                                                    |                                                  |              | 10-bit mode<br>20bit/10bit = LOW                                                                                                                        | SMPTE mode (SMPTE_BYPASS = HIGH and DVB_ASI = LOW):  Multiplexed Luma/Chroma data output for SD and HD data rates; Multiplexed Data Stream 1&2 for 3G data rate  DVB-ASI mode (SMPTE_BYPASS = LOW and DVB_ASI = HIGH):  8b/10b decoded DVB-ASI data  Data-Through mode (SMPTE_BYPASS = LOW and DVB_ASI = LOW):  Data output |  |

| B1                                                 | A_VDD                                            | Input Power  | POWER pin for analog                                                                                                                                    | circuitry. Connect to 3.3V DC analog.                                                                                                                                                                                                                                                                                       |  |

| B2, C3, C4                                         | PLL_VDD                                          | Input Power  | POWER pins for the Rec                                                                                                                                  | clocker PLL. Connect to 1.2V DC analog.                                                                                                                                                                                                                                                                                     |  |

| B3, F2, G1,<br>G2, G4                              | RSV                                              |              | These pins must be left                                                                                                                                 | unconnected.                                                                                                                                                                                                                                                                                                                |  |

| B4                                                 | VCO_GND                                          | Input Power  | GND pin for the VCO. C                                                                                                                                  | onnect to analog GND.                                                                                                                                                                                                                                                                                                       |  |

| B7, D9, G9,<br>J7                                  | IO_GND                                           | Input Power  | GND connection for dig                                                                                                                                  | gital I/O. Connect to digital GND.                                                                                                                                                                                                                                                                                          |  |

| C1, D1                                             | SDI, <del>SDI</del>                              | Analog Input | Serial Digital Differentia                                                                                                                              | al Input.                                                                                                                                                                                                                                                                                                                   |  |

| C2, D2, D3,<br>E3, F3                              | A_GND                                            | Input Power  | GND pins for sensitive a                                                                                                                                | nalog circuitry. Connect to analog GND.                                                                                                                                                                                                                                                                                     |  |

Table 1-1: Pin Descriptions (Continued)

| Pin<br>Number     | Name Type             |             | Description                                                                                                                         |

|-------------------|-----------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------|

|                   |                       |             | CONTROL SIGNAL INPUT                                                                                                                |

|                   |                       | Input       | Please refer to the Input Logic parameters in the DC Electrical Characteristics table for logic level threshold and compatibility.  |

|                   |                       |             | Used to reset the internal operating conditions to default settings and to reset the JTAG sequence.                                 |

|                   |                       |             | Normal mode (JTAG/ $\overline{\text{HOST}}$ = LOW):                                                                                 |

| C7                | RESET_TRST            |             | When LOW, all functional blocks are set to default conditions and all digital output signals become high impedance.                 |

|                   |                       |             | When HIGH, normal operation of the device resumes.                                                                                  |

|                   |                       |             | JTAG test mode (JTAG/ $\overline{HOST}$ = HIGH):                                                                                    |

|                   |                       |             | When LOW, all functional blocks are set to default and the JTAG test sequence is reset.                                             |

|                   |                       |             | When HIGH, normal operation of the JTAG test sequence resumes after $\overline{\text{RESET\_TRST}}$ is de-asserted.                 |

| D4, E4, F4        | PLL_GND               | Input Power | GND pins for the Reclocker PLL. Connect to analog GND.                                                                              |

| D5, E5, F5,<br>G5 | CORE_GND              | Input Power | GND connection for device core. Connect to digital GND.                                                                             |

| D6, E6, F6,<br>G6 | CORE_VDD              | Input Power | POWER connection for device core. Connect to 1.2V DC digital.                                                                       |

|                   | SW_EN                 |             | CONTROL SIGNAL INPUT                                                                                                                |

| D7                |                       | Input       | Please refer to the Input Logic parameters in the DC Electrical Characteristics table for logic level threshold and compatibility.  |

|                   |                       |             | Used to enable switch-line locking, as described in Section 4.10.1.                                                                 |

|                   |                       | Input       | CONTROL SIGNAL INPUT                                                                                                                |

|                   |                       |             | Please refer to the Input Logic parameters in the DC Electrical Characteristics table for logic level threshold and compatibility.  |

| D8                | JTAG/ <del>HOST</del> |             | Used to select JTAG test mode or host interface mode.                                                                               |

| 50                | 317.0711031           |             | When JTAG/HOST is HIGH, the host interface port is configured for JTAG test.                                                        |

|                   |                       |             | When JTAG/ $\overline{\text{HOST}}$ is LOW, normal operation of the host interface port resumes.                                    |

| E1                | SDI_VDD               | Input Power | POWER pin for SDI buffer. Connect to 3.3V DC analog.                                                                                |

| E2                | SDI_GND               | Input Power | GND pin for SDI buffer. Connect to analog GND.                                                                                      |

|                   |                       |             | COMMUNICATION SIGNAL OUTPUT                                                                                                         |

|                   |                       |             | Please refer to the Output Logic parameters in the DC Electrical Characteristics table for logic level threshold and compatibility. |

| E7                | SDOUT_TDO             | Output      | GSPI serial data output/test data out.                                                                                              |

| _,                | SDOUT_TDO             | Output      | In JTAG mode (JTAG/ $\overline{\text{HOST}}$ = HIGH), this pin is used to shift test results from the device.                       |

|                   |                       |             | In host interface mode, this pin is used to read status and configuration data from the device.                                     |

Table 1-1: Pin Descriptions (Continued)

| Pin<br>Number                                       | Name                                | Туре         | Description                                                                                                                                                                                                                                                                        |

|-----------------------------------------------------|-------------------------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                     |                                     |              | COMMUNICATION SIGNAL INPUT                                                                                                                                                                                                                                                         |

|                                                     |                                     |              | Please refer to the Input Logic parameters in the DC Electrical Characteristics table for logic level threshold and compatibility.                                                                                                                                                 |

| E8                                                  | SDIN_TDI                            | Input        | GSPI serial data in/test data in.                                                                                                                                                                                                                                                  |

| 20                                                  | 35111_151                           | трис         | In JTAG mode (JTAG/ $\overline{\text{HOST}}$ = HIGH), this pin is used to shift test date into the device.                                                                                                                                                                         |

|                                                     |                                     |              | In host interface mode, this pin is used to write address and configuration data words into the device.                                                                                                                                                                            |

| F1                                                  | TERM                                | Analog Input | Decoupling for internal SDI termination resistors.                                                                                                                                                                                                                                 |

|                                                     |                                     |              | COMMUNICATION SIGNAL INPUT                                                                                                                                                                                                                                                         |

|                                                     |                                     |              | Please refer to the Input Logic parameters in the DC Electrical Characteristics table for logic level threshold and compatibility.                                                                                                                                                 |

| F7                                                  | CS_TMS                              | Input        | Chip select / test mode start.                                                                                                                                                                                                                                                     |

| Γ7                                                  | C3_11VI3                            | прис         | In JTAG mode (JTAG/HOST = HIGH), this pin is Test Mode Start, use to control the operation of the JTAG test.                                                                                                                                                                       |

|                                                     |                                     |              | In host interface mode (JTAG/ $\overline{\text{HOST}}$ = LOW), this pin operates as the host interface chip select and is active LOW.                                                                                                                                              |

|                                                     |                                     |              | COMMUNICATION SIGNAL INPUT                                                                                                                                                                                                                                                         |

|                                                     |                                     |              | Please refer to the Input Logic parameters in the DC Electrical Characteristics table for logic level threshold and compatibility.                                                                                                                                                 |

|                                                     |                                     |              | Serial data clock signal.                                                                                                                                                                                                                                                          |

| F8                                                  | SCLK_TCK                            | Input        | In JTAG mode (JTAG/ $\overline{\text{HOST}}$ = HIGH), this pin is the JTAG clock.                                                                                                                                                                                                  |

|                                                     |                                     |              | In host interface mode (JTAG/ $\overline{\text{HOST}}$ = LOW), this pin is the host interface serial bit clock.                                                                                                                                                                    |

|                                                     |                                     |              | All JTAG/host interface addresses and data are shifted into/out of the device synchronously with this clock.                                                                                                                                                                       |

|                                                     |                                     |              | PARALLEL DATA BUS                                                                                                                                                                                                                                                                  |

|                                                     |                                     |              | Please refer to the Output Logic parameters in the DC Electrical Characteristics table for logic level threshold and compatibility.                                                                                                                                                |

| F9, F10, H9,<br>H10, J8, J9,<br>J10, K8, K9,<br>K10 | DOUT8, 9, 6, 7, 1,<br>4, 5, 0, 2, 3 | Output       | SMPTE mode (SMPTE_BYPASS = HIGH and DVB_ASI = LOW):  Chroma data output for SD and HD data rates; Data Stream 2 for 3G dat rate  20-bit mode 20-bit mode 20-bit/10bit = HIGH  DVB-ASI mode (SMPTE_BYPASS = LOV) and DVB_ASI = HIGH): Not defined  Data-Through mode (SMPTE_BYPASS) |

|                                                     |                                     |              | LOW andDVB_ASI = LOW): Data output                                                                                                                                                                                                                                                 |

|                                                     |                                     |              | 10-bit mode 20bit/10bit = LOW Forced LOW                                                                                                                                                                                                                                           |

|                                                     |                                     |              | CONTROL SIGNAL INPUT                                                                                                                                                                                                                                                               |

| G3                                                  | RC_BYP                              | Input        | Please refer to the Input Logic parameters in the DC Electrical Characteristics table for logic level threshold and compatibility.                                                                                                                                                 |

| 93                                                  | KC_D11                              | трис         | When this pin is LOW, the serial digital output is the buffered version of the input serial data. When this pin is HIGH, the serial digital output is the reclocked version of the input serial data.                                                                              |

Table 1-1: Pin Descriptions (Continued)

| Pin<br>Number | Name          | Туре              | Description                                                                                                                                                                                                                                                                                                 |

|---------------|---------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               |               |                   | CONTROL SIGNAL INPUT/OUTPUT                                                                                                                                                                                                                                                                                 |

|               |               |                   | Please refer to the Input/Output Logic parameters in the DC<br>Electrical Characteristics table for logic level threshold and<br>compatibility.                                                                                                                                                             |

|               |               |                   | Indicates the presence of valid SMPTE data.                                                                                                                                                                                                                                                                 |

| <b>G</b> 7    | SMPTE_BYPASS  | Input/Output      | When the AUTO/MAN bit in the host interface register is HIGH (Default), this pin is an OUTPUT. SMPTE_BYPASS is HIGH when the device locks to a SMPTE compliant input. SMPTE_BYPASS is LOW under all other conditions.                                                                                       |

| d/            | SWIFTE_BTFASS | Input/Output      | When the AUTO/MAN bit in the host interface register is LOW, th<br>pin is an INPUT:                                                                                                                                                                                                                         |

|               |               |                   | No SMPTE scrambling takes place, and none of the I/O processing features of the device are available when SMPTE_BYPASS is set LOW.                                                                                                                                                                          |

|               |               |                   | When SMPTE_BYPASS is set HIGH, the device carries out SMPTE scrambling and I/O processing.                                                                                                                                                                                                                  |

|               |               |                   | When SMPTE_BYPASS and DVB_ASI are both set LOW, the device operates in Data-Through mode.                                                                                                                                                                                                                   |

|               |               |                   | CONTROL SIGNAL INPUT                                                                                                                                                                                                                                                                                        |

|               |               |                   | Please refer to the Input/Output Logic parameters in the DC<br>Electrical Characteristics table for logic level threshold and<br>compatibility.                                                                                                                                                             |

|               |               |                   | Used to enable/disable DVB-ASI data extraction in manual mode.                                                                                                                                                                                                                                              |

| G8            | DVB_ASI       | Input/Output      | When the AUTO/MAN bit in the host interface is LOW, this pin is input and when the DVB_ASI pin is set HIGH the device will carry on DVB_ASI data extraction and processing. The SMPTE_BYPASS pin must be set LOW. When SMPTE_BYPASS and DVB_ASI are both set LOW, the device operates in Data-Through mode. |

|               |               |                   | When the AUTO/MAN bit in the host interface is HIGH (default), DVB-ASI is configured as a status output (set LOW), and DVB-ASI input streams are not supported or recognized.                                                                                                                               |

| H1            | BUFF_VDD      | Input Power       | POWER pin for the serial digital output $50\Omega$ buffer. Connect to 3.0 DC analog.                                                                                                                                                                                                                        |

| H2            | BUFF_GND      | Input Power       | GND pin for the cable driver buffer. Connect to analog GND.                                                                                                                                                                                                                                                 |

|               |               |                   | CONTROL SIGNAL INPUT                                                                                                                                                                                                                                                                                        |

| Н3            | AUDIO_EN/DIS  | Input             | Please refer to the Input Logic parameters in the DC Electrical Characteristics table for logic level threshold and compatibility.                                                                                                                                                                          |

|               |               |                   | Enables or disables audio extraction.                                                                                                                                                                                                                                                                       |

|               |               | _                 | 48kHz word clock for Audio.                                                                                                                                                                                                                                                                                 |

| H4            | WCLK          | Output            | Please refer to the Output Logic parameters in the DC Electrical Characteristics table for logic level threshold and compatibility.                                                                                                                                                                         |

|               |               |                   | CONTROL SIGNAL INPUT                                                                                                                                                                                                                                                                                        |

| H5            | TIM_861       | Input             | Please refer to the Input Logic parameters in the DC Electrical Characteristics table for logic level threshold and compatibility.                                                                                                                                                                          |

|               | 551           | mpst.             | Used to select CEA-861 timing mode.                                                                                                                                                                                                                                                                         |

|               |               |                   | When TIM_861 is HIGH, the device outputs CEA 861 timing signal (HSYNC/VSYNC/DE) instead of H:V:F digital timing signals.                                                                                                                                                                                    |

| Н6            | XTAL_OUT      | Digital<br>Output | Buffered 27MHz crystal output. Can be used to cascade the crysta signal.                                                                                                                                                                                                                                    |

Table 1-1: Pin Descriptions (Continued)

| Pin<br>Number | Name                      | Туре         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------|---------------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Н7            | 20bit/ <del>10bit</del>   | Input        | CONTROL SIGNAL INPUT  Please refer to the Input Logic parameters in the DC Electrical  Characteristics table for logic level threshold and compatibility.  Used to select the output bus width.  HIGH = 20-bit, LOW = 10-bit.                                                                                                                                                                                                                     |

| Н8            | IOPROC_EN/ <del>DIS</del> | Input        | CONTROL SIGNAL INPUT  Please refer to the Input Logic parameters in the DC Electrical Characteristics table for logic level threshold and compatibility.  Used to enable or disable audio and video processing features. When IOPROC_EN is HIGH, the audio and video processing features of the device are enabled. When IOPROC_EN is LOW, the processing features of the device are disabled, and the device is in a low-latency operating mode. |

| J1, K1        | SDO, <del>SDO</del>       | Output       | Serial Data Output Signal. $50\Omega$ CML buffer for interfacing to an external cable driver. Serial digital output signal operating at 2.97Gb/s, 2.97/1.001Gb/s, 1.485Gb/s, 1.485/1.001Gb/s and 270Mb/s.                                                                                                                                                                                                                                         |

| J2            | SDO_EN/ <del>DIS</del>    | Input        | Please refer to the Input Logic parameters in the DC Electrical Characteristics table for logic level threshold and compatibility.  Used to enable/disable the serial digital output stage.  When SDO_EN/DIS is LOW, the serial digital output signals, SDO and SDO, are both pulled HIGH.  When SDO_EN/DIS is HIGH, the serial digital output signals, SDO and SDO, are enabled.                                                                 |

| 13            | AOUT_1/2                  | Output       | Serial Audio Output; Channels 1 and 2.  Please refer to the Output Logic parameters in the DC Electrical Characteristics table for logic level threshold and compatibility.                                                                                                                                                                                                                                                                       |

| J4            | ACLK                      | Output       | 64fs sample clock for audio.  Please refer to the Output Logic parameters in the DC Electrical Characteristics table for logic level threshold and compatibility.                                                                                                                                                                                                                                                                                 |

| J5            | AOUT_5/6                  | Output       | Serial Audio Output; Channels 5 and 6.  Please refer to the Output Logic parameters in the DC Electrical Characteristics table for logic level threshold and compatibility.                                                                                                                                                                                                                                                                       |

| J6, K6        | XTAL2, XTAL1              | Analog Input | Input connection for 27MHz crystal.                                                                                                                                                                                                                                                                                                                                                                                                               |

| K2            | STANDBY                   | Input        | CONTROL SIGNAL INPUT  Please refer to the Input Logic parameters in the DC Electrical Characteristics table for logic level threshold and compatibility.  When this pin is set HIGH, the device is placed in a power-saving mode. No data processing occurs, and the digital I/Os are powered down.  In this mode, the serial digital output signals, SDO and SDO, are both pulled HIGH.                                                          |

| К3            | AOUT_3/4                  | Output       | Serial Audio Output; Channels 3 and 4.  Please refer to the Output Logic parameters in the DC Electrical Characteristics table for logic level threshold and compatibility.                                                                                                                                                                                                                                                                       |

Table 1-1: Pin Descriptions (Continued)

| Pin<br>Number | Name     | Туре   | Description                                                                                                                                                                                                |

|---------------|----------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

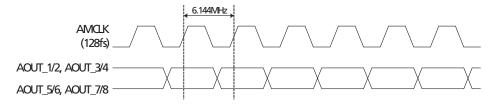

| K4            | AMCLK    | Output | Oversampled master clock for audio (128fs, 256fs, 512fs selectable).  Please refer to the Output Logic parameters in the DC Electrical  Characteristics table for logic level threshold and compatibility. |

| К5            | AOUT_7/8 | Output | Serial Audio Output; Channels 7 and 8.  Please refer to the Output Logic parameters in the DC Electrical Characteristics table for logic level threshold and compatibility.                                |

# 2. Electrical Characteristics

## 2.1 Absolute Maximum Ratings

**Table 2-1: Absolute Maximum Ratings**

| Parameter                                              | Value/Units     |

|--------------------------------------------------------|-----------------|

| Supply Voltage, Digital Core (CORE_VDD)                | -0.3V to +1.5V  |

| Supply Voltage, Digital I/O (IO_VDD)                   | -0.3V to +4.0V  |

| Supply Voltage, Analog 1.2V (PD_VDD, VCO_VDD)          | -0.3V to +1.5V  |

| Supply Voltage, Analog 3.3V (SDI_VDD, BUFF_VDD, A_VDD) | -0.3V to +4.0V  |

| Input Voltage Range (digital inputs)                   | -2.0V to +5.25V |

| Operating Temperature Range                            | -20°C to +85°C  |

| Functional Temperature Range                           | -40°C to +85°C  |

| Storage Temperature Range                              | -50°C to +125°C |

| Peak Reflow Temperature (JEDEC J-STD-020C)             | 260°C           |

| ESD Sensitivity, HBM (JESD22-A114)                     | 2kV             |

#### Note

Absolute Maximum Ratings are those values beyond which damage may occur. Functional operation under these conditions or at any other condition beyond those indicated in the AC/DC Electrical Characteristics sections is not implied.

## 2.2 Recommended Operating Conditions

**Table 2-2: Recommended Operating Conditions**

$T_A = -20$ °C to + 85°C, unless otherwise shown.

| Parameter                            | Symbol   | Conditions | Min  | Тур | Max  | Units | Notes |

|--------------------------------------|----------|------------|------|-----|------|-------|-------|

| Supply Voltage, Digital Core         | CORE_VDD | -          | 1.14 | 1.2 | 1.26 | V     | _     |

| Supply Voltage Digital I/O           | IO VDD   | 1.8V mode  | 1.71 | 1.8 | 1.89 | V     | =     |

| Supply Voltage, Digital I/O          | 10_VDD - | 3.3V mode  | 3.13 | 3.3 | 3.47 | V     | =     |

| Supply Voltage, PLL                  | PLL_VDD  | -          | 1.14 | 1.2 | 1.26 | V     | _     |

| Supply Voltage, Analog               | A_VDD    | -          | 3.13 | 3.3 | 3.47 | V     | 1     |

| Supply Voltage, Serial Digital Input | SDI_VDD  | -          | 3.13 | 3.3 | 3.47 | V     | 1     |

| Supply Voltage, CD Buffer            | BUFF_VDD | -          | 3.13 | 3.3 | 3.47 | V     | 1     |

#### Note:

1. The 3.3V supplies must track the 3.3V supply of an external EQ and external CD.

# 2.3 DC Electrical Characteristics

**Table 2-3: DC Electrical Characteristics**

| Parameter                          | Symbol           | Conditions             | Min             | Тур | Max             | Units |

|------------------------------------|------------------|------------------------|-----------------|-----|-----------------|-------|

| System                             |                  |                        |                 |     |                 |       |

|                                    |                  | 10bit 3G               | _               | 220 | 265             | mA    |

|                                    |                  | 20bit 3G               | -               | 215 | 265             | mA    |

| +1.2V Supply Current               | I <sub>1V2</sub> | 10/20bit HD            | -               | 175 | 215             | mA    |

|                                    |                  | 10/20bit SD            | -               | 145 | 180             | mA    |

|                                    |                  | DVB_ASI                | -               | 135 | 165             | mA    |

|                                    |                  | 10bit 3G               | -               | 32  | 34              | mA    |

|                                    |                  | 20bit 3G               | _               | 32  | 34              | mA    |

| +1.8V Supply Current               | I <sub>1V8</sub> | 10/20bit HD            | _               | 20  | 21              | mA    |

|                                    |                  | 10/20bit SD            | _               | 6   | 7               | mA    |

|                                    |                  | DVB_ASI                | _               | 6   | 7               | mA    |

|                                    |                  | 10bit 3G               | _               | 95  | 105             | mA    |

|                                    |                  | 20bit 3G               | _               | 95  | 105             | mA    |

| +3.3V Supply Current               | I <sub>3V3</sub> | 10/20bit HD            | _               | 65  | 75              | mA    |

|                                    |                  | 10/20bit SD            | _               | 35  | 45              | mA    |

|                                    |                  | DVB_ASI                | _               | 35  | 45              | mA    |

|                                    |                  | 10bit 3G               | _               | 380 | 470             | mW    |

|                                    |                  | 20bit 3G               | _               | 350 | 435             | mW    |

|                                    |                  | 10/20bit HD            | _               | 300 | 360             | mW    |

| Total Device Power (IO_VDD = 1.8V) | P <sub>1D8</sub> | 10/20bit SD            | _               | 235 | 305             | mW    |

|                                    |                  | DVB_ASI                | _               | 235 | 305             | mW    |

|                                    |                  | Reset                  | _               | 200 | _               | mW    |

|                                    |                  | Standby                | _               | 16  | 44              | mW    |

|                                    |                  | 10bit 3G               | _               | 580 | 700             | mW    |

|                                    |                  | 20bit 3G               | _               | 580 | 695             | mW    |

|                                    |                  | 10/20bit HD            | _               | 430 | 530             | mW    |

| Total Device Power (IO_VDD = 3.3V) | P <sub>3D3</sub> | 10/20bit SD            | _               | 290 | 370             | mW    |

|                                    |                  | DVB_ASI                | _               | 290 | 370             | mW    |