# **Serial Lite III Streaming Intel FPGA IP Core User Guide**

Updated for Intel® Quartus® Prime Design Suite: 18.1.1

**UG-01126 | 2020.05.05**Latest document on the web: **PDF | HTML**

## **Contents**

| 1. Se | rial Lite III Streaming Intel FPGA IP Core Quick Reference                         | 4  |

|-------|------------------------------------------------------------------------------------|----|

| 2. Ab | out the Serial Lite III Streaming IP Core                                          | 6  |

|       | 2.1. Serial Lite III Streaming IP Core Protocol                                    |    |

|       | 2.2. Serial Lite III Streaming IP Core Protocol Operating Modes                    |    |

|       | 2.2.1. Continuous Mode                                                             |    |

|       | 2.2.2. Burst Mode                                                                  |    |

|       | 2.3. Performance and Resource Utilization                                          |    |

| 3. Ge | etting Started                                                                     |    |

| 5. 00 | 3.1. Installing and Licensing Intel FPGA IP Cores                                  |    |

|       | 3.2. Intel FPGA IP Evaluation Mode                                                 |    |

|       | 3.2.1. Intel FPGA IP Evaluation Mode                                               |    |

|       |                                                                                    |    |

|       | 3.3. Specifying IP Core Parameters and Options                                     |    |

|       | 3.3.1. Serial Lite III Streaming IP Core Parameter Editor                          |    |

|       | 3.3.2. Intel Arria 10 Designs                                                      |    |

|       | 3.4. Serial Lite III Streaming IP Core Parameters                                  |    |

|       | 3.4.1. Parameter Settings for Intel Stratix 10 Devices                             |    |

|       | 3.4.2. Parameter Settings for Intel Arria 10 Devices                               |    |

|       | 3.4.3. Parameter Settings for Stratix V and Arria V GZ Devices                     |    |

|       | 3.5. Transceiver Reconfiguration Controller for Stratix V and Arria V GZ Designs   |    |

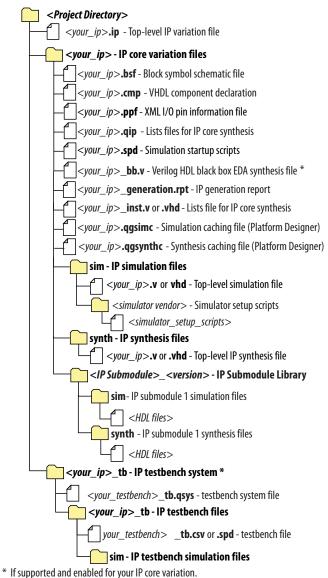

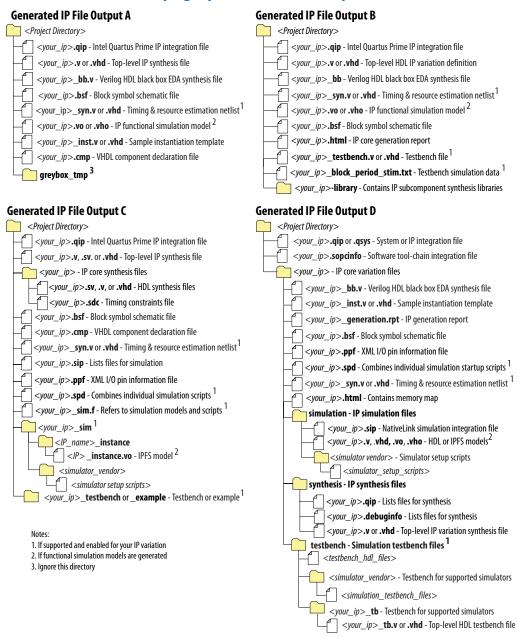

|       | 3.6. IP Core Generation Output (Intel Quartus Prime Pro Edition)                   |    |

|       | 3.7. IP Core Generation Output (Intel Quartus Prime Standard Edition)              |    |

|       | 3.8. Simulating                                                                    |    |

|       | 3.8.2. Simulating Inter FFGA IF Cores                                              |    |

|       | 3.8.3. Simulating and Verifying the Design                                         |    |

|       |                                                                                    |    |

| 4. Se | rial Lite III Streaming IP Core Design Examples                                    | 30 |

|       | 4.1. Serial Lite III Streaming IP Core Design Example for Intel Stratix 10 Devices | 30 |

|       | 4.2. Serial Lite III Streaming IP Core Design Example for Intel Arria 10 Devices   | 30 |

|       | 4.3. Serial Lite III Streaming IP Design Examples for Stratix V Devices            | 30 |

| 5. Se | rial Lite III Streaming IP Core Functional Description                             | 31 |

|       | 5.1. IP Core Architecture                                                          |    |

|       | 5.1.1. Serial Lite III Streaming Source Core                                       |    |

|       | 5.1.2. Serial Lite III Streaming Sink Core                                         |    |

|       | 5.1.3. Serial Lite III Streaming IP Core Duplex Core                               |    |

|       | 5.1.4. Interlaken PHY IP Duplex Core or Native PHY IP Duplex Core - Interlaken     | 57 |

|       | Mode or PCS Gearbox Mode                                                           | 37 |

|       | 5.1.5. Intel Stratix 10, Intel Arria 10, Stratix V, and Arria V GZ Variations      |    |

|       | 5.2. Transmission Overheads and Lane Rate Calculations                             |    |

|       | 5.3. Reset                                                                         |    |

|       | 5.4. Link-Up Sequence                                                              |    |

|       | 5.5. Error Detection, Reporting, and Recovering Mechanism                          |    |

|       | 5.6. CRC-32 Error Injection                                                        |    |

|       | 5.7. FIFO ECC Protection                                                           |    |

|       | 5.8. User Data Interface Waveforms                                                 | 40 |

|      | 5.9. Signals                                                                                                        | 52    |

|------|---------------------------------------------------------------------------------------------------------------------|-------|

|      | 5.9.1. Signals for Intel Stratix 10 Devices                                                                         |       |

|      | 5.9.2. Signals for Intel Arria 10 Devices                                                                           | 60    |

|      | 5.9.3. Signals for Stratix V and Arria V GZ Devices                                                                 | 67    |

|      | 5.10. Accessing Configuration and Status Registers                                                                  | 74    |

| 6. S | erial Lite III Streaming IP Core Clocking Guidelines                                                                | 75    |

|      | 6.1. Standard Clocking Mode                                                                                         | 75    |

|      | 6.1.1. Standard Clocking Mode in Serial Lite III Streaming Intel FPGA IP Core                                       |       |

|      | (Intel Stratix 10 Devices)                                                                                          | 75    |

|      | 6.1.2. Standard Clocking Mode in Intel Arria 10, Stratix V, and Arria V Devices                                     | 79    |

|      | 6.2. Advanced Clocking Mode                                                                                         | 82    |

|      | 6.2.1. Advanced Clocking Mode Structure for Serial Lite III Streaming Intel FPGA IP Core (Intel Stratix 10 Devices) | 82    |

|      | 6.2.2. Advanced Clocking Mode Structure For Intel Arria 10, Stratix V, and Arria                                    |       |

|      | V Devices                                                                                                           |       |

|      | 6.3. Standard Clocking Mode vs Advanced Clocking Mode                                                               |       |

|      | 6.4. Clocking Implementation Guidelines                                                                             |       |

|      | 6.4.1. Choosing TX PLL Type                                                                                         |       |

|      | 6.5. Core Latency                                                                                                   | 93    |

| 7. S | erial Lite III Streaming IP Core Configuration and Status Registers                                                 | 95    |

|      | 7.1. Register Map                                                                                                   | 95    |

|      | 7.2. Configuration and Status Registers                                                                             | 95    |

| 8. S | erial Lite III Streaming IP Core Debugging Guidelines                                                               | . 102 |

|      | 8.1. Creating a Signal Tap Debug File to Match Your Design Hierarchy                                                | 102   |

|      | 8.2. Serial Lite III Streaming IP Core Link Debugging                                                               |       |

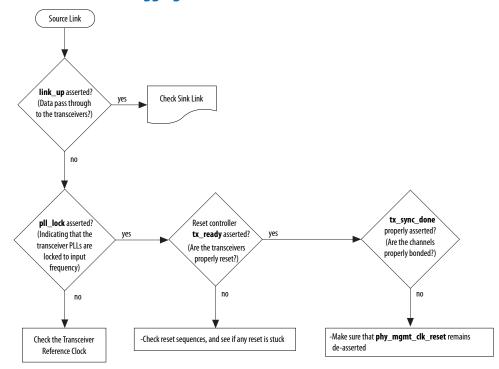

|      | 8.2.1. Source Core Link Debugging                                                                                   |       |

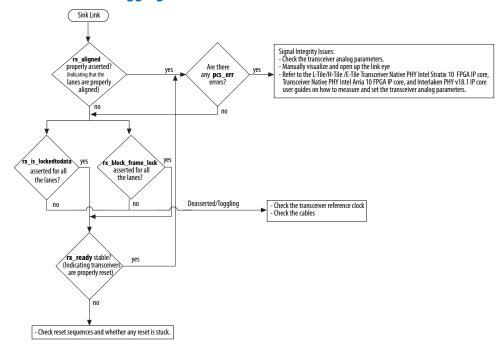

|      | 8.2.2. Sink Core Link Debugging                                                                                     | 104   |

| 9. S | erial Lite III Streaming IP Core User Guide Archives                                                                | 106   |

| 10   | Document Revision History for the Intel FPGA Serial Lite III Streaming IP Core                                      |       |

| -0.  | User Guide                                                                                                          | 107   |

|      |                                                                                                                     |       |

## 1. Serial Lite III Streaming Intel FPGA IP Core Quick Reference

The Serial Lite III Streaming Intel® FPGA IP core is a lightweight protocol suitable for high bandwidth streaming data in chip-to-chip, board-to-board, and backplane applications.

Table 1. Serial Lite III Streaming IP Core

| It                     | em                       | Description                                                                                                                                                                                                                                                                                                                                |

|------------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Release<br>Information | Version                  | 18.1.1 Intel Quartus <sup>®</sup> Prime Pro Edition (Intel Stratix <sup>®</sup> 10 and Intel Arria <sup>®</sup> 10 devices) 18.1 Intel Quartus Prime Standard Edition (Intel Arria 10, Stratix V and Arria V GZ devices)                                                                                                                   |

|                        | Release Date             | December 2018 (Intel Quartus Prime Pro Edition v18.1.1) September 2018 (Intel Quartus Prime Standard Edition v18.1)                                                                                                                                                                                                                        |

|                        | IP Catalog<br>Name       | Serial Lite III Streaming Intel FPGA IP (Intel Stratix 10, Stratix V, and Arria V GZ devices)     Serial Lite III Streaming Intel Arria 10 FPGA IP                                                                                                                                                                                         |

|                        | Ordering Code            | IP-SLITE3/ST                                                                                                                                                                                                                                                                                                                               |

|                        | Product ID               | 010A                                                                                                                                                                                                                                                                                                                                       |

|                        | Vendor ID                | 6AF7                                                                                                                                                                                                                                                                                                                                       |

| IP Core<br>Information | Core Features            | <ul> <li>Up to 28 Gbps<sup>(1)</sup> lane data rate for Intel Stratix 10 with H-tile or E-tile transceivers.</li> <li>Up to 17.4 Gbps lane data rates for Intel Arria 10 devices.</li> <li>Supports 1–24 serial lanes in configurations that provide nominal bandwidths from 3.125 gigabits per second (Gbps) to over 400 Gbps.</li> </ul> |

|                        | Protocol<br>Features     | Source (simplex transmitter), sink (simplex receiver), and duplex operations     Support for single or multiple lanes     64/67B physical layer encoding     Payload and idle scrambling     Error detection     Low overhead framing     Low point-to-point transfer latency                                                              |

|                        | Typical<br>Application   | High resolution video     Radar processing     Medical imaging     Baseband processing in wireless infrastructure                                                                                                                                                                                                                          |

|                        | Device Family<br>Support | Intel Stratix 10 (Advance support), Intel Arria 10 (Final support) , Arria V GZ (Final support), and Stratix V (Final support) FPGA devices.                                                                                                                                                                                               |

|                        |                          | continued                                                                                                                                                                                                                                                                                                                                  |

<sup>(1)</sup> Refer to Table 2 on page 8, Table 4 on page 9, and Table 5 on page 10 for maximum lane supported per data rate.

Intel Corporation. All rights reserved. Agilex, Altera, Arria, Cyclone, Enpirion, Intel, the Intel logo, MAX, Nios, Quartus and Stratix words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

9001:2015 Registered

| Item |             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |             | Advance support - The IP core is available for simulation and compilation for this device family. FPGA programming file (.pof) support is not available for Quartus Prime Pro - Stratix 10 Edition Beta software and as such IP timing closure cannot be guaranteed. Timing models include initial engineering estimates of delays based on early post-layout information. The timing models are subject to change as silicon testing improves the correlation between the actual silicon and the timing models. You can use this IP core for system architecture and resource utilization studies, simulation, pinout, system latency assessments, basic timing assessments (pipeline budgeting), and I/O transfer strategy (data-path width, burst depth, I/O standards tradeoffs).  Final support - The IP core is verified with final timing models for this device |

|      |             | family. The IP core meets all the functional and timing requirements for the device family and can be used in production designs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| De   | esign Tools | <ul> <li>IP parameter editor in the Intel Quartus Prime software for IP design instantiation and compilation</li> <li>Timing Analyzer in the Intel Quartus Prime software for timing analysis</li> <li>ModelSim-Intel FPGA Edition, MATLAB, or third-party tool using NativeLink for design simulation or synthesis</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

#### **Related Information**

- Intel Software Installation and Licensing

- What's New in Intel IP

- Serial Lite III Streaming Intel FPGA IP Core Release Notes

- Errata for Intel FPGA Serial Lite III Streaming IP core in the Knowledge Base

- Serial Lite III Streaming IP Core User Guide Archives on page 106

Provides a list of user guides for previous versions of the Intel FPGA Serial Lite III Streaming IP core.

- Timing and Power Models

Reports the default device support levels in the current version of the Quartus Prime Pro Edition software.

- Timing and Power Models

- Reports the default device support levels in the current version of the Quartus Prime Standard Edition software.

- Intel FPGA Serial Lite III Streaming IP Core Design Example User Guide for Intel Stratix 10 Devices

- Intel Arria 10 Serial Lite III Streaming IP Core Design Example User Guide

## 2. About the Serial Lite III Streaming IP Core

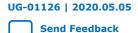

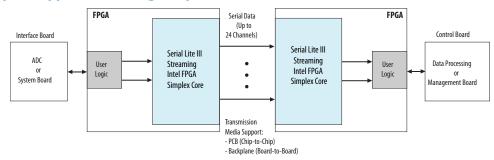

The Serial Lite III Streaming IP core is a high-speed serial communication protocol for chip-to-chip, board-to-board, and backplane application data transfers. This protocol offers high bandwidth, low overhead frames, low I/O count, and supports scalability in both number of lanes and lane speed.

The Serial Lite III Streaming IP core incorporates a media access control (MAC) block, a physical coding sublayer (PCS), and a physical media attachment (PMA). The IP core transmits and receives streaming data through the Avalon streaming interface on its FPGA fabric interface.

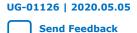

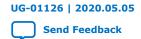

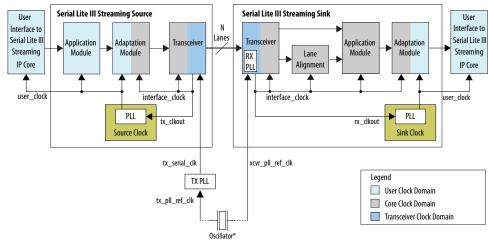

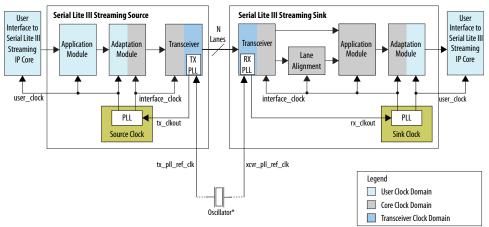

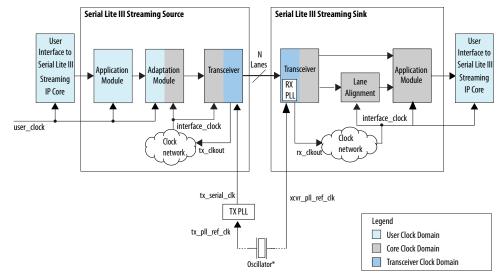

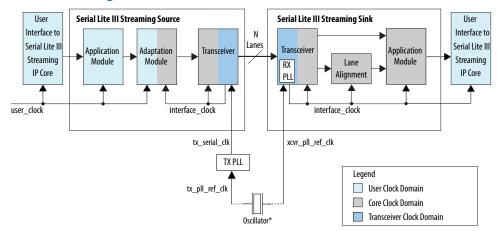

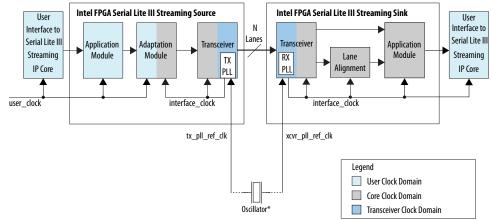

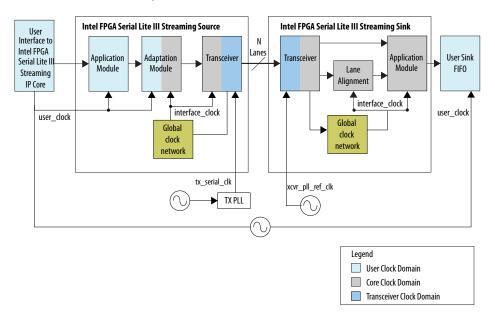

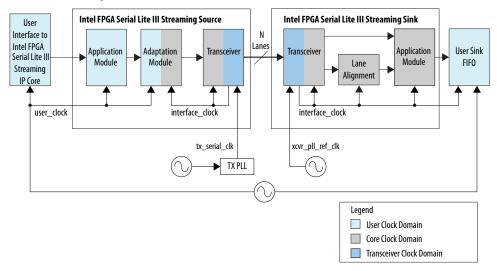

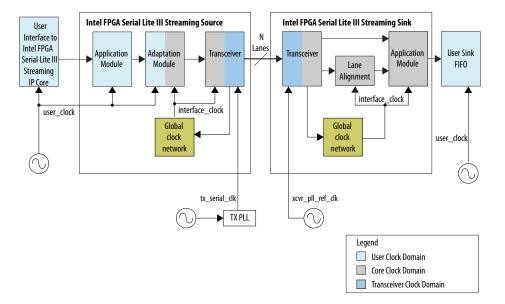

## Figure 1. Typical Application Using Simplex Core

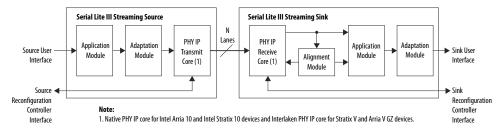

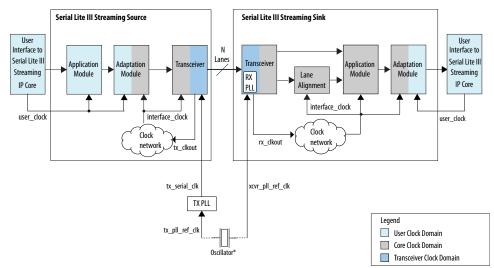

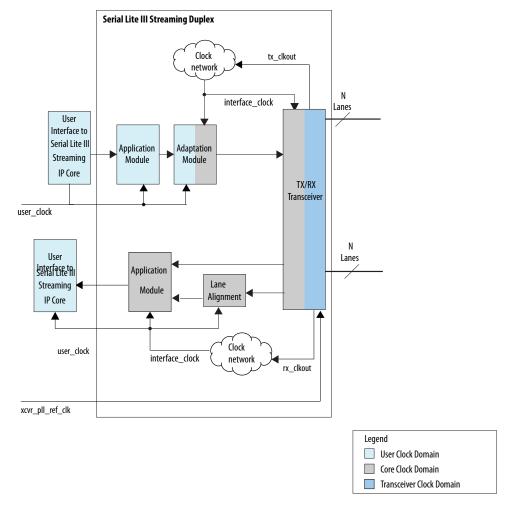

Figure 2. Typical System Application Using Duplex Core

## 2.1. Serial Lite III Streaming IP Core Protocol

The Serial Lite III Streaming IP core implements a protocol that supports high bandwidth data streaming over a unidirectional or bidirectional, high-speed serial link.

Intel Corporation. All rights reserved. Agilex, Altera, Arria, Cyclone, Enpirion, Intel, the Intel logo, MAX, Nios, Quartus and Stratix words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

9001:2015 Registered

The Serial Lite III Streaming IP core has the following protocol features:

- Simplex source only, simplex sink only, and duplex (transmitter and receiver)

operations

- Support for single or multiple lanes

- 64B/67B physical layer encoding

- Payload and idle scrambling

- Error detection:

- Source burst gap mismatch error

- Error Correction Code (ECC) with 1 bit correction and 2 or more bits detection

- Sink and source adaptation First In First Out (FIFO) overflow error

- Sink Cyclic Redundancy Check (CRC) errors

- Sink Physical Coding Sublayer (PCS) synchronization, metaframe, or CRC errors

- · Low protocol overhead

- Low point-to-point transfer latency

- Reduces soft logic resource utilization using hardened Transceiver Native PHY Intel Arria 10 FPGA IP core and L-Tile/H-Tile/E-Tile Transceiver Intel Stratix 10 FPGA IP Core or Interlaken PHY v18.1 IP core (Stratix V and Arria V GZ devices)

## 2.2. Serial Lite III Streaming IP Core Protocol Operating Modes

The protocol defines two operating modes for different applications: continuous and burst mode.

The IP core that you generate can be in either mode. No parameter option is available to select between continuous and burst modes. The selection depends on how you provide data at the Avalon streaming TX interface.

### 2.2.1. Continuous Mode

The Serial Lite III Streaming link operating in continuous mode accepts and transmits user data over the link, and presents it at the user interface at the receiving link at the same rate and without gaps in the stream, if user logic does not de-assert data valid signal as part of the stream. However, the streaming interface stops operating in continuous mode if user logic de-asserts the data valid signal in the middle of data transfer and there is no guarantee that the end-point sink is able to replicate the exact data pattern of the source. When operating in this mode, a link implementing the protocol looks like a data pipe that can transparently forward all data presented on the user interface to the far end of the link.

Continuous mode is appropriate for applications that require a simple interface to transmit a single, high bandwidth data stream. An example of this application is sensor data links for radar and wireless infrastructure. With this mode, data converters can connect to either end of the link with minimal interface logic.

#### Important:

Continuous mode is applicable only in Standard Clocking Mode., It is not possible to operate in this mode with asynchronous clocking implementation because asynchronous clocking requires data valid signal to be de-asserted, to break the data stream to avoid FIFO overflow at the sink due to PPM difference.

#### 2.2.2. Burst Mode

The Serial Lite III Streaming IP core link operating in burst mode accepts bursts of data across the user interface and transmits each burst across the link as a discrete data burst.

Burst mode is appropriate for applications where the data stream is divided into bursts of data. An example of this application is uncompressed digital video where the data stream is divided into lines of display raster. This mode provides more flexibility to the clocking and also supports multiplexing of multiple data streams across the link.

#### Important:

The minimum required gap between bursts is 1 user clock cycle on the transmit side. Therefore, you must provide one extra user clock cycle between an end of burst and the start of the next burst. The Serial Lite III Streaming IP core allows you to select between 1 or 2 burst gap. To connect the IP core of version 15.1 to IP core of the previous version, you must select a burst gap of 2 for backward compatibility.

#### **Related Information**

- Standard Clocking Mode on page 75

- Advanced Clocking Mode on page 82

## 2.3. Performance and Resource Utilization

Serial Lite III Streaming Intel FPGA IP in Intel Stratix 10 devices support the following transceiver tiles for each device speed grade and data rate:

Table 2. Serial Lite III Streaming Intel FPGA IP Transceiver Tiles Support in Intel Stratix 10 Devices

| Data Rate | Core Speed Grade | Maximum Supported Lanes |                    |                    |  |  |

|-----------|------------------|-------------------------|--------------------|--------------------|--|--|

|           |                  | L-Tile Transceiver      | H-Tile Transceiver | E-Tile Transceiver |  |  |

| 17.4 Gbps | 1                | 24                      | 24                 | 24                 |  |  |

|           | 2                | 22                      | 24                 | 24                 |  |  |

|           | 3                | 18                      | 20                 | 24                 |  |  |

| 25.0 Gbps | 1                | 6                       | 8                  | 12                 |  |  |

|           | 2                | 4                       | 6                  | 8                  |  |  |

| 28.0 Gbps | 1                | N/A                     | 4                  | 4                  |  |  |

|           | 2                | N/A                     | 2                  | 1                  |  |  |

## Table 3. Serial Lite III Streaming IP Performance and Resource Utilization with L-Tile Transceiver in Intel Stratix 10 Devices

These typical resources and expected performance for different Serial Lite III Streaming IP core variants are obtained using the Intel Quartus Prime Pro Edition software targeting the Intel Stratix 10 1SG280LU3F50E1VG device for 17.4 Gbps data rate and 1SG280LU2F50E1VG device for 25 Gbps data rate. The resource utilization numbers are the same for ECC enabled and disabled.

| Direction | Clocking Mode | Data Lanes | Per-Lane Data<br>Rate (Mbps) | ALMs  | Primary | Secondary | M20K   |

|-----------|---------------|------------|------------------------------|-------|---------|-----------|--------|

| Source    | Standard      | 24         | 17400                        | 11675 | 13622   | 776       | 49     |

|           | Standard      | 6          | 25000                        | 3160  | 3644    | 215       | 13     |

|           |               |            |                              |       |         | con       | tinued |

| Direction | Clocking Mode | Data Lanes | Per-Lane Data<br>Rate (Mbps) | ALMs  | Primary | Secondary | M20K |

|-----------|---------------|------------|------------------------------|-------|---------|-----------|------|

|           | Advance       | 24         | 17400                        | 11691 | 13571   | 919       | 49   |

|           | Advance       | 6          | 25000                        | 3139  | 3687    | 181       | 13   |

| Sink      | Standard      | 24         | 17400                        | 5181  | 7532    | 2065      | 49   |

|           | Standard      | 6          | 25000                        | 1463  | 2009    | 513       | 13   |

|           | Advance       | 24         | 17400                        | 4485  | 6994    | 2359      | 0    |

|           | Advance       | 6          | 25000                        | 1245  | 1792    | 629       | 0    |

| Duplex    | Standard      | 24         | 17400                        | 15793 | 19074   | 2913      | 98   |

|           | Standard      | 6          | 25000                        | 4299  | 5123    | 698       | 26   |

|           | Advance       | 24         | 17400                        | 14984 | 18880   | 2976      | 49   |

|           | Advance       | 6          | 25000                        | 4025  | 4980    | 812       | 13   |

## Table 4. Serial Lite III Streaming IP Performance and Resource Utilization with H-Tile Transceiver in Intel Stratix 10 Devices

These typical resources and expected performance for different Serial Lite III Streaming IP core variants are obtained using the Intel Quartus Prime Pro Edition software targeting the Intel Stratix 10 1SG280HU3F50E1VG device for 17.4 Gbps data rate, 1SG280HU2F50E1VG device for 25 Gbps data rate, and 1SG280HU1F50E1VG device for 28 Gbps data rate. The resource utilization numbers are the same for ECC enabled and disabled.

| Direction | Clocking Mode | Data Lanes | Per-Lane Data<br>Rate (Mbps) | ALMs  | Primary | Secondary | M20K |

|-----------|---------------|------------|------------------------------|-------|---------|-----------|------|

| Source    | Standard      | 24         | 17400                        | 11708 | 13604   | 851       | 49   |

| Source    | Standard      | 8          | 25000                        | 5013  | 5048    | 296       | 17   |

|           | Standard      | 4          | 28000                        | 2652  | 2803    | 193       | 9    |

|           | Advance       | 24         | 17400                        | 11638 | 13636   | 817       | 49   |

|           | Advance       | 8          | 25000                        | 4919  | 5195    | 324       | 17   |

|           | Advance       | 4          | 28000                        | 2649  | 2830    | 176       | 9    |

| Sink      | Standard      | 24         | 17400                        | 5175  | 7732    | 1907      | 49   |

|           | Standard      | 8          | 25000                        | 2685  | 3063    | 666       | 17   |

|           | Standard      | 4          | 28000                        | 1367  | 1659    | 263       | 9    |

|           | Advance       | 24         | 17400                        | 4524  | 7045    | 2295      | 0    |

|           | Advance       | 8          | 25000                        | 2530  | 3009    | 761       | 0    |

|           | Advance       | 4          | 28000                        | 1371  | 1599    | 397       | 0    |

| Duplex    | Standard      | 24         | 17400                        | 15790 | 19353   | 2814      | 98   |

|           | Standard      | 8          | 25000                        | 6239  | 7332    | 949       | 34   |

|           | Standard      | 4          | 28000                        | 3391  | 3916    | 526       | 18   |

|           | Advance       | 24         | 17400                        | 15012 | 18941   | 3078      | 49   |

|           | Advance       | 8          | 25000                        | 6208  | 7174    | 987       | 17   |

|           | Advance       | 4          | 28000                        | 3312  | 3824    | 533       | 9    |

## Table 5. Serial Lite III Streaming IP Performance and Resource Utilization with E-Tile Transceiver in Intel Stratix 10 Devices

These typical resources and expected performance for different Serial Lite III Streaming IP core variants are obtained using the Intel Quartus Prime Pro Edition software targeting the Intel Stratix 10 1ST280EY3F55E1VG device for 17.4 Gbps data rate, 1ST280EY2F55E1VG device for 25 Gbps data rate, and 1ST280EY1F55E1VG device for 28 Gbps data rate. The resource utilization numbers are the same for ECC enabled and disabled.

| Direction | Clocking Mode | Data Lanes | Per-Lane Data<br>Rate (Mbps) | ALMs  | Primary | Secondary | M20K |

|-----------|---------------|------------|------------------------------|-------|---------|-----------|------|

| Duplex    | Standard      | 24         | 17400                        | 48277 | 59072   | 10903     | 194  |

|           | Standard      | 12         | 25000                        | 24026 | 28845   | 5717      | 73   |

|           | Standard      | 4          | 28000                        | 8596  | 9825    | 1904      | 34   |

|           | Advance       | 24         | 17400                        | 47516 | 58816   | 11321     | 145  |

|           | Advance       | 12         | 25000                        | 24460 | 28608   | 5265      | 98   |

|           | Advance       | 4          | 28000                        | 8377  | 9559    | 1823      | 25   |

## Table 6. Serial Lite III Streaming IP Performance and Resource Utilization for Intel Arria 10 Devices

These typical resources and expected performance for different Serial Lite III Streaming IP core variants are obtained using the Intel Quartus Prime Pro Edition software targeting the Intel Arria 10 (10AX115S1F45I1SGES) FPGA devices.

| Direction | Clocking<br>Mode | Maximum<br>Supported<br>Data Lanes | Per-Lane<br>Data Rate<br>(Mbps) | ECC      | ALMs | Primary | Secondary | M20K |

|-----------|------------------|------------------------------------|---------------------------------|----------|------|---------|-----------|------|

| Source    | Standard         | 24                                 | 17400 <sup>(2)</sup>            | Disabled | 2613 | 5049    | 780       | 39   |

|           | Standard         | 24                                 | 17400 <sup>(2)</sup>            | Enabled  | 5961 | 9680    | 525       | 72   |

|           | Advanced         | 24                                 | 17400 <sup>(2)</sup>            | Disabled | 3009 | 5240    | 570       | 39   |

|           | Advanced         | 24                                 | 17400 <sup>(2)</sup>            | Enabled  | 6065 | 9659    | 552       | 72   |

| Sink      | Standard         | 24                                 | 17400 <sup>(2)</sup>            | Disabled | 3974 | 7550    | 1750      | 49   |

|           | Standard         | 24                                 | 17400 <sup>(2)</sup>            | Enabled  | 4065 | 7570    | 1632      | 50   |

|           | Advanced         | 24                                 | 17400 <sup>(2)</sup>            | Disabled | 3297 | 5815    | 1580      | 0    |

|           | Advanced         | 24                                 | 17400 <sup>(2)</sup>            | Enabled  | 3275 | 5524    | 1870      | 0    |

| Duplex    | Standard         | 24                                 | 17400 <sup>(2)</sup>            | Disabled | 6152 | 12511   | 2000      | 88   |

|           | Standard         | 24                                 | 17400 <sup>(2)</sup>            | Enabled  | 9313 | 16606   | 2193      | 122  |

|           | Advanced         | 24                                 | 17400 (2)                       | Disabled | 5833 | 10462   | 2146      | 39   |

|           | Advanced         | 24                                 | 17400 (2)                       | Enabled  | 8868 | 14853   | 2112      | 72   |

<sup>(2)</sup> Available only with transceiver speed grade 1.

## Table 7. Serial Lite III Streaming IP Performance and Resource Utilization for Stratix V and Arria V Devices

These typical resources and expected performance for different Serial Lite III Streaming IP core variants are obtained using the Intel Quartus Prime Standard Edition software targeting the Stratix V GX (5SGXMA7H2F35C2) and the Arria V GZ (5AGZME7K2F40I3L) FPGA devices.

| Direction | Clocking<br>Mode | Maximum<br>Supported<br>Data Lanes | Per-Lane<br>Data Rate<br>(Mbps) | ECC      | ALMs  | Primary | Secondary | M20K |

|-----------|------------------|------------------------------------|---------------------------------|----------|-------|---------|-----------|------|

| Source    | Standard         | 24                                 | 10312.50                        | Disabled | 5684  | 6114    | 46        | 39   |

|           | Standard         | 24                                 | 10312.50                        | Enabled  | 11122 | 13422   | 271       | 72   |

|           | Advanced         | 24                                 | 10312.50                        | Disabled | 5680  | 6104    | 43        | 39   |

|           | Advanced         | 24                                 | 10312.50                        | Enabled  | 11015 | 13418   | 239       | 72   |

| Sink      | Standard         | 24                                 | 10312.50                        | Disabled | 5499  | 9601    | 93        | 49   |

|           | Standard         | 24                                 | 10312.50                        | Enabled  | 5517  | 9510    | 91        | 50   |

|           | Advanced         | 24                                 | 10312.50                        | Disabled | 4356  | 7757    | 43        | 0    |

|           | Advanced         | 24                                 | 10312.50                        | Enabled  | 4356  | 7757    | 43        | 0    |

| Duplex    | Standard         | 24                                 | 10312.50                        | Disabled | 8742  | 15024   | 165       | 88   |

|           | Standard         | 24                                 | 10312.50                        | Enabled  | 14045 | 22279   | 337       | 122  |

|           | Advanced         | 24                                 | 10312.50                        | Disabled | 7550  | 13211   | 74        | 39   |

|           | Advanced         | 24                                 | 10312.50                        | Enabled  | 12606 | 20534   | 293       | 72   |

## 3. Getting Started

#### **Related Information**

- Introduction to Intel IP Cores

- Provides general information about all Intel FPGA IP cores, including parameterizing, generating, upgrading, and simulating IP cores.

- Creating Version-Independent IP and Qsys Simulation Scripts

Create simulation scripts that do not require manual updates for software or IP

version upgrades.

- Project Management Best Practices

Guidelines for efficient management and portability of your project and IP files.

## 3.1. Installing and Licensing Intel FPGA IP Cores

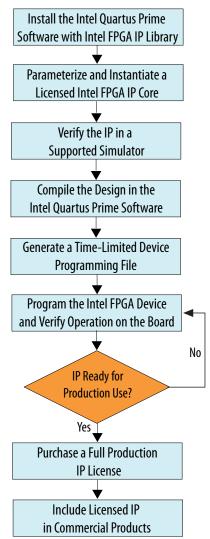

The Intel Quartus Prime software installation includes the Intel FPGA IP library. This library provides many useful IP cores for your production use without the need for an additional license. Some Intel FPGA IP cores require purchase of a separate license for production use. The Intel FPGA IP Evaluation Mode allows you to evaluate these licensed Intel FPGA IP cores in simulation and hardware, before deciding to purchase a full production IP core license. You only need to purchase a full production license for licensed Intel IP cores after you complete hardware testing and are ready to use the IP in production.

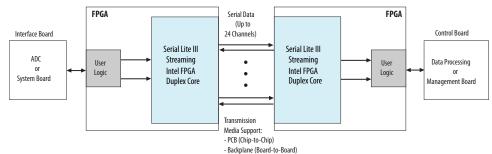

The Intel Quartus Prime software installs IP cores in the following locations by default:

## Figure 3. IP Core Installation Path

#### Table 8. IP Core Installation Locations

| Location                                                               | Software                                | Platform |

|------------------------------------------------------------------------|-----------------------------------------|----------|

| <pre><drive>:\intelFPGA_pro\quartus\ip\altera</drive></pre>            | Intel Quartus Prime Pro Edition         | Windows* |

| <pre><drive>:\intelFPGA\quartus\ip\altera</drive></pre>                | Intel Quartus Prime Standard<br>Edition | Windows  |

| <pre><home directory="">:/intelFPGA_pro/quartus/ip/altera</home></pre> | Intel Quartus Prime Pro Edition         | Linux*   |

| <pre><home directory="">:/intelFPGA/quartus/ip/altera</home></pre>     | Intel Quartus Prime Standard<br>Edition | Linux    |

Intel Corporation. All rights reserved. Agilex, Altera, Arria, Cyclone, Enpirion, Intel, the Intel logo, MAX, Nios, Quartus and Stratix words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

9001:2015 Registered

Note: The Intel Quartus Prime software does not support spaces in the installation path.

## 3.2. Intel FPGA IP Evaluation Mode

The free Intel FPGA IP Evaluation Mode allows you to evaluate licensed Intel FPGA IP cores in simulation and hardware before purchase. Intel FPGA IP Evaluation Mode supports the following evaluations without additional license:

- Simulate the behavior of a licensed Intel FPGA IP core in your system.

- Verify the functionality, size, and speed of the IP core quickly and easily.

- Generate time-limited device programming files for designs that include IP cores.

- Program a device with your IP core and verify your design in hardware.

Intel FPGA IP Evaluation Mode supports the following operation modes:

- **Tethered**—Allows running the design containing the licensed Intel FPGA IP indefinitely with a connection between your board and the host computer. Tethered mode requires a serial joint test action group (JTAG) cable connected between the JTAG port on your board and the host computer, which is running the Intel Quartus Prime Programmer for the duration of the hardware evaluation period. The Programmer only requires a minimum installation of the Intel Quartus Prime software, and requires no Intel Quartus Prime license. The host computer controls the evaluation time by sending a periodic signal to the device via the JTAG port. If all licensed IP cores in the design support tethered mode, the evaluation time runs until any IP core evaluation expires. If all of the IP cores support unlimited evaluation time, the device does not time-out.

- **Untethered**—Allows running the design containing the licensed IP for a limited time. The IP core reverts to untethered mode if the device disconnects from the host computer running the Intel Quartus Prime software. The IP core also reverts to untethered mode if any other licensed IP core in the design does not support tethered mode.

When the evaluation time expires for any licensed Intel FPGA IP in the design, the design stops functioning. All IP cores that use the Intel FPGA IP Evaluation Mode time out simultaneously when any IP core in the design times out. When the evaluation time expires, you must reprogram the FPGA device before continuing hardware verification. To extend use of the IP core for production, purchase a full production license for the IP core.

You must purchase the license and generate a full production license key before you can generate an unrestricted device programming file. During Intel FPGA IP Evaluation Mode, the Compiler only generates a time-limited device programming file (ct name>\_time\_limited.sof) that expires at the time limit.

Figure 4. Intel FPGA IP Evaluation Mode Flow

Note: Refer to each IP core's user guide for parameterization steps and implementation details.

Intel licenses IP cores on a per-seat, perpetual basis. The license fee includes first-year maintenance and support. You must renew the maintenance contract to receive updates, bug fixes, and technical support beyond the first year. You must purchase a full production license for Intel FPGA IP cores that require a production license, before generating programming files that you may use for an unlimited time. During Intel FPGA IP Evaluation Mode, the Compiler only generates a time-limited device programming file (project name>\_time\_limited.sof) that expires at the time limit. To obtain your production license keys, visit the Self-Service Licensing Center.

The Intel FPGA Software License Agreements govern the installation and use of licensed IP cores, the Intel Quartus Prime design software, and all unlicensed IP cores.

#### **Related Information**

- Intel Quartus Prime Licensing Site

- Introduction to Intel FPGA Software Installation and Licensing

### 3.2.1. Intel FPGA IP Evaluation Mode Timeout Behavior

All IP cores in a device time out simultaneously when the most restrictive evaluation time is reached. If there is more than one IP core in a design, the time-out behavior of the other IP cores may mask the time-out behavior of a specific IP core .

For IP cores, the untethered time-out is one hour; the tethered time-out value is indefinite. Your design stops working after the hardware evaluation time expires. The Intel Quartus Prime software uses Intel FPGA IP Evaluation Mode Files (.ocp) in your project directory to identify your use of the Intel FPGA IP Evaluation Mode evaluation program. After you activate the feature, do not delete these files.

When the evaluation time expires, the link\_up signal goes low.

### **Related Information**

AN 320: Using Intel FPGA IP Evaluation Mode

## 3.3. Specifying IP Core Parameters and Options

Follow these steps to specify IP core parameters and options.

- 1. In the Platform Designer IP Catalog (**Tools** ➤ **IP Catalog**), locate and double-click the name of the IP core to customize. The parameter editor appears.

- 2. Specify a top-level name for your custom IP variation. This name identifies the IP core variation files in your project. If prompted, also specify the target FPGA device family and output file HDL preference. Click **OK**.

- 3. Specify parameters and options for your IP variation:

- Optionally select preset parameter values. Presets specify all initial parameter values for specific applications (where provided).

- Specify parameters defining the IP core functionality, port configurations, and device-specific features.

- Specify options for generation of a timing netlist, simulation model, testbench, or example design (where applicable).

- Specify options for processing the IP core files in other EDA tools.

- 4. Click **Finish** to generate synthesis and other optional files matching your IP variation specifications. The parameter editor generates the top-level .qsys IP variation file and HDL files for synthesis and simulation. Some IP cores also simultaneously generate a testbench or example design for hardware testing.

The top-level IP variation is added to the current Intel Quartus Prime project. Click **Project > Add/Remove Files in Project** to manually add a .qsys (Intel Quartus Prime Standard Edition) or .ip (Intel Quartus Prime Pro Edition) file to a project. Make appropriate pin assignments to connect ports.

## 3.3.1. Serial Lite III Streaming IP Core Parameter Editor

Based on the values you set, the Serial Lite III Streaming IP core parameter editor automatically calculates the rest of the parameters, and provides you with the following values or information:

- Input data rate per lane

- Transceiver data rate per lane

- A list of feasible transceiver reference clock frequencies, one of which you select to provide to the core

#### Important:

If your design targets Stratix V or Arria V GZ devices, you cannot migrate your design to Intel Arria 10 and Intel Stratix 10 devices automatically. For Intel Arria 10 devices, the transceiver reconfiguration functionality is embedded inside the transceivers. Therefore, you must re-instantiate the IP core to target Intel Arria 10 devices. For Intel Stratix 10 devices, you must re-instantiate the IP core to target specific transceiver tiles due to the transceiver architecture differences. You cannot migrate your design from Intel Stratix 10 L-tile/H-Tile devices to Intel Stratix 10 E-Tile devices.

## **Related Information**

Parameter Settings for Intel Stratix 10 Devices on page 17

## 3.3.2. Intel Arria 10 Designs

If your design targets the Intel Arria 10 devices:

- The parameter editor displays a message about the required output clock frequency of the external TX PLL IP clock. For source or duplex modes, connect the Transceiver PHY Reset Controller to the TX PLL to ensure the appropriate HSSI power-up sequence.

- For source only Intel Arria 10 implementations, the parameter editor does not provide the transceiver reference clock frequency because the user is expected to provide the transmit serial clock. If you use an on-chip PLL to generate the transmit serial clock, you can use the same PLL reference clock frequency that you provide to the core in the sink direction, operating at the same user clock frequency (or equivalent transceiver lane data rate).

- The Serial Lite III Streaming Intel Arria 10 FPGA IP core expects the user to provide the transmitter's serial clock. If you compile the IP without the proper serial clock, the Intel Quartus Prime Compiler issues a compilation error.

- When generating the example testbench, the Serial Lite III Streaming Intel Arria 10 FPGA IP core instantiates an external transceiver ATX PLL for the transmit serial clock based on the required user clock only when configured in sink or duplex mode. The transceiver ATX PLL core is configured with the transceiver reference clock specified in the parameter editor and transmit serial clock.

- To generate the Serial Lite III Streaming Intel Arria 10 FPGA IP Core example testbench using the parameter editor, select **Generate Example Designs** > < directory\_name>. Intel recommends that you generate the Intel Arria 10 simulation testbench for the sink or duplex direction.

## **Related Information**

- Parameter Settings for Intel Arria 10 Devices on page 19

- Intel Stratix 10, Intel Arria 10, Stratix V, and Arria V GZ Variations on page 38

• Intel Arria 10 SerialLite III Streaming IP Core Design Example User Guide

## **3.4. Serial Lite III Streaming IP Core Parameters**

## **3.4.1. Parameter Settings for Intel Stratix 10 Devices**

Table 9. IP

| Parameter                                                            | Value                                                                       | Default                                                                                                                                                                                                             | Description                                                                                                                                                                                                                                                                                                          |  |

|----------------------------------------------------------------------|-----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| General Design Options                                               |                                                                             |                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                      |  |

| Direction                                                            | Source, Sink,<br>Duplex                                                     | Duplex                                                                                                                                                                                                              | Select the variation of the IP core. Supports source, sink, or full duplex transmissions.  Note: Sink or source only variant is not supported when                                                                                                                                                                   |  |

|                                                                      |                                                                             |                                                                                                                                                                                                                     | you select <b>E-Tile</b> as the transceiver tile in Intel Quartus Prime Pro Edition v18.1.                                                                                                                                                                                                                           |  |

| Number of lanes                                                      | 1-24                                                                        | 6                                                                                                                                                                                                                   | Specifies the number of lanes (equal to physical transceiver links) that are used to transfer the streaming data.                                                                                                                                                                                                    |  |

| Meta frame<br>length in words                                        | 200-8191                                                                    | 200                                                                                                                                                                                                                 | Specifies the metaframe length.                                                                                                                                                                                                                                                                                      |  |

| Transceiver<br>reference clock<br>frequency                          | <pre><range by="" plls="" supported="" the="" transceiver=""></range></pre> | 312.5 MHz                                                                                                                                                                                                           | Supports multiple transceiver reference clock frequencies for flexibility in the oscillator and PLL choices. This transceiver reference clock frequency must match the external PLL reference clock frequency for Intel Stratix 10 L-tile/H-tile devices                                                             |  |

|                                                                      |                                                                             |                                                                                                                                                                                                                     | Note: Transceiver reference clock is limited to 500 MHz when you select <b>E-Tile</b> as the transceiver tile in Intel Quartus Prime Pro Edition v18.1.                                                                                                                                                              |  |

| VCCR_GXB and<br>VCCT_GXB<br>supply voltage<br>for the<br>Transceiver | 1_1V,<br>1_0V                                                               | 1_0V                                                                                                                                                                                                                | Select VCCR_GXB and VCCT_GXB supply voltages. Refer to Intel Stratix 10 Device Family Pin Connection Guidelines for more information related to these pins. Note: This parameter is not available when you select E- Tile as the transceiver tile.                                                                   |  |

| Transceiver<br>channel type                                          | GX,<br>GXT                                                                  | GX                                                                                                                                                                                                                  | Select the transceiver channel variant. Select <b>GXT</b> as the transceiver variant to implement data rate more than 17.4 Gbps.                                                                                                                                                                                     |  |

|                                                                      |                                                                             |                                                                                                                                                                                                                     | Note: This parameter is not available when you select <b>E-Tile</b> as the transceiver tile.                                                                                                                                                                                                                         |  |

| Enable M20K ECC<br>support                                           | Yes/No                                                                      | No                                                                                                                                                                                                                  | Select to use error correcting code (ECC) protection to strengthen the FIFO buffers from single-event upset (SEU changes. Enables built-in error correcting code (ECC) support on the M20K embedded block memory for single-error correction, double-adjacent-error correction, and triple-adjacent-error detection. |  |

| Transceiver Tile                                                     | L-Tile,<br>H-Tile,<br>E-Tile                                                | <depending on<br="">the transceiver<br/>tile supported in<br/>the chosen<br/>device. For Intel<br/>Stratix 10<br/>devices which<br/>support H-Tile<br/>and E-Tile, the<br/>default value is<br/>H-Tile.</depending> | Reports the actual transceiver tile. The value changes according to the transceiver crete tile chosen in the device.                                                                                                                                                                                                 |  |

| User Interface                                                       | L                                                                           | 1                                                                                                                                                                                                                   | ı                                                                                                                                                                                                                                                                                                                    |  |

|                                                                      |                                                                             |                                                                                                                                                                                                                     | continued                                                                                                                                                                                                                                                                                                            |  |

| Parameter                                 | Value                                                                                | Default                 | Description                                                                                                                                                                                                                                                                                                                                                       |

|-------------------------------------------|--------------------------------------------------------------------------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Streaming Mode                            | Basic, Full                                                                          | Full                    | Specifies the streaming mode.  Basic: This is a pure streaming mode where data is sent without burst, sync, empty cycle, and frame delimiter to increase bandwidth.  Full: This mode sends a burst and sync cycle at the start of frame and a burst and empty cycle at the end of frame. Provide a gap of one empty cycle between two data frames.                |

| Required idle<br>cycles between<br>bursts | 1, 2                                                                                 | 2                       | Supports two values to optimize for bandwidth efficiency or maintain backward compatibility with existing Serial Lite III Streaming IP cores (legacy).  1: Recommended for high bandwidth streaming. The same Burst Gap setting must be set for both source and sink IP core.  2: For backward compatibility with Quartus II version 15.1 and older sink IP core. |

| Adaptation FIFO partial full threshold    | 8 - 18                                                                               | 15                      | Specifies the partial full threshold of the transmit FIFO. ready_tx signal will de-assert when data reaches this level in the FIFO.                                                                                                                                                                                                                               |

| Clocking mode                             | Standard clocking<br>mode,<br>Advanced clocking<br>mode                              | Standard clocking mode  | Specifies the clocking mode. Refer to Serial Lite III Streaming IP Core Clocking Guidelines on page 75 for more information.                                                                                                                                                                                                                                      |

| User input                                | User clock<br>frequency,<br>Transceiver data<br>rate                                 | User clock<br>frequency | Select <b>User clock frequency</b> to specify the user clock input and allow the IP core to determine the transceiver data rate.  Select <b>Transceiver data rate</b> to specify the desired data rate and allow the IP core to determine the user clock frequency.                                                                                               |

| User clock<br>frequency<br>required       | Minimum: 50 MHz<br>Maximum: Limited<br>by the supported<br>transceiver data<br>rates | 177.556818<br>MHz       | Specifies the desired frequency for the user clock input for the transmit (Standard Clocking Mode and Advanced Clocking Mode) and receive user interface (Standard Clocking Mode).  This frequency in turn determines the required transceiver data rate to support the calculated transmit and receive bandwidths.                                               |

| Transceiver data rate                     | required user clock<br>frequency *<br>overheads * 64                                 | 12.5 Gbps               | The effective data rate at the output of the transceivers, incorporating transmission and other overheads.  The parameter editor automatically calculates this value by adding the input data rate with transmission overheads to provide you with a selection of user clock frequency.                                                                           |

| Aggregate user bandwidth                  | number of lanes * required user clock frequency * 64                                 | 68.18 Gbps              | This value is derived by multiplying the number of lanes and user interface data rate.                                                                                                                                                                                                                                                                            |

## **IP Debug and Phy Dynamic Reconfiguration**

## **Table 10.** Native Transceiver Phy

| Parameter                      | Value    | Default | Description                                            |

|--------------------------------|----------|---------|--------------------------------------------------------|

| Dynamic Reconfiguration        |          |         |                                                        |

| Enable dynamic reconfiguration | , matica |         | Note: This parameter is enabled by default and can not |

| continued                      |          |         |                                                        |

#### UG-01126 | 2020.05.05

| Parameter                                                                 | Value         | Default | Description                                                                                                                                                                                                    |

|---------------------------------------------------------------------------|---------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Enable Altera<br>Debug Master<br>Endpoint                                 | On/Off        | Off     | Enables ADME and Optional Reconfiguration Logic parameters of the L-Tile/H-Tile/E-Tile Transceiver Native PHY Intel Stratix 10 FPGA IP Core.                                                                   |

| Optional Reconfigu                                                        | ıration Logic |         |                                                                                                                                                                                                                |

| Enable capability registers                                               | On/Off        | Off     | Enables capability registers that provide high level information about the configuration f the transceiver channel.                                                                                            |

| Set user-defined IP identifier                                            | User-defined  | 0       | Sets a user-defined numeric identifier that can be read from the user_identifier offset when the capability registers are enabled.  Note: To set the value, enabled the Enable capability registers parameter. |

| Enable control<br>and status<br>registers                                 | On/Off        | Off     | Enables soft registers to read status signals and write control signals on the PHY interface through the embedded debug.                                                                                       |

| Enable PRBS<br>(Pseudo Random<br>Binary Sequence)<br>soft<br>accumulators | On/Off        | Off     | Enables soft logic for performing PRBS bit and error accumulation when the hard PRBS generator and checker are used.  Note: This parameter is not available when you select E-Tile as the transceiver tile.    |

For information about parameters in the **PMA Adaptation** tab, please refer to the *PMA Adaptation* topic in the *Intel Stratix 10 E-Tile Transceiver PHY User Guide*.

Note:

The **PMA Adaptation** tab is only available in Intel Stratix 10 with E-tile transceiver devices. You must select **E-Tile** as the **Transceiver Tile** to use the parameters in the **PMA Adaptation** tab.

### **Related Information**

- Serial Lite III Streaming IP Core Parameter Editor on page 16

- Intel Stratix 10 L- and H-Tile Transceiver PHY User Guide Dynamic Reconfiguration Parameters

- Intel Stratix 10 E-Tile Transceiver PHY User Guide

For more information about the Intel Stratix 10 E-Tile Native PHY IP core.

- Intel Stratix 10 E-Tile Transceiver PHY User Guide For more information about PMA Adaptation parameters.

## 3.4.2. Parameter Settings for Intel Arria 10 Devices

### Table 11. IP

| Parameter              | Value                | Default | Description                                                                                                       |  |

|------------------------|----------------------|---------|-------------------------------------------------------------------------------------------------------------------|--|

| General Design Options |                      |         |                                                                                                                   |  |

| Direction              | Source, Sink, Duplex | Duplex  | Supports source, sink, or full duplex transmissions.                                                              |  |

| Number of lanes        | 1-24                 | 2       | Specifies the number of lanes (equal to physical transceiver links) that are used to transfer the streaming data. |  |

| continued              |                      |         |                                                                                                                   |  |

| Parameter                                 | Value                                                                                | Default                   | Description                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------------------------------------|--------------------------------------------------------------------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Transceiver reference clock frequency     | <range supported<br="">by the transceiver<br/>PLLs&gt;</range>                       | 644.53125 MHz             | Supports multiple transceiver reference clock frequencies for flexibility in the oscillator and PLL choices. This transceiver reference clock frequency must match the external PLL reference clock frequency.                                                                                                                                                                                                              |

| Meta frame<br>length in words             | 200-8191                                                                             | 200                       | Specifies the metaframe length.                                                                                                                                                                                                                                                                                                                                                                                             |

| Enable<br>Transceiver<br>Native PHY ADME  | On/Off                                                                               | Off                       | Turn on to enable ADME and Optional Reconfiguration Logic parameters of the Transceiver Native PHY Intel Arria $10/\text{Intel Cyclone}^{\otimes}$ 10 GX FPGA IP core.                                                                                                                                                                                                                                                      |

| Enable M20K ECC<br>support                | On/Off                                                                               | Off                       | Turn on to use error correcting code (ECC) protection to strengthen the FIFO buffers from single-event upset (SEU) changes. Enables built-in error correcting code (ECC) support on the M20K embedded block memory for single-error correction, double-adjacent-error correction, and triple-adjacent-error detection.                                                                                                      |

| User Interface                            |                                                                                      |                           |                                                                                                                                                                                                                                                                                                                                                                                                                             |

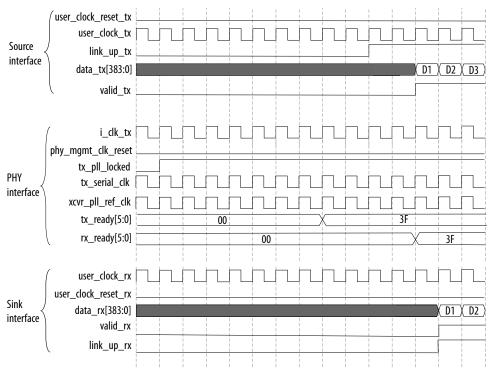

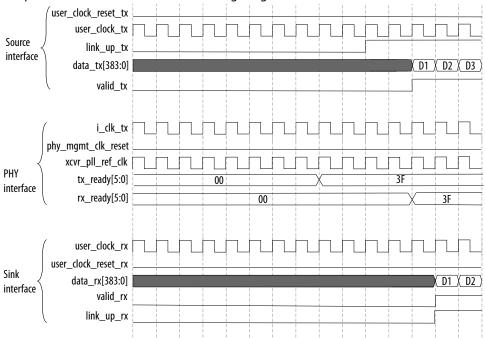

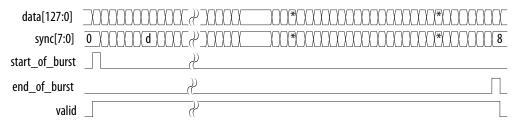

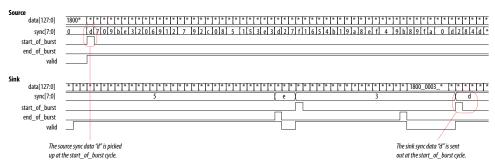

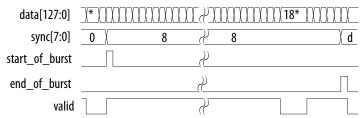

| Required idle<br>cycles between<br>bursts | 1, 2                                                                                 | 2                         | Supports two values to optimize for bandwidth efficiency or maintain backward compatibility with existing Serial Lite III Streaming IP cores (legacy).  1: Recommended for high bandwidth streaming. The same Burst Gap setting must be set for both source and sink IP core.  2: For backward compatibility with Quartus II version 15.1 and older sink IP core.                                                           |