Data sheet: Technical data

Document Number: MMA685x

Rev. 9, 01/2017

# MMA685x, Single-axis, SPI Inertial Sensor

MMA685x, a SafeAssure solution, is a SPI-based, single-axis, medium-g, over-damped lateral accelerometer designed for use in automotive airbag systems.

#### **Features**

- ±20 g to ±120 g full-scale range

- 3.3 V or 5 V single supply operation

- SPI-compatible serial interface

- 10-bit digital signed or unsigned SPI data output

- · Programmable arming functions

- 12 low-pass filter options, ranging from 50 Hz to 1000 Hz

- Optional offset cancellation with > 6 s averaging period and < 0.25 LSB/s slew rate

- Pb-free, 16-Pin QFN, 6 mm x 6 mm x 1.98 mm package

#### **Referenced Documents**

• AEC-Q100, Revision G, dated May 14, 2007 (http://www.aecouncil.com/)

| Ordering information |      |            |             |             |  |  |  |  |  |

|----------------------|------|------------|-------------|-------------|--|--|--|--|--|

| Device               | Axis | Axis Range | Package     | Shipping    |  |  |  |  |  |

| MMA6851BKCW          | Х    | ±25 g      | 98ASA00690D | Tubes       |  |  |  |  |  |

| MMA6853BKCW          | Х    | ±50 g      | 98ASA00690D | Tubes       |  |  |  |  |  |

| MMA6855BKCW          | Х    | ±120 g     | 98ASA00690D | Tubes       |  |  |  |  |  |

| MMA6856BKCW          | Х    | ±60 g      | 98ASA00690D | Tubes       |  |  |  |  |  |

| MMA6851BKCWR2        | Х    | ±25 g      | 98ASA00690D | Tape & Reel |  |  |  |  |  |

| MMA6853BKCWR2        | Х    | ±50 g      | 98ASA00690D | Tape & Reel |  |  |  |  |  |

| MMA6855BKCWR2        | Х    | ±120 g     | 98ASA00690D | Tape & Reel |  |  |  |  |  |

| MMA6856BKCWR2        | Х    | ±60 g      | 98ASA00690D | Tape & Reel |  |  |  |  |  |

# MMA685x

#### **Bottom View**

Pb-free 16-Pin QFN 6 mm x 6 mm x 1.98 mm package

# 1 General Description

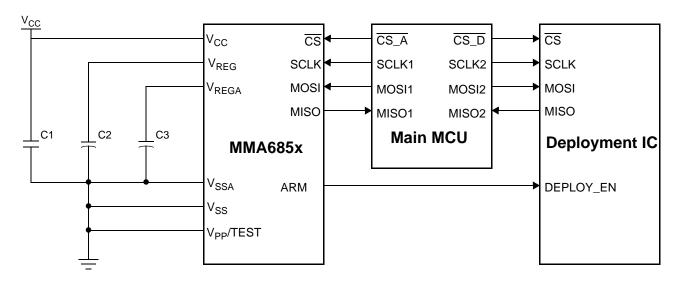

# 1.1 Application Diagram

Figure 1. Application Diagram

**Table 1. External Component Recommendations**

| Ref Des | Туре    | Description                     | Purpose                                                 |

|---------|---------|---------------------------------|---------------------------------------------------------|

| C1      | Ceramic | 0.1 μF, 10 %, 10 V Minimum, X7R | V <sub>CC</sub> Power Supply Decoupling                 |

| C2      | Ceramic | 1 μF, 10 %, 10 V Minimum, X7R   | Voltage Regulator Output Capacitor (C <sub>REG</sub> )  |

| C3      | Ceramic | 1 μF, 10 %, 10 V Minimum, X7R   | Voltage Regulator Output Capacitor (C <sub>REGA</sub> ) |

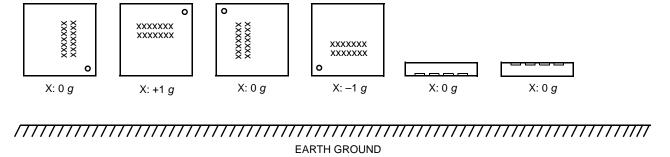

# 1.2 Device Orientation

Figure 2. Device Orientation Diagram

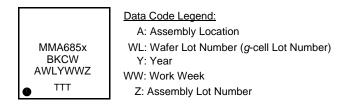

Figure 3. Part Marking

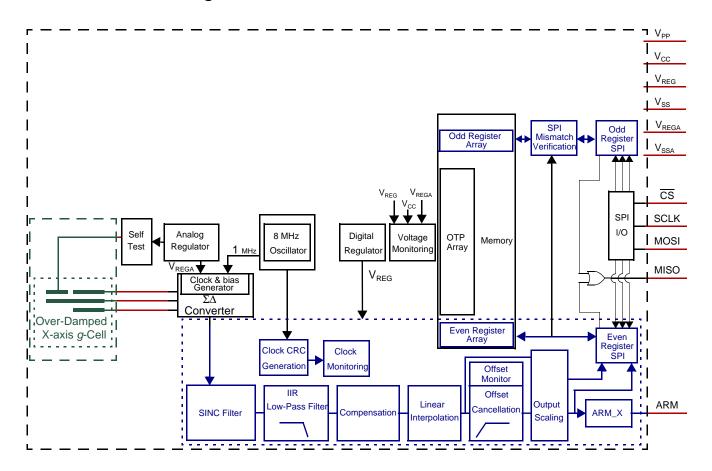

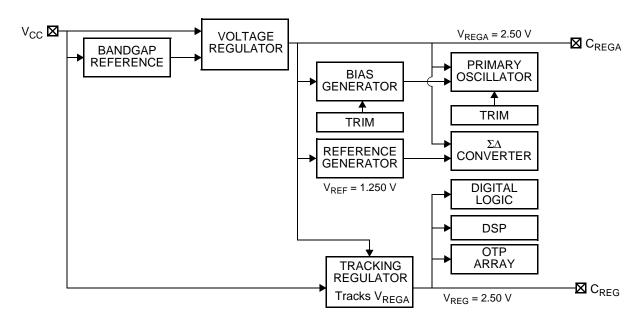

# 1.3 Internal Block Diagram

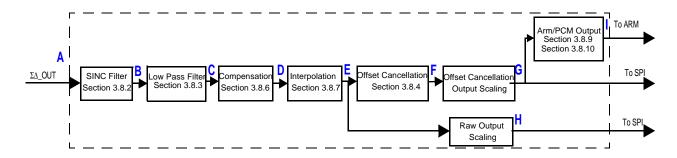

Figure 4. Block Diagram

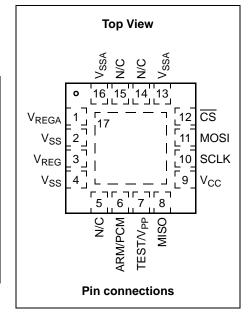

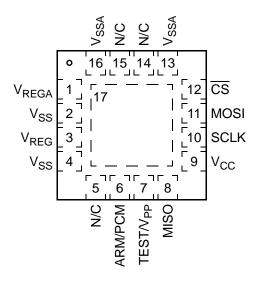

# 1.4 Pin Connections

Figure 5. 16-Pin QFN Package, Top View

**Table 2. Pin Description**

| Pin | Pin<br>Name              | Formal Name                | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----|--------------------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | V <sub>REGA</sub>        | Analog<br>Supply           | This pin is connected to the power supply for the internal analog circuitry. An external capacitor must be connected between this pin and $V_{SSA}$ . Reference Figure 1.                                                                                                                                                                                                                                                                                                                             |

| 2   | V <sub>SS</sub>          | Digital GND                | This pin is the power supply return node for the digital circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 3   | V <sub>REG</sub>         | Digital<br>Supply          | This pin is connected to the power supply for the internal digital circuitry. An external capacitor must be connected between this pin and $V_{SS}$ . Reference Figure 1.                                                                                                                                                                                                                                                                                                                             |

| 4   | V <sub>SS</sub>          | Digital GND                | This pin is the power supply return node for the digital circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5   | N/C                      | No Connect                 | No Connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

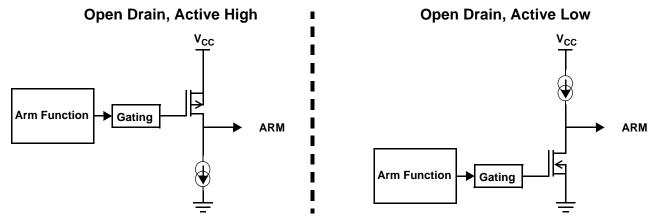

| 6   | ARM/<br>PCM              | Arm Output /<br>PCM Output | The function of this pin is configurable via the DEVCFG register as described in Section 3.1.6.5. When the arming output is selected, ARM can be configured as an open drain, active low output with a pullup current; or an open drain, active high output with a pulldown current. Alternatively, this pin can be configured as a digital output with a PCM signal proportional to the acceleration data. Reference Section 3.8.9 and Section 3.8.10. If unused, this pin must be left unconnected. |

| 7   | TEST/<br>V <sub>PP</sub> | Programming<br>Voltage     | This pin provides the power for factory programming of the OTP registers. This pin must be connected to $V_{SS}$ in the application.                                                                                                                                                                                                                                                                                                                                                                  |

| 8   | MISO                     | SPI Data Out               | This pin functions as the serial data output for the SPI port.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 9   | V <sub>CC</sub>          | Supply                     | This pin supplies power to the device. An external capacitor must be connected between this pin and V <sub>SS</sub> . Reference Figure 1.                                                                                                                                                                                                                                                                                                                                                             |

| 10  | SCLK                     | SPI Clock                  | This input pin provides the serial clock to the SPI port. An internal pulldown device is connected to this pin.                                                                                                                                                                                                                                                                                                                                                                                       |

| 11  | MOSI                     | SPI Data In                | This pin functions as the serial data input to the SPI port. An internal pulldown device is connected to this pin.                                                                                                                                                                                                                                                                                                                                                                                    |

| 12  | CS                       | Chip Select                | This input pin provides the chip select for the SPI port. An internal pullup device is connected to this pin.                                                                                                                                                                                                                                                                                                                                                                                         |

| 13  | V <sub>SSA</sub>         | Analog GND                 | This pin is the power supply return node for analog circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 14  | N/C                      | No Connect                 | No Connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 15  | N/C                      | No Connect                 | No Connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 16  | V <sub>SSA</sub>         | Analog GND                 | This pin is the power supply return node for analog circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 17  | PAD                      | Die Attach<br>Pad          | This pin is the die attach flag, and is internally connected to V <sub>SS</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     | Corner<br>Pads           | Corner Pads                | The corner pads are internally connected to V <sub>SS</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                         |

#### MMA685x

# **2 Electrical Characteristics**

# 2.1 Maximum Ratings

Maximum ratings are the extreme limits to which the device can be exposed without permanently damaging it.

| #              | Rating                                                                                      | Symbol                                                   | Value                         | Unit   |                   |

|----------------|---------------------------------------------------------------------------------------------|----------------------------------------------------------|-------------------------------|--------|-------------------|

| 1              | Supply Voltage                                                                              | V <sub>CC</sub>                                          | -0.3 to +7.0                  | V      | (3)               |

| 2              | C <sub>REG</sub> , C <sub>REGA</sub>                                                        | $V_{REG}$                                                | -0.3 to +3.0                  | V      | (3)               |

| 3              | SCLK, $\overline{\text{CS}}$ , MOSI, V <sub>PP</sub> /TEST                                  | V <sub>IN</sub>                                          | -0.3 to V <sub>CC</sub> + 0.3 | V      | (3)               |

| 4              | ARM                                                                                         | V <sub>IN</sub>                                          | -0.3 to V <sub>CC</sub> + 0.3 | V      | (3)               |

| 5              | MISO (high impedance state)                                                                 | V <sub>IN</sub>                                          | -0.3 to V <sub>CC</sub> + 0.3 | V      | (3)               |

| 6              | Acceleration without hitting internal g-cell stops                                          | g <sub>gcell_Clip</sub>                                  | ±500                          | g      | (3, 18)           |

| 7              | Acceleration without saturation of internal circuitry                                       | g <sub>ADC_Clip</sub>                                    | ±375                          | g      | (3)               |

| 8              | Powered Shock (six sides, 0.5 ms duration)                                                  | g <sub>pms</sub>                                         | ±1500                         | g      | (5, 18)           |

| 9              | Unpowered Shock (six sides, 0.5 ms duration)                                                | g <sub>shock</sub>                                       | ±2000                         | g      | (5, 18)           |

| 10             | Drop Shock (to concrete surface)                                                            | h <sub>DROP</sub>                                        | 1.2                           | m      | (5)               |

| 11<br>12<br>13 | Electrostatic Discharge Human Body Model (HBM) Charge Device Model (CDM) Machine Model (MM) | V <sub>ESD</sub><br>V <sub>ESD</sub><br>V <sub>ESD</sub> | ±2000<br>±750<br>±200         | V<br>V | (5)<br>(5)<br>(5) |

| 14             | Storage Temperature Range                                                                   | T <sub>stg</sub>                                         | -40 to +125                   | °C     | (5)               |

| 15             | Thermal Resistance - Junction to Case                                                       | $q_{\rm JC}$                                             | 2.5                           | °C/W   | (14)              |

# 2.2 Operating Range

The operating ratings are the limits normally expected in the application and define the range of operation.

| #        | Characteristic                                                      | Symbol            | Min                           | Тур                              | Max                          | Units |              |

|----------|---------------------------------------------------------------------|-------------------|-------------------------------|----------------------------------|------------------------------|-------|--------------|

| 16<br>17 | 3 3 3                                                               | V <sub>CC</sub>   | V <sub>L</sub><br>+3.135<br>— | V <sub>TYP</sub><br>+3.3<br>+5.0 | V <sub>H</sub><br>+5.25<br>— | V     | (15)<br>(15) |

| 18       | Operating Ambient Temperature Range<br>Verified by 100 % Final Test | T <sub>A</sub>    | T <sub>L</sub><br>-40         | _                                | T <sub>H</sub><br>+105       | С     | (1)          |

| 20       | Power-on Ramp Rate (V <sub>CC</sub> )                               | V <sub>CC_r</sub> | 0.000033                      | _                                | 3300                         | V/μs  | (19)         |

# 2.3 Electrical Characteristics - Power Supply and I/O

$V_L \leq (V_{CC} - V_{SS}) \leq V_H, \ T_L \leq T_A \leq T_H, \ |\Delta T_A| < 25 \ \text{K/min unless otherwise specified}$

| #                                            | Characteristic                                                                                                                                                                                                                                                                                                                                                                                                                                                |                          | Symbol                                                                | Min                                                    | Тур          | Max                                                       | Units                             |                                                                     |

|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-----------------------------------------------------------------------|--------------------------------------------------------|--------------|-----------------------------------------------------------|-----------------------------------|---------------------------------------------------------------------|

| 21                                           | Supply Current                                                                                                                                                                                                                                                                                                                                                                                                                                                | (4)                      | I <sub>DD</sub>                                                       | 3.0                                                    | _            | 7.0                                                       | mA                                | (1)                                                                 |

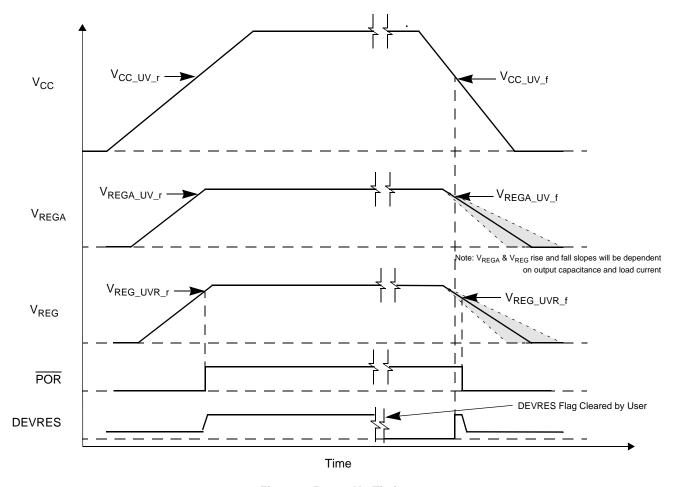

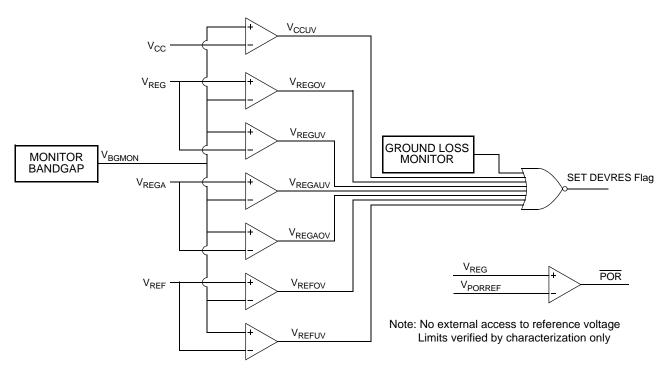

| 22<br>23<br>24<br>25<br>26<br>27<br>28<br>29 | Power Supply Monitor Thresholds (See Figure 9)  V <sub>CC</sub> Undervoltage (Falling)  V <sub>REG</sub> Undervoltage (Falling)  V <sub>REG</sub> Overvoltage (Rising)  V <sub>REGA</sub> Undervoltage (Falling)  V <sub>REGA</sub> Overvoltage (Rising)  Power Supply Monitor Hysteresis  V <sub>CC</sub> Undervoltage (Falling)  V <sub>REG</sub> Undervoltage, V <sub>REG</sub> Overvoltage  V <sub>REGA</sub> Undervoltage, V <sub>REGA</sub> Overvoltage | (4)<br>(4)<br>(4)<br>(4) | VCC_UV_f VREG_UV_f VREG_OV_r VREGA_UV_f VREGA_OV_r VHYST VHYST VHYST  | 2.74<br>2.10<br>2.65<br>2.20<br>2.65<br>65<br>20<br>20 |              | 3.02<br>2.25<br>2.85<br>2.35<br>2.85<br>110<br>210<br>150 | V<br>V<br>V<br>V<br>V<br>mV<br>mV | (3, 6)<br>(3, 6)<br>(3, 6)<br>(3, 6)<br>(3, 6)<br>(3)<br>(3)<br>(3) |

| 30<br>31<br>32                               | Power Supply RESET Thresholds (See Figure 6, and Figure 9)  V <sub>REG</sub> Undervoltage RESET (Falling)  V <sub>REG</sub> Undervoltage RESET (Rising)  V <sub>REG</sub> RESET Hysteresis                                                                                                                                                                                                                                                                    | (4)<br>(4)               | V <sub>REG_UVR_f</sub><br>V <sub>REG_UVR_r</sub><br>V <sub>HYST</sub> | 1.764<br>1.876<br>80                                   | _<br>_<br>_  | 2.024<br>2.152<br>140                                     | V<br>V<br>mV                      | (3, 6)<br>(3, 6)<br>(3)                                             |

| 33<br>34                                     | Internally Regulated Voltages VREG VREGA                                                                                                                                                                                                                                                                                                                                                                                                                      | (4)<br>(4)               | V <sub>REG</sub><br>V <sub>REGA</sub>                                 | 2.42<br>2.42                                           | 2.50<br>2.50 | 2.58<br>2.58                                              | V<br>V                            | (1, 3)<br>(1, 3)                                                    |

| 35<br>36                                     | External Filter Capacitor (C <sub>REG</sub> , C <sub>REGA</sub> ) Value ESR (including interconnect resistance)                                                                                                                                                                                                                                                                                                                                               |                          | C <sub>REG</sub><br>ESR                                               | 700<br>—                                               | 1000         | 1500<br>400                                               | nF<br>mΩ                          | (19)<br>(19)                                                        |

| 37<br>38                                     | Power Supply Coupling 50 kHz $\leq$ f <sub>n</sub> $\leq$ 300 kHz 4 MHz $\leq$ f <sub>n</sub> $\leq$ 100 MHz                                                                                                                                                                                                                                                                                                                                                  |                          |                                                                       |                                                        |              | 0.004<br>0.004                                            | LSB/mv<br>LSB/mv                  | (19)<br>(19)                                                        |

| 39<br>40                                     | Output High Voltage (MISO, PCM)<br>3.15 V $\leq$ (V <sub>CC</sub> - V <sub>SS</sub> ) $\leq$ 3.45 V (I <sub>Load</sub> = -1 mA)<br>4.75V $\leq$ (V <sub>CC</sub> - V <sub>SS</sub> ) $\leq$ 5.25 V (I <sub>Load</sub> = -1 mA)                                                                                                                                                                                                                                | (4)<br>(4)               | V <sub>OH_3</sub><br>V <sub>OH_5</sub>                                | V <sub>CC</sub> - 0.2<br>V <sub>CC</sub> - 0.4         | _            | _                                                         | V<br>V                            | (2, 3)<br>(2, 3)                                                    |

| 41<br>42                                     | Output Low Voltage (MISO PCM)<br>$3.15 \text{ V} \le (\text{V}_{CC} \cdot \text{V}_{SS}) \le 3.45 \text{ V} \text{ (I}_{Load} = 1 \text{ mA)}$<br>$4.75 \text{ V} \le (\text{V}_{CC} \cdot \text{V}_{SS}) \le 5.25 \text{ V} \text{ (I}_{Load} = 1 \text{ mA)}$                                                                                                                                                                                               | (4)<br>(4)               | $V_{\mathrm{OL}\_3} \ V_{\mathrm{OL}\_5}$                             |                                                        |              | 0.2<br>0.4                                                | V                                 | (2, 3)<br>(2, 3)                                                    |

| 43<br>44                                     | Open Drain Output High Voltage (ARM) 3.15 V $\leq$ (V <sub>CC</sub> - V <sub>SS</sub> ) $\leq$ 3.45 V (I <sub>ARM</sub> = -1 mA) 4.75 V $\leq$ (V <sub>CC</sub> - V <sub>SS</sub> ) $\leq$ 5.25 V (I <sub>ARM</sub> = -1 mA)                                                                                                                                                                                                                                  | (4)<br>(4)               | V <sub>ODH_3</sub><br>V <sub>ODH_5</sub>                              | V <sub>CC</sub> - 0.2<br>V <sub>CC</sub> - 0.4         |              | _<br>_                                                    | V<br>V                            | (2, 3)<br>(2, 3)                                                    |

|                                              | Open Drain Output Pulldown Current (ARM) 3.15 V $\leq$ (V <sub>CC</sub> - V <sub>SS</sub> ) $\leq$ 3.45 V (V <sub>ARM</sub> = 1.5 V) 4.75 V $\leq$ (V <sub>CC</sub> - V <sub>SS</sub> ) $\leq$ 5.25 V (V <sub>ARM</sub> = 1.5 V)                                                                                                                                                                                                                              | (4)<br>(4)               | I <sub>ODPD_3</sub><br>I <sub>ODPD_5</sub>                            | 50<br>50                                               |              | 100<br>100                                                | μΑ<br>μΑ                          | (2, 3)<br>(2, 3)                                                    |

| 47<br>48                                     | Open Drain Output Low Voltage (ARM) 3.15 V $\leq$ (V <sub>CC</sub> - V <sub>SS</sub> ) $\leq$ 3.45 V (I <sub>ARM</sub> = 1 mA) 4.75 V $\leq$ (V <sub>CC</sub> - V <sub>SS</sub> ) $\leq$ 5.25 V (I <sub>ARM</sub> = 1 mA)                                                                                                                                                                                                                                     | (4)<br>(4)               | V <sub>ODH_3</sub><br>V <sub>ODH_5</sub>                              |                                                        |              | 0.2<br>0.4                                                | V                                 | (2, 3)<br>(2, 3)                                                    |

|                                              | $\begin{array}{l} \text{Open Drain Output Pullup Current (ARM)} \\ 3.15 \ V \leq (V_{CC} \cdot V_{SS}) \leq 3.45 \ V \ (V_{ARM} = 1.5 \ V) \\ 4.75 \ V \leq (V_{CC} \cdot V_{SS}) \leq 5.25 \ V \ (V_{ARM} = 1.5 \ V) \end{array}$                                                                                                                                                                                                                            | (4)<br>(4)               | I <sub>ODPU_3</sub><br>I <sub>ODPU_5</sub>                            | -100<br>-100                                           |              | -50<br>-50                                                | μΑ<br>μΑ                          | (2, 3)<br>(2, 3)                                                    |

|                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                               | (4)                      | V <sub>IH</sub>                                                       | 2.0                                                    | _            | _                                                         | V                                 | (3, 6)                                                              |

|                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                               | (4)                      | V <sub>IL</sub>                                                       | _                                                      | _            | 1.0                                                       | V                                 | (3, 6)                                                              |

| 53                                           | Input Voltage Hysteresis CS, SCLK, MOSI                                                                                                                                                                                                                                                                                                                                                                                                                       | (4)                      | V <sub>I_HYST</sub>                                                   | 0.125                                                  | _            | 0.500                                                     | V                                 | (19)                                                                |

| 54<br>55                                     | Input Current High (at V <sub>IH</sub> ) ( <u>SC</u> LK, MOSI) Low (at V <sub>IL</sub> ) (CS)                                                                                                                                                                                                                                                                                                                                                                 | (4)<br>(4)               | I <sub>IH</sub><br>I <sub>IL</sub>                                    | -260<br>30                                             | –50<br>50    | -30<br>260                                                | μA<br>μA                          | (2, 3)<br>(2, 3)                                                    |

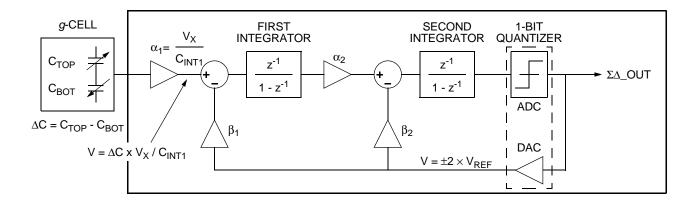

# 2.4 Electrical Characteristics - Sensor and Signal Chain

$V_L \leq (V_{CC} - V_{SS}) \leq V_H, \ T_L \leq T_A \leq T_H, \ |\Delta T_A| < 25 \ \text{K/min unless otherwise specified}$

| #                    | Characteristic                                                                                                                                |                          | Symbol                                                                                 | Min                                                   | Тур                                              | Max                                                   | Units                            |                                      |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|----------------------------------------------------------------------------------------|-------------------------------------------------------|--------------------------------------------------|-------------------------------------------------------|----------------------------------|--------------------------------------|

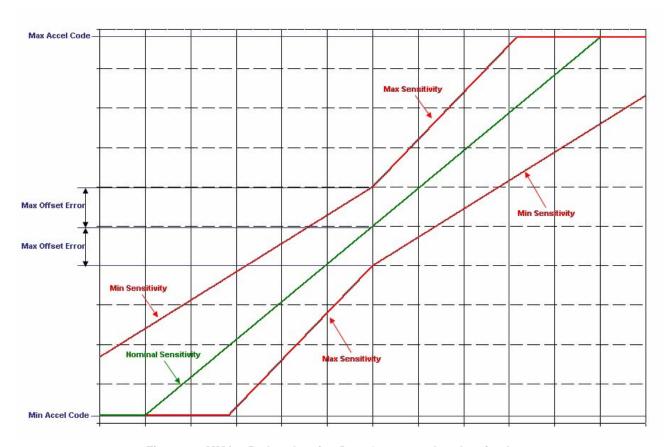

| 56<br>57<br>58<br>59 | 50 g (MMA6853)<br>60 g (MMA6856)                                                                                                              | (4)<br>(4)<br>(4)<br>(4) | SENS<br>SENS<br>SENS<br>SENS                                                           | _<br>_<br>_<br>_                                      | 20.479<br>9.766<br>8.192<br>4.096                | _<br>_<br>_<br>_                                      | LSB/g<br>LSB/g<br>LSB/g<br>LSB/g | (1, 9)<br>(1, 9)<br>(1, 9)<br>(1, 9) |

| 60<br>61<br>67       | $-40 \text{ °C} \le T_A \le 105 \text{ °C}$<br>$-40 \text{ °C} \le T_A \le 105 \text{ °C}, V_{CC\_UV\_f} \le V_{CC} - V_{SS} \le V_L$         | (4)<br>(4)               | ΔSENS<br>ΔSENS<br>ΔSENS                                                                | -4<br>-5<br>-5                                        |                                                  | +4<br>+5<br>+5                                        | %<br>%<br>%                      | (1)<br>(1)<br>(3)                    |

| 68<br>69<br>70<br>71 | 10-bits, signed   10-bits, unsigned, $V_{CC\_UV\_f} \le V_{CC} - V_{SS} \le V_L$ 10-bits, signed, $V_{CC\_UV\_f} \le V_{CC} - V_{SS} \le V_L$ | (4)<br>(4)               | OFFSET<br>OFFSET<br>OFFSET<br>OFFSET                                                   | 452<br>60<br>452<br>60                                | 512<br>0<br>512<br>0                             | 572<br>+60<br>572<br>+60                              | LSB<br>LSB<br>LSB<br>LSB         | (1)<br>(1)<br>(3)<br>(3)             |

| 72<br>73             | Offset Monitor Thresholds Positive Threshold (10-bits, unsigned) Negative Threshold (10-bits, unsigned)                                       |                          | OFFTHR <sub>POS</sub><br>OFFTHR <sub>NEG</sub>                                         |                                                       | 612<br>412                                       |                                                       | LSB<br>LSB                       | (7)<br>(7)                           |

| 74<br>75<br>76<br>77 | Range of Output (SPI, 10-bits, unsigned) Normal Fault Response Code Unused Codes Unused Codes                                                 |                          | RANGE<br>FAULT<br>UNUSED<br>UNUSED                                                     | 32<br>—<br>1<br>993                                   |                                                  | 992<br>—<br>31<br>1023                                | LSB<br>LSB<br>LSB<br>LSB         | (7)<br>(7)<br>(7)<br>(7)             |

| 78<br>79<br>80<br>81 | Range of Output (SPI, 10-bits, signed) Normal Fault Response Code Unused Codes Unused Codes                                                   |                          | RANGE<br>FAULT<br>UNUSED<br>UNUSED                                                     | -480<br><br>-511<br>481                               | _<br>-512<br>_<br>_                              | 480<br>—<br>–481<br>511                               | LSB<br>LSB<br>LSB<br>LSB         | (7)<br>(7)<br>(7)<br>(7)             |

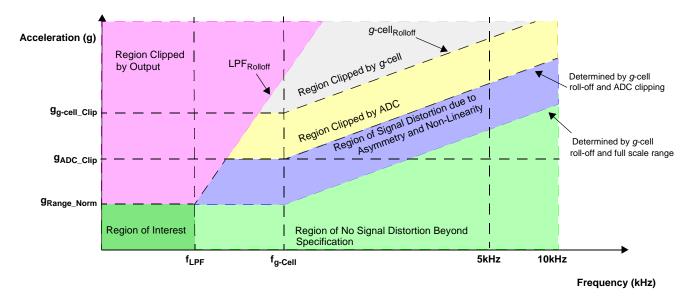

| 82                   | Nonlinearity                                                                                                                                  | (4)                      | NL <sub>OUT</sub>                                                                      | -1                                                    | _                                                | 1                                                     | % FSR                            | (3)                                  |

| 83<br>84             | System Output Noise<br>RMS (10-bit, All Ranges, 400 Hz, 4-pole LPF)<br>Peak to Peak (10-bit, All Ranges, 400 Hz, 4-pole LPF)                  |                          | n <sub>RMS</sub><br>n <sub>P-P</sub>                                                   |                                                       |                                                  | 0.5<br>1.0                                            | LSB<br>LSB                       | (3)<br>(3)                           |

| 85<br>86             | V <sub>YX</sub>                                                                                                                               | (4)<br>(4)               | $egin{array}{c} V_{ZX} \ V_{YX} \end{array}$                                           | -4<br>-4                                              |                                                  | +4<br>+4                                              | %<br>%                           | (3)<br>(3)                           |

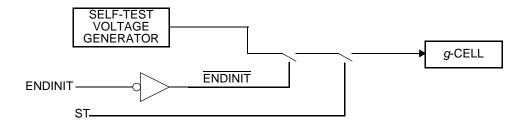

| 87<br>88<br>89<br>90 | STMAG = 0, -40 °C ≤ $I_A$ ≤ 105 °C<br>STMAG = 1, $T_A$ = 25 °C<br>STMAG = 1, -40 °C ≤ $T_A$ ≤ 105 °C<br>STMAG = 0, -40 °C ≤ $T_A$ ≤ 105 °C    | (4)<br>(4)<br>(4)<br>(4) | ΔST <sub>Low25</sub><br>ΔST <sub>Low</sub><br>ΔST <sub>HI25</sub><br>ΔST <sub>HI</sub> | ΔST <sub>MIN</sub><br>11.25<br>10.68<br>22.5<br>21.37 | ΔST <sub>NOM</sub><br>15<br>15<br>15<br>30<br>30 | ΔST <sub>MAX</sub><br>18.75<br>19.69<br>37.5<br>39.38 | g<br>g<br>g                      | (1)<br>(1)<br>(1)<br>(1)             |

| 92                   | $V_{CC\_UV\_f} \le V_{CC} - V_{SS} \le V_{L}$<br>STMAG = 1,-40 °C ≤ T <sub>A</sub> ≤ 105 °C                                                   |                          | ΔST <sub>Low</sub>                                                                     | 10.68                                                 | 15                                               | 19.69                                                 | g                                | (3)                                  |

|                      | $V_{CC\_UV\_f} \le V_{CC} - V_{SS} \le V_L$                                                                                                   |                          | ΔST <sub>HI</sub>                                                                      | 21.37                                                 | 30                                               | 39.38                                                 | g                                | (3)                                  |

| 93                   | Acceleration (without hitting internal <i>g</i> -cell stops) Any Range Positive/Negative                                                      |                          | g <sub>g-cell_Clip</sub>                                                               | 500                                                   | 560                                              | 600                                                   | g                                | (19)                                 |

# 2.5 Dynamic Electrical Characteristics - Signal Chain

$V_L \leq (V_{CC} - V_{SS}) \leq V_H, \ T_L \leq T_A \leq T_H, \ |\Delta T_A| < 25 \ \text{K/min unless otherwise specified}$

| #                                             | Characteristic                                                                                                                                                                                                                                                                 |                                               | Symbol                                                                                                                                                 | Min                                       | Тур                                                              | Max                                       | Units                                 |                                                                   |

|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|------------------------------------------------------------------|-------------------------------------------|---------------------------------------|-------------------------------------------------------------------|

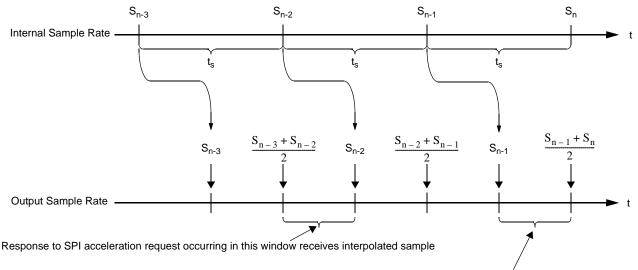

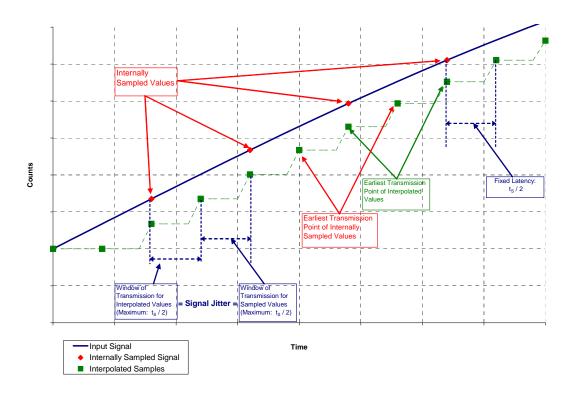

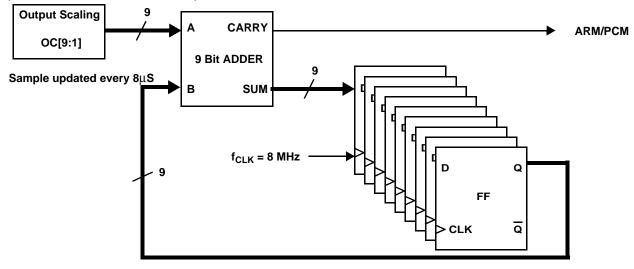

| 94<br>95<br>96                                | DSP Sample Rate (LPF 0,1,2,3,4,5) DSP Sample Rate (LPF 8,9,10,11,12,13) Interpolation Sample Rate                                                                                                                                                                              |                                               | t <sub>S</sub><br>t <sub>S</sub><br>t <sub>INTERP</sub>                                                                                                |                                           | 64/f <sub>OSC</sub><br>128/f <sub>OSC</sub><br>t <sub>S</sub> /2 | _<br>_<br>_                               | s<br>s<br>s                           | (7)<br>(7)<br>(7)                                                 |

| 97<br>98                                      | Datapath Latency (excluding $g$ -cell and Low Pass Filter) $T_S = 64/f_{OSC}$ $T_S = 128/f_{OSC}$                                                                                                                                                                              | (4)<br>(4)                                    | <sup>t</sup> DataPath_8<br><sup>t</sup> DataPath_16                                                                                                    | 33.0<br>51.9                              | 34.8<br>54.6                                                     | 36.5<br>57.4                              | μs<br>μs                              | (7, 16)<br>(7, 16)                                                |

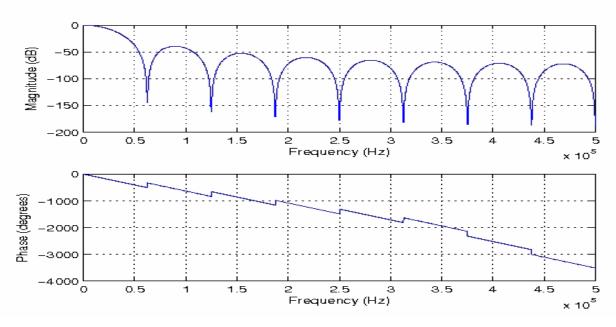

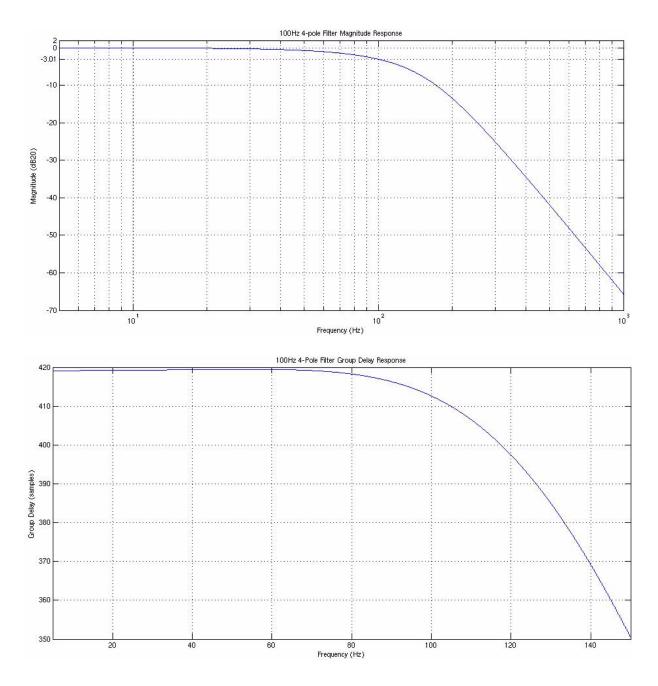

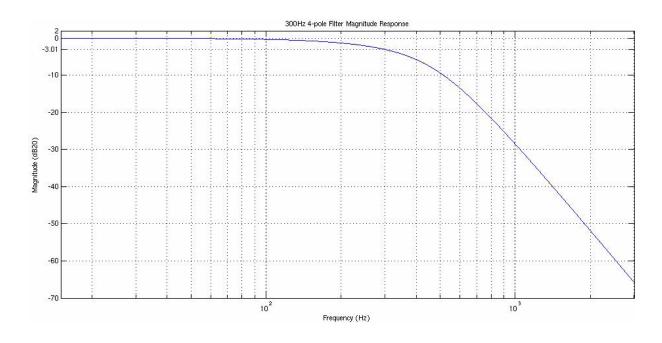

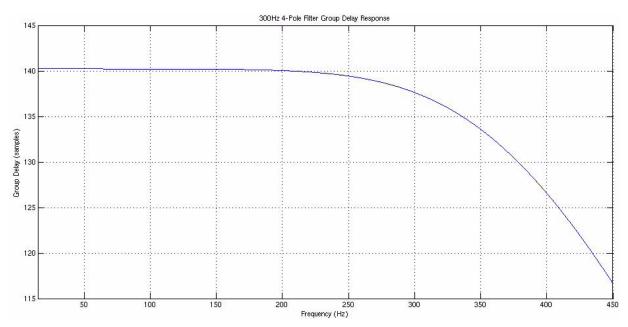

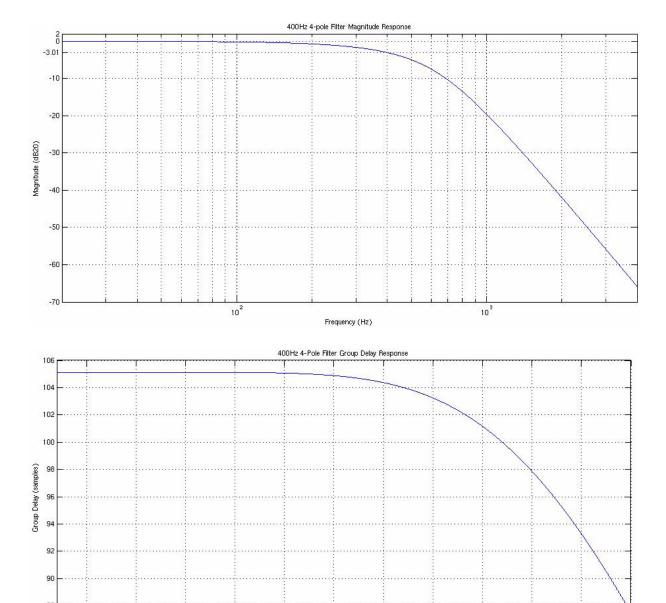

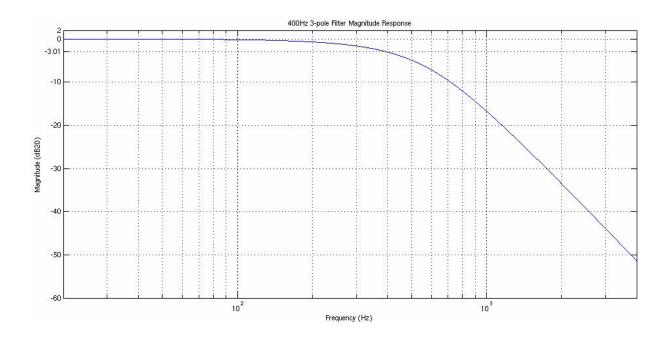

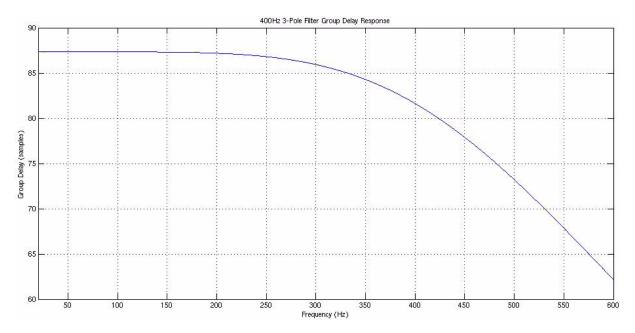

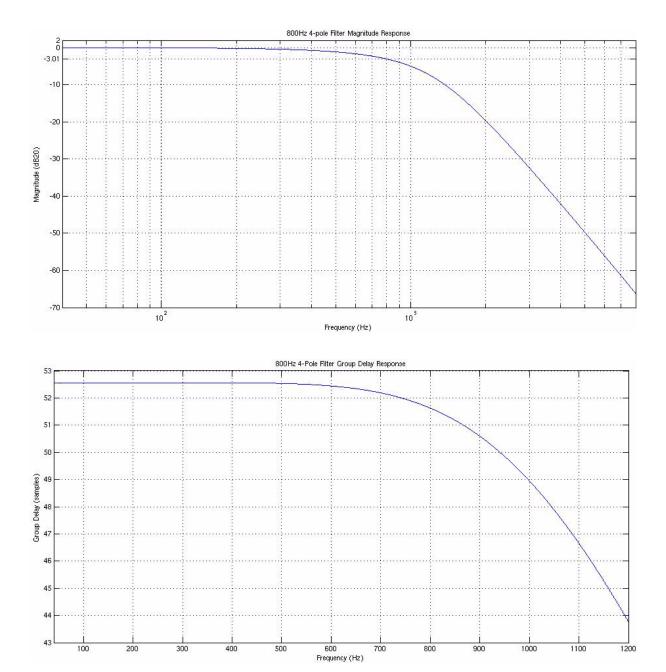

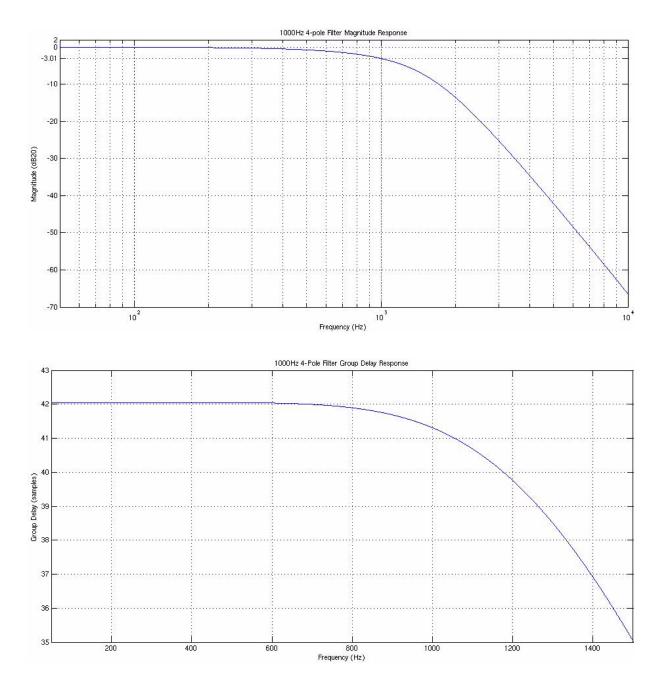

| 99<br>100<br>101<br>102<br>103<br>104         | Low-Pass Filter ( $t_s$ = 8 $\mu$ s)  Cutoff frequency 0: 100 Hz, 4-pole  Cutoff frequency 1: 300 Hz, 4-pole  Cutoff frequency 2: 400 Hz, 4-pole  Cutoff frequency 3: 800 Hz, 4-pole  Cutoff frequency 4: 1000 Hz, 4-pole  Cutoff frequency 5: 400 Hz, 3-pole                  | (4)<br>(4)<br>(4)<br>(4)<br>(4)<br>(4)        | fCO(LPF)<br>fC1(LPF)<br>fC2(LPF)<br>fC3(LPF)<br>fC4(LPF)<br>fC5(LPF)                                                                                   | 95<br>285<br>380<br>760<br>950<br>380     | 100<br>300<br>400<br>800<br>1000<br>400                          | 105<br>315<br>420<br>840<br>1050<br>420   | Hz<br>Hz<br>Hz<br>Hz<br>Hz<br>Hz      | (3, 7, 17)<br>(7, 17)<br>(7, 17)<br>(7, 17)<br>(7, 17)<br>(7, 17) |

| 105<br>106<br>107<br>108<br>109<br>110        | Low-Pass Filter (t <sub>s</sub> = 16µs) Cutoff frequency 8: 50 Hz, 4-pole Cutoff frequency 9: 150 Hz, 4-pole Cutoff frequency 10: 200 Hz, 4-pole Cutoff frequency 11: 400 Hz, 4-pole Cutoff frequency 12: 500 Hz, 4-pole Cutoff frequency 13: 200 Hz, 3-pole                   | (4)<br>(4)<br>(4)<br>(4)<br>(4)<br>(4)        | f <sub>C8</sub> (LPF)<br>f <sub>C9</sub> (LPF)<br>f <sub>C10</sub> (LPF)<br>f <sub>C11</sub> (LPF)<br>f <sub>C12</sub> (LPF)<br>f <sub>C13</sub> (LPF) | 47.5<br>142.5<br>190<br>380<br>475<br>190 | 50<br>150<br>200<br>400<br>500<br>200                            | 52.5<br>157.5<br>210<br>420<br>525<br>210 | Hz<br>Hz<br>Hz<br>Hz<br>Hz<br>Hz      | (7, 17)<br>(7, 17)<br>(7, 17)<br>(7, 17)<br>(7, 17)<br>(7, 17)    |

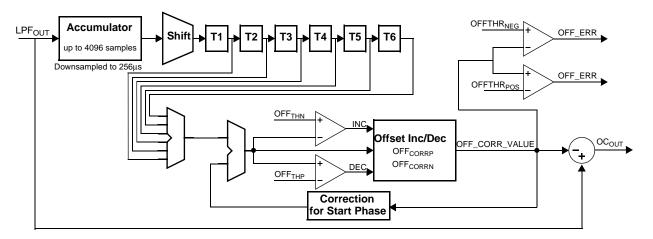

| 111<br>112<br>113<br>114<br>115<br>116<br>117 | Offset Cancellation (Normal Mode, 10-bit Output) Offset Averaging Period Offset Slew Rate Offset Update Rate Offset Correction Value per Update Positive Offset Correction Value per Update Negative Offset Correction Threshold Positive Offset Correction Threshold Negative | (4)<br>(4)<br>(4)<br>(4)<br>(4)<br>(4)<br>(4) | OFFAVEPER OFFSLEW OFFRATE OFFCORRP OFFCORRN OFFTHP OFFTHN                                                                                              |                                           | 6.291456<br>0.2384<br>1049<br>0.25<br>-0.25<br>0.125<br>0.125    |                                           | s<br>LSB/s<br>ms<br>LSB<br>LSB<br>LSB | (7)<br>(7)<br>(7)<br>(7)<br>(7)<br>(7)<br>(7)                     |

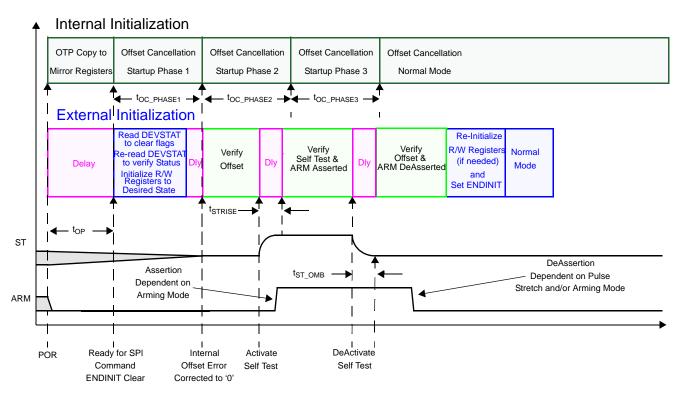

| 118                                           | Offset Monitor Bypass Time after Self-test Deactivation                                                                                                                                                                                                                        |                                               | t <sub>ST_OMB</sub>                                                                                                                                    | _                                         | 320                                                              | _                                         | t <sub>S</sub>                        | (3, 7)                                                            |

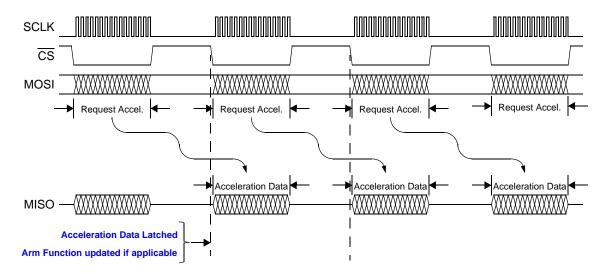

| 119                                           | Time Between Acceleration Data Requests                                                                                                                                                                                                                                        |                                               | t <sub>ACC_REQ</sub>                                                                                                                                   | 15                                        | _                                                                | _                                         | μs                                    | (3, 7, 20)                                                        |

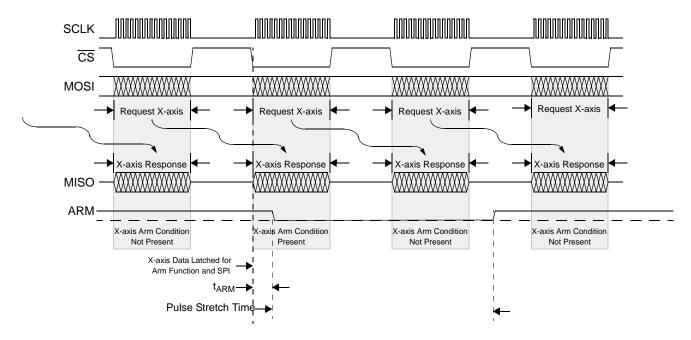

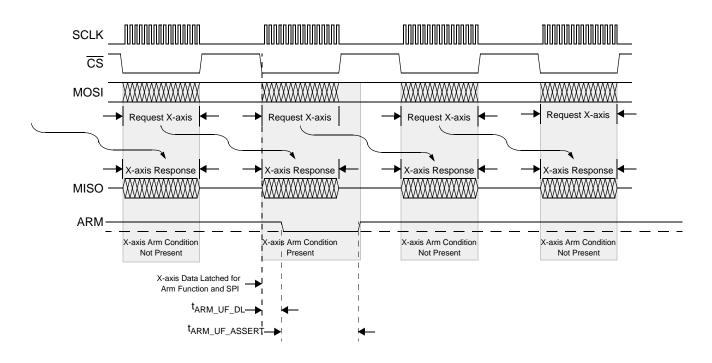

| 120<br>121<br>122                             | Arming Output Activation Time (ARM, I <sub>ARM</sub> = 200 μA) Moving Average and Count Arming Modes (2,3,4,5) Unfiltered Mode Activation Delay (Reference Figure 29) Unfiltered Mode Arm Assertion Time (Reference Figure 29)                                                 |                                               | t <sub>ARM</sub> tARM_UF_DLY tARM_UF_ASSERT                                                                                                            | 0<br>0<br>5.00                            |                                                                  | 1.05<br>1.05<br>6.579                     | μs<br>μs<br>μs                        | (3, 12)<br>(3, 12)<br>(3)                                         |

| 123                                           | Sensing Element Natural Frequency (−40 °C ≤ T <sub>A</sub> ≤ 105 °C)                                                                                                                                                                                                           |                                               | f <sub>gcell</sub>                                                                                                                                     | 10791                                     | _                                                                | 15879                                     | Hz                                    | (19)                                                              |

| 124                                           | Sensing Element Cutoff Frequency (–3 dB ref. to 0 Hz, –40 °C $\leq$ T <sub>A</sub> $\leq$ 105 °C)                                                                                                                                                                              |                                               | f <sub>gcell</sub>                                                                                                                                     | 0.851                                     | _                                                                | 2.29                                      | kHz                                   | (19)                                                              |

| 125                                           | Sensing Element Damping Ratio (−40 °C ≤ T <sub>A</sub> ≤ 105 °C)                                                                                                                                                                                                               |                                               | ζ <sub>gcell</sub>                                                                                                                                     | 2.46                                      |                                                                  | 9.36                                      | _                                     | (19)                                                              |

| 126                                           | Sensing Element Delay (@100 Hz, $-40$ °C $\leq$ T <sub>A</sub> $\leq$ 105 °C)                                                                                                                                                                                                  |                                               | f <sub>gcell_delay</sub>                                                                                                                               | 70                                        |                                                                  | 187                                       | μs                                    | (19)                                                              |

| 127                                           | Package Resonance Frequency                                                                                                                                                                                                                                                    |                                               | f <sub>Package</sub>                                                                                                                                   | 100                                       |                                                                  |                                           | kHz                                   | (19)                                                              |

| 128                                           | Package Quality Factor                                                                                                                                                                                                                                                         |                                               | q <sub>Package</sub>                                                                                                                                   | 1                                         | _                                                                | 5                                         |                                       | (19)                                                              |

# 2.6 Dynamic Electrical Characteristics - Supply and SPI

$V_L \le (V_{CC} - V_{SS}) \le V_H$ ,  $T_L \le T_A \le T_H$ ,  $|\Delta T_A| < 25$  K/min unless otherwise specified

| #                                                                                                     | Characteristic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                    | Symbol                                                                                                   | Min                                                | Тур    | Max         | Units                                    |                                                                                                 |

|-------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------|--------|-------------|------------------------------------------|-------------------------------------------------------------------------------------------------|

|                                                                                                       | Power-On Recovery Time (V <sub>CC</sub> = V <sub>CCMIN</sub> to first SPI access) Power-On Recovery Time (Internal POR to first SPI access)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                    | t <sub>OP</sub>                                                                                          | _                                                  | _      | 10<br>840   | ms<br>μs                                 | (3)<br>(3, 7)                                                                                   |

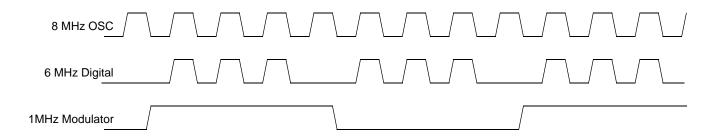

| 131<br>132                                                                                            | Internal Oscillator Frequency Test Frequency - Divided from Internal Oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | (4)                                                                | f <sub>OSC</sub><br>f <sub>OSCTST</sub>                                                                  | 7.6<br>0.95                                        | 8<br>1 | 8.4<br>1.05 | MHz<br>MHz                               | (7)<br>(1)                                                                                      |

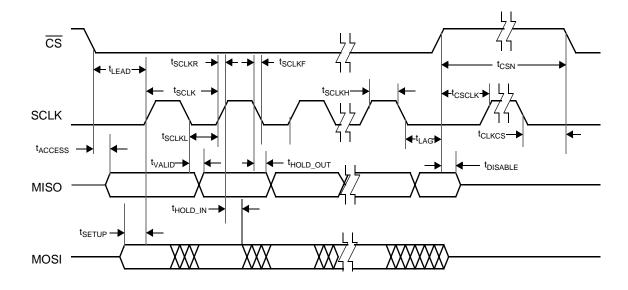

| 133<br>134<br>135<br>136<br>137<br>138<br>139<br>140<br>141<br>142<br>143<br>144<br>145<br>146<br>147 | Clock (SCLK) high time (90 % of $V_{CC}$ to 90 % of $V_{CC}$ ) Clock (SCLK) low time (10 % of $V_{CC}$ to 10 % of $V_{CC}$ ) Clock (SCLK) rise time (10 % of $V_{CC}$ to 90 % of $V_{CC}$ ) Clock (SCLK) fall time (90 % of $V_{CC}$ to 10 % of $V_{CC}$ ) $\overline{CS}$ asserted to SCLK high ( $\overline{CS}$ = 10 % of $V_{CC}$ to SCLK = 10 % of $V_{CC}$ ) $\overline{CS}$ asserted to MISO valid ( $\overline{CS}$ = 10 % of $V_{CC}$ to MISO = 10/90 % of $V_{CC}$ ) Data setup time (MOSI = 10/90 % of $V_{CC}$ to SCLK = 10 % of $V_{CC}$ ) MOSI Data hold time (SCLK = 90 % of $V_{CC}$ to MISO = 10/90 % of $V_{CC}$ ) MISO Data hold time (SCLK = 90 % of $V_{CC}$ to MISO = 10/90 % of $V_{CC}$ ) SCLK low to data valid (SCLK = 10 % of $V_{CC}$ to $\overline{CS}$ = 90 % of $V_{CC}$ ) SCLK low to $\overline{CS}$ high (SCLK = 10 % of $V_{CC}$ to $\overline{CS}$ = 90 % of $V_{CC}$ ) $\overline{CS}$ high to $\overline{CS}$ low ( $\overline{CS}$ = 90 % of $V_{CC}$ to $\overline{CS}$ = 90 % of $V_{CC}$ ) SCLK low to $\overline{CS}$ low ( $\overline{CS}$ = 90 % of $V_{CC}$ to $\overline{CS}$ = 90 % of $V_{CC}$ ) SCLK low to $\overline{CS}$ low ( $\overline{CS}$ = 90 % of $V_{CC}$ to $\overline{CS}$ = 90 % of $V_{CC}$ ) | (4)<br>(4)<br>(4)<br>(4)<br>(4)<br>(4)<br>(4)<br>(4)<br>(4)<br>(4) | tSCLK tSCLKH tSCLKL tSCLKR tSCLKF tLEAD tACCESS tSETUP tHOLD_IN tHOLD_OUT tVALID tLAG tCSN tCLKCS tCSCLK | 120<br>40<br>40<br>——————————————————————————————— |        |             | ns n | (3)<br>(3)<br>(19)<br>(19)<br>(3)<br>(3)<br>(3)<br>(3)<br>(3)<br>(3)<br>(3)<br>(3)<br>(3)<br>(3 |

- 1. Parameters tested 100 % at final test.

- 2. Parameters tested 100 % at wafer probe.

- 3. Parameters verified by characterization

- 4. Indicates a critical characteristic.

- Verified by qualification testing.

- 6. Parameters verified by pass/fail testing in production.

- Functionality guaranteed by modeling, simulation and/or design verification. Circuit integrity assured through IDDQ and scan testing. Timing is determined by internal system clock frequency.

- 8. N/A

- 9. Devices are trimmed at 100 Hz with 1000 Hz low-pass filter option selected. Response is corrected to 0 Hz response.

- 10. Low-pass filter cutoff frequencies shown are -3 dB referenced to 0 Hz response.

- 11. Power supply ripple at frequencies greater than 900 kHz should be minimized to the greatest extent possible.

- 12. Time from falling edge of  $\overline{\text{CS}}$  to ARM output valid.

- 13. N/A

- 14. Thermal resistance between the die junction and the exposed pad; cold plate is attached to the exposed pad.

- 15. Device characterized at all values of V<sub>L</sub> and V<sub>H</sub>. Production test is conducted at all typical voltages (V<sub>TYP</sub>) unless otherwise noted.

- 16. Data path Latency is the signal latency from *g*-cell to SPI output disregarding filter group delays.

- 17. Filter characteristics are specified independently, and do not include g-cell frequency response.

- 18. Electrostatic Deflection Test completed during wafer probe.

- 19. Verified by simulation.

- 20. Acceleration Data Request timing constraint only applies for proper operation of the Arming Function.

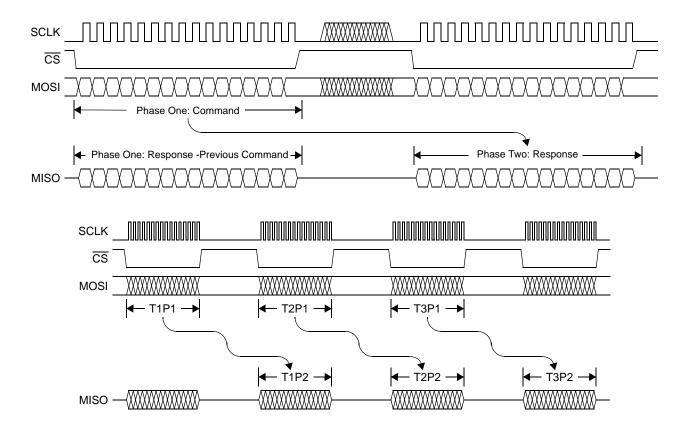

Figure 6. Power-Up Timing

Figure 7. Serial Interface Timing

# 3 Functional Description

# 3.1 Customer Accessible Data Array

A customer accessible data array allows for each device to be customized. The array consists of an OTP factory programmable block and read/write registers for device programmability and status. The OTP and writable register blocks incorporate independent CRC circuitry for fault detection (reference Section 3.2). The writable register block includes a locking mechanism to prevent unintended changes during normal operation. Portions of the array are reserved for factory-programmed trim values. The customer accessible data is shown in Table 3.

**Table 3. Customer Accessible Data**

|      | Location  |              |              |              | Bit Fu                | nction        |              |              |              | Туре  |

|------|-----------|--------------|--------------|--------------|-----------------------|---------------|--------------|--------------|--------------|-------|

| Addr | Register  | 7            | 6            | 5            | 4                     | 3             | 2            | 1            | 0            | Type  |

| \$00 | SN0       | SN[7]        | SN[6]        | SN[5]        | SN[4]                 | SN[3]         | SN[2]        | SN[1]        | SN[0]        |       |

| \$01 | SN1       | SN[15]       | SN[14]       | SN[13]       | SN[12]                | SN[11]        | SN[10]       | SN[9]        | SN[8]        | Ī     |

| \$02 | SN2       | SN[23]       | SN[22]       | SN[21]       | SN[20]                | SN[19]        | SN[18]       | SN[17]       | SN[16]       | 1     |

| \$03 | SN3       | SN[31]       | SN[30]       | SN[29]       | SN[28]                | SN[27]        | SN[26]       | SN[25]       | SN[24]       | Ī     |

| \$04 | Reserved  | Reserved     | Reserved     | Reserved     | Reserved              | Reserved      | Reserved     | Reserved     | Reserved     | F     |

| \$05 | Reserved  | Reserved     | Reserved     | Reserved     | Reserved              | Reserved      | Reserved     | Reserved     | Reserved     | Ī     |

| \$06 | FCTCFG    | STMAG        | 0            | 0            | 0                     | 0             | 0            | 0            | 0            | 1     |

| \$07 |           |              |              | Invalid Add  | dress: "Invalid Regis | ter Request"  |              |              |              | Ī     |

| \$08 | PN        | PN[7]        | PN[6]        | PN[5]        | PN[4]                 | PN[3]         | PN[2]        | PN[1]        | PN[0]        | 1     |

| \$09 |           |              |              | Invalid Add  | dress: "Invalid Regis | ter Request"  |              |              |              |       |

| \$0A | DEVCTL    | RES_1        | RES_0        | Reserved     | Reserved              | Reserved      | Reserved     | Reserved     | Reserved     |       |

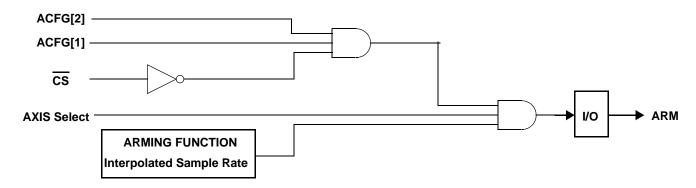

| \$0B | DEVCFG    | Reserved     | Reserved     | ENDINIT      | SD                    | OFMON         | A_CFG[2]     | A_CFG[1]     | A_CFG[0]     | Ī     |

| \$0C | DEVCFG_X  | ST           | Reserved     | Reserved     | Reserved              | LPF[3]        | LPF[2]       | LPF[1]       | LPF[0]       | 1     |

| \$0D |           |              |              | Invalid Add  | dress: "Invalid Regis | ter Request"  |              |              |              | Ī     |

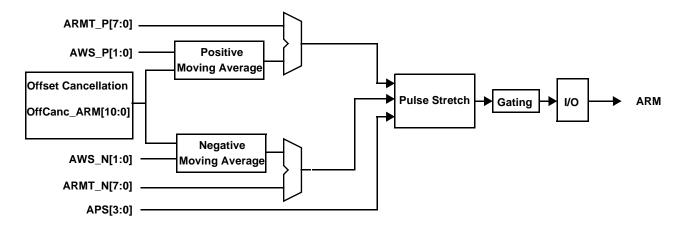

| \$0E | ARMCFG    | Reserved     | Reserved     | APS[1]       | APS[0]                | AWS_N[1]      | AWS_N[0]     | AWS_P[1]     | AWS_P[0]     | R/W   |

| \$0F |           |              |              | Invalid Add  | dress: "Invalid Regis | ster Request" |              |              |              | 10,00 |

| \$10 | ARMT_P    | AT_P[7]      | AT_P[6]      | AT_P[5]      | AT_P[4]               | AT_P[3]       | AT_P[2]      | AT_P[1]      | AT_P[0]      | 1     |

| \$11 |           |              |              | Invalid Add  | dress: "Invalid Regis | ter Request"  |              |              |              | Ī     |

| \$12 | ARMT_N    | AT_N[7]      | AT_N[6]      | AT_N[5]      | AT_N[4]               | AT_N[3]       | AT_N[2]      | AT_N[1]      | AT_N[0]      | 1     |

| \$13 |           |              |              | Invalid Add  | dress: "Invalid Regis | ter Request"  |              |              |              | Ī     |

| \$14 | DEVSTAT   | UNUSED       | IDE          | SDOV         | DEVINIT               | MISOERR       | 0            | OFFSET       | DEVRES       |       |

| \$15 | COUNT     | COUNT[7]     | COUNT[6]     | COUNT[5]     | COUNT[4]              | COUNT[3]      | COUNT[2]     | COUNT[1]     | COUNT[0]     | 1     |

| \$16 | OFFCORR_X | OFFCORR_X[7] | OFFCORR_X[6] | OFFCORR_X[5] | OFFCORR_X[4]          | OFFCORR_X[3]  | OFFCORR_X[2] | OFFCORR_X[1] | OFFCORR_X[0] | R     |

| \$17 |           |              |              | Invalid Add  | dress: "Invalid Regis | ter Request"  |              |              |              |       |

| \$1C | Reserved  | Reserved     | Reserved     | Reserved     | Reserved              | Reserved      | Reserved     | Reserved     | Reserved     | 1     |

| \$1D | Reserved  | Reserved     | Reserved     | Reserved     | Reserved              | Reserved      | Reserved     | Reserved     | Reserved     | 1     |

Type codes

F: Factory programmed OTP location

R/W: Read/write register

R: Read-only register

N/A: Not applicable

## 3.1.1 Device Serial Number Registers

A unique serial number is programmed into the serial number registers of each MMA685x device during manufacturing. The serial number is composed of the following information:

| Bit Range  | Content       |

|------------|---------------|

| S12 to S0  | Serial Number |

| S31 to S13 | Lot Number    |

Serial numbers begin at 1 for all produced devices in each lot, and are sequentially assigned. Lot numbers begin at 1 and are sequentially assigned. No lot will contain more devices than can be uniquely identified by the 13-bit serial number. Depending on lot size and quantities, all possible lot numbers and serial numbers may not be assigned.

The serial number registers are included in the OTP shadow register array CRC verification. Reference Section 3.2.1 for details regarding the CRC verification. Beyond this, the contents of the serial number registers have no impact on device operation or performance, and are only used for traceability purposes.

#### 3.1.2 Reserved Registers

These reserved registers are read-only and have no impact on device operation or performance.

**Table 4. Reserved Registers**

| Loca    | ation    | Bit      |          |          |          |          |          |          |          |  |  |

|---------|----------|----------|----------|----------|----------|----------|----------|----------|----------|--|--|

| Address | Register | 7        | 6        | 5        | 4        | 3        | 2        | 1        | 0        |  |  |

| \$04    | Reserved |  |  |

| \$05    | Reserved |  |  |

# 3.1.3 Factory Configuration Registers

The factory configuration register is a one time programmable, read only register which contains customer specific device configuration information that is programmed by NXP.

**Table 5. Factory Configuration Register**

| Loca    | ation    | Bit   |                  |  |  |  |  |  |   |

|---------|----------|-------|------------------|--|--|--|--|--|---|

| Address | Register | 7     | 7 6 5 4 3 2 1 0  |  |  |  |  |  | 0 |

| \$06    | FCTCFG   | STMAG | TMAG 0 0 0 0 0 0 |  |  |  |  |  | 0 |

#### 3.1.3.1 Self-test Magnitude Selection Bits (STMAG)

The self-test magnitude selection bits indicate if the nominal self-test deflection value is set to the low or high value as shown in the table below.

| STMAG | Full-Scale<br>Acceleration Range | Nominal Self-test Deflection Value<br>(Reference Section 2.4) |

|-------|----------------------------------|---------------------------------------------------------------|

| 0     | ≤ 60 <i>g</i>                    | $\Delta ST_Low$                                               |

| 1     | > 60 g                           | ΔST <sub>HI</sub>                                             |

# 3.1.4 Part Number Register (PN)

The part number register is a one time programmable, read only register which contains two digits of the device part number to identify the axis and range information. The contents of this register have no impact on device operation or performance.

**Table 6. Part Number Register**

| Loca    | ation    |       | Bit                                         |  |  |  |  |  |       |

|---------|----------|-------|---------------------------------------------|--|--|--|--|--|-------|

| Address | Register | 7     | 7 6 5 4 3 2 1 0                             |  |  |  |  |  |       |

| \$08    | PN       | PN[7] | PN[7] PN[6] PN[5] PN[4] PN[3] PN[2] PN[1] P |  |  |  |  |  | PN[0] |

| PN Regi | ster Value | Range                 |  |  |  |

|---------|------------|-----------------------|--|--|--|

| Decimal | HEX        | Reference Section 2.4 |  |  |  |

| 51      | \$33       | 20                    |  |  |  |

| 52      | \$34       | 35                    |  |  |  |

| 53      | \$35       | 50                    |  |  |  |

| 54      | \$36       | 75                    |  |  |  |

| 55      | \$37       | 100                   |  |  |  |

| 56      | \$38       | 60                    |  |  |  |

# 3.1.5 Device Control Register (DEVCTL)

The device control register is a read-write register which contains device control operations that can be applied during both initialization and normal operation.

**Table 7. Device Control Register**

| Loca    | ation    | Bit   |                                                                   |  |  |  |  |   |   |

|---------|----------|-------|-------------------------------------------------------------------|--|--|--|--|---|---|

| Address | Register | 7     | 7 6 5 4 3 2 1                                                     |  |  |  |  | 1 | 0 |

| \$0A    | DEVCTL   | RES_1 | RES_1 RES_0 Reserved Reserved Reserved Reserved Reserved Reserved |  |  |  |  |   |   |

| Reset   | Value    | 0     | 0 0 0 0 0 0                                                       |  |  |  |  | 0 |   |

# 3.1.5.1 Reset Control (RES\_1, RES\_0)

A series of three consecutive register write operations to the reset control bits in the DEVCTL register will cause a device reset. To reset the internal digital circuitry, the following register write operations must be performed in the order shown below. The register write operations must be consecutive SPI commands in the order shown or the device will not be reset.

| Register Write to DEVCTL | RES_1 | RES_0 | Effect       |

|--------------------------|-------|-------|--------------|

| SPI Register Write 1     | 0     | 0     | No Effect    |

| SPI Register Write 2     | 1     | 1     | No Effect    |

| SPI Register Write 3     | 0     | 1     | Device RESET |

The response to the Register Write returns '0' for RES\_1 and RES\_0. A Register Read of RES\_1 and RES\_0 returns '0' and terminates the reset sequence.

#### 3.1.5.2 Reserved Bits (DEVCTL[5:0])

Bits 5 through 0 of the DEVCTL register are reserved. A write to the reserved bits must always be logic '0' for normal device operation and performance.

# 3.1.6 Device Configuration Register (DEVCFG)

The device configuration register is a read/write register which contains data for general device configuration. The register can be written during initialization but is locked once the ENDINIT bit is set. This register is included in the writable register CRC check. Refer to Section 3.2.2 for details.

**Table 8. Device Configuration Register**

| Loca    | ation                    | Bit         |                                                                                                                       |  |  |   |   |  |  |

|---------|--------------------------|-------------|-----------------------------------------------------------------------------------------------------------------------|--|--|---|---|--|--|

| Address | Register                 | 7 6 5 4 3 2 |                                                                                                                       |  |  | 1 | 0 |  |  |

| \$0B    | DEVCFG                   | Reserved    | Reserved         Reserved         ENDINIT         SD         OFMON         A_CFG[2]         A_CFG[1]         A_CFG[0] |  |  |   |   |  |  |

| Reset   | eset Value 0 0 0 0 0 0 0 |             |                                                                                                                       |  |  | 0 |   |  |  |

#### 3.1.6.1 Reserved Bits (Reserved)

Bits 6 and 7 of the DEVCFG register are reserved. A write to the reserved bits must always be logic '0' for normal device operation and performance.

#### 3.1.6.2 End of Initialization Bit (ENDINIT)

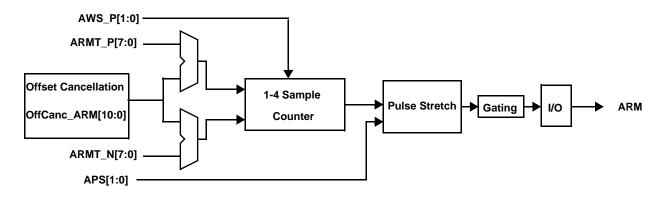

The ENDINIT bit is a control bit used to indicate that the user has completed all device and system level initialization tests, and that MMA685x will operate in normal mode. Once the ENDINIT bit is set, writes to all writable register bits are inhibited except for the DEVCTL register. Once written, the ENDINIT bit can only be cleared by a device reset. The writable register CRC check (reference Section 3.2.2) is only enabled when the ENDINIT bit is set.