# RENESAS

# DATASHEET

# ISL78220

#### 6-Phase Interleaved Boost PWM Controller with Light Load Efficiency Enhancement

FN7688 Rev 4.00 September 2, 2014

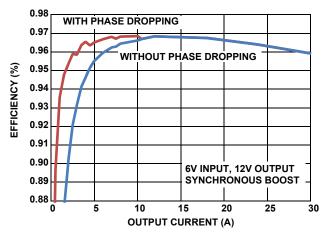

The ISL78220 6-phase controller is targeted for applications where high efficiency (>95%) and high power are required. The multiphase boost converter architecture uses interleaved timing to multiply channel ripple frequency and reduce input and output ripple. Lower ripple results in fewer input/output capacitors and therefore lower component cost and smaller implementation area.

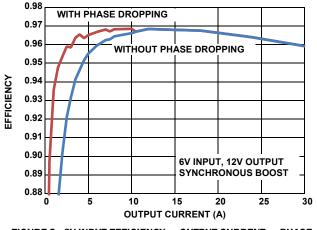

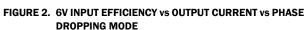

The ISL78220 has a dedicated pin to initiate the phase dropping scheme for higher efficiency at light load by dropping phases based on the load current, so the switching and core losses in the converter are reduced significantly. As the load increases, the dropped phase(s) are added back to accommodate heavy load transients and improve efficiency.

Input current is sensed continuously by measuring the voltage across a dedicated current sense resistor or by inductor DCR. This current sensing provides precision channel-current balancing, and per-phase overcurrent protection. A separate totalizing current limit function provides overcurrent protection for all the phases combined. This two-stage current protection provides maximum performance and circuit reliability.

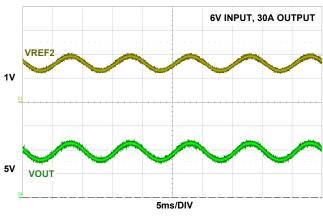

The ISL78220 can also provide for input voltage tracking via the VREF2 pin. The comparison reference voltage will be the lower of the VREF2 pin or the internal 2V reference. By using a resistor network between VIN and VREF2 pin, the output voltage can track input voltage to limit the output power during automotive cranking conditions.

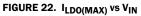

The ISL78220 can output a clock signal for expanding operation to 12 phases, which offers high system flexibility. The threshold-sensitive enable input is available to accurately coordinate the start-up of the ISL78220 with any other voltage rail.

# **Features**

- Peak current mode PWM control with adjustable slope compensation

- Precision resistor/DCR current sensing

- 2-, 3-, 4- or 6-phase operation

- Adjustable phase dropping/diode emulation/pulse skipping for high efficiency at light load

- Phase dropping facilitated with companion FET driver ISL78420 (featuring tri-level input control)

- Adjustable switching frequency or external synchronization from 75kHz up to 1MHz per phase

- Over-temperature/overvoltage protection

- 2V ±1.0% internal reference

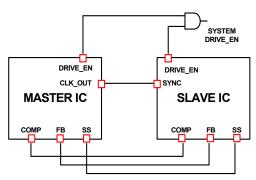

- Pb-free, 44 Ld 10x10 EP-TQFP package (RoHS compliant)

- -40°C to +125°C operating temperature range

- AEC-Q100 qualified

# **Applications**

- Automotive power supplies

- Start/stop DC/DC converter

- Electronic power steering systems (EPAS)

- Fuel pumps

- Injection system

- · Audio trunk amplifier power supplies

- · Telecom and industrial power supplies

### **Related Literature**

• <u>AN1726</u>, "ISL78220EVAL1Z: 6-Phase Interleaved Synchronous Boost Converter"

FIGURE 1. EFFICIENCY vs OUTPUT CURRENT vs PHASE DROPPING MODE

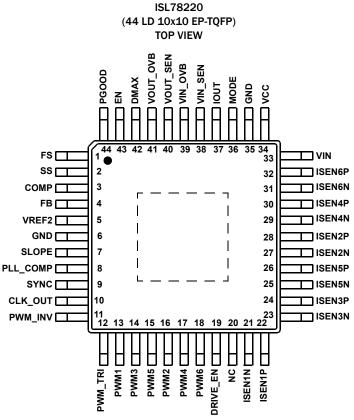

# **Pin Configuration**

## **Functional Pin Description**

| PIN # | SYMBOL   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                          |

|-------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | FS       | A resistor placed from FS to ground will set the PWM switching frequency.                                                                                                                                                                                                                                                                                                            |

| 2     | SS       | Use this pin to set-up the desired soft-start time. A capacitor placed from SS to ground will set up the soft-start ramp rate and in turn determine the soft-start time.                                                                                                                                                                                                             |

| 3     | COMP     | The output of the transconductance amplifier. Place the compensation network between COMP and GND for compensation loop design.                                                                                                                                                                                                                                                      |

| 4     | FB       | The inverting input of the transconductance amplifier. A resistor network should be placed between FB pin and output rail to set the output voltage.                                                                                                                                                                                                                                 |

| 5     | VREF2    | External reference input to the transconductance amplifier. When the VREF2 pin voltage drops below 1.8V, the internal reference will be shifted from 2V to VREF2. The VREF2 voltage can be programmed by connecting a resistor divider network from VCC or VIN.                                                                                                                      |

| 6     | GND      | Bias and reference ground for the IC.                                                                                                                                                                                                                                                                                                                                                |

| 7     | SLOPE    | This pin programs the slope of the internal slope compensation. A resistor should be connected from SLOPE pin to GND. Please refer to <u>"Adjustable Slope Compensation" on page 18</u> for how to choose the resistor value.                                                                                                                                                        |

| 8     | PLL_COMP | This pin serves as the compensation node for the PLL. A second order passive loop filter connected between PLL_COMP pin and GND compensates the PLL feedback loop.                                                                                                                                                                                                                   |

| 9     | SYNC     | Frequency synchronization pin. Connecting the SYNC pin to an external square pulse waveform (typically 20% to 80% duty cycle) will synchronize the converter switching frequency to the fundamental frequency of the input waveform. If SYNC function is not used, tie SYNC pin to GND. A 500nA current source is connected internally to pull-down the SYNC pin if it is left open. |

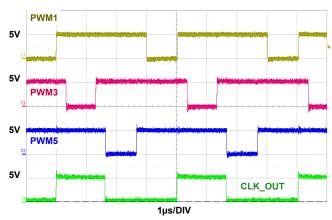

| 10    | CLK_OUT  | This pin provides a clock signal to synchronize with another ISL78220. This provides scalability and flexibility. The rising edge signal on the CLKOUT pin is in phase with the leading edge of the PWM1 signal.                                                                                                                                                                     |

| 11    | PWM_INV  | This pin determines the polarity of the PWM output signal. Pulling this pin to GND will force normal operation with inverting MOSFET drivers. Pulling this pin to VCC will invert the PWM signal for operation with non-inverting MOSFET drivers. This function provides the flexibility for the ISL78220 to work with different drivers.                                            |

# Functional Pin Description (Continued)

| PIN #                                                   | SYMBOL                                                                                                  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12                                                      | PWM_TRI                                                                                                 | This pin enables the tri-level of the PWM output signal. Pulling this pin to GND forces the PWM output to be traditional two level logic. Pulling the PWM_TRI pin to VCC will enable tri level PWM signals, then PWM output can be at the 2.5V tri level condition.                                                                                                                                                                                                              |

| 13, 14, 15,<br>16, 17, 18                               | PWM1, PWM3, PWM5,<br>PWM2, PWM4, PWM6                                                                   | Pulse width modulation outputs. Connect these pins to the PWM input pins of the external driver ICs. The number of active channels is determined by the state of PWM3, PWM4, PWM5 and PWM6. For 2-phase operation, connect PWM3 to VCC; similarly, connect PWM4 to VCC for 3-phase, connect PWM5 or PWM6 to VCC for 4-phase operation.                                                                                                                                           |

| 19                                                      | DRIVE_EN                                                                                                | Driver enable output pin. This pin is connected to the enable pin of MOSFET drivers.                                                                                                                                                                                                                                                                                                                                                                                             |

| 20                                                      | NC                                                                                                      | Not Connected – This pin is not electrically connected internally.                                                                                                                                                                                                                                                                                                                                                                                                               |

| 21, 22, 23,<br>24, 25, 26,<br>27, 28, 29,<br>30, 31, 32 | ISEN1N, ISEN1P, ISEN3N,<br>ISEN3P, ISEN5N, ISEN5P,<br>ISEN2N, ISEN2P, ISEN4N,<br>ISEN4P, ISEN6N, ISEN6P | The ISENxP and ISENxN pins are current sense inputs to individual differential amplifiers. The sensed current is<br>used as a reference for current mode control and overcurrent protection. Inactive channels should have their<br>respective ISENxN pins connected to VIN and ISENxP pins left open or tied to VIN. The ISL78220 utilizes external<br>sense resistor current sensing method or Inductor DCR sensing method.                                                    |

| 33                                                      | VIN                                                                                                     | Connect input rail to this pin. This pin is connected to the internal linear regulator, generating the power necessary to operate the chip. It is recommended the DC voltage applied to the VIN pin does not exceed 40V.                                                                                                                                                                                                                                                         |

| 34                                                      | VCC                                                                                                     | This pin is the output of the internal linear regulator that supplies the bias and gate voltage for the IC. A minimum $4.7\mu$ F decoupling ceramic capacitor should be connected from VCC to GND. The controller starts to operate when the voltage on this pin exceeds the rising POR threshold and shuts down when the voltage on this pin drops below the falling POR threshold. This pin can be connected directly to a +5V supply if VIN falls below 5.6V.                 |

| 35                                                      | GND                                                                                                     | Bias and reference ground for the IC.                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 36                                                      | MODE                                                                                                    | Mode selection pin. Pull this pin to logic HIGH for forced PWM mode; phase dropping/adding is inactive during forced PWM mode. Connecting a resistor from MODE pin to GND will initialize phase dropping mode (PDM). In PDM, a 5µA fixed reference current will flowing out of MODE pin, and the phase dropping threshold can be programmed by adjusting the resistor value.                                                                                                     |

| 37                                                      | IOUT                                                                                                    | IOUT is the current monitor pin with an additional OCP adjustment function. An RC network needs to be placed between IOUT and GND to ensure the proper operation. The voltage at the IOUT pin will be proportional to the input current. If the voltage on the IOUT pin is higher than 2V, the ISL78220 will go into overcurrent protection mode and the chip will latch off until the EN pin is toggled.                                                                        |

| 38                                                      | VIN_SEN                                                                                                 | The VIN_SEN pin is used for sensing the VIN voltage. A resistor divider network is connected between this pin and boost power stage input voltage rail. When the voltage on VIN_SEN is greater than 2.4V, the VIN_OVB pin will be pulled low to indicate an input overvoltage condition. The threshold voltage can be programmed by changing the divider ratios.                                                                                                                 |

| 39                                                      | VIN_OVB                                                                                                 | The VIN_OVB pin is an open drain indicator of an overvoltage condition at the input. When the voltage on the VIN_SEN pin is greater than the 2.4V threshold, the VIN_OVB pin will be pulled low.                                                                                                                                                                                                                                                                                 |

| 40                                                      | VOUT_SEN                                                                                                | The VOUT_SEN pin is used for sensing the output voltage, a resistor divider network is connected between this pin and output voltage rail. When the voltage on VOUT_SEN pin is greater than 2.4V, VOUT_OVB pin will be pulled low, indicating an output overvoltage condition.                                                                                                                                                                                                   |

| 41                                                      | VOUT_OVB                                                                                                | The VOUT_OVB pin is an open drain indicator of an overvoltage condition at the output. When the voltage on the VOUT_SEN pin is greater than the 2.4V threshold, the VOUT_OVB pin will be pulled low and latched, toggling VIN or EN will reset the latch.                                                                                                                                                                                                                        |

| 42                                                      | DMAX                                                                                                    | DMAX pin sets the maximum duty cycle of the PWM modulator. If the DMAX pin is connected to GND, the maximum duty cycle will be set to 91.7%. Floating this pin will limit the duty cycle to 75% and connecting the DMAX pin to VCC will limit the duty cycle to 83.3%.                                                                                                                                                                                                           |

| 43                                                      | EN                                                                                                      | This pin is a threshold-sensitive enable input for the controller. Connecting the power supply input to EN pin through an appropriate resistor divider provides a means to synchronize power-up of the controller and the MOSFET driver ICs. When EN pin is driven above 1.2V, the ISL78220 is active depending on status of the internal POR, and pending fault states. Driving EN pin below 1.1V will clear all fault states and the ISL78220 will soft-start when re-enabled. |

| 44                                                      | PGOOD                                                                                                   | This pin is used as an indication of the end of soft-start and output regulation. It is an open-drain logic output that is low impedance until the soft-start is completed. It will be pulled low again once the UV/OV/OC/OT conditions are detected.                                                                                                                                                                                                                            |

|                                                         | Exposed Pad                                                                                             | It is recommended to solder the Exposed Pad to the ground plane.                                                                                                                                                                                                                                                                                                                                                                                                                 |

# **Ordering Information**

| PART NUMBER<br>( <u>Notes 2, 3</u> ) | PART<br>MARKING                                                                                         | TEMP RANGE<br>(°C) | PACKAGE<br>(Pb-free) | PKG.<br>DWG. # |

|--------------------------------------|---------------------------------------------------------------------------------------------------------|--------------------|----------------------|----------------|

| ISL78220ANEZ ( <u>Note 1</u> )       | ISL78220 ANEZ                                                                                           | -40 to +125        | 44 Ld EP-TQFP        | Q44.10x10A     |

| ISL78220EVAL1Z                       | Evaluation Board: 6-phase synchronous boost (6V to 11V input, 12V, 30A output - see AN1726 for details) |                    |                      |                |

NOTES:

**1**. Add "-T\*" suffix for tape and reel. Please refer to <u>TB347</u> for details on reel specifications.

2. These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

3. For Moisture Sensitivity Level (MSL), please see device information page for ISL78220. For more information on MSL please see tech brief TB363.

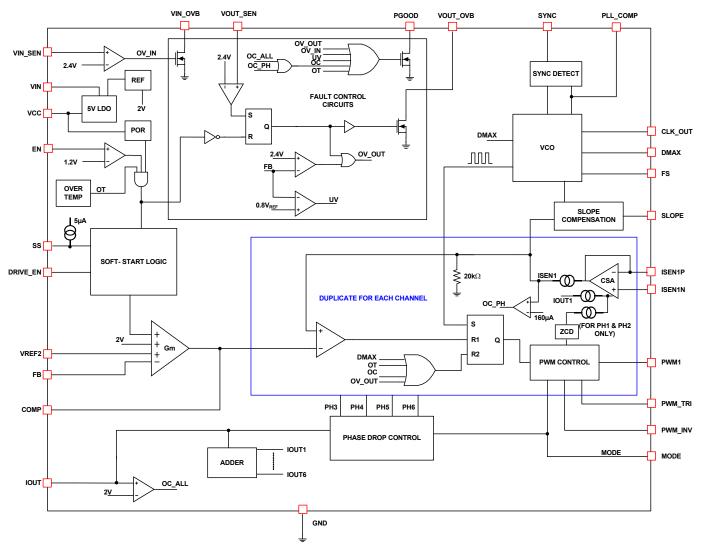

# ISL78220 Block Diagram

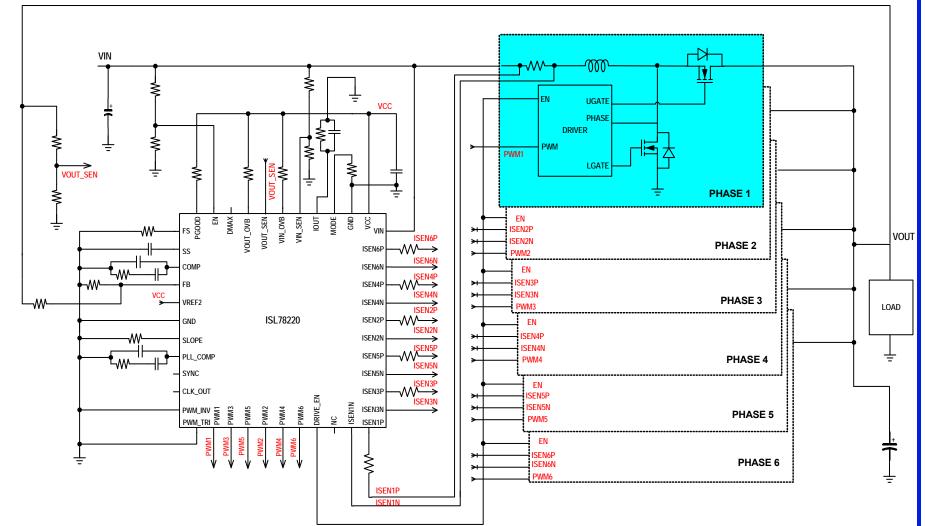

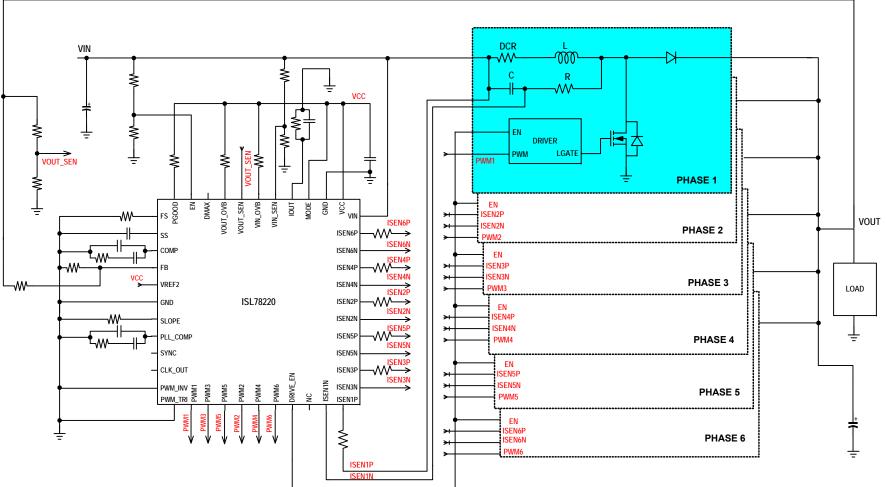

# **Typical Application 1: 6-Phase Synchronous Boost Converter with Sense Resistor Current** Sensing

ISL78220

NOTE: Please see ISL78420 for an Automotive Qualified 100V synchronous boost driver.

# Typical Application 2: 6-Phase Standard Boost Converter with DCR Current Sensing

#### **Absolute Maximum Ratings**

| Supply Voltage, VIN                                         |

|-------------------------------------------------------------|

| All Other Pins $\dots$ GND - 0.3V to V <sub>CC</sub> + 0.3V |

| ESD Rating                                                  |

| Human Body Model (Tested per JESD22-A114E)2.5kV             |

| Machine Model (Tested per JESD22-A115-A)                    |

| Charge Device Model (Tested per AEC-Q100-11) 1.5kV          |

| Latch-up (Tested per JESD78B, Class II, Level A) 100mA      |

#### **Thermal Information**

| Thermal Resistance (Typical)                | $\theta_{JA}$ (°C/W) | θ <b>JC</b> (°C∕W) |

|---------------------------------------------|----------------------|--------------------|

| 44 Ld EP-TQFP Package ( <u>Notes 4, 5</u> ) | 28                   | 2.5                |

| Maximum Junction Temperature                |                      | +150°C             |

| Maximum Storage Temperature Range           | 6                    | 5°C to +150°C      |

| Pb-Free Reflow Profile                      |                      | see <u>TB493</u>   |

#### **Operating Conditions**

| Voltage at VIN             | +5.6V to +40V          |

|----------------------------|------------------------|

| All ISEN_ Pins             | VIN - 5V to VIN + 0.3V |

| Voltage at VCC             | +5V ±5%                |

| Ambient Temperature (Auto) | 40°C to +125°C         |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTES:

4. θ<sub>JA</sub> is measured in free air with the component mounted on a high effective thermal conductivity test board with "direct attach" features. See Tech Brief <u>TB379</u>.

5. For  $\theta_{JC}$  the "case temp" location is the center of the exposed metal pad on the package underside.

**Electrical Specifications** Operating Conditions:  $V_{IN} = 12V$ ,  $T_A = -40$  °C to +125 °C, unless otherwise specified. Typical specifications are at  $T_A = +25$  °C. Boldface limits apply across the operating temperature range, -40 °C to +125 °C.

| PARAMETER                               | TEST CONDITIONS                                                                        | MIN<br>( <u>Note 6</u> ) | ТҮР                      | MAX<br>( <u>Note 6</u> ) | UNITS |

|-----------------------------------------|----------------------------------------------------------------------------------------|--------------------------|--------------------------|--------------------------|-------|

| SUPPLY INPUT                            |                                                                                        |                          | L                        |                          |       |

| Input Voltage Range                     |                                                                                        | 5.6                      | 12                       | 40                       | v     |

| Input Supply Current (Normal Mode)      | $V_{IN}$ = 12V, R <sub>FS</sub> = 158k $\Omega$ (For f <sub>S</sub> = 250kHz), EN = 5V |                          | 8                        | 12                       | mA    |

| Input Supply Current (Shutdown Mode)    | $V_{IN}$ = 12V, R <sub>FS</sub> = 158k $\Omega$ (For f <sub>S</sub> = 250kHz), EN = 0V |                          |                          | 10                       | μA    |

| INTERNAL LINEAR REGULATOR               |                                                                                        |                          | I.                       |                          |       |

| LDO Output Voltage (VCC Pin)            | $V_{IN}$ > 5.6V, C <sub>L</sub> = 4.7µF from VCC to GND, I <sub>VCC</sub> < 50mA       | 4.75                     | 5                        | 5.25                     | v     |

| LDO Current Limit (VCC pin)             | VCC = 3V, $C_L = 4.7 \mu F$ from VCC to GND                                            |                          | 200<br>( <u>Note 7</u> ) |                          | mA    |

| POWER-ON RESET (POR) AND ENABLE         |                                                                                        |                          | r.                       |                          |       |

| POR Threshold                           | VCC Rising                                                                             | 4.4                      | 4.5                      | 4.6                      | v     |

|                                         | VCC Falling                                                                            | 4.1                      | 4.2                      | 4.3                      | v     |

| EN Threshold                            | Rising                                                                                 | 1.1                      | 1.2                      | 1.3                      | v     |

|                                         | Hysteresis                                                                             |                          | 70                       |                          | mV    |

| OSCILLATOR                              |                                                                                        |                          | I.                       |                          |       |

| Accuracy of Switching Frequency Setting | R <sub>FS</sub> = 158kΩ from FS to GND                                                 | 225                      | 250                      | 275                      | kHz   |

| Adjustment Range of Switching Frequency |                                                                                        | 75                       |                          | 1000                     | kHz   |

| FS pin voltage                          |                                                                                        |                          | 1                        |                          | v     |

| SOFT-START                              |                                                                                        |                          | I.                       |                          |       |

| Soft-Start Current                      | C <sub>SS</sub> = 2.2nF from SS to GND                                                 | 4                        | 5                        | 6                        | μA    |

| Soft-Start Pre-Bias Voltage Range       |                                                                                        | 0                        |                          | 2                        | v     |

| Soft-Start Pre-Bias Voltage Accuracy    | V <sub>FB</sub> = 500mV                                                                | -25                      |                          | 25                       | mV    |

| Soft-Start Clamp Voltage                |                                                                                        |                          | 3.4                      |                          | v     |

| REFERENCE VOLTAGE                       |                                                                                        |                          | 1                        | 1                        |       |

| System Accuracy                         | -40°C to +125°C, measure at FB pin, V <sub>REF2</sub> > 2.5V                           | 1.98                     | 2                        | 2.02                     | v     |

| FB Pin Input Bias Current               | V <sub>FB</sub> = 2V, V <sub>REF2</sub> > 2.5V                                         | -1                       |                          | 1                        | μA    |

| VREF2 Pin Input Bias Current            | VREF2 = 1.6V                                                                           | -1                       |                          | 1                        | μA    |

FN7688 Rev 4.00 September 2, 2014

# **Electrical Specifications** Operating Conditions: $V_{IN} = 12V$ , $T_A = -40$ °C to +125 °C, unless otherwise specified. Typical specifications are at $T_A = +25$ °C. Boldface limits apply across the operating temperature range, -40 °C to +125 °C. (Continued) (Continued)

| PARAMETER                                                | TEST CONDITIONS                                                                                             | MIN<br>( <u>Note 6</u> ) | ТҮР                        | MAX<br>( <u>Note 6</u> ) | UNITS   |

|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|--------------------------|----------------------------|--------------------------|---------|

| V <sub>REF2</sub> External Reference Voltage Range       |                                                                                                             | 0.7                      |                            | 1.8                      | v       |

| VREF2 External Reference Voltage Accuracy                | -40°C to +125°C, measure at FB pin, VREF2 = 1.8V                                                            | -1                       |                            | 1                        | %       |

|                                                          | -40°C to +125°C, measure at FB pin, VREF2 = 0.7V                                                            | -1.5                     |                            | 1.5                      | %       |

| ERROR AMPLIFIER                                          |                                                                                                             |                          |                            |                          |         |

| Transconductance Gain                                    |                                                                                                             |                          | 2                          |                          | mS      |

| Output Impedance                                         |                                                                                                             |                          | 5                          |                          | MΩ      |

| Unity Gain Bandwidth                                     | C <sub>COMP</sub> = 100pF from COMP pin to GND                                                              |                          | 11                         |                          | MHz     |

| Slew Rate                                                | C <sub>COMP</sub> = 100pF from COMP pin to GND                                                              |                          | 2.5                        |                          | V/µs    |

| Output Current Capability                                |                                                                                                             |                          | ±300                       |                          | μA      |

| Maximum Output Voltage                                   |                                                                                                             | 3.5                      |                            |                          | v       |

| Minimum Output Voltage                                   |                                                                                                             |                          |                            | 0.5                      | v       |

| PWM CORE                                                 |                                                                                                             |                          |                            |                          |         |

| Duty Cycle Matching                                      | $I_{ISENxP} = 60\mu$ A, $R_{SLOPE} = 30.1$ k, $f_S = 250$ kHz,<br>$V_{COMP} = 2$ V, 6-phase, $T_A = +25$ °C | -6                       |                            | 6                        | %       |

| Zero Crossing Detection (ZCD) Threshold for<br>PWM1/PWM2 | R <sub>SEN1, 2</sub> = 750Ω                                                                                 |                          | 3                          |                          | mV      |

| Leading Edge Blanking (Audio Mode)                       | $V_{MODE} = VCC, V_{PWM_{TRI}} = VCC, V_{COMP} = 0.5V$                                                      |                          | Ts/12<br>( <u>Note 8</u> ) |                          | ns      |

| Leading Edge Blanking (Other Mode)                       | V <sub>MODE</sub> <4V or V <sub>PWM_TRI</sub> = GND, V <sub>COMP</sub> = 0.5V                               |                          | 130                        |                          | ns      |

| SLOPE pin Voltage                                        |                                                                                                             | 385                      | 515                        | 650                      | mV      |

| SENxN Bias Current                                       | V <sub>ISENxN</sub> = V <sub>ISENxP</sub> , from V <sub>IN</sub> - 1V to V <sub>IN</sub>                    |                          | 0.3                        |                          | μA      |

| SENxN, ISENxP Common Mode Voltage Range                  | V <sub>IN</sub> > 12V                                                                                       | V <sub>IN</sub> - 5      |                            | VIN                      | v       |

| PWMx OUTPUT                                              |                                                                                                             | 4                        | I                          | 1                        | 1       |

| PWMx Output Voltage LOW                                  | I <sub>PWMx</sub> = -500μA                                                                                  |                          |                            | 0.5                      | v       |

| PWMx Output Voltage HIGH                                 | I <sub>PWMx</sub> = +500μA                                                                                  | 4.5                      |                            |                          | v       |

| PWMx Tri-State Output Voltage                            | $I_{PWMx} = \pm 100 \mu A$                                                                                  | 2.3                      | 2.5                        | 2.7                      | v       |

| PWMx Pull-Down Current                                   | During Phase Detection Time ( $t_3$ on Figure 14), $V_{PWM}$ = 1V                                           |                          | 50                         |                          | μA      |

| PWM3 - PWM6 Disable Threshold                            | During Phase Detection Time (t <sub>3</sub> on Figure 14)                                                   | 3.5                      |                            |                          | v       |

| PHASE ADDING/DROPPING                                    |                                                                                                             |                          |                            |                          |         |

| MODE Pull-up Current                                     | V <sub>MODE</sub> = 2.4V                                                                                    | 4.2                      | 5.1                        | 6                        | μA      |

| VIOUT Threshold, 6-phase, Drop Phase 5/6                 | $V_{MODE} = 2.4V$                                                                                           | 1.575                    | 1.6                        | 1.625                    | v       |

| V <sub>IOUT</sub> Threshold, 6-phase, Drop Phase 4       | $V_{MODE} = 2.4V$                                                                                           | 1.175                    | 1.2                        | 1.225                    | v       |

| V <sub>IOUT</sub> Threshold, 6-phase, Drop Phase 3       | V <sub>MODE</sub> = 2.4V                                                                                    | 0.775                    | 0.8                        | 0.825                    | v       |

| V <sub>IOUT</sub> Threshold, 4-phase, Drop Phase 4       | V <sub>MODE</sub> = 1.6V                                                                                    | 1.175                    | 1.2                        | 1.225                    | v       |

| V <sub>IOUT</sub> Threshold, 4-phase, Drop Phase 3       | V <sub>MODE</sub> = 1.6V                                                                                    | 0.775                    | 0.8                        | 0.825                    | v       |

| / <sub>IOUT</sub> Threshold, 3-phase, Drop Phase 3       | V <sub>MODE</sub> = 1.8V                                                                                    | 1.175                    | 1.2                        | 1.225                    | v       |

| V <sub>IOUT</sub> Threshold Hysteresis                   |                                                                                                             |                          | 40                         |                          | mV      |

| Phase Drop Disable Threshold at MODE pin                 |                                                                                                             | 3.5                      | 4                          |                          | v       |

| CURRENT SENSE AND OVERCURRENT PROTECTIO                  | <br>DN                                                                                                      |                          |                            |                          |         |

| Peak Current Limit for Individual Channel                |                                                                                                             |                          | 160                        |                          | μA      |

| OUT Current Tolerance                                    | I <sub>ISENxP</sub> = 60μA, 6-phase                                                                         | 260                      | 280                        | 300                      | μΑ      |

| Maximum Voltage Limit at IOUT Pin                        |                                                                                                             | 200                      | 2.0                        |                          | μA<br>V |

# **Electrical Specifications** Operating Conditions: $V_{IN} = 12V$ , $T_A = -40$ °C to +125 °C, unless otherwise specified. Typical specifications are at $T_A = +25$ °C. Boldface limits apply across the operating temperature range, -40 °C to +125 °C. (Continued) (Continued)

| PARAMETER                              | TEST CONDITIONS                                              | MIN<br>( <u>Note 6</u> ) | ТҮР  | MAX<br>( <u>Note 6</u> ) | UNIT |

|----------------------------------------|--------------------------------------------------------------|--------------------------|------|--------------------------|------|

| DMAX PIN                               |                                                              |                          |      |                          |      |

| DMAX Threshold, High                   |                                                              | 3                        |      |                          | v    |

| DMAX Threshold, Low                    |                                                              |                          |      | 2                        | v    |

| DMAX Floating Voltage                  | During phase detection time (t <sub>3</sub> on Figure 14)    |                          | 2.5  |                          | v    |

| Max Duty Cycle, DMAX = GND             | V <sub>COMP</sub> = 3.5V                                     |                          | 91.7 |                          | %    |

| Max Duty Cycle, DMAX = FLOAT           | V <sub>COMP</sub> = 3.5V                                     |                          | 75   |                          | %    |

| Max Duty Cycle, DMAX = VCC             | V <sub>COMP</sub> = 3.5V                                     |                          | 83.3 |                          | %    |

| DMAX Source/Sink Current               | During t <sub>3</sub> on Figure 14                           |                          | 50   |                          | μA   |

| DMAX Source/Sink Current               | After t <sub>3</sub> on Figure 14                            | -1                       |      | 1                        | μA   |

| PWM_TRI, PWM_INV, SYNC PIN DIGITAL LOG |                                                              |                          |      | 4                        |      |

| Input Leakage Current                  | EN < 1V                                                      | -1                       |      | 1                        | μA   |

| Input Pull-Down Current                | EN > 2V, Pin Voltage = 2.1V                                  |                          | 0.4  | 1.5                      | μA   |

| Logic Input Low                        |                                                              |                          |      | 0.8                      | ٧    |

| Logic Input High                       |                                                              | 2                        |      |                          | ۷    |

| DRIVE_EN, CLK_OUT PIN                  |                                                              | U                        |      | -                        | 1    |

| Output High Voltage                    | I <sub>DRIVE_EN</sub> = 500μA                                | 4.5                      |      |                          | ٧    |

| Output Low Voltage                     | I <sub>DRIVE_EN</sub> = -500μA                               |                          |      | 0.5                      | ٧    |

| VOUT SENSE PIN                         |                                                              | U                        |      | -                        | 1    |

| Input Leakage Current                  |                                                              | -1                       |      | 1                        | μA   |

| Threshold Voltage                      |                                                              | 2.325                    | 2.4  | 2.475                    | ٧    |

| VIN SENSE PIN                          | <u> </u>                                                     | I                        |      |                          | 1    |

| Input Leakage Current                  |                                                              | -1                       |      | 1                        | μA   |

| Threshold Voltage                      |                                                              | 2.325                    | 2.4  | 2.475                    | v    |

| Hysteresis                             |                                                              |                          | 110  |                          | mV   |

| VOUT_OVB, VIN_OVB PIN                  |                                                              | i                        |      |                          |      |

| Leakage Current                        | V <sub>PIN</sub> = High                                      |                          |      | 1                        | μA   |

| Low Voltage                            | I <sub>PIN</sub> = 0.5mA                                     |                          |      | 0.2                      | v    |

| POWER-GOOD MONITOR PIN                 |                                                              | i                        |      |                          |      |

| PGOOD Leakage Current                  | PGOOD = High                                                 |                          |      | 1                        | μA   |

| PGOOD Low Voltage                      | I <sub>PGOOD</sub> = 0.5mA                                   |                          |      | 0.2                      | v    |

| Overvoltage Rising Trip Point          | V <sub>FB</sub> /V <sub>REF</sub> , V <sub>REF2</sub> > 2.5V | 117                      | 120  | 123                      | %    |

| Overvoltage Rising Hysteresis          | V <sub>FB</sub> /V <sub>REF</sub> , V <sub>REF2</sub> > 2.5V |                          | 5    |                          | %    |

| Undervoltage Rising Trip Point         | V <sub>FB</sub> /V <sub>REF</sub> , V <sub>REF2</sub> > 2.5V | 77                       | 80   | 83                       | %    |

| Undervoltage Rising Hysteresis         | V <sub>FB</sub> /V <sub>REF</sub> , V <sub>REF2</sub> > 2.5V |                          | 5    |                          | %    |

| OVER-TEMPERATURE PROTECTION            | · · · · · · · · · · · · · · · · · · ·                        | I I                      |      |                          |      |

| Over-Temperature Trip Point            |                                                              |                          | 160  |                          | °C   |

| Over-Temperature Recovery Threshold    |                                                              |                          | 145  |                          | °C   |

NOTES:

6. Parameters with MIN and/or MAX limits are 100% tested at +25 °C, unless otherwise noted. Compliance to datasheet limits is assured by one or more methods: production test, characterization and/or design.

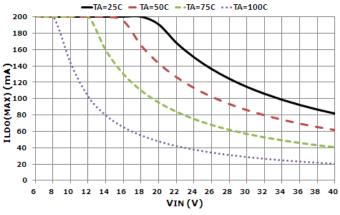

7. Please refer to LDO current derating curve in <u>"Internal 5V LDO Output Current Limit Derating Curves" on page 19</u> for IMAX vs VIN.

8. Ts = switching period = 1/(switching frequency).

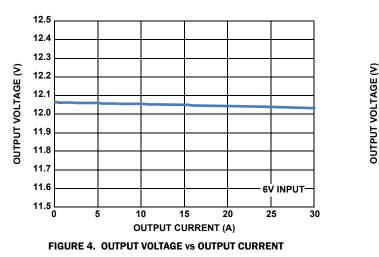

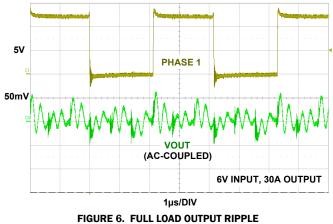

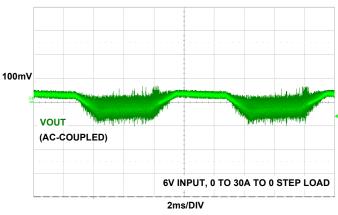

# **Typical Performance Curves**

0.99

12.5

12.4 12.3

12.2 12.1

12.0 11.9

11.8

11.7

11.6

11.5

6

7

FIGURE 3. 11V INPUT EFFICIENCY vs OUTPUT CURRENT vs PHASE DROPPING MODE

8

FIGURE 5. OUTPUT VOLTAGE vs INPUT VOLTAGE

**INPUT VOLTAGE (V)**

9

**30A OUTPUT**

11

10

# Typical Performance Curves (Continued)

FIGURE 12. MODULATING VREF2 INPUT

# **Operation Description**

#### **Multiphase Power Conversion**

The technical challenges associated with producing a single-phase converter, which is both cost-effective and thermally viable for high power applications have forced a change to the cost-saving approach of multiphase solution. The ISL78220 controller helps reduce the complexity of implementation by integrating vital functions and requiring minimal output components.

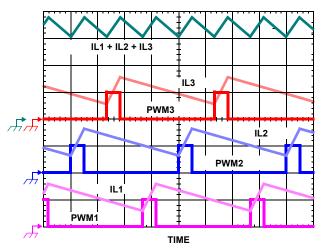

#### Interleaving

The switching of each channel in a multiphase converter is timed to be symmetrically out-of-phase with each of the other channels. Take a 3-phase converter for example, each channel switches 1/3 cycle after the previous channel and 1/3 cycle before the following channel. As a result, the three-phase converter has a combined ripple frequency three times greater than the ripple frequency of any one phase. In addition, the peak-to-peak amplitude of the combined inductor current is reduced in proportion to the number of phases (Equations 1 and 2). The increased ripple frequency and the lower ripple amplitude mean that the designer can use less per-channel inductance and lower total input and output capacitance for any performance specification.

Figure 13 illustrates the multiplicative effect on input ripple current. The three channel currents ( $I_{L1}$ ,  $I_{L2}$ , and  $I_{L3}$ ) combine to form the AC ripple current and the DC input current. The ripple component has three times the ripple frequency of each individual channel current. Each PWM pulse is triggered 1/3 of a cycle after the start of the PWM pulse of the previous phase.

To understand the reduction of the ripple current amplitude in the multiphase circuit, examine the equation representing an individual channel's peak-to-peak inductor current.

In Equation 1,  $V_{IN}$  and  $V_{OUT}$  are the input and the output voltages respectively, L is the single-channel inductor value, and  $f_S$  is the switching frequency.

$$I_{P-P} = \frac{(V_{OUT} - V_{IN})V_{IN}}{Lf_S V_{OUT}}$$

(EQ. 1)

The input capacitors conduct the ripple component of the inductor current. In the case of multiphase converters, the capacitor current is the sum of the ripple currents from each of the individual channels. Compare Equation 1 to the expression for the peak-to-peak current after the summation of N symmetrically phase-shifted inductor currents in Equation 2. Peak-to-peak ripple current decreases by an amount proportional to the number of channels. Reducing the inductor ripple current allows the designer to use fewer or less costly input capacitors.

$$I_{C(P-P)} = \frac{(V_{OUT} - N V_{IN}) V_{IN}}{Lf_{S} V_{OUT}}$$

(EQ. 2)

FIGURE 13. PWM AND INDUCTOR-CURRENT WAVEFORMS FOR 3-PHASE CONVERTER

#### **PWM Operations**

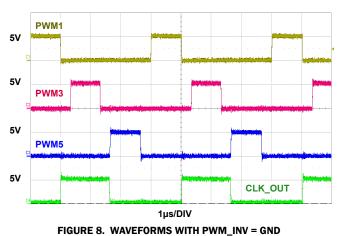

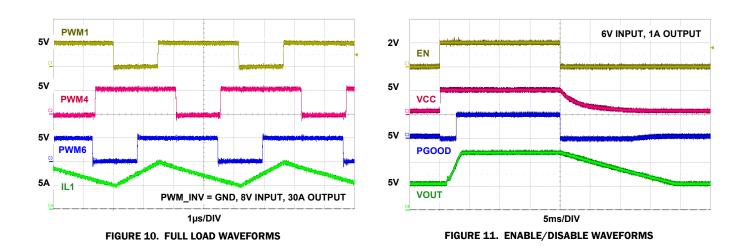

The timing of each channel is set by the total number of active channels. The default channel setting for the ISL78220 is 6, and the switching cycle is defined as the time between PWM pulse initiation signals of each channel. The cycle time of the pulse initiation signal is the inversion of the switching frequency set by the resistor between the FS pin and ground. The PWM signals command the MOSFET drivers to turn on/off the channel MOSFETs. Normal operation assumes PWM\_INV is tied to GND and inverting MOSFET drivers are used.

In the default 6-phase operation, the PWM2 pulse starts 1/6 of a cycle after PWM1, the PWM3 pulse starts 1/6 of a cycle after PWM2, the PWM4 pulse starts 1/6 of a cycle after PWM3, the PWM5 pulse starts 1/6 of a cycle after PWM4, and the PWM6 pulse starts 1/6 of a cycle after PWM5.

#### **Phase Selection**

The ISL78220 can work in 1, 2, 3, 4, 5 or 6-phase configuration. Connecting the PWM5 or PWM6 to VCC selects 4-phase operation and the pulse times are spaced in 1/4 cycle increments. Connecting the PWM4 to VCC selects 3-phase operation and the pulse times are spaced in 1/3 cycle increments. Connecting the PWM3 to VCC selects 2-phase operation and the pulse times are spaced in 1/2 cycle increments. For the unused ISENxN and ISENxP, a 1k $\Omega$  resistor is recommended to connect ISENxN and ISENxP, and connect ISENxN to VIN.

# **Modes of Operations**

The different mode of operations will be determined by the voltage combinations of the MODE pin and the PWM\_TRI pin.

If automatic phase adding/dropping function is not needed, the MODE pin should be tied to VCC (Logic HIGH). If higher light load efficiency is preferred, phase adding/dropping function could be implemented by connecting the MODE pin through a resistor to GND. A 5µA reference current will flow out of MODE pin to generate corresponding V<sub>MODE</sub>. V<sub>MODE</sub> is used to compare with V<sub>IOUT</sub> to determine the phase adding/dropping level.

When PWM\_TRI is tied to GND (Logic LOW), the PWM outputs will be 2-levels (i.e., 0V and 5V).When PWM\_TRI is pulled to VCC (Logic HIGH), apart from generating the 0V and 5V PWM signals, the PWM outputs can also generate 2.5V tri-level signal. The external driver can identify this tri-level signal and turn off both low-side and high-side output signals accordingly.

The truth table regarding V<sub>MODE</sub> and V<sub>PWM\_TRI</sub> for different mode of applications is summarized in Table 1.

| CASE | MODE   | PWM<br>_TRI | EXTERNAL<br>DRIVER<br>IDENTIFY<br>2.5V TRI-LEVEL<br>SIGNAL? | APPLICATIONS                                                                                                                                                                          |

|------|--------|-------------|-------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A    | 1      | 1           | Yes                                                         | Synchronous boost for audio<br>amplifier power supply. No<br>phase dropping. (Note)                                                                                                   |

| В    | Analog | 1           | Yes                                                         | Applications that need<br>improving light load efficiency<br>(automatic phase dropping +<br>cycle-by-cycle diode emulation<br>+ pulse skipping).                                      |

| С    | 1      | 0           | No                                                          | Applications that the external driver cannot identify tri-level signal, no phase dropping.                                                                                            |

| D    | Analog | 0           | No                                                          | Applications that the external<br>driver cannot identify tri-level<br>signal, with improved light load<br>efficiency (e.g., 6-phase<br>non-synchronous boost with<br>phase dropping). |

TABLE 1. OPERATION MODE FOR DIFFERENT APPLICATIONS

NOTE: Forced minimum ON pulses exists.

## Considerations for Audio Amplifier Power Supply Application

For multiphase boost converters used in audio amplifier applications, it is preferred to have the following features:

- **1**. Automatic phase dropping function is NOT needed because the load is fast changing.

- In car audio amplifier applications, the switching frequency is preferred to be fixed, such that it will not interfere with FM/AM band.

- 3. For synchronous boost, diode emulation is needed during start-up in order to prevent negative current dumping to the input side.

- 4. For synchronous boost, a maximum duty cycle limitation on the synchronous FET is preferred.

Based on the above mentioned "preferred features", For audio amplifier applications, it does not need phase dropping/adding, but it needs a tri-state PWM signal if synchronous boost structure is used. Also in order to limit the maximum duty cycle of the synchronous FET, the minimal turn on time of the active FET (Low-side FET for boost structure) will be changed from fixed 130ns to variable time, which is 1/12 of the switching periods.

# **Operation Initialization Before Soft-Start**

Prior to converter initialization, proper conditions must exist on the enable inputs (EN pin) and VCC pin. When both conditions are met, the controller begins soft-start. Once the output voltage is within the proper window of operation,  $V_{PGOOD}$  is asserted logic high.

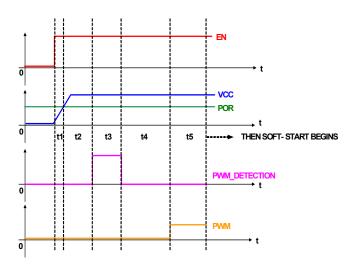

Figure 14 shows the ISL78220 internal circuit functions before the soft-start begins.

#### FIGURE 14. CIRCUIT INITIALIZATION BEFORE SOFT-START

As shown on Figure 14, there are 5x intervals before the soft-start is initialized, they are specified as  $t_1$ ,  $t_2$ ,  $t_3$ ,  $t_4$  and  $t_5$ , respectively. The descriptions for each time interval are as follows:

**Time t<sub>1</sub>:** The enable comparator holds the ISL78220 in shutdown until the V<sub>EN</sub> rises above 1.2V at the beginning of t<sub>1</sub> time period. During t<sub>1</sub>, V<sub>VCC</sub> will gradually increase until it reaches the internal power-on reset (POR) rising threshold. Then the system enters t<sub>2</sub>.

**Time t<sub>2</sub>:** During t<sub>2</sub> time, the device initialization occurs. The time duration for t<sub>2</sub> is typically from 60 $\mu$ s to 100 $\mu$ s.

**Time t<sub>3</sub>:** The internal PWM detection signal will be asserted and the system enters the t<sub>3</sub> period. During t<sub>3</sub> the ISL78220 will detect the voltage on each PWM pin to determine the active phase number. If PWM1 or PWM2 is accidentally pulled to VCC, the chip will be latched off and wait for power recycling. The time duration for t<sub>3</sub> is fixed to around 30µs.

**Time t<sub>4</sub>:** When internal PWM detection signal is released the system enters  $t_4$  period. During  $t_4$  period the ISL78220 will wait until the internal PLL circuits are locked to the pre-set oscillator frequency. When PLL locking is achieved, the oscillator will generate output at CLK\_OUT pin. The time duration for  $t_4$  is typically around 0.5ms, depending on PLL\_COMP pin configuration.

**Time t<sub>5</sub>:** After the PLL locks the frequency, the system enters the t<sub>5</sub> period. During t<sub>5</sub> the PWM outputs are held in a high-impedance state (If  $V_{PWM_TRI} = 1$ ) or logic low (if  $V_{PWM_TRI} = 0$ ), and the  $V_{DRIVE_EN}$  is logic LOW to assure the external drivers remain off. The ISL78220 has one unique

feature to pre-bias the  $V_{SS}$  based on  $V_{FB}$  information during this time. The duration time for  $t_5$  is around 50 $\mu s.$

After t<sub>5</sub> the soft-start process will begin. The following section will discuss the soft-start in detail for different applications.

# Soft-Start Process for Different Modes (Refer to Table 1)

At the beginning of soft-start, the SS pin voltage will start ramping up from a voltage equaling to FB voltage. The soft-start period ends when the SS pin voltage reaches the lower power-good threshold that is 80% of the lower value of VREF2 or 2V.

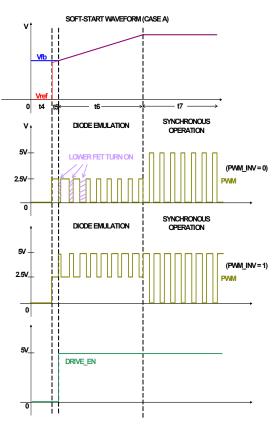

#### Case A (V<sub>MODE</sub> = VCC, V<sub>PWM\_TRI</sub> = VCC)

Figure 15 shows the pre-bias start-up PWM waveform for case A in Table 1. The  $V_{PWM_{TRI}}$  = VCC so that PWM can output tri-level signal, which the external drivers need to identify, and  $V_{MODF}$  = VCC to ban the automatic phase dropping function.

**Time t<sub>4</sub>, t<sub>5</sub>:** Same as the t<sub>4</sub>, t<sub>5</sub> in Figure 14, soft-start has not started yet. See <u>"Operation Initialization Before Soft-Start" on page 13</u> for a detailed description.

**Time t<sub>6</sub>:** At the beginning of t<sub>6</sub> the SS pin has already been pre-biased to a value very close to the  $V_{FB}$ , so that the internal reference signal will start from the voltage close to FB pin. This scheme will eliminate the internal delay for a non pre-biased application.

The DRIVE\_EN pin, which is connected to the enable pins of the external drivers, will be pulled high when first PWM toggles at the beginning of  $t_{6}$ , as a results external drivers will start working. The PWM signals will switch between tri-level and low. The driver will only turn on the lower MOSFET accordingly, and the duty cycle will increase gradually from 0 to steady state. The synchronous MOSFET (Upper FET for Boost converter) will never turn on during this time, so diode emulation can be achieved during the start-up and in turn prevent negative current flowing from output to input.

**Time t7:** Soft-start finishes at the beginning of t7. The PWMs will change to a 2-level 0V to 5V switching signal and the synchronous MOSFET will be turned on.

FIGURE 15. SOFT-START WAVEFORM (CASE A) (Note: t4, t5 periods are from Figure 5)

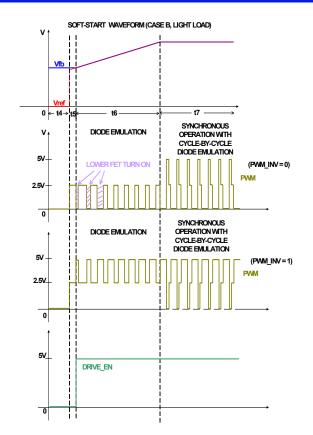

#### Case B (V<sub>MODE</sub> < 4V, V<sub>PWM\_TRI</sub> = VCC, Light Load Condition)

The only difference between the case A and case B start-up waveforms is that at light load, case B can drop phases and have cycle-by-cycle diode emulation at PWM1 and PWM2.

For the case B applications, where good light load efficiency is always preferred, the ISL78220 provides three light load efficiency enhancement methods. When the load current reduces, the ISL78220 will first assert the automatic phase dropping function to reduce the active phase number according to the load level. The minimum active phase number is two. If the load current further reduces even when running at two-phase operation, the ISL78220 will assert a second method by utilizing cycle-by-cycle diode emulation. During this time the IC will sense the inductor current, and when the current is approximately zero it will turn off the synchronous MOSFET. If the load current is further reduced to deep light load operation, pulse skipping function will kick in to optimize the overall efficiency.

FIGURE 16. SOFT-START WAVEFORM (CASE B, LIGHT LOAD) (Note: t4, t5 periods are from <u>Figure 5</u>)

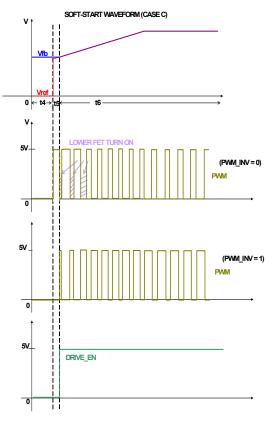

#### Case C ( $V_{PWM}_{TRI} = 0$ )

For applications that the driver cannot identify a tri-state PWM signal, the  $V_{PWM\_TRI}$  should be connected to GND (Logic LOW), such that the PWM signal will only be two levels between OV and 5V. Then DRIVE\_EN pin can be connected to the EN pin of the external drivers. DRIVE\_EN will be asserted when the PWM first toggles such that the pre-bias start up capability can be achieved. Detailed soft-start for case C is shown in Figure 17.

**Time t<sub>4</sub>, t<sub>5</sub>:** Same as the t<sub>4</sub>, t<sub>5</sub> in <u>Figure 14</u>, soft-start has not started yet, see <u>"Operation Initialization Before Soft-Start" on page 13</u> for detailed description.

**Time t<sub>6</sub>:** At the beginning of t<sub>6</sub>, the PWM signal will start to switch between 0V and 5V. The driver will turn on the lower and upper MOSFETs accordingly, and the duty cycle for lower MOSFET will increase gradually from 0 to steady state. DRIVE\_EN will be pulled high when the first PWM toggles at the beginning of t<sub>6</sub> to enable the external drivers.

FIGURE 17. SOFT-START WAVEFORM (CASE C, LIGHT LOAD) (Note: t4, t5 periods are from Figure 5)

# Soft-Start Ramp Slew Rate Calculation

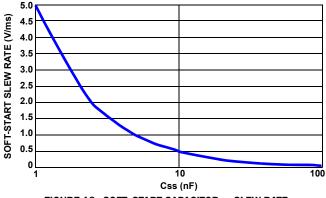

The soft-start ramp slew rate  ${\sf SR}_{\sf SS}$  is determined by the capacitor value  ${\sf C}_{\sf SS}$  from SS pin to GND.  ${\sf C}_{\sf SS}$  can be calculated based on Equation 3:

$$SR_{SS} = \frac{5X10^{-12}}{C_{SS}} \left(\frac{V}{\mu s}\right)$$

(EQ. 3)

Figure 18 shows the relationship between C<sub>SS</sub> and SR<sub>SS</sub>.

FIGURE 18. SOFT- START CAPACITOR vs SLEW RATE

# **Oscillator and Synchronization**

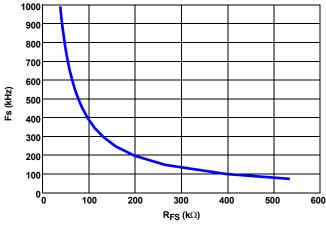

The switching frequency is determined by the selection of the frequency-setting resistor,  $R_{FS}$ , connected from FS pin to GND. Equation 4 is provided to assist in selecting the correct resistor value.

$$R_{FS} = 4X10^{10} \left(\frac{1}{f_{SW}} - 5X10^{-8}\right)$$

(EQ. 4)

where  $f_{SW}$  is the switching frequency of each phase. Figure 19 shows the relationship between  $R_{FS}$  and switching frequency.

FIGURE 19. R<sub>FS</sub> vs SWITCHING FREQUENCY

The maximum frequency at each PWM output is 1MHz. If the FS pin is accidentally shorted to GND or connected to a low impedance node, the internal circuits will detect this fault condition and fold back the switching frequency to the 75kHz minimal value.

The ISL78220 contains a phase lock loop (PLL) circuit and has frequency synchronization capability by simply connecting SYNC pin to an external square pulse waveform (typically 20% to 80% duty cycle). In normal operation, the external SYNC frequency needs to be at least 20% faster than the internal oscillator frequency setting. The ISL78220 will synchronize its switching frequency to the fundamental frequency of the input waveform. The frequency synchronization feature will synchronize the rising edge of the PWM1 clock signal with the rising edge of the external clock signal at the SYNC pin.

The PLL is compensated with a series resistor-capacitor (Rc and Cc) from the PLL\_COMP pin to GND and a capacitor (Cp) from PLL\_COMP to GND. Typical values are Rc =  $6.8k\Omega$ , Cc = 6.8nF, Cp = 1nF. The typical lock time is around 0.5ms.

The CLK\_OUT pin provides a square pulse waveform at the switching frequency. The amplitude is 5V with approximately 40% positive duty cycle, and the rising edge is synchronized with the leading edge of PWM1.

# **Current Sensing**

The ISL78220 senses the current continuously for fast response. It supports both sense resistor and inductor DCR current sensing methods. The sensed current for each active channel will be used for loop control, phase current balance, individual channel overcurrent protection and total average current protection. The internal circuitry, shown in Figures 20 and 21, represents a single channel. This circuitry is repeated for each channel, but may not be active depending on the status of the PWM3, PWM4, PWM5, and PWM6 pin voltage.

Peak current mode control is implemented by feeding back the current output of the current sense amplifier (CSA) to the regulator control loop. Individual channel peak current limit is implemented by comparing the CSA output current with  $160\mu$ A. When the peak current limit comparator is tripped, the PWM on-pulse is terminated and the IC is latched off.

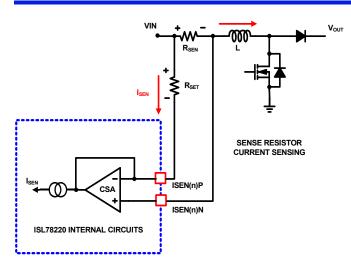

#### **Sense Resistor Current Sensing**

A sense resistor can be placed in series with the power inductor. As shown in Figure 20, The ISL78220 acquires the channel current information by sensing the voltage signal across the sense resistor. Because the voltage on both the positive input and the negative input of CSA are forced to be equal, the voltage across R<sub>SET</sub> is equivalent to the voltage drop across the R<sub>SEN</sub> resistor. The resulting current into the ISENxP pin is proportional to the channel current, I<sub>L</sub>. Equation 5 for I<sub>SEN</sub> is derived where I<sub>L</sub> is the channel current:

$$I_{SEN} = I_{L} \cdot \frac{R_{SEN}}{R_{ISET}}$$

(EQ. 5)

FIGURE 20. SENSE RESISTOR CURRENT SENSING

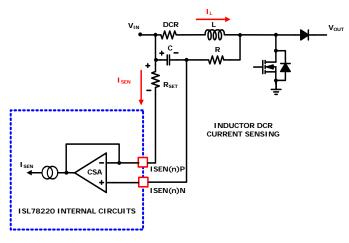

#### **Inductor DCR Sensing**

An inductor's winding is characteristic of a distributed resistance as measured by the DCR (Direct Current Resistance) parameter.

FIGURE 21. INDUCTOR DCR CURRENT SENSING

Consider the inductor DCR as a separate lumped quantity, as shown in Figure 21. The channel current I<sub>L</sub>, flowing through the inductor, will also pass through the DCR. Equation 6 shows the S-domain equivalent voltage across the inductor V<sub>L</sub>.

$$V_{L} = I_{L} \cdot (s \cdot L + DCR)$$

(EQ. 6)

A simple R-C network across the inductor extracts the DCR voltage, as shown in Figure 21.

The voltage on the capacitor  $V_{C},$  can be shown to be proportional to the channel current  $I_{L},$  see Equation 7.

$$V_{C} = \frac{\left(s \cdot \frac{L}{DCR} + 1\right) \cdot (DCR \cdot I_{L})}{(s \cdot RC + 1)}$$

(EQ. 7)

If the R-C network components are selected such that the RC time constant (= R\*C) matches the inductor time constant (= L/DCR), the voltage across the capacitor V<sub>C</sub> is equal to the

voltage drop across the DCR, i.e., proportional to the channel current.

With the internal low-offset differential current sense amplifier, the capacitor voltage V<sub>C</sub> is replicated across the sense resistor R<sub>SET</sub>. Therefore the current flows into the ISENxP pin is proportional to the inductor current. <u>Equation 8</u> shows that the ratio of the channel current to the sensed current I<sub>SEN</sub> is driven by the value of the sense resistor and the DCR of the inductor.

$$I_{\text{SEN}} = I_{\text{L}} \cdot \frac{\text{DCR}}{\text{R}_{\text{SET}}}$$

(EQ. 8)

# Light Load Efficiency Enhancement Schemes

For switching mode power supplies, the total loss is related to both the conduction loss and the switching loss. At heavy load the conduction loss is dominant while the switching loss will take charge at light load condition. Therefore, if a multiphase converter is running at a fixed phase number for the entire load range, we will observe that below a certain load point the total efficiency starts to drop heavily. The ISL78220 has automatic phase dropping, cycle-by-cycle diode emulation and pulse skipping features to enhance the light load efficiency. By observing the total input current on-the-fly and dropping the active phase numbers accordingly, the overall system can achieve optimized efficiency over the entire load range. All the above mentioned light load enhancement features can be disabled by simply pulling the MODE pin to VCC.

#### Adjustable Automatic Phase Dropping/Adding at Light Load Condition

If the MODE pin is connected to a resistor to GND, and the voltage on the MODE pin is lower than its disable threshold 4V, the adjustable automatic phase dropping/adding mode will be enabled. When the ISL78220 controller works in this mode, it will automatically adjust the active phase number by comparing the V<sub>MODE</sub> and V<sub>IOUT</sub>, which represents sensed total current information. The V<sub>MODE</sub> sets the overall phase dropping threshold, and the V<sub>IOUT</sub> is proportional to the input current, which is in turn proportional to the load current. The smaller the load current, the lower the voltage observed on the IOUT pin, and the ISL78220 will drop phases in operation. Once the MODE pin voltage is fixed, the threshold to determine how many phases are in operation is dependent on two factors:

- **1**. The maximum configured phase number.

- 2. The voltage on the IOUT pin (V $_{\rm IOUT}$ ).

For example, if the converter is working in 6-phase operation and the MODE pin is set to 1.2V, in this case the converter will monitor the V<sub>IOUT</sub> and compare to 1.2V, such that when the V<sub>IOUT</sub> is less than 800mV (66.6% of 1.2V), it will drop from 6-phase to 4-phase; if less than 600mV (50% of 1.2V), it will drop to 3-phase; if less than 400mV (33% of 1.2V), it will drop to 2-phase. The detailed threshold setting is shown in the "Electrical Specifications" table on page 8.

If PWM\_TRI is tied to VCC, the dropped phase will provide a 2.5V tri-level signal at its PWM output. The external driver has to

identify this tri-state signal and turn off both the lower and upper switches accordingly. For better transient response during phase dropping, the ISL78220 will gradually reduce the duty cycle of the phase from steady state to zero, typically within 15 switching cycles. This gradual dropping scheme will help smooth the change of the PWM signal and, in turn, will help to stabilize the system when phase dropping happens.

The ISL78220 also has an automatic phase adding feature similar to phase dropping, but when doing phase adding there will not be 15 switching cycles gradually adding. It will add phases instantly to take care of the increased load condition. The phase adding scheme is controlled by three factors.

- 1. The maximum configured phase number

- 2. The voltage on the IOUT pin ( $V_{IOUT}$ ).

- 3. Individual phase current

Factors 1 and 2 are similar to the phase dropping scheme. If the  $V_{\text{IOUT}}$  is higher than the phase dropping threshold plus the hysteresis voltage, the dropped phase will be added back one by one instantly.

The previously mentioned phase-adding method can take care of the condition that the load current increases slowly. However, if the load is fast increasing the IC will using different phase adding scheme. The ISL78220 monitors the individual channel current for all active phases. During phase adding the system will bring down the pre-set channel current limit to 2/3 of its original value (160µA). If any of the phase's sensed current hit the 2/3 of pre-set channel current limit threshold (i.e., 106.7µA), all the phases will be added back instantly. After a fixed 1.5ms delay, the phase dropping circuit will be activated and the system will react to drop the phase number to the correct value.

During phase adding when either phase hit the pre-set channel current limit, there will be 200µs blanking time such that per-channel OCP will not be triggered during this blanking time.

#### **Diode Emulation at Very Light Load Condition**

When phase dropping is asserted and the minimum phase operation is 2 phases, if the load is still reducing and synchronous boost structure is used, the ISL78220 controller will enter into forced cycle-by-cycle diode emulation mode. The PWM output will be tri-stated when inductor current falls to zero, such that the synchronous MOSFET can be turned off accordingly cycle-by-cycle for forced diode emulation. This cycle-by-cycle diode emulation scheme will only be asserted when two conditions are met:

- 1. The PWM\_TRI pin voltage is logic HIGH.

- 2. Only two phases are running either by phase dropping or initial configuration.

By utilizing the cycle-by-cycle diode emulation scheme in this way, negative current is prevented and the system can still optimize the efficiency even at very light load condition.

#### **Pulse Skipping at Deep Light Load Condition**

If the converter enters diode emulation mode and the load is still reducing, eventually pulse skipping will occur to increase the deep light load efficiency.

# **Adjustable Slope Compensation**

For a boost converter working in current mode control, slope compensation is needed when steady state duty cycle is larger than 50%. When slope compensation is too low the converter can suffer from jitter or oscillation. On the other hand, over compensation of the slope will cause the reduction of the phase margin. Therefore, proper design of the slope compensation is needed.

The ISL78220 features adjustable slope compensation by setting the resistor value  $R_{SLOPE}$  from the SLOPE pin to GND. This function will ease the compensation design and provide more flexibility in choosing the external components.

For current mode control, typically we need the compensation slope  $m_A$  to be 50% of the inductor current down ramp slope  $m_B$  when the lower MOSFET is off. The equation for choosing the suitable resistor value is as follows:

$$\mathsf{R}_{\mathsf{SLOPE}} = \frac{1.136 \times 10^6 \times \mathsf{LxR}_{\mathsf{SET}}}{(\mathsf{V}_{\mathsf{OUT}} - \mathsf{V}_{\mathsf{IN}})(\mathsf{R}_{\mathsf{SEN}})}(\Omega) \tag{EQ. 9}$$

# **Fault Monitoring and Protection**

The ISL78220 actively monitors input/output voltage and current to detect fault conditions. Fault monitors trigger protective measures to prevent damage to the load. Common power-good indicator pin (PGOOD pin) and VIN\_OVB, VOUT\_OVB pins are provided for linking to external system monitors.

#### **PGOOD Signal**

The PGOOD pin is an open-drain logic output to indicate that the soft-start period is completed and the output voltage is within the specified range. This pin is pulled low during soft-start and releases high after a successful soft-start. PGOOD will be pulled low when a UV/OV/OC/OT fault occurs.

#### **Input Overvoltage Detection**