# 2.1-channel high-efficiency digital audio system Sound Terminal®

Datasheet - production data

PowerSSO-36 with exposed pad down (EPD)

#### **Features**

- Wide-range supply voltage

- 5 V to 26 V (operating range)

- 30 V (absolute maximum rating)

- Four power output configurations

- 2 channels of ternary PWM (stereo mode) (2 x 30 W into 8  $\Omega$  at 22 V)

- 3 channels left, right using binary and LFE using ternary PWM (2.1 mode) (2 x 15 W + 1 x 30 W into 2 x 4Ω, 1 x 8 Ω at 22 V)

- 2 channels of ternary PWM (2 x 30 W) + stereo lineout ternary)

- FFX<sup>®</sup>100 dB SNR and dynamic range

- Selectable 32 to 192 kHz input sampling rates

- I<sup>2</sup>C control with selectable device address

- Digital gain/attenuation +42 dB to -80 dB with 0.125 dB/step resolution

- Soft-volume update with programmable ratio

- Individual channel and master gain/attenuation

- Two independent DRCs configurable as a dual-band anti-clipper (B<sup>2</sup>DRC) or independent limiters/compressors

- EQ-DRC for DRC based on filtered signals

- Dedicated LFE processing for bass boosting with 0.125 dB/step resolution

- Audio presets:

- 15 preset crossover filters

- 5 preset anti-clipping modes

- Preset nighttime listening mode

- Individual channel and master soft/hard mute

- Independent channel volume and DSP bypass

- Automatic zero-detect mute

- Automatic invalid input-detect mute

- I<sup>2</sup>S input data interface

- · Input and output channel mapping

- Up to 8 user-programmable biquads per channel

- 3 coefficient banks for EQ presets storing with fast recall via I<sup>2</sup>C interface

- Extended coefficient dynamic up to -4..4 for easy implementation of high shelf filters

- Bass/treble tones and de-emphasis control

- Selectable high-pass filter for DC blocking

- Advanced AM interference frequency switching and noise suppression modes

- Selectable high- or low-bandwidth noise-shaping topologies

- Selectable clock input ratio

- 96 kHz internal processing sampling rate with quantization error noise shaping for very low cutoff frequency filters

- Thermal overload and short-circuit protection embedded

- Video apps: 576 x Fs input mode supported

- Fully compatible with STA339BW, STA369BWS and STA350BW

Table 1. Device summary

| Order code | Package      | Packing       |  |

|------------|--------------|---------------|--|

| STA369BW   | Power SSO-36 | Tube          |  |

| STA369BWTR | Power SSO-36 | Tape and reel |  |

Contents STA369BW

# **Contents**

| 1 | Desc               | cription  |                                            | . 10 |

|---|--------------------|-----------|--------------------------------------------|------|

|   | 1.1                | Block o   | diagram                                    | 11   |

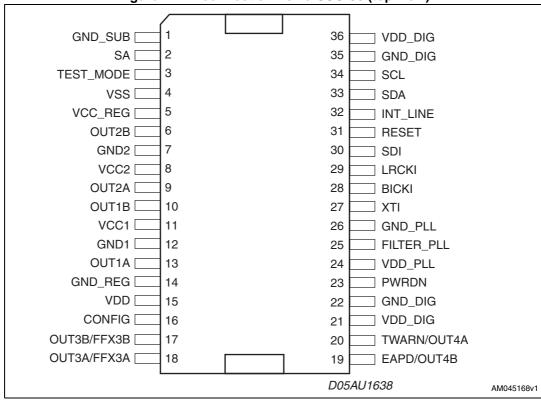

| 2 | Pin e              | connect   | tions                                      | . 12 |

|   | 2.1                | Conne     | ection diagram                             | . 12 |

|   | 2.2                | Pin des   | scription                                  | . 12 |

| 3 | Elec               | trical sp | pecifications                              | . 14 |

|   | 3.1                | Absolu    | ute maximum ratings                        | . 14 |

|   | 3.2                | Therma    | al data                                    | . 14 |

|   | 3.3                | Recom     | nmended operating conditions               | . 15 |

|   | 3.4                | Electric  | cal specifications for the digital section | . 15 |

|   | 3.5                | Electric  | cal specifications for the power section   | . 16 |

| 4 | Cha                | racteriza | ation curves                               | . 18 |

|   | 4.1                | Mono p    | parallel BTL characteristics               | . 23 |

| 5 | Seria              | al audio  | interface                                  | . 25 |

|   |                    | 5.0.1     | Timings                                    | 25   |

|   |                    | 5.0.2     | Delay serial clock enable                  | 25   |

|   |                    | 5.0.3     | Channel input mapping                      | 25   |

| 6 | Proc               | essing    | data paths                                 | . 26 |

| 7 | I <sup>2</sup> C k | ous spec  | cification                                 | . 28 |

|   | 7.1                | Comm      | nunication protocol                        | . 28 |

|   |                    | 7.1.1     | Data transition or change                  | 28   |

|   |                    | 7.1.2     | Start condition                            | 28   |

|   |                    | 7.1.3     | Stop condition                             | 28   |

|   |                    | 7.1.4     | Data input                                 | 28   |

|   | 7.2                | Device    | addressing                                 | . 28 |

|   | 7.3                | Write c   | pperation                                  | . 29 |

|   |                    | 7.3.1     | Byte write                                 | 29   |

|   |                    | 7.3.2     | Multi-byte write                           | 29   |

|   |                    |           |                                            |      |

STA369BW Contents

|   | 7.4  | Read    | Read operation                               |      |  |

|---|------|---------|----------------------------------------------|------|--|

|   |      | 7.4.1   | Current address byte read                    | . 29 |  |

|   |      | 7.4.2   | Current address multi-byte read              | . 29 |  |

|   |      | 7.4.3   | Random address byte read                     | . 29 |  |

|   |      | 7.4.4   | Random address multi-byte read               | . 29 |  |

|   |      | 7.4.5   | Write mode sequence                          | . 30 |  |

|   |      | 7.4.6   | Read mode sequence                           | . 30 |  |

| 8 | Regi | ster de | scription                                    | 31   |  |

|   | 8.1  | Config  | guration register A (addr 0x00)              | 34   |  |

|   |      | 8.1.1   | Master clock select                          | . 34 |  |

|   |      | 8.1.2   | Interpolation ratio select                   | . 35 |  |

|   |      | 8.1.3   | Thermal warning recovery bypass              | . 35 |  |

|   |      | 8.1.4   | Thermal warning adjustment bypass            | . 35 |  |

|   |      | 8.1.5   | Fault detect recovery bypass                 | . 36 |  |

|   | 8.2  | Config  | guration register B (addr 0x01)              | 36   |  |

|   |      | 8.2.1   | Serial audio input interface format          | . 36 |  |

|   |      | 8.2.2   | Serial data interface                        | . 37 |  |

|   |      | 8.2.3   | Serial data first bit                        | . 37 |  |

|   |      | 8.2.4   | Delay serial clock enable                    | . 39 |  |

|   |      | 8.2.5   | Channel input mapping                        | . 39 |  |

|   | 8.3  | Config  | guration register C (addr 0x02)              | 40   |  |

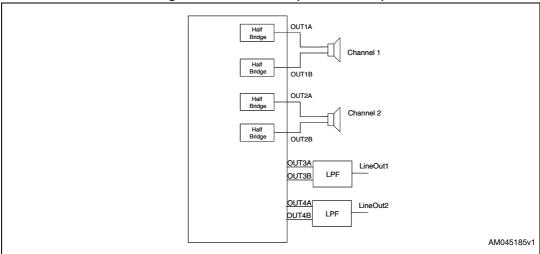

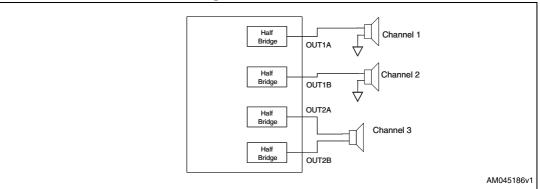

|   |      | 8.3.1   | FFX power output mode                        | . 40 |  |

|   |      | 8.3.2   | FFX compensating pulse size register         | . 40 |  |

|   |      | 8.3.3   | Overcurrent warning detect adjustment bypass | . 41 |  |

|   | 8.4  | Config  | guration register D (addr 0x03)              | 41   |  |

|   |      | 8.4.1   | High-pass filter bypass                      | . 41 |  |

|   |      | 8.4.2   | De-emphasis                                  | . 41 |  |

|   |      | 8.4.3   | DSP bypass                                   | . 42 |  |

|   |      | 8.4.4   | Post-scale link                              | . 42 |  |

|   |      | 8.4.5   | Biquad coefficient link                      | . 42 |  |

|   |      | 8.4.6   | Dynamic range compression/anti-clipping bit  | . 42 |  |

|   |      | 8.4.7   | Zero-detect mute enable                      | . 43 |  |

|   |      | 8.4.8   | Submix mode enable                           | . 43 |  |

|   | 8.5  | Config  | guration register E (addr 0x04)              | 43   |  |

|   |      | 8.5.1   | Max power correction variable                | . 43 |  |

|   |      |         |                                              |      |  |

|      | 8.5.2   | Max power correction                          | . 43 |

|------|---------|-----------------------------------------------|------|

|      | 8.5.3   | Noise-shaper bandwidth selection              | . 44 |

|      | 8.5.4   | AM mode enable                                | . 44 |

|      | 8.5.5   | PWM speed mode                                | . 44 |

|      | 8.5.6   | Distortion compensation variable enable       | . 44 |

|      | 8.5.7   | Zero-crossing volume enable                   | . 44 |

|      | 8.5.8   | Soft-volume update enable                     | . 45 |

| 8.6  | Configu | ıration register F (addr 0x05)                | . 45 |

|      | 8.6.1   | Output configuration                          | . 45 |

|      | 8.6.2   | Invalid input detect mute enable              | . 51 |

|      | 8.6.3   | Binary output mode clock loss detection       | . 51 |

|      | 8.6.4   | LRCK double trigger protection                | . 51 |

|      | 8.6.5   | Auto EAPD on clock loss                       | . 51 |

|      | 8.6.6   | IC power-down                                 | . 51 |

|      | 8.6.7   | External amplifier power-down                 | . 52 |

| 8.7  | Volume  | control registers (addr 0x06 - 0x0A)          | . 52 |

|      | 8.7.1   | Mute/line output configuration register       | . 52 |

|      | 8.7.2   | Master volume register                        | . 52 |

|      | 8.7.3   | Channel 1 volume                              | . 52 |

|      | 8.7.4   | Channel 2 volume                              | . 53 |

|      | 8.7.5   | Channel 3 / line output volume                | . 53 |

| 8.8  | Audio p | reset registers (addr 0x0B and 0x0C)          | . 54 |

|      | 8.8.1   | Audio preset register 1 (addr 0x0B)           | . 54 |

|      | 8.8.2   | Audio preset register 2 (addr 0x0C)           | . 55 |

|      | 8.8.3   | AM interference frequency switching           | . 55 |

|      | 8.8.4   | Bass management crossover                     | . 55 |

| 8.9  | Channe  | el configuration registers (addr 0x0E - 0x10) | . 56 |

|      | 8.9.1   | Tone control bypass                           | . 56 |

|      | 8.9.2   | EQ bypass                                     | . 56 |

|      | 8.9.3   | Volume bypass                                 | . 57 |

|      | 8.9.4   | Binary output enable registers                | . 57 |

|      | 8.9.5   | Limiter select                                | . 57 |

|      | 8.9.6   | Output mapping                                | . 57 |

| 8.10 | Tone co | ontrol register (addr 0x11)                   | . 58 |

|      | 8.10.1  | Tone control                                  | . 58 |

| 8.11 | Dynami  | ic control registers (addr 0x12 - 0x15)       | . 58 |

STA369BW Contents

|      | 8.11.1   | Limiter 1 attack/release rate                          | 58 |

|------|----------|--------------------------------------------------------|----|

|      | 8.11.2   | Limiter 1 attack/release threshold                     | 58 |

|      | 8.11.3   | Limiter 2 attack/release rate                          | 58 |

|      | 8.11.4   | Limiter 2 attack/release threshold                     | 59 |

|      | 8.11.5   | Limiter 1 extended attack threshold (addr 0x32)        | 62 |

|      | 8.11.6   | Limiter 1 extended release threshold (addr 0x33)       | 62 |

|      | 8.11.7   | Limiter 2 extended attack threshold (addr 0x34)        | 63 |

|      | 8.11.8   | Limiter 2 extended release threshold (addr 0x35)       | 63 |

| 8.12 | User-de  | fined coefficient control registers (addr 0x16 - 0x26) | 63 |

|      | 8.12.1   | Coefficient address register                           | 63 |

|      | 8.12.2   | Coefficient b1 data register bits 23:16                | 63 |

|      | 8.12.3   | Coefficient b1 data register bits 15:8                 | 63 |

|      | 8.12.4   | Coefficient b1 data register bits 7:0                  | 63 |

|      | 8.12.5   | Coefficient b2 data register bits 23:16                | 64 |

|      | 8.12.6   | Coefficient b2 data register bits 15:8                 | 64 |

|      | 8.12.7   | Coefficient b2 data register bits 7:0                  | 64 |

|      | 8.12.8   | Coefficient a1 data register bits 23:16                | 64 |

|      | 8.12.9   | Coefficient a1 data register bits 15:8                 | 64 |

|      | 8.12.10  | Coefficient a1 data register bits 7:0                  | 64 |

|      | 8.12.11  | Coefficient a2 data register bits 23:16                | 64 |

|      | 8.12.12  | Coefficient a2 data register bits 15:8                 | 65 |

|      | 8.12.13  | Coefficient a2 data register bits 7:0                  | 65 |

|      | 8.12.14  | Coefficient b0 data register bits 23:16                | 65 |

|      | 8.12.15  | Coefficient b0 data register bits 15:8                 | 65 |

|      | 8.12.16  | Coefficient b0 data register bits 7:0                  | 65 |

|      | 8.12.17  | Coefficient write/read control register                | 65 |

|      | 8.12.18  | User-defined EQ                                        | 68 |

|      | 8.12.19  | Pre-scale                                              | 68 |

|      | 8.12.20  | Post-scale                                             | 68 |

|      | 8.12.21  | Overcurrent post-scale                                 | 69 |

| 8.13 | Variable | e max power correction registers (addr 0x27 - 0x28)    | 70 |

| 8.14 | Variable | e distortion compensation registers (addr 0x29 - 0x2A) | 70 |

| 8.15 | Fault-de | etect recovery constant registers (addr 0x2B - 0x2C)   | 71 |

| 8.16 | Device   | status register (addr 0x2D)                            | 71 |

| 8.17 | EQ coef  | fficients and DRC configuration register (addr 0x31)   | 72 |

| 8.18 | Extende  | ed configuration register (addr 0x36)                  | 73 |

|    |      | 8.18.1   | Dual-band DRC73                                                             |

|----|------|----------|-----------------------------------------------------------------------------|

|    |      | 8.18.2   | EQ DRC mode                                                                 |

|    |      | 8.18.3   | Extended post-scale range75                                                 |

|    |      | 8.18.4   | Extended attack rate75                                                      |

|    |      | 8.18.5   | Extended BIQUAD selector                                                    |

|    | 8.19 | EQ sof   | t-volume configuration registers (addr 0x37 - 0x38) 76                      |

|    | 8.20 | DRC R    | MS filter coefficients (addr 0x39-0x3E)                                     |

|    | 8.21 | Extra v  | olume resolution configuration registers (address 0x3F) 78                  |

|    | 8.22 | Quanti   | zation error noise correction (address 0x48)                                |

|    | 8.23 | Extend   | ed coefficient range up to -44 (address 0x49, 0x4A) 80                      |

|    | 8.24 | Miscell  | aneous registers (address 0x4B, 0x4C)                                       |

|    |      | 8.24.1   | Rate powerdown enable (RPDNEN) bit (address 0x4B, bit D7)81                 |

|    |      | 8.24.2   | Noise-shaping on DC cut filter enable (NSHHPEN) bit (address 0x4B, bit D6)  |

|    |      | 8.24.3   | Bridge immediate off (BRIDGOFF) bit (address 0x4B, bit D5)81                |

|    |      | 8.24.4   | Channel PWM enable (CPWMEN) bit (address 0x4B, bit D2)82                    |

|    |      | 8.24.5   | Power-down delay selector (PNDLSL[2:0]) bits (address 0x4C, bit D4, D3, D2) |

| 9  | Appl | ication  |                                                                             |

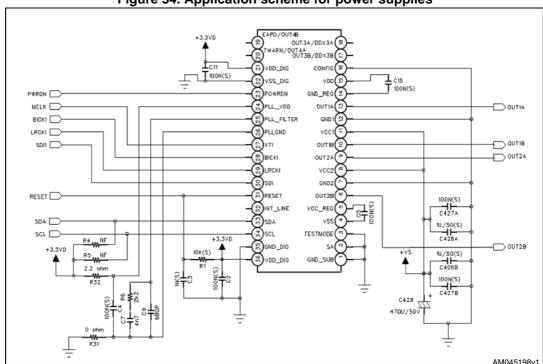

|    | 9.1  | Applica  | ation scheme for power supplies                                             |

|    | 9.2  | PLL filt | er schematic                                                                |

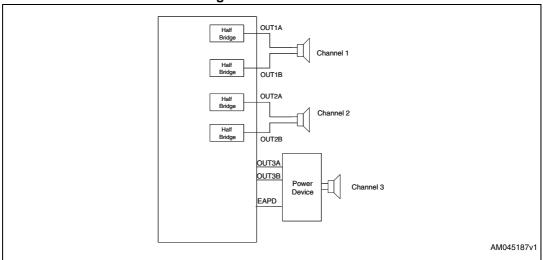

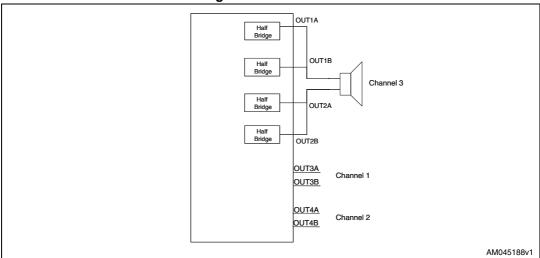

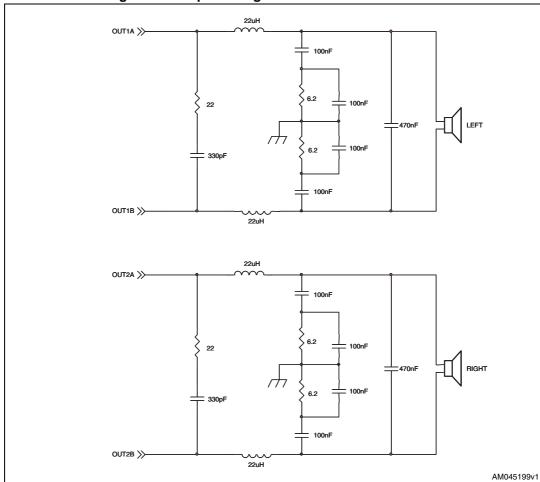

|    | 9.3  | Typical  | output configuration 83                                                     |

| 10 | Pack | age the  | rmal characteristics 85                                                     |

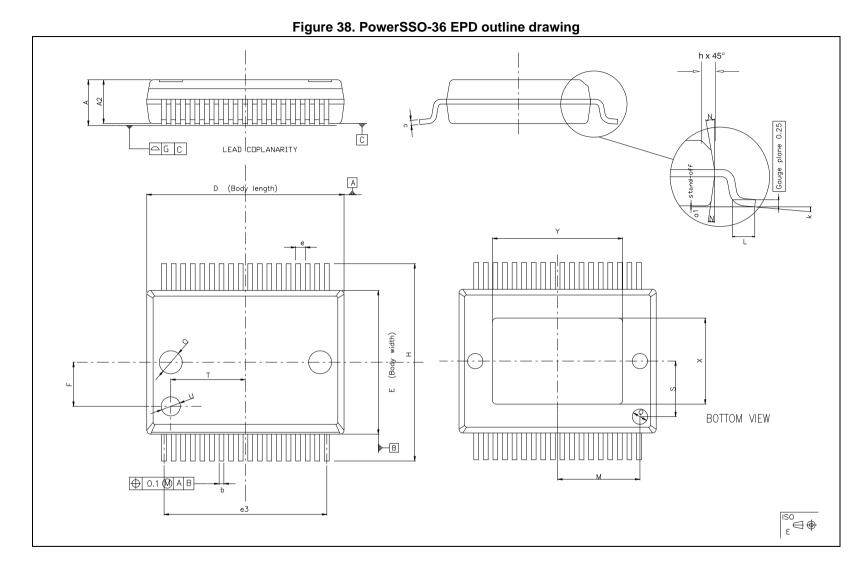

| 11 | Pack | age me   | chanical data                                                               |

| 12 | Revi | sion his | tory                                                                        |

STA369BW List of tables

# List of tables

| Table 1.  | Device summary                                                 | 1  |

|-----------|----------------------------------------------------------------|----|

| Table 2.  | Pin description                                                | 11 |

| Table 3.  | Absolute maximum ratings                                       | 13 |

| Table 4.  | Thermal data                                                   | 13 |

| Table 5.  | Recommended operating conditions                               | 14 |

| Table 6.  | Electrical specifications - digital section                    |    |

| Table 7.  | Electrical specifications - power section                      |    |

| Table 8.  | Timing parameters for slave mode                               |    |

| Table 9.  | Register summary                                               |    |

| Table 10. | Master clock select                                            |    |

| Table 11. | Input sampling rates                                           |    |

| Table 12. | Internal interpolation ratio                                   |    |

| Table 13. | IR bit settings as a function of input sampling rate           |    |

| Table 14. | Thermal warning recovery bypass                                |    |

| Table 15. | Thermal warning adjustment bypass                              |    |

| Table 16. | Fault detect recovery bypass                                   |    |

| Table 17. | Serial audio input interface                                   |    |

| Table 18. | Serial data first bit                                          |    |

| Table 19. | Support serial audio input formats for MSB-first (SAIFB = 0)   |    |

| Table 20. | Supported serial audio input formats for LSB-first (SAIFB = 1) |    |

| Table 21. | Delay serial clock enable                                      |    |

| Table 21. | Channel input mapping                                          |    |

| Table 23. | FFX power output mode                                          |    |

| Table 23. | Output modes                                                   |    |

| Table 24. | FFX compensating pulse size bits                               |    |

| Table 25. | Compensating pulse size                                        |    |

| Table 20. | Overcurrent warning bypass                                     |    |

| Table 27. | High-pass filter bypass                                        |    |

| Table 26. | De-emphasis                                                    |    |

| Table 29. | DSP bypass                                                     |    |

|           | Post-scale link                                                |    |

| Table 31. |                                                                |    |

| Table 32. | Biquad coefficient link                                        |    |

| Table 33. | Dynamic range compression/anti-clipping bit                    |    |

| Table 34. | Zero-detect mute enable                                        |    |

| Table 35. | Submix mode enable                                             |    |

| Table 36. | Max power correction variable                                  |    |

| Table 37. | Max power correction                                           |    |

| Table 38. | Noise-shaper bandwidth selection                               |    |

| Table 39. | AM mode enable                                                 |    |

| Table 40. | PWM speed mode                                                 |    |

| Table 41. | Distortion compensation variable enable                        |    |

| Table 42. | Zero-crossing volume enable                                    |    |

| Table 43. | Soft-volume update enable                                      |    |

| Table 44. | Output configuration                                           |    |

| Table 45. | Output configuration engine selection                          |    |

| Table 46. | Invalid input detect mute enable                               |    |

| Table 47. | Binary output mode clock loss detection                        |    |

| Table 48. | LRCK double trigger protection                                 | 51 |

List of tables STA369BW

| Table 49. | Auto EAPD on clock loss                                              | 51 |

|-----------|----------------------------------------------------------------------|----|

| Table 50. | IC power-down                                                        | 51 |

| Table 51. | External amplifier power-down                                        |    |

| Table 52. | Line output configuration                                            | 52 |

| Table 53. | Master volume offset as a function of MV[7:0]                        |    |

| Table 54. | Channel volume as a function of CxV[7:0]                             | 54 |

| Table 55. | Audio preset gain compression/limiters selection for AMGC[3:2] = 00  | 54 |

| Table 56. | AM interference frequency switching bits                             | 55 |

| Table 57. | Audio preset AM switching frequency selection                        | 55 |

| Table 58. | Bass management crossover                                            | 55 |

| Table 59. | Bass management crossover frequency                                  |    |

| Table 60. | Tone control bypass                                                  | 56 |

| Table 61. | EQ bypass                                                            | 57 |

| Table 62. | Binary output enable registers                                       | 57 |

| Table 63. | Channel limiter mapping as a function of CxLS bits                   | 57 |

| Table 64. | Channel output mapping as a function of CxOM bits                    | 57 |

| Table 65. | Tone control boost/cut as a function of BTC and TTC bits             | 58 |

| Table 66. | Limiter attack rate as a function of LxA bits                        | 60 |

| Table 67. | Limiter release rate as a function of LxR bits                       | 60 |

| Table 68. | Limiter attack threshold as a function of LxAT bits (AC-mode)        | 61 |

| Table 69. | Limiter release threshold as a function of LxRT bits (AC-mode)       | 61 |

| Table 70. | Limiter attack threshold as a function of LxAT bits (DRC -mode)      | 62 |

| Table 71. | Limiter release threshold as a as a function of LxRT bits (DRC-mode) | 62 |

| Table 72. | RAM block for biquads, mixing, scaling and bass management           | 69 |

| Table 73. | Status register bits                                                 | 71 |

| Table 74. | EQ RAM select                                                        | 72 |

| Table 75. | Anti-clipping and DRC preset                                         | 72 |

| Table 76. | Anti-clipping selection for AMGC[3:2] = 01                           | 72 |

| Table 77. | Biquad filter settings                                               |    |

| Table 78. | PowerSSO-36 EPD dimensions                                           | 86 |

| Table 79. | Document revision history                                            | 88 |

STA369BW List of figures

# List of figures

| -ıgure 1.  | Block diagram                                                    | 1              |

|------------|------------------------------------------------------------------|----------------|

| igure 2.   | Pin connection PowerSSO-36 (top view)                            | 12             |

| igure 3.   | Test circuit                                                     |                |

| Figure 4.  | Demonstration board, 2.0 channels                                |                |

| Figure 5.  | Mono parallel BTL schematic                                      |                |

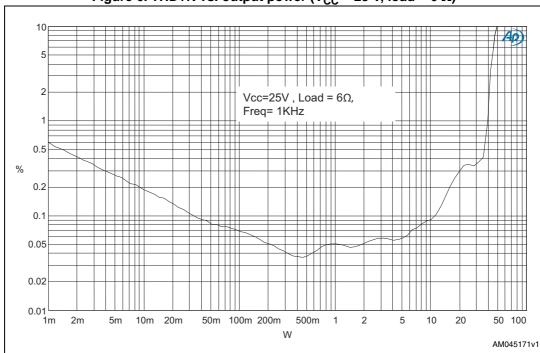

| Figure 6.  | THD+N vs. output power (V <sub>CC</sub> = 25 V, load = 6 W)      |                |

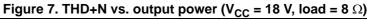

| igure 7.   | THD+N vs. output power (V <sub>CC</sub> = 18 V, load = 8 W)      |                |

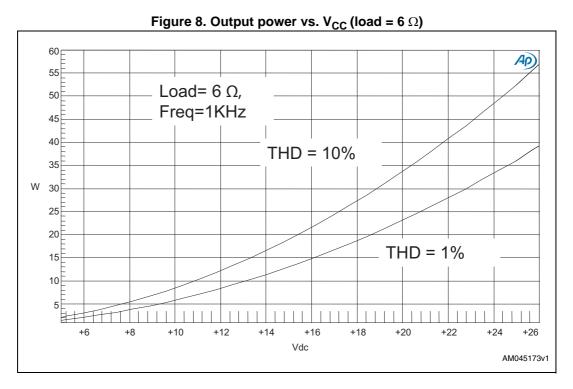

| Figure 8.  | Output power vs. V <sub>CC</sub> (load = 6 W)                    |                |

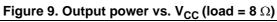

| Figure 9.  | Output power vs. V <sub>CC</sub> (load = 8 W)                    |                |

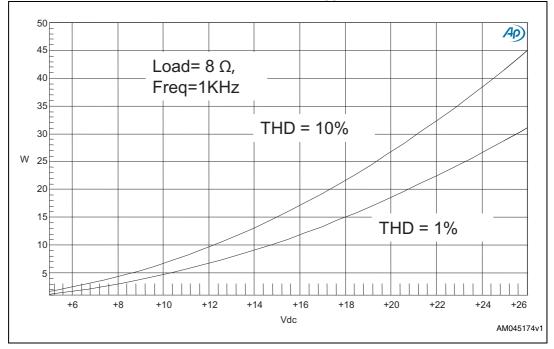

| Figure 10. | Efficiency vs. output power (V <sub>CC</sub> = 25 V, load = 6 W) |                |

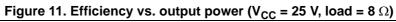

| Figure 11. | Efficiency vs. output power (V <sub>CC</sub> = 25 V, load = 8 W) |                |

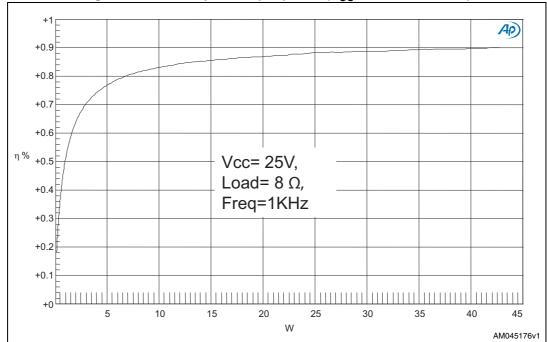

| Figure 12. | THD+N vs. output power (V <sub>CC</sub> = 25 V, load = 3 W)      | 23             |

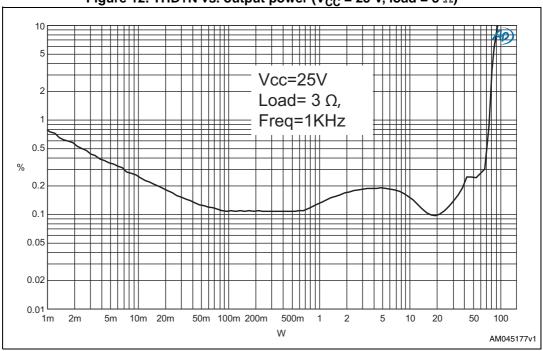

| igure 13.  | Output power vs. V <sub>CC</sub> (load = 3 W)                    | 23             |

| igure 14.  | Efficiency vs. output power (V <sub>CC</sub> = 26 V, load = 3 W) | 24             |

| Figure 15. | Efficiency vs. output power (V <sub>CC</sub> = 18 V, load = 3 W) | 24             |

| Figure 16. | Timing diagram for SAI interface                                 |                |

| igure 17.  | Left and right processing - part 1                               | 26             |

| igure 18.  | Processing - part 2                                              | 27             |

| igure 19.  | Write mode sequence                                              | 30             |

| igure 20.  | Read mode sequence                                               | 30             |

| igure 21.  | OCFG = 00 (default value)                                        | <del>1</del> 6 |

| igure 22.  | OCFG = 01                                                        | <del>1</del> 6 |

| igure 23.  | OCFG = 10                                                        | <del>1</del> 6 |

| igure 24.  | OCFG = 11                                                        | <b>ļ</b> 7     |

| igure 25.  | Output mapping scheme                                            | <b>ļ</b> 7     |

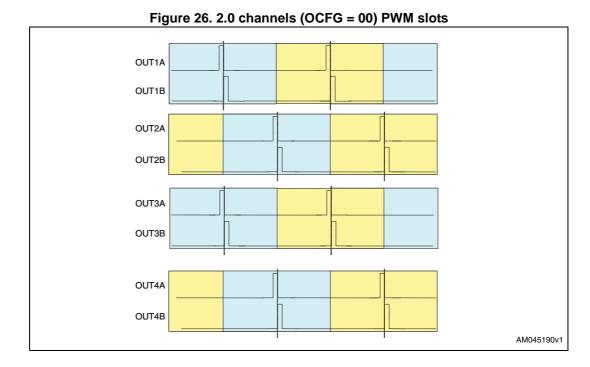

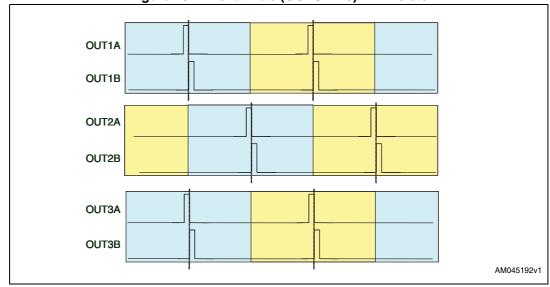

| igure 26.  | 2.0 channels (OCFG = 00) PWM slots                               | 18             |

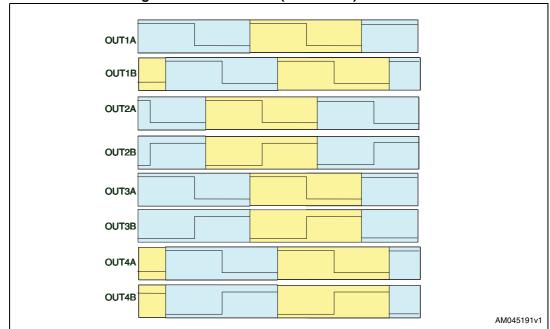

| igure 27.  | 2.1 channels (OCFG = 01) PWM slots                               | 19             |

| igure 28.  | 2.1 channels (OCFG = 10) PWM slots                               | 50             |

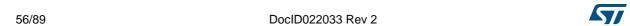

| igure 29.  | Basic limiter and volume flow diagram                            |                |

| igure 30.  | B <sup>2</sup> DRC scheme                                        | 73             |

| Figure 31. | EQDRC scheme                                                     | 75             |

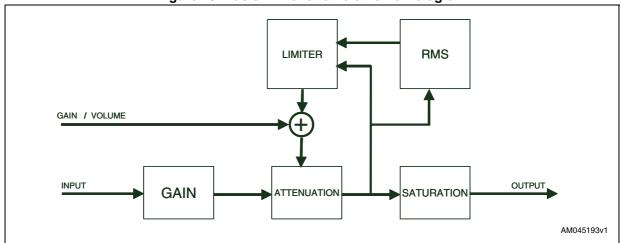

| igure 32.  | Extra resolution volume scheme                                   | 78             |

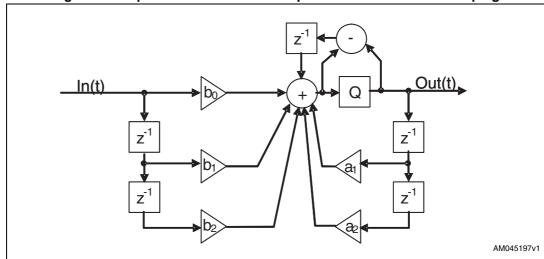

| igure 33.  | Biquad filter structure with quantization error noise-shaping    | 30             |

| igure 34.  | Application scheme for power supplies 8                          | 33             |

| igure 35.  | Output configuration for stereo BTL mode                         |                |

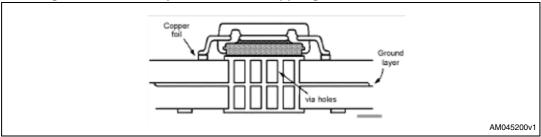

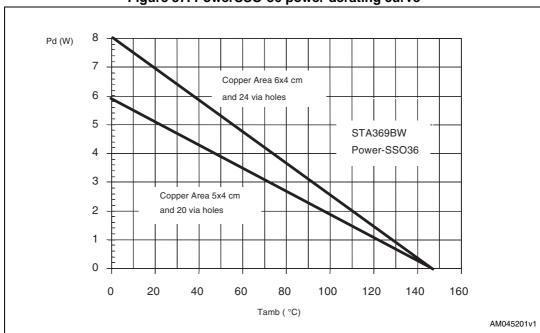

| igure 36.  | Double-layer PCB with 2 copper ground areas and 24 via holes     | 35             |

| igure 37.  | PowerSSO-36 power derating curve                                 | 35             |

| iaure 38.  | PowerSSO-36 EPD outline drawing                                  | 37             |

Description STA369BW

# 1 Description

The STA369BW is an integrated solution of digital audio processing, digital amplifier control, and FFX-power output stage, thereby creating a high-power single-chip FFX<sup>®</sup> solution comprising high-quality, high-efficiency, and all-digital amplification.

The STA369BW is based on an FFX (fully flexible amplification) processor, a proprietary technology from STMicroelectronics. FFX is the evolution and the enlargement of ST's ternary technology: the new processor can be configured to work in ternary, binary differential and phase-shift PWM modulation schemes.

The STA369BW contains the ternary, binary and binary differential implementations, a subset of the full capability of the FFX processor.

The STA369BW is part of the Sound Terminal<sup>®</sup> family that provides full digital audio streaming to the speaker, offering cost effectiveness, low power dissipation and sound enrichment.

The STA369BW power section consists of four independent half-bridges. These can be configured via digital control to operate in different modes. 2.1 channels can be provided by two half-bridges and a single full-bridge, providing up to 2 x 15 W + 1 x 30 W of music output power, by using standard 4 and 8  $\Omega$  speakers. Two channels can be provided by two full-bridges, providing up to 2 x 30 W, by using standard 8  $\Omega$  speaker at 22 V. The IC can also be configured as 2.1 channels with 2 x 30 W provided by the device and external power for FFX power drive. Please refer to the package thermal characteristics and application suggestions for more details.

Also provided in the STA369BW are a full assortment of digital processing features. This includes up to 8 programmable biquads (EQ) per channel. Special digital signal processing techniques are available in order to manage low-frequency quantization noise in case of very low frequency cutoff filter thresholds. The coefficient range -4..4 allows the easy implementation of high shelf filters. Available presets allow the advantage of earlier time-to-market by substantially reducing the amount of software development needed for certain functions. This includes audio preset volume loudness, preset volume curves and preset EQ settings. There are also new advanced AM radio interference reduction modes. The dual-band DRC dynamically equalizes the system to provide speaker linear frequency response regardless of output power level. This feature independently processes the two bands, controlling dynamically the output power level in each band, thus providing better sound clarity.

The serial audio data input interface accepts all possible formats, including the popular I<sup>2</sup>S format. Three channels of FFX processing are provided. This high-quality conversion from PCM audio to FFX PWM switching waveform provides over 100 dB SNR and dynamic range.

10/89 DocID022033 Rev 2

STA369BW **Description**

#### 1.1 **Block diagram**

I<sup>2</sup>C Pro tection curre nt/the rm al I<sup>2</sup>S interface Channel Pow er control Chann el 1B Logic Vo lu me control FFX Regulators Chann el 2B PLL Bias Digita I DSP Power AM045167v1

Figure 1. Block diagram

Pin connections STA369BW

# 2 Pin connections

# 2.1 Connection diagram

Figure 2. Pin connection PowerSSO-36 (top view)

# 2.2 Pin description

Table 2. Pin description

| Pin | Туре  | Name      | Description                                      |

|-----|-------|-----------|--------------------------------------------------|

| 1   | GND   | GND_SUB   | Substrate ground                                 |

| 2   | I     | SA        | I <sup>2</sup> C select address (pull-down)      |

| 3   | I     | TEST_MODE | This pin must be connected to ground (pull-down) |

| 4   | I/O   | VSS       | Internal reference at Vcc-3.3 V                  |

| 5   | I/O   | VCC_REG   | Internal Vcc reference                           |

| 6   | 0     | OUT2B     | Output half-bridge 2B                            |

| 7   | GND   | GND2      | Power negative supply                            |

| 8   | Power | VCC2      | Power positive supply                            |

| 9   | 0     | OUT2A     | Output half-bridge 2A                            |

| 10  | 0     | OUT1B     | Output half-bridge 1B                            |

STA369BW Pin connections

Table 2. Pin description (continued)

| Pin | Туре  | Name        | Description                                                              |

|-----|-------|-------------|--------------------------------------------------------------------------|

| 11  | Power | VCC1        | Power positive supply                                                    |

| 12  | GND   | GND1        | Power negative supply                                                    |

| 13  | 0     | OUT1A       | Output half-bridge 1A                                                    |

| 14  | GND   | GND_REG     | Internal ground reference                                                |

| 15  | Power | VDD         | Internal 3.3 V reference voltage                                         |

| 16  | I     | CONFIG      | Parallel mode command                                                    |

| 17  | 0     | OUT3B/FFX3B | PWM out CH3B / external bridge driver                                    |

| 18  | 0     | OUT3A/FFX3A | PWM out CH3A / external bridge driver                                    |

| 19  | 0     | EAPD/OUT4B  | Power-down for external bridge / PWM out CH4B                            |

| 20  | I/O   | TWARN/OUT4A | Thermal warning from external bridge (pull-up when input) / PWM out CH4A |

| 21  | Power | VDD_DIG     | Digital supply voltage                                                   |

| 22  | GND   | GND_DIG     | Digital ground                                                           |

| 23  | I     | PWRDN       | Power down (pull-up)                                                     |

| 24  | Power | VDD_PLL     | Positive supply for PLL                                                  |

| 25  | I     | FILTER_PLL  | Connection to PLL filter                                                 |

| 26  | GND   | GND_PLL     | Negative supply for PLL                                                  |

| 27  | I     | XTI         | PLL input clock                                                          |

| 28  | I     | BICKI       | I <sup>2</sup> S serial clock                                            |

| 29  | I     | LRCKI       | I <sup>2</sup> S left/right clock                                        |

| 30  | I     | SDI         | I <sup>2</sup> S serial data channels 1 and 2                            |

| 31  | I     | RESET       | Reset (pull-up)                                                          |

| 32  | 0     | INT_LINE    | Fault interrupt                                                          |

| 33  | I/O   | SDA         | I <sup>2</sup> C serial data                                             |

| 34  | I     | SCL         | I <sup>2</sup> C serial clock                                            |

| 35  | GND   | GND_DIG     | Digital ground                                                           |

| 36  | Power | VDD_DIG     | Digital supply voltage                                                   |

# 3 Electrical specifications

### 3.1 Absolute maximum ratings

Table 3. Absolute maximum ratings

| Symbol           | Parameter                           |      | Тур | Max | Unit |

|------------------|-------------------------------------|------|-----|-----|------|

| V <sub>cc</sub>  | Power supply voltage (VCCxA, VCCxB) | -0.3 |     | 30  | V    |

| VDD_DIG          | Digital supply voltage              | -0.3 |     | 4   | V    |

| VDD_PLL          | PLL supply voltage                  | -0.3 |     | 4   |      |

| T <sub>op</sub>  | Operating junction temperature      | -20  |     | 150 | °C   |

| T <sub>stg</sub> | Storage temperature                 | -40  |     | 150 | °C   |

#### Warning:

Stresses beyond those listed in *Table 3* above may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "Recommended operating conditions" are not implied. Exposure to AMR conditions for extended periods may affect device reliability. In the real application, power supplies with nominal values rated within the recommended operating conditions, may rise beyond the maximum operating conditions for a short time when no or very low current is sunk (amplifier in mute state). In this case the reliability of the device is guaranteed, provided that the absolute maximum ratings are not exceeded.

#### 3.2 Thermal data

Table 4. Thermal data

| Symbol                 | Parameter                                      | Min | Тур | Max | Unit |

|------------------------|------------------------------------------------|-----|-----|-----|------|

| R <sub>th j-case</sub> | Thermal resistance junction-case (thermal pad) |     |     | 1.5 | °C/W |

| T <sub>th-sdj</sub>    | Thermal shutdown junction temperature          |     | 150 |     | °C   |

| T <sub>th-w</sub>      | Thermal warning temperature                    |     | 130 |     | °C   |

| T <sub>th-sdh</sub>    | Thermal shutdown hysteresis                    |     | 20  |     | °C   |

| R <sub>th j-amb</sub>  | Thermal resistance junction-ambient (1)        |     |     |     |      |

<sup>1.</sup> See Section 10: Package thermal characteristics on page 85 for details.

14/89 DocID022033 Rev 2

# 3.3 Recommended operating conditions

Table 5. Recommended operating conditions

| Symbol           | Parameter                           | Min | Тур | Max | Unit |

|------------------|-------------------------------------|-----|-----|-----|------|

| V <sub>cc</sub>  | Power supply voltage (VCCxA, VCCxB) | 5   |     | 26  | V    |

| VDD_DIG          | Digital supply voltage              | 2.7 | 3.3 | 3.6 | V    |

| VDD_PLL          | PLL supply voltage                  | 2.7 | 3.3 | 3.6 | V    |

| T <sub>amb</sub> | Ambient temperature                 | -20 |     | +85 | °C   |

# 3.4 Electrical specifications for the digital section

Table 6. Electrical specifications - digital section

| Symbol          | Parameter                                            | Conditions              | Min              | Тур | Max              | Unit |

|-----------------|------------------------------------------------------|-------------------------|------------------|-----|------------------|------|

| I <sub>il</sub> | Low-level input current without pull-up/down device  | Vi = 0 V                |                  | 1   | 5                | μΑ   |

| I <sub>ih</sub> | High-level input current without pull-up/down device | Vi = VDD_DIG<br>= 3.6 V |                  | 1   | 5                | μΑ   |

| V <sub>il</sub> | Low-level input voltage                              |                         |                  |     | 0.2 *<br>VDD_DIG | V    |

| V <sub>ih</sub> | High-level input voltage                             |                         | 0.8 *<br>VDD_DIG |     |                  | V    |

| V <sub>ol</sub> | Low-level output voltage                             | lol=2 mA                |                  |     | 0.4 *<br>VDD_DIG | V    |

| V <sub>oh</sub> | High-level output voltage                            | Ioh=2 mA                | 0.8 *<br>VDD_DIG |     |                  | V    |

| I <sub>pu</sub> | Pull-up/down current                                 |                         | 25               | 66  | 125              | μΑ   |

| R <sub>pu</sub> | Equivalent pull-up/down resistance                   |                         |                  | 50  |                  | kΩ   |

# 3.5 Electrical specifications for the power section

The specifications given in this section are valid for the operating conditions:  $V_{CC}$  = 22 V, f = 1 kHz,  $f_{sw}$  = 384 kHz,  $T_{amb}$  = 25° C and  $R_L$  = 8  $\Omega$ , unless otherwise specified.

Table 7. Electrical specifications - power section

| Symbol            | Parameter                                      | Conditions                                                                            | Min | Тур  | Max | Unit |

|-------------------|------------------------------------------------|---------------------------------------------------------------------------------------|-----|------|-----|------|

|                   | Continuous output power, BTL, ternary          | THD = 1%                                                                              |     | 20   |     | W    |

| Po                | mode                                           | THD = 10%                                                                             |     | 30   |     | VV   |

| PO                | Continuous output power SE, binary             | THD = 1%                                                                              |     | 12   |     | W    |

|                   | mode, $R_L = 4 \Omega$                         | THD = 10%                                                                             |     | 15   |     | VV   |

| R <sub>dsON</sub> | Power Pchannel/Nchannel MOSFET (total bridge)  | I <sub>d</sub> = 1.5 A                                                                |     | 180  | 250 | mΩ   |

| Idss              | Power Pchannel/Nchannel leakage                | VCC = 20 V                                                                            |     |      | 10  | μА   |

| I <sub>LDT</sub>  | Low current dead time (static)                 | Resistive load <sup>(1)</sup>                                                         |     | 8    | 15  | ns   |

| I <sub>HDT</sub>  | High current dead time (dynamic)               | I load <sup>(1)</sup> = 1.5 A                                                         |     | 15   | 30  | ns   |

| t <sub>r</sub>    | Rise time                                      | Resistive load <sup>(1)</sup>                                                         |     | 10   | 18  | ns   |

| t <sub>f</sub>    | Fall time                                      | Resistive load <sup>(1)</sup>                                                         |     | 10   | 18  | ns   |

| V <sub>cc</sub>   | Supply voltage operating voltage               |                                                                                       | 5   |      | 26  | V    |

|                   | Supply current from Vcc in power-down          | PWRDN = 0                                                                             |     | 1    |     | μА   |

| I <sub>vcc</sub>  | Supply current from Vcc in operation           | PCM input signal<br>= -60 dBfs,<br>Switching frequency<br>= 384 kHz,<br>No LC filters |     | 52   | 60  | mA   |

| I <sub>vdd</sub>  | Supply current FFX processing (reference only) | Internal clock = 49.152 MHz                                                           |     | 55   | 70  | mA   |

| llim              | Overcurrent limit                              | (2)                                                                                   | 2.6 | 2.8  |     | Α    |

| Isc               | Short-circuit protection                       | Hi-Z output                                                                           | 3.1 | 3.3  |     | Α    |

| UVL               | Undervoltage protection                        |                                                                                       |     |      | 4.3 | V    |

| OVP               | Overvoltage protection                         |                                                                                       |     | 29   |     | V    |

| t <sub>min</sub>  | Output minimum pulse width                     | No load                                                                               |     | 100  |     | ns   |

| DR                | Dynamic range                                  |                                                                                       |     | 100  |     | dB   |

| CND               | Signal-to-noise ratio, ternary mode            | A-Weighted                                                                            |     | 100  |     | dB   |

| SNR               | Signal-to-noise ratio binary mode              |                                                                                       |     | 90   |     | dB   |

| THD+N             | Total harmonic distortion + noise              | FFX stereo mode,<br>Po = 1 W<br>f = 1 kHz                                             |     | 0.09 |     | %    |

16/89 DocID022033 Rev 2

| Symbol            | Parameter                     | Conditions                                                                              | Min | Тур | Max | Unit |  |

|-------------------|-------------------------------|-----------------------------------------------------------------------------------------|-----|-----|-----|------|--|

| X <sub>TALK</sub> | Crosstalk                     | FFX stereo mode,<br><5 kHz<br>One channel driven<br>at 1 W<br>Other channel<br>measured |     | 80  |     | dB   |  |

| PSRR              | Power Supply Rejection Ratio  | FFX stereo mode,<br><5 kHz<br>VRipple01V RMS<br>Audio input = dither<br>only            |     | 80  |     | dB   |  |

| n                 | Peak efficiency, FFX mode     | Po = 2 x 25 W<br>into 8 Ω                                                               |     | 90  |     | %    |  |

| η                 | Peak efficiency, binary modes | Po = 2 x 10W into 4Ω<br>+ 1 x 20W into 8 $\Omega$                                       |     | 86  |     | /0   |  |

Table 7. Electrical specifications - power section (continued)

<sup>2.</sup> Limit current if the register (OCRB Section 8.3.3) overcurrent warning detect adjustment bypass is enabled. When disabled refer to the Isc.

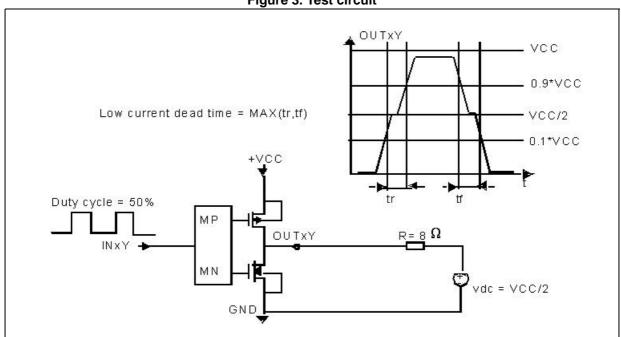

Figure 3. Test circuit

<sup>1.</sup> Refer to Figure 3: Test circuit.

STA369BW **Characterization curves**

#### **Characterization curves** 4

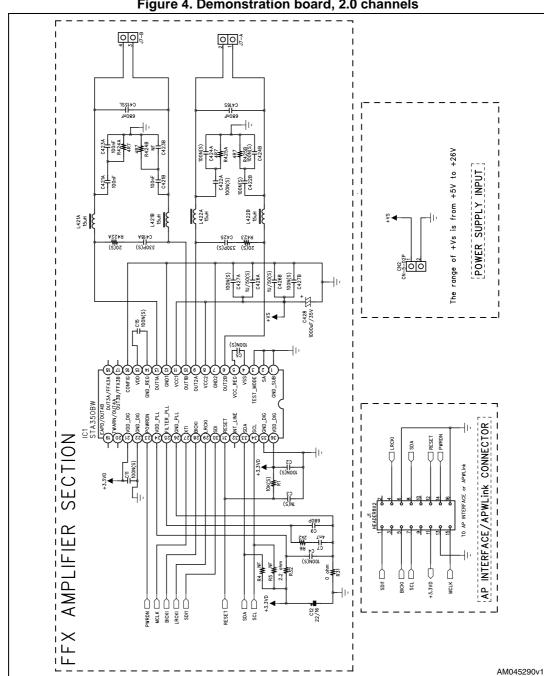

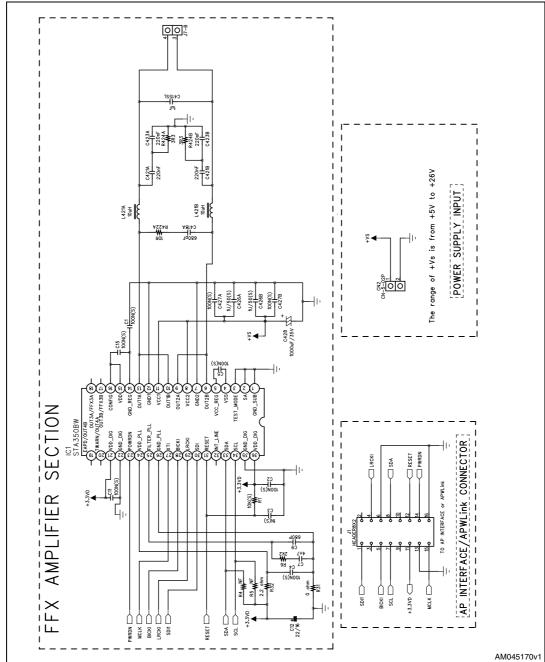

The following characterization curves were made using the STA369BW demonstration board with 2.0 channels (refer to the schematic in Figure 6) under the following test conditions:

$V_{CC}$  = 22 V, f = 1 kHz,  $f_{SW}$  = 384 kHz, Tamb = 25 °C and RL = 8  $\Omega$ , unless otherwise specified.

Figure 4. Demonstration board, 2.0 channels

STA369BW Characterization curves

Figure 5. Mono parallel BTL schematic

Characterization curves STA369BW

Figure 6. THD+N vs. output power (V<sub>CC</sub> = 25 V, load = 6  $\Omega$ )

Characterization curves STA369BW

Figure 10. Efficiency vs. output power ( $V_{CC}$  = 25 V, load = 6  $\Omega$ )

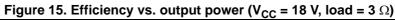

# 4.1 Mono parallel BTL characteristics

Figure 12. THD+N vs. output power ( $V_{CC}$  = 25 V, load = 3  $\Omega$ )

Figure 13. Output power vs.  $V_{CC}$  (load = 3  $\Omega$ )

Characterization curves STA369BW

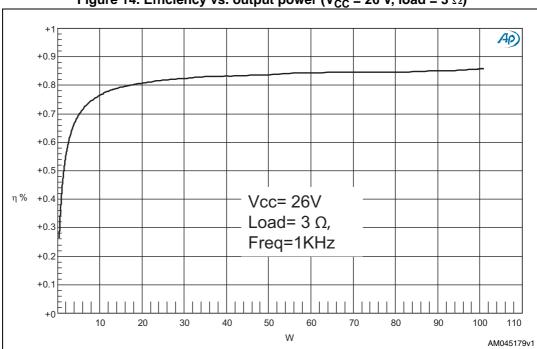

Figure 14. Efficiency vs. output power ( $V_{CC}$  = 26 V, load = 3  $\Omega$ )

STA369BW Serial audio interface

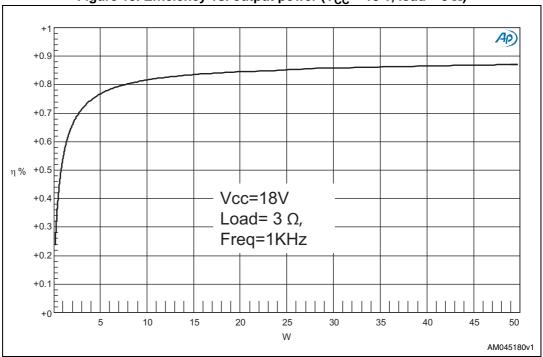

### 5 Serial audio interface

The STA369BW audio serial input interface was designed to interface with standard digital audio components and to accept a number of serial data formats. The STA369BW always acts as the slave when receiving audio input from standard digital audio components. Serial data for two channels is provided using three inputs: left/right clock LRCKI, serial clock BICKI, and serial data SDI12.

The SAI bit and the SAIFB bit are used to specify the serial data format. The default serial data format is I<sup>2</sup>S, MSB-first.

### 5.0.1 Timings

In the STA369BW the BICKI and LRCKI pins are configured as inputs and they must be supplied by the external peripheral.

Figure 16. Timing diagram for SAI interface

Table 8. Timing parameters for slave mode

| Symbol            | Parameter                               | Min | Тур | Max | Unit |

|-------------------|-----------------------------------------|-----|-----|-----|------|

| t <sub>BCy</sub>  | BICK cycle time                         | 80  | -   | i   | ns   |

| t <sub>BCH</sub>  | BICK pulse width high                   | 40  | -   | -   | ns   |

| t <sub>BCL</sub>  | BICK pulse width low                    | 40  | -   | -   | ns   |

| t <sub>LRSU</sub> | LRCKI setup time to BICKI strobing edge | 40  | -   | -   | ns   |

| t <sub>LRH</sub>  | LRCKI hold time to BICKI strobing edge  | 40  | -   | -   | ns   |

| t <sub>LRJT</sub> | LRCKI Jitter Tolerance                  |     |     | 40  | ns   |

#### 5.0.2 Delay serial clock enable

To tolerate anomalies in some I<sup>2</sup>S master devices, a PLL clock cycle delay can be added to the BICKI signal before the SAI interface.

#### 5.0.3 Channel input mapping

Each channel received via I<sup>2</sup>S can be mapped to any internal processing channel via the channel input mapping registers. This allows for flexibility in processing. The default settings of these registers map each I<sup>2</sup>S input channel to its corresponding processing channel.

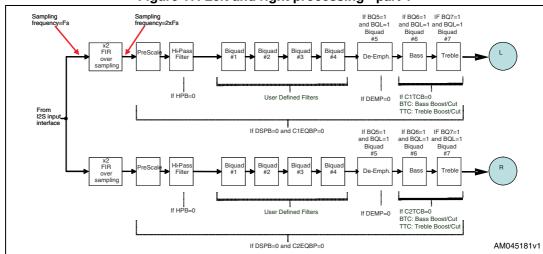

# 6 Processing data paths

Figure 17 and 18 illustrate the data processing paths inside the STA369BW.

The whole processing chain is composed of two consecutive sections. In the first one, dual-channel processing is implemented, as described below, and then each channel is fed into the post-mixing block allowing to generate either a third channel (typically used in 2.1 output configuration and with crossover filters enabled) or to have the channels processed by the dual-band DRC block (2.0 output configuration with crossover filters used to define the cutoff frequency of the two bands).

The first section begins with a 2x oversampling FIR filter allowing for 2\*Fs audio processing. Then a selectable high-pass filter removes the DC level (enabled if HFB=0).

The channel 1 and 2 processing chain can include up to 8 filters, depending on the selected configuration (bits BQL, BQ5, BQ6, BQ7 and XO[3:0]).

By default 4 independent filters per channel are enabled, plus the pre-configured De-Emphasis, Bass and Treble controls (BQL=0, BQ5=0, BQ6=0, BQ7=0).

If the coefficient sets are linked (BQL=1) it's then possible to use De-Emphasis, Bass and Treble filters in a user-defined configuration (provided the relevant BQx bits are set). In other words, both channels will use the same processing coefficients and can have up to 7 filters each. Note that if BQL=0 the BQx bits are ignored and the 5th, 6th and 7th filters are configured as, respectively, De-Emphasis, Bass and Treble controls.

Moreover the common 8th filter, from the subsequent processing section, can be available on both channels (provided the pre-defined crossover frequencies are not used, XO[3:0]=0, and the dual-band DRC is not used).

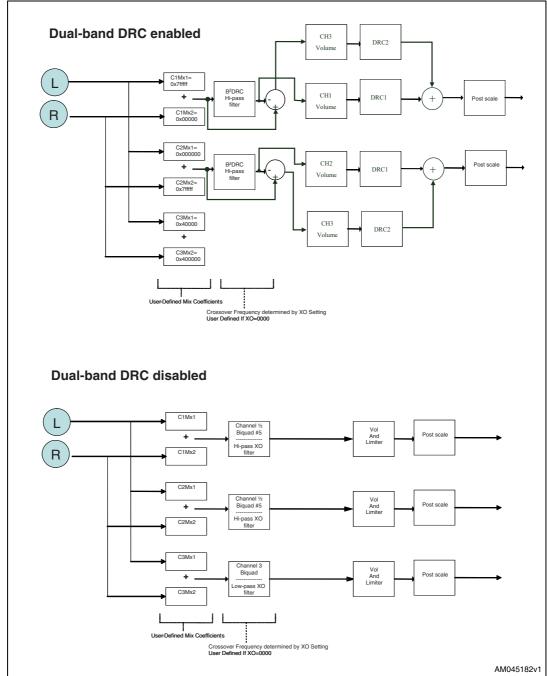

In the second section mixing and crossover filters are available. If  $B^2DRC$  is not enabled (*Figure 18*), they are fully user-programmable and allow generating a third channel (2.1 outputs). Alternatively, in  $B^2DRC$  mode, those blocks will be used to split the sub-band and define the cutoff frequencies of the two bands. A prescaler and a final post-scaler allow full control over the signal dynamic respectively before and after the filtering stages. A mixer function is also available.

Figure 17. Left and right processing - part 1

57

Figure 18. Processing - part 2

# 7 I<sup>2</sup>C bus specification

The STA369BW supports the I<sup>2</sup>C protocol via the input ports SCL and SDA\_IN (master to slave) and the output port SDA\_OUT (slave to master). This protocol defines any device that sends data to the bus as a transmitter and any device that reads the data as a receiver. The device that controls the data transfer is known as the master and the other as the slave. The master always starts the transfer and provides data to the serial clock for synchronization. The STA369BW is always a slave device in all of its communications. It supports up to 400 kb/sec rate (fast-mode bit rate). The STA369BW I<sup>2</sup>C is a slave-only interface. The I<sup>2</sup>C interface works properly only in the case that the master clock generated by the PLL has a frequency 10 times higher compared to the frequency of the applied SCL signal.

### 7.1 Communication protocol

#### 7.1.1 Data transition or change

Data changes on the SDA line must only occur when the SCL clock is low. An SDA transition while the clock is high is used to identify a START or STOP condition.

#### 7.1.2 Start condition

START is identified by a high-to-low transition of the data bus SDA signal while the clock signal SCL is stable in the high state. A START condition must precede any command for data transfer.

#### 7.1.3 Stop condition

STOP is identified by a low-to-high transition of the data bus SDA signal while the clock signal SCL is stable in the high state. A STOP condition terminates communication between the STA369BW and the bus master.

#### 7.1.4 Data input

During data input the STA369BW samples the SDA signal on the rising edge of clock SCL. For correct device operation the SDA signal must be stable during the rising edge of the clock and the data can change only when the SCL line is low.

## 7.2 Device addressing

To start communication between the master and the STA369BW, the master must initiate a start condition. Following this, the master sends 8 bits (MSB first), corresponding to the device select address and read or write mode, to the SDA line.

The seven most significant bits are the device address identifiers, corresponding to the  $I^2C$  bus definition. In the STA369BW the  $I^2C$  interface has two device addresses depending on the SA port configuration, 0x38 when SA = 0, and 0x3A when SA = 1.

The eighth bit (LSB) identifies the read or write operation RW. This bit is set to 1 in read mode and to 0 for write mode. After a START condition the STA369BW identifies on the bus the device address and if a match is found, it acknowledges the identification on the SDA

DocID022033 Rev 2

bus during the 9th bit time. The byte following the device identification byte is the internal space address.

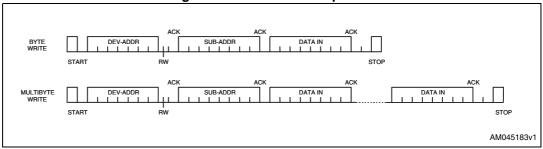

### 7.3 Write operation

Following the START condition the master sends a device select code with the RW bit set to 0. The STA369BW acknowledges this and then writes the byte of the internal address. After receiving the internal byte address the STA369BW again responds with an acknowledgement.

#### 7.3.1 Byte write

In the byte write mode the master sends one data byte which is acknowledged by the STA369BW. The master then terminates the transfer by generating a STOP condition.

#### 7.3.2 Multi-byte write

The multi-byte write modes can start from any internal address. The master generating a STOP condition terminates the transfer.

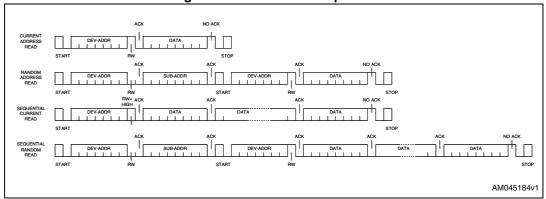

### 7.4 Read operation

#### 7.4.1 Current address byte read

Following the START condition the master sends a device select code with the RW bit set to 1. The STA369BW acknowledges this and then responds by sending one byte of data. The master then terminates the transfer by generating a STOP condition.

#### 7.4.2 Current address multi-byte read

The multi-byte read modes can start from any internal address. Sequential data bytes are read from sequential addresses within the STA369BW. The master acknowledges each data byte read and then generates a STOP condition, terminating the transfer.

#### 7.4.3 Random address byte read

Following the START condition the master sends a device select code with the RW bit set to 0. The STA369BW acknowledges this and then the master writes the internal address byte. After receiving the internal byte address, the STA369BW again responds with an acknowledgement. The master then initiates another START condition and sends the device select code with the RW bit set to 1. The STA369BW acknowledges this and then responds by sending one byte of data. The master then terminates the transfer by generating a STOP condition.

#### 7.4.4 Random address multi-byte read

The multi-byte read modes can start from any internal address. Sequential data bytes are read from sequential addresses within the STA369BW. The master acknowledges each data byte read and then generates a STOP condition, terminating the transfer.

### 7.4.5 Write mode sequence

Figure 19. Write mode sequence

### 7.4.6 Read mode sequence

Figure 20. Read mode sequence

# 8 Register description

Table 9. Register summary

| Addr | Name         | D7       | D6       | D5       | D4       | D3       | D2       | D1       | D0           |

|------|--------------|----------|----------|----------|----------|----------|----------|----------|--------------|

| 0x00 | CONFA        | FDRB     | TWAB     | TWRB     | IR1      | IR0      | MCS2     | MCS1     | MCS0         |

| 0x01 | CONFB        | C2IM     | C1IM     | DSCKE    | SAIFB    | SAI3     | SAI2     | SAI1     | SAI0         |

| 0x02 | CONFC        | OCRB     |          | CSZ3     | CSZ2     | CSZ1     | CSZ0     | OM1      | OM0          |

| 0x03 | CONFD        | SME      | ZDE      | DRC      | BQL      | PSL      | DSPB     | DEMP     | HPB          |

| 0x04 | CONFE        | SVE      | ZCE      | DCCV     | PWMS     | AME      | NSBW     | MPC      | MPCV         |

| 0x05 | CONFF        | EAPD     | PWDN     | ECLE     | LDTE     | BCLE     | IDE      | OCFG1    | OCFG0        |

| 0x06 | MUTE/LO<br>C | LOC1     | LOC0     | Reserved | Reserved | СЗМ      | C2M      | C1M      | MMUTE        |

| 0x07 | MVOL         | MV7      | MV6      | MV5      | MV4      | MV3      | MV2      | MV1      | MV0          |

| 0x08 | C1VOL        | C1V7     | C1V6     | C1V5     | C1V4     | C1V3     | C1V2     | C1V1     | C1V0         |

| 0x09 | C2VOL        | C2V7     | C2V6     | C2V5     | C2V4     | C2V3     | C2V2     | C2V1     | C2V0         |

| 0x0A | C3VOL        | C3V7     | C3V6     | C3V5     | C3V4     | C3V3     | C3V2     | C3V1     | C3V0         |

| 0x0B | AUTO1        | Reserved | Reserved | AMGC1    | AMGC0    | Reserved | Reserved | Reserved | Reserve<br>d |

| 0x0C | AUTO2        | XO3      | XO2      | XO1      | XO0      | AMAM2    | AMAM1    | AMAM0    | AMAME        |

| 0x0D | AUTO3        |          |          |          | Rese     | rved     |          |          |              |

| 0x0E | C1CFG        | C1OM1    | C1OM0    | C1LS1    | C1LS0    | C1BO     | C1VBP    | C1EQBP   | C1TCB        |

| 0x0F | C2CFG        | C2OM1    | C2OM0    | C2LS1    | C2LS0    | C2BO     | C2VBP    | C2EQBP   | C2TCB        |

| 0x10 | C3CFG        | C3OM1    | СЗОМО    | C3LS1    | C3LS0    | СЗВО     | C3VBP    | Reserved | Reserve<br>d |

| 0x11 | TONE         | TTC3     | TTC2     | TTC1     | TTC0     | BTC3     | BTC2     | BTC1     | BTC0         |

| 0x12 | L1AR         | L1A3     | L1A2     | L1A1     | L1A0     | L1R3     | L1R2     | L1R1     | L1R0         |

| 0x13 | L1ATRT       | L1AT3    | L1AT2    | L1AT1    | L1AT0    | L1RT3    | L1RT2    | L1RT1    | L1RT0        |

| 0x14 | L2AR         | L2A3     | L2A2     | L2A1     | L2A0     | L2R3     | L2R2     | L2R1     | L2R0         |

| 0x15 | L2ATRT       | L2AT3    | L2AT2    | L2AT1    | L2AT0    | L2RT3    | L2RT2    | L2RT1    | L2RT0        |

| 0x16 | CFADDR       | Reserved | Reserved | CFA5     | CFA4     | CFA3     | CFA2     | CFA1     | CFA0         |

| 0x17 | B1CF1        | C1B23    | C1B22    | C1B21    | C1B20    | C1B19    | C1B18    | C1B17    | C1B16        |

| 0x18 | B1CF2        | C1B15    | C1B14    | C1B13    | C1B12    | C1B11    | C1B10    | C1B9     | C1B8         |

| 0x19 | B1CF3        | C1B7     | C1B6     | C1B5     | C1B4     | C1B3     | C1B2     | C1B1     | C1B0         |

| 0x1A | B2CF1        | C2B23    | C2B22    | C2B21    | C2B20    | C2B19    | C2B18    | C2B17    | C2B16        |

| 0x1B | B2CF2        | C2B15    | C2B14    | C2B13    | C2B12    | C2B11    | C2B10    | C2B9     | C2B8         |

| 0x1C | B2CF3        | C2B7     | C2B6     | C2B5     | C2B4     | C2B3     | C2B2     | C2B1     | C2B0         |

| 0x1D | A1CF1        | C3B23    | C3B22    | C3B21    | C3B20    | C3B19    | C3B18    | C3B17    | C3B16        |

Register description STA369BW

Table 9. Register summary (continued)

| Addr | Name     | D7          | D6       | D5       | D4       | D3       | D2       | D1       | D0           |

|------|----------|-------------|----------|----------|----------|----------|----------|----------|--------------|

| 0x1E | A1CF2    | C3B15       | C3B14    | C3B13    | C3B12    | C3B11    | C3B10    | C3B9     | C3B8         |

| 0x1F | A1CF3    | C3B7        | C3B6     | C3B5     | C3B4     | C3B3     | C3B2     | C3B1     | C3B0         |

| 0x20 | A2CF1    | C4B23       | C4B22    | C4B21    | C4B20    | C4B19    | C4B18    | C4B17    | C4B16        |

| 0x21 | A2CF2    | C4B15       | C4B14    | C4B13    | C4B12    | C4B11    | C4B10    | C4B9     | C4B8         |

| 0x22 | A2CF3    | C4B7        | C4B6     | C4B5     | C4B4     | C4B3     | C4B2     | C4B1     | C4B0         |

| 0x23 | B0CF1    | C5B23       | C5B22    | C5B21    | C5B20    | C5B19    | C5B18    | C5B17    | C5B16        |

| 0x24 | B0CF2    | C5B15       | C5B14    | C5B13    | C5B12    | C5B11    | C5B10    | C5B9     | C5B8         |

| 0x25 | B0CF3    | C5B7        | C5B6     | C5B5     | C5B4     | C5B3     | C5B2     | C5B1     | C5B0         |

| 0x26 | CFUD     | Reserved    |          |          |          | RA       | R1       | WA       | W1           |

| 0x27 | MPCC1    | MPCC15      | MPCC14   | MPCC13   | MPCC12   | MPCC11   | MPCC10   | MPCC9    | MPCC8        |

| 0x28 | MPCC2    | MPCC7       | MPCC6    | MPCC5    | MPCC4    | MPCC3    | MPCC2    | MPCC1    | MPCC0        |

| 0x29 | DCC1     | DCC15       | DCC14    | DCC13    | DCC12    | DCC11    | DCC10    | DCC9     | DCC8         |

| 0x2A | DCC2     | DCC7        | DCC6     | DCC5     | DCC4     | DCC3     | DCC2     | DCC1     | DCC0         |

| 0x2B | FDRC1    | FDRC15      | FDRC14   | FDRC13   | FDRC12   | FDRC11   | FDRC10   | FDRC9    | FDRC8        |

| 0x2C | FDRC2    | FDRC7       | FDRC6    | FDRC5    | FDRC4    | FDRC3    | FDRC2    | FDRC1    | FDRC0        |

| 0x2D | STATUS   | PLLUL       | FAULT    | UVFAULT  | OVFAULT  | OCFAULT  | OCWARN   | TFAULT   | TWARN        |

| 0x2E | Reserved | Rese        | erved    | RO1BACT  | R5BACT   | R4BACT   | R3BACT   | R2BACT   | R1BACT       |

| 0x2F | Reserved | Rese        | erved    | R01BEND  | R5BEND   | R4BEND   | R3BEND   | R2BEND   | R1BEND       |

| 0x30 | Reserved |             | Reserved |          | R5BBAD   | R4BBAD   | R3BBAD   | R2BBAD   | R1BBAD       |

| 0x31 | EQCFG    | XOB         | Reserved | Reserved | AMGC3    | AMGC2    | Reserved | SEL1     | SEL0         |

| 0x32 | EATH1    | EATHEN<br>1 | EATH1[6] | EATH1[5] | EATH1[4] | EATH1[3] | EATH1[2] | EATH1[1] | EATH1[0      |

| 0x33 | ERTH1    | ERTHEN<br>1 | ERTH1[6] | ERTH1[5] | ERTH1[4] | ERTH1[3] | ERTH1[2] | ERTH1[1] | ERTH1[<br>0] |

| 0x34 | EATH2    | EATHEN<br>2 | EATH2[6] | EATH2[5] | EATH2[4] | EATH2[3] | EATH2[2] | EATH2[1] | EATH2[0      |

| 0x35 | ERTH2    | ERTHEN<br>2 | ERTH2[6] | ERTH2[5] | ERTH2[4] | ERTH2[3] | ERTH2[2] | ERTH2[1] | ERTH2[<br>0] |

| 0x36 | CONFX    | MDRC[1]     | MDRC[0]  | PS48DB   | XAR1     | XAR2     | BQ5      | BQ6      | BQ7          |

| 0x37 | SVCA     | Reserved    | Reserved | SVUPE    | SVUP[4]  | SVUP[3]  | SVUP[2]  | SVUP[1]  | SVUP[0]      |

| 0x38 | SVCB     | Reserved    | Reserved | SVDWE    | SVDW[4]  | SVDW[3]  | SVDW[2]  | SVDW[1]  | SVDW[0]      |

| 0x39 | RMS0A    | R_C0[23]    | R_C0[22] | R_C0[21] | R_C0[20] | R_C0[19] | R_C0[18] | R_C0[17] | R_C0[16<br>] |

| 0x3A | RMS0B    | R_C0[15]    | R_C0[14] | R_C0[13] | R_C0[12] | R_C0[11] | R_C0[10] | R_C0[9]  | R_C0[8]      |

| 0x3B | RMS0C    | R_C0[7]     | R_C0[6]  | R_C0[5]  | R_C0[4]  | R_C0[3]  | R_C0[2]  | R_C0[1]  | R_C0[0]      |

Table 9. Register summary (continued)

| Addr | Name      | D7       | D6          | D5           | D4        | D3       | D2            | D1          | D0           |

|------|-----------|----------|-------------|--------------|-----------|----------|---------------|-------------|--------------|

| 0x3C | RMS1A     | R_C1[23] | R_C1[22]    | R_C1[21]     | R_C1[20]  | R_C1[19] | R_C1[18]      | R_C1[17]    | R_C1[16<br>] |

| 0x3D | RMS1B     | R_C1[15] | R_C1[14]    | R_C1[13]     | R_C1[12]  | R_C1[11] | R_C1[10]      | R_C1[9]     | R_C1[8]      |

| 0x3E | RMS1C     | R_C1[7]  | R_C1[6]     | R_C1[5]      | R_C1[4]   | R_C1[3]  | R_C1[2]       | R_C1[1]     | R_C1[0]      |

| 0x3F | EVOLRES   | VRESEN   | VRESTG      | C3VR[1]      | C3VR[0]   | C2VR[1]  | C2VR[0]       | C1VR[1]     | C1VR[0]      |

| 0x40 | Reserved  |          |             |              |           |          |               |             |              |

| 0x41 | Reserved  |          |             |              |           |          |               |             |              |

| 0x42 | Reserved  |          |             |              |           |          |               |             |              |

| 0x43 | Reserved  |          |             |              |           |          |               |             |              |

| 0x44 | Reserved  |          |             |              |           |          |               |             |              |

| 0x45 | Reserved  |          |             |              |           |          |               |             |              |

| 0x46 | Reserved  |          |             |              |           |          |               |             |              |

| 0x47 | Reserved  |          |             |              |           |          |               |             |              |

| 0x48 | NSHAPE    | NSHXEN   | NSHB7E<br>N | NSHB6EN      | NSHB5EN   | NSHB4EN  | NSHB3E<br>N   | NSHB2E<br>N | NSHB1E<br>N  |

| 0x49 | CXT[B4B1] | CXTB4[1] | CXTB4[0]    | CXTB3[1]     | CXTB3[0]  | CXTB2[1] | CXTB2[0]      | CXTB1[1]    | CXTB1[0      |

| 0x4A | CXT[B7B5  | Reserved | Reserved    | CXTB7[1]     | CXTB7[0]  | CXTB6[1] | CXTB6[0]      | CXTB5[1]    | CXTB5[0      |

| 0x4B | MISC1     | RPDNEN   | NSHHPE<br>N | BRIDGOF<br>F | Reserved  | Reserved | CPWMEN        | Reserved    | Reserve<br>d |

| 0x4C | MISC2     | Reserved | Reserved    | Reserved     | PNDLSL[2] | PNDLSL[1 | PNDLSL[<br>0] | Reserved    | Reserve<br>d |

| 0x4D | Reserved  |          |             |              |           |          |               |             |              |

| 0x4E | Reserved  |          |             |              |           |          |               |             |              |

| 0x4F | Reserved  |          |             |              |           |          |               |             |              |

| 0x50 | Reserved  |          |             |              |           |          |               |             |              |

| 0x51 | Reserved  |          |             |              |           |          |               |             |              |

| 0x52 | Reserved  |          |             |              |           |          |               |             |              |

| 0x53 | Reserved  |          |             |              |           |          |               |             |              |

| 0x54 | Reserved  |          |             |              |           |          |               |             |              |

| 0x55 | Reserved  |          |             |              |           |          |               |             |              |

| 0x56 | Reserved  |          |             |              |           |          |               |             | _            |

Register description STA369BW

# 8.1 Configuration register A (addr 0x00)

| D7   | D6   | D5   | D4  | D3  | D2   | D1   | D0   |

|------|------|------|-----|-----|------|------|------|

| FDRB | TWAB | TWRB | IR1 | IR0 | MCS2 | MCS1 | MCS0 |

| 0    | 1    | 1    | 0   | 0   | 0    | 1    | 1    |

#### 8.1.1 Master clock select

Table 10. Master clock select

| Bit | R/W | RST | Name | Description                                                                                 |

|-----|-----|-----|------|---------------------------------------------------------------------------------------------|

| 0   | R/W | 1   | MCS0 |                                                                                             |

| 1   | R/W | 1   | MCS1 | Selects the ratio between the input I <sup>2</sup> S sampling frequency and the input clock |

| 2   | R/W | 0   | MCS2 |                                                                                             |

The STA369BW supports sampling rates of 32 kHz, 44.1 kHz, 48 kHz, 88.2 kHz, 96 kHz, 176.4 kHz, and 192 kHz. Therefore the internal clock is:

- 32.768 MHz for 32 kHz

- 45.1584 MHz for 44.1 kHz, 88.2 kHz, and 176.4 kHz

- 49.152 MHz for 48 kHz, 96 kHz, and 192 kHz

The external clock frequency provided to the XTI pin must be a multiple of the input sampling frequency ( $f_s$ ).

The relationship between the input clock and the input sampling rate is determined by both the MCSx and the IR (input rate) register bits. The MCSx bits determine the PLL factor generating the internal clock and the IR bit determines the oversampling ratio used internally.

Table 11. Input sampling rates

| Input sampling rate  fs (kHz) | IR |          | MCS[2:0] |          |          |          |          |  |  |

|-------------------------------|----|----------|----------|----------|----------|----------|----------|--|--|

|                               |    | 101      | 100      | 011      | 010      | 001      | 000      |  |  |

| 32, 44.1, 48                  | 00 | 576 * fs | 128 * fs | 256 * fs | 384 * fs | 512 * fs | 768 * fs |  |  |

| 88.2, 96                      | 01 | NA       | 64 * fs  | 128 * fs | 192 * fs | 256 * fs | 384 * fs |  |  |

| 176.4, 192                    | 1X | NA       | 32 * fs  | 64 * fs  | 96 * fs  | 128 * fs | 192 * fs |  |  |

#### 8.1.2 Interpolation ratio select

Table 12. Internal interpolation ratio

| Bit | R/W | RST | Name     | Description                                                                             |

|-----|-----|-----|----------|-----------------------------------------------------------------------------------------|

| 4:3 | R/W | 00  | IR [1:0] | Selects internal interpolation ratio based on input I <sup>2</sup> S sampling frequency |

The STA369BW has variable interpolation (oversampling) settings such that internal processing and FFX output rates remain consistent. The first processing block interpolates by either 2-times or 1-time (pass-through) or provides a 2-times downsample. The oversampling ratio of this interpolation is determined by the IR bits.

Table 13. IR bit settings as a function of input sampling rate

| Input sampling rate fs (kHz) | IR | 1st stage interpolation ratio |

|------------------------------|----|-------------------------------|

| 32                           | 00 | 2-times oversampling          |

| 44.1                         | 00 | 2-times oversampling          |

| 48                           | 00 | 2-times oversampling          |

| 88.2                         | 01 | Pass-through                  |

| 96                           | 01 | Pass-through                  |

| 176.4                        | 10 | 2-times downsampling          |

| 192                          | 10 | 2-times downsampling          |

|                              |    |                               |

#### 8.1.3 Thermal warning recovery bypass

Table 14. Thermal warning recovery bypass

| Bit | R/W | RST | Name | Description                                                            |

|-----|-----|-----|------|------------------------------------------------------------------------|

| 5   | R/W | 1   | IWRR | Thermal warning recovery enabled     Thermal warning recovery disabled |

If the thermal warning adjustment is enabled (TWAB = 0), then the thermal warning recovery determines if the -3 dB output limit is removed when thermal warning is negative.

If TWRB = 0 and TWAB = 0, then when a thermal warning disappears the -3 dB output limit is removed and the gain is added back to the system. If TWRB = 1 and TWAB = 0, then when a thermal warning disappears the -3 dB output limit remains until TWRB is changed to zero or the device is reset.

#### 8.1.4 Thermal warning adjustment bypass

Table 15. Thermal warning adjustment bypass

| Bit | R/W | RST | Name | Description                                                                |

|-----|-----|-----|------|----------------------------------------------------------------------------|

| 6   | R/W | 1   |      | Thermal warning adjustment enabled     Thermal warning adjustment disabled |

Register description STA369BW

The on-chip STA369BW power output block provides feedback to the digital controller using inputs to the power control block. Input TWARN is used to indicate a thermal warning condition. When TWARN is asserted (set to 0) for a period of time greater than 400 ms, the power control block forces a -3 dB output limit (determined by TWOCL in the coefficient RAM) to the modulation limit in an attempt to eliminate the thermal warning condition. Once the thermal warning output limit adjustment is applied, it remains in this state until reset, unless FDRB = 0.

#### 8.1.5 Fault detect recovery bypass

Table 16. Fault detect recovery bypass

| Bit | R/W | RST | Name | Description                                                      |

|-----|-----|-----|------|------------------------------------------------------------------|

| 7   | R/W | 0   | FDRB | fault detect recovery enabled     fault detect recovery disabled |

The on-chip STA369BW power output block provides feedback to the digital controller using inputs to the power control block. The FAULT input is used to indicate a fault condition (either overcurrent or thermal). When FAULT is asserted (set to 0), the power control block attempts a recovery from the fault by asserting the tri-state output (setting it to 0 which directs the power output block to begin recovery), holds it at 0 for period of time in the range of 0.1 ms to 1 second as defined by the fault-detect recovery constant register (FDRC registers 0x29-0x2A), then toggles it back to 1. This sequence is repeated as long as the fault indication exists. This feature is enabled by default but can be bypassed by setting the FDRB control bit to 1.

# 8.2 Configuration register B (addr 0x01)

| D7   | D6   | D5    | D4    | D3   | D2   | D1   | D0   |

|------|------|-------|-------|------|------|------|------|

| C2IM | C1IM | DSCKE | SAIFB | SAI3 | SAI2 | SAI1 | SAI0 |

| 1    | 0    | 0     | 0     | 0    | 0    | 0    | 0    |

#### 8.2.1 Serial audio input interface format

Table 17. Serial audio input interface

| Bit | R/W | RST | Name | Description                                                                 |

|-----|-----|-----|------|-----------------------------------------------------------------------------|

| 0   | R/W | 0   | SAI0 |                                                                             |

| 1   | R/W | 0   | SAI1 | Determines the interface format of the input serial digital audio interface |

| 2   | R/W | 0   | SAI2 |                                                                             |

| 3   | R/W | 0   | SAI3 |                                                                             |

#### 8.2.2 Serial data interface

The STA369BW audio serial input was designed to interface with standard digital audio components and to accept a number of serial data formats. The STA369BW always acts as the slave when receiving audio input from standard digital audio components. Serial data for two channels is provided using three inputs: left/right clock LRCKI, serial clock BICKI, and serial data 1 and 2 SDI12.

The SAI bits (D3 to D0) and the SAIFB bit (D4) are used to specify the serial data format. The default serial data format is I<sup>2</sup>S, MSB-first. Available formats are shown in the tables that follow.

#### 8.2.3 Serial data first bit

Table 18. Serial data first bit

| SAIFB | Format    |