# Enpirion® Power Datasheet ES1020QI Power Sequencing Controller

NOT RECOMMENDED FOR NEW DESIGN

ES1020QI Datasheet

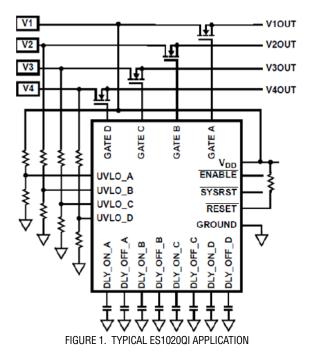

# The Altera Enpirion ES1020QI is an integrated 4-channel controlled-on/controlled-off power-supply sequencer with supply monitoring, fault protection and a "sequence completed" signal (RESET). For larger systems, more than four supplies can be sequenced by simply connecting a wire between the SYSRESET pins of cascaded ICs. The ES1020QI uses a patented, micropower 7x charge pump to drive four external low-cost NFET switch gates above the supply rail by 5.3V. These ICs can be biased from 5V down to 1.5V by any supply.

External resistors provide flexible voltage threshold programming of monitored rail voltages. Delay and sequencing are provided by external capacitors for ramp-up and ramp-down.

Additional I/O is provided for indicating and driving the RESET state in various configurations.

For volume applications, other programmable options and features are available.

#### **Features**

- Enables Arbitrary Turn-on and Turn-off Sequencing of Up to Four Power Supplies (0.7V to 5V)

- Operates From 1.5V to 5V Supply Voltage

- Supplies V<sub>DD</sub> +5.3V of Charge Pumped Gate Drive

- Adjustable Voltage Slew Rate for Each Rail

- Multiple Sequencers Can be Daisy-Chained to Sequence an Infinite Number of Independent Supplies

- Glitch Immunity

- Undervoltage Lockout for Each Supply

- Low ENABLE Input

- QFN Package

- Pb-free (RoHS-compliant)

## **Applications**

- Graphics Cards

- FPGA/ASIC/Microprocessor/PowerPC Supply Sequencing

- Network Routers

- Telecommunications Systems

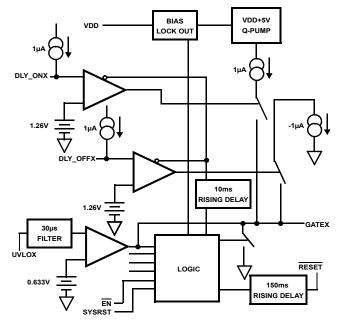

FIGURE 2. ES1020QI Block Diagram

101 Innovation Drive San Jose, CA 95134 www.altera.com

10041

© 2014 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

## **Ordering Information**

| PART NUMBER<br>(Notes 1, 2) | PART MARKING | TEMP. RANGE (°C) | PACKAGE<br>(Pb-free) | PKG. DWG. # |

|-----------------------------|--------------|------------------|----------------------|-------------|

| ES1020QI                    | S1020        | -40 to +85       | 24 Ld 4x4 QFN        | L24.4x4     |

#### NOTES:

- 1. Add "T" suffix for Tape and Reel. Please refer to Packing and Marking Information: <a href="https://www.altera.com/support/reliability/packing/rel-packing-and-marking.html">www.altera.com/support/reliability/packing/rel-packing-and-marking.html</a>

- 2. These Altera Enpirion Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Altera Enpirion Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

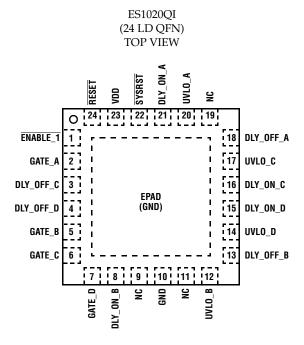

## **Pin Configurations**

### **ES1020QI Feature Matrix**

| PART<br>NAME | EN/EN | CMOS/<br>TTL | GATE DRIVE<br>OR OPEN<br>DRAIN<br>OUTPUTS | REQUIRED<br>CONDITIONS<br>FOR INITIAL<br>START-UP | NUMBER OF<br>UVLO INPUTS<br>MONITORED<br>BY EACH<br>RESET | NUMBER OF<br>CHANNELS<br>THAT TURN OFF<br>WHEN ONE<br>UVLO FAULTS | PRESET OR<br>Adjustable<br>Sequence | NUMBER OF<br>UVLO AND<br>PAIRS OF I/O | FEATURES     |

|--------------|-------|--------------|-------------------------------------------|---------------------------------------------------|-----------------------------------------------------------|-------------------------------------------------------------------|-------------------------------------|---------------------------------------|--------------|

| ES1020QI     | ĒN    | CMOS         | Gate Drive                                | 4 UVLO<br>1 EN                                    | 4 UVLO                                                    | 4 Gates                                                           | Time Adjustable<br>On and Off       | 4 Monitors<br>with 1 I/O              | Auto Restart |

## **Pin Descriptions**

| PIN       | PIN NUMBER |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME      | ES1020QI   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| $V_{DD}$  | 23         | Chip Bias. Bias IC from nominal 1.5V to 5V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| GND       | 10         | Bias Return. IC ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| ENABLE_1  | 1          | Input to start on/off sequencing. Input to initiate start of programmed sequencing of supplies on or off. Enable functionality disabled for 10ms after UVLO is satisfied.                                                                                                                                                                                                                                                                                                                                                          |

| RESET     | 24         | RESET Output. RESET provides low signal 150ms after all GATEs are fully enhanced. Delay is for stabilization of output voltages. RESET asserts low upon UVLO not being satisfied or ENABLE being deasserted. RESET outputs are open-drain, N-channel FET and are guaranteed to be in correct state for VDD down to 1V and are filtered to ignore fast transients on VDD and UVLO_X.                                                                                                                                                |

| UVLO_A    | 20         | Undervoltage Lockout/Monitoring Input. Provides a programmable UV lockout                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| UVLO_B    | 12         | referenced to an internal 0.633V reference. Filtered to ignore short (<30µs) transients below programmed UVLO level.                                                                                                                                                                                                                                                                                                                                                                                                               |

| UVLO_C    | 17         | a transients below programmed oveo level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| UVLO_D    | 14         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| DLY_ON_A  | 21         | Gate On Delay Timer Output. Allows programming of delay and sequence for VOUT                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| DLY_ON_B  | 8          | turn-on using a capacitor to ground. Each capacitor charged with 1µA 10ms after                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| DLY_ON_C  | 16         | turn-on initiated by ENABLE. Internal current source provides delay to associated FET GATE turn-on.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| DLY_ON_D  | 15         | TEL GATE WITHOUT.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| DLY_OFF_A | 18         | Gate Off Delay Timer Output. Allows programming of delay and sequence for VOUT                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| DLY_OFF_B | 13         | turn-off through ENABLE via a capacitor to ground. Each capacitor charged with                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| DLY_OFF_C | 3          | 1μA internal current source to an internal reference voltage, causing corresponding gate to be pulled down, thus turning off FET.                                                                                                                                                                                                                                                                                                                                                                                                  |

| DLY_OFF_D | 4          | gate to be puned down, thas turning our ren.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| GATE_A    | 2          | FET Gate Drive Output. Drives external FETs with 1μA current source to soft-start                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| GATE_B    | 5          | ramp into load.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| GATE_C    | 6          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| GATE_D    | 7          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| SYSRST    | 22         | System Reset I/O. As an input, allows for immediate and unconditional latch-off of all GATE outputs when driven low. This input can also be used to initiate programmed sequence with 'zero' wait (no 10ms stabilization delay) from input signal on this pin being driven high to first GATE. As an output, when there is a UV condition, this pin pulls low. If common to other SYSRST pins in a multiple IC configuration, it causes immediate and unconditional latch-off of all other GATEs on all other ES1020QI sequencers. |

| GND       | EPAD       | Ground. Die Substrate. Can be left floating.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| NC        | 9, 11, 19  | No Connect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

#### Absolute Maximum Ratings (Note 5)

| V <sub>DD</sub>       | +6.0V                         |

|-----------------------|-------------------------------|

| GATE                  | 0.3V to V <sub>DD</sub> +6V   |

| UVLO, ENABLE, SYSRST  | $0.3V$ to $V_{\rm DD} + 0.3V$ |

| RESET, DLY_ON, DLYOFF | $0.3V$ to $V_{DD} + 0.3V$     |

#### **Thermal Information**

| Thermal Resistance (Typical)  | $\theta_{JA}$ (°C/W) | θ <sub>JC</sub> (°C/W) |

|-------------------------------|----------------------|------------------------|

| 24 Ld 4x4 QFN Package (Notes  | s 3, 4) 46           | 8                      |

| Maximum Junction Temperature. |                      | +125°C                 |

| Maximum Storage Temperature   | Range                | 65°C to +150°C         |

#### **Operating Conditions**

| V <sub>DD</sub> Supply Voltage Range | +1.5V to +5.5V |

|--------------------------------------|----------------|

| Temperature Range (T <sub>A</sub> )  | 40°C to +85°C  |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTES:

- 3.  $\theta_{JA}$  is measured in free air with the component mounted on a high effective thermal conductivity test board with "direct attach" features.

- 4. For  $\theta_{IC}$ , the "case temp" location is the center of the exposed metal pad on the package underside.

- 5. All voltages are relative to GND, unless otherwise specified.

Electrical Specifications  $V_{\rm DD}$  = 1.5V to +5V,  $T_{\rm A}$  =  $T_{\rm J}$  = -40°C to +85°C, unless otherwise specified. Boldface limits apply over the operating temperature range, -40°C to +85°C.

| PARAMETER                                       | SYMBOL                             | TEST CONDITIONS                                     | MIN<br>(Note 6) | ТҮР                 | MAX<br>(Note 6) | UNIT  |

|-------------------------------------------------|------------------------------------|-----------------------------------------------------|-----------------|---------------------|-----------------|-------|

| UVLO                                            |                                    |                                                     |                 |                     |                 |       |

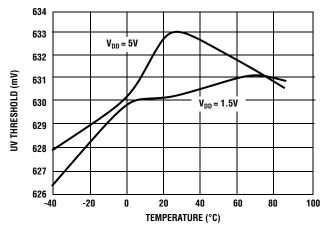

| Falling Undervoltage Lockout Threshold          | V <sub>UVLOvth</sub>               | T <sub>J</sub> = +25°C                              | 619             | 633                 | 647             | mV    |

| Undervoltage Lockout Threshold Tempco           | $TC_{UVLOvth}$                     |                                                     |                 | 40                  |                 | μV/°C |

| Undervoltage Lockout Hysteresis                 | V <sub>UVLOhys</sub>               |                                                     |                 | 10                  |                 | mV    |

| Undervoltage Lockout Threshold Range            | RUVLOvth                           | Max V <sub>UVLOvth</sub> - Min V <sub>UVLOvth</sub> |                 | 7                   |                 | mV    |

| Undervoltage Lockout Delay                      | TUVLOdel                           | ENABLE satisfied                                    |                 | 10                  |                 | ms    |

| Transient Filter Duration                       | t <sub>FIL</sub>                   | V <sub>DD</sub> , UVLO, ENABLE glitch filter        |                 | 30                  |                 | μs    |

| DELAY ON/OFF                                    |                                    | 1                                                   | -               | I .                 | 1               | I     |

| Delay Charging Current                          | DLY_ichg                           | $V_{DLY} = 0V$                                      | 0.92            | 1                   | 1.08            | μА    |

| Delay Charging Current Range                    | DLY_ichg_r                         | DLY_ichg(max) - DLY_ichg(min)                       |                 | 0.08                |                 | μА    |

| Delay Charging Current Temperature Coefficient  | TC_DLY_ichg                        |                                                     |                 | 0.2                 |                 | nA/°C |

| Delay Threshold Voltage                         | DLY_Vth                            |                                                     | 1.238           | 1.266               | 1.294           | V     |

| Delay Threshold Voltage Temperature Coefficient | TC_DLY_Vth                         |                                                     |                 | 0.2                 |                 | mV/°C |

| ENABLE, RESET AND SYSRST I/O                    |                                    |                                                     |                 | I                   |                 | •     |

| ENABLE Threshold                                | $V_{ENh}$                          |                                                     |                 | 0.5 V <sub>DD</sub> |                 | V     |

| ENABLE Hysteresis                               | V <sub>ENh</sub> -V <sub>ENI</sub> | Measured at V <sub>DD</sub> = 1.5V                  |                 | 0.2                 |                 | V     |

| ENABLE Lockout Delay                            | t <sub>delEN_LO</sub>              | UVLO satisfied                                      |                 | 10                  |                 | ms    |

| ENABLE Input Capacitance                        | Cin_en                             |                                                     |                 | 5                   |                 | pF    |

| RESET Pull-up Voltage                           | Vpu_rst                            |                                                     |                 | $V_{DD}$            |                 | V     |

| RESET Pull-Down Current                         | I <sub>RSTpd1</sub>                | $V_{DD} = 1.5V$ , $\overline{RST} = 0.1V$           |                 | 5                   |                 | mA    |

|                                                 | I <sub>RSTpd3</sub>                | $V_{DD} = 3.3V$ , $\overline{RST} = 0.1V$           |                 | 13                  |                 | mA    |

|                                                 | I <sub>RSTpd5</sub>                | $V_{DD} = 5V$ , $\overline{RST} = 0.1V$             |                 | 17                  |                 | mA    |

| RESET Delay after GATE High                     | T <sub>RSTdel</sub>                | GATE = V <sub>DD</sub> +5V                          |                 | 160                 |                 | ms    |

## Electrical Specifications $V_{DD} = 1.5 V$ to +5V, $T_A = T_J = -40$ °C to +85°C, unless otherwise specified. Boldface limits apply over the operating temperature range, -40°C to +85°C. (Continued)

| PARAMETER                                        | SYMBOL                  | TEST CONDITIONS                                       | MIN<br>(Note 6)      | ТҮР                    | MAX<br>(Note 6) | UNIT  |

|--------------------------------------------------|-------------------------|-------------------------------------------------------|----------------------|------------------------|-----------------|-------|

| RESET Output Low                                 | $V_{\overline{RSTI}}$   | Measured at $V_{DD} = 5V$ with $5k$ pull-up resistors |                      |                        | 0.1             | V     |

| RESET Output Capacitance                         | C <sub>OUT_RST</sub>    |                                                       |                      | 10                     |                 | pF    |

| SYSRST Pull-Up Voltage                           | Vpu_srst                |                                                       |                      | $V_{DD}$               |                 | V     |

| SYSRST Pull-Down Current                         | lpu_1.5                 | V <sub>DD</sub> = 1.5V                                |                      | 5                      |                 | μА    |

|                                                  | lpu_5                   | $V_{DD} = 5V$                                         |                      | 100                    |                 | μA    |

| SYSRST Low Output Voltage                        | Vol_srst                | $V_{DD} = 1.5V$ , $I_{OUT} = 100\mu A$                |                      | 150                    |                 | mV    |

| SYSRST Output Capacitance                        | Cout_srst               |                                                       |                      | 10                     |                 | pF    |

| SYSRST Low to GATE Turn-Off                      | t <sub>delSYS_G</sub>   | GATE = 80% of V <sub>DD</sub> + 5V                    |                      | 40                     |                 | ns    |

| GATE                                             |                         |                                                       | 1                    |                        |                 |       |

| GATE Turn-On Current                             | I <sub>GATEon</sub>     | GATE = 0V                                             | 0.8                  | 1.1                    | 1.4             | μΑ    |

| GATE Turn-Off Current                            | I <sub>GATEoff_I</sub>  | GATE = V <sub>DD</sub> , Disabled                     | -1.4                 | -1.05                  | -0.8            | μΑ    |

| GATE Current Range                               | I <sub>GATE_range</sub> | Within IC I <sub>GATE</sub> max-min                   |                      |                        | 0.35            | μА    |

| GATE Turn-On/Off Current Temperature Coefficient | TC_I <sub>GATE</sub>    |                                                       |                      | 0.2                    |                 | nA/°C |

| GATE Pull-Down High Current                      | I <sub>GATEoff_h</sub>  | GATE = V <sub>DD</sub> , UVLO = 0V                    |                      | 88                     |                 | mA    |

| GATE High Voltage                                | $V_{GATEh}$             | $V_{DD}$ < 2V, $T_{J}$ = +25°C                        |                      | V <sub>DD</sub> + 4.9V |                 | V     |

|                                                  | $V_{GATEh}$             | V <sub>DD</sub> > 2V                                  | V <sub>DD</sub> + 5V | V <sub>DD</sub> + 5.3V |                 | V     |

| GATE Low Voltage                                 | $V_{GATEI}$             | Gate Low Voltage, V <sub>DD</sub> = 1V                |                      | 0                      | 0.1             | V     |

| BIAS                                             |                         |                                                       |                      |                        |                 |       |

| IC Supply Current                                | I <sub>VDD_5V</sub>     | $V_{DD} = 5V$                                         |                      | 0.20                   | 0.5             | mA    |

|                                                  | I <sub>VDD_3.3V</sub>   | $V_{DD} = 3.3V$                                       |                      | 0.14                   |                 | mA    |

|                                                  | I <sub>VDD_1.5V</sub>   | V <sub>DD</sub> = 1.5V                                |                      | 0.10                   |                 | mA    |

| V <sub>DD</sub> Power-on Reset                   | V <sub>DD</sub> _POR    |                                                       |                      |                        | 1               | ٧     |

#### NOTE:

<sup>6.</sup> Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Temperature limits established by characterization and are not production tested.

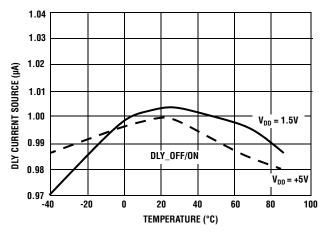

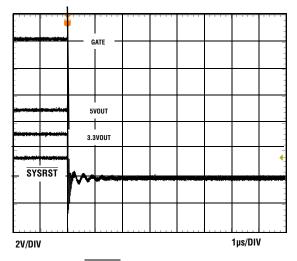

## **Typical Performance Curves**

FIGURE 3. UVLO THRESHOLD VOLTAGE

FIGURE 4. DLY CHARGE CURRENT

FIGURE 5. SYSRST LOW TO OUTPUT LATCH-OFF

## **Descriptions and Operation**

The ES1020QI sequencer is a 4-channel voltage sequencing controller, and is designed for use in multiple-voltage systems requiring power sequencing of various supply voltages. Individual voltage rails are gated on and off by external N-Channel MOSFETs, the gates of which are driven by an internal charge pump to  $V_{DD}$  + 5.3V (VQP) in a user-programmed sequence.

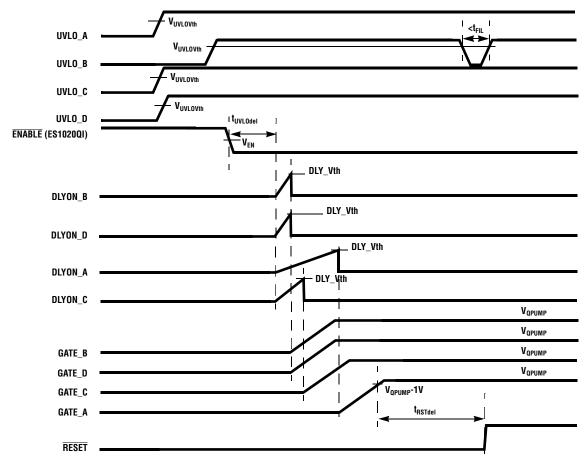

The 4-channel ES1020QI  $\overline{ENABLE}$  must be asserted low, and all four voltages to be sequenced must be above their respective user-programmed undervoltage lockout (UVLO) levels before programmed output turn-on sequencing can begin. Sequencing order and delay are determined by the choice of external capacitor values on the DLY\_ON and DLY\_OFF pins. Once all four UVLO inputs and  $\overline{ENABLE}$  are satisfied for 10ms ( $t_{delEN\_LO}$ ), the four DLY\_ON capacitors are simultaneously charged with 1 $\mu$ A current sources to the DLY\_Vth level of 1.27V. As each DLY\_ON pin reaches the DLY\_Vth level, its associated GATE turns on, with a 1 $\mu$ A source current to the charge pump voltage (VQP) of V<sub>DD</sub> + 5.3V. Thus, all four GATEs sequentially turn on in the user defined order. Once at DLY\_Vth, the DLY\_ON pins discharge so they are ready when next needed.

After the entire turn-on sequence has been completed and all GATEs have reached the charge pumped voltage (VQP), a 160ms delay ( $T_{\overline{RST}del}$ ) is started to ensure stability, after which the  $\overline{RESET}$  output is released to go high.

After turn-on, if any input falls below its UVLO point for longer than the glitch filter period (~30µs), it is considered a fault. RESET and SYSRST are pulled low, and all GATEs are simultaneously also pulled low. In this mode, the GATEs are pulled low with 88mA.

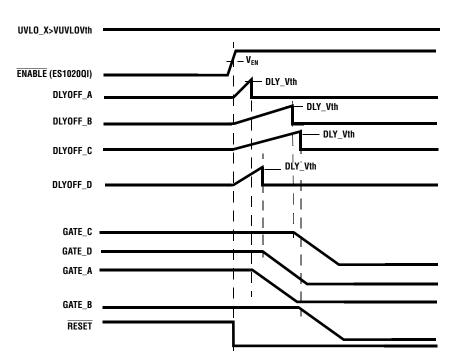

Normal shutdown mode is entered when no UVLO is violated and  $\overline{\text{ENABLE}}$  is deasserted. When  $\overline{\text{ENABLE}}$  is deasserted,  $\overline{\text{RESET}}$  is immediately asserted and pulled low. Next, all four shutdown ramp capacitors on the DLY\_OFF pins are charged with a 1 $\mu$ A source. When any ramp-capacitor reaches DLY\_Vth, a latch is set, and a current is sunk on the respective GATE pin to turn off its external MOSFET. When the GATE voltage is approximately 0.6V, the GATE is pulled down the rest of the way at a higher current level. Each individual external FET is thus turned off, which removes the voltages from the load in the user programmed sequence.

Table 1 shows the nominal time delay on the DLY\_X pins for various capacitor values, from the start of charging to the 1.27V reference. This table does not include the 10ms of  $\overline{\text{ENABLE}}$  lockout delay during a start-up sequence, but it does represent the time from the end of the  $\overline{\text{ENABLE}}$  lockout delay to the start of GATE transition. There is no  $\overline{\text{ENABLE}}$  lockout delay for a sequence-off, so this table illustrates the delay to GATE transition from a disable signal.

TABLE 1. NOMINAL DELAY TO SEQUENCING THRESHOLD

| DLY PIN CAPACITANCE | TIME(s) |

|---------------------|---------|

| Open                | 0.00006 |

| 100pF               | 0.00013 |

| 1000pF              | 0.0013  |

| 0.01μF              | 0.013   |

| 0.1μF               | 0.13    |

| 1μF                 | 1.3     |

| 10μF                | 13      |

NOTE: Nom.  $T_{DEL SEO}$  = Capacitor ( $\mu F$ )\*1.3M $\Omega$

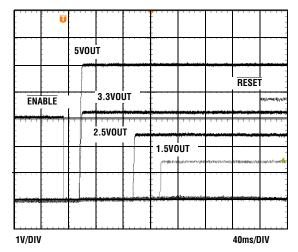

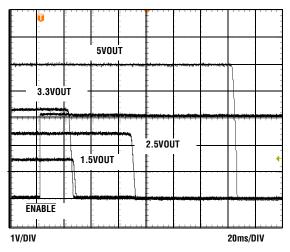

Figure 6 shows the turn-on and Figure 7 shows the nominal turn-off timing diagram of the ES1020QI.

Delay and flexible sequencing possibilities include multiple series, parallel, or adjustable capacitors that can be used to easily fine-tune timing over that offered by standard value capacitors.

FIGURE 6. ES1020QI TURN-ON AND GLITCH RESPONSE TIMING DIAGRAM

May 28, 2014

FIGURE 7. ES1020QI TURN-OFF TIMING DIAGRAM

## **Typical Performance Waveforms**

FIGURE 8. ES1020QI SEQUENCED TURN-ON

FIGURE 9. ES1020QI SEQUENCED TURN-OFF

**Application Considerations**

#### **Timing Error Sources**

In any system there are variance contributors. For the ES1020QI, timing errors are mainly contributed by three sources.

#### **Capacitor Timing Mismatch Error**

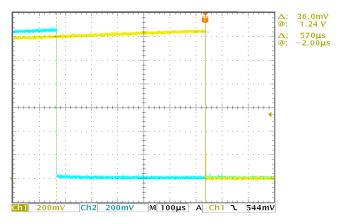

Obviously, the absolute capacitor value is an error source; thus, lower-percentage tolerance capacitors help to reduce this error source. Figure 10 illustrates a difference of 0.57ms between two DLY\_X outputs ramping to DLY\_X threshold voltage. These 5% capacitors were from a common source. In applications where two or more GATEs or LOGIC outputs must have concurrent transitions, it is recommended that a common GATE drive be used to eliminate this timing error.

FIGURE 10. CAPACITOR TIMING MISMATCH

#### DLY\_X Threshold Voltage and Charging Current Mismatch

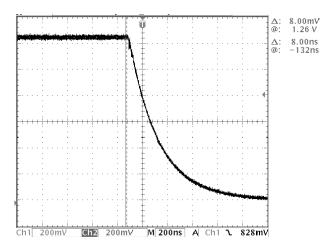

The two other error sources come from the IC itself and are found across the four DLY\_X outputs. These errors are the DLY\_X threshold voltage (DLY\_Vth) variance when the GATE\_X charging and discharging current latches are set, and the DLY\_X charging current (DLY\_ichg) variances to determine the time to next sequencing event. Both of these parameters are bounded by specification. Figure 11 shows that, with a common capacitor, the typical error contributed by these factors is insignificant, since both DLY\_X traces overlay each other.

FIGURE 11. DLY\_VTH AND DLY\_ICHG TIMING MISMATCH

## **Revision History**

The table lists the revision history for this document.

| DATE      | REVISION | CHANGE           |

|-----------|----------|------------------|

| May, 2014 | Α        | Initial release. |

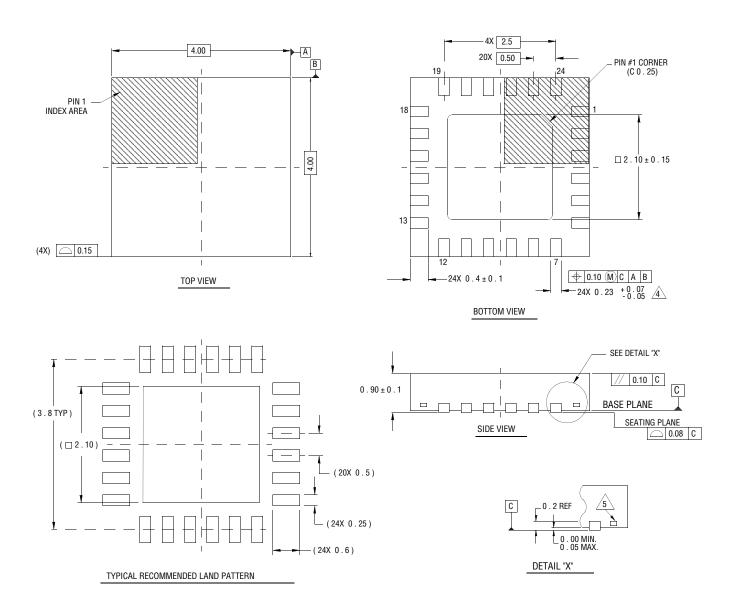

## **Package Outline Drawing**

# **L24.4x4**24 LEAD QUAD FLAT NO-LEAD PLASTIC PACKAGE Rev 4, 10/06

#### NOTES:

- Dimensions are in millimeters.

Dimensions in ( ) for Reference Only.

- 2. Dimensioning and tolerancing conform to AMSE Y14.5m-1994.

- 3. Unless otherwise specified, tolerance : Decimal  $\pm 0.05$

- 4. Dimension b applies to the metallized terminal and is measured between 0.15mm and 0.30mm from the terminal tip.

- 5. Tiebar shown (if present) is a non-functional feature.

- The configuration of the pin #1 identifier is optional, but must be located within the zone indicated. The pin #1 identifier may be either a mold or mark feature.

OOO «ЛайфЭлектроникс" "LifeElectronics" LLC

ИНН 7805602321 КПП 780501001 P/C 40702810122510004610 ФАКБ "АБСОЛЮТ БАНК" (ЗАО) в г.Санкт-Петербурге К/С 3010181090000000703 БИК 044030703

Компания «Life Electronics» занимается поставками электронных компонентов импортного и отечественного производства от производителей и со складов крупных дистрибьюторов Европы, Америки и Азии.

С конца 2013 года компания активно расширяет линейку поставок компонентов по направлению коаксиальный кабель, кварцевые генераторы и конденсаторы (керамические, пленочные, электролитические), за счёт заключения дистрибьюторских договоров

#### Мы предлагаем:

- Конкурентоспособные цены и скидки постоянным клиентам.

- Специальные условия для постоянных клиентов.

- Подбор аналогов.

- Поставку компонентов в любых объемах, удовлетворяющих вашим потребностям.

- Приемлемые сроки поставки, возможна ускоренная поставка.

- Доставку товара в любую точку России и стран СНГ.

- Комплексную поставку.

- Работу по проектам и поставку образцов.

- Формирование склада под заказчика.

- Сертификаты соответствия на поставляемую продукцию (по желанию клиента).

- Тестирование поставляемой продукции.

- Поставку компонентов, требующих военную и космическую приемку.

- Входной контроль качества.

- Наличие сертификата ISO.

В составе нашей компании организован Конструкторский отдел, призванный помогать разработчикам, и инженерам.

Конструкторский отдел помогает осуществить:

- Регистрацию проекта у производителя компонентов.

- Техническую поддержку проекта.

- Защиту от снятия компонента с производства.

- Оценку стоимости проекта по компонентам.

- Изготовление тестовой платы монтаж и пусконаладочные работы.

Тел: +7 (812) 336 43 04 (многоканальный) Email: org@lifeelectronics.ru