#### **FEATURES**

Dual receivers

Maximum receiver bandwidth: 200 MHz Fully integrated, fractional-N, RF synthesizers Fully integrated clock synthesizer Multichip phase synchronization for RF LO and baseband clocks JESD204B datapath interface Tuning range (center frequency): 75 MHz to 6000 MHz

#### **APPLICATIONS**

3G/4G/5G FDD, macrocell base stations Wideband active antenna systems Massive multiple input, multiple output (MIMO) Phased array radar Electronic warfare Military communications Portable test equipment

#### **GENERAL DESCRIPTION**

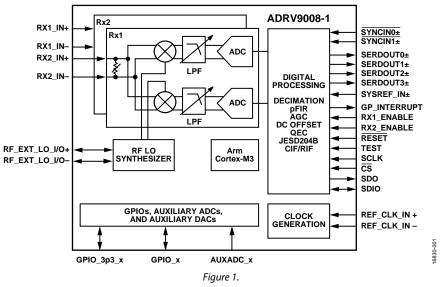

The ADRV9008-1 is a highly integrated, dual radio frequency (RF), agile receiver offering integrated synthesizers and digital signal processing functions. The IC delivers a versatile combination of high performance and low power consumption required by 3G/4G/5G macrocell, frequency division duplex (FDD), base station applications.

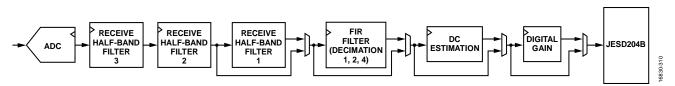

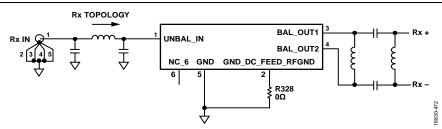

The receive path consists of two independent, wide bandwidth, direct conversion receivers with state-of-the-art dynamic range. The complete receive subsystem includes automatic and manual attenuation control, dc offset correction, quadrature error correction (QEC), and digital filtering, eliminating the need for these functions in the digital baseband. RF front-end control and several auxiliary functions, such as analog-to-digital converters (ADCs), digital-to-analog converters (DACs), and general-purpose input/outputs (GPIOs) for the power amplifier (PA), are also integrated.

# **Integrated Dual RF Receivers**

In addition to automatic gain control (AGC), the ADRV9008-1 also features flexible external gain control modes, allowing dynamic gain control.

The received signals are digitized with a set of four, high dynamic range, continuous time, sigma-delta  $(\Sigma - \Delta)$  ADCs that provide inherent antialiasing. The combination of the direct conversion architecture (which does not suffer from out of band image mixing) and the lack of aliasing reduces the requirements of the RF filters compared to the requirements of traditional intermediate frequency (IF) receivers.

The fully integrated phase-locked loop (PLL) provides high performance, low power, fractional-N, RF synthesis for the receiver signal paths. An additional synthesizer generates the clocks needed for the converters, digital circuits, and serial interface. A multichip synchronization mechanism synchronizes the phase of the RF local oscillator (LO) and baseband clocks between multiple ADRV9008-1 chips. The ADRV9008-1 features the isolation that high performance base station applications require. All voltage controlled oscillators (VCOs) and loop filter components are integrated.

The high speed JESD204B interface supports up to 12.288 Gbps lane rates, resulting in a single lane per receiver in the widest bandwidth mode. The interface also supports interleaved mode for lower bandwidths, reducing the total number of high speed data interface lanes to one. Both fixed and floating point data formats are supported. The floating point format allows internal AGC to be invisible to the demodulator device.

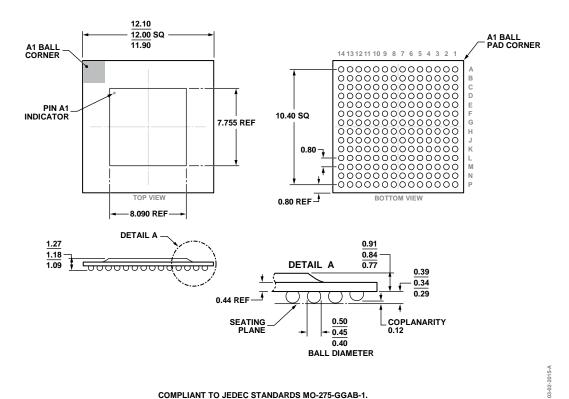

The core of the ADRV9008-1 can be powered directly from 1.3 V and 1.8 V regulators and is controlled via a standard 4-wire serial port. Comprehensive power-down modes are included to minimize power consumption during normal use. The ADRV9008-1 is packaged in a 12 mm  $\times$  12 mm, 196-ball chip scale ball grid array (CSP\_BGA).

Rev. 0

#### **Document Feedback**

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

# TABLE OF CONTENTS

#### **REVISION HISTORY**

9/2018—Revision 0: Initial Version

| Theory of Operation                                  |

|------------------------------------------------------|

| Receivers                                            |

| Clock Input                                          |

| Synthesizers                                         |

| SPI                                                  |

| JTAG Boundary Scan 47                                |

| Power Supply Sequence                                |

| GPIO_x Pins 48                                       |

| Auxiliary Converters                                 |

| JESD204B Data Interface                              |

| Applications Information 49                          |

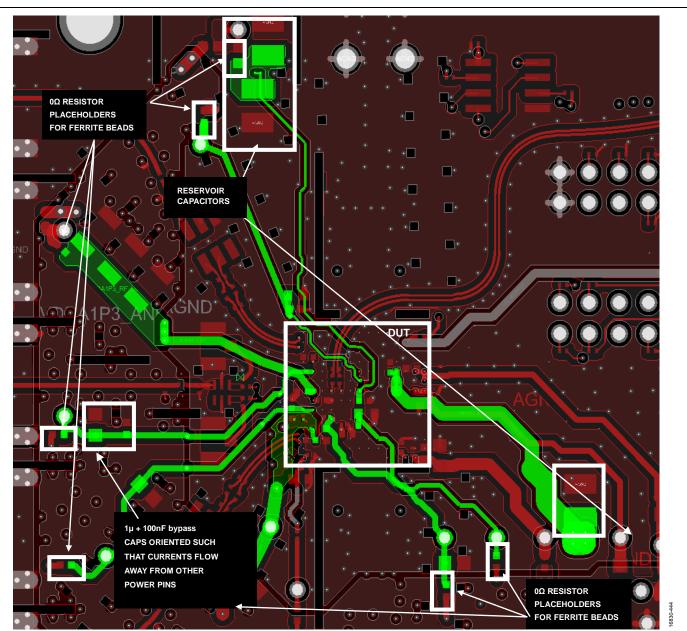

| PCB Layout and Power Supply Recommendations          |

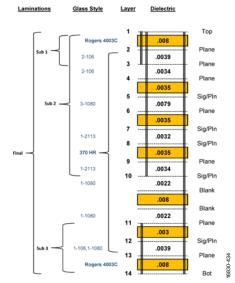

| PCB Material and Stackup Selection                   |

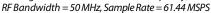

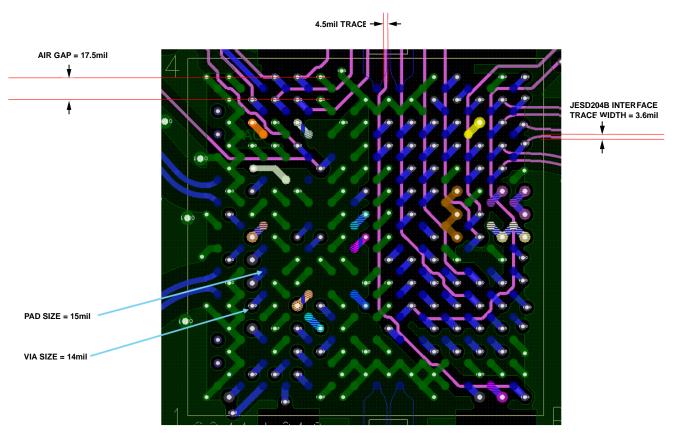

| Fanout and Trace Space Guidelines51                  |

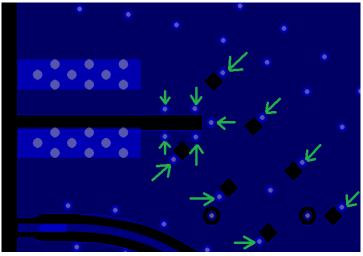

| Component Placement and Routing Guidelines           |

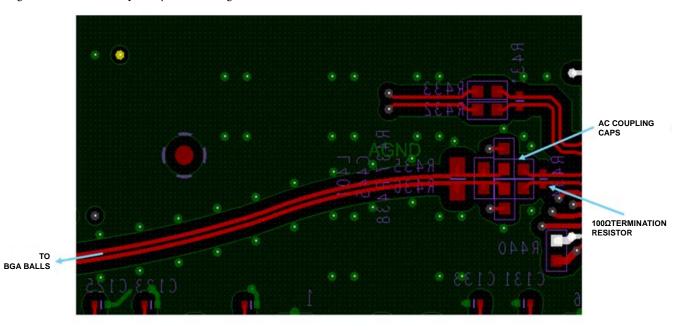

| RF and JESD204B Transmission Line Layout             |

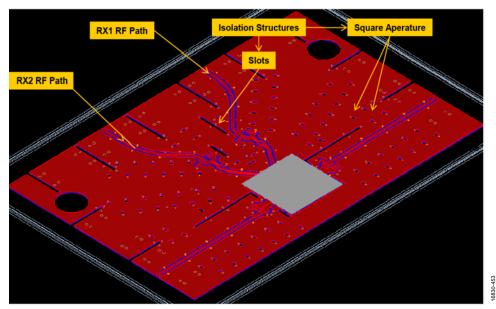

| Isolation Techniques Used on the ADRV9008-1W/PCBZ 60 |

| RF Port Interface Information61                      |

| Outline Dimensions                                   |

| Ordering Guide68                                     |

|                                                      |

### FUNCTIONAL BLOCK DIAGRAM

### **SPECIFICATIONS**

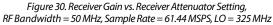

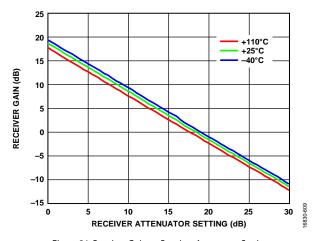

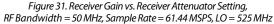

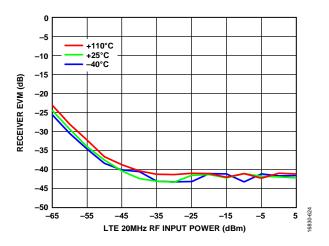

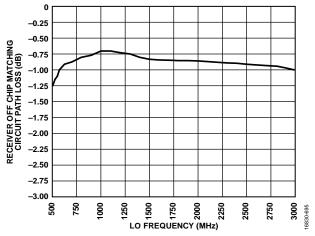

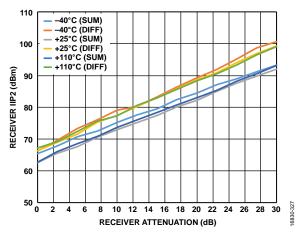

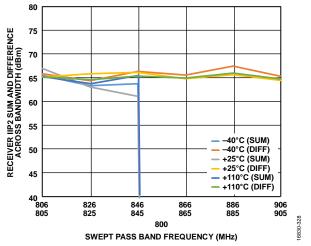

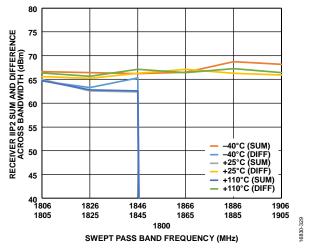

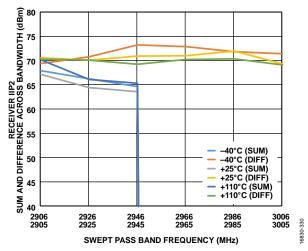

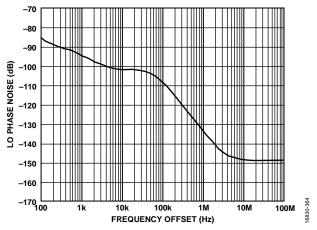

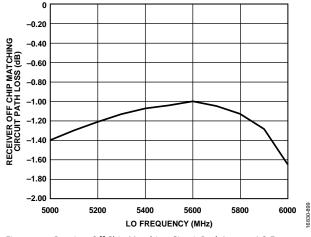

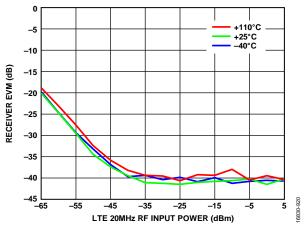

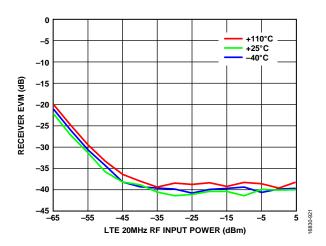

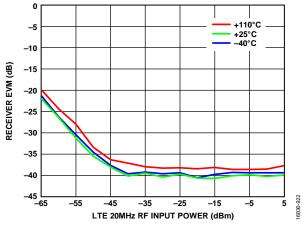

Electrical characteristics at VDDA1P3<sup>1</sup> = 1.3 V, VDDD1P3\_DIG = 1.3 V,  $T_J$  = full operating temperature range, and LO frequency ( $f_{LO}$ ) = 1800 MHz, unless otherwise noted. The specifications in Table 1 are not de-embedded. Refer to the Typical Performance Characteristics section for input/output circuit path loss. The device configuration profile for the 75 MHz to 525 MHz frequency range is as follows: receiver = 50 MHz bandwidth (inphase quadrature (I/Q) rate = 61.44 MHz), JESD204B rate = 9.8304 GSPS, and device clock = 245.76 MHz. Unless otherwise specified, the device configuration for all other frequency ranges is as follows: receiver = 200 MHz bandwidth (I/Q rate = 245.76 MHz), JESD204B rate = 9.8304 GSPS, and device clock = 245.76 MHz.

| Parameter                            | Symbol            | Min | Тур   | Max  | Unit | Test Conditions/Comments                                                                                                                                                        |

|--------------------------------------|-------------------|-----|-------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RECEIVERS                            |                   |     |       |      |      |                                                                                                                                                                                 |

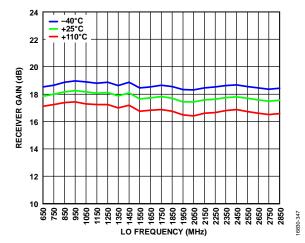

| Center Frequency                     |                   | 75  |       | 6000 | MHz  |                                                                                                                                                                                 |

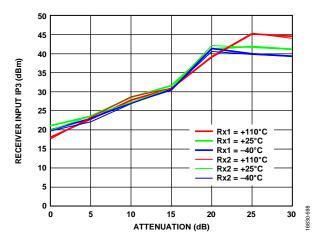

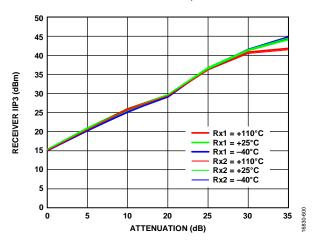

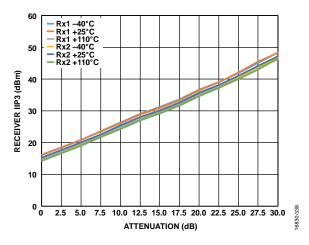

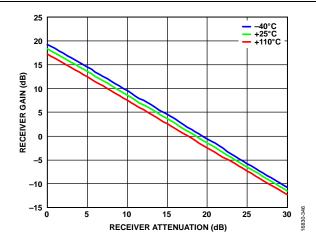

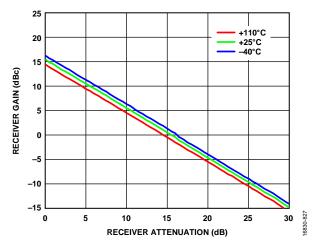

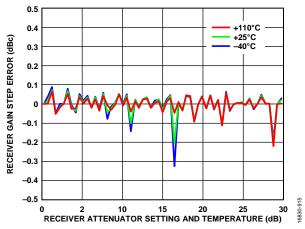

| Gain Range                           |                   |     | 30    |      | dB   |                                                                                                                                                                                 |

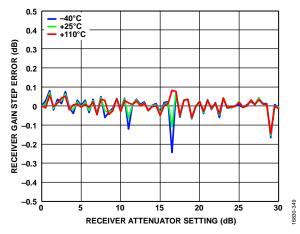

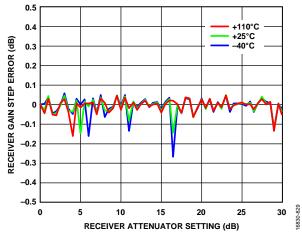

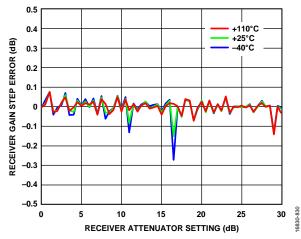

| Analog Gain Step                     |                   |     | 0.5   |      | dB   | Attenuator steps from 0 dB to 6 dB                                                                                                                                              |

|                                      |                   |     | 1     |      | dB   | Attenuator steps from 6 dB to 30 dB                                                                                                                                             |

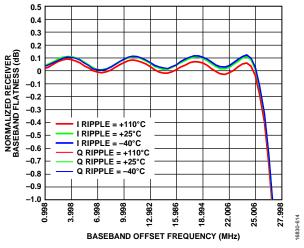

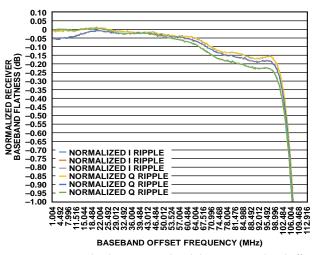

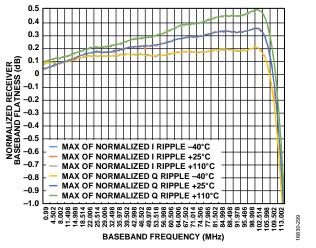

| Bandwidth Ripple                     |                   |     | ±0.5  |      | dB   | 200 MHz bandwidth, compensated by<br>programmable finite impulse response (FIR)<br>filter                                                                                       |

|                                      |                   |     | ±0.2  |      | dB   | Any 20 MHz bandwidth span, compensated by programmable FIR filter                                                                                                               |

| Receiver (Rx) Bandwidth              |                   |     |       | 200  | MHz  |                                                                                                                                                                                 |

| Receiver Alias Band<br>Rejection     |                   | 80  |       |      | dB   | Due to digital filters                                                                                                                                                          |

| Maximum Useable Input<br>Level       | P <sub>HIGH</sub> |     |       |      |      | 0 dB attenuation, increases decibel<br>for decibel with attenuation, continuous<br>wave (CW) = 1800 MHz, corresponds to<br>-1 dBFS at ADC                                       |

|                                      |                   |     | -11   |      | dBm  | $75 \text{ MHz} < f \le 3000 \text{ MHz}$                                                                                                                                       |

|                                      |                   |     | -10.2 |      | dBm  | 3000 MHz < f ≤ 4800 MHz                                                                                                                                                         |

|                                      |                   |     | -9.5  |      | dBm  | 4800 MHz < f $\leq$ 6000 MHz                                                                                                                                                    |

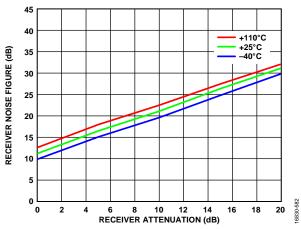

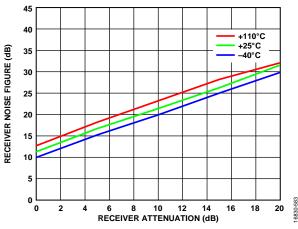

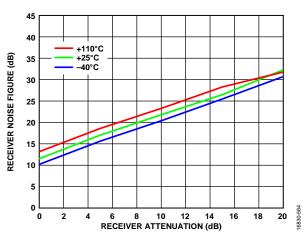

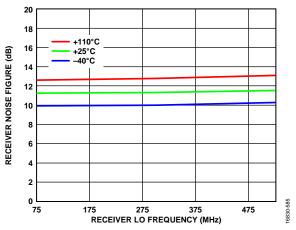

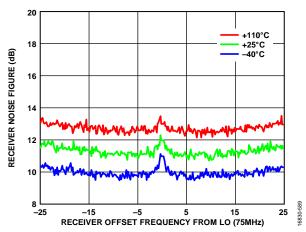

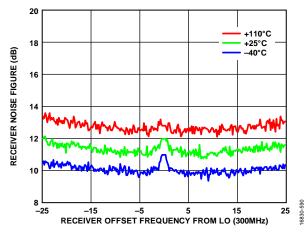

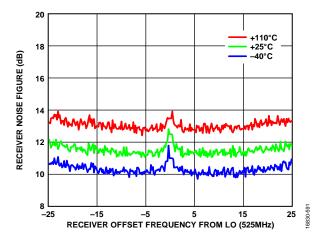

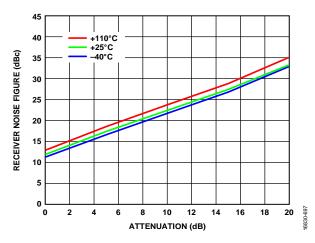

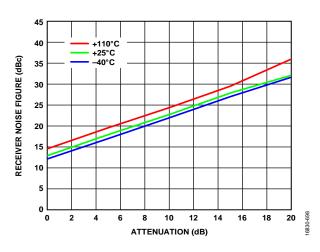

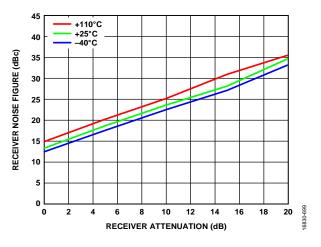

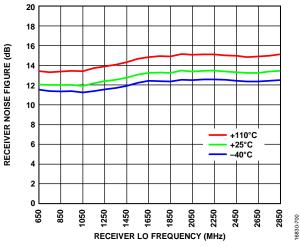

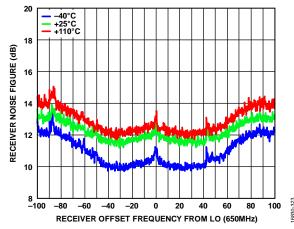

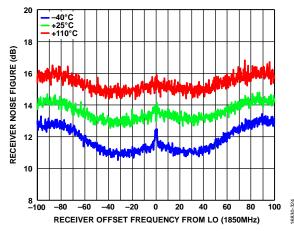

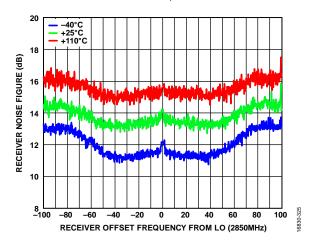

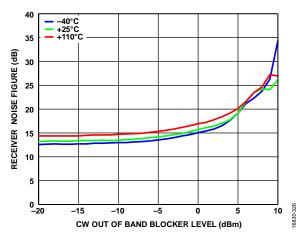

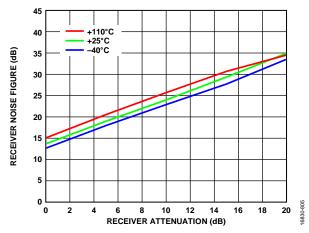

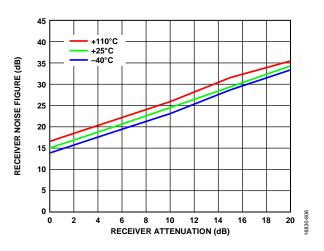

| Noise Figure                         | NF                |     |       |      |      | 0 dB attenuation, at receiver port                                                                                                                                              |

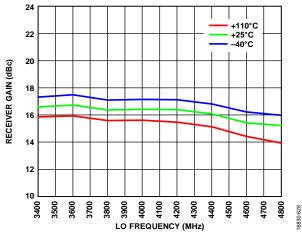

|                                      |                   |     | 11.5  |      | dB   | $75 \text{ MHz} < f \le 600 \text{ MHz}$                                                                                                                                        |

|                                      |                   |     | 12    |      | dB   | $600 \text{ MHz} < f \le 3000 \text{ MHz}$                                                                                                                                      |

|                                      |                   |     | 13    |      | dB   | $3000 \text{ MHz} < f \le 4800 \text{ MHz}$                                                                                                                                     |

|                                      |                   |     | 15.2  |      | dB   | $4800 \text{ MHz} < f \le 6000 \text{ MHz}$                                                                                                                                     |

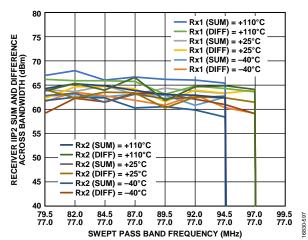

| Ripple                               |                   |     | 1.8   |      | dB   | At band edge maximum bandwidth mode                                                                                                                                             |

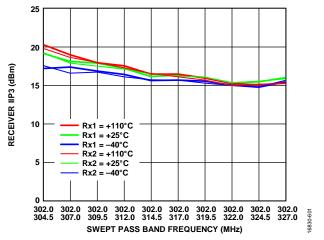

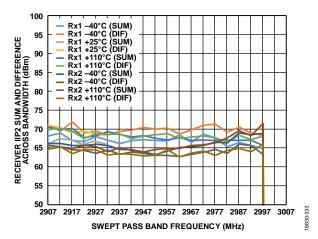

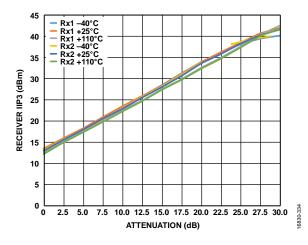

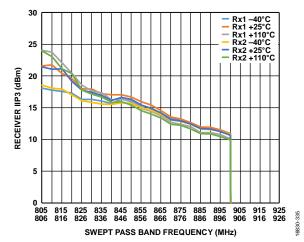

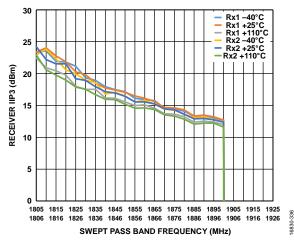

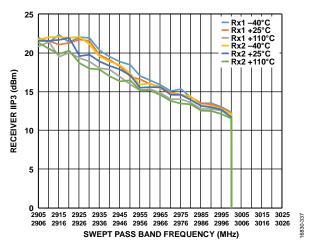

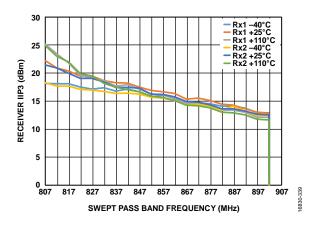

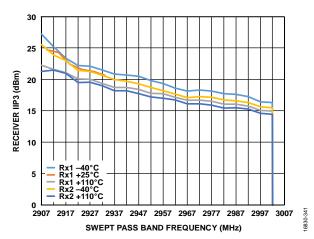

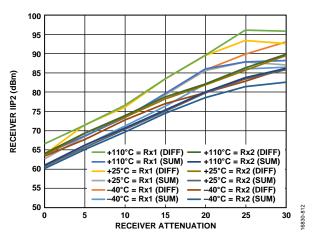

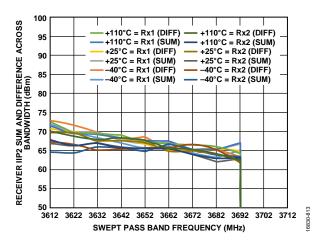

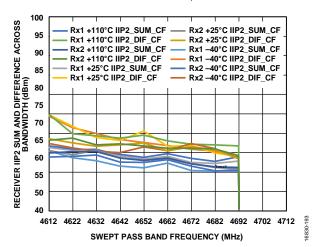

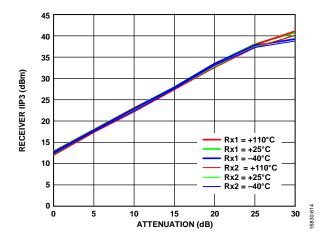

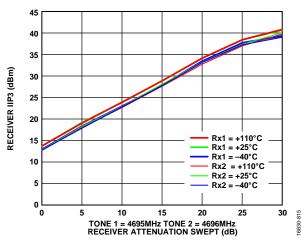

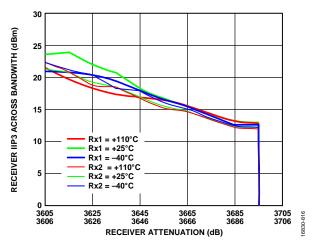

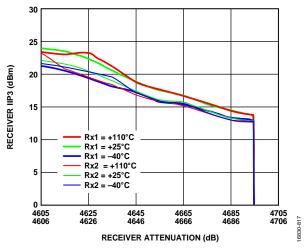

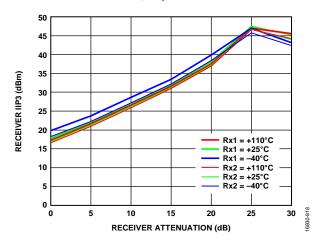

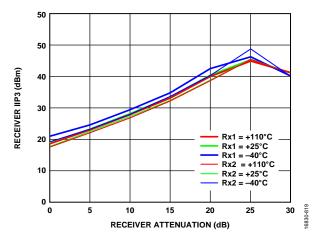

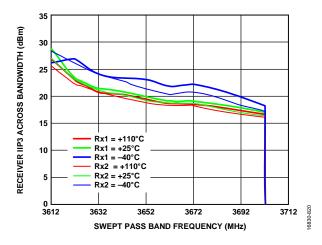

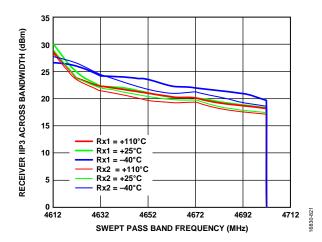

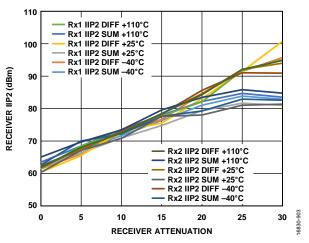

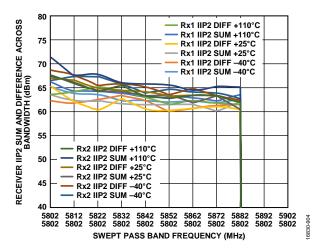

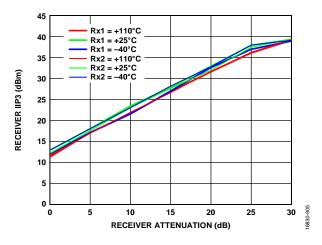

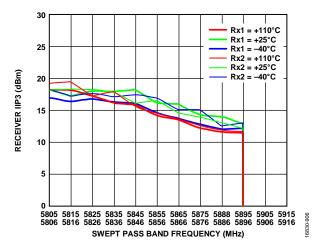

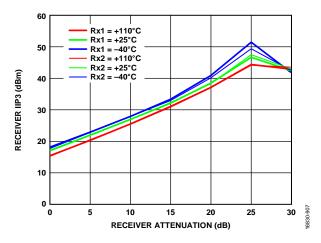

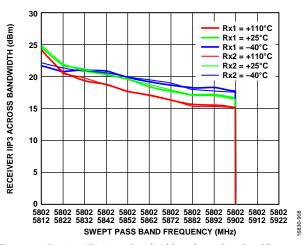

| Input Third-Order Intercept<br>Point | IIP3              |     |       |      |      |                                                                                                                                                                                 |

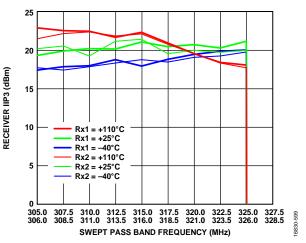

| Difference Product                   |                   |     | 12    |      | dBm  | 75 MHz < f $\leq$ 600 MHz, (P <sub>HIGH</sub> – 12) dB per tone; 600 MHz < f $\leq$ 6000 MHz, (P <sub>HIGH</sub> – 10) dB per tone; two tones near band edge                    |

| Sum Product                          |                   |     | 12    |      | dBm  | 75 MHz < f $\leq$ 600 MHz, (P <sub>HIGH</sub> – 12) dB per tone; 600 MHz < f $\leq$ 6000 MHz, (P <sub>HIGH</sub> – 10) dB per tone; two tones at bandwidth/6 offset from the LO |

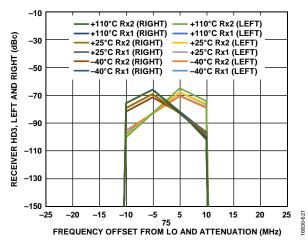

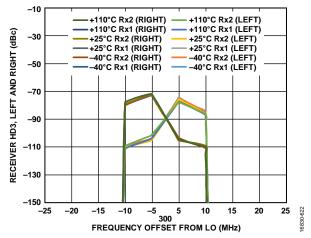

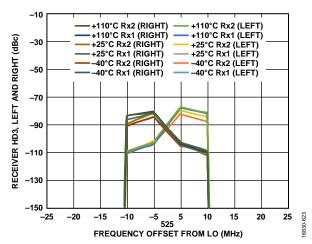

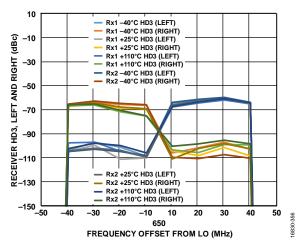

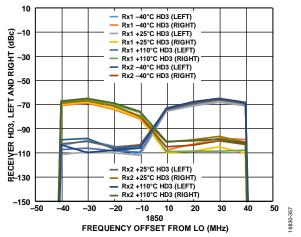

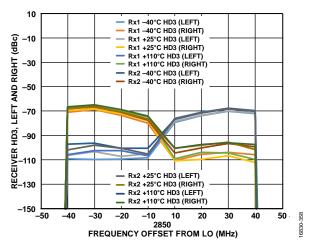

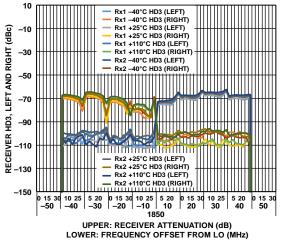

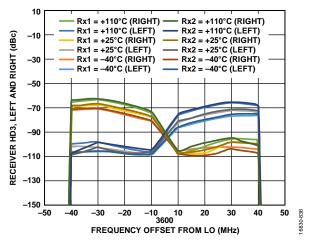

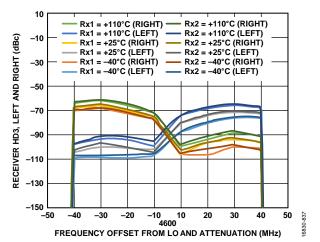

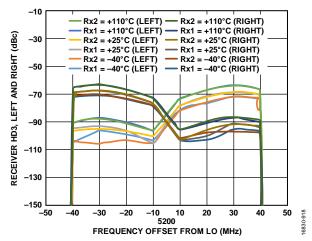

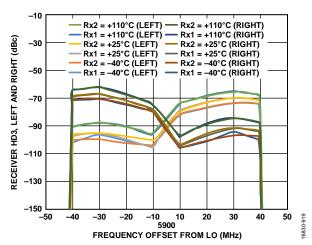

| Third-Order Harmonic<br>Distortion   | HD3               |     |       |      |      | 75 MHz < f $\leq$ 600 MHz, (P <sub>HIGH</sub> – 6) dB; 600 MHz < f $\leq$ 6000 MHz, (P <sub>HIGH</sub> – 4) dB; CW tone at bandwidth/6 offset from the LO                       |

|                                      |                   |     | -65   |      | dBc  | 75 MHz < f $\leq$ 600 MHz                                                                                                                                                       |

|                                      |                   |     | -66   |      | dBc  | $600 \text{ MHz} < f \le 4800 \text{ MHz}$                                                                                                                                      |

|                                      |                   |     | -62   |      | dBc  | $4800 \text{ MHz} < f \le 6000 \text{ MHz}$                                                                                                                                     |

| Parameter                         | Symbol | Min Typ Max | Unit    | Test Conditions/Comments                                                 |

|-----------------------------------|--------|-------------|---------|--------------------------------------------------------------------------|

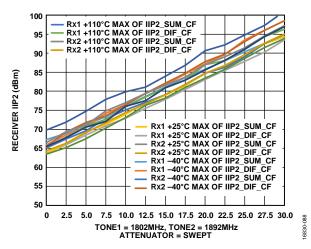

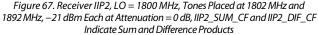

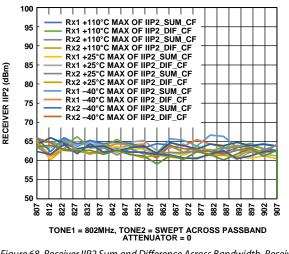

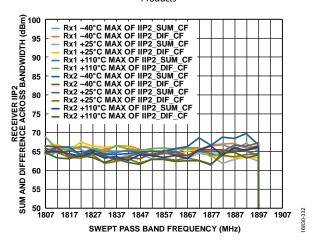

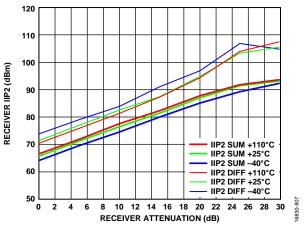

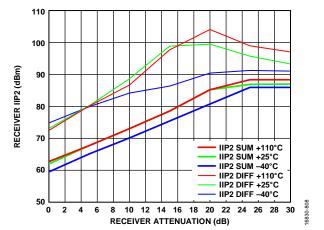

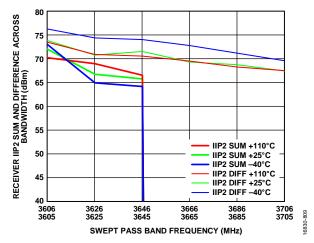

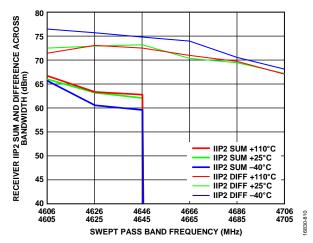

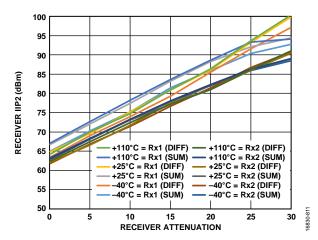

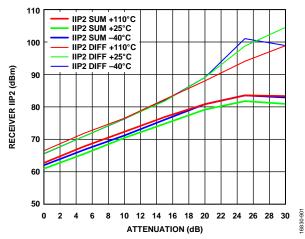

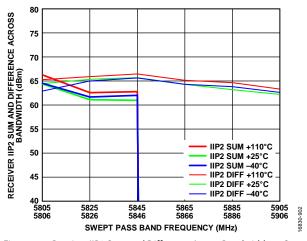

| Second-Order Input                | IIP2   | 62          | dBm     | 75 MHz < f $\leq$ 600 MHz, (P <sub>HIGH</sub> – 12) dB per               |

| Intermodulation                   |        |             |         | tone; 600 MHz < f $\le$ 6000 MHz, (P <sub>HIGH</sub> - 10) dE            |

| Intercept Point                   |        |             | 10      | per tone; 0 dB attenuation, complex                                      |

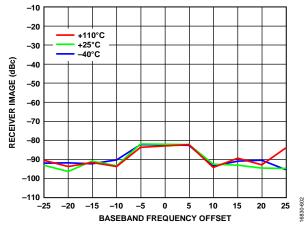

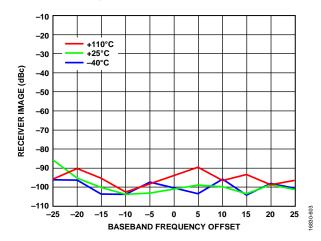

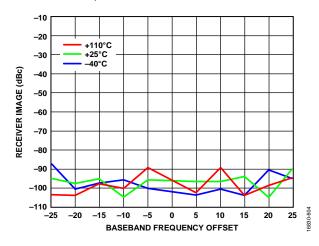

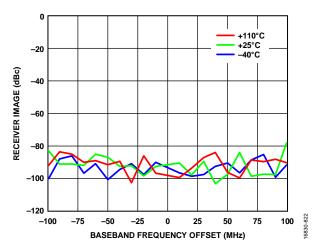

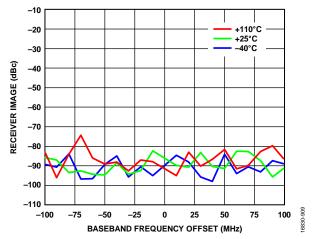

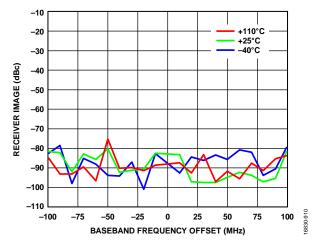

| Image Rejection                   |        | 75          | dB      | QEC active, within 200 MHz receiver bandwidth                            |

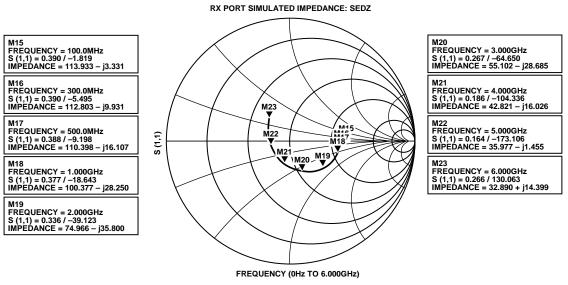

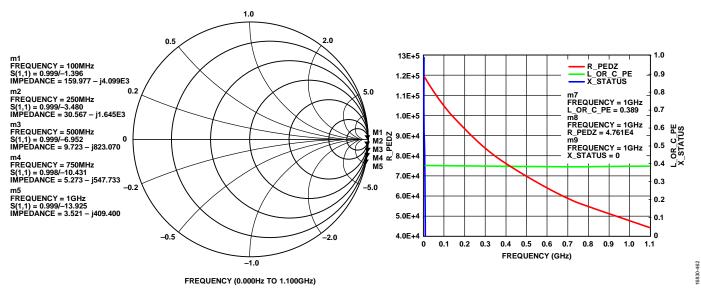

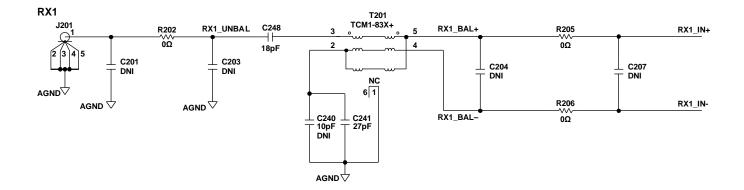

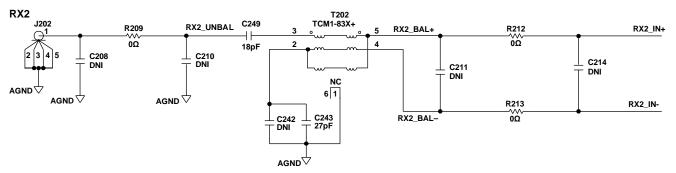

| Input Impedance                   |        | 100         | Ω       | Differential (see Figure 168)                                            |

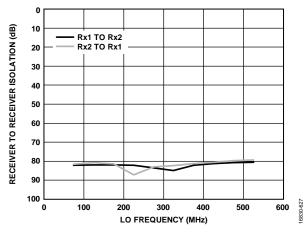

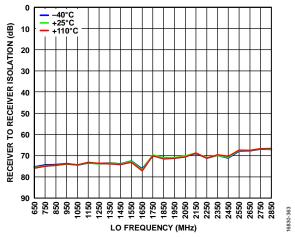

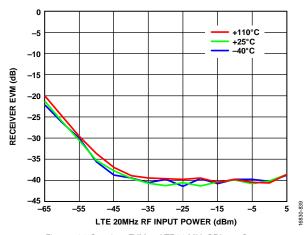

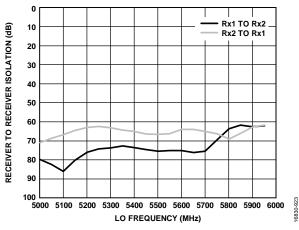

| Receiver to Receiver              |        | 77          | dB      | 75 MHz < f ≤ 600 MHz                                                     |

| Isolation                         |        |             |         |                                                                          |

|                                   |        | 65          | dB      | $600 \text{ MHz} < f \le 4800 \text{ MHz}$                               |

|                                   |        | 61          | dB      | $4800 \text{ MHz} < f \le 6000 \text{ MHz}$                              |

| Receiver Band Spurs               |        | -95         | dBm     | No more than one spur at this level per                                  |

| Referenced to RF Input at         |        |             |         | 10 MHz of receiver bandwidth                                             |

| Maximum Gain                      |        |             |         |                                                                          |

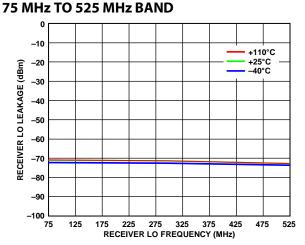

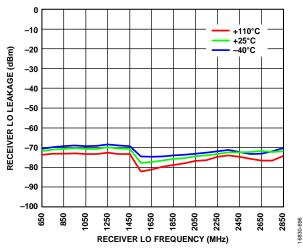

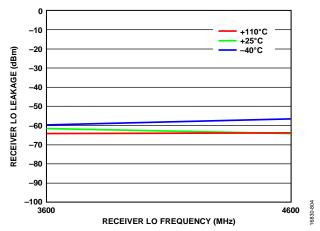

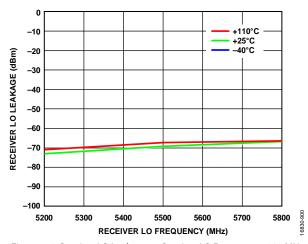

| Receiver LO Leakage at            |        |             |         | Leakage decreases decibel for decibel with attenuation for first 12 dB   |

| Receiver Input at<br>Maximum Gain |        |             |         | attenuation for first 12 dB                                              |

|                                   |        | -70         | dBm     | 75 MHz < f ≤ 600 MHz                                                     |

|                                   |        | -70<br>-70  | dBm     | $600 \text{ MHz} < f \le 3000 \text{ MHz}$                               |

|                                   |        | -70<br>-65  | dBm     | $3000 \text{ MHz} < f \le 5000 \text{ MHz}$                              |

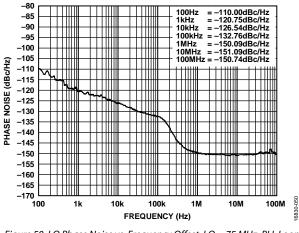

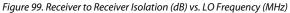

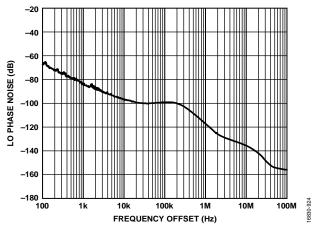

| LO SYNTHESIZER                    |        | -07         | UDIII   |                                                                          |

|                                   |        | 2.2         |         |                                                                          |

| LO Frequency Step                 |        | 2.3         | Hz      | 1.5 GHz to 2.8 GHz, 76.8 MHz phase<br>frequency detector (PFD) frequency |

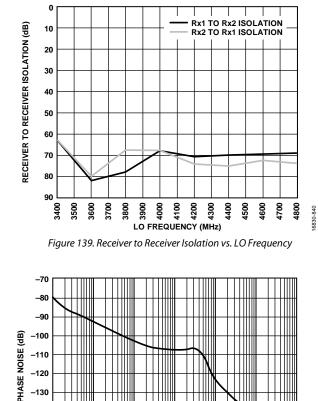

|                                   |        | 95          | dBc     |                                                                          |

| LO Spur                           |        | -85         | abc     | Excludes integer boundary spurs<br>2 kHz to 18 MHz                       |

| Integrated Phase Noise            |        | 0.014       | Q       |                                                                          |

| 75 MHz LO                         |        | 0.014       | °rms    | Narrow PLL loop bandwidth (50 kHz)                                       |

| 1900 MHz LO                       |        | 0.2         | °rms    | Narrow PLL loop bandwidth (50 kHz)                                       |

| 3800 MHz LO                       |        | 0.36        | °rms    | Wide PLL loop bandwidth (300 kHz)                                        |

| 5900 MHz LO                       |        | 0.54        | °rms    | Wide PLL loop bandwidth (300 kHz)                                        |

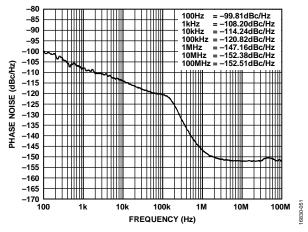

| Spot Phase Noise                  |        |             |         |                                                                          |

| 75 MHz LO                         |        |             | 15 // / | Narrow PLL loop bandwidth                                                |

| 10 kHz Offset                     |        | -126.5      | dBc/Hz  |                                                                          |

| 100 kHz Offset                    |        | -132.8      | dBc/Hz  |                                                                          |

| 1 MHz Offset                      |        | -150.1      | dBc/Hz  |                                                                          |

| 10 MHz Offset                     |        | -150.7      | dBc/Hz  |                                                                          |

| 1900 MHz LO                       |        |             |         | Narrow PLL loop bandwidth                                                |

| 100 kHz Offset                    |        | -100        | dBc/Hz  |                                                                          |

| 200 kHz Offset                    |        | -115        | dBc/Hz  |                                                                          |

| 400 kHz Offset                    |        | -120        | dBc/Hz  |                                                                          |

| 600 kHz Offset                    |        | -129        | dBc/Hz  |                                                                          |

| 800 kHz Offset                    |        | -132        | dBc/Hz  |                                                                          |

| 1.2 MHz Offset                    |        | -135        | dBc/Hz  |                                                                          |

| 1.8 MHz Offset                    |        | -140        | dBc/Hz  |                                                                          |

| 6 MHz Offset                      |        | -150        | dBc/Hz  |                                                                          |

| 10 MHz Offset                     |        | -153        | dBc/Hz  |                                                                          |

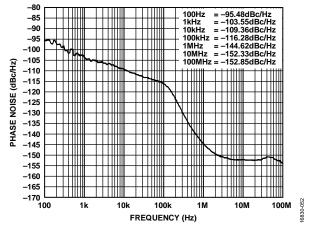

| 3800 MHz LO                       |        |             |         | Wide PLL loop bandwidth                                                  |

| 100 kHz Offset                    |        | -104        | dBc/Hz  |                                                                          |

| 1.2 MHz Offset                    |        | -125        | dBc/Hz  |                                                                          |

| 10 MHz Offset                     |        | -145        | dBc/Hz  |                                                                          |

| 5900 MHz LO                       |        |             |         | Wide PLL loop bandwidth                                                  |

| 100 kHz Offset                    |        | -99         | dBc/Hz  |                                                                          |

| 1.2 MHz Offset                    |        | -119.7      | dBc/Hz  |                                                                          |

| 10 MHz Offset                     |        | -135.4      | dBc/Hz  |                                                                          |

| LO PHASE SYNCHRONIZATION          | 1      |             |         | Change in LO delay per temperature                                       |

|                                   |        |             |         | change                                                                   |

| Phase Deviation                   | 1      | 1.6         | ps/°C   |                                                                          |

| Parameter                                      | Symbol             | Min      | Тур           | Max                | Unit             | Test Conditions/Comments                                       |

|------------------------------------------------|--------------------|----------|---------------|--------------------|------------------|----------------------------------------------------------------|

| EXTERNAL LO INPUT                              |                    |          |               |                    |                  |                                                                |

| Input Frequency                                | f <sub>extlo</sub> | 300      |               | 8000               | MHz              | Input frequency must be 2× the desired LO frequency            |

| Input Signal Power                             |                    | 0        |               | 12                 | dBm              | 50 $\Omega$ matching at the source                             |

|                                                |                    |          | 3             |                    | dBm              | $f_{EXTLO} \le 2 \text{ GHz}$ , add 0.5 dBm/GHz above 2 GHz    |

|                                                |                    |          | 6             |                    | dBm              | $f_{EXTLO} = 8 \text{ GHz}$                                    |

| External LO Input Signal<br>Differential       |                    |          |               |                    |                  | To ensure adequate QEC                                         |

| Phase Error                                    |                    |          |               | 3.6                | ps               |                                                                |

| Amplitude Error                                |                    |          |               | 1                  | dB               |                                                                |

| Duty Cycle Error                               |                    |          |               | 2                  | %                |                                                                |

| Even Order Harmonics                           |                    |          |               | -50                | dBc              |                                                                |

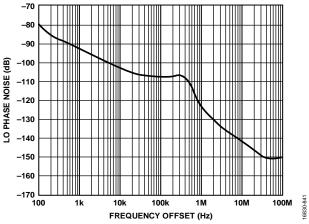

| CLOCK SYNTHESIZER                              |                    |          |               |                    |                  |                                                                |

| Integrated Phase Noise                         |                    |          |               |                    |                  | 1 kHz to 100 MHz                                               |

| 1966.08 MHz LO                                 |                    |          | 0.4           |                    | °rms             | PLL optimized for close in phase noise                         |

| Spot Phase Noise                               |                    |          |               |                    |                  |                                                                |

| 1966.08 MHz                                    |                    |          | 100           |                    | 10 /11           |                                                                |

| 100 kHz Offset                                 |                    |          | -109          |                    | dBc/Hz<br>dBc/Hz |                                                                |

| 1 MHz Offset<br>10 MHz Offset                  |                    |          | -129<br>-149  |                    | dBc/Hz           |                                                                |

| REFERENCE CLOCK                                |                    |          | -149          |                    | UBC/HZ           |                                                                |

| (REF_CLK_IN±)                                  |                    |          |               |                    |                  |                                                                |

| Frequency Range                                |                    | 10       |               | 1000               | MHz              |                                                                |

| Signal Level                                   |                    | 0.3      |               | 2.0                | V p-p            | AC-coupled, common-mode voltage ( $V_{CM}$ ) =                 |

| 5                                              |                    |          |               |                    |                  | 618 mV, use <1 V p-p input clock for best spurious performance |

| AUXILIARY CONVERTERS                           |                    |          |               |                    |                  |                                                                |

| ADC                                            |                    |          |               |                    |                  |                                                                |

| Resolution                                     |                    |          | 12            |                    | Bits             |                                                                |

| Input Voltage                                  |                    |          |               |                    |                  |                                                                |

| Minimum                                        |                    |          | 0.05          |                    | V                |                                                                |

| Maximum                                        |                    |          | VDDA_         |                    | V                |                                                                |

|                                                |                    |          | 3P3 –<br>0.05 |                    |                  |                                                                |

| DAC                                            |                    |          | 0.00          |                    |                  |                                                                |

| Resolution                                     |                    |          | 10            |                    | Bits             | Includes four offset levels                                    |

| Output Voltage                                 |                    |          |               |                    |                  |                                                                |

| Minimum                                        |                    |          | 0.7           |                    | V                | 1 V V <sub>REF</sub>                                           |

| Maximum                                        |                    |          | VDDA_         |                    | V                | 2.5 V V <sub>REF</sub>                                         |

|                                                |                    |          | 3P3 –         |                    |                  |                                                                |

|                                                |                    |          | 0.3           |                    |                  |                                                                |

| Output Drive Capability DIGITAL SPECIFICATIONS |                    |          | 10            |                    | mA               |                                                                |

| (CMOS): SERIAL PERIPHERAL                      |                    |          |               |                    |                  |                                                                |

| INTERFACE (SPI), GPIO_x                        |                    |          |               |                    |                  |                                                                |

| Logic Inputs                                   |                    |          |               |                    |                  |                                                                |

| Input Voltage<br>High Level                    |                    | VDD      |               | VDD_               | v                |                                                                |

| nıgii Level                                    |                    | NTERFACE |               | INTERFACE          | V                |                                                                |

| Low Level                                      |                    | 0        |               | VDD_               | v                |                                                                |

|                                                |                    |          |               | INTERFACE<br>× 0.2 |                  |                                                                |

| Input Current                                  |                    |          |               |                    |                  |                                                                |

| High Level                                     |                    | -10      |               | +10                | μA               |                                                                |

| Parameter                                                                                 | Symbol           | Min                        | Тур | Max                        | Unit | Test Conditions/Comments             |

|-------------------------------------------------------------------------------------------|------------------|----------------------------|-----|----------------------------|------|--------------------------------------|

| Low Level                                                                                 |                  | -10                        |     | +10                        | μA   |                                      |

| Logic Outputs                                                                             |                  |                            |     |                            |      |                                      |

| Output Voltage                                                                            |                  |                            |     |                            |      |                                      |

| High Level                                                                                |                  | VDD_<br>INTERFACE<br>× 0.8 |     |                            | V    |                                      |

| Low Level                                                                                 |                  |                            |     | VDD_<br>INTERFACE<br>× 0.2 | V    |                                      |

| Drive Capability                                                                          |                  |                            | 3   |                            | mA   |                                      |

| DIGITAL SPECIFICATIONS<br>(CMOS): GPIO_3p3_x                                              |                  |                            |     |                            |      |                                      |

| Logic Inputs                                                                              |                  |                            |     |                            |      |                                      |

| Input Voltage                                                                             |                  |                            |     |                            |      |                                      |

| High Level                                                                                |                  | VDDA_<br>3P3 × 0.8         |     | VDDA_3P3                   | V    |                                      |

| Low Level                                                                                 |                  | 0                          |     | VDDA_<br>3P3 × 0.2         | v    |                                      |

| Input Current                                                                             |                  |                            |     |                            |      |                                      |

| High Level                                                                                |                  | -10                        |     | +10                        | μΑ   |                                      |

| Low Level                                                                                 |                  | -10                        |     | +10                        | μΑ   |                                      |

| Logic Outputs                                                                             |                  |                            |     |                            |      |                                      |

| Output Voltage                                                                            |                  |                            |     |                            |      |                                      |

| High Level                                                                                |                  | VDDA_<br>3P3 × 0.8         |     |                            | V    |                                      |

| Low Level                                                                                 |                  |                            |     | VDDA_<br>3P3 × 0.2         | V    |                                      |

| Drive Capability                                                                          |                  |                            | 4   |                            | mA   |                                      |

| DIGITAL SPECIFICATIONS, LOW<br>VOLTAGE DIFFERENTIAL<br>SIGNALING (LVDS)                   |                  |                            |     |                            |      |                                      |

| Logic Inputs (SYSREF_IN±,<br>SYNCINx±)                                                    |                  |                            |     |                            |      |                                      |

| Input Voltage Range                                                                       |                  | 825                        |     | 1675                       | mV   | Each differential input in the pair  |

| Input Differential Voltage<br>Threshold                                                   |                  | -100                       |     | +100                       | mV   |                                      |

| Receiver Differential<br>Input Impedance                                                  |                  |                            | 100 |                            | Ω    | Internal termination enabled         |

| SPITIMING                                                                                 |                  |                            |     |                            |      | See the UG-1295 for more information |

| SCLK Period                                                                               | t <sub>CP</sub>  | 20                         |     |                            | ns   |                                      |

| SCLK Pulse Width                                                                          | t <sub>MP</sub>  | 10                         |     |                            | ns   |                                      |

| CS Setup to First SCLK                                                                    | tsc              | 3                          |     |                            | ns   |                                      |

| Rising Edge                                                                               |                  |                            |     |                            |      |                                      |

| Last SCLK Falling Edge to $\overline{\text{CS}}$<br>Hold                                  | t <sub>HC</sub>  | 0                          |     |                            | ns   |                                      |

| SDIO Data Input Setup to<br>SCLK                                                          | ts               | 2                          |     |                            | ns   |                                      |

| SDIO Data Input Hold to<br>SCLK                                                           | t <sub>H</sub>   | 0                          |     |                            | ns   |                                      |

| SCLK Rising Edge to Output<br>Data Delay (3-Wire Mode<br>or 4-Wire Mode)                  | t <sub>co</sub>  | 3                          |     | 8                          | ns   |                                      |

| Bus Turnaround Time, Read<br>After Baseband Processor<br>(BBP) Drives Last Address<br>Bit | t <sub>нzм</sub> | t <sub>Η</sub>             |     | tco                        | ns   |                                      |

| Parameter                                                             | Symbol               | Min   | Тур    | Max             | Unit            | Test Conditions/Comments                                                                                   |

|-----------------------------------------------------------------------|----------------------|-------|--------|-----------------|-----------------|------------------------------------------------------------------------------------------------------------|

| Bus Turnaround Time, Read<br>After ADRV9008-1 Drives<br>Last Data Bit | t <sub>HZS</sub>     | 0     |        | t <sub>co</sub> | ns              |                                                                                                            |

| JESD204B DATA OUTPUT<br>TIMING                                        |                      |       |        |                 |                 | AC-coupled                                                                                                 |

| Unit Interval                                                         | UI                   | 81.38 |        | 320             | ps              |                                                                                                            |

| Data Rate Per Channel (NRZ)                                           |                      | 3125  |        | 12288           | Mbps            |                                                                                                            |

| Rise Time                                                             | t <sub>R</sub>       | 24    | 39.5   |                 | ps              | 20% to 80% in 100 Ω load                                                                                   |

| Fall Time                                                             | t <sub>F</sub>       | 24    | 39.4   |                 | ps              | 20% to 80% in 100 Ω load                                                                                   |

| Output Common-Mode<br>Voltage                                         | $V_{CM}$             | 0     |        | 1.8             | V               | AC-coupled                                                                                                 |

| Differential Output Voltage                                           | V <sub>DIFF</sub>    | 360   | 600    | 770             | mV              |                                                                                                            |

| Short-Circuit Current                                                 |                      | -100  |        | +100            | mA              |                                                                                                            |

| Differential Termination<br>Impedance                                 |                      | 80    | 94.2   | 120             | Ω               |                                                                                                            |

| Total Jitter                                                          |                      |       | 15.13  |                 | ps              | Bit error rate (BER) = $10^{-15}$                                                                          |

| Uncorrelated Bounded<br>High Probability Jitter                       | UBHPJ                |       | 0.56   |                 | ps              |                                                                                                            |

| Duty Cycle Distortion                                                 | DCD                  |       | 0.369  |                 | ps              |                                                                                                            |

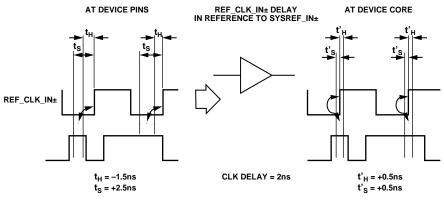

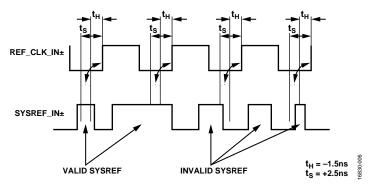

| SYSREF_IN± Setup Time to<br>REF_CLK_IN±                               |                      | 2.5   |        |                 | ns              | See Figure 2                                                                                               |

| SYSREF_IN± Hold Time to<br>REF_CLK_IN±                                |                      | -1.5  |        |                 | ns              | See Figure 2                                                                                               |

| Latency                                                               | t <sub>LAT FRM</sub> |       |        |                 |                 | $REF_CLK_IN \pm = 245.76 MHz$                                                                              |

|                                                                       | _                    |       | 89.4   |                 | Clock<br>cycles | Receiver bandwidth = 200 MHz, IQ rate = 245.76 MHz, lane rate = 9830.4 MHz,<br>M = 2, L = 2, N = 16, S = 1 |

|                                                                       |                      |       | 364.18 |                 | ns              |                                                                                                            |

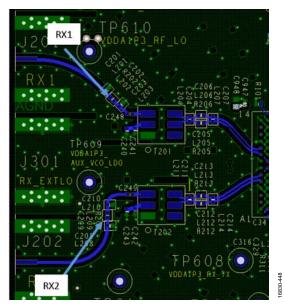

<sup>1</sup> VDDA1P3 refers to all analog 1.3 V supplies, including VDDA1P3\_RF\_SYNTH, VDDA1P3\_BB, VDDA1P3\_RX\_RF, VDDA1P3\_RF\_VCO\_LDO, VDDA1P3\_RF\_LO, VDDA1P3\_SER, VDDA1P3\_CLOCK\_SYNTH, VDDA1P3\_CLOCK\_VCO\_LDO, VDDA1P3\_AUX\_SYNTH, and VDDA1P3\_AUX\_VCO\_LDO.

#### **CURRENT AND POWER CONSUMPTION SPECIFICATIONS**

#### Table 2.

| Parameter                          | Min   | Тур  | Мах   | Unit | Test Conditions/Comments                                                                                        |

|------------------------------------|-------|------|-------|------|-----------------------------------------------------------------------------------------------------------------|

| SUPPLY CHARACTERISTICS             |       |      |       |      |                                                                                                                 |

| VDDA1P3 <sup>1</sup> Analog Supply | 1.267 | 1.3  | 1.33  | V    |                                                                                                                 |

| VDDD1P3_DIG Supply                 | 1.267 | 1.3  | 1.33  | V    |                                                                                                                 |

| VDDA1P8_AN Supply                  | 1.71  | 1.8  | 1.89  | V    |                                                                                                                 |

| VDDA1P8_BB Supply                  | 1.71  | 1.8  | 1.89  | V    |                                                                                                                 |

| VDD_INTERFACE Supply               | 1.71  | 1.8  | 2.625 | V    | CMOS and LVDS supply, 1.8 V to 2.5 V nominal range                                                              |

| VDDA_3P3 Supply                    | 3.135 | 3.3  | 3.465 | V    |                                                                                                                 |

| POSITIVE SUPPLY CURRENT            |       |      |       |      | LO at 2600 MHz                                                                                                  |

| 200 MHz Receiver Bandwidth         |       |      |       |      | Two receivers enabled                                                                                           |

| VDDA1P3 <sup>1</sup> Analog Supply |       | 1645 |       | mA   |                                                                                                                 |

| VDDD1P3_DIG Supply                 |       | 984  |       | mA   | Receiver QEC active                                                                                             |

| VDDA1P8_AN Supply                  |       | 0.4  |       | mA   |                                                                                                                 |

| VDDA1P8_BB Supply                  |       | 68   |       | mA   |                                                                                                                 |

| VDD_INTERFACE Supply               |       | 8    |       | mA   |                                                                                                                 |

| VDDA_3P3 Supply                    |       | 3    |       | mA   | No Auxiliary DAC x or AUXADC_x enabled (if enabled, AUXADC_x adds 2.7 mA, and each Auxiliary DAC x adds 1.5 mA) |

| Total Power Dissipation            |       | 3.57 |       | W    | Typical supply voltages, receiver QEC active                                                                    |

<sup>1</sup> VDDA1P3 refers to all analog 1.3 V supplies, including VDDA1P3\_RF\_SYNTH, VDDA1P3\_BB, VDDA1P3\_RX\_RF, VDDA1P3\_RX, VDDA1P3\_RF\_VCO\_LDO, VDDA1P3\_RF\_LO, VDDA1P3\_SER, VDDA1P3\_CLOCK\_SYNTH, VDDA1P3\_CLOCK\_VCO\_LDO, VDDA1P3\_AUX\_SYNTH, and VDDA1P3\_AUX\_VCO\_LDO.

## **Data Sheet**

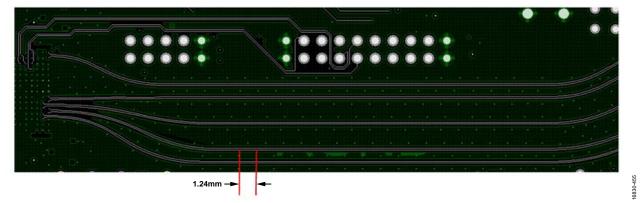

16830-005

#### **TIMING DIAGRAMS**

NOTES 1. t<sub>H</sub> AND t<sub>S</sub> ARE THE HOLD AND SETUP TIMES FOR THE REF\_CLK\_IN± PINS. t'<sub>H</sub> AND t'<sub>S</sub> REFER TO THE DELAYED HOLD AND SETUP TIMES AT THE DEVICE CORE IN REFERENCE TO THE SYSREF\_N± SIGNALS DUE TO AN INTERNAL BUFFER THAT THE SIGNAL PASSES THROUGH.

Figure 2. SYSREF\_IN± Setup and Hold Timing

Figure 3. SYSREF\_IN± Setup and Hold Timing Examples, Relative to Device Clock

### **ABSOLUTE MAXIMUM RATINGS**

#### Table 3.

| 1 4010 01                                         |                                     |

|---------------------------------------------------|-------------------------------------|

| Parameter                                         | Rating                              |

| VDDA1P3 <sup>1</sup> to VSSA                      | –0.3 V to +1.4 V                    |

| VDDD1P3_DIG to VSSD                               | –0.3 V to +1.4 V                    |

| VDD_INTERFACE to VSSA                             | –0.3 V to +3.0 V                    |

| VDDA_3P3 to VSSA                                  | –0.3 V to +3.9 V                    |

| VDD_INTERFACE Logic Inputs and<br>Outputs to VSSD | –0.3 V to VDD_<br>INTERFACE + 0.3 V |

| JESD204B Logic Outputs to VSSA                    | -0.3 V to VDDA1P3_SER               |

| Input Current to Any Pin Except<br>Supplies       | ±10 mA                              |

| Maximum Input Power into RF Port                  | 23 dBm (peak)                       |

| Maximum Junction Temperature                      | 110°C                               |

| Storage Temperature Range                         | –65°C to +150°C                     |

|                                                   |                                     |

<sup>1</sup> VDDA1P3 refers to all analog 1.3 V supplies, including VDDA1P3\_RF\_SYNTH, VDDA1P3\_BB, VDDA1P3\_RX\_RF, VDDA1P3\_RX, VDDA1P3\_RF\_VCO\_LDO, VDDA1P3\_RF\_LO, VDDA1P3\_CLOCK\_SYNTH, VDDA1P3\_CLOCK\_SYNTH, and VDDA1P3\_CLOCK\_VCO\_LDO.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### **REFLOW PROFILE**

The ADRV9008-1 reflow profile is in accordance with the JEDEC JESD204B criteria for Pb-free devices. The maximum reflow temperature is 260°C.

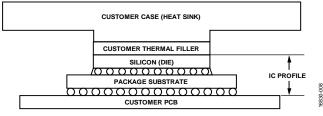

#### THERMAL MANAGEMENT

The ADRV9008-1 is a high power device that can dissipate over 3 W depending on the user application and configuration. Because of the power dissipation, the ADRV9008-1 uses an exposed die package to provide the customer with the most effective method of controlling the die temperature. The exposed die allows cooling of the die directly. Figure 4 shows the profile view of the device mounted to a user printed circuit board (PCB) and a heat sink (typically the aluminum case) to keep the junction (exposed die) below the maximum junction temperature shown in Table 3. The device is designed for a lifetime of 10 years when operating at the maximum junction temperature.

#### THERMAL RESISTANCE

$\theta_{JA}$  is specified for the worst-case conditions, that is, a device soldered in a circuit board for surface-mount packages. Thermal resistance data for the ADRV9008-1 mounted on both a JEDEC 2S2P test board and a 10-layer Analog Devices, Inc., evaluation board is listed in Table 4. Do not exceed the absolute maximum junction temperature rating in Table 3. Ten-layer PCB entries refer to the 10-layer Analog Devices evaluation board, which more accurately reflects the PCB used in customer applications.

#### Table 4. Thermal Resistance<sup>1, 2</sup>

| Package Type | $\theta_{JA}$ $\theta_{JC_{TOP}}$ |      | θ <sub>JB</sub> | Ψ,, | $\Psi_{JB}$ | Unit |  |  |  |  |  |

|--------------|-----------------------------------|------|-----------------|-----|-------------|------|--|--|--|--|--|

| BC-196-13    | 21.1                              | 0.04 | 4.9             | 0.3 | 4.9         | °C/W |  |  |  |  |  |

$^1$  For the  $\theta_{\rm JC}$  test, 100  $\mu m$  thermal interface material (TIM) is used. TIM is assumed to have 3.6 thermal conductivity watts/(meter  $\times$  Kelvin).

<sup>2</sup> Using enhanced heat removal techniques such as PCB, heat sink, and airflow improves the thermal resistance values.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

Figure 4. Typical Thermal Management Solution

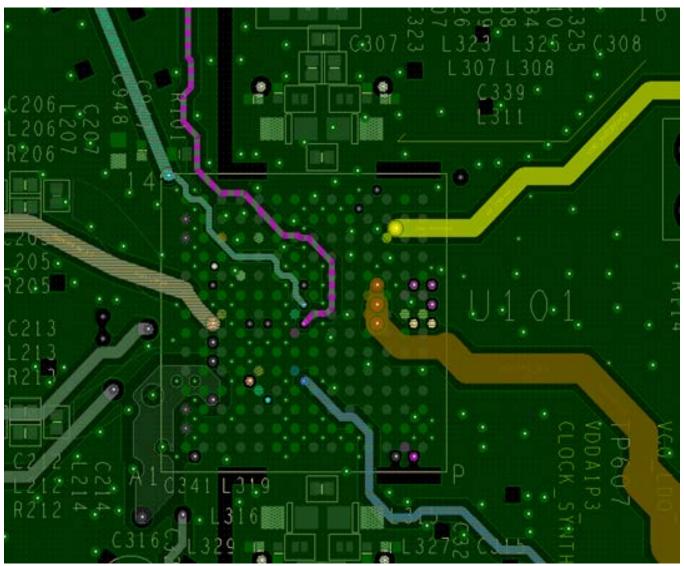

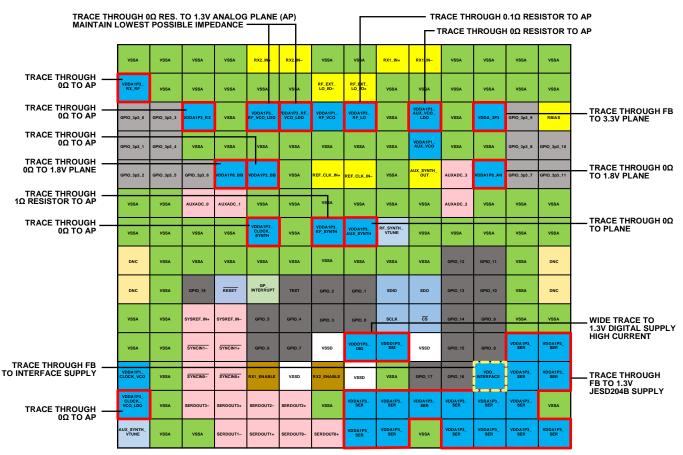

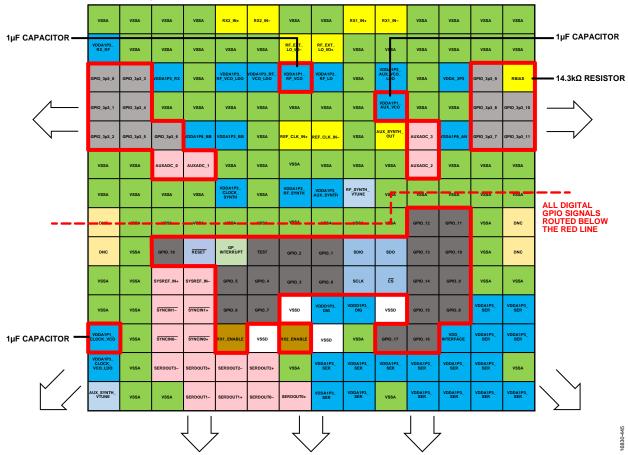

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

|   | 1                             | 2          | 3          | 4          | 5                           | 6                      | 7                    | 8                     | 9                  | 10                          | 11              | 12              | 13              | 14              |

|---|-------------------------------|------------|------------|------------|-----------------------------|------------------------|----------------------|-----------------------|--------------------|-----------------------------|-----------------|-----------------|-----------------|-----------------|

| A | VSSA                          | VSSA       | VSSA       | VSSA       | RX2_IN+                     | RX2_IN-                | VSSA                 | VSSA                  | RX1_IN+            | RX1_IN-                     | VSSA            | VSSA            | VSSA            | VSSA            |

| в | VDDA1P3_<br>RX_RF             | VSSA       | VSSA       | VSSA       | VSSA                        | VSSA                   | RF_EXT_<br>LO_I/O-   | RF_EXT_<br>LO_I/O+    | VSSA               | VSSA                        | VSSA            | VSSA            | VSSA            | VSSA            |

| с | GPIO_3p3_0                    | GPIO_3p3_3 | VDDA1P3_RX | VSSA       | VDDA1P3_<br>RF_VCO_LDO      | VDDA1P3_RF_<br>VCO_LDO | VDDA1P1_<br>RF_VCO   | VDDA1P3_<br>RF_LO     | VSSA               | VDDA1P3_<br>AUX_VCO_<br>LDO | VSSA            | VDDA_3P3        | GPIO_3p3_9      | RBIAS           |

| D | GPIO_3p3_1                    | GPIO_3p3_4 | VSSA       | VSSA       | VSSA                        | VSSA                   | VSSA                 | VSSA                  | VSSA               | VDDA1P1_<br>AUX_VCO         | VSSA            | VSSA            | GPIO_3p3_8      | GPIO_3p3_10     |

| E | GPIO_3p3_2                    | GPIO_3p3_5 | GPIO_3p3_6 | VDDA1P8_BB | VDDA1P3_BB                  | VSSA                   | REF_CLK_IN+          | REF_CLK_IN-           | VSSA               | AUX_SYNTH_<br>OUT           | AUXADC_3        | VDDA1P8_AN      | GPIO_3p3_7      | GPIO_3p3_11     |

| F | VSSA                          | VSSA       | AUXADC_0   | AUXADC_1   | VSSA                        | VSSA                   | VSSA                 | VSSA                  | VSSA               | VSSA                        | AUXADC_2        | VSSA            | VSSA            | VSSA            |

| G | VSSA                          | VSSA       | VSSA       | VSSA       | VDDA1P3_<br>CLOCK_<br>SYNTH | VSSA                   | VDDA1P3_<br>RF_SYNTH | VDDA1P3_<br>AUX_SYNTH | RF_SYNTH_<br>VTUNE | VSSA                        | VSSA            | VSSA            | VSSA            | VSSA            |

| н | DNC                           | VSSA       | VSSA       | VSSA       | VSSA                        | VSSA                   | VSSA                 | VSSA                  | VSSA               | VSSA                        | GPIO_12         | GPIO_11         | VSSA            | DNC             |

| J | DNC                           | VSSA       | GPIO_18    | RESET      | GP_<br>INTERRUPT            | TEST                   | GPIO_2               | GPIO_1                | SDIO               | SDO                         | GPIO_13         | GPIO_10         | VSSA            | DNC             |

| к | VSSA                          | VSSA       | SYSREF_IN+ | SYSREF_IN- | GPIO_5                      | GPIO_4                 | GPIO_3               | GPIO_0                | SCLK               | CS                          | GPIO_14         | GPIO_9          | VSSA            | VSSA            |

| L | VSSA                          | VSSA       | SYNCIN1-   | SYNCIN1+   | GPIO_6                      | GPIO_7                 | VSSD                 | VDDD1P3_<br>DIG       | VDDD1P3_<br>DIG    | VSSD                        | GPIO_15         | GPIO_8          | VDDA1P3_<br>SER | VDDA1P3_<br>SER |

| м | VDDA1P1_<br>CLOCK_VCO         | VSSA       | SYNCIN0-   | SYNCIN0+   | RX1_ENABLE                  | VSSD                   | RX2_ENABLE           | VSSD                  | VSSA               | GPIO_17                     | GPIO_16         |                 | VDDA1P3_<br>SER | VDDA1P3_<br>SER |

| N | VDDA1P3_<br>CLOCK_<br>VCO_LDO | VSSA       | SERDOUT3-  | SERDOUT3+  | SERDOUT2-                   | SERDOUT2+              | VSSA                 | VDDA1P3_<br>SER       | VDDA1P3_<br>SER    | VDDA1P3_<br>SER             | VDDA1P3_<br>SER | VDDA1P3_<br>SER | VDDA1P3_<br>SER | VSSA            |

| Ρ | AUX_SYNTH_<br>VTUNE           | VSSA       | VSSA       | SERDOUT1-  | SERDOUT1+                   | SERDOUT0-              | SERDOUT0+            | VDDA1P3_<br>SER       | VDDA1P3_<br>SER    | VSSA                        | VDDA1P3_<br>SER | VDDA1P3_<br>SER | VDDA1P3_<br>SER | VDDA1P3_<br>SER |

ADRV9008-1

16830-999

Figure 5. Pin Configuration

#### **Table 5. Pin Function Descriptions**

| Pin No.                          | Туре  | Mnemonic | Description                               |

|----------------------------------|-------|----------|-------------------------------------------|

| A1 to A4, A7, A8, A11 to A14, B2 | Input | VSSA     | Analog Supply Voltage (V <sub>ss</sub> ). |

| to B6, B9 to B14, C4, C9, C11,   |       |          |                                           |

| D3 to D9, D11, D12, E6, E9, F1,  |       |          |                                           |

| F2, F5 to F10, F12 to F14, G1    |       |          |                                           |

| to G4, G6, G10 to G14, H2 to     |       |          |                                           |

| H10, H13, J2, J13, K1, K2, K13,  |       |          |                                           |

| K14, L1, L2, M2, M9, N2, N7,     |       |          |                                           |

| N14, P2, P3, P10                 |       |          |                                           |

| Pin No. | Туре             | Mnemonic                          | Description                                                                                                                                                                                                                                                                                                                                                            |

|---------|------------------|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

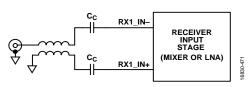

| A5, A6  | Input            | RX2_IN+, RX2_IN–                  | Differential Input for Receiver 1. When unused, connect these pins to ground.                                                                                                                                                                                                                                                                                          |

| A9, A10 | Input            | RX1_IN+, RX1_IN–                  | Differential Input for Receiver 2. When unused, connect these pins to ground.                                                                                                                                                                                                                                                                                          |

| B1      | Input            | VDDA1P3_RX_RF                     | Receiver Mixer Supply.                                                                                                                                                                                                                                                                                                                                                 |

| B7, B8  | Input            | RF_EXT_LO_I/O-,<br>RF_EXT_LO_I/O+ | Differential External LO Input/Output. If these pins are used<br>for external LO, the input frequency must be 2× the desired<br>carrier frequency. When unused, do not connect these pins.                                                                                                                                                                             |

| C1      | Input/<br>output | GPIO_3p3_0                        | GPIO Pin Referenced to 3.3 V Supply. The alternate function is<br>Auxiliary DAC 4. Because this pin contains an input stage, the<br>voltage on the pin must be controlled. When unused, this pin<br>can be tied to ground through a resistor to safeguard against<br>misconfiguration, or this pin can be left floating, programmed as<br>an output, and driven low.   |

| C2      | Input/<br>output | GPIO_3p3_3                        | GPIO Pin Referenced to 3.3 V Supply. Because this pin contains<br>an input stage, the voltage on the pin must be controlled. When<br>unused, this pin can be tied to ground through a resistor to<br>safeguard against misconfiguration, or this pin can be left<br>floating, programmed as an output, and driven low.                                                 |

| С3      | Input            | VDDA1P3_RX                        | 1.3 V Supply for Receiver Baseband Circuits, Transimpedance<br>Amplifier (TIA), Baseband Filters, and Auxiliary DACs.                                                                                                                                                                                                                                                  |

| C5, C6  | Input            | VDDA1P3_RF_VCO_LDO                | RF VCO Low Dropout (LDO) Supply Inputs. Connect Pin C5 to<br>Pin C6. Use a separate trace to a common supply point.                                                                                                                                                                                                                                                    |

| C7      | Input            | VDDA1P1_RF_VCO                    | 1.1 V VCO Supply. Decouple this pin with 1 μF.                                                                                                                                                                                                                                                                                                                         |

| C8      | Input            | VDDA1P3_RF_LO                     | 1.3 V LO Generator for RF Synthesizer. This pin is sensitive to aggressors.                                                                                                                                                                                                                                                                                            |

| C10     | Input            | VDDA1P3_AUX_VCO_LDO               | 1.3 V Supply.                                                                                                                                                                                                                                                                                                                                                          |

| C12     | Input            | VDDA_3P3                          | General-Purpose Output Pull-Up Voltage and Auxiliary DAC Supply Voltage.                                                                                                                                                                                                                                                                                               |

| C13     | Input/<br>output | GPIO_3p3_9                        | GPIO Pin Referenced to 3.3 V Supply. The alternative function<br>is Auxiliary DAC 9. Because this pin contains an input stage,<br>the voltage on the pin must be controlled. When unused, this<br>pin can be tied to ground through a resistor to safeguard<br>against misconfiguration, or this pin can be left floating,<br>programmed as an output, and driven low. |

| C14     | Input/<br>output | RBIAS                             | Bias Resistor. Tie this pin to ground using a 14.3 k $\Omega$ resistor.<br>This pin generates an internal current based on an external 1% resistor.                                                                                                                                                                                                                    |

| D1      | Input/<br>output | GPIO_3p3_1                        | GPIO Pin Referenced to 3.3 V Supply. The alternative function<br>is Auxiliary DAC 5. Because this pin contains an input stage,<br>the voltage on the pin must be controlled. When unused, this<br>pin can be tied to ground through a resistor to safeguard<br>against misconfiguration, or this pin can be left floating,<br>programmed as an output, and driven low. |

| D2      | Input/<br>output | GPIO_3p3_4                        | GPIO Pin Referenced to 3.3 V Supply. The alternative function<br>is Auxiliary DAC 6. Because this pin contains an input stage,<br>the voltage on the pin must be controlled. When unused, this<br>pin can be tied to ground through a resistor to safeguard<br>against misconfiguration, or this pin can be left floating,<br>programmed as an output, and driven low. |

| D10     | Input            | VDDA1P1_AUX_VCO                   | 1.1 V VCO Supply. Decouple with 1 μF.                                                                                                                                                                                                                                                                                                                                  |

| D13     | Input/<br>output | GPIO_3p3_8                        | GPIO Pin Referenced to 3.3 V Supply. The alternative function<br>is Auxiliary DAC 1. Because this pin contains an input stage,<br>the voltage on the pin must be controlled. When unused, this<br>pin can be tied to ground through a resistor to safeguard<br>against misconfiguration, or this pin can be left floating,<br>programmed as an output, and driven low. |

| Pin No.          | Туре             | Mnemonic                 | Description                                                                                                                   |

|------------------|------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| D14              | Input/           | GPIO_3p3_10              | GPIO Pin Referenced to 3.3 V Supply. The alternative function                                                                 |

|                  | output           |                          | is Auxiliary DAC 0. Because this pin contains an input stage,                                                                 |

|                  |                  |                          | the voltage on the pin must be controlled. When unused, this                                                                  |

|                  |                  |                          | pin can be tied to ground through a resistor to safeguard                                                                     |

|                  |                  |                          | against misconfiguration, or this pin can be left floating, programmed as an output, and driven low.                          |

| E1               | Input/           | GPIO_3p3_2               | GPIO Pin Referenced to 3.3 V Supply. Because this pin contains                                                                |

| 21               | output           | 010_565_2                | an input stage, the voltage on the pin must be controlled.                                                                    |

|                  | output           |                          | When unused, this pin can be tied to ground through a resistor                                                                |

|                  |                  |                          | to safeguard against misconfiguration, or this pin can be left                                                                |

|                  |                  |                          | floating, programmed as an output, and driven low.                                                                            |

| E2               | Input/           | GPIO_3p3_5               | GPIO Pin Referenced to 3.3 V Supply. The alternative function                                                                 |

|                  | output           |                          | is Auxiliary DAC 7. Because this pin contains an input stage,                                                                 |

|                  |                  |                          | the voltage on the pin must be controlled. When unused, this                                                                  |

|                  |                  |                          | pin can be tied to ground through a resistor to safeguard                                                                     |

|                  |                  |                          | against misconfiguration, or this pin can be left floating, programmed as an output, and driven low.                          |

| E3               | Input/           | GPIO_3p3_6               | GPIO Pin Referenced to 3.3 V Supply. The alternative function                                                                 |

| 23               | output           | GFI0_5P5_0               | is Auxiliary DAC 8. Because this pin contains an input stage,                                                                 |

|                  | output           |                          | the voltage on the pin must be controlled. When unused, this                                                                  |

|                  |                  |                          | pin can be tied to ground through a resistor to safeguard                                                                     |

|                  |                  |                          | against misconfiguration, or this pin can be left floating,                                                                   |

|                  |                  |                          | programmed as an output, and driven low.                                                                                      |

| E4               | Input            | VDDA1P8_BB               | 1.8 V Supply for the ADC and DAC.                                                                                             |

| E5               | Input            | VDDA1P3_BB               | 1.3 V Supply for the ADC, DAC, and Auxiliary ADCs.                                                                            |

| E7, E8           | Input            | REF_CLK_IN+, REF_CLK_IN- | Device Clock Differential Input.                                                                                              |

| E10              | Output           | AUX_SYNTH_OUT            | Auxiliary PLL Output. When unused, do not connect this pin.                                                                   |

| E11, F3, F4, F11 | Input            | AUXADC_0 to AUXADC_3     | Auxiliary ADC Input. When unused, connect these pins to ground                                                                |

|                  |                  |                          | with a pull-down resistor, or connect directly to ground.                                                                     |

| E12              | Input            | VDDA1P8_AN               | 1.8 V Bias Supply for Analog Circuitry.                                                                                       |

| E13              | Input/           | GPIO_3p3_7               | GPIO Pin Referenced to 3.3 V Supply. The alternative function                                                                 |

|                  | output           |                          | is Auxiliary DAC 2. Because this pin contains an input stage,<br>the voltage on the pin must be controlled. When unused, this |

|                  |                  |                          | pin can be tied to ground through a resistor to safeguard                                                                     |

|                  |                  |                          | against misconfiguration, or this pin can be left floating,                                                                   |

|                  |                  |                          | programmed as an output, and driven low.                                                                                      |

| E14              | Input/           | GPIO_3p3_11              | GPIO Pin Referenced to 3.3 V Supply. The alternative function                                                                 |

|                  | output           |                          | is Auxiliary DAC 3. Because this pin contains an input stage,                                                                 |

|                  |                  |                          | the voltage on the pin must be controlled. When unused, this                                                                  |

|                  |                  |                          | pin can be tied to ground through a resistor to safeguard                                                                     |

|                  |                  |                          | against misconfiguration, or this pin can be left floating,<br>programmed as outputs, and driven low.                         |

| G5               | Input            |                          | 1.3 V Supply Input for Clock Synthesizer. Use a separate trace                                                                |

| GS               | Input            | VDDA1P3_CLOCK_SYNTH      | on the PCB back to a common supply point.                                                                                     |

| G7               | Input            | VDDA1P3_RF_SYNTH         | 1.3 V RF Synthesizer Supply Input. This pin is sensitive to                                                                   |

| G,               | mpat             |                          | aggressors.                                                                                                                   |

| G8               | Input            | VDDA1P3_AUX_SYNTH        | 1.3 V Auxiliary Synthesizer Supply Input.                                                                                     |

| G9               | Output           | RF_SYNTH_VTUNE           | RF Synthesizer V <sub>TUNE</sub> Output.                                                                                      |

| H1, J1, H14, J14 | DNC <sup>1</sup> | DNC                      | Do Not Connect. Do not connect these pins.                                                                                    |

| H11              | Input/           | GPIO_12                  | Digital GPIO, 1.8 V to 2.5 V. Because this pin contains an input                                                              |

|                  | output           |                          | stage, the voltage on the pin must be controlled. When                                                                        |