# S34ML08G1 NAND Flash Memory for Embedded

8 Gb, 1-bit ECC, x8 I/O, 3V  $V_{CC}$

Data Sheet (Advance Information)

**Notice to Readers:** This document states the current technical specifications regarding the Spansion product(s) described herein. Each product described herein may be designated as Advance Information, Preliminary, or Full Production. See *Notice On Data Sheet Designations* for definitions.

## **Notice On Data Sheet Designations**

Spansion Inc. issues data sheets with Advance Information or Preliminary designations to advise readers of product information or intended specifications throughout the product life cycle, including development, qualification, initial production, and full production. In all cases, however, readers are encouraged to verify that they have the latest information before finalizing their design. The following descriptions of Spansion data sheet designations are presented here to highlight their presence and definitions.

#### **Advance Information**

The Advance Information designation indicates that Spansion Inc. is developing one or more specific products, but has not committed any design to production. Information presented in a document with this designation is likely to change, and in some cases, development on the product may discontinue. Spansion Inc. therefore places the following conditions upon Advance Information content:

"This document contains information on one or more products under development at Spansion Inc. The information is intended to help you evaluate this product. Do not design in this product without contacting the factory. Spansion Inc. reserves the right to change or discontinue work on this proposed product without notice."

#### **Preliminary**

The Preliminary designation indicates that the product development has progressed such that a commitment to production has taken place. This designation covers several aspects of the product life cycle, including product qualification, initial production, and the subsequent phases in the manufacturing process that occur before full production is achieved. Changes to the technical specifications presented in a Preliminary document should be expected while keeping these aspects of production under consideration. Spansion places the following conditions upon Preliminary content:

"This document states the current technical specifications regarding the Spansion product(s) described herein. The Preliminary status of this document indicates that product qualification has been completed, and that initial production has begun. Due to the phases of the manufacturing process that require maintaining efficiency and quality, this document may be revised by subsequent versions or modifications due to changes in technical specifications."

#### Combination

Some data sheets contain a combination of products with different designations (Advance Information, Preliminary, or Full Production). This type of document distinguishes these products and their designations wherever necessary, typically on the first page, the ordering information page, and pages with the DC Characteristics table and the AC Erase and Program table (in the table notes). The disclaimer on the first page refers the reader to the notice on this page.

#### Full Production (No Designation on Document)

When a product has been in production for a period of time such that no changes or only nominal changes are expected, the Preliminary designation is removed from the data sheet. Nominal changes may include those affecting the number of ordering part numbers available, such as the addition or deletion of a speed option, temperature range, package type, or  $V_{IO}$  range. Changes may also include those needed to clarify a description or to correct a typographical error or incorrect specification. Spansion Inc. applies the following conditions to documents in this category:

"This document states the current technical specifications regarding the Spansion product(s) described herein. Spansion Inc. deems the products to have been in sufficient production volume such that subsequent versions of this document are not expected to change. However, typographical or specification corrections, or modifications to the valid combinations offered may occur."

Questions regarding these document designations may be directed to your local sales office.

## S34ML08G1 NAND Flash Memory for Embedded

8 Gb, 1-bit ECC, x8 I/O, 3V V<sub>CC</sub>

Data Sheet (Advance Information)

## **General Description**

The Spansion® S34ML08G1 8-Gb NAND is offered in 3.3  $V_{CC}$  with x8 I/O interface. This document contains information for the S34ML08G1 device, which is a dual-die stack of two S34ML04G1 die. For detailed specifications, please refer to the discrete die data sheet: S34ML01G1\_04G1.

#### **Distinctive Characteristics**

- Density

- 8 Gb (4 Gb x 2)

- Architecture (For each 4 Gb device)

- Input / Output Bus Width: 8-bits

- Page Size: (2048 + 64) bytes; 64 bytes is spare area

- Block Size: 64 Pages or (128k + 4k) bytes

- Plane Size

- 2048 Blocks per Plane or (256M + 8M) bytes

- Device Size

- 2 Planes per Device or 512 Mbyte

- NAND Flash Interface

- Open NAND Flash Interface (ONFI) 1.0 compliant

- Address, Data and Commands multiplexed

- Supply Voltage

- 3.3V device: Vcc = 2.7V ~ 3.6V

#### ■ Security

- One Time Programmable (OTP) area

- Hardware program/erase disabled during power transition

#### Additional Features

- Supports Multiplane Program and Erase commands

- Supports Copy Back Program

- Supports Multiplane Copy Back Program

- Supports Read Cache

#### **■** Electronic Signature

- Manufacturer ID: 01h

#### ■ Operating Temperature

- Industrial: -40°C to 85°C

- Automotive: -40°C to 105°C

#### **Performance**

- Page Read / Program

- Random access: 25 µs (Max)

- Sequential access: 25 ns (Min)

- Program time / Multiplane Program time: 200 µs (Typ)

- Block Erase / Multiplane Erase (S34ML04G1)

- Block Erase time: 3.5 ms (Typ)

#### ■ Reliability

- 100,000 Program / Erase cycles (Typ)

(with 1 bit / 512 + 16 byte ECC)

- 10 Year Data retention (Typ)

- Blocks zero and one are valid and will be valid for at least 1000 program-erase cycles with ECC

#### ■ Package Options

- Lead Free and Low Halogen

- 48-Pin TSOP 12 x 20 x 1.2 mm

- 63-Ball BGA 9 x 11 x 1 mm

## **Table of Contents**

| Gen  | eral Description                                                                                                                                                        |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Dist | inctive Characteristics                                                                                                                                                 |

| Perf | formance 3                                                                                                                                                              |

| 1.   | Connection Diagram 5                                                                                                                                                    |

| 2.   | Pin Description                                                                                                                                                         |

| 3.   | Block Diagrams                                                                                                                                                          |

| 4.   | Addressing                                                                                                                                                              |

| 5.   | Read Status Enhanced                                                                                                                                                    |

| 6.   | Extended Read Status                                                                                                                                                    |

| 7.   | Read ID         10           7.1         Read Parameter Page         11                                                                                                 |

| 8.   | Electrical Characteristics138.1Valid Blocks138.2DC Characteristics148.3Pin Capacitance148.4Power Consumptions and Pin Capacitance for Allowed Stacking Configurations14 |

| 9.   | Physical Interface159.1 Physical Diagram15                                                                                                                              |

| 10.  | Ordering Information                                                                                                                                                    |

| 11.  | <b>Appendix A</b> — <b>Errata</b>                                                                                                                                       |

| 12.  | Revision History                                                                                                                                                        |

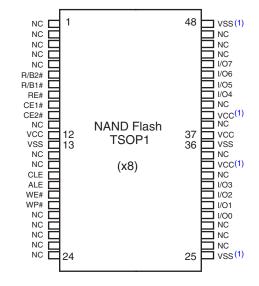

## 1. Connection Diagram

48 NC ¬ vss (1) NC NC NC ] NC NC NC NC NC R/B# RE# NC VCC (1) NC NC NAND Flash 12 13 vcc VCC TSOP1 VSS vss NC Ū vcc (1) NC (8x)CLE ALE WE# NC **i** 1/03 1/02 WP# 1/01 **i**/00 NC NC NC ☐ NC NC ] NC J ∨SS (1) NC 25

Figure 1.1 48-Pin TSOP1 Contact x8 Device (1 CE 8 Gb)

#### Note:

1. These pins should be connected to power supply or ground (as designated) following the ONFI specification, however they might not be bonded internally.

Figure 1.2 48-Pin TSOP1 Contact x8 Device (2 CE 8 Gb)

#### Note:

1. These pins should be connected to power supply or ground (as designated) following the ONFI specification, however they might not be bonded internally.

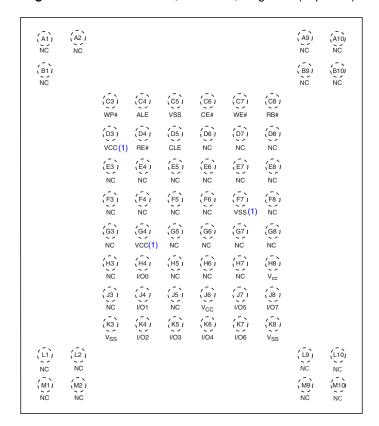

Figure 1.3 63-BGA Contact, x8 Device, Single CE (Top View)

#### Note:

These pins should be connected to power supply or ground (as designated) following the ONFI specification, however they might not be bonded internally.

## 2. Pin Description

Table 2.1 Pin Description

| Pin Name    | Description                                                                                                                                                                                                                                        |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1/00 - 1/07 | Inputs/Outputs. The I/O pins are used for command input, address input, data input, and data output. The I/O pins float to High-Z when the device is deselected or the outputs are disabled.                                                       |

| CLE         | <b>Command Latch Enable.</b> This input activates the latching of the I/O inputs inside the Command Register on the rising edge of Write Enable (WE#).                                                                                             |

| ALE         | Address Latch Enable. This input activates the latching of the I/O inputs inside the Address Register on the rising edge of Write Enable (WE#).                                                                                                    |

| CE#         | Chip Enable. This input controls the selection of the device. When the device is not busy CE# low selects the memory.                                                                                                                              |

| WE#         | Write Enable. This input latches Command, Address and Data. The I/O inputs are latched on the rising edge of WE#.                                                                                                                                  |

| RE#         | <b>Read Enable.</b> The RE# input is the serial data-out control, and when active drives the data onto the I/O bus. Data is valid t <sub>REA</sub> after the falling edge of RE# which also increments the internal column address counter by one. |

| WP#         | Write Protect. The WP# pin, when low, provides hardware protection against undesired data modification (program / erase).                                                                                                                          |

| R/B#        | Ready Busy. The Ready/Busy output is an Open Drain pin that signals the state of the memory.                                                                                                                                                       |

| VCC         | Supply Voltage. The $V_{CC}$ supplies the power for all the operations (Read, Program, Erase). An internal lock circuit prevents the insertion of Commands when $V_{CC}$ is less than $V_{LKO}$ .                                                  |

| VSS         | Ground.                                                                                                                                                                                                                                            |

| NC          | Not Connected.                                                                                                                                                                                                                                     |

#### Notes:

- 1. A 0.1  $\mu$ F capacitor should be connected between the  $V_{CC}$  Supply Voltage pin and the  $V_{SS}$  Ground pin to decouple the current surges from the power supply. The PCB track widths must be sufficient to carry the currents required during program and erase operations.

- An internal voltage detector disables all functions whenever V<sub>CC</sub> is below 1.8V to protect the device from any involuntary program/erase during power transitions.

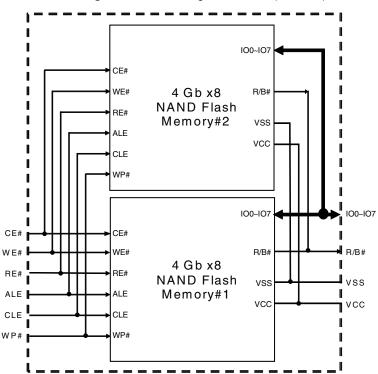

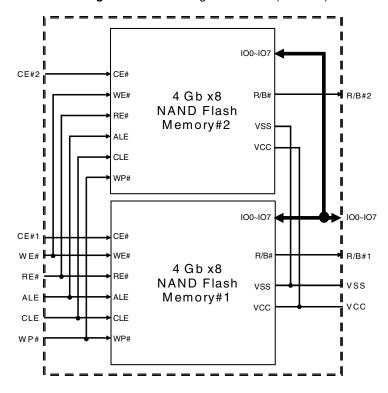

## 3. Block Diagrams

Address Register/ Counter Program Erase Controller HV Generation 4096 Mbit + 128 Mbit (4 Gb Device) DECOD NAND Flash ALE Memory Array CLE E R WE# Command Interface WP# Logic RE# Page Buffer Y Decoder Command Register I/O Buffer Data I/O0~I/O7

Figure 3.1 Functional Block Diagram — 4 Gb

Figure 3.2 Block Diagram — 1 CE (4 Gb x 8)

Figure 3.3 Block Diagram — 2 CE (4 Gb x 8)

## 4. Addressing

Table 4.1 Address Cycle Map

| Bus Cycle               | I/O0      | I/O1       | I/O2       | I/O3       | 1/04      | I/O5      | I/O6       | I/O7      |

|-------------------------|-----------|------------|------------|------------|-----------|-----------|------------|-----------|

| 1st / Col. Add. 1       | A0 (CA0)  | A1 (CA1)   | A2 (CA2)   | A3 (CA3)   | A4 (CA4)  | A5 (CA5)  | A6 (CA6)   | A7 (CA7)  |

| 2nd / Col. Add. 2       | A8 (CA8)  | A9 (CA9)   | A10 (CA10) | A11 (CA11) | Low       | Low       | Low        | Low       |

| 3rd / Row Add. 1        | A12 (PA0) | A13 (PA1)  | A14 (PA2)  | A15 (PA3)  | A16 (PA4) | A17 (PA5) | A18 (PLA0) | A19 (BA0) |

| 4th / Row Add. 2        | A20 (BA1) | A21 (BA2)  | A22 (BA3)  | A23 (BA4)  | A24 (BA5) | A25 (BA6) | A26 (BA7)  | A27 (BA8) |

| 5th / Row Add. 3<br>(6) | A28 (BA9) | A29 (BA10) | A30 (BA11) | Low        | Low       | Low       | Low        | Low       |

#### Notes:

- 1. CAx = Column Address bit.

- 2. PAx = Page Address bit.

- 3. PLA0 = Plane Address bit zero.

- 4. BAx = Block Address bit.

- 5. Block address concatenated with page address and plane address = actual page address, also known as the row address.

- 6. A30 for 8 Gb (4 Gb x 2 DDP) (1CE).

For the address bits, the following rules apply:

- A0 A11: column address in the page

- A12 A17: page address in the block

- A18: plane address (for multiplane operations) / block address (for normal operations)

- A19 A30: block address

#### 5. Read Status Enhanced

Read Status Enhanced is used to retrieve the status value for a previous operation in the following cases:

- In the case of concurrent operations on a multi-die stack.

- When two dies are stacked to form a dual-die package (DDP), it is possible to run one operation on the first die, then activate a different operation on the second die, for example: Erase while Read, Read while Program, etc.

- In the case of multiplane operations in the same die.

#### Extended Read Status

Multi-die stack devices support the Extended Read Status operation. When two operations are active in separate dies at the same time, this feature allows the host to check the status of a given die. For example, the first die could be executing a Page Program while the second die is performing a Page Read. Refer to Table 6.1 for a description of each command.

Table 6.1 Extended Read Status

| Command | Die    | Row Address with 4 Gb Dies |

|---------|--------|----------------------------|

| F2h     | First  | 0 to 3FFFFh                |

| F3h     | Second | 40000h to 7FFFFh           |

#### 7. Read ID

The device contains a product identification mode, initiated by writing 90h to the command register, followed by an address input of 00h.

**Note**: If you want to execute Read Status command (0x70) after Read ID sequence, you should input dummy command (0x00) before Read Status command (0x70).

For the S34ML04G1 device, five read cycles sequentially output the manufacturer code (01h), and the device code and 3rd, 4th, and 5th cycle ID, respectively. The command register remains in Read ID mode until further commands are issued to it.

Table 7.1 Read ID for Supported Configurations (1)

| Density                                      | Org | V <sub>cc</sub> | 1st | 2nd | 3rd | 4th | 5th |

|----------------------------------------------|-----|-----------------|-----|-----|-----|-----|-----|

| 4 Gb                                         | x8  | 3.3V            | 01h | DCh | 90h | 95h | 54h |

| 8 Gb<br>(4 Gb x 2 – DDP with<br>two CE#)     | x8  | 3.3V            | 01h | DCh | 90h | 95h | 54h |

| 8 Gb<br>(4 Gb x 2 – DDP with<br>one CE#) (1) | x8  | 3.3V            | 01h | D3h | D1h | 95h | 58h |

#### Note:

1. See See Appendix A — Errata on page 18. for information on READ ID in MCPs.

CLE CE# WE# tWHR tAR ALE tREA RE# 8 Gb Device (4 Gb x 2 - DDP with one CE#) 90h 00h 01h D3h D1h 95h 58h Device Code Read ID Address 1 Maker 3rd Cycle 4th Cycle 5th Cycle Code Command Cycle

Figure 7.1 Read ID Operation Timing — 8 Gb

#### 5<sup>th</sup> ID Data

Table 7.2 Read ID Byte 5 Description — S34ML04G1

|                      | Description | 1/07 | I/O6 I/O5 I/O4 | 1/03 1/02 | I/O1 | I/O0 |

|----------------------|-------------|------|----------------|-----------|------|------|

|                      | 1           |      |                | 0 0       |      |      |

| Dlane Number         | 2           |      |                | 0 1       |      |      |

| Plane Number         | 4           |      |                | 1 0       |      |      |

|                      | 8           |      |                | 11        |      |      |

|                      | 64 Mb       |      | 000            |           |      |      |

|                      | 128 Mb      |      | 0 0 1          |           |      |      |

|                      | 256 Mb      |      | 0 1 0          |           |      |      |

| Plane Size           | 512 Mb      |      | 0 1 1          |           |      |      |

| (without spare area) | 1 Gb        |      | 100            |           |      |      |

|                      | 2 Gb        |      | 101            |           |      |      |

|                      | 4 Gb        |      | 110            |           |      |      |

|                      | 8 Gb        |      | 111            |           |      |      |

| Reserved             |             | 0    |                |           | 0    | 0    |

## 7.1 Read Parameter Page

The device supports the ONFI Read Parameter Page operation, initiated by writing ECh to the command register, followed by an address input of 00h. The command register remains in Parameter Page mode until further commands are issued to it. Table 7.3 explains the parameter fields.

Table 7.3 Parameter Page Description (Sheet 1 of 3)

| Byte  | O/M | Description                                                                                                                                                                                                                                                              | Values                                                                                                 |

|-------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

|       |     | Revision Information and Features Block                                                                                                                                                                                                                                  | ·                                                                                                      |

| 0-3   | М   | Parameter page signature  Byte 0: 4Fh, "O"  Byte 1: 4Eh, "N"  Byte 2: 46h, "F"  Byte 3: 49h, "I"                                                                                                                                                                         | 4Fh, 4Eh, 46h, 49h                                                                                     |

| 4-5   | М   | Revision number  2-15 Reserved (0)  1 1 = supports ONFI version 1.0  0 Reserved (0)                                                                                                                                                                                      | 02h, 00h                                                                                               |

| 6-7   | М   | Features supported  5-15 Reserved (0)  4 1 = supports odd to even page Copyback  3 1 = supports interleaved operations  2 1 = supports non-sequential page programming  1 1 = supports multiple LUN operations  0 1 = supports 16-bit data bus width                     | 1Eh, 00h                                                                                               |

| 8-9   | М   | Optional commands supported  6-15 Reserved (0)  5 1 = supports Read Unique ID  4 1 = supports Copyback  3 1 = supports Read Status Enhanced  2 1 = supports Get Features and Set Features  1 1 = supports Read Cache commands  0 1 = supports Page Cache Program command | 1Bh, 00h                                                                                               |

| 10-31 |     | Reserved (0)                                                                                                                                                                                                                                                             | 00h                                                                                                    |

|       |     | Manufacturer Information Block                                                                                                                                                                                                                                           |                                                                                                        |

| 32-43 | М   | Device manufacturer (12 ASCII characters)                                                                                                                                                                                                                                | 53h, 50h, 41h, 4Eh, 53h, 49h,<br>4Fh, 4Eh, 20h, 20h, 20h, 20h                                          |

| 44-63 | М   | Device model (20 ASCII characters)                                                                                                                                                                                                                                       | 53h, 33h, 34h, 4Dh, 4Ch, 30h,<br>38h, 47h, 31h, 20h, 20h, 20h,<br>20h, 20h, 20h, 20h, 20h,<br>20h, 20h |

| 64    | М   | JEDEC manufacturer ID                                                                                                                                                                                                                                                    | 01h                                                                                                    |

Table 7.3 Parameter Page Description (Sheet 2 of 3)

| Byte    | O/M | Description                                                                                                                                                                                                                              | Values             |

|---------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| 65-66   | 0   | Date code                                                                                                                                                                                                                                | 00h                |

| 67-79   |     | Reserved (0)                                                                                                                                                                                                                             | 00h                |

|         |     | Memory Organization Block                                                                                                                                                                                                                | 1 ****             |

| 80-83   | М   | Number of data bytes per page                                                                                                                                                                                                            | 00h, 08h, 00h, 00h |

| 84-85   | M   | Number of spare bytes per page                                                                                                                                                                                                           | 40h, 00h           |

| 86-89   | M   | Number of data bytes per partial page                                                                                                                                                                                                    | 00h, 02h, 00h, 00h |

| 90-91   | М   | Number of spare bytes per partial page                                                                                                                                                                                                   | 10h, 00h           |

| 92-95   | М   | Number of pages per block                                                                                                                                                                                                                | 40h, 00h, 00h, 00h |

| 96-99   | М   | Number of blocks per logical unit (LUN)                                                                                                                                                                                                  | 00h, 10h, 00h, 00h |

| 100     | М   | Number of logical units (LUNs)                                                                                                                                                                                                           | 02h                |

| 101     | М   | Number of address cycles 4-7 Column address cycles 0-3 Row address cycles                                                                                                                                                                | 23h                |

| 102     | М   | Number of bits per cell                                                                                                                                                                                                                  | 01h                |

| 103-104 | М   | Bad blocks maximum per LUN                                                                                                                                                                                                               | 50h, 00h           |

| 105-106 | М   | Block endurance                                                                                                                                                                                                                          | 01h, 05h           |

| 107     | М   | Guaranteed valid blocks at beginning of target                                                                                                                                                                                           | 01h                |

| 108-109 | М   | Block endurance for guaranteed valid blocks                                                                                                                                                                                              | 01h, 03h           |

| 110     | М   | Number of programs per page                                                                                                                                                                                                              | 04h                |

| 111     | М   | Partial programming attributes  5-7 Reserved  4 1 = partial page layout is partial page data followed by partial page spare  1-3 Reserved  0 1 = partial page programming has constraints                                                | 00h                |

| 112     | М   | Number of bits ECC correctability                                                                                                                                                                                                        | 01h                |

| 113     | М   | Number of interleaved address bits  4-7 Reserved (0)  0-3 Number of interleaved address bits                                                                                                                                             | 01h                |

| 114     | 0   | Interleaved operation attributes  4-7 Reserved (0)  3 Address restrictions for program cache  2 1 = program cache supported  1 1 = no block address restrictions  0 Overlapped / concurrent interleaving support                         | 04h                |

| 115-127 |     | Reserved (0)                                                                                                                                                                                                                             | 00h                |

|         |     | Electrical Parameters Block                                                                                                                                                                                                              |                    |

| 128     | М   | I/O pin capacitance                                                                                                                                                                                                                      | 0Ah                |

| 129-130 | М   | Timing mode support  6-15 Reserved (0)  5 1 = supports timing mode 5  4 1 = supports timing mode 4  3 1 = supports timing mode 3  2 1 = supports timing mode 2  1 1 = supports timing mode 1  0 1 = supports timing mode 0, shall be 1   | 1Fh, 00h           |

| 131-132 | 0   | Program cache timing mode support  6-15 Reserved (0)  5 1 = supports timing mode 5  4 1 = supports timing mode 4  3 1 = supports timing mode 3  2 1 = supports timing mode 2  1 1 = supports timing mode 1  0 1 = supports timing mode 0 | 1Fh, 00h           |

| 133-134 | М   | t <sub>PROG</sub> Maximum page program time (μs)                                                                                                                                                                                         | BCh, 02h           |

| 135-136 | М   | t <sub>BERS</sub> Maximum block erase time (μs)                                                                                                                                                                                          | 10h, 27h           |

| 137-138 | М   | t <sub>R</sub> Maximum page read time (μs)                                                                                                                                                                                               | 19h, 00h           |

| 139-140 | М   | t <sub>CCS</sub> Minimum Change Column setup time (ns)                                                                                                                                                                                   | 64h, 00h           |

Table 7.3 Parameter Page Description (Sheet 3 of 3)

| Byte    | O/M          | Description                          | Values                      |  |  |  |  |  |

|---------|--------------|--------------------------------------|-----------------------------|--|--|--|--|--|

| 141-163 |              | Reserved (0)                         | 00h                         |  |  |  |  |  |

|         | Vendor Block |                                      |                             |  |  |  |  |  |

| 164-165 | М            | Vendor specific Revision number      | 00h                         |  |  |  |  |  |

| 166-253 |              | Vendor specific                      | 00h                         |  |  |  |  |  |

| 254-255 | М            | Integrity CRC                        | 7Bh, 09h                    |  |  |  |  |  |

|         |              | Redundant Parameter Pages            |                             |  |  |  |  |  |

| 256-511 | М            | Value of bytes 0-255                 | Repeat Value of bytes 0-255 |  |  |  |  |  |

| 512-767 | М            | Value of bytes 0-255                 | Repeat Value of bytes 0-255 |  |  |  |  |  |

| 768+    | 0            | Additional redundant parameter pages | FFh                         |  |  |  |  |  |

#### Note:

## 8. Electrical Characteristics

## 8.1 Valid Blocks

Table 8.1 Valid Blocks — 4 Gb

| Device    | Symbol          | Min      | Тур | Max  | Unit   |

|-----------|-----------------|----------|-----|------|--------|

| S34ML04G1 | N <sub>VB</sub> | 4016     | _   | 4096 | Blocks |

| S34ML08G1 | N <sub>VB</sub> | 8032 (1) | _   | 8192 | Blocks |

#### Note:

1. Each 4 Gb has maximum 80 bad blocks.

<sup>1.</sup> O" Stands for Optional, "M" for Mandatory.

#### 8.2 DC Characteristics

**Table 8.2** DC Characteristics and Operating Conditions (Values listed are for each 4 Gb NAND, 8 Gb (4 Gb x 2) will be additive accordingly)

| Parameter                                                  |                 | Symbol                | Test Conditions                                                          | Min                   | Тур | Max                   | Units |

|------------------------------------------------------------|-----------------|-----------------------|--------------------------------------------------------------------------|-----------------------|-----|-----------------------|-------|

| Power-On Current                                           |                 | I <sub>CC0</sub>      | Power up Current                                                         | _                     | 15  | 30                    | mA    |

|                                                            | Sequential Read | I <sub>CC1</sub>      | $t_{RC} = t_{RC} \text{ (min), CE\#} = V_{IL},$ $I_{OUT} = 0 \text{ mA}$ | _                     | 15  | 30                    | mA    |

| Operating Current                                          | Program         |                       | Normal                                                                   | _                     | 1   | 30                    | mA    |

|                                                            | Fiogram         | I <sub>CC2</sub>      | Cache                                                                    | _                     |     | 40                    | mA    |

|                                                            | Erase           | I <sub>CC3</sub>      | _                                                                        | _                     | 15  | 30                    | mA    |

| Standby current, (TTL)                                     |                 | I <sub>CC4</sub>      | CE# = V <sub>IH</sub> ,<br>WP# = 0V/Vcc                                  | _                     | _   | 1                     | mA    |

| Standby current, (CMOS)                                    |                 | I <sub>CC5</sub>      | $CE\# = V_{CC}-0.2,$ $WP\# = 0/V_{CC}$                                   | _                     | 10  | 50                    | μА    |

| Input Leakage Current                                      |                 | ILI                   | V <sub>IN</sub> = 0 to 3.6V                                              | _                     | _   | ±10                   | μΑ    |

| Output Leakage Current                                     |                 | I <sub>LO</sub>       | V <sub>OUT</sub> = 0 to 3.6V                                             | _                     | _   | ±10                   | μΑ    |

| Input High Voltage                                         |                 | V <sub>IH</sub>       | _                                                                        | V <sub>CC</sub> x 0.8 | _   | $V_{CC} + 0.3$        | V     |

| Input Low Voltage                                          |                 | V <sub>IL</sub>       | _                                                                        | -0.3                  |     | V <sub>CC</sub> x 0.2 | V     |

| Output High Voltage                                        |                 | V <sub>OH</sub>       | I <sub>OH</sub> = -400 μA                                                | 2.4                   | _   | _                     | V     |

| Output Low Voltage                                         |                 | V <sub>OL</sub>       | I <sub>OL</sub> = 2.1 mA                                                 | _                     | _   | 0.4                   | V     |

| Output Low Current (R/B#)                                  |                 | I <sub>OL(R/B#)</sub> | V <sub>OL</sub> = 0.4V                                                   | 8                     | 10  | _                     | mA    |

| V <sub>CC</sub> Supply Voltage<br>(erase and program locko | ut)             | V <sub>LKO</sub>      | _                                                                        | _                     | 1.8 | _                     | V     |

#### Notes:

- 1. All  $V_{CCO}$  and  $V_{CC}$  pins, and  $V_{SS}$  and  $V_{SSO}$  pins respectively are shorted together.

- 2. Values listed in this table refer to the complete voltage range for  $V_{CC}$  and  $V_{CCQ}$  and to a single device in case of device stacking.

- 3. All current measurements are performed with a 0.1 µF capacitor connected between the V<sub>CC</sub> Supply Voltage pin and the V<sub>SS</sub> Ground pin.

- 4. Standby current measurement can be performed after the device has completed the initialization process at power-up.

## 8.3 Pin Capacitance

Table 8.3 Pin Capacitance (TA = 25°C, f=1.0 MHz)

| Parameter      | Symbol          | Test Condition | Min | Max | Unit |

|----------------|-----------------|----------------|-----|-----|------|

| Input          | C <sub>IN</sub> | $V_{IN} = 0V$  | _   | 10  | pF   |

| Input / Output | C <sub>IO</sub> | $V_{IL} = 0V$  |     | 10  | pF   |

#### Note:

1. For the stacked devices version the Input is 10 pF x [number of stacked chips] and the Input/Output is 10 pF x [number of stacked chips].

## 8.4 Power Consumptions and Pin Capacitance for Allowed Stacking Configurations

When multiple dies are stacked in the same package, the power consumption of the stack will increase according to the number of chips. As an example, the standby current is the sum of the standby currents of all the chips, while the active power consumption depends on the number of chips concurrently executing different operations.

When multiple dies are stacked in the same package the pin/ball capacitance for the single input and the single input/output of the combo package must be calculated based on the number of chips sharing that input or that pin/ball.

## **Physical Interface**

#### **Physical Diagram** 9.1

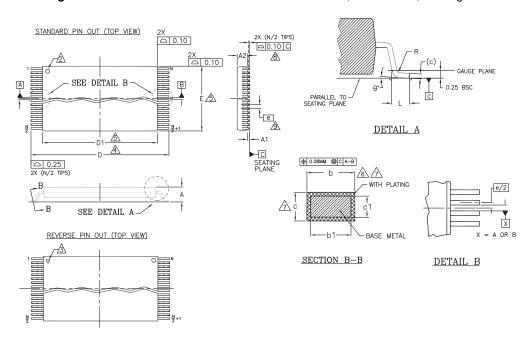

#### 48-Pin Thin Small Outline Package (TSOP1) 9.1.1

Figure 9.1 TS2 48 — 48-lead Plastic Thin Small Outline, 12 x 20 mm, Package Outline

| PACKAGE | TS2 48        |       |       |  |  |

|---------|---------------|-------|-------|--|--|

| JEDEC   | MO-142 (D) DD |       |       |  |  |

| SYMBOL  | MIN           | NOM   | MAX   |  |  |

| Α       |               |       | 1.20  |  |  |

| A1      | 0.05          |       | 0.15  |  |  |

| A2      | 0.95          | 1.00  | 1.05  |  |  |

| b1      | 0.17          | 0.20  | 0.23  |  |  |

| b       | 0.17          | 0.22  | 0.27  |  |  |

| c1      | 0.10          |       | 0.16  |  |  |

| С       | 0.10          |       | 0.21  |  |  |

| D       | 19.80         | 20.00 | 20.20 |  |  |

| D1      | 18.30         | 18.40 | 18.50 |  |  |

| E       | 11.90         | 12.00 | 12.10 |  |  |

| e       | 0.50 BASIC    |       |       |  |  |

| L       | 0.50          | 0.60  | 0.70  |  |  |

| θ       | 0°            |       | 8     |  |  |

| R       | 0.08          |       | 0.20  |  |  |

| N       | 48            |       |       |  |  |

DIMENSIONS ARE IN MILLIMETERS (mm). (DIMENSIONING AND TOLERANCING CONFORM TO ANSI Y14.5M-1994).

PIN 1 IDENTIFIER FOR STANDARD PIN OUT (DIE UP).

PIN 1 IDENTIFIER FOR REVERSE PIN OUT (DIE DOWN): INK OR LASER MARK.

TO BE DETERMINED AT THE SEATING PLANE \_-C\_\_. THE SEATING PLANE IS DEFINED AS THE PLANE OF CONTACT THAT IS MADE WHEN THE PACKAGE LEADS ARE ALLOWED TO REST FREELY ON A FLAT HORIZONTAL SURFACE.

DIMENSIONS D1 AND E DO NOT INCLUDE MOLD PROTRUSION. ALLOWABLE MOLD PROTRUSION ON E IS 0.15mm PER SIDE AND ON D1 IS 0.25mm PER SIDE.

6. DIMENSION 6 DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.08mm TOTAL IN EXCESS OF b DIMENSION AT MAX. MATERIAL CONDITION DAMBAR CANNOT BE LOCATED ON LOWER RADIUS OR THE FOOT. MINIMUM SPACE BETWEEN PROTRUSION AND AN ADJACENT LEAD TO BE 0.07mm.

7. THESE DIMENSIONS APPLY TO THE FLAT SECTION OF THE LEAD BETWEEN 0.10mm AND 0.25mm FROM THE LEAD TIP.

8. LEAD COPLANARITY SHALL BE WITHIN 0.10mm AS MEASURED FROM

9 DIMENSION "e" IS MEASURED AT THE CENTERLINE OF THE LEADS.

5007 \ f16-038 \ 6.5.13

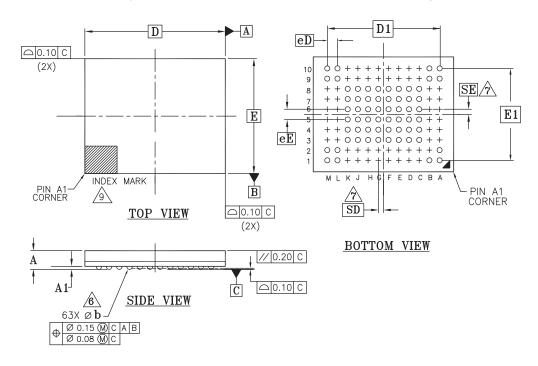

### 9.1.2 63-Pin Ball Grid Array (BGA)

Figure 9.2 VLD063 — 63-Pin BGA, 11 mm x 9 mm Package

| PACKAGE | VLD 063                                                                                                                                        |            |      |                          |  |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------|------------|------|--------------------------|--|

| JEDEC   | M0-207(M)                                                                                                                                      |            |      |                          |  |

|         | 11.00 mm x 9.00 mm<br>PACKAGE                                                                                                                  |            | mm   |                          |  |

| SYMBOL  | MIN                                                                                                                                            | NOM        | MAX  | NOTE                     |  |

| Α       |                                                                                                                                                |            | 1.00 | PROFILE                  |  |

| A1      | 0.25                                                                                                                                           |            |      | BALL HEIGHT              |  |

| D       |                                                                                                                                                | 11.00 BSC. |      | BODY SIZE                |  |

| Е       |                                                                                                                                                | 9.00 BSC.  |      | BODY SIZE                |  |

| D1      |                                                                                                                                                | 8.80 BSC.  |      | MATRIX FOOTPRINT         |  |

| E1      |                                                                                                                                                | 7.20 BSC.  |      | MATRIX FOOTPRINT         |  |

| MD      | 12                                                                                                                                             |            |      | MATRIX SIZE D DIRECTION  |  |

| ME      | 10                                                                                                                                             |            |      | MATRIX SIZE E DIRECTION  |  |

| n       | 63                                                                                                                                             |            |      | BALL COUNT               |  |

| Øb      | 0.40                                                                                                                                           | 0.45       | 0.50 | BALL DIAMETER            |  |

| eЕ      | 0.80 BSC.                                                                                                                                      |            |      | BALL PITCH               |  |

| eD      | 0:80 BSC.                                                                                                                                      |            |      | BALL PITCH               |  |

| SD      | 0.40 BSC.                                                                                                                                      |            |      | SOLDER BALL PLACEMENT    |  |

| SE      | 0.40 BSC.                                                                                                                                      |            |      | SOLDER BALL PLACEMENT    |  |

|         | A3-A8,B2-B8,C1,C2,C9,C10<br>D1,D2,D9,D10,E1,E2,E9,E10<br>F1,F2,F9,F10,G1,G2,G9,G10<br>H1,H2,H9,H10,J1,J2,J9,J10<br>K1,K2,K9,K10<br>L3-L8,M3-M8 |            |      | DEPOPULATED SOLDER BALLS |  |

#### NOTES:

- DIMENSIONING AND TOLERANCING METHODS PER ASME Y14.5M-1994.

- 2. ALL DIMENSIONS ARE IN MILLIMETERS.

- 3. BALL POSITION DESIGNATION PER JEP95, SECTION 3, SPP-020.

- 4. e REPRESENTS THE SOLDER BALL GRID PITCH.

- 5. SYMBOL "MD" IS THE BALL MATRIX SIZE IN THE "D" DIRECTION.

SYMBOL "ME" IS THE BALL MATRIX SIZE IN THE

"E" DIRECTION.

$\ensuremath{\mathsf{n}}$  IS THE TOTAL NUMBER OF POPULATED SOLDER BALL POSITIONS FOR MATRIX SIZE MD X ME.

6 DIMENSION "b" IS MEASURED AT THE MAXIMUM BALL DIAMETER IN A PLANE PARALLEL TO DATUM C.

DIAME IER IN A PLANE PARALLEL TO DATUM C.

SO' AND "SE" ARE MEASURED WITH RESPECT TO DATUMS A AND B AND DEFINE THE POSITION OF THE CENTER SOLDER BALL IN THE OUTER ROW.

WHEN THERE IS AN ODD NUMBER OF SOLDER BALLS IN THE OUTER ROW "SD" OR "SE" = 0.

WHEN THERE IS AN EVEN NUMBER OF SOLDER BALLS IN THE OUTER ROW, "SD" = eD/2 AND "SE" = eE/2.

8. "+" INDICATES THE THEORETICAL CENTER OF DEPOPULATED BALLS.

A1 CORNER TO BE IDENTIFIED BY CHAMFER, LASER OR INK MARK, METALLIZED MARK INDENTATION OR OTHER MEANS.

g5013 \ 16-038.28 \ 6.5.13

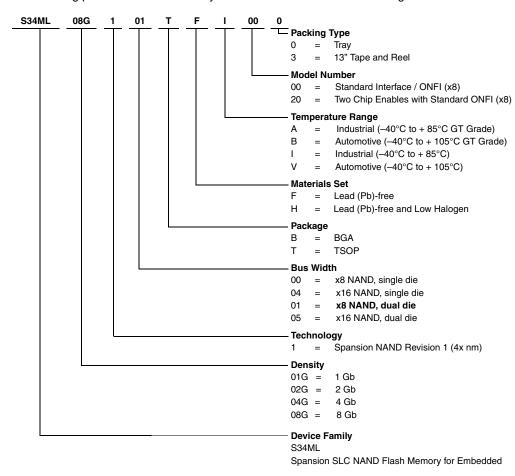

## 10. Ordering Information

The ordering part number is formed by a valid combination of the following:

#### **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult your local sales office to confirm availability of specific valid combinations and to check on newly released combinations.

| Valid Combinations |         |            |              |                 |                      |                                |                 |                        |

|--------------------|---------|------------|--------------|-----------------|----------------------|--------------------------------|-----------------|------------------------|

| Device<br>Family   | Density | Technology | Bus<br>Width | Package<br>Type | Temperature<br>Range | Additional<br>Ordering Options | Packing<br>Type | Package<br>Description |

| S34ML              | 08G     | 1          | 01           | TF              | A, B, I, V           | 00, 20                         | 0.3             | TSOP                   |

| 334IVIL            | 060     | ı          | 01           | ВН              | А, Б, І, V           | 00                             | 0, 3            | BGA (1)                |

#### Note:

1. BGA package marking omits the leading "S34" and the Packing Type designator from the ordering part number.

## 11. Appendix A — Errata

For Spansion NAND MCPs (Multi-Chip Package) like the 8 Gb (2 x 4 Gb), due to the internal bonding, READ ID automatically changes to the hard-wired values and currently there is no way to change it electrically. Therefore, the Spansion NAND 8 Gb with one CE# will not follow the same methodology of READ ID as SDPs (Single Die Package). The READ ID values for the 8-Gb Spansion NAND with one CE# will be as follows:

1st Byte: 01h 2nd Byte: D3h 3rd Byte: D1h 4th Byte: 95h 5th Byte: 58h

|                                             | 1st Byte | 2nd Byte | 3rd Byte | 4th Byte | 5th Byte |

|---------------------------------------------|----------|----------|----------|----------|----------|

| 8 Gb with one CE#<br>(Currently with error) | 01h      | D3h      | D1h      | 95h      | 58h      |

| 8 Gb with one CE#<br>(Spansion methodology) | 01h      | DCh      | 91h      | 95h      | 54h      |

Currently, Spansion does not plan to fix the problem. If there are any issues related to this, please contact Spansion NAND Product Marketing for further questions.

## 12. Revision History

| Section                         | Description                                                                                                          |  |  |  |  |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Revision 01 (August 23, 2012)   |                                                                                                                      |  |  |  |  |

|                                 | Initial release                                                                                                      |  |  |  |  |

| Revision 02 (October 1, 2012)   |                                                                                                                      |  |  |  |  |

| Addressing                      | Address Cycle Map table: corrected data                                                                              |  |  |  |  |

| Read ID                         | Read ID for Supported Configurations table: added row – 8 Gb (4 Gb x 2 – DDP with two CE#)                           |  |  |  |  |

|                                 | Parameter Page Description table:                                                                                    |  |  |  |  |

| Read Parameter Page             | corrected Electrical Parameters Block values for bytes 129-130 and bytes 131-132                                     |  |  |  |  |

|                                 | corrected Vendor Block values for bytes 254-255                                                                      |  |  |  |  |

| Appendix A                      | Added text                                                                                                           |  |  |  |  |

| Revision 03 (November 29, 2012) |                                                                                                                      |  |  |  |  |

| Ordering Information            | Added Model Number                                                                                                   |  |  |  |  |

| Revision 04 (December 19, 2012) |                                                                                                                      |  |  |  |  |

| Read Parameter Page             | Parameter Page Description table:                                                                                    |  |  |  |  |

| ricad i arameter i age          | corrected Description for Bytes 129-130 and bytes 131-132                                                            |  |  |  |  |

|                                 | DC Characteristics and Operating Conditions table:                                                                   |  |  |  |  |

| DC Characteristics              | corrected Test Conditions for I <sub>CC1</sub>                                                                       |  |  |  |  |

| DO CHARACTERISTICS              | Output High Voltage: removed $I_{OH} = 100 \mu A$ row<br>Output Low Voltage: removed $I_{OI} = 100 \mu A$ row        |  |  |  |  |

|                                 | Output Low Current (R/B#): removed V <sub>OL</sub> = 0.1V row                                                        |  |  |  |  |

| Ordering Information            | Valid Combinations table: removed Bus Width 05                                                                       |  |  |  |  |

| Revision 05 (August 9, 2013)    |                                                                                                                      |  |  |  |  |

| Distinctive Characteristics     | Security: Removed Serial number (unique ID)                                                                          |  |  |  |  |

| Distinctive Orial acteristics   | Operating Temperature: removed Commercial and Extended temperatures                                                  |  |  |  |  |

| Performance                     | Updated Reliability                                                                                                  |  |  |  |  |

| Connection Diagram              | Added figure: 48-Pin TSOP1 Contact x8 Device (1 CE 8 Gb)                                                             |  |  |  |  |

| Addressing                      | Address Cycle Map table: appended Note                                                                               |  |  |  |  |

| Addressing                      | Added text to Bus Cycle column                                                                                       |  |  |  |  |

| Extended Read Status            | Extended Read Status table: removed Commands F4h and F5h                                                             |  |  |  |  |

| Read Parameter Page             | Parameter Page Description table: corrected Byte 44-63, 100, and 254-255 Values                                      |  |  |  |  |

| Valid Blocks                    | Valid Blocks table: clarified Device values                                                                          |  |  |  |  |

| DC Characteristics              | DC Characteristics and Operating Conditions table: added row, 'V <sub>CC</sub> Supply Voltage'                       |  |  |  |  |

| Physical Interface              | Updated figures:                                                                                                     |  |  |  |  |

|                                 | TS2 48 — 48-lead Plastic Thin Small Outline, 12 x 20 mm, Package Outline                                             |  |  |  |  |

|                                 | VLD063 — 63-Pin BGA, 11 mm x 9 mm Package                                                                            |  |  |  |  |

| Ordering Information            | Updated Materials Set: H = Low Halogen to H = Lead (Pb)-free and Low Halogen                                         |  |  |  |  |

| Devision 00 (April 4, 0044)     | Valid Combinations table: removed 04G; Added Note                                                                    |  |  |  |  |

| Revision 06 (April 1, 2014)     |                                                                                                                      |  |  |  |  |

| Ordering Information            | Updated Temperature Range to include A (-40°C to 85°C GT Grade), B (-40°C to 105°C GT Grade), and V (-40°C to 105°C) |  |  |  |  |

|                                 | Valid Combinations table: added A, B, V to Temperature Range                                                         |  |  |  |  |

#### Colophon

The products described in this document are designed, developed and manufactured as contemplated for general use, including without limitation, ordinary industrial use, general office use, personal use, and household use, but are not designed, developed and manufactured as contemplated (1) for any use that includes fatal risks or dangers that, unless extremely high safety is secured, could have a serious effect to the public, and could lead directly to death, personal injury, severe physical damage or other loss (i.e., nuclear reaction control in nuclear facility, aircraft flight control, air traffic control, mass transport control, medical life support system, missile launch control in weapon system), or (2) for any use where chance of failure is intolerable (i.e., submersible repeater and artificial satellite). Please note that Spansion will not be liable to you and/or any third party for any claims or damages arising in connection with above-mentioned uses of the products. Any semiconductor devices have an inherent chance of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of over-current levels and other abnormal operating conditions. If any products described in this document represent goods or technologies subject to certain restrictions on export under the Foreign Exchange and Foreign Trade Law of Japan, the US Export Administration Regulations or the applicable laws of any other country, the prior authorization by the respective government entity will be required for export of those products.

#### Trademarks and Notice

The contents of this document are subject to change without notice. This document may contain information on a Spansion product under development by Spansion. Spansion reserves the right to change or discontinue work on any product without notice. The information in this document is provided as is without warranty or guarantee of any kind as to its accuracy, completeness, operability, fitness for particular purpose, merchantability, non-infringement of third-party rights, or any other warranty, express, implied, or statutory. Spansion assumes no liability for any damages of any kind arising out of the use of the information in this document.

Copyright © 2012-2014 Spansion Inc. All rights reserved. Spansion®, the Spansion logo, MirrorBit®, MirrorBit® Eclipse™, ORNAND™ and combinations thereof, are trademarks and registered trademarks of Spansion LLC in the United States and other countries. Other names used are for informational purposes only and may be trademarks of their respective owners.

OOO «ЛайфЭлектроникс" "LifeElectronics" LLC

ИНН 7805602321 КПП 780501001 P/C 40702810122510004610 ФАКБ "АБСОЛЮТ БАНК" (ЗАО) в г.Санкт-Петербурге К/С 3010181090000000703 БИК 044030703

Компания «Life Electronics» занимается поставками электронных компонентов импортного и отечественного производства от производителей и со складов крупных дистрибьюторов Европы, Америки и Азии.

С конца 2013 года компания активно расширяет линейку поставок компонентов по направлению коаксиальный кабель, кварцевые генераторы и конденсаторы (керамические, пленочные, электролитические), за счёт заключения дистрибьюторских договоров

#### Мы предлагаем:

- Конкурентоспособные цены и скидки постоянным клиентам.

- Специальные условия для постоянных клиентов.

- Подбор аналогов.

- Поставку компонентов в любых объемах, удовлетворяющих вашим потребностям.

- Приемлемые сроки поставки, возможна ускоренная поставка.

- Доставку товара в любую точку России и стран СНГ.

- Комплексную поставку.

- Работу по проектам и поставку образцов.

- Формирование склада под заказчика.

- Сертификаты соответствия на поставляемую продукцию (по желанию клиента).

- Тестирование поставляемой продукции.

- Поставку компонентов, требующих военную и космическую приемку.

- Входной контроль качества.

- Наличие сертификата ISO.

В составе нашей компании организован Конструкторский отдел, призванный помогать разработчикам, и инженерам.

Конструкторский отдел помогает осуществить:

- Регистрацию проекта у производителя компонентов.

- Техническую поддержку проекта.

- Защиту от снятия компонента с производства.

- Оценку стоимости проекта по компонентам.

- Изготовление тестовой платы монтаж и пусконаладочные работы.

Тел: +7 (812) 336 43 04 (многоканальный) Email: org@lifeelectronics.ru