# Serial RapidIO Gen2 Endpoint v4.1

# LogiCORE IP Product Guide

**Vivado Design Suite**

PG007 June 7, 2017

# **Table of Contents**

#### **IP Facts**

| Chapter 1: Overview                        |

|--------------------------------------------|

| System Overview                            |

| Applications                               |

| Unsupported Features                       |

| Licensing                                  |

| Recommended Design Experience              |

| Chapter 2: Product Specification           |

| Standards Compliance                       |

| Performance                                |

| Resource Utilization                       |

| Serial Transceiver Support                 |

| Top-Level Wrapper 11                       |

| Port Descriptions                          |

| Register Space 51                          |

| Chapter 3: Designing with the Core         |

| General Design Guidelines 73               |

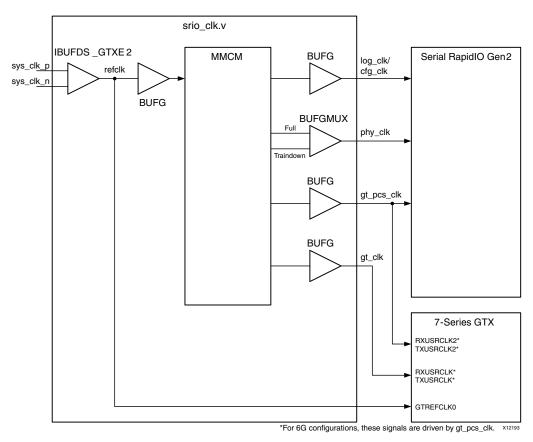

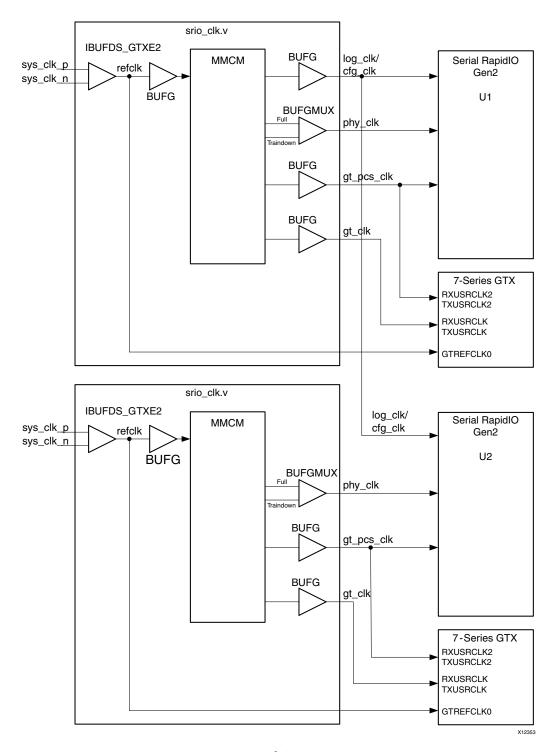

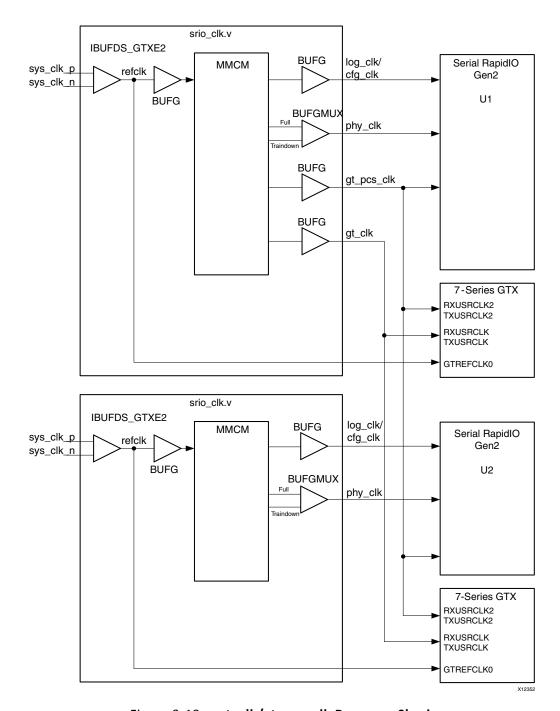

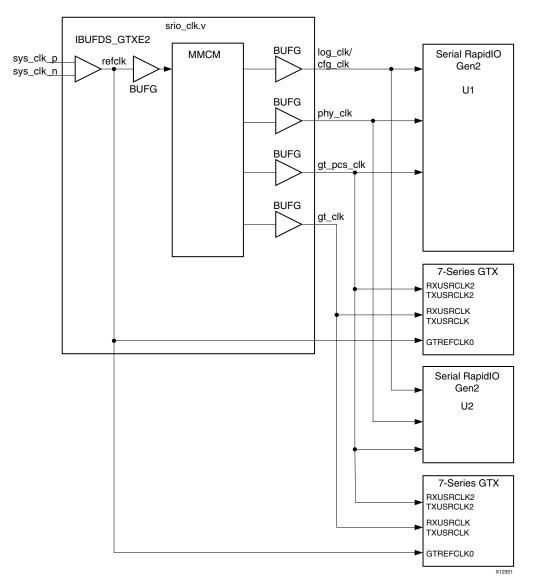

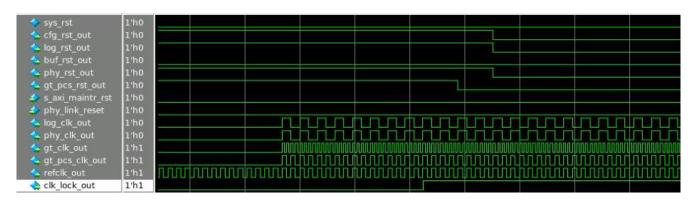

| Clocking91                                 |

| Resets                                     |

| Shared Logic Related Port Descriptions 100 |

| Protocol Description                       |

| Chapter 4: Design Flow Steps               |

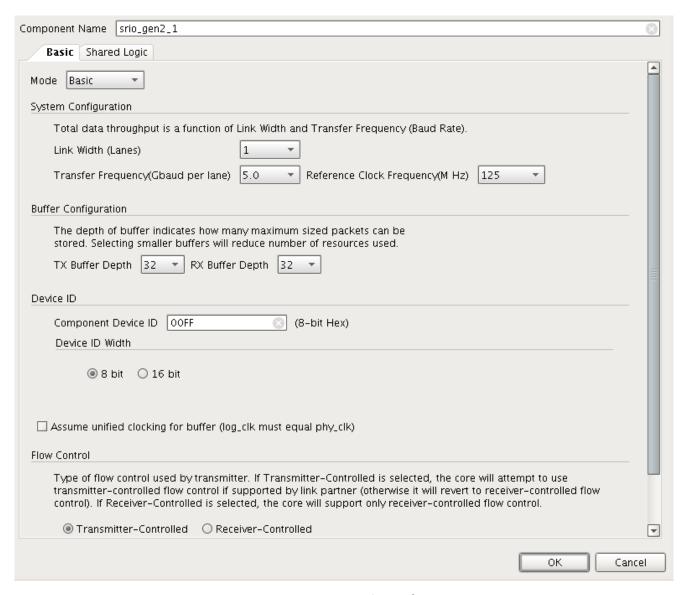

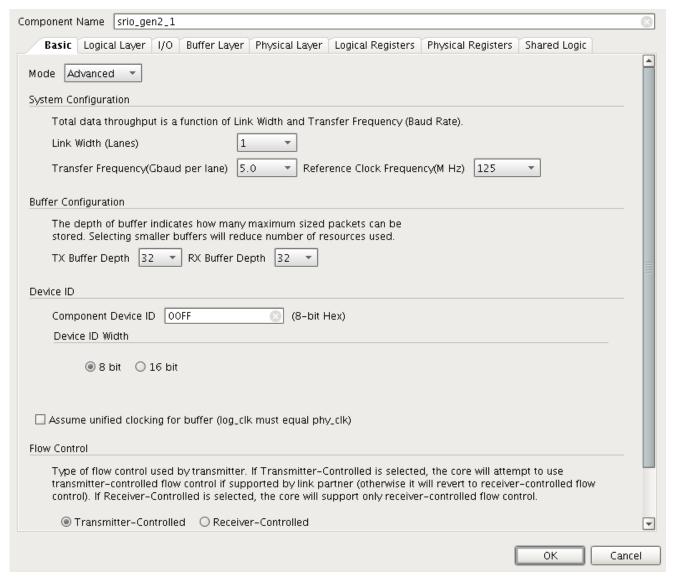

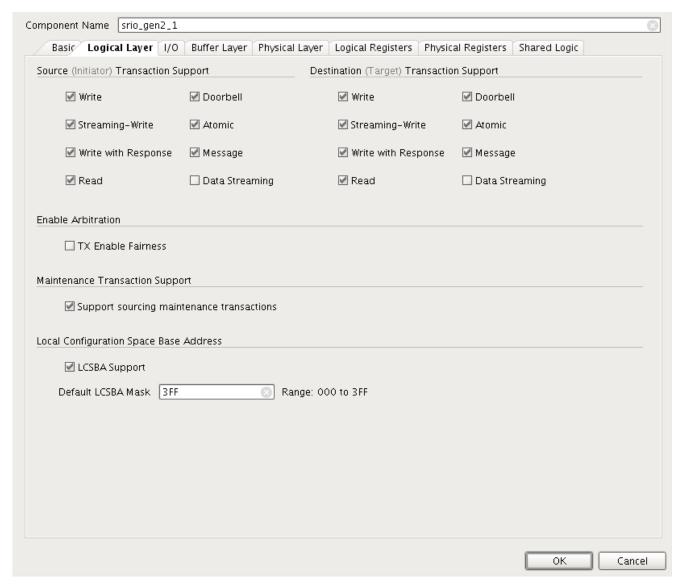

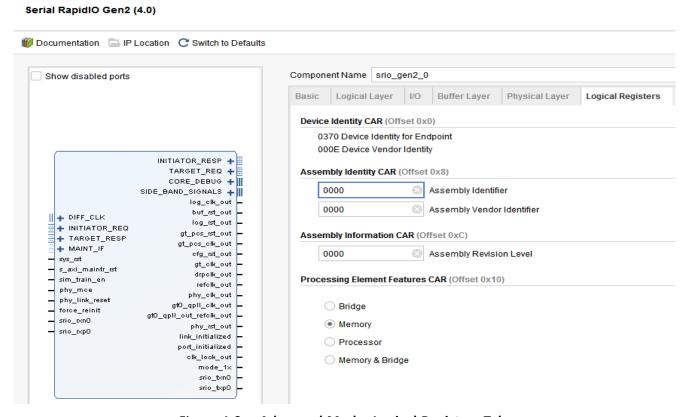

| Customizing and Generating the Core 129    |

| Constraining the Core                      |

| Simulation                                 |

| Synthesis and Implementation               |

| Chapter 5: Detailed Example Design         |

| Overview                                   |

| Generating the Core                                | 153 |

|----------------------------------------------------|-----|

| Directory and File Contents                        | 154 |

| Example Design                                     | 157 |

| Implementing the Example Design                    | 162 |

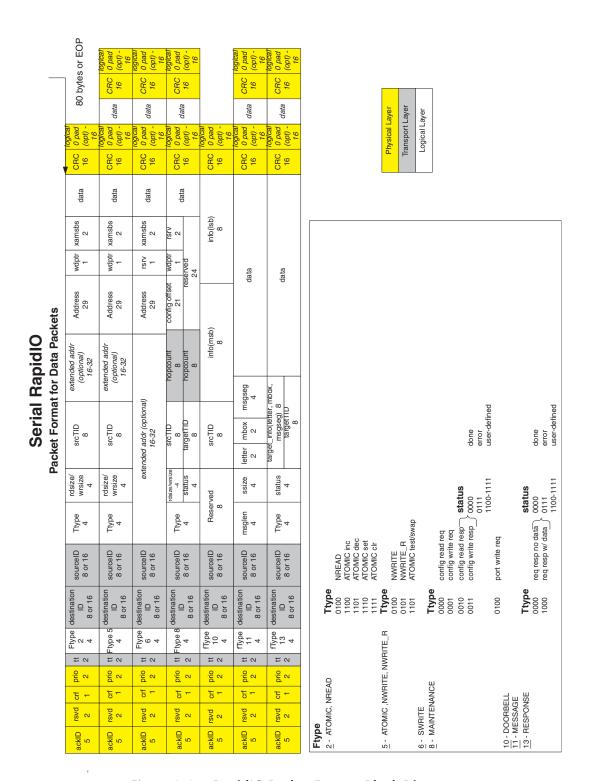

| Simulating the Example Design                      | 162 |

| Chapter 6: Test Bench                              |     |

| Demonstration Test Bench                           | 165 |

| Appendix A: Packet and Control Symbol Formats      |     |

| Scope                                              | 167 |

| Appendix B: Migrating and Upgrading                |     |

| Migrating to the Vivado Design Suite               | 170 |

| Upgrading in the Vivado Design Suite               | 170 |

| Appendix C: Debugging                              |     |

| Finding Help on Xilinx.com                         | 178 |

| Debug Tools                                        |     |

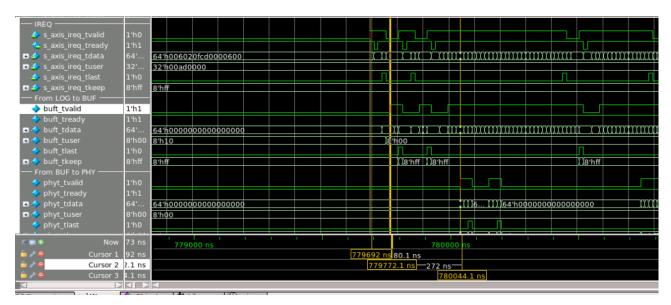

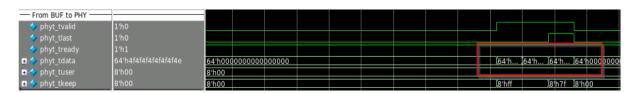

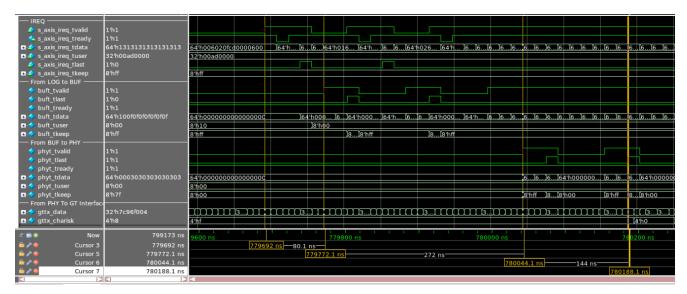

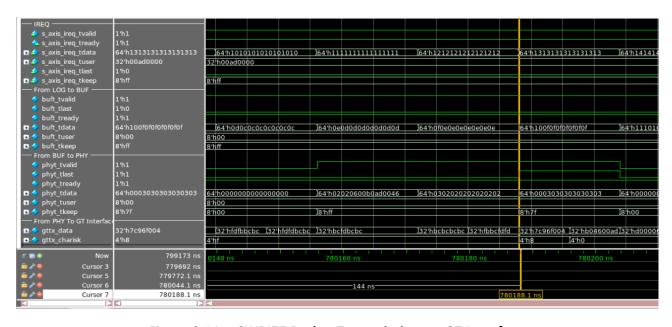

| Waveform Analysis and Debug                        |     |

| Hardware Debug 1                                   | 189 |

| Appendix D: Additional Resources and Legal Notices |     |

| Xilinx Resources                                   | 195 |

| References                                         | 195 |

| Revision History                                   | 196 |

| Please Read: Important Legal Notices 1             | 197 |

### Introduction

The LogiCORE™ IP Serial RapidIO Gen2

Endpoint Solution (SRIO Gen2 Endpoint)

comprises a highly flexible and optimized Serial

RapidIO Gen2 Physical Layer and a Serial

RapidIO Gen2 Logical (I/O) and Transport Layer.

This IP solution is provided in netlist form with

supporting example design code. The SRIO

Gen2 Endpoint supports 1x, 2x, and 4x lane

widths. It comes with a configurable buffer

design, reference clock module, reset module,

and configuration fabric reference design. The

SRIO Gen2 Endpoint uses AXI4-Stream

interfaces for high-throughput data transfer

and AXI4-Lite interfaces for the configuration

(maintenance) interfaces.

### **Features**

- Designed to RapidIO Interconnect Specification rev. 2.2

- Supports 1x, 2x and 4x operation with the ability to train down to 1x from 2x or 4x

- Supports per-lane speeds of 1.25, 2.5, 3.125, 5.0, and 6.25 Gbaud

### **Logical Layer**

- Concurrent Initiator and Target operations

- Doorbell and Message support

- Dedicated port for maintenance transactions

- Simple handshaking mechanism to control data flow using standard AXI4-Lite and AXI4-Stream interfaces

- Programmable source ID on all outgoing packets

- Optional large system support for 16-bit device IDs

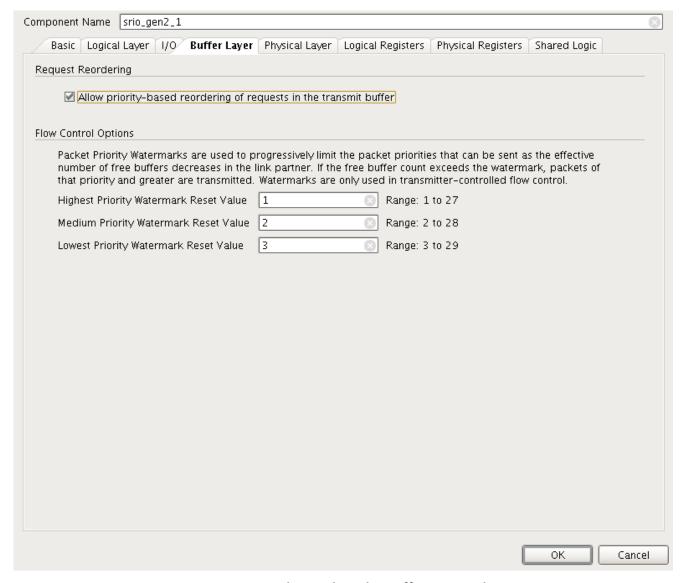

#### **Buffer**

- Independently configurable TX and RX Buffer depths of 8, 16, or 32 packets

- Support for independent clocks

- Optional TX Flow Control support

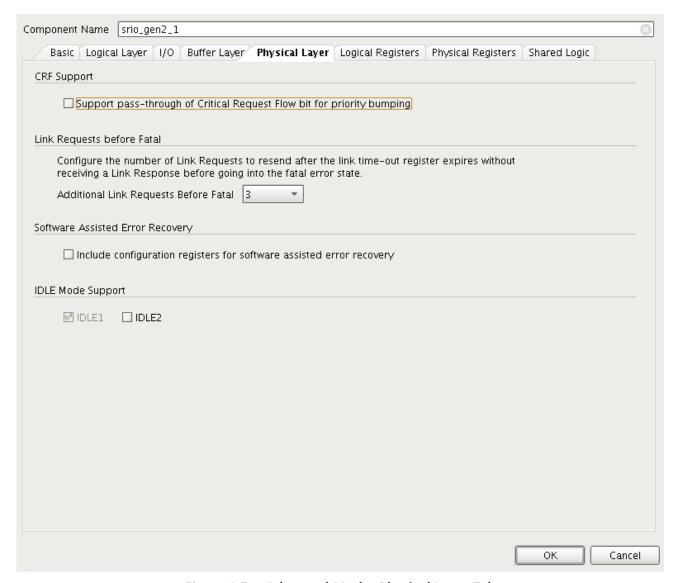

### **Physical Layer**

- Configurable IDLE1/IDLE2 sequence support

- Supports critical request flow

- · Support for multicast events

| LogiCORE IP Facts Table                           |                                                                                                   |  |

|---------------------------------------------------|---------------------------------------------------------------------------------------------------|--|

|                                                   | Core Specifics                                                                                    |  |

| Supported Device Family (1)                       | UltraScale+™ Families,<br>UltraScale™ Architecture, Zynq®-7000,<br>Virtex®-7, Kintex®-7, Artix®-7 |  |

| Supported User<br>Interfaces                      | AXI4-Stream, AXI4-Lite                                                                            |  |

| Resources                                         | Performance and Resource Utilization web page                                                     |  |

| Provided with Core                                |                                                                                                   |  |

| Design Files                                      | Encrypted RTL                                                                                     |  |

| Example Design                                    | Configuration Fabric Design with Verilog Source                                                   |  |

| Test Bench                                        | Verilog                                                                                           |  |

| Constraints File                                  | XDC                                                                                               |  |

| Simulation Model                                  | Encrypted Verilog                                                                                 |  |

| Supported S/W<br>Driver                           | N/A                                                                                               |  |

| Tested Design Flows <sup>(2)</sup>                |                                                                                                   |  |

| Design Entry                                      | Vivado® Design Suite                                                                              |  |

| Simulation (3)                                    | For the supported simulators, see the Xilinx<br>Design Tools: Release Notes Guide                 |  |

| Synthesis                                         | Vivado synthesis                                                                                  |  |

| Support                                           |                                                                                                   |  |

| Provided by Xilinx at the Xilinx Support web page |                                                                                                   |  |

- For a complete list of supported devices, see the Vivado IP catalog.

- 2. For the supported versions of the tools, see the Xilinx Design Tools: Release Notes Guide.

- 3. Requires a Verilog LRM-IEEE 1364-2005 encryption-compliant simulator.

# Overview

The RapidIO Interconnect Architecture, designed to be compatible with the most popular integrated communications processors, host processors, and networking digital signal processors, is a high-performance, packet-switched, interconnect technology. It addresses the need of the high-performance embedded industry for reliability, increased bandwidth, and faster bus speeds in an intra-system interconnect.

The RapidIO standard is defined in three layers: *logical*, *transport* and *physical*. The logical layer defines the overall protocol and packet formats. This is the information necessary for endpoints to initiate and complete a transaction. The transport layer provides the route information necessary for a packet to move from endpoint to endpoint. The physical layer describes the device-level interface specifics such as packet transport mechanisms, flow control, electrical characteristics, and low-level error management. This partitioning provides the flexibility to add new transaction types to the logical specification without requiring modification to the transport or physical layer specifications.

- For more information about the RapidIO core, see www.xilinx.com/rapidio

- For more information about the RapidIO standards and specifications, see www.rapidio.org

## **System Overview**

The SRIO Gen2 Endpoint is comprised of the following:

- A Serial RapidIO Gen2 top-level wrapper (srio\_gen2\_<core\_version>\_unifiedtop) containing:

- Serial RapidIO Gen2 Physical Layer (PHY)

- Serial RapidIO Gen2 Logical (I/O) and Transport Layer (LOG)

- Serial RapidIO Gen2 Buffer Design (BUF)

- Reference design for clocking, resets, and configuration accesses

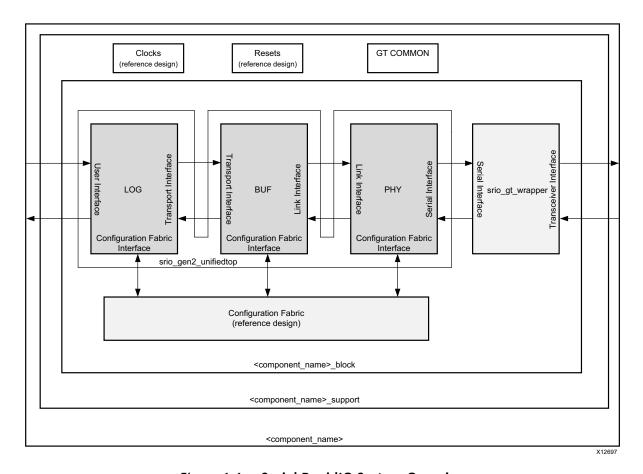

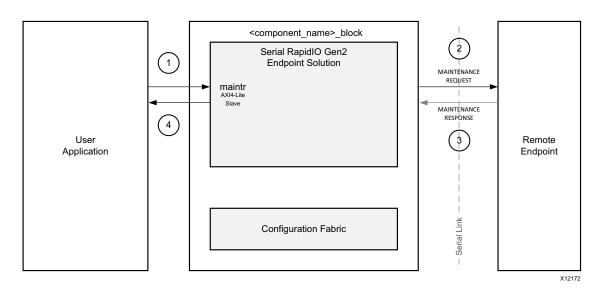

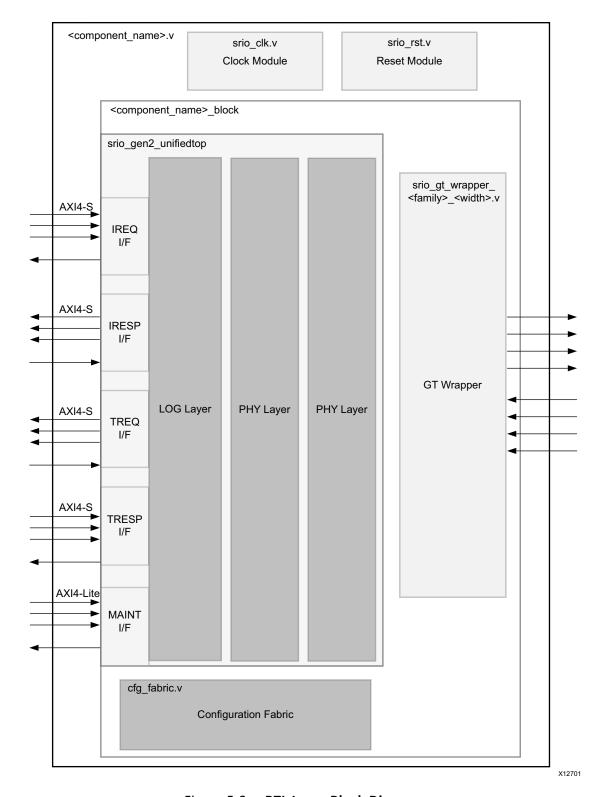

The SRIO Gen2 Endpoint is shown in Figure 1-1.

Figure 1-1: Serial RapidIO System Overview

The SRIO Gen2 Endpoint is delivered through a layered approach.

- The srio\_gen2\_<core\_version>\_unifiedtop wrapper contains the LOG, BUF, and PHY. The

wrapper presents all the ports from these sub-cores, but ties off any unused ports. This

allows you to use the same wrapper for various configurations of the core, such as the

full core or just the PHY.

- The <component\_name>\_block integrates the srio\_gen2\_<core\_version>\_unifiedtop wrapper, the srio\_gt\_wrapper, and configuration fabric reference design. The srio\_gen2\_<core\_version>\_unifiedtop wrapper provides all the ports of the LOG, BUF, and PHY, and the <component\_name>\_block connects them.

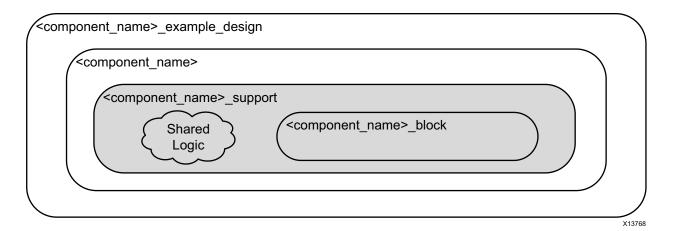

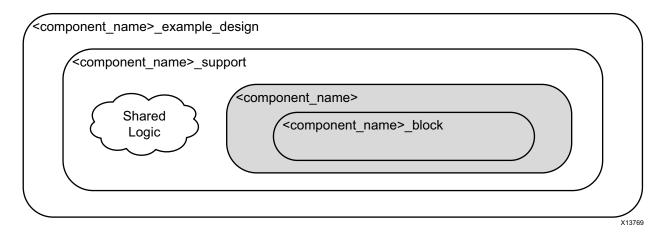

- The <component\_name>\_support wrapper contains the clock and reset modules. For 7 series devices, the wrapper contains the GT COMMON modules.

- <component\_name> is the top-level wrapper. This wrapper is used to integrate an

entire SRIO Gen2 Endpoint into your design. There is also an option available to

generate <component\_name> without <component\_name>\_support through the

Vivado® Integrated Design Environment (IDE). For more information about this option,

see Chapter 4, Customizing and Generating the Core.

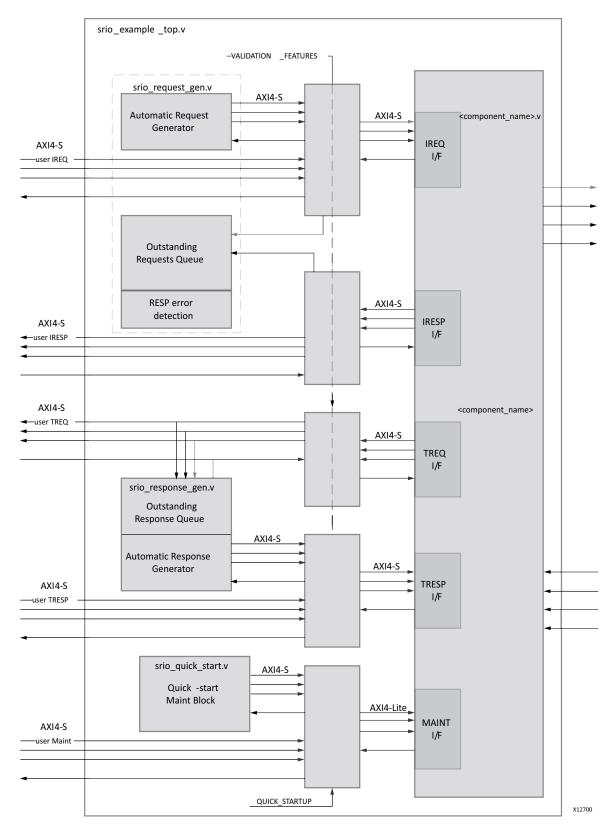

Although not shown in Figure 1-1, the srio\_example\_top wrapper includes all the components described previously in addition to an example design. This is used for testing and demonstration purposes, both in simulation and hardware.

# **Applications**

The SRIO Gen2 Endpoint is well suited for control and data operations in communication and embedded systems requiring high-speed I/O with low latency. Typical applications include:

- Wireless Base Stations as interconnect on Channel Cards or Radio Equipment controller

- DSP farms for image and signal processing which is ideal for multi-processor communication interconnect

- Scientific, military, and industrial equipment

- High-availability enterprise storage as reliable, low latency, and high bandwidth memory interface

- Edge Networking for multimedia data compression

## **Unsupported Features**

The following feature is not supported:

• Train down to lane-R (redundant lane). The redundant lane is lane 1 in a x2 configuration, and is lane 2 in a x4 configuration.

# Licensing

### **License Checkers**

If the IP requires a license key, the key must be verified. The Vivado® design tools have several license checkpoints for gating licensed IP through the flow. If the license check succeeds, the IP can continue generation. Otherwise, generation halts with error. License checkpoints are enforced by the following Vivado design tools:

- Vivado synthesis

- Vivado implementation

- write\_bitstream (Tcl command)

**IMPORTANT:** IP license level is ignored at checkpoints. The test confirms a valid license exists. It does not check IP license level.

### **License Type**

This Xilinx LogiCORE™ IP module is provided under the terms of the Xilinx Core License Agreement. The module is shipped as part of the Vivado Design Suite. For full access to all core features in simulation and in hardware, you must purchase a license for the core. Contact your local Xilinx sales representative for information about pricing and availability.

For more information, please visit the Serial RapidIO Gen2 product page.

Information about other Xilinx LogiCORE IP modules is available at the Xilinx Intellectual Property page. For information on pricing and availability of other Xilinx LogiCORE IP modules and tools, contact your local Xilinx sales representative.

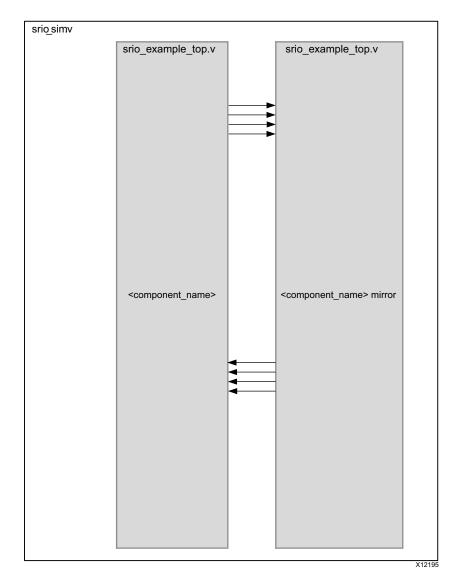

# **Recommended Design Experience**

Although the SRIO Gen2 Endpoint is fully verified, the challenge associated with implementing a complete design varies depending on the configuration and functionality of the application.

**RECOMMENDED:** For best results, previous experience building high performance, pipelined FPGA designs using Xilinx implementation software and a Xilinx design constraints (XDC) file is recommended. Design flow training about XDC files can been found at www.xilinx.com/training/fpga/essentials-of-fpga-design.htm.

Contact your local Xilinx representative for a closer review and estimation for your specific requirements.

# **Product Specification**

The SRIO Gen2 Endpoint is presented as three sub-cores (provided through the srio\_gen2\_<core\_version>\_unifiedtop wrapper) combined into a single solution using the <component\_name> module. The wrapper provides a high-level, low maintenance interface for most use models while allowing control of sub-components where necessary.

This chapter gives a basic, functional overview for each sub-core and interface including signal lists and register definitions. Not all the signals listed in the following sections come out of the <component\_name>.

# **Standards Compliance**

The Serial RapidIO Gen2 Physical Layer (PHY), Serial RapidIO Gen2 Logical Layer (LOG), and Serial RapidIO Gen2 Buffer (BUF) are designed according the *RapidIO Interconnect Specification rev. 2.2* (RapidIO Specification) [Ref 13]. Although working knowledge of the RapidIO Specification is not required to use the SRIO Gen2 Endpoint, it might be necessary to reference the specifications for details outside of the scope of this guide. This guide references portions of the RapidIO Specification when necessary.

The following list of the chapters of the *RapidIO Interconnect Specification rev 2.2* specification directly relate to the SRIO Gen2 Endpoint:

- Part 1: Input/Output System Logical Specifies functionality of the Serial RapidIO Gen2 Logical (I/O) and Transport Layer.

- **Part 2: Message Passing Logical** Specifies functionality of the Serial RapidIO Gen2 Logical (I/O) and Transport Layer when Doorbell and Message parsing is enabled.

- **Part 3: Common Transport** Specifies functionality of the Serial RapidIO Gen2 Logical (I/O) and Transport Layer.

- **Part 6: Serial Physical Layer** Specifies functionality of the Serial RapidIO Gen2 Physical Layer and the Serial RapidIO Gen2 Buffer.

## **Performance**

Table 2-1 shows the recommended speed grades for each supported device.

Table 2-1: Recommended Speed Grade Details (1)

| Link<br>Width | Performance per<br>Lane (Gb/s) | Artix-7                        | Kintex-7             | Virtex-7 | Zynq-7000 <sup>(2)</sup> | UltraScale |

|---------------|--------------------------------|--------------------------------|----------------------|----------|--------------------------|------------|

|               | 3.125/2.5/1.25                 | 1, 2L                          | 1, 2L                | 1, 2L    | 1                        | 1, 1L      |

| 1x            | 5                              | 2, 2L                          | 1, 2L                | 1, 2L    | 1                        | 1          |

|               | 6.25                           | 2, 2L                          | 1, 2L                | 1, 2L    | 1                        | 1          |

|               | 3.125/2.5/1.25                 | 1, 2L                          | 1, 2L                | 1, 2L    | 1                        | 1, 1L      |

| 2x            | 5                              | 2, 2L <sup>(3)</sup>           | 1, 2L <sup>(3)</sup> | 1, 2L    | 1                        | 1          |

|               | 6.25                           | NA                             | 1, 2L <sup>(3)</sup> | 1, 2L    | 1                        | 1          |

| 4x            | 3.125/2.5/1.25                 | 1, 2L<br>(3.125 no 2L support) | 1, 2L                | 1, 2L    | 1                        | 1, 1L      |

|               | 5                              | NA                             | 2                    | 2, 2L    | 2                        | 2          |

|               | 6.25                           | NA                             | 3                    | 3        | 3                        | 3          |

#### **Notes:**

- 1. Other speed grades are not recommended. They may require significant design effort to close timing.

- 2. .Supports both GTX and GTP for Zynq-7000 devices. Table 2-1 shows only Zynq GTX speed grades. Zynq GTP speed grades are similar to Artix-7 speed grades.

- 3. Artix-7 and Kintex-7 low voltage devices (artix7l, kintex7l) do not support line rates over 3.125 Gbps.

- 4. Speed grade details of UltraScale+ are exactly the same as UltraScale details.

# **Resource Utilization**

For details about resource utilization, visit Performance and Resource Utilization.

# **Serial Transceiver Support**

Table 2-2 shows the supported families and serial transceiver (GT) types. For designs using 7 series devices, only production wrappers are supported.

Table 2-2: Serial Transceiver Support

| Family    | Serial Transceiver |

|-----------|--------------------|

| Artix®-7  | GTP                |

| Kintex®-7 | GTX                |

Table 2-2: Serial Transceiver Support (Cont'd)

| Family       | Serial Transceiver |

|--------------|--------------------|

| Virtex®-7    | GTX/GTH            |

| Zynq®-7000   | GTX,GTP            |

| UltraScale™  | GTH, GTY           |

| UltraScale+™ | GTH, GTY           |

# **Top-Level Wrapper**

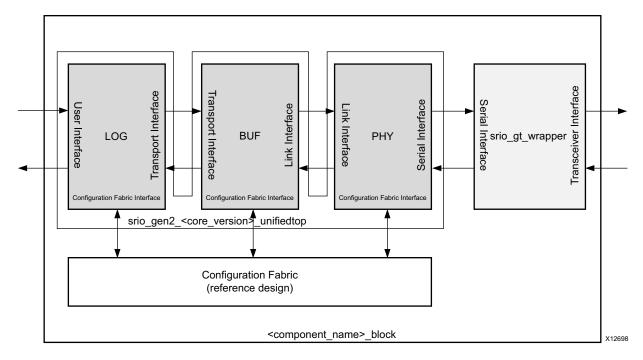

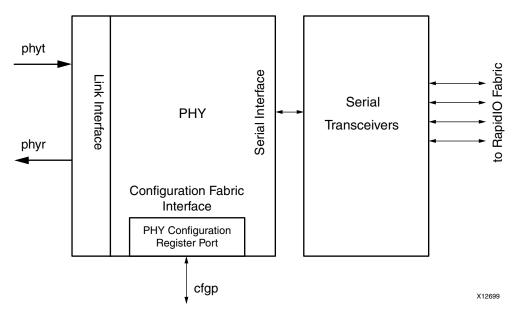

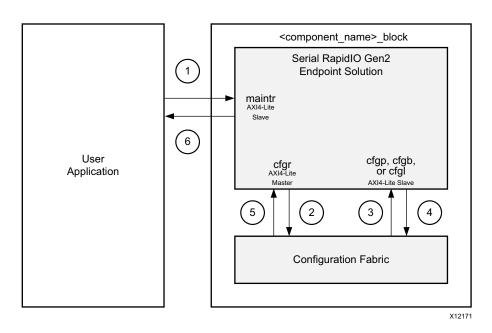

The <component\_name>\_block module bundles each component of the SRIO Gen2 Endpoint, including the reference design, to provide a packaged solution around which to design. Figure 2-1 provides a basic block diagram of how each piece fits into the <component\_name>\_block module, and a general view of the data interaction between each piece of the <component\_name>\_block design.

Figure 2-1: Top-Level Wrapper Block Diagram

# **Port Descriptions**

This section details the interfaces on each of the three sub-cores of the SRIO Gen2 Endpoint, and the interfaces for the modules in the reference design.

### **Logical Layer Interfaces**

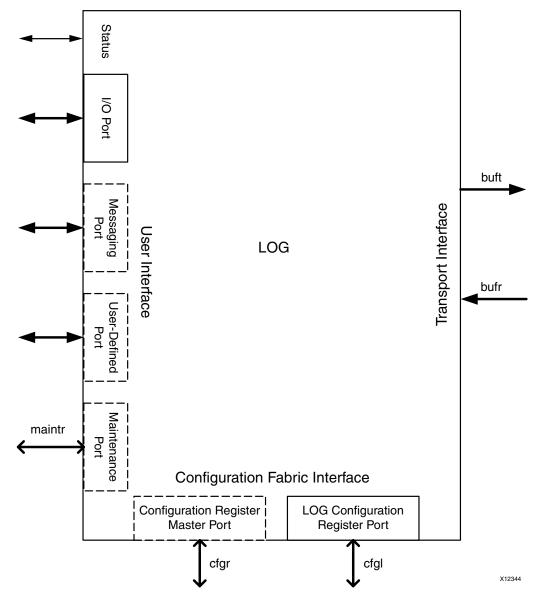

The Logical Layer (LOG) is partitioned into several modules that control the concatenation and parsing of transmit and receive packets. The LOG has three interfaces:

- User Interface

- Transport Interface

- Configuration Fabric Interface

Figure 2-2 shows the ports associated with each of the LOG interfaces. In Figure 2-2, solid arrowheads represent AXI4-Stream ports, and open arrowheads represent AXI4-Lite ports.

Note: Port names and descriptions are from the LOG point of view.

Figure 2-2: LOG Interfaces

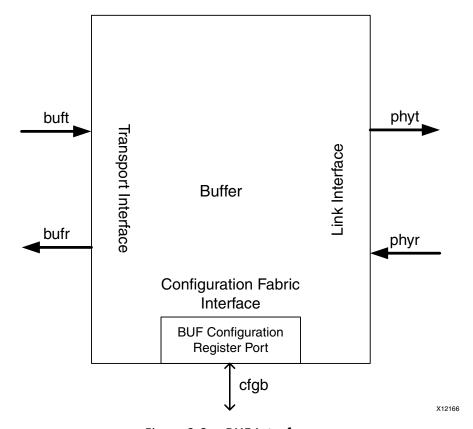

The user interface contains ports from which a packet can be issued or consumed. The number of ports and the transaction types associated with each port can be configured when the core is generated. Configuration read and write accesses can also be initiated from these ports to the configuration registers that reside in this SRIO Gen2 Endpoint device or to a remote device. These interfaces are fed out through the Serial RapidIO wrapper and are used for packet generation and consumption.

The Transport Interface contains two ports, Receive and Transmit, and is designed to be connected with a RapidIO-compliant Physical Layer or buffering application. This interface is invisible from outside the wrapper module.

The Configuration Fabric Interface contains two ports:

- **Configuration Master** port, which issues reads and writes to the local configuration space through the Configuration Fabric.

- **LOG Configuration Register** port, which is a slave interface for reads and writes to any configuration registers that are defined as part of the Logical or Transport Layers.

The Configuration Fabric decodes the address of reads or writes from the Configuration Bus Master and passes them to the Configuration Register ports of the LOG, PHY and BUF. This interaction is kept completely within the <component\_name>\_block module.

### Clock and Reset Interface

Table 2-3 lists the signals associated with the clock and resets for the LOG layer at <component\_name>\_block.

Table 2-3: LOG Clock and Reset Interface Signal List

| Signal                | Direction | Description                                                                                                                                                                                                              |

|-----------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| log_lcl_log_clk       | Output    | Clock for the LOG. In example design, log_clk depends on line rate and link width (a core trained down from Nx to 1x still uses the Nx clock rate). See Clocking in Chapter 3 for more information.                      |

|                       |           | <b>Note:</b> This signal is the same as log_clk, which is the name used in other areas of this document.                                                                                                                 |

| log_rst               | Input     | Reset for LOG. Must deassert synchronously to log_clk. See Resets in Chapter 3.                                                                                                                                          |

| log_lcl_cfg_clk Input | Input     | Configuration Register Interface clock. If the AXI4-Lite Maintenance Port and the Configuration Fabric reference design are in use, this must be equivalent to log_clk. Otherwise, this clock is independent of log_clk. |

|                       |           | <b>Note:</b> This signal is the same as cfg_clk, which is the name used in other areas of this document.                                                                                                                 |

| log_lcl_cfg_rst       | Input     | Configuration Register Interface reset. Clears LOG registers to default values. Must deassert synchronously to cfg_clk.                                                                                                  |

|                       |           | <b>Note:</b> This signal is the same as cfg_rst, which is the name used in other areas of this document.                                                                                                                 |

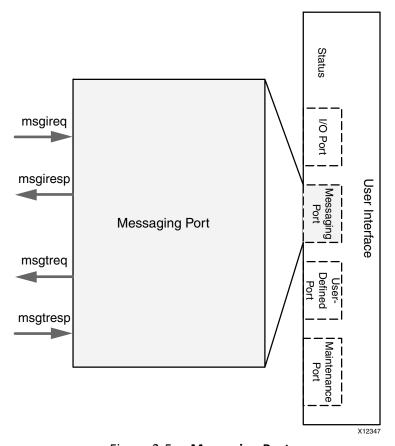

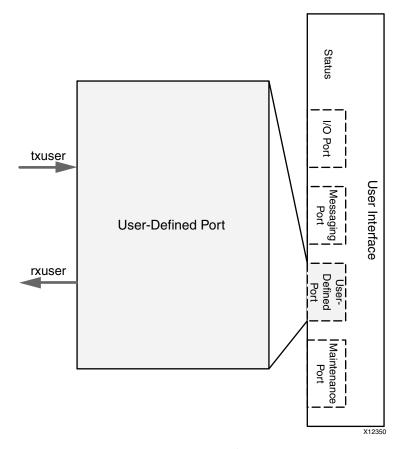

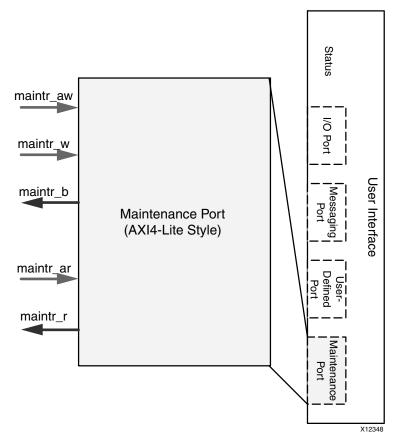

#### **User Interfaces**

The user interface contains a set of I/O ports and the following optional ports:

- Messaging Port

- Maintenance Port

- User-Defined Port

These interfaces are available from the <component\_name>\_block level. Each transaction type is assigned to a particular port. Typically, any supported I/O transactions such as NWRITEs, NWRITE\_Rs, SWRITEs, NREADs, and RESPONSEs (not including MAINTENANCE responses) are transmitted or received on the I/O port. MESSAGE transactions (if supported) can be assigned to either the Messaging port or the I/O port. DOORBELL transactions use the I/O port regardless of whether the Messaging port is present. If the Maintenance port is enabled, all Maintenance packets are expected on the Maintenance port. If a transaction is user-defined, an unsupported type, or does not have an assigned port, it uses the User-Defined port (when the User-Defined port is disabled, received packets that do not correspond to another port are dropped).

#### I/O Port

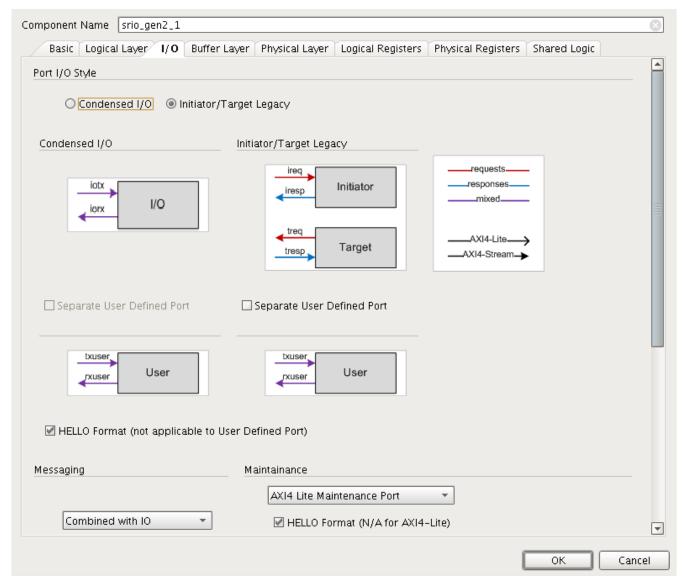

The I/O port can be configured in one of two styles: Condensed I/O or Initiator/Target. The signals available depend on the style selected during core generation.

The I/O port is built from AXI4-Stream channels. Two packet formats are available:

- HELLO

- SRIO Stream

**IMPORTANT:** All channels in the I/O port must use the same packet format, which is selected when the core is generated. See Chapter 3, Designing with the Core for more information on port usage.

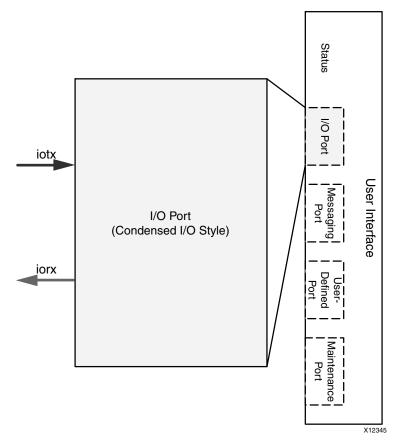

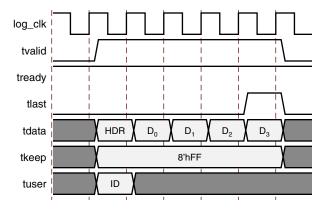

#### Condensed I/O

The Condensed I/O port style reduces the number of channels used to transmit and receive I/O packets. There is one AXI4-Stream channel used to transmit all packet types associated with the I/O port (iotx). Similarly, there is one channel used for all received I/O port packets (iorx). Figure 2-3 shows the Condensed I/O port.

**Note:** Port names and descriptions are from the LOG point of view.

Figure 2-3: Condensed I/O Port

Table 2-4 lists the signals associated with the Condensed I/O port. The s\_axis\_iotx\* signals are associated with the CONDENSED\_IO\_TX interface, and the m\_axis\_iorx\* signals are associated with the CONDENSED\_IO\_RX interface at the <component\_name> level.

Table 2-4: Condensed I/O Port Signal List

| Signal                  | Direction | Description                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| s_axis_iotx_tvalid      | Input     | Indicates that the information on the channel is valid.                                                                                                                                                                                                                                                                                                                                                                      |

| s_axis_iotx_tready      | Output    | Handshaking signal. Indicates that the data from the source is accepted (if valid).                                                                                                                                                                                                                                                                                                                                          |

| s_axis_iotx_tdata[63:0] | Input     | Packet header and data.                                                                                                                                                                                                                                                                                                                                                                                                      |

| s_axis_iotx_tkeep[7:0]  | Input     | Byte qualifier that indicates whether the content of the associated byte of data is valid. If port is configured to use HELLO format, this must be tied to 8'hFF. For ports configured to use SRIO Stream format, this input should be set to 8'hFF except when tlast is asserted.  Bit 7 corresponds to the most significant byte of data (tdata[63:56]), and bit 0 corresponds to the least significant byte (tdata[7:0]). |

| s_axis_iotx_tlast       | Input     | Indicates the last beat of a packet.                                                                                                                                                                                                                                                                                                                                                                                         |

Table 2-4: Condensed I/O Port Signal List (Cont'd)

| Signal                  | Direction | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| s_axis_iotx_tuser[31:0] | Input     | HELLO Format: Valid on the first beat of a packet, this signal consists of the Source ID (31:16) and Destination ID (15:0) for the packet. If using 8-bit Device IDs, the most significant byte of each ID should be padded with 0s. The Source ID portion of the signal is tied to the deviceid signal.  SRIO Stream Format: In this format, tuser is only 8 bits wide. Bit 1 is used to set the Critical Request Flow (CRF) flag for the packet, and should be tied to zero if CRF support is disabled. All other bits are reserved.  On subsequent beats within a packet, this field is reserved. |

| m_axis_iorx_tvalid      | Output    | Indicates that the information on the channel is valid.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| m_axis_iorx_tready      | Input     | Handshaking signal. Indicates that the data from the source is accepted (if valid).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| m_axis_iorx_tdata[63:0] | Output    | Packet header and data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| m_axis_iorx_tkeep[7:0]  | Output    | Byte qualifier that indicates whether the content of the associated byte of data is valid. If port is configured to use HELLO format, this is tied to 8'hFF. For ports configured to use SRIO Stream format, this output is set to 8'hFF except when tlast is asserted.  Bit 7 corresponds to the most significant byte of data (tdata[63:56]) and bit 0 corresponds to the least significant byte (tdata[7:0]).                                                                                                                                                                                     |

| m_axis_iorx_tlast       | Output    | Indicates the last beat of a packet.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| m_axis_iorx_tuser[31:0] | Output    | HELLO Format: Valid on the first beat of a packet, this signal consists of the Source ID (31:16) and Destination ID (15:0) for the packet. If using 8-bit Device IDs, the most significant byte of each ID is padded with 0s.  SRIO Stream Format: In this format, tuser is only 8 bits wide. Bit 1 is set if the Critical Request Flow (CRF) flag for the packet was set. All other bits are reserved.  On subsequent beats within a packet, this field is reserved.                                                                                                                                |

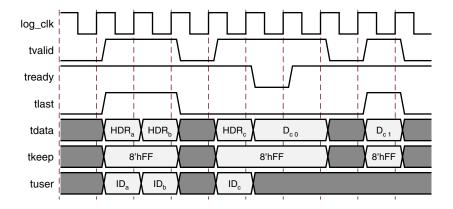

#### Initiator/Target

The Initiator/Target port style allows separation of transactions intended for remote devices (placed on Initiator port) from transactions targeting the local endpoint (placed on Target port).

As shown in Figure 2-4, there are four AXI4-Stream channels for I/O transactions when using the Initiator/Target port style. In Figure 2-4, request channels are shown in black and response channels in gray.

**Note:** Port names and descriptions are from the LOG point of view.

Figure 2-4: Initiator/Target Port

Requests generated by the local endpoint are placed on the Initiator Request (ireq) channel to be transmitted on the link. Responses received from a remote device are presented to the user design on the Initiator Response (iresp) channel.

Requests originating from a remote device which are received by the core are presented to the user design on the Target Request (treq) channel. Responses to these requests, which are generated by the user design, are placed on the Target Response (tresp) channel.

Table 2-5 shows the signals associated with the Initiator/Target port. At the <component\_name > level, the following signals are associated with these interfaces:

- s\_axis\_ireq\* are associated with INITIATOR\_IREQ.

- m\_axis\_iresp\* are associated with INITIATOR\_IRESP.

- m\_axis\_treq\* are associated with TARGET\_TREQ.

- s\_axis\_tresp\* are associated with TARGET\_TRESP.

Table 2-5: Initiator/Target Port Signal List

| s_axis_ireq_tvalid         Input         Indicates that the information on the interface is valid.           s_axis_ireq_tready         Output         Handshaking signal. Indicates that the data from the source is accepted (if valid).           s_axis_ireq_tdata[63:0]         Input         Packet header and data.           s_axis_ireq_tkeep[7:0]         Byte qualifier that indicates whether the content of the associated byte of data is valid. If port is configured to use the JELLO format, this insuts the tied to 8 hrs. For ports configured to use the SRIO Stream format, this input should be set to 8 hrs. Fexcept when that is asserted.           s_axis_ireq_tlaset         Input         Indicates the last beat of a packet.           HELLO Format: Valid on the first beat of a packet, this signal consists of the Source ID (31:16) and Destination ID (15:0) for the packet. If using 8-bit Device IDs, the most significant byte of each ID should be padded with 0s. In the default example design, Device ID is connected to the Source ID. However, those with a custom design should make the necessary connection.           s_axis_ireq_tuser[31:0]         Input         Rist Source ID (31:16) and Destination ID (15:0) for the packet. If using 8-bit Device IDs, the most significant byte of each ID should be padded with 0s. In the default example design, Device ID is connected to the Source ID. However, those with a custom design should make the necessary connection.           m_axis_iresp_tvalid         Output         Rist Cornected to Inconnected to                                                                                                                                                                                                                                                                                                                                    | Signal                   | Direction | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| s_axis_ireq_tdata[63:0] Input Packet header and data.  Byte qualifier that indicates whether the content of the associated byte of data is valid. If port is configured to use the HELLO format, this must be tied to 8' hFF. For ports configured to use the SRIO Stream format, this input should be set to 8' hFF except when tlast is asserted.  Bit 7 corresponds to the most significant byte of data (tdata[63:56]), and bit 0 corresponds to the least significant byte (tdata[7:0]).  Linput Indicates the last beat of a packet.  HELLO Format: Valid on the first beat of a packet, this signal consists of the Source ID (31:16) and Destination ID (15:0) for the packet. If using 8-bit Device IDs, the most significant byte of each ID should be padded with 0s. In the default example design, Device ID is connected to the Source ID. However, those with a custom design should make the necessary connection.  SRIO Stream Format: In this format, tuser is only 8 bits wide. Bit 1 is used to set the Critical Request Flow (CRF) flag for the packet, and should be tied to zero if CRF support is disabled. All other bits are reserved.  On subsequent beats within a packet, this field is reserved.  M_axis_iresp_teady  Input Indicates that the information on the interface is valid.  Handshaking signal. Indicates that the data from the source is accepted (if valid).  M_axis_iresp_teady  M_axis_iresp_teady  M_axis_iresp_teady  M_axis_iresp_teady  Input Indicates that the information on the interface is valid.  Byte qualifier that indicates whether the content of the associated byte of data is valid. If port is configured to use HELLO format, this is dea to 8' hFFP. For ports configured to use SRIO Stream format, this output is set to 8' hFFP except when tlast is asserted.  Bit 7 corresponds to the most significant byte of data (tdata[63:56]) and bit 0 corresponds to the least significant byte (tdata[7:0]).  M_axis_iresp_tuser[31:0]  Output Indicates the last beat of a packet.  HELLO Format: Valid on the first beat of a packet, this signal consists | s_axis_ireq_tvalid       | Input     | Indicates that the information on the interface is valid.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Byte qualifier that indicates whether the content of the associated byte of data is valid. If port is configured to use the HELLO format, this must be tied to 8 'hbr. For ports configured to use the SRIO Stream format, this input should be set to 8'hFF except when tlast is asserted.  Byt 7 corresponds to the most significant byte of data (tdata[63:56]), and bit 0 corresponds to the least significant byte (tdata[7:0]).    Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | s_axis_ireq_tready       | Output    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| byte of data is valid. If port is configured to use the HELLO format, this must be tied to 8 "hFF. For ports configured to use the SRIO Stream format, this input should be set to 8 hFF except when tlast is asserted.  Bit 7 corresponds to the most significant byte of data (tdata[63:56]), and bit 0 corresponds to the least significant byte (tdata[7:0]).  s_axis_ireq_tlast  Input Indicates the last beat of a packet.  HELLO Format: Valid on the first beat of a packet, this signal consists of the Source ID (31:16) and Destination ID (15:0) for the packet. If using 8-bit Device IDs, the most significant byte of each ID should be padded with 0s. In the default example desemble packet. If using 8-bit Device IDs, the most significant byte of each ID should be padded with 0s. In the default example desemble packet. If using 8-bit Device IDs, the most significant byte of each ID should be padded with 0s. In the default example desemble of the packet, If using 8-bit Device IDs, the most significant byte of each ID should be tied to zero if CRF support is disabled. All other bits are reserved.  On subsequent beats within a packet, this field is reserved.  M_axis_iresp_tready  Input Indicates that the information on the interface is valid.  Handshaking signal. Indicates that the data from the source is accepted (if valid).  M_axis_iresp_tdata[63:0]  Output Packet header and data.  Byte qualifier that indicates whether the content of the associated byte of data is valid. If port is configured to use HELLO format, this is tied to 8 'hFF. For ports configured to use SRIO Stream format, this set to 8 'hFF except when tlast is asserted.  Bit 7 corresponds to the most significant byte of data (tdata[63:56]) and bit 0 corresponds to the least significant byte (tdata[7:0]).  M_axis_iresp_tlast  Output Indicates the last beat of a packet.  HELLO Format: Valid on the first beat of a packet, this signal consists of the Source ID (31:16) and Destination ID (15:0) for the packet. If using 8-bit Device IDs, the most significant byte of ea | s_axis_ireq_tdata[63:0]  | Input     | Packet header and data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Indicates the last beat of a packet.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | s_axis_ireq_tkeep[7:0]   | Input     | byte of data is valid. If port is configured to use the HELLO format, this must be tied to 8'hFF. For ports configured to use the SRIO Stream format, this input should be set to 8'hFF except when tlast is asserted.  Bit 7 corresponds to the most significant byte of data                                                                                                                                                                                                                                                                        |

| HELLO Format: Valid on the first beat of a packet, this signal consists of the Source ID (31:16) and Destination ID (15:0) for the packet. If using 8-bit Device IDs, the most significant byte of each ID should be padded with 0s. In the default example design, Device ID is connected to the Source ID. However, those with a custom design should make the necessary connection.  SRIO Stream Format: In this format, tuser is only 8 bits wide. Bit 1 is used to set the Critical Request Flow (CRF) flag for the packet, and should be tied to zero if CRF support is disabled. All other bits are reserved.  On subsequent beats within a packet, this field is reserved.  M_axis_iresp_tready  Input  Handshaking signal. Indicates that the data from the source is accepted (if valid).  M_axis_iresp_tdata[63:0]  Output  Packet header and data.  Byte qualifier that indicates whether the content of the associated byte of data is valid. If port is configured to use HELLO format, this is tied to 8 'hFF. For ports configured to use SRIO Stream format, this output is set to 8 'hFF except when tlast is asserted.  Bit 7 corresponds to the most significant byte of data (tdata[63:56]) and bit 0 corresponds to the least significant byte (tdata[7:0]).  m_axis_iresp_tuser[31:0]  M_axis_iresp_tuser[31:0]  Output  HELLO Format: Valid on the first beat of a packet, this signal consists of the Source ID (31:16) and Destination ID (15:0) for the packet. If using 8-bit Device IDs, the most significant byte of each ID should be padded with 0s.  SRIO Stream Format: In this format, tuser is only 8 bits wide. Bit 1 is set if the Critical Request Flow (CRF) flag for the packet was set. All other bits are reserved. On subsequent beats within a packet, this field is reserved.                                                                                                                                                                                                                                                                                                    |                          | _         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| consists of the Source ID (31:16) and Destination ID (15:0) for the packet. If using 8-bit Device IDs, the most significant byte of each ID should be padded with 0s. In the default example design, Device ID is connected to the Source ID. However, those with a custom design should make the necessary connection.  SRIO Stream Format: In this format, tuser is only 8 bits wide. Bit 1 is used to set the Critical Request Flow (CRF) flag for the packet, and should be tied to zero if CRF support is disabled. All other bits are reserved.  On subsequent beats within a packet, this field is reserved.  M_axis_iresp_tready  Input  M_axis_iresp_tdata[63:0]  Output  Byte qualifier that indicates that the data from the source is accepted (if valid).  M_axis_iresp_tkeep[7:0]  Output  Byte qualifier that indicates whether the content of the associated byte of data is valid. If port is configured to use HELLO format, this is tied to 8° hFF. For ports configured to use HELLO format, this output is set to 8 'hFF except when tlast is asserted.  Bit 7 corresponds to the most significant byte of data (tdata[63:56]) and bit 0 corresponds to the least significant byte (tdata[7:0]).  M_axis_iresp_tuser[31:0]  M_axis_iresp_tuser[31:0]  Output  Indicates the last beat of a packet.  HELLO Format: Valid on the first beat of a packet, this signal consists of the Source ID (31:16) and Destination ID (15:0) for the packet. If using 8-bit Device IDs, the most significant byte of each ID should be padded with 0s.  SRIO Stream Format: In this format, tuser is only 8 bits wide. Bit 1 is set if the Critical Request Flow (CRF) flag for the packet was set. All other bits are reserved.  On subsequent beats within a packet, this field is reserved.                                                                                                                                                                                                                                                                                                                          | s_axis_ireq_tlast        | Input     | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| m_axis_iresp_tready Input Handshaking signal. Indicates that the data from the source is accepted (if valid).  m_axis_iresp_tdata[63:0] Output Packet header and data.  Byte qualifier that indicates whether the content of the associated byte of data is valid. If port is configured to use HELLO format, this is tied to 8 ' hFF. For ports configured to use SRIO Stream format, this output is set to 8 ' hFF except when tlast is asserted.  Bit 7 corresponds to the most significant byte of data (tdata[63:56]) and bit 0 corresponds to the least significant byte (tdata[7:0]).  m_axis_iresp_tlast  Output Indicates the last beat of a packet.  HELLO Format: Valid on the first beat of a packet, this signal consists of the Source ID (31:16) and Destination ID (15:0) for the packet. If using 8-bit Device IDs, the most significant byte of each ID should be padded with 0s.  SRIO Stream Format: In this format, tuser is only 8 bits wide. Bit 1 is set if the Critical Request Flow (CRF) flag for the packet was set. All other bits are reserved.  On subsequent beats within a packet, this field is reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | s_axis_ireq_tuser[31:0]  | Input     | consists of the Source ID (31:16) and Destination ID (15:0) for the packet. If using 8-bit Device IDs, the most significant byte of each ID should be padded with 0s. In the default example design, Device ID is connected to the Source ID. However, those with a custom design should make the necessary connection.  SRIO Stream Format: In this format, tuser is only 8 bits wide. Bit 1 is used to set the Critical Request Flow (CRF) flag for the packet, and should be tied to zero if CRF support is disabled. All other bits are reserved. |

| Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | m axis iresp tvalid      | Output    | Indicates that the information on the interface is valid.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Byte qualifier that indicates whether the content of the associated byte of data is valid. If port is configured to use HELLO format, this is tied to 8'hFF. For ports configured to use SRIO Stream format, this output is set to 8'hFF except when tlast is asserted.  Bit 7 corresponds to the most significant byte of data (tdata[63:56]) and bit 0 corresponds to the least significant byte (tdata[7:0]).  M_axis_iresp_tlast  Output  Output  Indicates the last beat of a packet.  HELLO Format: Valid on the first beat of a packet, this signal consists of the Source ID (31:16) and Destination ID (15:0) for the packet. If using 8-bit Device IDs, the most significant byte of each ID should be padded with 0s.  SRIO Stream Format: In this format, tuser is only 8 bits wide. Bit 1 is set if the Critical Request Flow (CRF) flag for the packet was set. All other bits are reserved.  On subsequent beats within a packet, this field is reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | m_axis_iresp_tready      | Input     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| byte of data is valid. If port is configured to use HELLO format, this is tied to 8 'hff. For ports configured to use SRIO Stream format, this output is set to 8 'hff except when tlast is asserted.  Bit 7 corresponds to the most significant byte of data (tdata[63:56]) and bit 0 corresponds to the least significant byte (tdata[7:0]).  Maxis_iresp_tlast  Output  Indicates the last beat of a packet.  HELLO Format: Valid on the first beat of a packet, this signal consists of the Source ID (31:16) and Destination ID (15:0) for the packet. If using 8-bit Device IDs, the most significant byte of each ID should be padded with 0s.  SRIO Stream Format: In this format, tuser is only 8 bits wide. Bit 1 is set if the Critical Request Flow (CRF) flag for the packet was set. All other bits are reserved.  On subsequent beats within a packet, this field is reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | m_axis_iresp_tdata[63:0] | Output    | Packet header and data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| HELLO Format: Valid on the first beat of a packet, this signal consists of the Source ID (31:16) and Destination ID (15:0) for the packet. If using 8-bit Device IDs, the most significant byte of each ID should be padded with 0s.  SRIO Stream Format: In this format, tuser is only 8 bits wide. Bit 1 is set if the Critical Request Flow (CRF) flag for the packet was set. All other bits are reserved.  On subsequent beats within a packet, this field is reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | m_axis_iresp_tkeep[7:0]  | Output    | byte of data is valid. If port is configured to use HELLO format, this is tied to 8'hFF. For ports configured to use SRIO Stream format, this output is set to 8'hFF except when tlast is asserted.  Bit 7 corresponds to the most significant byte of data (tdata[63:56]) and bit 0 corresponds to the least significant byte                                                                                                                                                                                                                        |

| consists of the Source ID (31:16) and Destination ID (15:0) for the packet. If using 8-bit Device IDs, the most significant byte of each ID should be padded with 0s.  SRIO Stream Format: In this format, tuser is only 8 bits wide. Bit 1 is set if the Critical Request Flow (CRF) flag for the packet was set. All other bits are reserved.  On subsequent beats within a packet, this field is reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | m_axis_iresp_tlast       | Output    | Indicates the last beat of a packet.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| m_axis_treq_tvalid Output Indicates that information on the interface is valid.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | m_axis_iresp_tuser[31:0] | Output    | consists of the Source ID (31:16) and Destination ID (15:0) for the packet. If using 8-bit Device IDs, the most significant byte of each ID should be padded with 0s.  SRIO Stream Format: In this format, tuser is only 8 bits wide. Bit 1 is set if the Critical Request Flow (CRF) flag for the packet was set. All other bits are reserved.                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | m_axis_treq_tvalid       | Output    | Indicates that information on the interface is valid.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

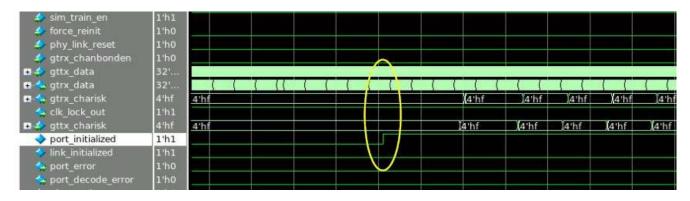

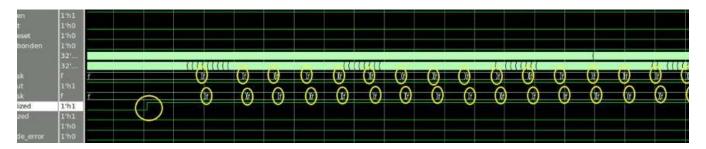

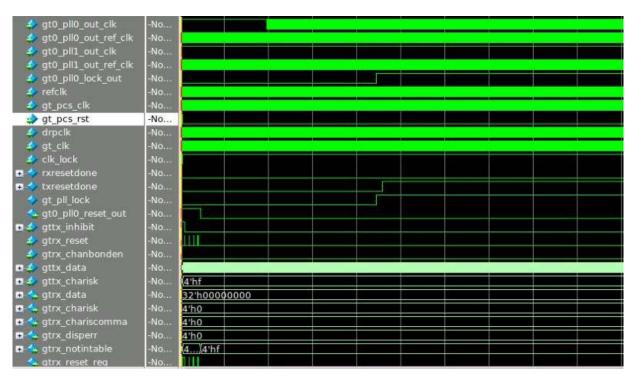

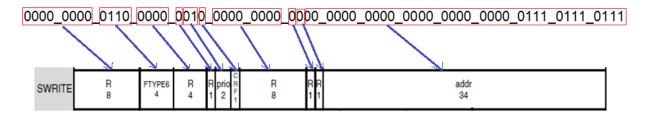

Table 2-5: Initiator/Target Port Signal List (Cont'd)