# XGS 12000, XGS 9400 and XGS 8000 Global Shutter CMOS Image Sensors

# XGS Family

### **Description**

The XGS CMOS image sensor family provides high resolution, high performance global shutter image capture. The family comes in different resolutions in a single package; 8.8, 9.4 and 12.6 Megapixels with up to 1-inch optical format. The 21 mm x 20 mm package makes the XGS family particularly suited for integration in 29 mm x 29 mm camera formats. The high speed, 12-bit output maximally leverages interfaces such as USB 3.2, Thunderbolt  $^{\text{TM}}$  2 and 10 GigE.

Image data is read out through a column ADC architecture and then transferred over a HiSPi interface. On-chip logic, programmable via the serial interface, generates internal timing for integration and readout control. Up to three register configurations can be programmed and sequentially enabled (frame by frame) using a single command over the control interface.

Table 1. KEY PERFORMANCE PARAMETERS

| Parameter           |                                          | Typical Value                 |  |  |

|---------------------|------------------------------------------|-------------------------------|--|--|

| Optical Format      | XGS 12000                                | 1-inch (16.4 mm Diagonal)     |  |  |

|                     | XGS 9400                                 | 1/1.2-inch (13.9 mm Diagonal) |  |  |

|                     | XGS 8000                                 | 1/1.1-inch (14.8 mm Diagonal) |  |  |

| Active Pixels       | XGS 12000                                | 4096 (H) x 3072 (V)           |  |  |

|                     | XGS 9400                                 | 3072 (H) x 3072 (V)           |  |  |

|                     | XGS 8000                                 | 4096 (H) x 2160 (V)           |  |  |

| Pixel Size          | 3.2 μm                                   |                               |  |  |

| Color Filter Array  | Monochrome, Baye                         | er                            |  |  |

| Shutter Type        | Global Shutter                           |                               |  |  |

| Input Clock         | 32.4 MHz                                 |                               |  |  |

| Output Interface    | HiSPi (24 Lanes - 1                      | 777.6 Mbps/lane)              |  |  |

| Frame Rate (12-bit) | 24 Lanes (-X1)                           |                               |  |  |

|                     | XGS 12000                                | 90 fps                        |  |  |

|                     | XGS 9400                                 | 90 fps                        |  |  |

|                     | XGS 8000                                 | 128 fps                       |  |  |

|                     | 12 Lanes (-X2)                           |                               |  |  |

|                     | XGS 9400                                 | 56 fps                        |  |  |

|                     | XGS 8000                                 | 80 fps                        |  |  |

|                     | 6 Lanes (-X3)                            |                               |  |  |

|                     | XGS 12000                                | 28 fps                        |  |  |

| Read Noise          | < 4 e- (1x), 1.9 e- (                    | (4x)                          |  |  |

| SNR <sub>MAX</sub>  | 40 dB                                    |                               |  |  |

| Dynamic Range       | 68 dB                                    |                               |  |  |

| Supply Voltages     | 1.2V, 2.8 V, 3 V (0.4 V, 1.8 V Optional) |                               |  |  |

| Power Consumption   | 1 W (Full Speed, Full Resolution)        |                               |  |  |

| Operating Temp.     | -40°C to 85°C (Junction)                 |                               |  |  |

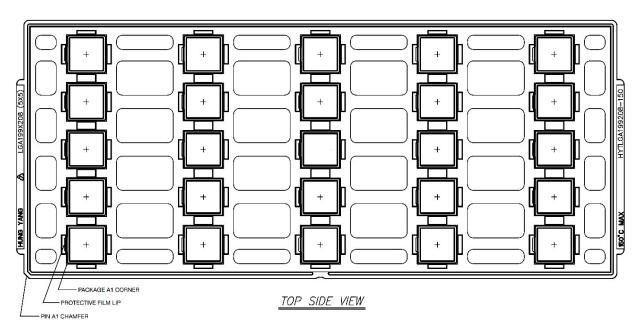

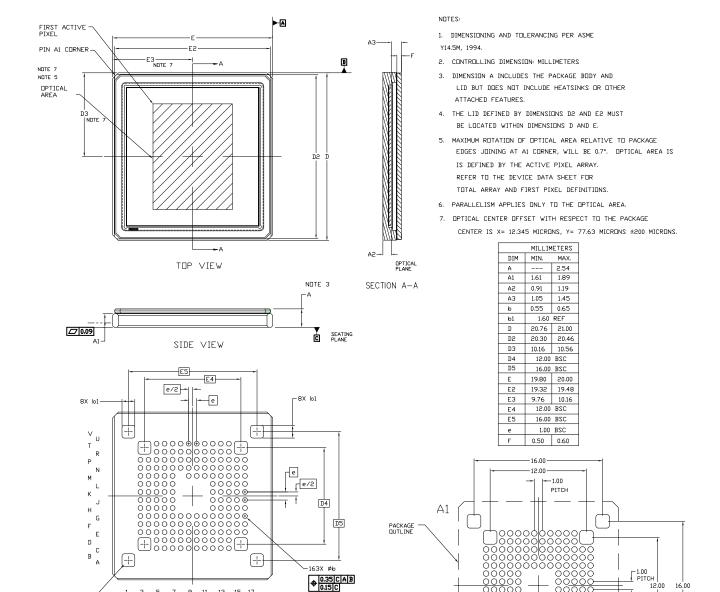

| Package             | 163-pin CLGA (Ceramic Land Grid Array)   |                               |  |  |

### ON Semiconductor®

#### www.onsemi.com

#### **Features**

- On-chip 12-bit Column ADCs

- Companding Mode for 60 fps (12-lane) and 30 fps (6-lane) at Full Resolution

- Data Interface: 24-lane HiSPi (Scalable Low-Voltage Signaling)

- Configurable Number of HiSPi Lanes: 24, 18, 12 or 6 Lanes

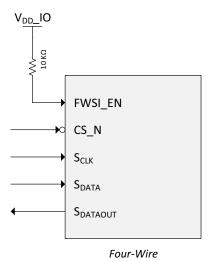

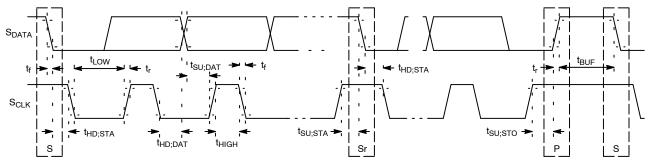

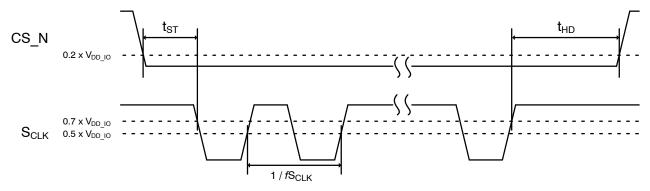

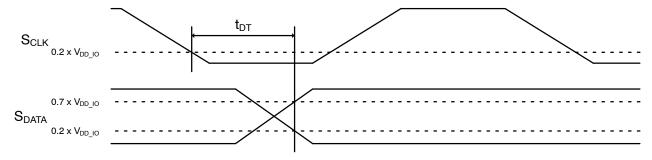

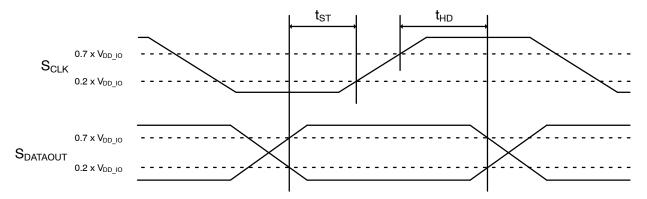

- Two-Wire (I<sup>2</sup>C) and Four-Wire (SPI)

Serial Interface

- Triggered Integration and Readout Control

- Programmable Control for up to 8 Regions of Interest (ROI)

- Context Switching

- These Devices are Pb-Free, Halogen Free/ BFR Free and are RoHS Compliant

### **Applications**

- Machine Vision

- Security

- Intelligent Transportation Systems (ITS)

- Broadcasting

- Medical

- Scientific

## **ORDERING INFORMATION**

Table 2. ORDERABLE PART NUMBERS (Notes 1 and 2)

| Part Number         | Minimum Order Quantity | Produ       | uct Descr | ription     | Speed Grade    | Resolution (H x V) |

|---------------------|------------------------|-------------|-----------|-------------|----------------|--------------------|

| NOIX1SN012KB-LTI    | 25                     | 12.6 Mp     | Mono      | 0° CRA      | 24 Lanes       | 4096 x 3072        |

| NOIX1SN012KB-LTI1   | 4                      |             |           | !           |                |                    |

| NOIX1SE012KB-LTI    | 25                     | 12.6 Mp     | Color     | 0° CRA      | 1              |                    |

| NOIX1SE012KB-LTI1   | 4                      |             | <u> </u>  |             | ]              |                    |

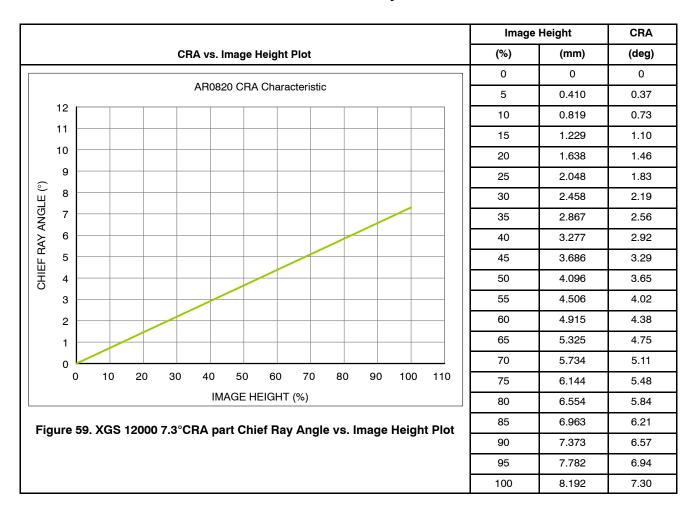

| NOIX1SF012KB-LTI    | 25                     | 12.6 Mp     | Color     | 7.3° CRA    |                |                    |

| NOIX1SF012KB-LTI1   | 4                      |             | <u> </u>  |             |                | _                  |

| NOIX3SN012KB-LTI    | 25                     | 12.6 Mp     | Mono      | 0° CRA      | 6 Lanes        |                    |

| NOIX3SN012KB-LTI1   | 4                      |             | <u> </u>  | <u> </u>    | <u> </u>       |                    |

| NOIX3SE012KB-LTI    | 25                     | 12.6 Mp     | Color     | 0° CRA      |                |                    |

| NOIX3SE012KB - LTI1 | 4                      | <u></u>     | '         |             |                | <u> </u>           |

| NOIX1SN9400B-LTI    | 25                     | 9.4 Mp      | Mono      | 0° CRA      | 24 Lanes       | 3072 x 3072        |

| NOIX1SN9400B-LTI1   | 4                      |             |           | !           |                |                    |

| NOIX1SE9400B-LTI    | 25                     | 9.4 Mp      | Color     | 0° CRA      | 1              |                    |

| NOIX1SE9400B - LTI1 | 4                      |             | <u> </u>  | !           |                |                    |

| NOIX2SN9400B-LTI    | 25                     | 9.4 Mp      | Mono      | 0° CRA      | 12 Lanes       | 1                  |

| NOIX2SN9400B-LTI1   | 4                      |             |           |             |                |                    |

| NOIX2SE9400B-LTI    | 25                     | 9.4 Mp      | Color     | 0° CRA      |                |                    |

| NOIX2SE9400B-LTI    | 4                      |             |           |             |                |                    |

|                     |                        | <del></del> | T         | <del></del> | <del>1</del> . | ·                  |

| NOIX1SN8000B-LTI    | 25                     | 8.8 Mp      | Mono      | 0° CRA      | 24 Lanes       | 4096 x 2160        |

| NOIX1SN8000B-LTI1   | 4                      |             |           |             |                |                    |

| NOIX1SE8000B-LTI    | 25                     | 8.8 Mp      | Color     | 0° CRA      |                |                    |

| NOIX1SE8000B-LTI1   | 4                      |             |           |             |                |                    |

| NOIX2SF8000B-LTI    | 25                     | 8.8 Mp      | Color     | 7.3° CRA    | 12 Lanes       | ]                  |

| NOIX2SF8000B-LTI1   | 4                      |             |           |             | ]              |                    |

| NOIX2SN8000B-LTI    | 25                     | 8.8 Mp      | Mono      | 0° CRA      |                |                    |

| NOIX2SN8000B-LTI1   | 4                      |             |           |             |                |                    |

| NOIX2SE8000B-LTI    | 25                     | 8.8 Mp      | Color     | 0° CRA      |                |                    |

See the ON Semiconductor Device Nomenclature document (TND310/D) for a full description of the naming convention used for image sensors. For reference documentation, including information on evaluation kits, please visit our web site at www.onsemi.com.

## **Table 3. ORDERING INFORMATION EVALUATION KITS**

4

| Part Number          | Product Description                        | Additional Information                                  |

|----------------------|--------------------------------------------|---------------------------------------------------------|

| NOIX1SN012KBLFB-GEVB | Sensor Headboard (12.6 Mp, Mono, 24-Lane)  | Demo Kit Headboard (incl.<br>NOIX1SN012KB-LTI) (Note 3) |

| NOIX1SE012KBLFB-GEVB | Sensor Headboard (12.6 Mp, Color, 24-Lane) | Demo Kit Headboard (incl.<br>NOIX1SE012KB-LTI) (Note 3) |

| AGBAN6CS-GEVK        | Frame Buffer Demo Board                    | AP21088 including Power Adapter                         |

| AGB1N0CS-GEVK        | Demo 3 Board                               | FPGA Base Board including USB Cable and Tripod          |

<sup>3.</sup> Sensors are soldered to the headboard.

NOIX2SE8000B-LTI1

<sup>2.</sup> All devices listed in Table 2 are equipped with microlenses.

### **GENERAL DESCRIPTION**

The XGS family from ON Semiconductor covers three resolutions: 12.6 Mp, 9.4 Mp and 8.8 Mp and three speed grades (24, 12 or 6 HiSPi lanes). Refer to Table 2 for an overview of the available combinations of resolution and speed. Various operating modes enable flexible sensor operation to meet application specific requirements such as reduced data rate implemented by HiSPi lane multiplexing.

### **FUNCTIONAL OVERVIEW**

The XGS family features global shutter technology for accurate capture of moving objects. Global shutter requires

all pixels to simultaneously integrate light although the subsequent readout is sequential. Note that integration and readout can occur in parallel; while reading out one frame, integration of the next frame can start (i.e. *pipelined operation*). The core of the sensor is the 12.6 Mp active pixel array.

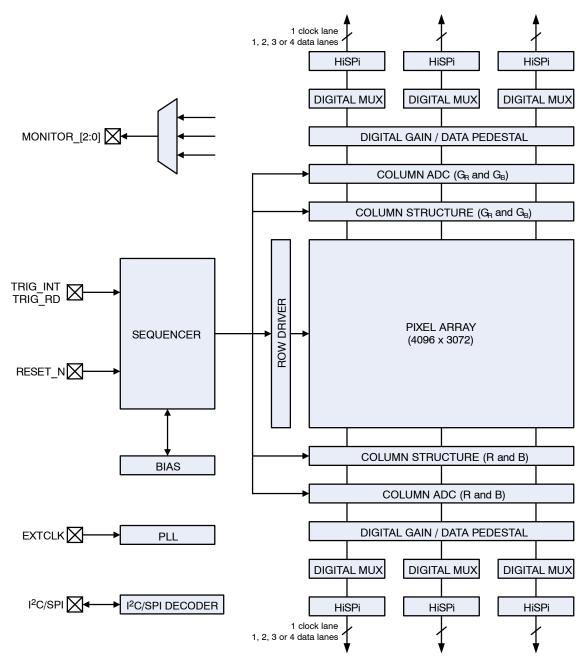

Figure 1 gives an overview of the major functional blocks of the XGS sensor.

Figure 1. Functional Block Diagram (XGS 12000)

The on-chip logic, programmable through the Two-Wire (I<sup>2</sup>C) or Four-Wire (SPI) Serial Interface, generates all internal timing for integration control and frame readout. Once a row has been read, the data from the columns is sequenced through an analog signal chain (providing coarse analog gain) and then through a 12-bit column ADC. The data from the ADCs is first stored in the on-chip column memory bank prior to being processed by the digital data path (which provides additional data processing including digital gain and offset). The digital multiplexer can be configured to reduce the number of active data lanes. The maximum output pixel rate on a single lane is 64.8 Megapixel per second, corresponding to a clock rate of 32.4 MHz.

Advanced trigger functions enable synchronization to external events (triggered master and slave mode) but also allow synchronizing image readout with the host (receiver) on a frame or line basis (triggered frame or line readout). The sensor supports configuration of up to eight independent ROIs and up to three register configurations (*contexts*) can be programmed and sequentially applied (frame by frame) with a single command over the control interface.

Refer to Figure 1 for the functional blocks described hereafter.

- Two-Wire Serial Interface (I<sup>2</sup>C)

I<sup>2</sup>C-compatible, two-wire serial interface enables user interaction with sensor.

- (Four-Wire) Serial Peripheral Interface (SPI)

The Four-Wire serial interface can be used as an

alternative to the two-wire interface. The SPI enables

faster sensor (re-)configuration compared to the

two-wire serial interface.

### • EXTCLK

The nominal input-clock frequency is 32.4 MHz. This clock serves as the base clock for the derived clock domains required by the internal sub-blocks and HiSPi output interface.

- Phase-locked Loop (PLL)

The on-chip phase-locked loop generates all the internal system clocks, including the HiSPi clock.

- Bias Generator

The bias generator generates the required reference currents used by the on-chip blocks.

### Sequencer

The sequencer generates the sensor timing and controls the image core which contains all pixels, driving and readout circuits. It controls the ADC circuits and provides the necessary information to the digital data path. The sequencer operating and readout modes (ROI readout, subsampling...) can be configured through the SPI interface. The readout parameters are synchronized to frame boundaries to support dynamic reconfiguration without generating any corrupted images.

#### • Row Driver

The row drivers generate the reset and select signals used to operate the pixel array.

### • Monitor Pins

The sequencer can communicate its internal states through the monitor output pins.

#### • Column Structure

The column structure contains the analog circuits necessary to ensure a proper transfer of the signal to the column ADC. This structure includes the column amplifiers which can be used to apply analog gain to the signal before these are converted by the ADCs. The sensor supports analog gain of 1x, 2x and 4x. The analog gain is applied globally to all pixels.

#### Column ADC

For each column, a 12-bit ADC converts the analog signal into a digital value.

### • Digital Gain

A linear, digital gain ranging from 1/32x up to 2x can be configured separately for each color channel in steps of 1/32.

#### • Data Pedestal

This block adds a user programmable, per color channel digital offset to the pixel values.

## • Digital Mux

This block handles the lane multiplexing which can be used to reduce the number of output lanes.

### HiSPi

The 24 HiSPi lanes are laid out in six identical HiSPi blocks. Each block consists of four data lanes and one clock lane. The number of active data lanes (1, 2, 3 or 4) depends on the selected multiplex mode.

#### **PIXEL DATA FORMAT**

### **PIXEL ARRAY STRUCTURE**

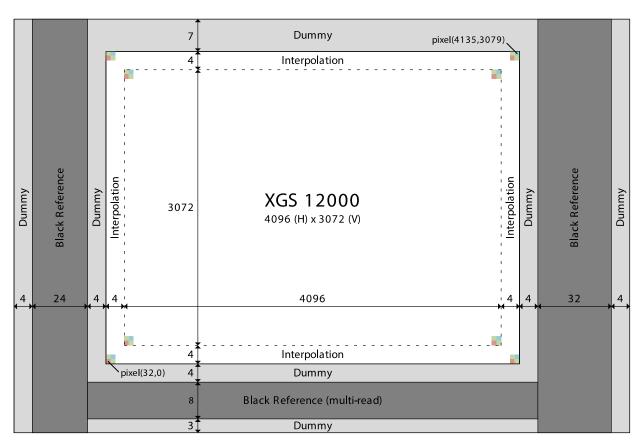

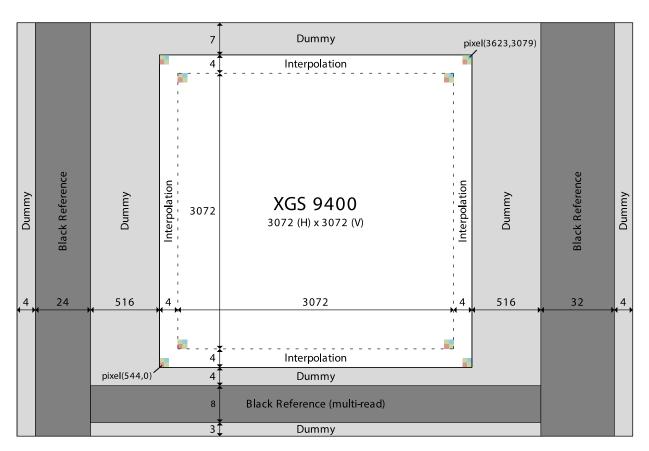

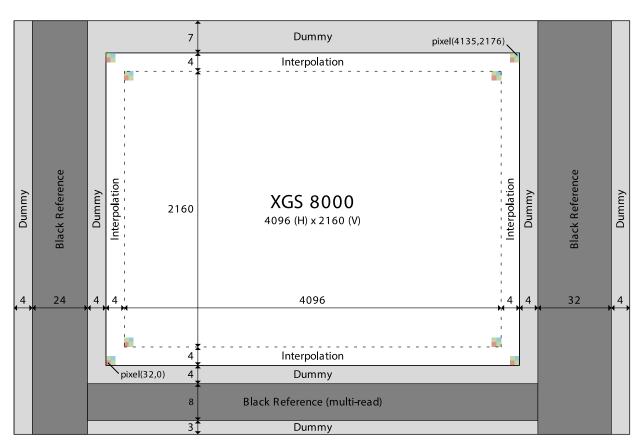

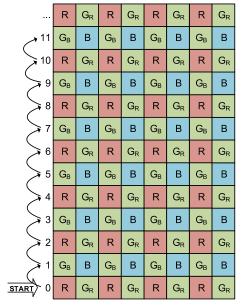

The XGS 12000 active pixel array consists of 4096 columns by 3072 rows of optically active pixels. The active resolution of XGS 8000 and XGS 9600 can be found in Table 1. As shown in Figures 2 through 4, the active array is surrounded by a four–pixel wide collar of interpolation pixels for color interpolation purposes. The entire active array (including interpolation pixels) is isolated from the black reference pixels by a collar of dummy pixels. The purpose of these dummy pixels is to improve the image uniformity within the active area. The complete pixel array, including all dummy, black and interpolation pixels, consists of a total of 4176 columns and 3102 rows (2190 rows for XGS 8000). The sensor's active pixel array is shown with the first pixel in the bottom left corner (refer to Figures 2 through 4).

The color version of the sensor has a Bayer Color Filter Array (CFA) placed on top of the pixels. The mapping of the CFA with respect to the active pixel array is shown in Figure 2 through 4.

#### **PIXEL ARRAY READOUT**

The electrical black reference lines are read out at the start of every frame. The number of lines to be read out is configurable through the M lines configuration

(configurable for each context). The ROI configurations are processed after the black reference lines. The lines accessible through the window configurations are limited to the active area region, including interpolation rows. Note that the windows are configured in logical kernel addresses. A kernel contains four image lines and the kernel with logical address 0 corresponds to the lines with physical addresses:

- 15:18 for XGS 12000 and XGS 9400

- 471:474 for XGS 8000

Each window configuration consists of two parameters: a start address and window height. The configured windows are reordered such that the ROI with the smallest start address is read out first. After completion of the readout of the first ROI, the line address pointer will be initialized to the start address of the next ROI. For overlapping windows, the sequencer will just continue the readout. Note that the overlapping part is read out only once.

Lines are read out from left to right and each line contains different types of pixels. A line starts with 4 dummy pixels followed by 24 electrical black reference pixels. The regular image pixels are preceded and followed by 4 dummy pixels. Dummy pixels are identical to the regular pixels, but may deviate in performance. Therefore the dummy pixels should be discarded. Each line is ended by another 32 black reference pixels followed by 4 dummy pixels.

Figure 2. XGS 12000 Pixel Array

Figure 3. XGS 9400 Pixel Array

Figure 4. XGS 8000 Pixel Array

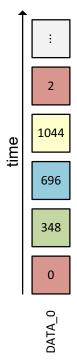

#### Readout Order

Frame readout starts by setting the read address to the first row of the configured ROI. Once the row is read, the read address is incremented and the next row is read. This cycle continues until the last row of the ROI has been read. The incremental addressing scheme is depicted in Figure 5.

Figure 5. Incremental Row Addressing Sequence

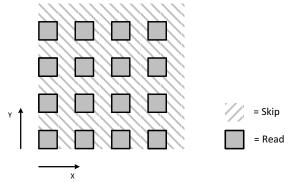

### Subsampled Readout

During subsampled readout only a subset of the pixel array is read out, enabling faster read out with the same field of view but at the expense of reduced image resolution. In order to support subsampling on both monochrome and color sensors, XGS supports two different subsampling schemes:

## 1. Read One Skip One

In this mode, one out of four pixels is selected for readout by selecting every other line and column in the image array. The Read-One-Skip-One mode is depicted in Figure 6 below. This subsampling mode does not preserve the Bayer pattern so it is recommended for monochrome devices only.

Figure 6. Monochrome Subsampling (Read-1-Skip-1)

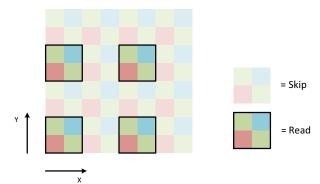

### 2. Read Two Skip Two

The Read-Two-Skip-Two subsampling scheme is recommended for color sensors as it preserves the Bayer pattern. When using the Read-Two-Skip-Two scheme, the sensor first reads two rows and then skips two rows. From each row being read, first two adjacent pixels will be read, then two will be skipped. This readout scheme is depicted in Figure 7.

Figure 7. Color Subsampling (Read-2-Skip-2)

### Reverse Readout

XGS supports reverse readout in the vertical (Y-) direction. If active\_config\_reg.active\_reversed is set to 1, the ROIs will be read top to bottom instead of the default (active\_config\_reg.active\_reversed = 0) bottom to top readout direction.

### **CONFIGURATION AND PINOUT**

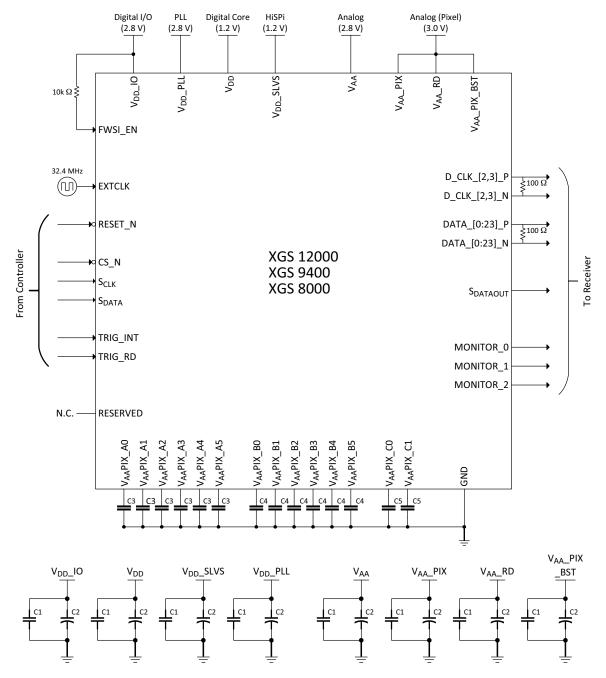

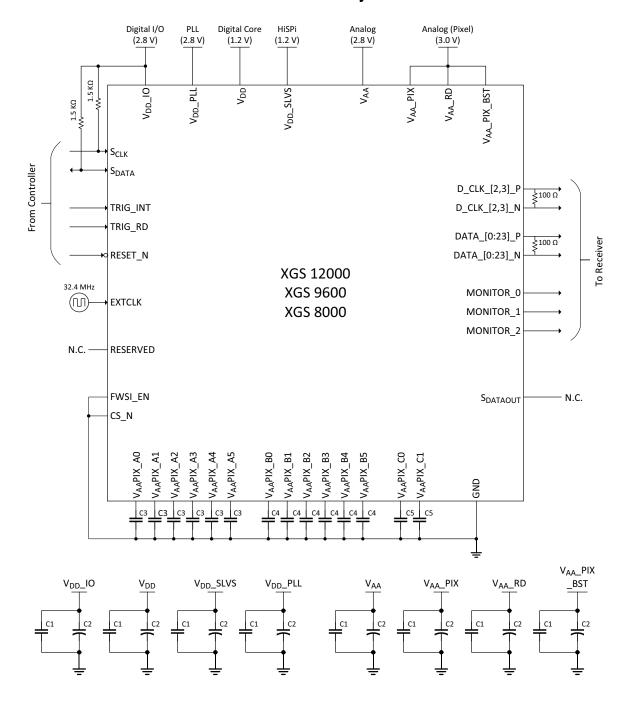

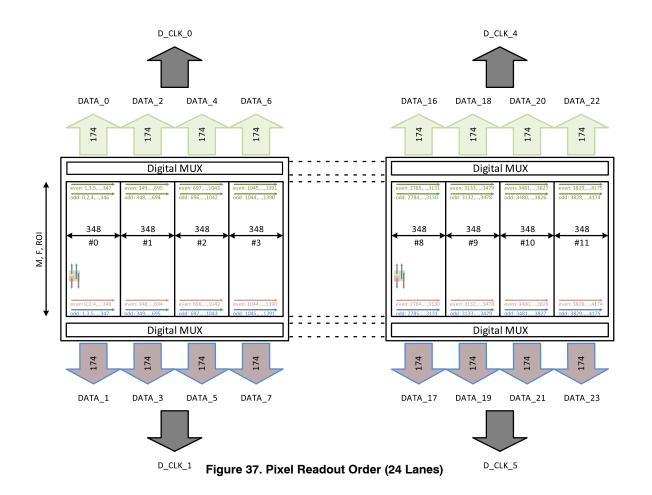

## **TYPICAL CONFIGURATIONS**

Two possible configuration examples are depicted in the figures below. The first example (Figure 8) uses the Four-Wire Serial Interface while the second example (Figure 9) depicts a typical Two-Wire Serial Interface implementation. Pin connections to (and from) the sensor and power supply configurations are shown in the figures

below. The recommended decoupling capacitors are listed in Table 4.

### Configuration Example:

- V<sub>DD</sub>\_SLVS = 1.2 V (or 0.4 V); V<sub>DD</sub> = 1.2 V; V<sub>DD</sub>\_IO = 2.8 V (or 1.8 V); V<sub>DD</sub>\_PLL = 2.8 V;

- V<sub>AA</sub> = 2.8 V; V<sub>AA</sub>\_PIX = 3.0 V; V<sub>AA</sub>\_RD = 3.0 V; V<sub>AA</sub>\_PIX\_BST = 3.0 V

- 24 data lanes + 2 clock lanes

Figure 8. Typical Configuration (Four-Wire Serial Interface)

- 1. All power supplies must be adequately decoupled (see Table 4) Decoupling.

- 2. In this example, only 2 (out of 6) HiSPi clock lanes are used; D\_CLK\_2 to sample data on the even data lanes (top readout) and D\_CLK\_3 to sample data on the odd data lanes (bottom readout).

- 3. The active HiSPi lanes need to be terminated using 100  $\Omega$  resistors placed as close to the receiver as possible.

- 4. Unused HiSPi outputs (data and/or clock lanes) must be left floating.

- 5. It is highly recommended to route the monitor signals to the receiver (FPGA) for debugging purposes. If the MONITOR outputs are not used, they must be left floating.

- 6. If the TRIGGER inputs are not used, tie them to GND.

- 7. No distinction is made between analog and digital ground (internally shorted).

- 8. FWSI\_EN must be connected to V<sub>DD</sub>\_IO through a 10 kΩ resistor (enable Four–Wire Serial Interface).

- 9. I/O signals voltage must be configured to match  $V_{DD}$ \_IO voltage to minimize any leakage currents.

- 10. Digital inputs RESET\_N and CS\_N are both active low.

Figure 9. Typical Configuration (Two-Wire Serial Interface)

- 1. All power supplies must be adequately decoupled (see Table 4) Decoupling.

- 2. In this example, only 2 (out of 6) HiSPi clock lanes are used; D\_CLK\_2 to sample data on the even data lanes (top readout) and D\_CLK\_3 to sample data on the odd data lanes (bottom readout).

- 3. The active HiSPi lanes need to be terminated using 100  $\Omega$  resistors placed as close to the receiver as possible.

- 4. Unused HiSPi outputs (data and/or clock lanes) must be left floating.

- 5. It is highly recommended to route the monitor signals to the receiver (FPGA) for debugging purposes. If the MONITOR outputs are not used, they must be left floating.

- 6. If the TRIGGER inputs are not used, tie them to GND.

- 7. No distinction is made between analog and digital ground (internally shorted).

- 8. FWSI\_EN and CS\_N must be tied to GND when using the Two-Wire Serial Interface. S<sub>dataout</sub> can be left floating.

- 9. I/O signals voltage must be configured to match V<sub>DD</sub>IO voltage to minimize any leakage currents.

- 10. Digital input RESET\_N is active low.

- 11. ON Semiconductor recommends using a 1.5 k $\Omega$  pull-up resistor to  $V_{DD}$ IO on both Sclk and Sdata.

**Table 4. DECOUPLING RECOMMENDATIONS**

| Capacitor | Recommended Capacitor Value (μF) | Capacitor | Recommended Capacitor Value (μF) |

|-----------|----------------------------------|-----------|----------------------------------|

| C1, C5    | 0.1                              | СЗ        | 0.1 + 4.7                        |

| C2        | 10                               | C4        | 0.1 + 2.2                        |

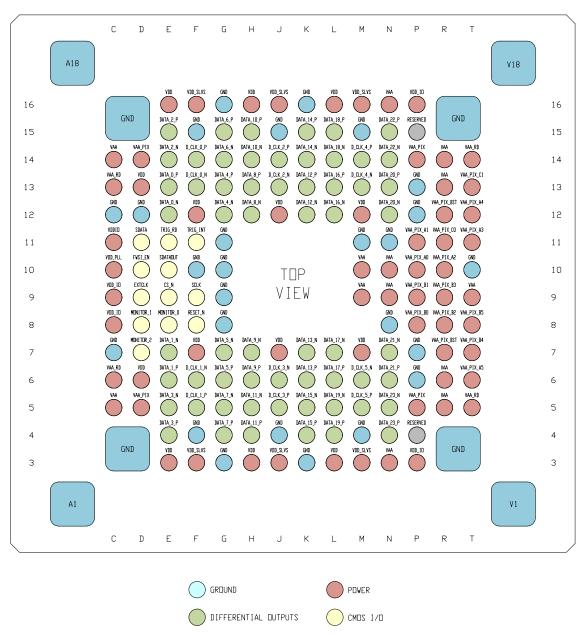

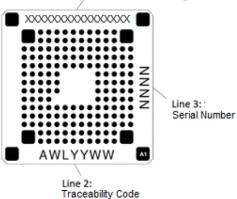

## **PINOUT**

Figure 10. XGS CLGA Package Pinout (Top View; Pads Down)

# **PIN LIST**

Table 5. PIN DESCRIPTIONS (163-PIN LGA PACKAGE)

| Name                  | LGA Pin Name                                                                                                                                              | Type             | Description                                                                                                                  |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------|

| GND                   | A1, A18, C3, C7, C12, C16, F4, F15, G3, G16, J4, J15, K3, K16, M4, M11, M15, N8, N11, P7, P12, T3, T10, T16, V1, V18, D12, F10, G8, G9, G10, G11, P6, P13 | Ground           | Ground                                                                                                                       |

| V <sub>DD</sub> _PLL  | C10                                                                                                                                                       | Power            | PLL Power Supply                                                                                                             |

| V <sub>AA</sub>       | C5, C14, M9, M10, N3, N9, N10, N16,<br>R5, R6, R13, R14, T9                                                                                               | Power            | Analog Supply                                                                                                                |

| V <sub>AA</sub> _RD   | C6, C13, T5, T14                                                                                                                                          | Power            | Analog Supply for Row Driver                                                                                                 |

| V <sub>DD</sub> _IO   | C8, C9, C11, P3, P16                                                                                                                                      | Power            | I/O Supply                                                                                                                   |

| FWSI_EN               | D10                                                                                                                                                       | Input            | 'HIGH' -> Four-Wire Serial Interface (SPI) 'LOW' -> Two-Wire Serial Interface (I <sup>2</sup> C)                             |

| S <sub>DATA</sub>     | D11                                                                                                                                                       | Input/<br>Output | Four-Wire Serial Interface (SPI): SPI Slave In<br>Two-Wire Serial Interface (I <sup>2</sup> C): Serial Data Input/<br>Output |

| V <sub>AA</sub> _PIX  | D5, D14, P5, P14                                                                                                                                          | Power            | Pixel Supply                                                                                                                 |

| $V_{DD}$              | D6, D13, E3, E16, F7, F12, H3, H16, J7, J12, L3, L16, M7, M12                                                                                             | Power            | Digital Supply                                                                                                               |

| MONITOR_2             | D7                                                                                                                                                        | Output           | Monitor Output 2. If unused, do not connect.                                                                                 |

| MONITOR_1             | D8                                                                                                                                                        | Output           | Monitor Output 1. If unused, do not connect.                                                                                 |

| EXTCLK                | D9                                                                                                                                                        | Input            | External Clock Input                                                                                                         |

| S <sub>DATAOUT</sub>  | E10                                                                                                                                                       | Output           | Four-Wire Serial Interface (SPI): SPI Slave Out Two-Wire Serial Interface (I <sup>2</sup> C): Do not connect                 |

| TRIG_RD               | E11                                                                                                                                                       | Input            | Trigger Input for Readout Control. If unused, connect to ground.                                                             |

| DATA_0_N              | E12                                                                                                                                                       | HiSPi            | Differential Data Channel [0], Negative                                                                                      |

| DATA_0_P              | E13                                                                                                                                                       | HiSPi            | Differential Data Channel [0], Positive                                                                                      |

| DATA_2_N              | E14                                                                                                                                                       | HiSPi            | Differential Data Channel [2], Negative                                                                                      |

| DATA_2_P              | E15                                                                                                                                                       | HiSPi            | Differential Data Channel [2], Positive                                                                                      |

| DATA_3_P              | E4                                                                                                                                                        | HiSPi            | Differential Data Channel [3], Positive                                                                                      |

| DATA_3_N              | E5                                                                                                                                                        | HiSPi            | Differential Data Channel [3], Negative                                                                                      |

| DATA_1_P              | E6                                                                                                                                                        | HiSPi            | Differential Data Channel [1], Positive                                                                                      |

| DATA_1_N              | E7                                                                                                                                                        | HiSPi            | Differential Data Channel [1], Negative                                                                                      |

| MONITOR_0             | E8                                                                                                                                                        | Output           | Monitor Output 0. If unused do not connect.                                                                                  |

| CS_N                  | E9                                                                                                                                                        | Input            | Four-Wire Serial Interface (SPI): SPI Chip Select (active low) Two-Wire Serial Interface (I <sup>2</sup> C): Connect to GND  |

| TRIG_INT              | F11                                                                                                                                                       | Input            | Trigger Input for Integration Control. If unused, connect to ground.                                                         |

| D_CLK_0_N             | F13                                                                                                                                                       | HiSPi            | Differential Clock [0], Negative                                                                                             |

| D_CLK_0_P             | F14                                                                                                                                                       | HiSPi            | Differential Clock [0], Positive                                                                                             |

| V <sub>DD</sub> _SLVS | F3, F16, J3, J16, M3, M16                                                                                                                                 | Power            | HiSPi Supply                                                                                                                 |

| D_CLK_1_P             | F5                                                                                                                                                        | HiSPi            | Differential Clock [1], Positive                                                                                             |

| D_CLK_1_N             | F6                                                                                                                                                        | HiSPi            | Differential Clock [1], Negative                                                                                             |

| RESET_N               | F8                                                                                                                                                        | Input            | Asynchronous Hard Reset (Active Low)                                                                                         |

| S <sub>CLK</sub>      | F9                                                                                                                                                        | Input            | Serial Interface Clock Input                                                                                                 |

Table 5. PIN DESCRIPTIONS (163-PIN LGA PACKAGE)

| Name      | LGA Pin Name | Type  | Description                              |

|-----------|--------------|-------|------------------------------------------|

| DATA_4_N  | G12          | HiSPi | Differential Data Channel [4], Negative  |

| DATA_4_P  | G13          | HiSPi | Differential Data Channel [4], Positive  |

| DATA_6_N  | G14          | HiSPi | Differential Data Channel [6], Negative  |

| DATA_6_P  | G15          | HiSPi | Differential Data Channel [6], Positive  |

| DATA_7_P  | G4           | HiSPi | Differential Data Channel [7], Positive  |

| DATA_7_N  | G5           | HiSPi | Differential Data Channel [7], Negative  |

| DATA_5_P  | G6           | HiSPi | Differential Data Channel [5], Positive  |

| DATA_5_N  | G7           | HiSPi | Differential Data Channel [5], Negative  |

| DATA_8_N  | H12          | HiSPi | Differential Data Channel [8], Negative  |

| DATA_8_P  | H13          | HiSPi | Differential Data Channel [8], Positive  |

| DATA_10_N | H14          | HiSPi | Differential Data Channel [10], Negative |

| DATA_10_P | H15          | HiSPi | Differential Data Channel [10], Positive |

| DATA_11_P | H4           | HiSPi | Differential Data Channel [11], Positive |

| DATA_11_N | H5           | HiSPi | Differential Data Channel [11], Negative |

| DATA_9_P  | H6           | HiSPi | Differential Data Channel [9], Positive  |

| DATA_9_N  | H7           | HiSPi | Differential Data Channel [9], Negative  |

| D_CLK_2_N | J13          | HiSPi | Differential Clock [2], Negative         |

| D_CLK_2_P | J14          | HiSPi | Differential Clock [2], Positive         |

| D_CLK_3_P | J5           | HiSPi | Differential Clock [3], Positive         |

| D_CLK_3_N | J6           | HiSPi | Differential Clock [3], Negative         |

| DATA_12_N | K12          | HiSPi | Differential Data Channel [12], Negative |

| DATA_12_P | K13          | HiSPi | Differential Data Channel [12], Positive |

| DATA_14_N | K14          | HiSPi | Differential Data Channel [14], Negative |

| DATA_14_P | K15          | HiSPi | Differential Data Channel [14], Positive |

| DATA_15_P | K4           | HiSPi | Differential Data Channel [15], Positive |

| DATA_15_N | K5           | HiSPi | Differential Data Channel [15], Negative |

| DATA_13_P | K6           | HiSPi | Differential Data Channel [13], Positive |

| DATA_13_N | K7           | HiSPi | Differential Data Channel [13], Negative |

| DATA_16_N | L12          | HiSPi | Differential Data Channel [16], Negative |

| DATA_16_P | L13          | HiSPi | Differential Data Channel [16], Positive |

| DATA_18_N | L14          | HiSPi | Differential Data Channel [18], Negative |

| DATA_18_P | L15          | HiSPi | Differential Data Channel [18], Positive |

| DATA_19_P | L4           | HiSPi | Differential Data Channel [19], Positive |

| DATA_19_N | L5           | HiSPi | Differential Data Channel [19], Negative |

| DATA_17_P | L6           | HiSPi | Differential Data Channel [17], Positive |

| DATA_17_N | L7           | HiSPi | Differential Data Channel [17], Negative |

| D_CLK_4_N | M13          | HiSPi | Differential Clock [4], Negative         |

| D_CLK_4_P | M14          | HiSPi | Differential Clock [4], Positive         |

| D_CLK_5_P | M5           | HiSPi | Differential Clock [5], Positive         |

| D_CLK_5_N | M6           | HiSPi | Differential Clock [5], Negative         |

| DATA_20_N | N12          | HiSPi | Differential Data Channel [20], Negative |

| DATA_20_P | N13          | HiSPi | Differential Data Channel [20], Positive |

Table 5. PIN DESCRIPTIONS (163-PIN LGA PACKAGE)

| Name                     | LGA Pin Name | Type       | Description                                        |

|--------------------------|--------------|------------|----------------------------------------------------|

| DATA_22_N                | N14          | HiSPi      | Differential Data Channel [22], Negative           |

| DATA_22_P                | N15          | HiSPi      | Differential Data Channel [22], Positive           |

| DATA_23_P                | N4           | HiSPi      | Differential Data Channel [23], Positive           |

| DATA_23_N                | N5           | HiSPi      | Differential Data Channel [23], Negative           |

| DATA_21_P                | N6           | HiSPi      | Differential Data Channel [21], Positive           |

| DATA_21_N                | N7           | HiSPi      | Differential Data Channel [21], Negative           |

| V <sub>AA</sub> _PIX_A0  | P10          | Decoupling | External Noise Decoupling (0.1 μF + 4.7 μF to GND) |

| V <sub>AA</sub> _PIX_A1  | P11          | Decoupling | External Noise Decoupling (0.1 μF + 4.7 μF to GND) |

| V <sub>AA</sub> _PIX_A2  | R10          | Decoupling | External Noise Decoupling (0.1 μF + 4.7 μF to GND) |

| V <sub>AA</sub> _PIX_A3  | T11          | Decoupling | External Noise Decoupling (0.1 μF + 4.7 μF to GND) |

| V <sub>AA</sub> _PIX_A4  | T12          | Decoupling | External Noise Decoupling (0.1 μF + 4.7 μF to GND) |

| V <sub>AA</sub> _PIX_A5  | T6           | Decoupling | External Noise Decoupling (0.1 μF + 4.7 μF to GND) |

| V <sub>AA</sub> _PIX_B0  | P8           | Decoupling | External Noise Decoupling (0.1 μF + 2.2 μF to GND) |

| V <sub>AA</sub> _PIX_B1  | P9           | Decoupling | External Noise Decoupling (0.1 μF + 2.2 μF to GND) |

| V <sub>AA</sub> _PIX_B2  | R8           | Decoupling | External Noise Decoupling (0.1 μF + 2.2 μF to GND) |

| V <sub>AA</sub> _PIX_B3  | R9           | Decoupling | External Noise Decoupling (0.1 μF + 2.2 μF to GND) |

| V <sub>AA</sub> _PIX_B4  | Т7           | Decoupling | External Noise Decoupling (0.1 μF + 2.2 μF to GND) |

| V <sub>AA</sub> _PIX_B5  | Т8           | Decoupling | External Noise Decoupling (0.1 μF + 2.2 μF to GND) |

| V <sub>AA</sub> _PIX_C0  | R11          | Decoupling | External Noise Decoupling (0.1 μF to GND)          |

| V <sub>AA</sub> _PIX_C1  | T13          | Decoupling | External Noise Decoupling (0.1 μF to GND)          |

| V <sub>AA</sub> _PIX_BST | R7, R12      | Power      | Pixel Booster Supply                               |

| RESERVED                 | P4, P15      | N/A        | Reserved (do not connect)                          |

#### **SENSOR STATES**

After Power-Up and while the RESET\_N pin is driven low, the image sensor enters a RESET state until the RESET N signal is de-asserted.

Once the RESET\_N pin is driven high, the sensor will start loading the default configuration, stored in the on–chip memory, into its configuration registers before it enters the SLEEP state. While the sensor is in the SLEEP state, the registers can be programmed using the serial interface. To exit the SLEEP state and enter STANDBY mode, the reset\_register\_reg (R0x3700) needs to be set to 0x001C. This register upload enables all analog blocks (including the on–chip PLL) and soon as the sensor\_status\_reg (R0x3706) returns value 0xEB, the sensor is in STANDBY state.

When in STANDBY mode and upon user intervention the training patterns or IDLE words can be sent over the video interface allowing receiver locking. Once the host is ready to receive image data, the sensor's sequencer can be enabled. Depending on the configured operation mode, the sensor will either wait for user interaction or start grabbing images autonomously (CAPTURE). Disabling the sequencer moves the sensor state back to STANDBY. When disabling the PLL and analog blocks while in STANDBY state, the state machine will transition back to the SLEEP state. Asserting the RESET\_N pin forces the sensor to enter the RESET state, regardless of the current state.

The sensor state diagram is shown in Figure 11.

Figure 11. Sensor State Diagram

**Table 6. TYPICAL TRANSITION TIMES**

| Sensor State    | Transition Time                                     | Description                                                                                                                        |

|-----------------|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| POWER-DOWN      | 25 ms                                               | Time required to transition from POWER-DOWN to CAPTURE state.                                                                      |

| SLEEP           | 10 ms                                               | Time required to transition from SLEEP to CAPTURE state.                                                                           |

| STANDBY         | < 16 line times                                     | Time required to transition from STANDBY to CAPTURE state.                                                                         |

| WAIT_ON_TRIGGER | 2 line times + Synchroniza-<br>tion Delay (< 50 ns) | Time required to transition from WAIT_ON_TRIGGER to CAPTURE (upon trigger action). A minimum delay of one line time will be added. |

<sup>\*</sup>The sleep mode functionality is not available on XGS12M. Please use the standby mode when the sensor is idle. Technical details on this issue can be found in the developer guide.

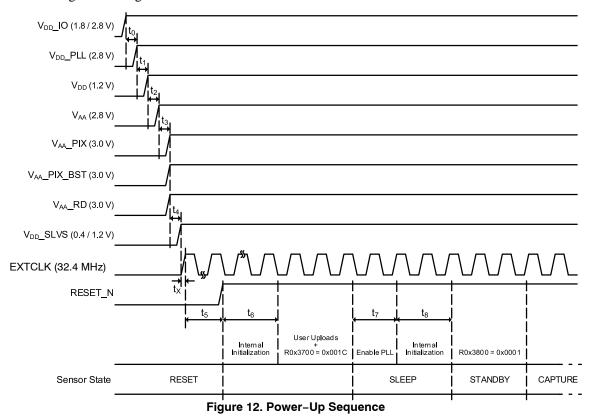

# POWER-UP AND POWER-DOWN SEQUENCE POWER-UP SEQUENCE

The recommended Power-Up sequence for the XGS sensor is shown in Figure 12. The available power supplies ( $V_{DD}$ \_IO,  $V_{DD}$ \_PLL,  $V_{DD}$ ,  $V_{AA}$ ,  $V_{AA}$ \_PIX,  $V_{AA}$ \_PIX\_BST,  $V_{AA}$ \_RD and  $V_{DD}$ \_SLVS) must have the separation specified below.

- 1. Turn on V<sub>DD</sub>\_IO power supply.

- 2. After 0–100 μs, turn on V<sub>DD</sub>\_PLL power supply.

- 3. After  $0-100 \mu s$ , turn on  $V_{DD}$  power supply.

- 4. After 0–100  $\mu$ s, turn on  $V_{AA}$  power supply.

- 5. Once  $V_{AA}$  is stable, power up  $V_{AA}$ \_PIX,  $V_{AA}$ \_PIX\_BST and  $V_{AA}$ \_RD.

- Once V<sub>AA</sub>\_PIX, V<sub>AA</sub>\_PIX\_BST and V<sub>AA</sub>\_RD are stable, power up V<sub>DD</sub>\_SLVS.

- 7. After V<sub>DD</sub> SLVS is stable, enable EXTCLK.

- 8. After EXTCLK has settled, hold RESET\_N low (active) for at least 30 EXTCLK cycles before de-asserting the reset signal.

- 9. The sensor then loads the default register values from its on-chip memory. As soon as RESET\_N is pulled up (released), the sensor starts loading the default register values from it internal memory. When loading is done (sensor\_status\_reg R0x3706 -> 0xEB), the sensor is ready to accept user uploads. the sensor is ready to accept user uploads (e.g. to configure a special mode).

- 10. Enable PLL and initialize sensor's internal analog blocks (reset\_register\_reg = 0x001C).

- 11. Once the analog blocks are initialized, the sensor transitions to STANDBY state and is ready to start image operations.

- 12. Enable the sequencer to transition to the CAPTURE state (*general config0 reg[0] = 1*).

Table 7. POWER-UP SEQUENCE

| Symbol         | Definition                                                                                 | Min           | Тур            | Max | Unit          |

|----------------|--------------------------------------------------------------------------------------------|---------------|----------------|-----|---------------|

| t <sub>0</sub> | V <sub>DD</sub> _IO to V <sub>DD</sub> _PLL                                                | 0<br>(Note 5) | 100            |     | μs            |

| t <sub>1</sub> | V <sub>DD</sub> _PLL to V <sub>DD</sub>                                                    | 0<br>(Note 5) | 100            |     | μs            |

| t <sub>2</sub> | V <sub>DD</sub> to V <sub>AA</sub>                                                         | 0<br>(Note 5) | 100            |     | μs            |

| t <sub>3</sub> | V <sub>AA</sub> to V <sub>AA</sub> _PIX/V <sub>AA</sub> _PIX_BST/V <sub>AA</sub> _RD       | 0<br>(Note 5) | 100            |     | μs            |

| t <sub>4</sub> | V <sub>AA</sub> _PIX/V <sub>AA</sub> _PIX_BST/V <sub>AA</sub> _RD to V <sub>DD</sub> _SLVS | 0<br>(Note 5) | 100            |     | μs            |

| t <sub>X</sub> | EXTCLK Settling Time                                                                       | 0.5           | 30<br>(Note 4) |     | ms            |

| t <sub>5</sub> | Hard Reset                                                                                 | 30            |                |     | EXTCLK cycles |

| t <sub>6</sub> | Internal Initialization (ready once R0x3706 reads back 0xEB)                               | 1.5           |                |     | ms            |

| t <sub>7</sub> | PLL Lock Time                                                                              | 10            | 70             |     | μs            |

| t <sub>8</sub> | Internal Initialization                                                                    |               | 6.5            |     | ms            |

The EXTCLK settling time is component-dependent.

The minimum time does not include the settling time of the power supply.

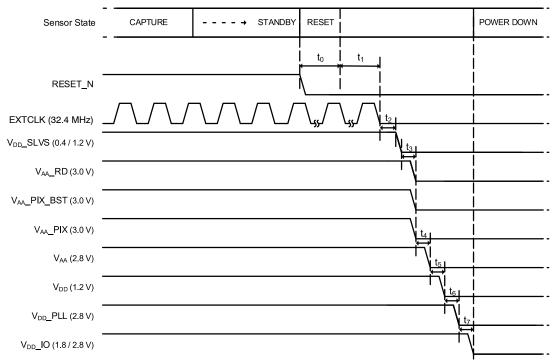

### **POWER-DOWN SEQUENCE**

The recommended Power–Down sequence for the XGS sensor is shown in Figure 13. The available power supplies must have the separation specified below.

- 1. Disable CAPTURE if output is active by disabling the sequencer (general\_config0\_reg[0] = 0).

- 2. Issue a sensor STANDBY request (reset\_register\_reg[2] = 0). By default, the transition to STANDBY state happens either after completion of current row (or frame) readout or instantly (configurable).

- In STANDBY mode, activate reset by pulling down the RESET\_N line for at least 30 EXTCLKs.

- 4. EXTCLK can be stopped 0.5 ms after RESET\_N.

- 5. Turn off power supplies one by one. Wait at least until the supplies are stable before turning off the next supply. (reverse order of Power–Up Sequence).

Figure 13. Power-Down Sequence

#### Table 8. POWER-DOWN SEQUENCE

| Symbol         | Definition                                                                                     | Min        | Тур | Max | Unit          |

|----------------|------------------------------------------------------------------------------------------------|------------|-----|-----|---------------|

| t <sub>0</sub> | Hard Reset                                                                                     | 30         |     |     | EXTCLK cycles |

| t <sub>1</sub> | Reset to Disable EXTCLK                                                                        | 0.5        |     |     | ms            |

| t <sub>2</sub> | V <sub>AA</sub> _RD / V <sub>AA</sub> _PIX_BST / V <sub>AA</sub> _PIX to V <sub>AA</sub>       | 0 (Note 6) |     |     | μs            |

| t <sub>3</sub> | V <sub>DD</sub> _SLVS to V <sub>AA</sub> _RD / V <sub>AA</sub> _PIX_BST / V <sub>AA</sub> _PIX | 0 (Note 6) |     |     | μs            |

| t <sub>4</sub> | V <sub>AA</sub> _RD / V <sub>AA</sub> _PIX_BST / V <sub>AA</sub> _PIX to V <sub>AA</sub>       | 0 (Note 6) |     |     | μs            |

| t <sub>5</sub> | V <sub>AA</sub> to V <sub>DD</sub>                                                             | 0 (Note 6) |     |     | μs            |

| t <sub>6</sub> | V <sub>DD</sub> to V <sub>DD</sub> _PLL                                                        | 0 (Note 6) |     |     | μs            |

| t <sub>7</sub> | V <sub>DD</sub> _PLL to V <sub>DD</sub> _IO                                                    | 0 (Note 6) |     |     | μs            |

6. The minimum time does not include the settling time of the power supply.

#### **INTEGRATION MODES**

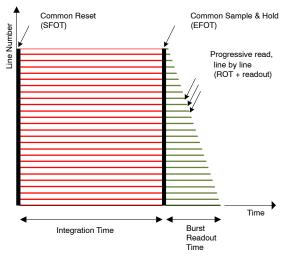

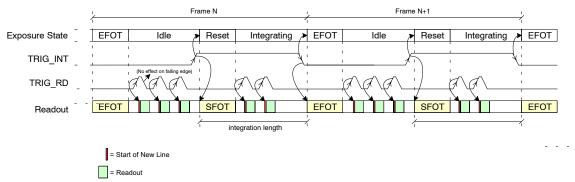

In a global shutter sensor, light integration takes place on all pixels in parallel, although subsequent readout is sequential. Figure 14 shows the integration and readout sequence for the global shutter. All pixels are light sensitive during the same period of time.

Figure 14. Global Shutter Operation

The whole pixel core is reset simultaneously and after the integration time all pixel values are sampled at the same time on the storage node inside each pixel. The pixel core is read out line by line after integration. Note that Figure 14 shows a configuration where integration and readout operations are not pipelined. In a pipelined configuration, integration and readout are performed simultaneously.

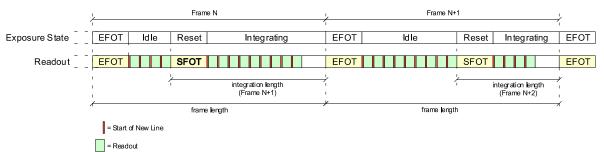

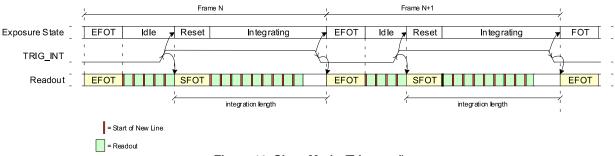

#### Pipelined Global Shutter Mode

In pipelined shutter mode, the integration and readout are active concurrently. Images are continuously read and integration of frame N is ongoing during readout of the previous frame N-1. The readout of every frame starts with a Frame Overhead time (EFOT), during which the analog value on the pixel diode is transferred to the pixel memory element. After the Frame Overhead Time, the sensor is read out line per line. Image array operations and readout are pipelined. The image array operations are performed in the Row Overhead Time (ROT). During the ROT sequence, an image row is selected for readout.

At the start of the integration the sequencer schedules another global operation on the pixel array. This sequence is referred to as Start of integration frame overhead sequence (SFOT). During this SFOT, the readout shall be halted temporarily.

### **MASTER MODE (NON-TRIGGERED)**

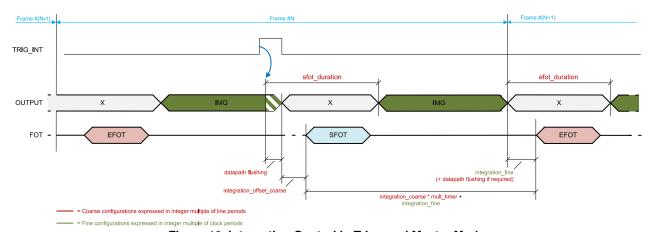

Figure 15. Master Mode (non-Triggered)

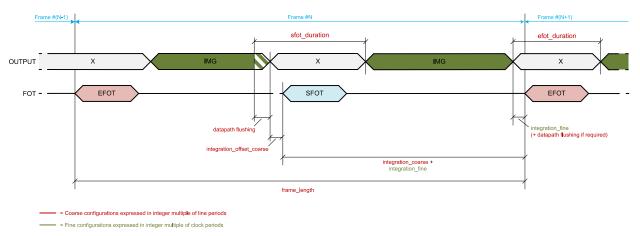

In this operation mode, the integration time is set through the register interface and the sensor integrates and reads out the images autonomously. The sensor acquires images without any user interaction as shown in Figure 15.

On a high level, the frame time consists of a non-integrating time and integration time (during which the pixels are light sensitive and integrating light). The sum of both parameters is the frame time, which is configured in multiple of line periods. Within this total frame time, the Sequencer schedules the frame operations required to initiate and terminate the light integration. The integration period is started with a Start-of-Integration FOT (SFOT) sequence and is ended with an End-of-Integration FOT (EFOT) sequence. Note that both SFOT and EFOT operations take some time during which the readout will be halted. This will be reflected in an idle period on the sensor's interface. The parameters defining the frame and integration properties are listed in Table 9 below.

**Table 9. INTEGRATION AND FRAME TIMING PARAMETERS**

| Name                      | Description                                                                                                                                                                                                                                                                                                                                                                     |

|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| line_time                 | Duration of one line, expressed in logic clock cycles.  The minimum line time shall be dictated by the A/D conversion time and readout time (whichever is larger).                                                                                                                                                                                                              |

| frame_length              | Defines the total frame time as frame_length * line_time logic clock periods. This parameter needs to be configured large enough such that both the integration control operations (i.e. SFOT, EFOT and configured integration time) and the readout operations (ROI readout + black lines) can happen.                                                                         |

| integration_coarse        | Defines the coarse part of the integration time. Total integration time in logic clock periods is integration_coarse * line_time + integration_fine                                                                                                                                                                                                                             |

| integration_fine          | Defines the fine part of the integration time. Total integration time in logic clock periods is integration_coarse * line_time + integration_fine                                                                                                                                                                                                                               |

| integration_offset_coarse | Offset between the Sequencer induced SFOT period and the start of the SFOT, expressed in line periods.  The total integration offset time, expressed in logic clock cycles, is defined as (integration_offset_coarse + overhead) * line_time.  This parameter allows to increase the latency between a trigger event and the effective start of integration in triggered modes. |

The frame parameters and their relations are depicted in Figure 16 below. Note that the green area depicts the readout of regular lines (black reference / ROI defined image lines), while the grey area represents the access to dummy lines (no image data). The shaded green part represents the line

periods during which the control and datapath pipeline is flushed.

$\label{eq:minimum} \mbox{Minimum integration time limitations are listed in Table 10.}$

Figure 16. Frame Timing and Exposure Parameters

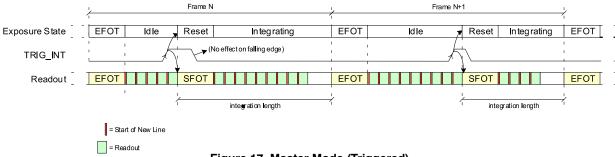

# **MASTER MODE (TRIGGERED)**

Figure 17. Master Mode (Triggered)

In Triggered Master Mode, a rising edge on the TRIG\_INT pin is used to trigger the start of integration as shown in Figure 17. The integration time is defined by register configuration (integration\_coarse, integration\_fine). The sensor shall autonomously integrate during this predefined time, after which the EFOT operation starts and the image array is read out sequentially. A falling

edge on the synchronization pin does not have any impact on the readout or integration and subsequent frames are started again for each rising edge.

Figure 18 below shows the pipelined operation in triggered master mode (i.e. trigger assertion during frame readout).

Figure 18. Integration Control in Triggered Master Mode

Note that each trigger reads out only one image.

The latency between a trigger event and the start of the SFOT operation is constant and predictable. It is defined by the coarse offset configuration + overhead.

### NOTES:

- The trigger is an asynchronous signal which is synchronized in the SCU. As a consequence, synchronization jitter can be observed.

- The polarity of the TRIG\_INT pin is controlled by trig\_int\_polarity. The operation described above corresponds to trig\_int\_polarity = '0'.

- The response time between a rising edge of TRIG\_INT and the start of integration is fixed, besides the synchronization uncertainty and jitter.

The following register is not used in this mode and has no influence (implicitly defined by the trigger):

• frame\_length

Minimum integration time limitations are listed in Table 10.

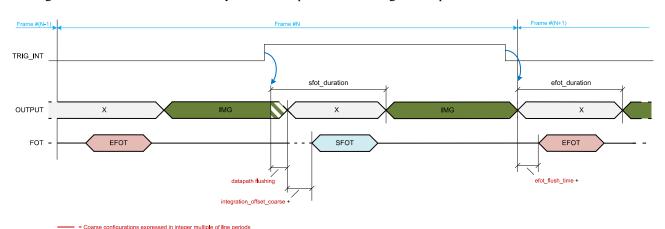

### **SLAVE MODE (TRIGGERED)**

Figure 19. Slave Mode (Triggered)

The slave mode depicted in Figure 19 adds more manual control to the sensor. The integration time registers (*frame\_length* and *integration*) are ignored in this mode and the integration time is rather controlled by an external pin.

As soon as the control pin is asserted, the Sequencer schedules the SFOT operations. The integration continues until the external pin is deasserted by the user/system. Now, the image is sampled and the readout is initiated.

Figure 20. Integration Control in Slave Mode (Triggered)

The latency between the trigger events and the SFOT/EFOT operations respectively is fixed and predictable. The latency between a trigger assertion and the SFOT operation is controlled through integration\_offset\_coarse.

### NOTES:

- The trigger is an asynchronous signal which is synchronized in the Sequencer. As a consequence, synchronization jitter can be observed.

- The response time between a TRIG\_INT event and the start/end of integration shall be constant, besides the synchronization uncertainty and jitter.

- The following registers are not used in this mode and do not have any influence (implicitly defined by the trigger):

- integration coarse,

- integration fine,

- frame length

Minimum integration time limitations are listed in Table 10 below.

# Table 10. MINIMUM INTEGRATION TIME LIMITATIONS (Note 7)

|                        | Minimum Integrati           | on Time (in μs) |

|------------------------|-----------------------------|-----------------|

| Number of Output Lanes | Short Integration<br>Config | Default Config  |

| 6                      | 10                          | 60              |

| 12                     | 10                          | 30              |

| 24                     | 10                          | 20              |

<sup>7.</sup> The minimum integration time depends on the configured line time. The values in this table assume the minimum recommended line time is used.

<sup>8.</sup> Refer to the XGS 12000 Developer Guide for more information on the minimum integration times.

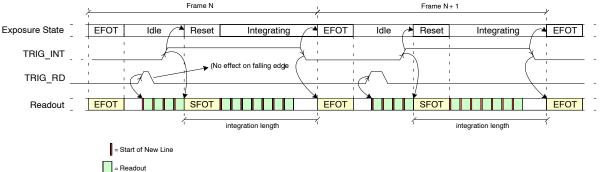

#### **READOUT MODES**

By default, the readout of the pixel array does not require any user interaction. The sequencer initiates the readout as soon as integration ends and the entire readout is done autonomously. This is the default readout mode. Optionally, the frame readout can be controlled externally. This requires configuring the TRIG\_RD input as a frame or line trigger. Table 11 below lists the parameters that control the triggered readout operation.

**Table 11. TRIGGERED READOUT PARAMETERS**

| Register Name      | Description                                                                                                                                                                                                                              |  |  |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| frame_trigger_en   | Start the frame readout upon assertion of TRIG_RD when enabled. This configuration has priority over line_trigger_en.                                                                                                                    |  |  |

| frame_trigger_mode | Only valid for frame triggered readout modes.  '0': Regular frame triggered mode: The sensor starts the readout of one frame upon a rising trigger edge  '1': The sequencer continues frame grabbing as long as the trigger is asserted. |  |  |

| line_trigger_en    | Start the readout of one line upon assertion of TRIG_RD when enabled. Only one line is read out for each trigger assertion.                                                                                                              |  |  |

Note that *contexts\_reg.frames* determines how many frames can be read out. This implies that the sequencer will not accept any new trigger once the number of

*contexts\_reg.frames* have been read out. If this is not desired, frames should be configured to 0.

#### FRAME TRIGGERED READOUT

Figure 21. Frame Triggered Readout Mode

XGS 12000 supports two frame triggered readout options, configurable in the *frame\_trigger\_mode* register (refer to Table 11).

frame trigger mode = 0

In a global shutter mode, the integration is ended by the EFOT. In a non-triggered readout mode, the readout is initiated automatically after the EFOT operations. In frame triggered mode, the Sequencer will not start the readout, but instead it waits until the frame-trigger gets asserted. Once an event (rising of falling depending on the configured polarity) is detected the readout starts and the image is read out line after line.

Note that the trigger assertion is latched and served at the first coming internal new line reference (internal time base). As a consequence one may observe a trigger latency up to a line time.

Frame triggered readout can be combined with triggered integration modes.

$frame\_trigger\_mode = 1$

In this mode, the trigger acts as an external sequencer enable signal. An event (rising or falling depending on the configured polarity) starts the frame readout. After this first frame, the sequencer continues running, cycling through the active contexts, if more than one context is enabled. The end condition depends on the value given in *contexts\_reg.frames*:

- contexts\_reg.frames > 0: The Sequencer continues running and reads out the given amount of frames, after which it returns to the WAIT\_ON\_TRIGGER state. After the readout, the sequencer is waiting for another trigger, after which a new sequence is initiated. Note that a new batch of frames shall be read out in case the trigger is asserted at the end of the previous batch.

- contexts\_reg.frames = 0: The Sequencer continues running as long as the TRIG\_RD is asserted. Once the trigger is deasserted, the Sequencer returns to the

WAIT\_ON\_TRIGGER state, in which it is ready to accept a new trigger event.

Note that this mode is available for both triggered and non-triggered global shutter modes and it can be combined with the use of multiple contexts. When using multiple contexts it is also possible to configure the number of desired frames per context. The sequencer cycles through the active contexts and generates as many frames as configured per context. When retriggered, the sequencer reinitializes the frame properties and starts the readout from a fresh state (i.e. does not continue from where it ended in the previous batch).

### **LINE TRIGGERED READOUT**

Figure 22. Line Triggered Readout

The line triggered readout mode is enabled when line\_trigger\_en is asserted and frame\_trigger\_en is deasserted. The line triggered readout mode is comparable to frame triggered readout, but in this mode only one line is read out for each trigger. Note that a trigger is latched and interpreted during the following line period if the sensor is retriggered during readout.

Line triggered readout is to be used in conjunction with triggered integration modes.

#### **Features Overview**

The XGS family has a wide array of features to enhance functionality or to increase versatility. A summary of features follows.

### RESET

The RESET\_N input (pin F8) is an active low control input for asynchronous hard reset. During the power-up period, RESET\_N must be asserted, then must be deasserted after the power supplies are settled. The minimum RESET N assert time is 30 EXTCLK cycles.

### **MONITOR OUTPUTS**

The XGS sequencer provides three monitor outputs (pins E8, D8 and D7) which can be used to monitor the internal states of the sequencer. The monitor signals can be configured separately for each monitor output.

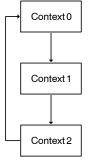

#### **CONTEXT SWITCHING**

XGS supports up to three contexts which allow the user to program a number of configurations and let the sensor cycle through these. Switching from one context to another is done at the start of a frame and cannot corrupt the ongoing readout. The registers that control the switching are grouped in the *contexts\_reg*. The active context switching can be done manually by changing the value in the *active\_contexts*

register or the sequencer can take control. If programmed, the sequencer will cycle through two or three contexts sequentially as depicted in Figures 23 and 24.

Two Context Switching

(context\_reg.active\_contexts = 0x3)

context 0 → context 1 → context 0...

Figure 23. Two Context Switching

Three Context Switching

(context\_reg.active\_contexts = 0x7)

context 0 → context 1 → context 2 → context 0...

Figure 24. Three Context Switching

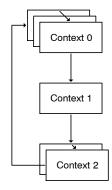

Multiple Frame Context Switching

In addition to defining up to three contexts, the number

of frames per context can be configured for each context separately. In the example configuration depicted in Figure 25, the sensor first generates three frames using *context 0* settings followed by a single *context 1* frame and two *context 2* frames. The sensor loops through this sequence until the sequencer is disabled. The number of frames per context switch is configured in *contexts\_reg.frames\_ctxt0* (for context0).  $3 \times 10^{-5} \text{ context } 1 \rightarrow 2 \times 10^{-5} \text{ context } 2 \text{ context } 2$

$\rightarrow$  3 x context 0...

Figure 25. Multiple Frame Context Switching

#### **TEST PATTERN**

The XGS sensor has the capability of injecting a number of test patterns into the datapath. As the test pattern generator is placed at the beginning of the digital datapath, it can be used to check the functions of the digital blocks or to test the frame grabber or receiver operation. The test patterns can be configured in the test\_pattern\_mode\_reg.test\_pattern\_mode and only one pattern can be activated at a given point in time.

### **DATA PEDESTAL**

The data pedestal is a constant offset that is added to the pixel values at the end of the datapath. The pedestal or offset value can be configured separately for each color channel  $(G_R,G_B,R)$  and  $(G_R,G_B,R)$  and for each context. The offset is a 12-bit value.

#### **GAIN STAGES**

Analog Gain

A column-based analog gain of 1x, 2x or 4x can be applied to the output signal.

Digital Gain

As opposed to the analog gain stage, the digital gain can be configured to separate levels for each color channel ( $G_R$ ,  $G_B$ , R and B). The digital gain factor ranges from 1/32 to 2

in steps of 1/32 (64 steps) and its configuration can be represented by the equation below:

Digital gain = Dg factor/

$$2^5$$

(eq. 1)

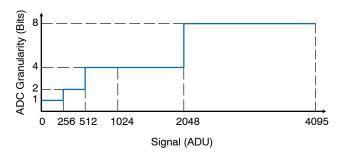

#### **COMPANDING MODE**

The companding mode can be used to compress 12-bit pixel data into 10-bit values. The line time remains the time required to convert a 12-bit ADC sample; gain is only achieved when, due to lane multiplexing, the system becomes I/O limited. In that situation, being able to send out 12-bit pixels using only 10 bits, can be useful to boost the frame rate. When companding mode is enabled, the precision of the digital output is 1 Least Significant Bit (LSB) in the low light area, but towards the upper region, the granularity gradually increases to 2, 4, and 8 LSBs as shown in Figure 26. In all cases the ADC quantization steps will be less than the photon shot noise performance of the pixel.

Figure 26. ADC Granularity - Companding Mode

#### FRAME RATE

Assuming the readout of a frame takes longer than the integration, the frame rate can be influenced by changing one or more of the following parameters:

- Vertical resolution (number of lines in ROI)

- Number of data output lanes (24 / 18 / 12 / 6) or mux mode (4:4 / 4:3 / 4:2 / 4:1)

The frame rate scales linearly with the number of lines (vertical direction) but not with the number of columns (horizontal direction) due to the column ADC architecture. Using the sensor with a reduced number of data lanes will lower the frame rate.

Alternatively, the frame time can be configured through *line\_time* and *frame\_time*. The line time should be large enough in order to process a full line and the frame time should be configured such that at least all ROIs can be read out and that the maximum integration can be scheduled in. When one of the two conditions are violated the sensor gives either priority to the readout or the integration (*int\_priority*).

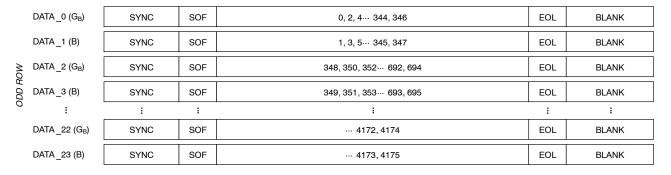

#### LANE MULTIPLEXING

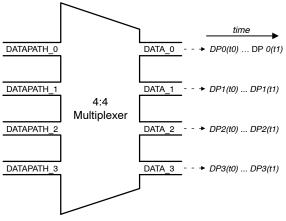

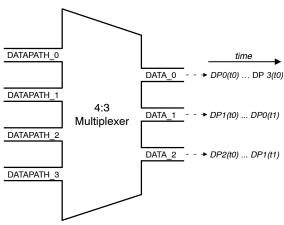

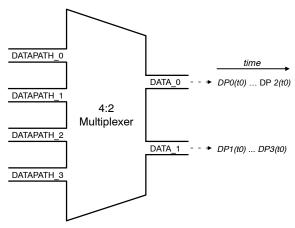

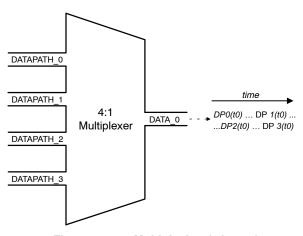

The lane multiplexing function can be used to reduce the number of output data lanes and thus the output data rate. This can be useful in case the receiver cannot accept all 24 data lanes or the backend is unable to process the sensor's full data rate. The sensor has one multiplexer for each PHY; six in total. Each multiplexer connects 4 datapath outputs to one PHY and can be configured to distribute the data from the 4 datapath inputs over either 1, 2, 3 or 4 outputs; i.e. the sensor supports 4 multiplexing schemes:

• 4:4 multiplexing: no multiplexing; each datapath lane is connected to a HiSPi lane (total of 24 lanes).

- 4:3 multiplexing: four datapath lanes are multiplexed to three HiSPi lanes (total of 18 lanes).

- 4:2 multiplexing: four datapath lanes are multiplexed to two HiSPi lanes (total of 12 lanes).

- 4:1 multiplexing: four datapath lanes are multiplexed to a single HiSPi lane (total of 6 lanes).

The four different multiplexing schemes are illustrated in Figures 27 to 30. The pixel readout order for each multiplexing mode is depicted in Figures 31 to 34.

Figure 27. 4:4 Multiplexing (24 Lanes)

Figure 28. 4:3 Multiplexing (18 Lanes)

Figure 29. 4:2 Multiplexing (12 Lanes)

Figure 30. 4:1 Multiplexing (6 Lanes)

Table 14 lists the active data lanes in function of the multiplexing scheme. As depicted in Table 14, HiSPi lane 0

is the lane that is always active, regardless of the selected multiplex scheme.

Table 12. ACTIVE DATA LANES IN PHY0 IN FUNCTION OF MUX MODE

| Mux Mode | Lane_0 | Lane_2 | Lane_4 | Lane_6 |

|----------|--------|--------|--------|--------|

| 4:4      | Х      | Х      | Х      | Х      |

| 4:3      | Х      | Х      | Х      |        |

| 4:2      | Х      | Х      |        |        |

| 4:1      | Х      |        |        |        |

NOTE: Lane usage is illustrated using the first four lanes only (i.e. for a single PHY).

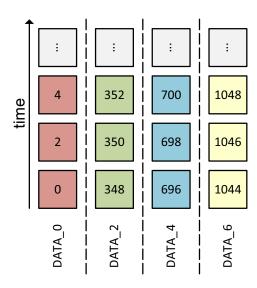

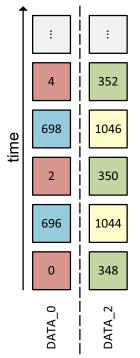

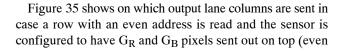

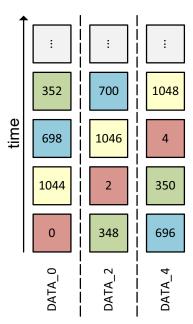

The data output on each lane within a single PHY, depending on the multiplexing scheme, is represented in

Figures 31 to 34. The numbers in the squares represent the actual column address in the pixel array.

Figure 31. Column Output with 4:4 Multiplexing

Figure 33. Column Output with 4:2 Multiplexing

Figure 32. Column Output with 4:3 Multiplexing

Figure 34. Column Output with 4:1 Multiplexing

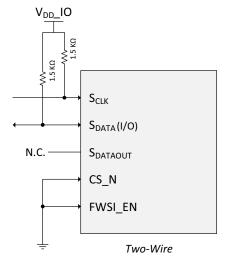

numbered lanes) and R and B pixels to the bottom (odd numbered lanes). Figure 36 shows the column output in case a row with an odd address is read.

| DATA_0 (G <sub>R</sub> )  | SYNC                                                                           | SOF         | 1, 3, 5 345, 347                                                                                                                                                                                                 | EOL                                                                                                                                                                               | BLANK                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------------------|--------------------------------------------------------------------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DATA_1 (R) SYNC           |                                                                                | SOF         | 0, 2, 4… 344, 346                                                                                                                                                                                                | EOL                                                                                                                                                                               | BLANK                                                                                                                                                                                                                                                                                                                                                                                          |

| DATA_2 (G <sub>R</sub> )  | SYNC                                                                           | SOF         | 349, 351, 353··· 693, 695                                                                                                                                                                                        | EOL                                                                                                                                                                               | BLANK                                                                                                                                                                                                                                                                                                                                                                                          |

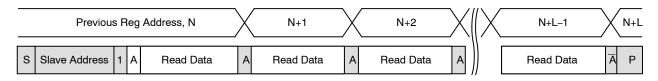

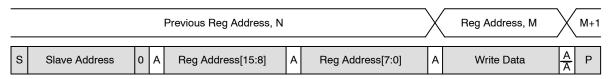

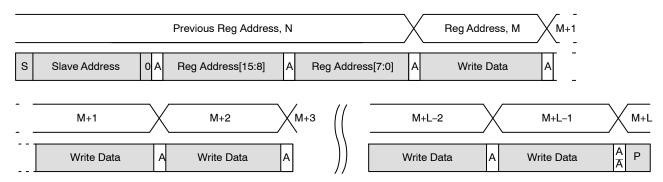

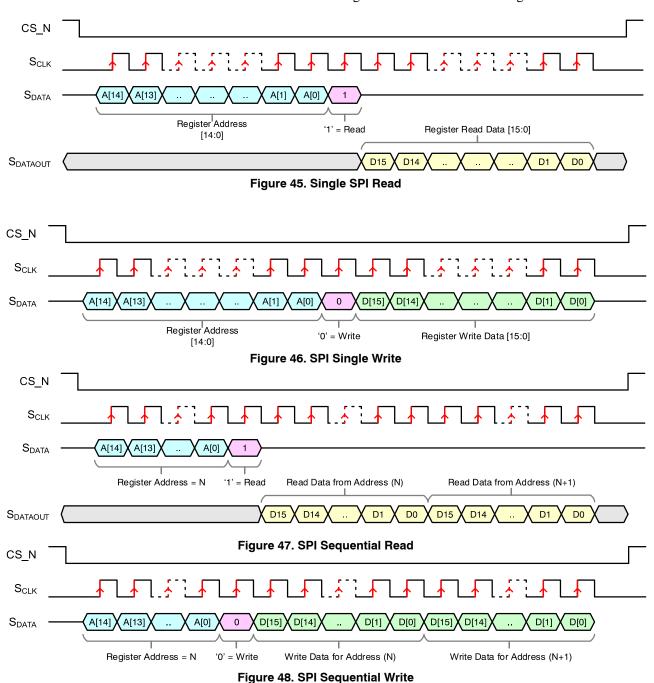

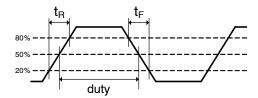

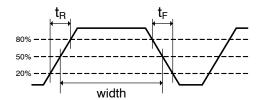

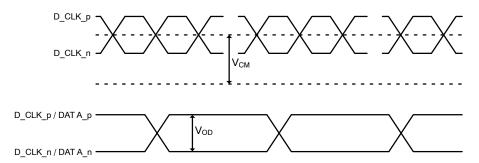

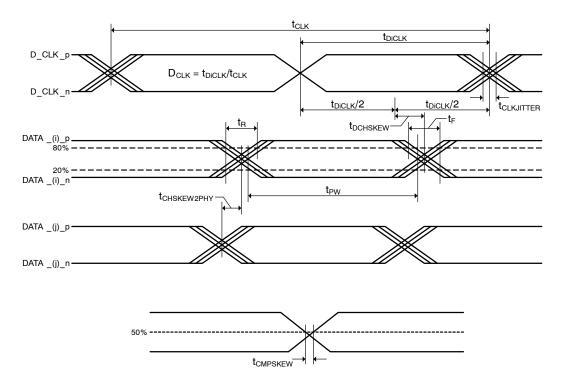

| DATA_3 (R)                | SYNC                                                                           | SOF         | 348, 350, 352··· 692, 694                                                                                                                                                                                        | EOL                                                                                                                                                                               | BLANK                                                                                                                                                                                                                                                                                                                                                                                          |