# RENESAS

## EL9110

## Differential Receiver/Equalizer

The EL9110 is a single channel differential receiver and equalizer. It contains a high speed differential receiver with 5 programmable poles. The outputs of these pole blocks are then summed into an output buffer. The equalization length is set with the voltage on a single pin. The EL9110 also contains a three-statable output, enabling multiple devices to be connected in parallel and used in a multiplexing application.

The gain can be adjusted up or down by 6dB using the  $V_{GAIN}$  control signal. In addition, a further 6dB of gain can be switched in to provide a matched drive into a cable.

The EL9110 has a bandwidth of 150MHz and consumes just 33mA on  $\pm 5V$  supply. A single input voltage is used to set the compensation levels for the required length of cable.

The EL9110 is available in the 16 Ld QSOP package and is specified for operation over the full -40°C to +85°C temperature range.

## **Ordering Information**

| PART<br>NUMBER           |         |                         | PKG. DWG. # |  |

|--------------------------|---------|-------------------------|-------------|--|

| EL9110IU                 | 9110IU  | 16 Ld QSOP              | MDP0040     |  |

| EL9110IU-T7*             | 9110IU  | 16 Ld QSOP              | MDP0040     |  |

| EL9110IU-T13*            | 9110IU  | 16 Ld QSOP              | MDP0040     |  |

| EL9110IUZ<br>(Note)      | 9110IUZ | 16 Ld QSOP<br>(Pb-free) | MDP0040     |  |

| EL9110IUZ-T7*<br>(Note)  | 9110IUZ | 16 Ld QSOP<br>(Pb-free) | MDP0040     |  |

| EL9110IUZ-T13*<br>(Note) | 9110IUZ | 16 Ld QSOP<br>(Pb-free) | MDP0040     |  |

\*Please refer to TB347 for details on reel specifications.

NOTE: These Intersil Pb-free plastic packaged products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate PLUS ANNEAL - e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

## Features

- · 150MHz -3dB bandwidth

- CAT-5 compensation

- 75MHz @ 1000ft

- 125MHz @ 500ft

- 33mA supply current

- Differential input range 3.2V

- Common mode input range ±4.5V

- ±5V supply

- Output to within 1.5V of supplies

- · Available in 16 Ld QSOP package

- · Pb-free available (RoHS compliant)

## Applications

- · Twisted-pair receiving/equalizer

- KVM (Keyboard/Video/Mouse)

- · VGA over twisted-pair

- Security video

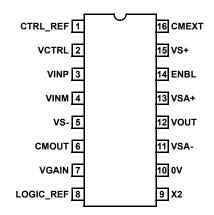

#### Pinout

EL9110 (16 LD QSOP) TOP VIEW

FN7305 Rev 5.00 November 30, 2007

#### **Absolute Maximum Ratings** (T<sub>A</sub> = +25°C)

| Supply Voltage between V <sub>S</sub> + and V <sub>S</sub> |                                                 |

|------------------------------------------------------------|-------------------------------------------------|

| Maximum Continuous Output Current                          |                                                 |

| Pin Voltages                                               | . V <sub>S</sub> 0.5V to V <sub>S</sub> + +0.5V |

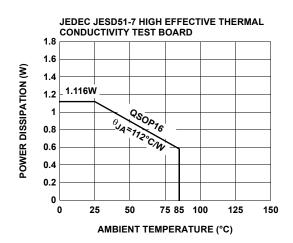

#### **Thermal Information**

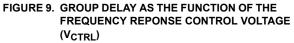

| Power Dissipation                                | See Curves      |

|--------------------------------------------------|-----------------|

| Storage Temperature                              | -65°C to +150°C |

| Ambient Operating Temperature                    | 40°C to +85°C   |

| Die Junction Temperature                         | +150°C          |

| Pb-free reflow profile                           | see link below  |

| http://www.intersil.com/pbfree/Pb-FreeReflow.asp | )               |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

IMPORTANT NOTE: All parameters having Min/Max specifications are guaranteed. Typ values are for information purposes only. Unless otherwise noted, all tests are at the specified temperature and are pulsed tests, therefore:  $T_J = T_C = T_A$

## **Electrical Specifications** $V_{SA}$ + = $V_{A}$ + = +5V, $V_{SA}$ = $V_{A}$ = -5V, $T_{A}$ = +25°C, Unless Otherwise Specified

| PARAMETER           | DESCRIPTION                    | CONDITIONS                                                                                           | MIN<br>(Note 1) | ТҮР     | MAX<br>(Note 1) | UNIT      |

|---------------------|--------------------------------|------------------------------------------------------------------------------------------------------|-----------------|---------|-----------------|-----------|

| AC PERFORM          | ANCE                           |                                                                                                      |                 |         | 1 1             |           |

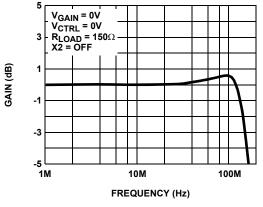

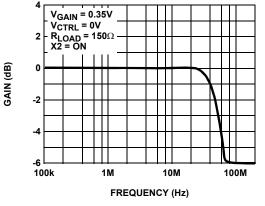

| BW                  | Bandwidth                      | (See Figure 1)                                                                                       |                 | 150     |                 | MHz       |

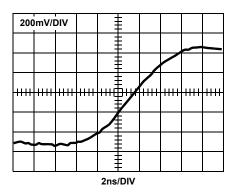

| SR                  | Slew Rate                      | $V_{IN}$ = -1V to +1V, $V_G$ = 0.35, $V_C$ = 0, $R_L$ = 75 + 75 $\Omega$                             |                 | 1.5     |                 | V/ns      |

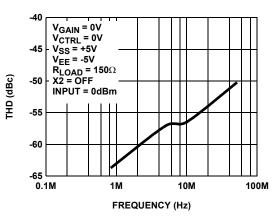

| THD                 | Total Harmonic Distortion      | 10MHz 1V <sub>P-P</sub> out, V <sub>G</sub> = 0.35V, X2 gain, V <sub>C</sub> = 0                     |                 | -50     |                 | dBc       |

| DC PERFORM          | ANCE                           |                                                                                                      | I               | 1       | 1 1             |           |

| V <sub>OS</sub>     | Offset Voltage (bin #1)        | X2 gain, no equalization                                                                             |                 | -10     | +250            | mV        |

|                     | Offset Voltage (bin #2)        | _                                                                                                    |                 | CPI9049 |                 | mV        |

| INPUT CHARA         | CTERISTICS                     |                                                                                                      | I.              |         |                 |           |

| CMIR                | Common-mode Input Range        | Common-mode extension off                                                                            |                 | -4/+3.5 |                 | V         |

| CMIRx               | Extended CMIR                  | Common-mode extension on                                                                             |                 | ±4.5    |                 | V         |

| O <sub>NOISE</sub>  | Output Noise                   | $V_G$ = 0.35, X2 gain, 75 + 75 $\Omega$ load, $V_C$ = 0.6                                            |                 | 25      |                 | mV<br>RMS |

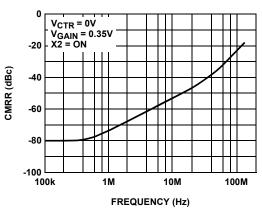

| CMRR                | Common-mode Rejection Ratio    | Measured at 10kHz                                                                                    |                 | 60      |                 | dB        |

| CMRR+               | Common-mode Rejection Ratio    | Measured at 10MHz                                                                                    |                 | 50      |                 | dB        |

| CMBW                | CM Amplifier Bandwidth         | 10K    10pF load                                                                                     |                 | 50      |                 | MHz       |

| CM <sub>SLEW</sub>  | CM Slew Rate                   | Measured @ +1V to -1V                                                                                |                 | 100     |                 | V/µs      |

| CINDIFF             | Differential Input Capacitance | Capacitance V <sub>INP</sub> to V <sub>INM</sub>                                                     |                 | 600     |                 | fF        |

| R <sub>INDIFF</sub> | Differential Input Resistance  | Resistance V <sub>INP</sub> to V <sub>INM</sub>                                                      | 1               | 2.4     |                 | MΩ        |

| CINCM               | CM Input Capacitance           | Capacitance V <sub>INP</sub> = V <sub>INM</sub> to ground                                            |                 | 1.2     |                 | pF        |

| R <sub>INCM</sub>   | CM Input Resistance            | Resistance V <sub>INP</sub> = V <sub>INM</sub> to ground                                             | 1               | 2.8     |                 | MΩ        |

| +I <sub>IN</sub>    | Positive Input Current         | DC bias @ V <sub>INP</sub> = V <sub>INM</sub> = 0V                                                   |                 | 1       |                 | μA        |

| -I <sub>IN</sub>    | Negative Input Current         | DC bias @ V <sub>INP</sub> = V <sub>INM</sub> = 0V                                                   |                 | 1       |                 | μA        |

| VINDIFF             | Differential Input Range       | $V_{\mbox{\scriptsize INP}}$ - $V_{\mbox{\scriptsize INM}}$ when slope gain falls to 0.9             | 2.5             | 3.2     |                 | V         |

| OUTPUT CHAP         | RACTERISTICS                   |                                                                                                      | ľ               |         | 1 1             |           |

| V <sub>O</sub>      | Output Voltage Swing           | R <sub>L</sub> = 150Ω                                                                                |                 | ±3.5    |                 | V         |

| IOUT                | Output Drive Current           | R <sub>L</sub> = 10Ω, V <sub>INP</sub> = 1V, V <sub>INM</sub> = 0V, X2 = gain, V <sub>G</sub> = 0.35 | 50              | 60      |                 | mA        |

| R <sub>OUTCM</sub>  | CM Output Resistance           | at 100kHz                                                                                            |                 | 30      |                 | Ω         |

| DiffGain            | Differential Gain              | $V_{C}$ = 0, $V_{G}$ = 0.35, X2 = 5, $R_{L}$ = 75 + 75 $\Omega$                                      | 0.85            | 1.0     | 1.1             |           |

| SUPPLY              |                                |                                                                                                      |                 |         |                 |           |

| I <sub>SON</sub>    | Supply Current                 | V <sub>ENBL</sub> = 5, V <sub>INM</sub> = 0                                                          | 27              |         | 38              | mA        |

| ISOFF               | Supply Current                 | V <sub>ENBL</sub> = 0, V <sub>INM</sub> = 0                                                          | 0.4             |         | 0.8             | mA        |

| PARAMETER        | DESCRIPTION                  | CONDITIONS                                                         | MIN<br>(Note 1) | ТҮР | MAX<br>(Note 1) | UNIT |

|------------------|------------------------------|--------------------------------------------------------------------|-----------------|-----|-----------------|------|

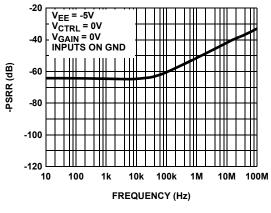

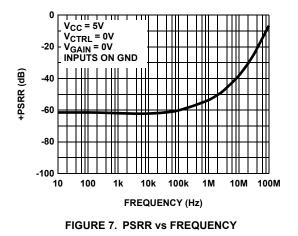

| PSRR             | Power Supply Rejection Ratio | DC to 100kHz, ±5V supply                                           |                 | 60  |                 | dB   |

| LOGIC CONTR      | OL PINS                      | · ·                                                                |                 |     |                 |      |

| V <sub>HI</sub>  | Logic High Level             | V <sub>IN</sub> - V <sub>LOGIC</sub> ref for guaranteed high level | 1.35            |     |                 | V    |

| V <sub>LOW</sub> | Logic Low Level              | V <sub>IN</sub> - V <sub>LOGIC</sub> ref for guaranteed low level  |                 |     | 0.8             | V    |

| ILOGICH          | Logic High Input Current     | V <sub>IN</sub> = 5V, V <sub>LOGIC</sub> = 0V                      |                 |     | 50              | μA   |

| ILOGICL          | Logic Low Input Current      | $V_{IN} = 0V, V_{LOGIC} = 0V$                                      |                 |     | 15              | μA   |

NOTE:

1. Parts are 100% tested at +25°C. Over-temperature limits established by characterization and are not production tested.

# Pin Descriptions

| PIN NUMBER | PIN NAME  | PIN TYPE    | PIN FUNCTION                                                       |

|------------|-----------|-------------|--------------------------------------------------------------------|

| 1          | CTRL_REF  | Input       | Reference voltage for $V_{\mbox{GAIN}}$ and $V_{\mbox{CTRL}}$ pins |

| 2          | VCTRL     | Input       | Control voltage (0 to 1V) to set equalization                      |

| 3          | VINP      | Input       | Positive differential input                                        |

| 4          | VINM      | Input       | Negative differential input                                        |

| 5          | VS-       | Power       | -5V to core of chip                                                |

| 6          | CMOUT     | Output      | Output of common mode voltage present at inputs                    |

| 7          | VGAIN     | Input       | Control voltage to set overall gain (0V to 1V)                     |

| 8          | LOGIC_REF | Input       | Reference voltage for all logic signals                            |

| 9          | X2        | Logic Input | Logic signal; low - gain = 1, high - gain = 2                      |

| 10         | 0V        |             | 0V reference for output voltage                                    |

| 11         | VSA-      | Power       | -5V to output buffer                                               |

| 12         | VOUT      | Output      | Single-ended output voltage reference to pin 10                    |

| 13         | VSA+      | Power       | +5V to output buffer                                               |

| 14         | ENBL      | Logic Input | Logic signal to enable pin; low - disabled, high - enabled         |

| 15         | VS+       | Power       | +5V to core of chip                                                |

| 16         | CMEXT     | Logic Input | Logic signal to enable CM range extension; active high             |

## **Typical Performance Curves**

FIGURE 1. FREQUENCY RESPONSE

FIGURE 2. TOTAL HARMONIC DISTORTION

FIGURE 3. RISE TIME

FIGURE 5. CM AMPLIFIER BANDWIDTH

FIGURE 4. COMMON MODE REJECTION

FIGURE 6. PSRR vs FREQUENCY

## Typical Performance Curves (Continued)

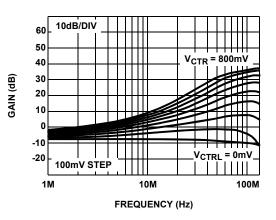

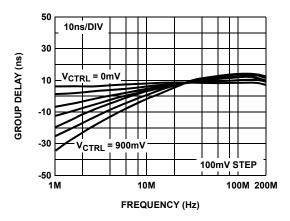

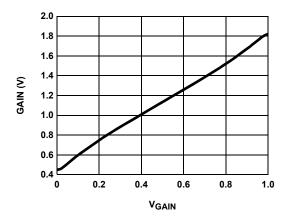

FIGURE 8. GAIN AS THE FUNCTION OF VCTRL

FIGURE 10. PACKAGE POWER DISSIPATION vs AMBIENT TEMPERATURE

FIGURE 11. PACKAGE POWER DISSIPATION vs AMBIENT TEMPERATURE

## Applications Information

#### Logic Control

The EL9110 has three logical input pins, Chip Enable (ENBL), Common Mode Extend (CMEXT), and Switch Gain (X2). The logic circuits all have a nominal threshold of 1.1V above the potential of the logic reference pin. In most applications it is expected that this chip will run from a +5V, 0V, -5V supply system with logic being run between 0V and +5V. In this case the logic reference voltage should be tied to the 0V supply. If the logic is referenced to the -5V rail, then the logic reference should be connected to -5V. The logic reference pin sources about  $60\mu$ A and this will rise to about 200 $\mu$ A if all inputs are true (positive).

The logic inputs all source up to  $10\mu$ A when they are held at the logic reference level. When taken positive, the inputs sink a current dependent on the high level, up to  $50\mu$ A for a high level 5V above the reference level.

The logic inputs, if not used, should be tied to the appropriate voltage in order to define their state.

#### **Control Reference and Signal Reference**

Analog control voltages are required to set the equalizer and contrast levels. These signals are voltages in the range 0V to 1V, which are referenced to the control reference pin. It is expected that the control reference pin will be tied to 0V and the control voltage will vary from 0V to 1V. It is; however, acceptable to connect the control reference to any potential between -5V and 0V to which the control voltages are referenced.

The control voltage pins themselves are high impedance. The control reference pin will source between  $0\mu$ A and  $200\mu$ A depending on the control voltages being applied.

The control reference and logic reference effectively remove the necessity for the 0V rail and operation from  $\pm$ 5V (or 0V and 10V) only is possible. However we still need a further reference to define the 0V level of the single ended output signal. The reference for the output signal is provided by the 0V pin. The output stage cannot pull fully up or down to either supply so it is important that the reference is positioned to allow full output swing. The 0V reference should be tied to a 'quiet ground' as any noise on this pin is transferred directly to the output. The 0V pin is a high impedance pin and draws dc bias currents of a few µA and similar levels of AC current.

## **Common Mode Extension**

The common mode extension circuitry extends the range of input common mode voltage before the input differential amplifier is overloaded. It does this by reducing the voltage equally at both inputs of the first differential amplifier as the common mode signal rises towards the supply. Similarly, when the common mode input signal goes low, the inputs to the first differential amplifier are raised whilst preserving the differential signal and maintain the amplifier within its common mode operating range.

This operation may not always be desirable. A problem occurs because the EL9110 sinks or sources a common mode current though its input pins to create the common mode offset voltage. Assuming the system has been set up so that the differential line has a well-balanced impedance, then a problem will only occur when the common mode impedance to ground is not low. This will occur in systems where the inputs to the EL9110 are AC coupled. In such systems it is recommended that the common mode extension be disabled. In systems where the differential input signal is directly coupled and has its common mode level defined by a low impedance line driver, the common mode extension circuitry can extend the total common mode range by 2V to 3V.

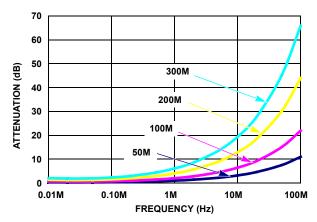

#### Equalizing

When transmitting a signal across a twisted pair cable, it is found that the high frequency (above 1MHz) information is attenuated more significantly than the information at low frequencies. The attenuation is predominantly due to resistive skin effect losses and has a loss curve which depends on the resistivity of the conductor, surface condition of the wire and the wire diameter. For the range of high performance twisted pair cables based on 24awg copper wire (Cat 5 etc.) these parameters vary only a little between cable types, and in general cables exhibit the same frequency dependence of loss. (The lower loss cables can be compared with somewhat longer lengths of their more lossy brothers.) This enables a single equalizing law equation to be built into the EL9110.

With a control voltage applied between pins 2 and 1, the frequency dependence of the equalization is shown in Figure 8. The equalization matches the cable loss up to about 100MHz. Above this, system gain is rolled off rapidly to reduce noise bandwidth. The roll-off occurs more rapidly for higher control voltages, thus the system (cable + equalizer) bandwidth reduces as the cable length increases. This is desirable, as noise becomes an increasing issue as the equalization increases.

The cable loss for 100m, 200m, and 300m of CAT 5 cable, based on manufacturer's loss curves is shown in Figure 14.

Thus:

- 100m requires V<sub>C</sub> = 0.2V

- 200m requires V<sub>C</sub> = 0.6V

and:

300m requires V<sub>C</sub> = 1.0V approximately

#### Contrast

By varying the voltage between pins 7 and 1, the gain of the signal path can be changed in the ratio 4:1. The gain change varies almost linearly with control voltage. For normal

operation it is anticipated the X2 mode will be selected and the output load will be back matched. A unity gain to the output load will then be achieved with a gain control voltage of about 0.35V. This allows the gain to be trimmed up or down by 6dB to compensate for any gain/loss errors that affect the contrast of the video signal. Figure 12 shows an example plot of the gain to the load with gain control voltage.

FIGURE 12. VARIATION OF GAIN WITH GAIN CONTROL VOLTAGE

FIGURE 13. CAT-5 CABLE ATTENUATION CHARACTERISTICS

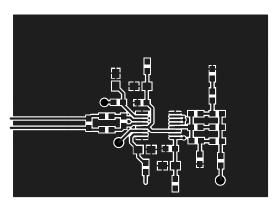

## Circuit and Layout Recommendation

The interconnection cable is a transmission line therefore for proper function it should be treated like transmission line, a refection-free termination is necessary.

A reflection-free termination is a real "ohmic" resistor with as less as possible reactive parasitic.

The traces of the layout, up to the point where of the termination resistor placed, are part of the transmission line which also includes the cable's connector. A connector with a better controlled impedance is an obligation for good picture quality. The termination resistor should be placed close to the inputs of the device's pins (pin 3 and pin 4.) The small capacitance differential and common mode capacitance of the input pins of the device makes it possible to connect parallel to the termination resistor.

The cable will work as an antenna for all the RF spectrum which is "in the air" where the cable is used. The spectrum, particularly its common mode components, could and will contain high energy level of transients which are above the built-in protection level of the device and easily could damage its inputs. Using a transient protection circuit according to the given application is recommended.

Since the used signal's bandwidth is in the range of 100MHz, for layout and power supply bypassing the roles of RF design should be applied.

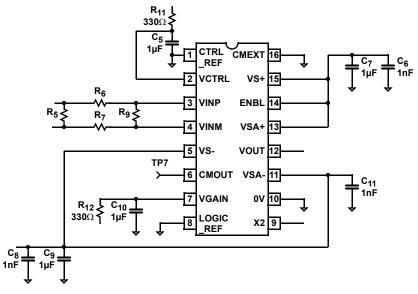

The following picture is taken from the DB9110 demoboard's layout. For better visibility the ground plain is removed.

The ground plane is shown in Figure 14.

FIGURE 14. DEMO BOARD LAYOUT

The accompanying circuit diagram is shown in Figure 15.

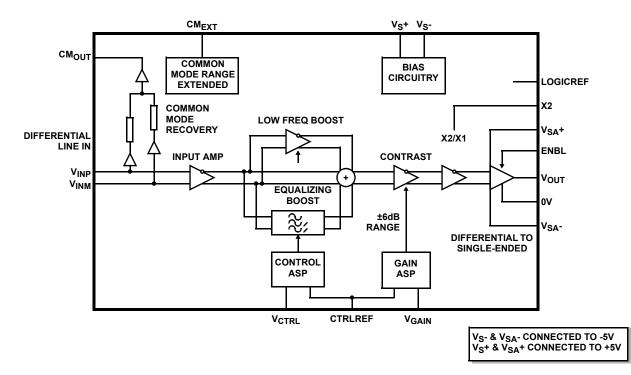

Block Diagram

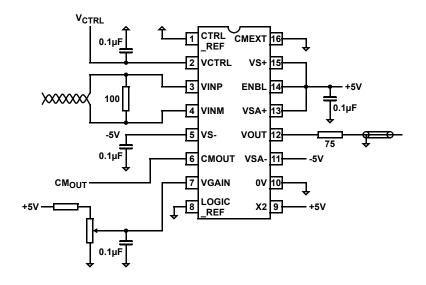

## **Typical Application**

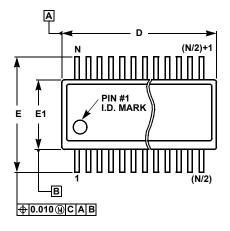

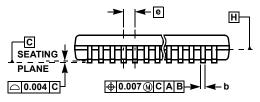

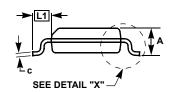

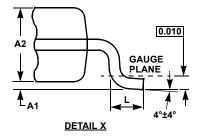

## Quarter Size Outline Plastic Packages Family (QSOP)

#### **MDP0040**

QUARTER SIZE OUTLINE PLASTIC PACKAGES FAMILY

|             |        | INCHES |        |           |       |  |

|-------------|--------|--------|--------|-----------|-------|--|

| SYMBOL      | QSOP16 | QSOP24 | QSOP28 | TOLERANCE | NOTES |  |

| А           | 0.068  | 0.068  | 0.068  | Max.      | -     |  |

| A1          | 0.006  | 0.006  | 0.006  | ±0.002    | -     |  |

| A2          | 0.056  | 0.056  | 0.056  | ±0.004    | -     |  |

| b           | 0.010  | 0.010  | 0.010  | ±0.002    | -     |  |

| с           | 0.008  | 0.008  | 0.008  | ±0.001    | -     |  |

| D           | 0.193  | 0.341  | 0.390  | ±0.004    | 1, 3  |  |

| E           | 0.236  | 0.236  | 0.236  | ±0.008    | -     |  |

| E1          | 0.154  | 0.154  | 0.154  | ±0.004    | 2, 3  |  |

| е           | 0.025  | 0.025  | 0.025  | Basic     | -     |  |

| L           | 0.025  | 0.025  | 0.025  | ±0.009    | -     |  |

| L1          | 0.041  | 0.041  | 0.041  | Basic     | -     |  |

| Ν           | 16     | 24     | 28     | Reference | -     |  |

| Rev. F 2/07 |        |        |        |           |       |  |

NOTES:

1. Plastic or metal protrusions of 0.006" maximum per side are not included.

2. Plastic interlead protrusions of 0.010" maximum per side are not included.

3. Dimensions "D" and "E1" are measured at Datum Plane "H".

4. Dimensioning and tolerancing per ASME Y14.5M-1994.

© Copyright Intersil Americas LLC 2003-2007. All Rights Reserved. All trademarks and registered trademarks are the property of their respective owners.

For additional products, see www.intersil.com/en/products.html

Intersil products are manufactured, assembled and tested utilizing ISO9001 quality systems as noted in the quality certifications found at <u>www.intersil.com/en/support/qualandreliability.html</u>

Intersil products are sold by description only. Intersil may modify the circuit design and/or specifications of products at any time without notice, provided that such modification does not, in Intersil's sole judgment, affect the form, fit or function of the product. Accordingly, the reader is cautioned to verify that datasheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

#### ООО "ЛайфЭлектроникс"

ИНН 7805602321 КПП 780501001 Р/С 40702810122510004610 ФАКБ "АБСОЛЮТ БАНК" (ЗАО) в г.Санкт-Петербурге К/С 3010181090000000703 БИК 044030703

Компания «Life Electronics» занимается поставками электронных компонентов импортного и отечественного производства от производителей и со складов крупных дистрибьюторов Европы, Америки и Азии.

С конца 2013 года компания активно расширяет линейку поставок компонентов по направлению коаксиальный кабель, кварцевые генераторы и конденсаторы (керамические, пленочные, электролитические), за счёт заключения дистрибьюторских договоров

Мы предлагаем:

- Конкурентоспособные цены и скидки постоянным клиентам.

- Специальные условия для постоянных клиентов.

- Подбор аналогов.

- Поставку компонентов в любых объемах, удовлетворяющих вашим потребностям.

- Приемлемые сроки поставки, возможна ускоренная поставка.

- Доставку товара в любую точку России и стран СНГ.

- Комплексную поставку.

- Работу по проектам и поставку образцов.

- Формирование склада под заказчика.

- Сертификаты соответствия на поставляемую продукцию (по желанию клиента).

- Тестирование поставляемой продукции.

- Поставку компонентов, требующих военную и космическую приемку.

- Входной контроль качества.

- Наличие сертификата ISO.

В составе нашей компании организован Конструкторский отдел, призванный помогать разработчикам, и инженерам.

Конструкторский отдел помогает осуществить:

- Регистрацию проекта у производителя компонентов.

- Техническую поддержку проекта.

- Защиту от снятия компонента с производства.

- Оценку стоимости проекта по компонентам.

- Изготовление тестовой платы монтаж и пусконаладочные работы.

Тел: +7 (812) 336 43 04 (многоканальный) Email: org@lifeelectronics.ru

#### www.lifeelectronics.ru