# 2-WIRE SERIAL E<sup>2</sup>PROM

www.sii-ic.com

© Seiko Instruments Inc., 2010-2011

Rev.3.1 00 c

The S-24C04C is a 2-wire, low current consumption and wide range operation serial  $E^2$ PROM. The S-24C04C has the capacity of 4 K-bit, and the organization is 512 words  $\times$  8-bit. Page write and sequential read are available.

#### ■ Features

Operating voltage range Read: 1.6 V to 5.5 V

Write: 1.7 V to 5.5 V

Page write: 16 bytes / page

Sequential read

Operation frequency: 400 kHz (V<sub>CC</sub> = 1.6 V to 5.5 V)

• Write time: 5.0 ms max.

• Noise suppression: Schmitt trigger and noise filter on input pins (SCL, SDA)

Write protect function during the low power supply voltage

Endurance: 10<sup>6</sup> cycles / word\*<sup>1</sup> (Ta = +25°C)

• Data retention: 100 years (Ta = +25°C)

Memory capacity 4 K-bit

Write protect: 100%

Initial shipment data: FFh

Lead-free (Sn 100%), halogen-free\*<sup>2</sup>

\*1. For each address (Word: 8-bit)

\*2. Refer to "■ Product Name Structure" for details.

# ■ Packages

- 8-Pin SOP (JEDEC)

- 8-Pin TSSOP

- TMSOP-8

- SNT-8A

Caution This product is intended to use in general electronic devices such as consumer electronics, office equipment, and communications devices. Before using the product in medical equipment or automobile equipment including car audio, keyless entry and engine control unit, contact to SII is indispensable.

# **■** Pin Configurations

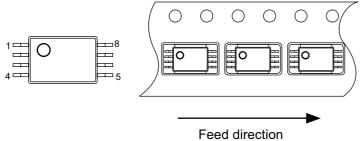

# 1. 8-Pin SOP (JEDEC)

8-Pin SOP (JEDEC) Top view

Figure 1

S-24C04CI-J8T1U

Table 1

| Pin No. | Symbol            | Description                                     |  |  |  |  |

|---------|-------------------|-------------------------------------------------|--|--|--|--|

| 1       | NC <sup>*1</sup>  | No connection                                   |  |  |  |  |

| 2       | A1                | Slave address input                             |  |  |  |  |

| 3       | A2                | Slave address input                             |  |  |  |  |

| 4       | GND               | Ground                                          |  |  |  |  |

| 5       | SDA <sup>*2</sup> | Serial data I/O                                 |  |  |  |  |

| 6       | SCL*2             | Serial clock input                              |  |  |  |  |

|         |                   | Write protect input                             |  |  |  |  |

| 7       | WP                | Connected to V <sub>CC</sub> : Protection valid |  |  |  |  |

|         |                   | Open or connected to GND: Protection invalid    |  |  |  |  |

| 8       | VCC               | Power supply                                    |  |  |  |  |

- \*1. Connect to GND or  $V_{\text{CC}}$ .

- \*2. Do not use it in high impedance.

# 2. 8-Pin TSSOP

8-Pin TSSOP Top view

Figure 2

S-24C04CI-T8T1U

#### Table 2

| Pin No. | Symbol | Description                                     |

|---------|--------|-------------------------------------------------|

| 1       | NC*1   | No connection                                   |

| 2       | A1     | Slave address input                             |

| 3       | A2     | Slave address input                             |

| 4       | GND    | Ground                                          |

| 5       | SDA*2  | Serial data I/O                                 |

| 6       | SCL*2  | Serial clock input                              |

|         |        | Write protect input                             |

| 7       | WP     | Connected to V <sub>CC</sub> : Protection valid |

|         |        | Open or connected to GND: Protection invalid    |

| 8       | VCC    | Power supply                                    |

- \*1. Connect to GND or  $V_{\text{CC}}$ .

- \*2. Do not use it in high impedance.

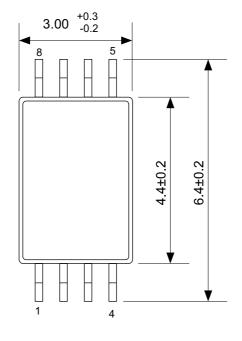

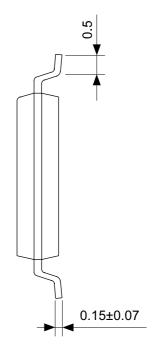

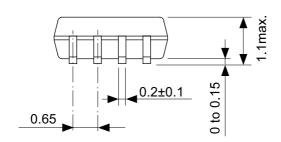

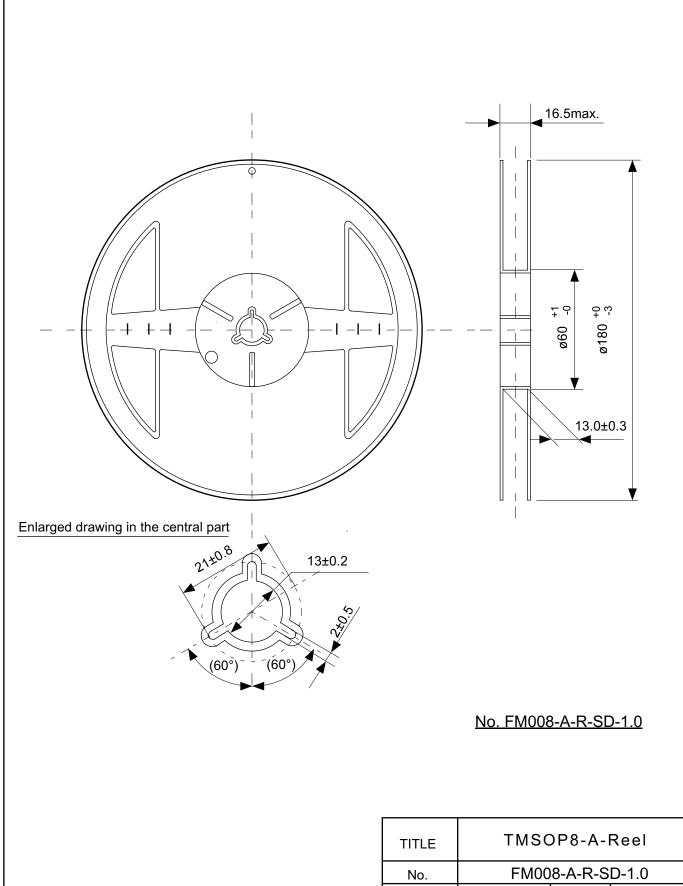

#### 3. TMSOP-8

TMSOP-8 Top view

Figure 3

S-24C04CI-K8T3U

Table 3

| Pin No. | Symbol           | Description                                     |  |  |  |  |

|---------|------------------|-------------------------------------------------|--|--|--|--|

| 1       | NC <sup>*1</sup> | No connection                                   |  |  |  |  |

| 2       | A1               | Slave address input                             |  |  |  |  |

| 3       | A2               | Slave address input                             |  |  |  |  |

| 4       | GND              | Ground                                          |  |  |  |  |

| 5       | SDA*2            | Serial data I/O                                 |  |  |  |  |

| 6       | SCL*2            | Serial clock input                              |  |  |  |  |

|         |                  | Write protect input                             |  |  |  |  |

| 7       | WP               | Connected to V <sub>CC</sub> : Protection valid |  |  |  |  |

|         |                  | Open or connected to GND: Protection invalid    |  |  |  |  |

| 8       | VCC              | Power supply                                    |  |  |  |  |

<sup>\*1.</sup> Connect to GND or  $V_{\text{CC}}$ .

# 4. SNT-8A

SNT-8A Top view

Figure 4

S-24C04CI-I8T1U

Table 4

| Pin No. | Symbol           | Description                                                                                                      |

|---------|------------------|------------------------------------------------------------------------------------------------------------------|

| 1       | NC <sup>*1</sup> | No connection                                                                                                    |

| 2       | A1               | Slave address input                                                                                              |

| 3       | A2               | Slave address input                                                                                              |

| 4       | GND              | Ground                                                                                                           |

| 5       | SDA*2            | Serial data I/O                                                                                                  |

| 6       | SCL*2            | Serial clock input                                                                                               |

| 7       | WP               | Write protect input Connected to V <sub>CC</sub> : Protection valid Open or connected to GND: Protection invalid |

| 8       | VCC              | Power supply                                                                                                     |

<sup>\*1.</sup> Connect to GND or  $V_{\text{CC}}$ .

Remark Refer to the "Package drawings" for the details.

<sup>\*2.</sup> Do not use it in high impedance.

<sup>\*2.</sup> Do not use it in high impedance.

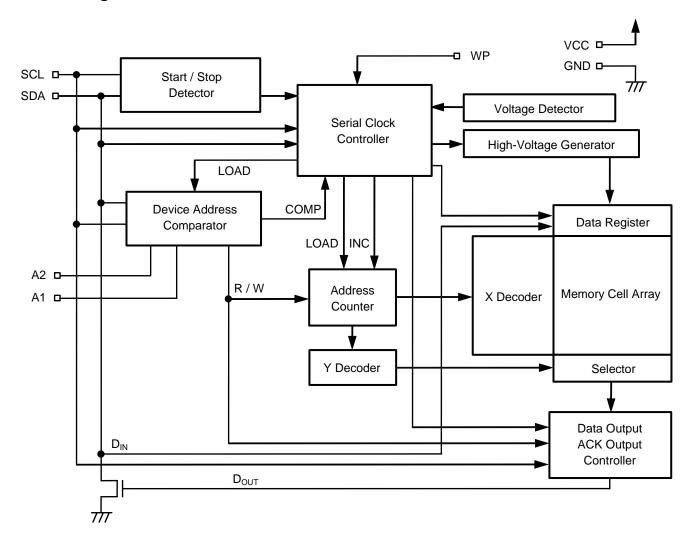

# **■** Block Diagram

Figure 5

# ■ Absolute Maximum Ratings

Table 5

| Item                          | Symbol           | Absolute Maximum Ratings | Unit |

|-------------------------------|------------------|--------------------------|------|

| Power supply voltage          | V <sub>CC</sub>  | −0.3 to +6.5             | V    |

| Input voltage                 | V <sub>IN</sub>  | −0.3 to +6.5             | V    |

| Output voltage                | $V_{OUT}$        | −0.3 to +6.5             | V    |

| Operation ambient temperature | T <sub>opr</sub> | −40 to +85               | °C   |

| Storage temperature           | T <sub>stq</sub> | −65 to +150              | °C   |

Caution The absolute maximum ratings are rated values exceeding which the product could suffer physical damage. These values must therefore not be exceeded under any conditions.

# **■** Recommended Operating Conditions

Table 6

| Item                     | Symbol          | Condition                                  | Ta = -40°0          | Unit                |       |  |

|--------------------------|-----------------|--------------------------------------------|---------------------|---------------------|-------|--|

| item                     | Symbol          | Condition                                  | Min.                | Max.                | Offic |  |

| Dower oupply voltage     | V <sub>CC</sub> | Read Operation                             | 1.6                 | 5.5                 | V     |  |

| Power supply voltage     |                 | Write Operation                            | 1.7                 | 5.5                 | V     |  |

| High level input voltage | $V_{IH}$        | $V_{CC} = 1.6 \text{ V to } 5.5 \text{ V}$ | $0.7 \times V_{CC}$ | 5.5                 | V     |  |

| Low level input voltage  | $V_{IL}$        | $V_{CC} = 1.6 \text{ V to } 5.5 \text{ V}$ | -0.3                | $0.3 \times V_{CC}$ | V     |  |

# **■** Pin Capacitance

Table 7

$(Ta = +25^{\circ}C, f = 1.0 \text{ MHz}, V_{CC} = 5.0 \text{ V})$

|                   |                  | (10                                     | 3 - TZ3 C, I - | 1.0 MILE, VC | ; - 3.0 v) |

|-------------------|------------------|-----------------------------------------|----------------|--------------|------------|

| Item              | Symbol           | Condition                               | Min.           | Max.         | Unit       |

| Input capacitance | C <sub>IN</sub>  | V <sub>IN</sub> = 0 V (SCL, A1, A2, WP) | _              | 10           | pF         |

| I/O capacitance   | C <sub>I/O</sub> | $V_{I/O} = 0 V (SDA)$                   | _              | 10           | pF         |

#### **■** Endurance

Table 8

| Item      | Symbol         | Operation Ambient Temperature | Min.            | Max. | Unit            |

|-----------|----------------|-------------------------------|-----------------|------|-----------------|

| Endurance | N <sub>W</sub> | Ta = +25°C                    | 10 <sup>6</sup> | -    | cycles / word*1 |

<sup>\*1.</sup> For each address (Word: 8 bits)

# ■ Data Retention

Table 9

| Item           | Symbol | Operation Ambient Temperature | Min. | Max. | Unit |

|----------------|--------|-------------------------------|------|------|------|

| Data retention | _      | Ta = +25°C                    | 100  | -    | year |

# **■ DC Electrical Characteristics**

# Table 10

| Item                       | Symbol           | Condition | $Ta = -40^{\circ}$<br>$V_{CC} = 1.6$<br>$f_{SCL} = 4$ | Unit |    |  |

|----------------------------|------------------|-----------|-------------------------------------------------------|------|----|--|

|                            |                  |           | Min.                                                  | Max. |    |  |

| Current consumption (READ) | I <sub>CC1</sub> | _         | -                                                     | 0.8  | mA |  |

#### Table 11

| Item                        |                  |           | Ta = -40°0                                 |      |      |

|-----------------------------|------------------|-----------|--------------------------------------------|------|------|

|                             | Symbol           | Condition | $V_{CC} = 1.7 \text{ V to } 5.5 \text{ V}$ |      | Unit |

|                             |                  | Condition | $f_{SCL} = 4$                              |      |      |

|                             |                  |           | Min.                                       | Max. |      |

| Current consumption (WRITE) | I <sub>CC2</sub> | _         | _                                          | 2.5  | mA   |

# Table 12

|                             |                  |                                                           | $Ta = -40^{\circ}C \text{ to } +85^{\circ}C$ |            |                |            |                |            |      |

|-----------------------------|------------------|-----------------------------------------------------------|----------------------------------------------|------------|----------------|------------|----------------|------------|------|

| Item                        | Symbol           | Condition                                                 | $V_{CC} = 2.5$                               | V to 5.5 V | $V_{CC} = 1.8$ | V to 5.5 V | $V_{CC} = 1.6$ | V to 1.8 V | Unit |

|                             |                  |                                                           | Min.                                         | Max.       | Min.           | Max.       | Min.           | Max.       |      |

| Standby current consumption | I <sub>SB</sub>  | $V_{IN} = V_{CC}$ or GND                                  | -                                            | 3.5        | -              | 3.5        | -              | 2.0        | μА   |

| Input leakage current 1     | I <sub>LI1</sub> | SCL, SDA,<br>$V_{IN} = GND \text{ to } V_{CC}$            | -                                            | 1.0        | -              | 1.0        | _              | 1.0        | μА   |

| Input leakage current 2     | I <sub>LI2</sub> | A1, A2<br>$V_{IN} > 0.7 \times V_{CC}$<br>At standby mode | -                                            | 1.0        | -              | 1.0        | -              | 1.0        | μΑ   |

| Output leakage current      | I <sub>LO</sub>  | SDA $V_{OUT} = GND \text{ to } V_{CC}$                    | _                                            | 1.0        | _              | 1.0        | _              | 1.0        | μА   |

| Input current 1             | I <sub>IL</sub>  | WP $V_{IN} < 0.3 \times V_{CC}$                           | _                                            | 50.0       | _              | 50.0       | _              | 50.0       | μА   |

| Input current 2             | I <sub>IH</sub>  | WP $V_{IN} > 0.7 \times V_{CC}$                           | -                                            | 2.0        | -              | 2.0        | -              | 2.0        | μА   |

| Input Impedance 1           | Z <sub>IL</sub>  | WP $V_{IN} = 0.3 \times V_{CC}$                           | 30                                           | ı          | 30             | ı          | 30             | _          | kΩ   |

| Input Impedance 2           | Z <sub>IH</sub>  | WP $V_{IN} = 0.7 \times V_{CC}$                           | 500                                          | _          | 500            | _          | 500            | -          | kΩ   |

|                             |                  | I <sub>OL</sub> = 3.2 mA                                  | _                                            | 0.4        | _              | _          | _              | _          | V    |

| Low level output voltage    | $V_{OL}$         | I <sub>OL</sub> = 1.5 mA                                  | _                                            | 0.3        | _              | 0.3        | _              | 0.3        | V    |

|                             |                  | $I_{OL} = 0.7 \text{ mA}$                                 | _                                            | 0.2        | _              | 0.2        | _              | 0.2        | V    |

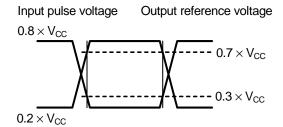

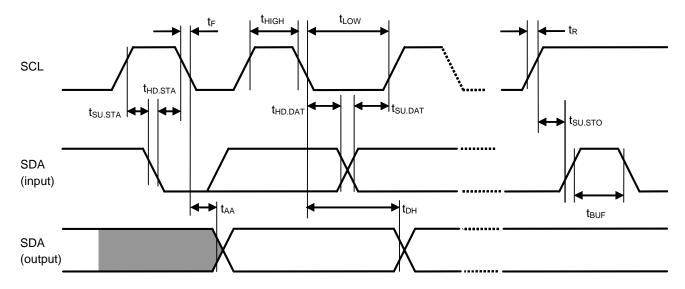

# ■ AC Electrical Characteristics

**Table 13 Measurement Conditions**

| Input pulse voltage               | $0.2 \times V_{CC}$ to $0.8 \times V_{CC}$ |

|-----------------------------------|--------------------------------------------|

| Input pulse rising / falling time | 20 ns or less                              |

| Output reference voltage          | $0.3 \times V_{CC}$ to $0.7 \times V_{CC}$ |

| Output load                       | 100 pF                                     |

Figure 6 Input / Output Waveform during AC Measurement

Table 14

|                            |                     | $Ta = -40^{\circ}C \text{ to } +85^{\circ}C$ |              |      |

|----------------------------|---------------------|----------------------------------------------|--------------|------|

| Item                       | Symbol              | Symbol $V_{CC} = 1.6$                        | S V to 5.5 V | Unit |

|                            |                     | Min.                                         | Max.         |      |

| SCL clock frequency        | f <sub>SCL</sub>    | 0                                            | 400          | kHz  |

| SCL clock time "L"         | t <sub>LOW</sub>    | 1.3                                          | _            | μs   |

| SCL clock time "H"         | t <sub>HIGH</sub>   | 0.6                                          | _            | μs   |

| SDA output delay time      | t <sub>AA</sub>     | 0.1                                          | 0.9          | μs   |

| SDA output hold time       | t <sub>DH</sub>     | 50                                           | _            | ns   |

| Start condition setup time | t <sub>SU.STA</sub> | 0.6                                          | _            | μs   |

| Start condition hold time  | t <sub>HD.STA</sub> | 0.6                                          | _            | μs   |

| Data input setup time      | t <sub>SU.DAT</sub> | 100                                          | _            | ns   |

| Data input hold time       | t <sub>HD.DAT</sub> | 0                                            | _            | ns   |

| Stop condition setup time  | t <sub>su.sto</sub> | 0.6                                          | _            | μs   |

| SCL, SDA rising time       | t <sub>R</sub>      | -                                            | 0.3          | μs   |

| SCL, SDA falling time      | t <sub>F</sub>      | -                                            | 0.3          | μs   |

| WP setup time              | t <sub>WS1</sub>    | 0                                            | _            | μs   |

| WP hold time               | t <sub>WH1</sub>    | 0                                            | _            | μs   |

| WP release setup time      | t <sub>WS2</sub>    | 0                                            | _            | μs   |

| WP release hold time       | t <sub>WH2</sub>    | 0                                            |              | μs   |

| Bus release time           | t <sub>BUF</sub>    | 1.3                                          |              | μs   |

| Noise suppression time     | tı                  | -                                            | 50           | ns   |

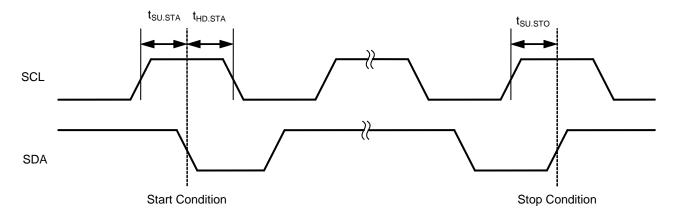

Figure 7 Bus Timing

Seiko Instruments Inc.

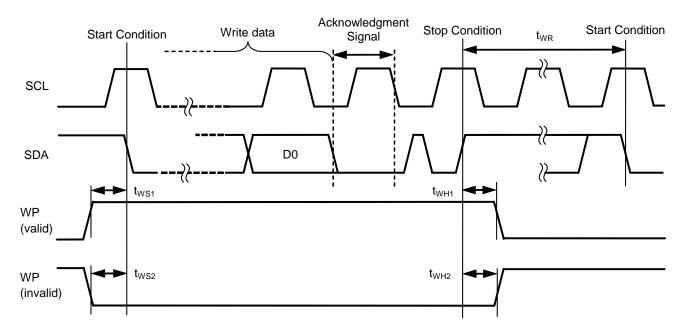

Table 15

|            |                 | Ta = -40°0                                 | Unit |    |

|------------|-----------------|--------------------------------------------|------|----|

| Item       | Symbol          | $V_{CC} = 1.7 \text{ V to } 5.5 \text{ V}$ |      |    |

|            |                 | Min.                                       | Max. |    |

| Write time | t <sub>WR</sub> | _                                          | 5.0  | ms |

Figure 8 Write Cycle Timing

#### ■ Pin Functions

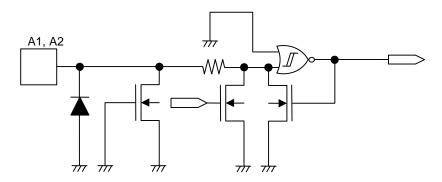

## 1. A1 and A2 (Slave address input) pins

In the S-24C04C, to set the slave address, connect each pin of A1, A2 to GND or  $V_{CC}$ . Therefore the users can set 4 types of slave address by a combination of A1, A2 pins.

Comparing the slave address transmitted from the master device and one that you set, makes possible to select the S-24C04C from other devices connected onto the bus.

Each A1 and A2 pin has a pull-down resistor. In open, these pins have the status when they are connected to GND.

#### 2. SDA (Serial data input / output) pin

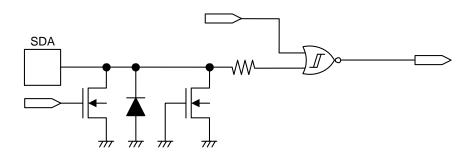

The SDA pin is used for the bi-directional transmission of serial data. This pin is a signal input pin, and an Nch open drain output pin.

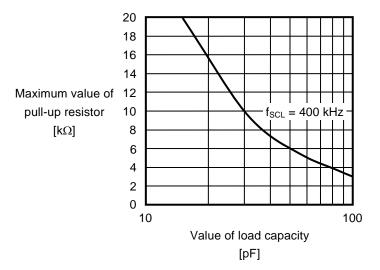

In use, generally, connect the SDA line to any other device which has the open-drain or open-collector output with Wired-OR connection by pulling up to  $V_{CC}$  by a resistor (**Figure 9** shows the relation with an output load).

## 3. SCL (Serial clock input) pin

The SCL pin is used for the serial clock input. Since the signals are processed at a rising or falling edge of the SCL clock, pay attention to the rising and falling time and comply with the specification.

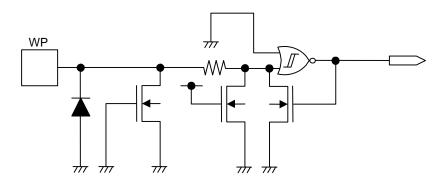

## 4. WP (Write protect input) pin

The write protect is enabled by connecting the WP pin to  $V_{CC}$  When not using the write protect, connect this pin to GND or set in open.

Figure 9 Output Load

#### ■ Initial Shipment Data

Initial shipment data of all addresses is "FFh".

# ■ Operation

#### 1. Start condition

Start is identified by a high to low transition of the SDA line while the SCL line is stable at high. Every operation begins from a start condition.

#### 2. Stop condition

Stop is identified by a low to high transition of the SDA line while the SCL line is stable at high.

When a device receives a stop condition during a read sequence, the read operation is interrupted, and the device enters standby mode.

When a device receives a stop condition during a write sequence, the reception of the write data is halted, and the S-24C04C initiates a write cycle.

Figure 10 Start / Stop Conditions

10

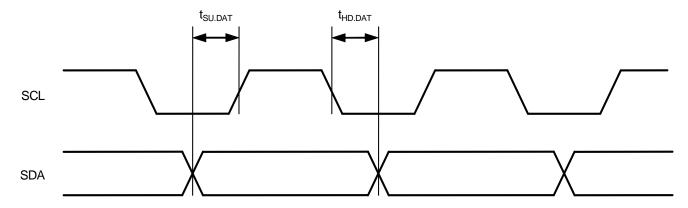

#### 3. Data transmission

Changing the SDA line while the SCL line is low, data is transmitted.

Changing the SDA line while the SCL line is high, a start or stop condition is recognized.

Figure 11 Data Transmission Timing

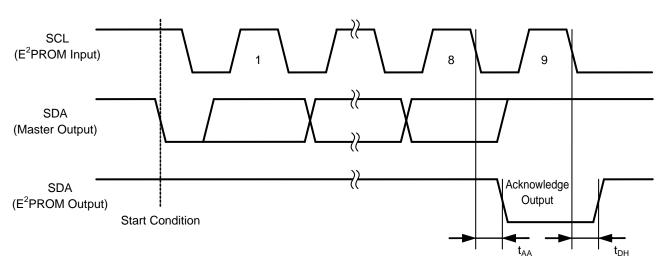

#### 4. Acknowledge

The unit of data transmission is 8 bits. During the 9th clock cycle period the receiver on the bus pulls down the SDA line to acknowledge the receipt of the 8-bit data.

When an internal write cycle is in progress, the device does not generate an acknowledge.

Figure 12 Acknowledge Output Timing

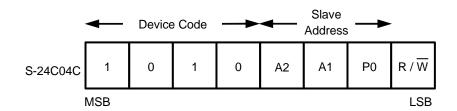

#### 5. Device addressing

To start communication, the master device on the system generates a start condition to the bus line. Next, the master device sends 7-bit device address and a 1-bit read / write instruction code on to the SDA bus.

The higher 4 bits of the device address are the "Device Code", and are fixed to "1010".

In the S-24C04C, successive 2 bits are the "Slave Address". These 2 bits are used to identify a device on the system bus and are compared with the predetermined value which is defined by the address input pins (A2, A1). When the comparison result matches, the slave device responds with an acknowledge during the 9th clock cycle.

The successive 1 bit (P0) is used to define a page address and choose the two 256-byte memory blocks (Address 000h to 0FFh and 100h to 1FFh).

Figure 13 Device Address

#### 6. Write

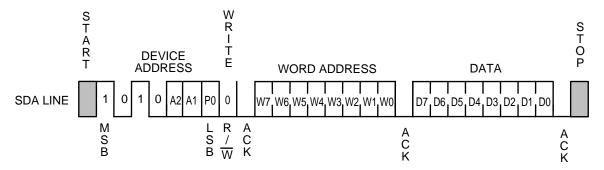

#### 6. 1 Byte write

When the master sends a 7-bit device address and a 1-bit read / write instruction code set to "0", following a start condition, the S-24C04C acknowledges it. The S-24C04C then receives an 8-bit word address and responds with an acknowledge. After the S-24C04C receives 8-bit write data and responds with an acknowledge, it receives a stop condition and that initiates the write cycle at the addressed memory.

During the write cycle all operations are forbidden and no acknowledge is generated.

Figure 14 Byte Write

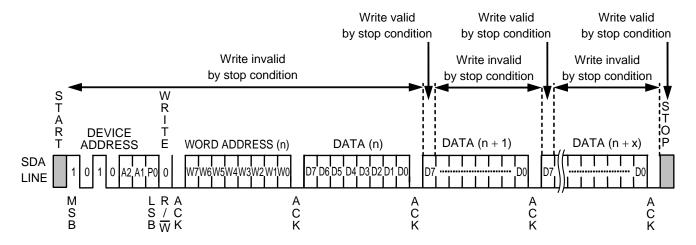

#### 6. 2 Page write

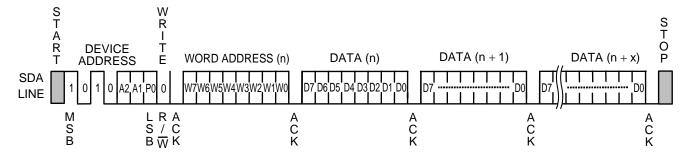

The page write mode allows up to 16 bytes to be written in a single write operation in the S-24C04C.

Its basic process to transmit data is as same as byte write, but it operates page write by sequentially receiving 8-bit write data as much data as the page size has.

When the S-24C04C receives a 7-bit device address and a 1-bit read / write instruction code set to "0", following a start condition, it generates an acknowledge. Then the S-24C04C receives an 8-bit word address, and responds with an acknowledge. After the S-24C04C receives 8-bit write data and responds with an acknowledge, it receives 8-bit write data corresponding to the next word address, and generates an acknowledge. The S-24C04C repeats reception of 8-bit write data and generation of acknowledge in succession. The S-24C04C can receive as many write data as the maximum page size.

Receiving a stop condition initiates a write cycle of the area starting from the designated memory address and having the page size equal to the received write data.

Figure 15 Page Write

In the S-24C04C, the lower 4 bits of the word address are automatically incremented every time when the S-24C04C receives 8-bit write data. If the size of the write data exceeds 16 bytes, the upper 4 bits of the word address and page address (P0) remain unchanged, and the lower 4 bits are rolled over and the last 16-byte data that the S-24C04C received will be overwritten.

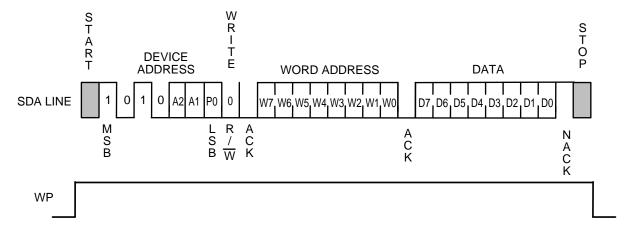

#### 6. 3 Write protect

Write protect is available in the S-24C04C. When the WP pin is connected to the  $V_{CC}$ , write operation to memory area is forbidden at all.

When the WP pin is connected to GND or set in open, the write protect is invalid, and write operation in all memory area is available.

Fix the level of the WP pin from start condition in the write operation (byte write, page write) until stop condition. If the WP pin changes during this time, the address data being written at this time is not guaranteed. Regarding the timing of write protect, refer to **Figure 8**.

In not using the write protect, connect the WP pin to GND or set it open. The write protect is valid in the range of operation power supply voltage.

As seen in **Figure 16** when the write protect is valid, the S-24C04C does not generate an acknowledgment signal after data input.

Figure 16 Write Protect

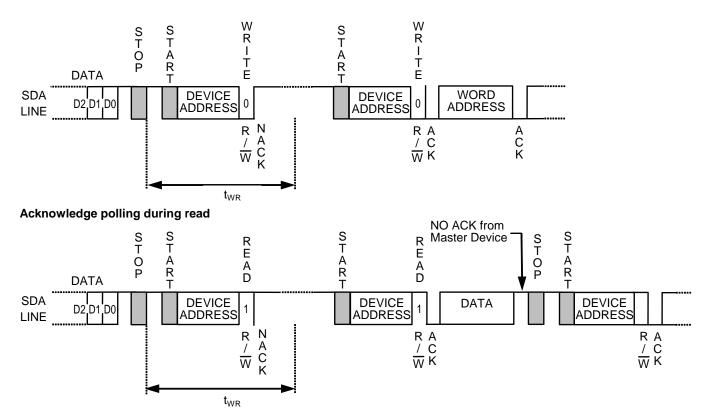

#### 6. 4 Acknowledge polling

Acknowledge polling is used to know the completion of the write cycle in the S-24C04C.

After the S-24C04C receives a stop condition and once starts the write cycle, all operations are forbidden and no response is made to the signal transmitted by the master device.

Accordingly the master device can recognize the completion of the write cycle in the S-24C04C by detecting a response from the slave device after transmitting the start condition, the device address and the read / write instruction code to the S-24C04C, namely to the slave devices.

That is, if the S-24C04C does not generate an acknowledge, the write cycle is in progress and if the S-24C04C generates an acknowledge, the write cycle has been completed.

It is recommended to use the read instruction "1" as the read / write instruction code transmitted by the master device.

#### Acknowledge polling during write

Remark

Users are able to input word address and data after ACK output in acknowledge polling during write.

Users are able to read data after ACK output in acknowledge polling during read. However, after that users input the write instruction, a start condition may not be input during data output. Input a stop condition and the next instruction after data output and ACK output.

Figure 17 Usage Example of Acknowledge Polling

#### 7. Read

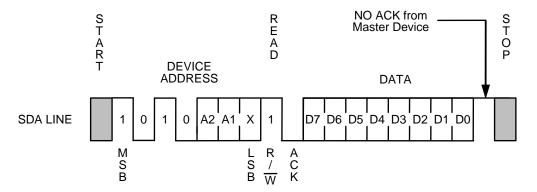

#### 7. 1 Current address read

Either in writing or in reading the S-24C04C holds the last accessed memory address. The memory address is maintained as long as the power voltage does not decrease less than the operating voltage.

The master device can read the data at the memory address of the current address pointer without assigning the word address as a result, when it recognizes the position of the address pointer in the S-24C04C. This is called "Current Address Read".

In the following the address counter in the S-24C04C is assumed to be "n".

When the S-24C04C receives a 7-bit device address and a 1-bit read / write instruction code set to "1" following a start condition, it responds with an acknowledge.

Next, an 8-bit data at the address "n" is sent from the S-24C04C synchronous to the SCL clock. The address counter is incremented and the content of the address counter becomes n + 1.

The master device outputs stop condition not an acknowledge, the reading of S-24C04C is ended.

Figure 18 Current Address Read

Attention should be paid to the following point on the recognition of the address pointer in the S-24C04C. In Read, the memory address counter in the S-24C04C is automatically incremented after output of the 8th bit of the data. In Write, on the other hand, the upper bits of the memory address (the upper bits of the word address and the page address<sup>1</sup>) are left unchanged and are not incremented.

\*1. In the S-24C04C, the upper 4 bits of the word address and the page address P0

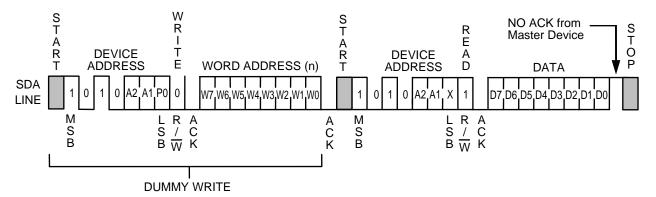

#### 7. 2 Random read

Random read is used to read the data at an arbitrary memory address.

A dummy write is performed to load the memory address into the address counter.

When the S-24C04C receives a 7-bit device address and a 1-bit read / write instruction code set to "0" following a start condition, it responds with an acknowledge.

And the S-24C04C receives 8-bit word address and responds with an acknowledge. The memory address is loaded to the address counter in the S-24C04C by these operations. Reception of write data does not follow in a dummy write whereas reception of write data follows in byte write and in page write.

Since the memory address is loaded into the memory address counter by dummy write, the master device can read the data starting from the arbitrary memory address by transmitting a new start condition and performing the same operation in the current address read.

That is, when the S-24C04C receives a 7-bit device address and a 1-bit read / write instruction code set to "1", following a start condition signal, it responds with an acknowledge. Next, 8-bit data is transmitted from the S-24C04C in synchronous to the SCL clock. The master device outputs stop condition not an acknowledge, the reading of S-24C04C is ended.

Figure 19 Random Read

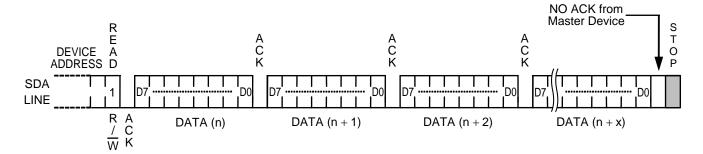

#### 7.3 Sequential read

When the S-24C04C receives a 7-bit device address and a 1-bit read / write instruction code set to "1" following a start condition both in current address read and random read, it responds with an acknowledge.

When an 8-bit data is output from the S-24C04C synchronous to the SCL clock, the address counter is automatically incremented.

When the master device responds with an acknowledge, the data at the next memory address is transmitted. Response with an acknowledge by the master device has the memory address counter in the S-24C04C incremented and makes it possible to read data in succession. This is called "Sequential Read".

The master device outputs stop condition not an acknowledge, the reading of S-24C04C is ended.

Data can be read in succession in the sequential read mode. When the memory address counter reaches the last word address, it rolls over to the first word address.

Figure 20 Sequential Read

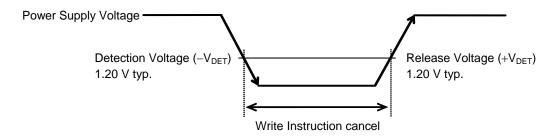

# ■ Write Protect Function during the Low Power Supply Voltage

The S-24C04C has a built-in detection circuit which operates with the low power supply voltage, cancels Write when the power supply voltage drops and power-on. Its detection and release voltages are 1.20 V typ. (Refer to **Figure 21**). The S-24C04C cancels Write by detecting a low power supply voltage when it receives a stop condition. In the data trasmission and the Write operation, data in the address written during the low power supply voltage is not assurable.

Figure 21 Operation during Low Power Supply Voltage

# ■ Using S-24C04C

## 1. Adding a pull-up resistor to SDA I/O pin and SCL input pin

In consideration of  $I^2$ C-bus protocol function, the SDA I/O pins should be connected with a pull-up resistor. The S-24C04C cannot transmit normally without using a pull-up resistor.

In case that the SCL input pin of the S-24C04C is connected to the Nch open drain output pin of the master device, connect the SCL pin with a pull-up resistor. As well, in case the SCL input pin of the S-24C04C is connected to the tristate output pin of the master device, connect the SCL pin with a pull-up resistor in order not to set it in high impedance. This prevents the S-24C04C from error caused by an uncertain output (high impedance) from the tri-state pin when resetting the master device during the voltage drop.

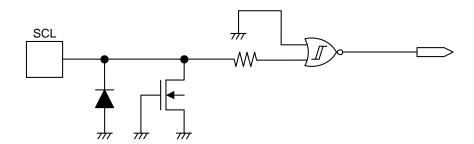

#### 2. Equivalent circuit of input and I/O pin

Each pin (SCL, SDA) of the S-24C04C does not have a built-in pull-down or pull-up resistor. The WP, A1, A2 pin includes a pull-down resistor. The SDA line has an open-drain output. The followings are equivalent circuits of the pins.

Figure 22 SCL Pin

Figure 23 SDA Pin

Figure 24 WP Pin

Figure 25 A1, A2 Pins

22

#### 3. Phase adjustment during S-24C04C access

The S-24C04C does not have a pin to reset (the internal circuit). The users cannot forcibly reset it externally. If the communication to the S-24C04C interrupted, the users need to handle it as you do for software.

In the S-24C04C, users are able to reset the internal circuit by inputting a start condition and a stop condition.

Although the reset signal is input to the master device, the S-24C04C's internal circuit does not go in reset, but it does by inputting a stop condition to the S-24C04C. The S-24C04C keeps the same status thus cannot do the next operation. Especially, this case corresponds to that only the master device is reset when the power supply voltage drops.

If the power supply voltage restored in this status, input the instruction after resetting (adjusting the phase with the master device) the S-24C04C. How to reset is shown below.

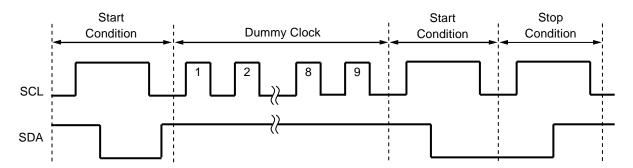

#### [How to reset S-24C04C]

The S-24C04C is able to be reset by a start and stop instructions. When the S-24C04C is reading data "0" or is outputting the acknowledgment signal, outputs "0" to the SDA line. In this status, the master device cannot output an instruction to the SDA line. In this case, terminate the acknowledgment output operation or the Read operation, and then input a start instruction. **Figure 26** shows this procedure.

First, input a start condition. Then transmit 9 clocks (dummy clock) of SCL. During this time, the master device sets the SDA line to "H". By this operation, the S-24C04C interrupts the acknowledgment output operation or data output, so input a start condition<sup>\*1</sup>. When a start condition is input, the S-24C04C is reset. To make doubly sure, input the stop condition to the S-24C04C. The normal operation is then possible.

Figure 26 Resetting S-24C04C

\*1. After 9 clocks (dummy clock), if the SCL clock continues to being output without inputting a start condition, S-24C04C may go in the write operation when it receives a stop condition. To prevent this, input a start condition after 9 clocks (dummy clock).

**Remark** Regarding this reset procedure with dummy clock, it is recommended to perform at the system initialization after applying the power supply voltage.

#### 4. Acknowledge check

The I<sup>2</sup>C-bus protocol includes an acknowledge check function as a handshake function to prevent a communication error. This function allows detection of a communication failure during data communication between the master device and S-24C04C. This function is effective to prevent malfunction, so it is recommended to perform an acknowledge check with the master device.

#### 5. Built-in power-on-clear circuit

The S-24C04C has a built-in power-on-clear circuit that initializes itself at the same time during power-on. Unsuccessful initialization may cause a malfunction. To operate the power-on-clear circuit normally, the following conditions must be satisfied to raise the power supply voltage.

#### 5. 1 Raising power supply voltage

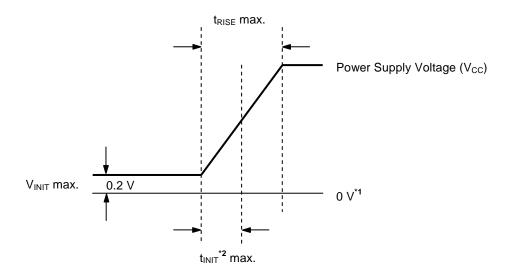

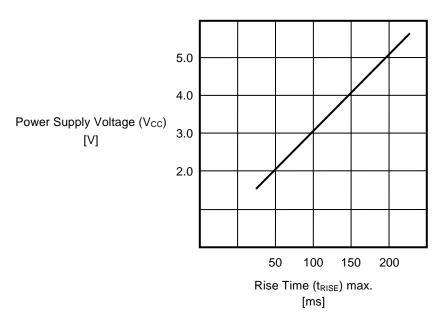

Shown in **Figure 27**, raise the power supply voltage from 0.2 V max., within the time defined as  $t_{RISE}$  which is the time required to reach the power supply voltage to be set.

For example, if the power supply voltage is 5.0 V,  $t_{RISE} = 200 \text{ ms}$  seen in **Figure 28**. The power supply voltage must be raised within 200 ms.

- \*1. 0 V means there is no difference in potential between the VCC pin and the GND pin of the S-24C04C.

- \*2. t<sub>INIT</sub> is the time required to initialize the S-24C04C. No instructions are accepted during this time.

Figure 27 Raising Power Supply Voltage

For example: If the supply voltage = 5.0 V, raise the power supply voltage to 5.0 V within 200 ms.

Figure 28 Rise Time of Power Supply Voltage

When initialization is successfully completed by the power-on-clear circuit, the S-24C04C enters the standby status.

If the power-on-clear circuit does not operate;

The S-24C04C has not completed initialization, an instruction previously input is still valid or an instruction may be inappropriately recognized. In this case, S-24C04C may perform the Write operation.

The voltage drops due to power off while the S-24C04C is being accessed. Even if the master device is reset due to the low power voltage, the S-24C04C may malfunction unless the power-on-clear operation conditions of S-24C04C are satisfied.

When not using this rise time seen in **Figure 28**, adjust the phase (reset) to reset the internal circuit in the S-24C04C normally.

#### 5. 2 Initialization time

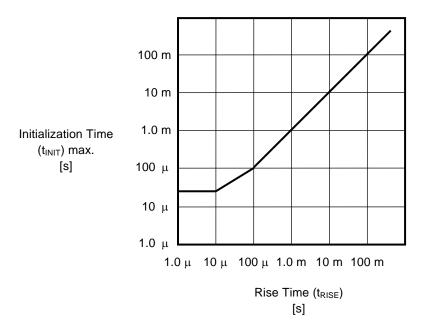

The S-24C04C initializes at the same time when the power supply voltage is raised. Input instructions to the S-24C04C after initialization. S-24C04C does not accept any instruction during initialization.

Figure 29 shows the initialization time of the S-24C04C.

Figure 29 Initialization Time of S-24C04C

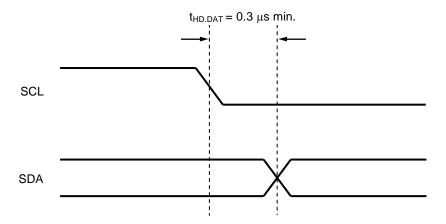

#### 6. Data hold time $(t_{HD.DAT} = 0 \text{ ns})$

If SCL and SDA of the S-24C04C are changed at the same time, it is necessary to prevent a start / stop condition from being mistakenly recognized due to the effect of noise.

The S-24C04C may error if it does not recognize a start / stop condition correctly during transmission.

In the S-24C04C, it is recommended to set the delay time of  $0.3~\mu s$  minimum from a falling edge of SCL for the SDA. This is to prevent S-24C04C from going in a start / stop condition due to the time lag caused by the load of the bus line.

Figure 30 S-24C04C Data Hold Time

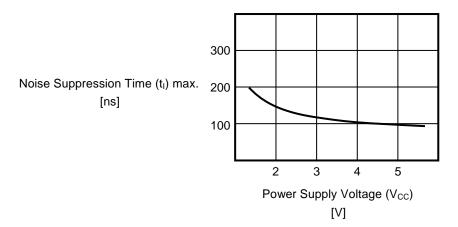

#### 7. SDA pin and SCL pin noise suppression time

The S-24C04C includes a built-in low-pass filter at the SDA and SCL pins to suppress noise. This means that if the power supply voltage is 5.0 V, noise with a pulse width of 100 ns or less can be suppressed. For details of the assurable value, refer to noise suppression time (t<sub>i</sub>) in **Table 14**.

Figure 31 Noise Suppression Time for SDA and SCL Pins

#### 8. Operation when input stop condition during input write data

The S-24C04C does the write operation only when it receives data of 1 byte or more and receives a stop condition immediately after ACK output.

Refer to Figure 32 regarding details.

Figure 32 Write Operation by Inputting Stop Condition during Write

#### 9. Command cancel by start condition

By a start condition, users are able to cancel command which is being input. However, adjust the phase while the S-24C04C is outputting "L" because users are not able to input a start condition. When users cancel the command, there may be a case that the address will not be identified. Use random read for the read operation, not current address read.

#### 10. Precaution for use

Absolute maximum ratings: Do not operate these ICs in excess of the absolute maximum ratings (as listed on the data sheet). Exceeding the supply voltage rating can cause latch-up.

Operations with moisture on the S-24C04C pins may occur malfunction by short-circuit between pins. Especially, in occasions like picking the S-24C04C up from low temperature tank during the evaluation. Be sure that not remain frost on the S-24C04C pin to prevent malfunction by short-circuit.

Also attention should be paid in using on environment, which is easy to dew for the same reason.

# ■ Precautions

- Do not apply an electrostatic discharge to this IC that exceeds the performance ratings of the built-in electrostatic protection circuit.

- SII claims no responsibility for any and all disputes arising out of or in connection with any infringement of the products including this IC upon patents owned by a third party.

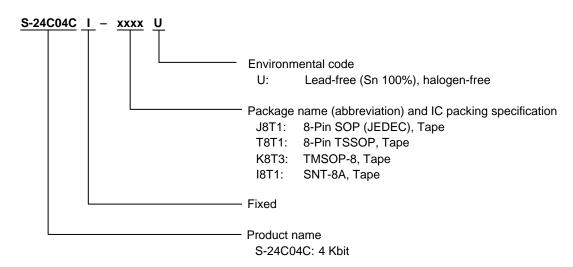

# **■ Product Name Structure**

#### 1. Product name

#### 2. Packages

| Dookogo nomo      | Drawing code |              |              |              |

|-------------------|--------------|--------------|--------------|--------------|

| Package name      | Package      | Tape         | Reel         | Land         |

| 8-Pin SOP (JEDEC) | FJ008-Z-P-SD | FJ008-Z-C-SD | FJ008-Z-R-SD | _            |

| 8-Pin TSSOP       | FT008-Z-P-SD | FT008-Z-C-SD | FT008-Z-R-SD | _            |

| TMSOP-8           | FM008-A-P-SD | FM008-A-C-SD | FM008-A-R-SD | _            |

| SNT-8A            | PH008-A-P-SD | PH008-A-C-SD | PH008-A-R-SD | PH008-A-L-SD |

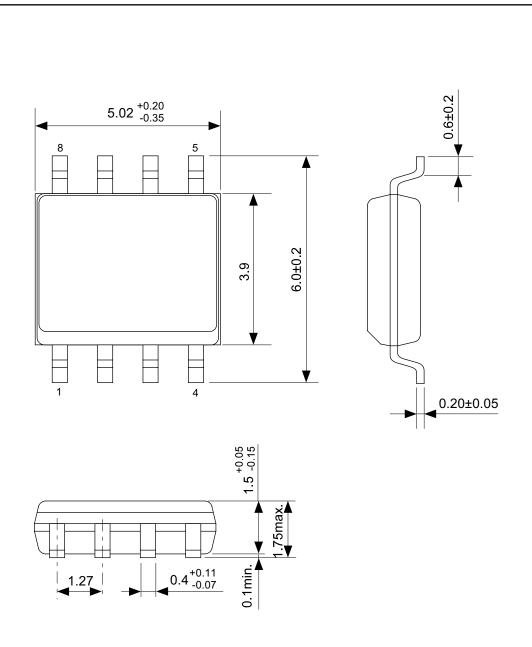

# No. FJ008-Z-P-SD-2.0

| TITLE                  | SOP8J-Z-PKG Dimensions |  |

|------------------------|------------------------|--|

| No.                    | FJ008-Z-P-SD-2.0       |  |

| SCALE                  |                        |  |

| UNIT                   | mm                     |  |

|                        |                        |  |

|                        |                        |  |

|                        |                        |  |

| Seiko Instruments Inc. |                        |  |

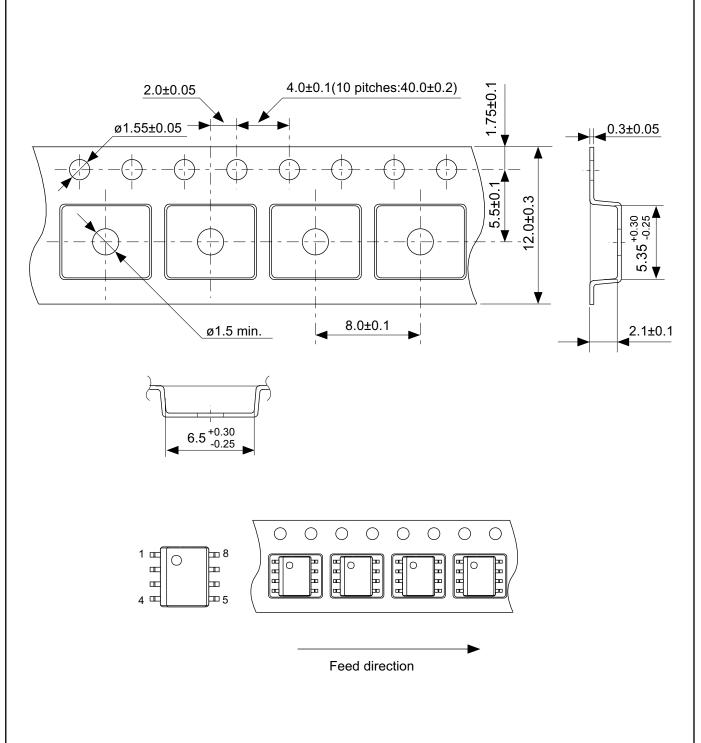

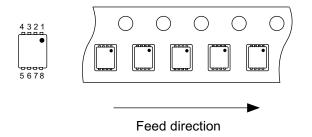

# No. FJ008-Z-C-SD-1.0

| TITLE                  | SOP8J-Z-Carrier Tape |  |

|------------------------|----------------------|--|

| No.                    | FJ008-Z-C-SD-1.0     |  |

| SCALE                  |                      |  |

| UNIT                   | mm                   |  |

|                        |                      |  |

|                        |                      |  |

| Seiko Instruments Inc. |                      |  |

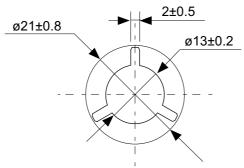

Enlarged drawing in the central part

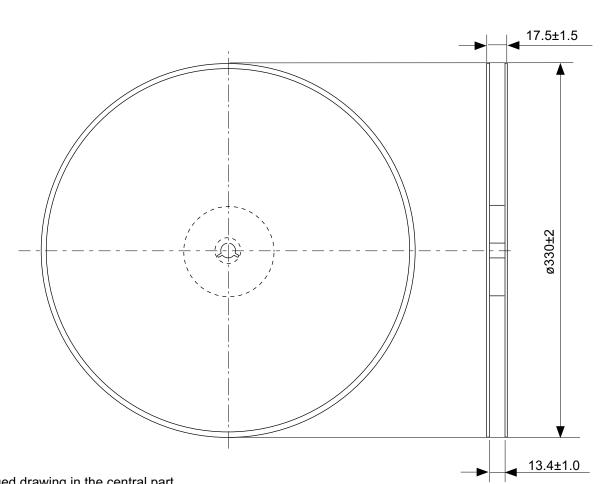

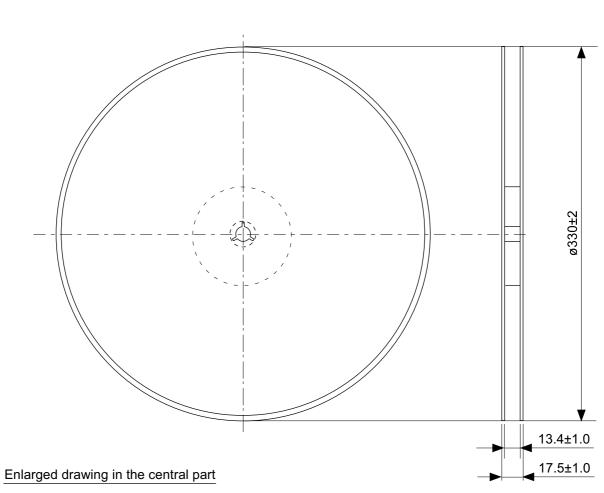

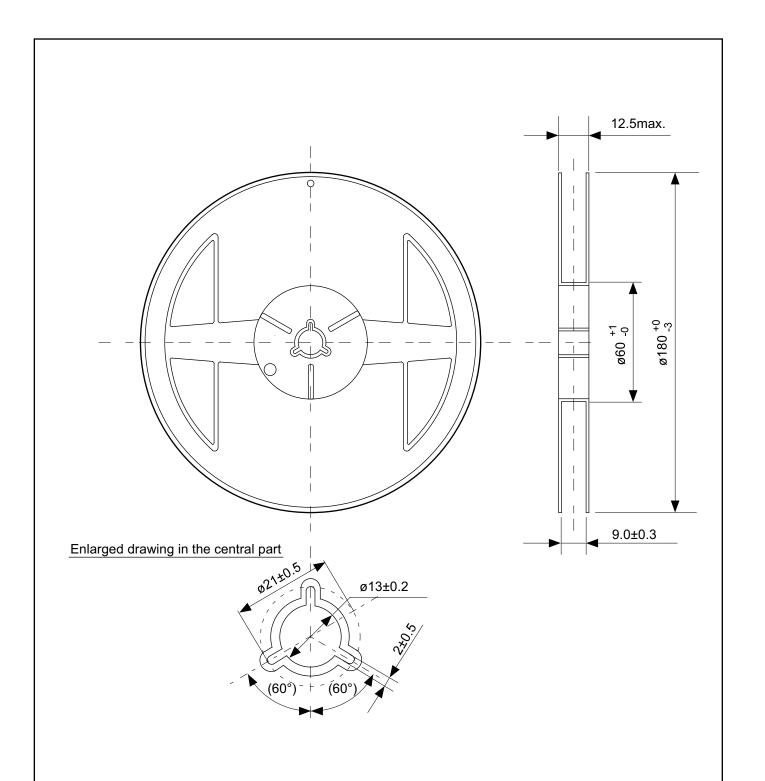

# No. FJ008-Z-R-SD-1.0

| TITLE                  | SOP   | 8J-Z-Re | el    |

|------------------------|-------|---------|-------|

| No.                    | FJ008 | Z-R-SD- | 1.0   |

| SCALE                  |       | QTY.    | 4,000 |

| UNIT                   | mm    |         |       |

|                        |       |         |       |

|                        |       |         |       |

|                        |       |         |       |

| Seiko Instruments Inc. |       |         |       |

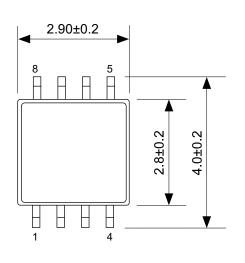

# No. FT008-Z-P-SD-1.0

| TITLE                  | TSSOP8-Z-PKG Dimensions |  |

|------------------------|-------------------------|--|

| No.                    | FT008-Z-P-SD-1.0        |  |

| SCALE                  |                         |  |

| UNIT                   | mm                      |  |

|                        |                         |  |

|                        |                         |  |

|                        |                         |  |

|                        |                         |  |

| Seiko Instruments Inc. |                         |  |

# No. FT008-Z-C-SD-1.0

| TITLE                  | TSSOP8-Z-Carrier Tape |  |

|------------------------|-----------------------|--|

| No.                    | FT008-Z-C-SD-1.0      |  |

| SCALE                  |                       |  |

| UNIT                   | mm                    |  |

|                        |                       |  |

|                        |                       |  |

|                        |                       |  |

| Seiko Instruments Inc. |                       |  |

# No. FT008-Z-R-SD-1.0

| TITLE                  | TSSOP8-Z-Reel |     |          |       |

|------------------------|---------------|-----|----------|-------|

| No.                    | F             | T00 | 8-Z-R-SD | -1.0  |

| SCALE                  |               |     | QTY.     | 4,000 |

| UNIT                   | mm            |     |          |       |

|                        |               |     |          |       |

|                        |               |     |          |       |

| Cailea Instrumenta Ins |               |     |          |       |

| Seiko Instruments Inc. |               |     |          |       |

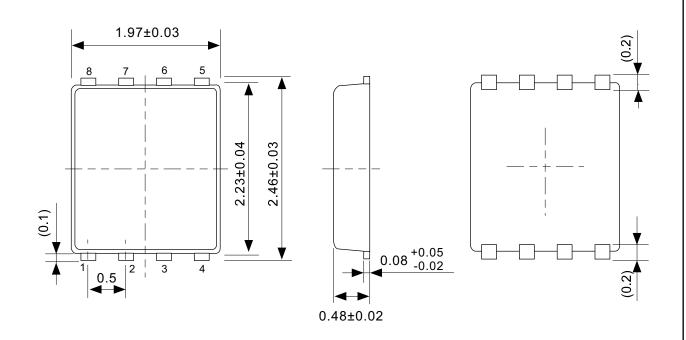

# No. FM008-A-P-SD-1.1

| TITLE | TMSOP8-A-PKG Dimensions |

|-------|-------------------------|

| No.   | FM008-A-P-SD-1.1        |

| SCALE |                         |

| UNIT  | mm                      |

|       |                         |

|       |                         |

|       |                         |

|       | Seiko Instruments Inc.  |

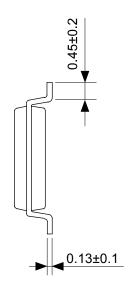

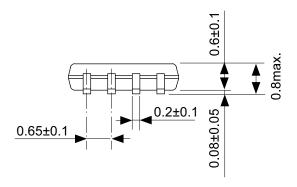

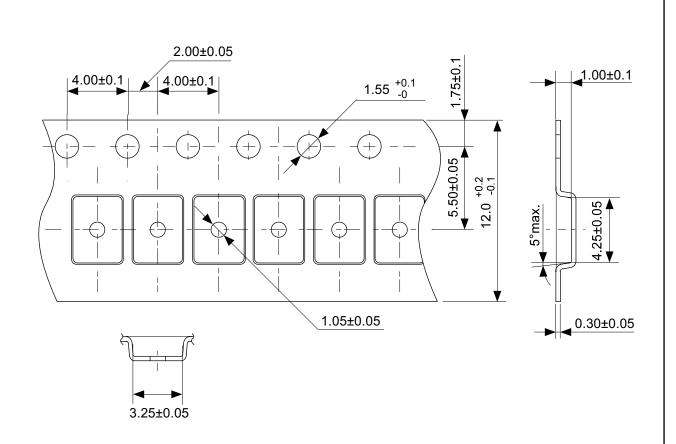

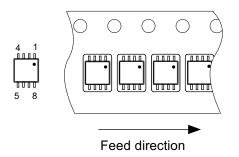

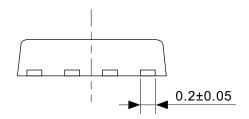

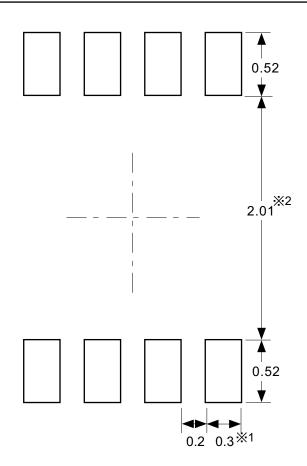

# No. FM008-A-C-SD-1.0

| TITLE | TMSOP8-A-Carrier Tape  |

|-------|------------------------|

| No.   | FM008-A-C-SD-1.0       |

| SCALE |                        |

| UNIT  | mm                     |

|       |                        |

|       |                        |

|       |                        |

|       | Seiko Instruments Inc. |

| TITLE | TMSOP8-A-Reel    |         |       |

|-------|------------------|---------|-------|

| No.   | FM008-A-R-SD-1.0 |         |       |

| SCALE |                  | QTY.    | 4,000 |

| UNIT  | mm               | -       |       |

|       |                  |         |       |

|       |                  |         |       |

|       | Seiko Instr      | ruments | Inc.  |

# No. PH008-A-P-SD-2.0

| TITLE                  | SNT-8A-A-PKG Dimensions |  |

|------------------------|-------------------------|--|

| No.                    | PH008-A-P-SD-2.0        |  |

| SCALE                  |                         |  |

| UNIT                   | mm                      |  |

|                        |                         |  |

|                        |                         |  |

|                        |                         |  |

|                        |                         |  |

| Seiko Instruments Inc. |                         |  |

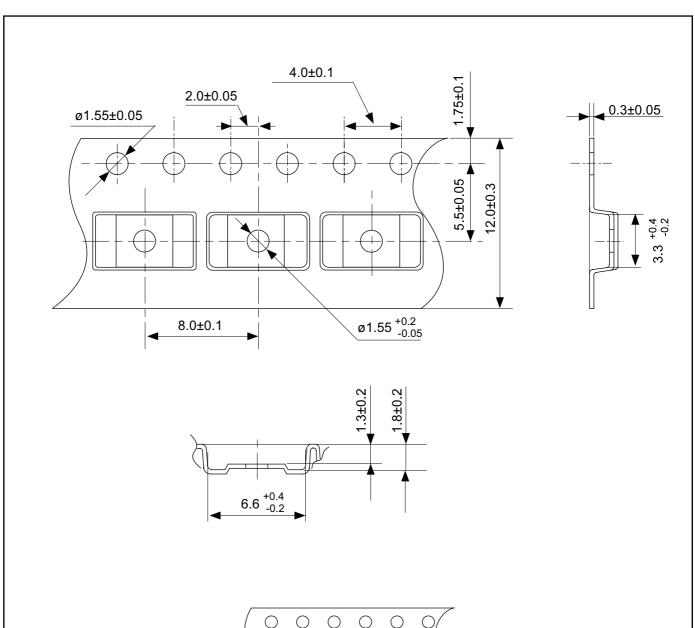

# No. PH008-A-C-SD-1.0

| TITLE                  | SNT-8A-A-Carrier Tape |  |

|------------------------|-----------------------|--|

| No.                    | PH008-A-C-SD-1.0      |  |

| SCALE                  |                       |  |

| UNIT                   | mm                    |  |

|                        |                       |  |

|                        |                       |  |

|                        |                       |  |

|                        |                       |  |

| Seiko Instruments Inc. |                       |  |

# No. PH008-A-R-SD-1.0

| TITLE                 | SNT-8A-A-Reel    |      |       |

|-----------------------|------------------|------|-------|

| No.                   | PH008-A-R-SD-1.0 |      |       |

| SCALE                 |                  | QTY. | 5,000 |

| UNIT                  | mm               |      |       |

|                       |                  |      |       |

|                       |                  |      |       |

|                       |                  |      |       |

| Seiko Instruments Inc |                  |      |       |

- ※1. ランドパターンの幅に注意してください (0.25 mm min. / 0.30 mm typ.)。 ※2. パッケージ中央にランドパターンを広げないでください (1.96 mm ~ 2.06 mm)。

- 注意 1. パッケージのモールド樹脂下にシルク印刷やハンダ印刷などしないでください。

- 2. パッケージ下の配線上のソルダーレジストなどの厚みをランドパターン表面から0.03 mm 以下にしてください。

- 3. マスク開口サイズと開口位置はランドパターンと合わせてください。

- 4. 詳細は "SNTパッケージ活用の手引き" を参照してください。

- ※1. Pay attention to the land pattern width (0.25 mm min. / 0.30 mm typ.).

- X2. Do not widen the land pattern to the center of the package (1.96 mm to 2.06mm).

- Caution 1. Do not do silkscreen printing and solder printing under the mold resin of the package.

- 2. The thickness of the solder resist on the wire pattern under the package should be 0.03 mm or less from the land pattern surface.

- 3. Match the mask aperture size and aperture position with the land pattern.

- 4. Refer to "SNT Package User's Guide" for details.

- ※1. 请注意焊盘模式的宽度 (0.25 mm min. / 0.30 mm typ.)。

- ※2. 请勿向封装中间扩展焊盘模式 (1.96 mm ~ 2.06 mm)。

- 注意 1. 请勿在树脂型封装的下面印刷丝网、焊锡。

- 2. 在封装下、布线上的阻焊膜厚度 (从焊盘模式表面起) 请控制在0.03 mm以下。

- 3. 掩膜的开口尺寸和开口位置请与焊盘模式对齐。

- 4. 详细内容请参阅 "SNT封装的应用指南"。

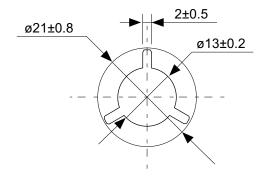

No. PH008-A-L-SD-4.0

| SNT-8A-A-Land Recommendation |

|------------------------------|

| PH008-A-L-SD-4.0             |

|                              |

| mm                           |

|                              |

|                              |

|                              |

| eiko Instruments Inc.        |

|                              |

# SII Seiko Instruments Inc. www.sii-ic.com

- The information described herein is subject to change without notice.

- Seiko Instruments Inc. is not responsible for any problems caused by circuits or diagrams described herein

whose related industrial properties, patents, or other rights belong to third parties. The application circuit

examples explain typical applications of the products, and do not guarantee the success of any specific

mass-production design.

- When the products described herein are regulated products subject to the Wassenaar Arrangement or other agreements, they may not be exported without authorization from the appropriate governmental authority.

- Use of the information described herein for other purposes and/or reproduction or copying without the express permission of Seiko Instruments Inc. is strictly prohibited.

- The products described herein cannot be used as part of any device or equipment affecting the human body, such as exercise equipment, medical equipment, security systems, gas equipment, vehicle equipment, in-vehicle equipment, aviation equipment, aerospace equipment, and nuclear-related equipment, without prior written permission of Seiko Instruments Inc.

- The products described herein are not designed to be radiation-proof.

- Although Seiko Instruments Inc. exerts the greatest possible effort to ensure high quality and reliability, the

failure or malfunction of semiconductor products may occur. The user of these products should therefore

give thorough consideration to safety design, including redundancy, fire-prevention measures, and

malfunction prevention, to prevent any accidents, fires, or community damage that may ensue.

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

ABLIC:

S-24C04CI-I8T1U

OOO «ЛайфЭлектроникс" "LifeElectronics" LLC

ИНН 7805602321 КПП 780501001 P/C 40702810122510004610 ФАКБ "АБСОЛЮТ БАНК" (ЗАО) в г.Санкт-Петербурге К/С 3010181090000000703 БИК 044030703

Компания «Life Electronics» занимается поставками электронных компонентов импортного и отечественного производства от производителей и со складов крупных дистрибьюторов Европы, Америки и Азии.

С конца 2013 года компания активно расширяет линейку поставок компонентов по направлению коаксиальный кабель, кварцевые генераторы и конденсаторы (керамические, пленочные, электролитические), за счёт заключения дистрибьюторских договоров

#### Мы предлагаем:

- Конкурентоспособные цены и скидки постоянным клиентам.

- Специальные условия для постоянных клиентов.

- Подбор аналогов.

- Поставку компонентов в любых объемах, удовлетворяющих вашим потребностям.

- Приемлемые сроки поставки, возможна ускоренная поставка.

- Доставку товара в любую точку России и стран СНГ.

- Комплексную поставку.

- Работу по проектам и поставку образцов.

- Формирование склада под заказчика.

- Сертификаты соответствия на поставляемую продукцию (по желанию клиента).

- Тестирование поставляемой продукции.

- Поставку компонентов, требующих военную и космическую приемку.

- Входной контроль качества.

- Наличие сертификата ISO.

В составе нашей компании организован Конструкторский отдел, призванный помогать разработчикам, и инженерам.

Конструкторский отдел помогает осуществить:

- Регистрацию проекта у производителя компонентов.

- Техническую поддержку проекта.

- Защиту от снятия компонента с производства.

- Оценку стоимости проекта по компонентам.

- Изготовление тестовой платы монтаж и пусконаладочные работы.

Тел: +7 (812) 336 43 04 (многоканальный) Email: org@lifeelectronics.ru