## **IQS229** Datasheet

## Single Channel Capacitive Proximity/Touch Controller for SAR Applications

The IQS229 ProxSense<sup>®</sup> IC is a self-capacitance controller designed for applications that are required to meet SAR regulations. The IQS229 can also be used to detect a long term presence as a movement detector. The IQS229 operates standalone and can be configured via digital inputs.

## **Features**

- SAR compliance in mobile devices according to the IEC 62209-2 ed1.0 standard and the FCC standard (KDB 616217 - D04 SAR for laptop and tablets v01)

- Failsafe firmware/hardware design

- Automatic Tuning (ATI)

- On-chip movement detection algorithm

- Minimal external components

- Standalone operation

- 25mm detection distance

- Up to 60pF sensor load

- Internal Capacitor Implementation (ICI) reference capacitor on-chip

- Configuration settings via external pins

- Activation threshold

- Movement filter threshold

## **Applications**

- SAR detection for tablets and mobile phones

- SAR detection for wireless charging stations (operating frequency > 100 MHz)

- SAR detection for USB dongle-type devices

- Movement detection devices (anti-theft)

- Activation time-out

- Supply voltage: 1.8V to 3.6V

- Low power consumption: 30uA (sub 10uA in sleep mode)

- Low profile DFN10 package (3x3)

- Reed relay replacement

- White goods and appliances

- Human Interface Devices

- Proximity activated backlighting

- Applications with long-term activation

| Available Packages         |        |  |  |  |

|----------------------------|--------|--|--|--|

| T <sub>A</sub> DFN10 (3x3) |        |  |  |  |

| -40°C to 85°C              | IQS229 |  |  |  |

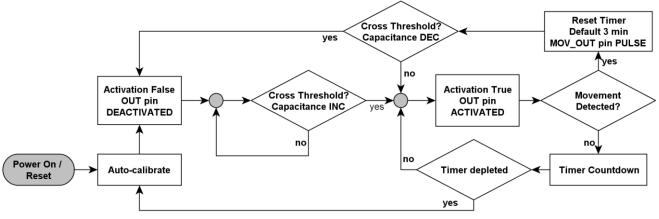

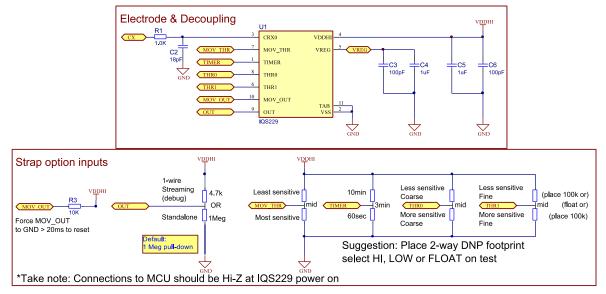

Figure 1.1 Flow diagram of the IQS229 user interface

## **1** Overview

## 1.1 Device

The IQS229 is a device tailored for longterm proximity or touch activations. It offers two Boolean outputs, one with an activation threshold for large capacitive shifts and the other with a threshold for small movements even during a normal activation.

## **1.1.1 Normal operation**

With a normal activation (hand brought close) the output will become active. The output will de-activate as soon as the action is reversed (hand taken away). In addition a separate movement output will become active when movement is detected according to a movement threshold. Movement may be detected before the normal threshold is crossed. Movement

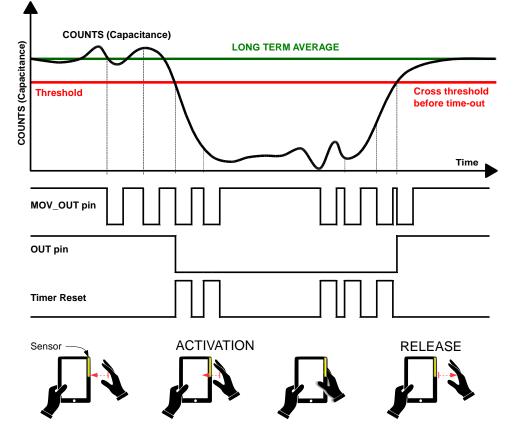

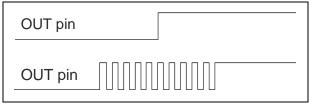

## Figure 1.2 Plot of IQS229 streaming data along with the digital response

detection is done via a completely separate digital filter while improving the efficiency of the sensor output (timer reset on movement).

## 1.1.2 Long term activation

In a normal activation the output will stay active for as long as movements are detected. A time-out timer (configurable time) will be reset with each movement.

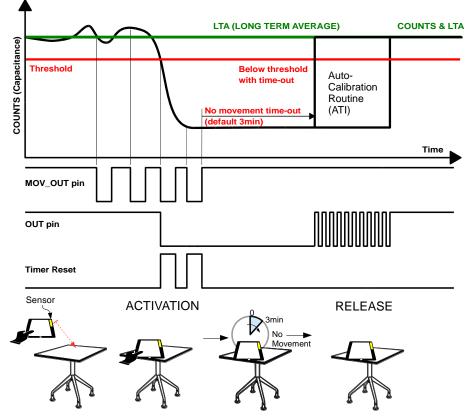

## 1.1.3 Long term recovery

When changing the sensor capacitive environment, the sensor will adapt to the new environment. If the new environment decreases capacitance (wooden table to air), the sensor will rapidly adapt in order to accept new human activations. If the new environment increases capacitance (like air to steel table), the sensor will remain in activation until a time-out occurs (as seen time-out with no movement around the sensor.

## 1.1.4 Fail-safe features

For SAR application the device includes various features to ensure fail-safe operation:

- Active low with pull-down resistor ensures activation with failure (at the cost of leakage current with no activation)

- Hard reset by pulling the movement pin low. This allows for a restart and device status check.

- Characteristic toggle on output pin with power-up and soft reset to check if the IC is functioning.

## 1.1.5 Integrated features

The device includes an internal voltage

#### Figure 1.3 Example of a time-out event with re-calibration

in Figure 1.3) or until the device is returned to its previous environment.

When the timer runs out, the output will be de-activated. Re-calibration is possible after de-activation because the timer will only regulator and reference capacitor (C<sub>s</sub>).

Various advanced signal processing techniques are combined for creating a robust solution.

These techniques include:

- Movement detection filter (to release an activation in the case of inactivity)

- Advanced noise filtering on incoming sample stream

- Superior methods of parasitic capacitance compensation while preserving sensitivity

## **1.1.6 Data streaming**

A 1-wire data streaming interface is offered for debugging purposes. Streaming mode and stand-alone mode are interchangeable via simple hardware configurations. This is offered because streaming may be useful at various stages of a design.

Streaming mode is offered through a simple pull-up resistor on the standard digital output pin. Standalone mode is enabled through a pull-down resistor on this pin.

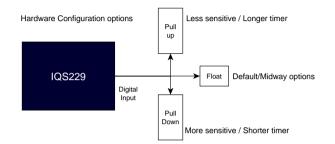

## **1.1.7 Hardware configuration options**

Various configuration options are made available through digital input pins. These include:

- the activation threshold,

- inactivity time-out settings

- and movement threshold selection

Special device configurations are only available on special request and can be done by setting one time programmable (OTP) options. These will only be available on special orders, aiming to meet most needs with configuration pins.

## **1.1.8 Automatic Calibration**

Proven Automatic Tuning Implementation (ATI) algorithms are used to calibrate the device to the sense electrode. This algorithm is optimised for applications where a fixed detection distance (in mid-air) is required for failure safe detection.

## **1.1.9 Capacitive sensing method**

The *charge transfer* method of capacitive sensing is employed on the IQS229. (The charge transfer principle is thoroughly

described in the application note: "<u>AZD004</u> - Azoteq Capacitive Sensing".)

## 1.2 **Operation**

## 1.2.1 Device Setup

Typical device use allows for very little to no setup before integration. A few characteristics may be fixed via four of the IQS229 pins - each having three possible pin states. This should suffice for most simple and intended applications.

**Note:** It is important that any pins connected to an MCU are kept high impedance (Hi-Z) from the MCU side during power-up. This is to ensure correct start-up especially with a high impedance strap resistor on the OUT pin for standalone power-up.

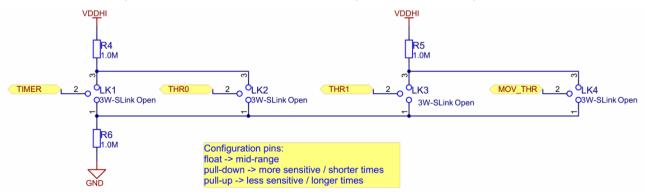

## 1.2.2 Configuration pin setup

Configuration options are selected by:

- Floating a pin

- pull-up resistor

- pull-down resistor

See section 0 for choosing a specific configuration. For configurations not covered by the configuration pins, custom ICs will be available in bulk orders. Information on custom configurations are available on special request.

At start-up device parameters are read and set according to the configuration pin states. Configuration pins are then changed to digital outputs and are written to the state that was read (for minimising current consumption<sup>1</sup>). Floating pins are written low. After configuration, calibration routines are run which can be run periodically in order to run with optimal sensitivity.

## **1.2.3 Movement filters**

The movement filter runs continually and the dedicated digital output will activate for

$<sup>^1</sup>$  Known issue & workaround: The THR0 and TIMER pin are written low when pulled high. Use a 1M $\Omega$  on these pins to limit current consumption.

a time depending on the intensity of the movement.

## **1.2.4 External control**

The movement output (optional line to connect to master device) can be used to signal a "reseed" ( $t_{reseed}$ ) or "sleep mode" ( $t_{sleep}$ ). A short pulse will force the reference counts (long-term average) to match the actual counts (capacitance of sensor). By writing the pin low for a longer time, will force the IC into sleep mode for low current consumption (2uA + required pull-up on movement pin). When sleep mode is entered, the IQS229 will reset upon wake-up.

In sleep mode the output pin is written low in order to minimise current consumption.

## 1.2.5 Low power options

As mentioned in the section above, a charge halt will initiate the sleep mode. The device will reset and return to normal power as soon as the line is released.

## **1.3 Applicability**

All specifications, except where specifically mentioned otherwise, provided by this datasheet are applicable to the following ranges:

Temperature:-40C to +85C Supply voltage (V<sub>DDHI</sub>): 1.8V to 3.6V

# 1.4 Passing the SAR qualification testing with the IQS229

For design information on passing the SAR qualification testing with Azoteq movement based sensors, please see the application note: "AZD073 SAR qualification with Azoteq movement-based sensors"

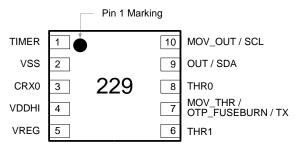

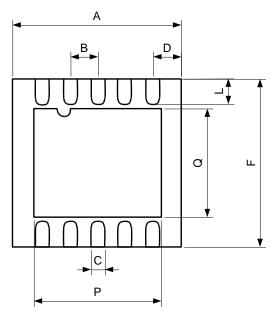

## 2 Packaging and Pin-Out

The IQS229 is available in a DFN10 (3x3) package.

## Figure 2.1 IQS229 pin-out (DFN10 package)

#### Table 2.1 Pin-out description

|     | IQS229 in DFN10                   |                      |                                                                                                                                                                                               |  |  |  |  |

|-----|-----------------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin | Name                              | Туре                 | Function                                                                                                                                                                                      |  |  |  |  |

| 1   | TIMER                             | Digital Input        | "No movement" timeout period selection                                                                                                                                                        |  |  |  |  |

| 2   | VSS                               | Signal GND           |                                                                                                                                                                                               |  |  |  |  |

| 3   | CRX0                              | Sense electrode      | Connect to conductive area intended for sensor                                                                                                                                                |  |  |  |  |

| 4   | VDDHI                             | Supply Input         | Supply:1.8V – 3.6V                                                                                                                                                                            |  |  |  |  |

| 5   | VREG                              | Regulator output     | Requires external capacitor                                                                                                                                                                   |  |  |  |  |

| 6   | THR1                              | Digital Input        | Threshold1 selection (fine)                                                                                                                                                                   |  |  |  |  |

| 7   | MOV_THR /<br>OTP_FUSEBURN /<br>TX | Digital Input        | Movement Threshold selection / Connect to<br>configuration device for changing OTP<br>options<br>Projected capacitance option TX electrode                                                    |  |  |  |  |

| 8   | THR0                              | Digital Input        | Threshold0 selection (coarse)                                                                                                                                                                 |  |  |  |  |

| 9   | OUT / SDA                         | Digital Output/Input | Activation output (active low) / 1-wire Data /<br>Input at power-up to determine standalone<br>or streaming<br>I <sup>2</sup> C data pin for configuration and I <sup>2</sup> C debug<br>mode |  |  |  |  |

| 10  | MOV_OUT / SCL                     | Digital Output/Input | Movement output (active low) / Input for<br>reseed and charge halt<br>I <sup>2</sup> C clock pin for configuration and I <sup>2</sup> C debug<br>mode                                         |  |  |  |  |

## 3 Reference Design

## **4** Configuration Options

## 4.1 Activation Threshold

The threshold adjustment is offered through two configuration pins.

THR0 is a first level of threshold adjustment. THR1 is a second level for refining the threshold. See Table 4.1 for details on choosing the threshold

## Table 4.1 Threshold adjustment guide

|                                                                   | L = LOGIC LOW, H = LOGIC HIGH, F = FLOAT |           |           |            |            |            |            |                  |  |

|-------------------------------------------------------------------|------------------------------------------|-----------|-----------|------------|------------|------------|------------|------------------|--|

| THR0 (pin 8)                                                      |                                          |           |           |            |            |            |            |                  |  |

| L                                                                 | L                                        | L         | F         | F          | F          | Н          | Н          | Н                |  |

| THR1 (pin 6)                                                      |                                          |           |           |            |            |            |            |                  |  |

| L                                                                 | F                                        | Н         | L         | F          | Н          | L          | F          | Н                |  |

| Corresponding Threshold Level                                     |                                          |           |           |            |            |            |            |                  |  |

| 0                                                                 | 1                                        | 2         | 3         | 4          | 5          | 6          | 7          | 8                |  |

|                                                                   |                                          | Ent       | ry Th     | resh       | old R      | atio       |            |                  |  |

| 1/<br>512                                                         | 2/<br>512                                | 4/<br>512 | 6/<br>512 | 10/<br>512 | 14/<br>512 | 18/<br>512 | 24/<br>512 | 32/<br>512       |  |

| Со                                                                | rresp                                    | ondi      | ng Ei     | ntry 1     | Thres      | hold       | Cour       | nts <sup>i</sup> |  |

| 3"                                                                | 4                                        | 9         | 14        | 23         | 32         | 42         | 56         | 74               |  |

| Corresponding Release Threshold<br>Counts (counts from reference) |                                          |           |           |            |            |            |            |                  |  |

| 3                                                                 | 3                                        | 7         | 11        | 18         | 24         | 32         | 42         | 56               |  |

|                                                                   | lore s                                   | sensit    | ive       |            | Le         | ess se     | ensitiv    | /e►              |  |

It is important to note that most sensitive settings are heavily dependent on design factors influencing SNR. These may be in order where fail-safe activations are required, but is not recommended for activation critical applications.

## 4.2 Timer Settings

Large environmental shifts (capacitance increases or decreases) are regarded as activations. Such conditions are intelligently cleared via the movement filter and timer. The timer would reset with each detected movement. If no movement is detected for the duration of the timer, the activation will be cleared. A few options exist for the duration of this timer.

Timer options are a summarized in the table below:

| TIMER (pin 1) | Time-out |

|---------------|----------|

| Low           | 60sec    |

| Float         | 3min     |

| High          | 10min    |

For custom timers the IQS229 makes it possible to distinguish between a threshold release and a no-movement release. The master device may then override the IQS229 output until the custom master timer has expired.

Figure 4.1 Normal release with threshold crossing (top), time-out release after nomovement condition (bottom)

<sup>&</sup>lt;sup>i</sup> Assuming a target of 1200 counts, threshold may be more for a larger amount, and less for a smaller amount (usually by only 1 count)

<sup>&</sup>lt;sup>ii</sup> Threshold calculations limit any threshold value to always be larger than 2 counts

## 4.4 Human movement filter threshold

The MOV\_THR pin offers adjustment of the threshold used to determine if a movement event should be triggered. From a default setting (pin FLOATING), the threshold can be increased or decreased by a percentage of the capacitive sensor operating point (long-term average).

| MOV_THR (pin 7) | Movement<br>Threshold |

|-----------------|-----------------------|

| Low             | More sensitive        |

| Float           | Default               |

| High            | Less sensitive        |

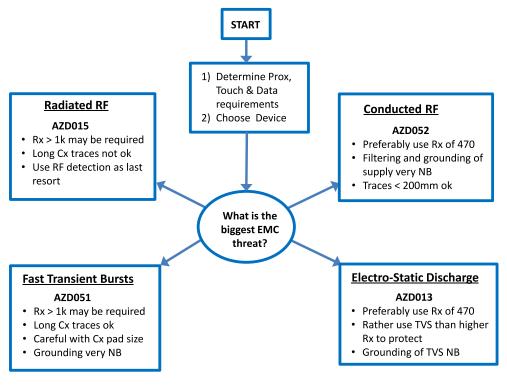

## **5** Design Considerations

## 5.1 Power Supply and PCB Layout

Azoteg IC's provide a high level of on-chip hardware and software noise filtering and ESD protection (refer to application note "AZD013 - ESD Overview"). Designing PCB's with better noise immunity against EMI, FTB and ESD in mind, it is always advisable to keep the critical noise suppression components like the de-coupling capacitors and series resistors in Figure 3.1. as close as possible to the IC. Always maintain a good ground connection and ground pour underneath the IC. For more guidelines please refer to the relevant application notes as mentioned in the next section.

## 5.2 Design Rules for Harsh EMC Environments

## 5.3 High Sensitivity

Through patented design and advanced signal processing, the device is able to provide extremely high sensitivity to detect proximity. This enables designs to detect proximity at distances that cannot be equaled by most other products. When the device is used in environments where high levels of noise or floating metal objects exist, a reduced proximity threshold is proposed to ensure reliable functioning of the sensor. The high sensitivity also allows the device to sense through overlay materials with low dielectric constants, such as wood or porous plastics.

For more guidelines on the layout of capacitive sense electrodes, please refer to application note "<u>AZD008 - Design</u> <u>Guidelines for Touch Pads</u>", available on the Azoteq web page: <u>www.azoteq.com</u>.

Applicable application notes: AZD013, AZD015, AZD051, and AZD052.

## 6 1-Wire data streaming mode

The IQS229 has the capability to stream data over the OUT pin to a master controller or debugging device. This provides the designer with the capability to obtain the parameters within the device in order to aid design into applications. Data streaming is performed as a 1-wire data protocol on the OUT pin. The function of this pin is therefore lost when the device is placed in streaming mode. The function of the MOV\_OUT pin remains. The MOV\_OUT pin may now be used to only read streaming data when movements occur. This enables 1-wire data processing only on the occurrence of movement events.

Data streaming can be enabled as shown in Figure 3.1 by simply placing a strong pull-up resistor on the OUT pin  $(4.7k\Omega)$  is recommended). Debugging and qualification during production may be done by simply probing the output pin with a strong pull-up while the weaker pull-down  $(1M\Omega)$  is placed on

the PCB. This will put the standalone module in 1-wire streaming mode.

Data streaming is initiated by the IQS229. When data streaming is enabled data is sent following each charge cycle.

Figure 6.1 Illustrates the communication protocol for initialising and sending data with the 1 wire communication protocol.

- Communication is initiated by a START bit. Bit defined as a low condition for t<sub>START</sub>.

- 2. Following the START bit, is a synchronisation byte ( $T_{INIT} = 0xAA$ ). This byte is used by the MCU for clock synchronisation.

- 3. Following T<sub>INIT</sub> the data bytes will be sent. 20 bytes will be sent after each charge cycle.

- 4. Each byte sent will be preceded by a START bit and a STOP bit will follow every byte.

- 5. STOP bit indicated by taking pin 1 high. The STOP bit does not have a defined period.

Figure 6.1 1-wire data streaming mode

The following table defines the data streamed Azoteq provides a graphic user interface to from the IQS229 device during streaming evaluate the user interface and debug current mode.

#### Table 6.1 Byte definitions for 1-wire streaming mode

| Byte | Bit     | Value                                                    |

|------|---------|----------------------------------------------------------|

| 0    | 7:0     | System Flags                                             |

|      | 7       | Activation                                               |

|      | 6       | Movement                                                 |

|      | 5       | Timer Active                                             |

|      | 4       | Filter Halt                                              |

|      | 3       | ls channel 0                                             |

|      | 2       | ATI tuning busy                                          |

|      | 1       | Noise detected                                           |

|      | 0       | Zoom                                                     |

| 1    | 15:8    | CH0 CS High byte                                         |

| 2    | 23:16   | CH0 CS Low byte                                          |

| 3    | 31:24   | CH0 LTA High byte                                        |

| 4    | 39:32   | CH0 LTA Low byte                                         |

| 5    | 47:40   | CH1 CS High byte                                         |

| 6    | 55:48   | CH1 CS Low byte                                          |

| 7    | 63:56   | CH1 LTA High byte                                        |

| 8    | 71:64   | CH1 LTA Low byte                                         |

| 9    | 79:72   | Movement Filter                                          |

| 10   | 87:80   | Movement Filter                                          |

| 11   | 95:88   | Entry threshold high byte                                |

| 12   | 103:96  | Entry threshold low byte                                 |

| 13   | 111:104 | Exit threshold high byte                                 |

| 14   | 119:112 | Exit threshold low byte                                  |

| 15   | 127:120 | Strap configuration                                      |

|      | 127:124 | Activation threshold                                     |

|      | 123:122 | Timer setting                                            |

|      | 121:220 | Movement threshold                                       |

| 16   | 135:128 | Multiplier channel 0                                     |

| 17   | 143:136 | Multiplier channel 1                                     |

| 18   | 151:144 | Parasitic capacitance<br>compensation (PCC)              |

| 10   | 450.450 | channel 0                                                |

| 19   | 159:152 | Parasitic capacitance<br>compensation (PCC)<br>channel 1 |

designs.

Sample code available: "AZD017 - IQS127 1-Wire Protocol SAMPLE CODE" This code represents the same protocol and only needs to be adapted for the longer data stream.

## 7 Typical Application

## 7.1 Minimizing Resistor straps

Component count is an important factor for applications with limited space and cost constraints. This section addresses this with a slightly more complex configuration than the standard reference design. This configuration should lead the designer to a safe minimal component design.

Figure 7.1 IQS229 configuration pin options

## Table 7.1 Table of constraints for resistor strap optimization

| Resistor<br>strap<br>state | Applicable<br>pins | Output state<br>after start-up      | Resistor value | Current consumption | Combination<br>strap                  |

|----------------------------|--------------------|-------------------------------------|----------------|---------------------|---------------------------------------|

| Pull down                  | All input pins     | Written low<br>when pulled<br>low   | 1kΩ ≤ R ≤ 2MΩ  | Only at<br>power-on | Yes, all pins                         |

| Pull up                    | THR0 and<br>TIMER  | Written low<br>when pulled<br>high  | 1MΩ ≤ R ≤ 2MΩ  | Continuous          | Applicable<br>pins may be<br>combined |

| Pull up                    | THR1 and MOV_THR   | Written high<br>when pulled<br>high | 1kΩ ≤ R ≤ 2MΩ  | Only at power-on    | Applicable<br>pins may be<br>combined |

Figure 7.2 shows the reference design for a minimal resistor layout. With a fixed design, a minimum of 0 strap resistors and maximum of 3 strap resistors are expected.

## Figure 7.2 Minimal resistor strap configuration

## 8 Specifications

## 8.1 Absolute maximum ratings

The following absolute maximum parameters are specified for the device:

Exceeding these maximum specifications may cause damage to the device.

| Operating temperature                                              | -40°C to 85°C                              |

|--------------------------------------------------------------------|--------------------------------------------|

| <ul> <li>Supply Voltage (VDDHI – VSS)</li> </ul>                   | 3.6V                                       |

| Maximum pin voltage                                                | VDDHI + 0.5V (may not<br>exceed VDDHI max) |

| <ul> <li>Maximum continuous current (for specific Pins)</li> </ul> | 10mA                                       |

| Minimum pin voltage                                                | VSS - 0.5V                                 |

| Minimum power-on slope                                             | 100V/s                                     |

| ESD protection                                                     | ±8kV (Human body model)                    |

| Package Moisture Sensitivity Level (MSL)                           | 1                                          |

#### Table 8.1 IQS229 General Operating Conditions<sup>1</sup>

| DESCRIPTION               | Conditions                 | PARAMETER                | MIN         | TYP          | MAX          | UNIT |

|---------------------------|----------------------------|--------------------------|-------------|--------------|--------------|------|

| Supply voltage            |                            | V <sub>DDHI</sub>        | 1.8         | 3.3V         | 3.6          | V    |

| Internal regulator output | $1.8 \le V_{DDHI} \le 3.6$ | V <sub>REG</sub>         | 1.62        | 1.7          | 1.79         | V    |

| Default Operating Current | 3.3V                       | I <sub>IQS229NP</sub>    | -           | 100          |              | μA   |

| Low Power Setting 1*      | 3.3V, LP=32                | I <sub>IQS229LP32</sub>  | -           | <40          |              | μA   |

| Low Power Setting 2*      | 3.3V, LP=64                | I <sub>IQS229LP64</sub>  | -           | <20          |              | μA   |

| Low Power Setting 3*      | 3.3V, LP=256               | I <sub>IQS229LP256</sub> | 7<br>(1.8V) | 10<br>(3.3V) | 12<br>(3.6V) | μA   |

\*LP interval period = Low power value (LP) x 1ms

## Table 8.2 Start-up and shut-down slope Characteristics

| DESCRIPTION      | Conditions                                | PARAMETER | MIN  | MAX | UNIT |

|------------------|-------------------------------------------|-----------|------|-----|------|

| Power On Reset   | V <sub>DDHI</sub> Slope ≥ 100V/s<br>@25°C | POR       |      | 1.6 | V    |

| Brown Out Detect | V <sub>DDHI</sub> Slope ≥ 100V/s<br>@25°C | BOD       | 1.05 |     | V    |

$<sup>^{1}</sup>$  Operating current shown in this datasheet does include power dissipation through the recommended 1M $\Omega$  strapping resistor on the OUT pin for failsafe modes.

## Table 8.3 Digital input trigger levels

| DESCRIPTION                                      | Conditions | PARAMETER                  | MIN  | TYPICAL | MAX  | UNIT |

|--------------------------------------------------|------------|----------------------------|------|---------|------|------|

| MOV_OUTpin<br>OUT pin                            | VDD = 3.3V | Input low level voltage    | 1.19 | 1.3     | 1.3  | V    |

| THR0 pin<br>THR1 pin<br>MOV_THR pin<br>TIMER pin | VDD = 3.3V | Input low level<br>voltage | 0.73 | 0.9     | 1.55 | V    |

| All digital inputs                               | VDD = 1.8V | Input low level voltage    | 0.54 | 0.6     | 0.76 | V    |

| All digital inputs                               | VDD = 1.8V | Input high level voltage   | 0.9  | 1.0     | 1.2  | V    |

| All digital inputs                               | VDD = 3.3V | Input high level voltage   | 1.90 | 2.1     | 2.20 | V    |

#### Table 8.4 Digital output levels

| DESCRIPTION         | Conditions   | PARAMETER       | @1mA         | @10mA       | UNIT |

|---------------------|--------------|-----------------|--------------|-------------|------|

| Output voltage low  | VDDHI = 3.3V | V <sub>OL</sub> | 0.01         | 0.1         | V    |

| Output voltage high | VDDHI = 3.3V | V <sub>OH</sub> | VDDHI – 0.02 | VDDHI – 0.2 | V    |

## Table 8.5 MOV\_OUT pin input signal characteristic

| DESCRIPTION                            | Conditions      | PARAMETER           | MIN | MAX | UNIT |

|----------------------------------------|-----------------|---------------------|-----|-----|------|

| Input signal for<br>reseed instruction | MOV_OUT pin low | t <sub>reseed</sub> | 20  | 40  | ms   |

| Input signal for sleep instruction     | MOV_OUT pin low | t <sub>sleep</sub>  | 80  | -   | ms   |

## 9 Package information

| Dimension | [mm]   |

|-----------|--------|

| А         | 3 ±0.1 |

| В         | 0.5    |

| С         | 0.25   |

| D         | n/a    |

| F         | 3 ±0.1 |

| L         | 0.4    |

| Р         | 2.4    |

| Q         | 1.65   |

#### Table 9.1 DFN-10 Package dimensions (bottom)

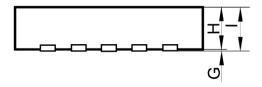

#### Table 9.2 DFN-10 Package dimensions (side)

| Dimension | [mm]    |

|-----------|---------|

| G         | 0.05    |

| Н         | 0.65    |

| I         | 0.7-0.8 |

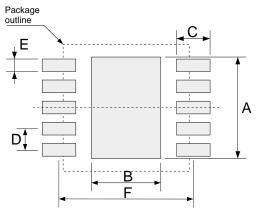

#### Table 9.3 DFN-10 Landing dimensions

| Dimension | [mm] |

|-----------|------|

| А         | 2.4  |

| В         | 1.65 |

| С         | 0.8  |

| D         | 0.5  |

| E         | 0.3  |

| F         | 3.2  |

Figure 9.1 DFN-10 Package dimensions (bottom view)

Figure 9.3 DFN-10 Landing dimensions

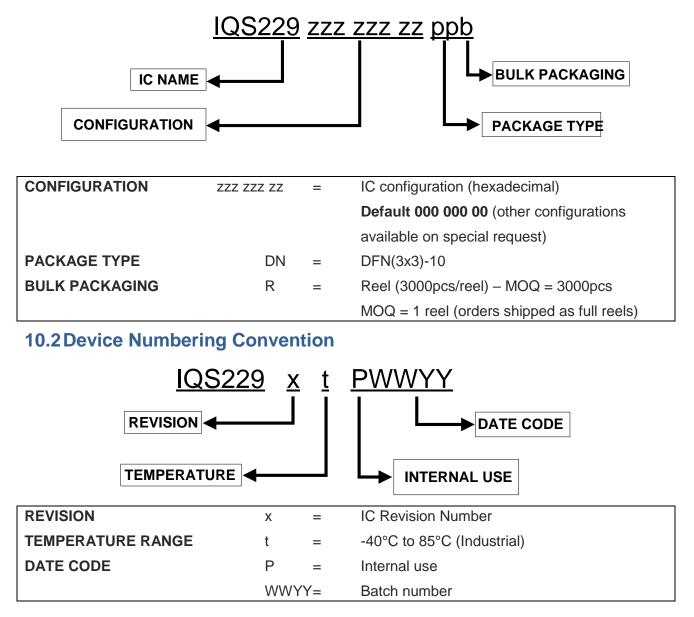

## **10 Ordering and Part-number Information**

## **10.1 Ordering Information**

Please check stock availability with your local distributor.

## **Revision History**

| Revision Number | Description                                                                                     | Date of issue    |

|-----------------|-------------------------------------------------------------------------------------------------|------------------|

| V0.9            | Draft revision                                                                                  | 22 August 2013   |

| V0.9.1          | Pre-Release                                                                                     | 1 October 2013   |

| V1.0            | Release                                                                                         | 7 October 2013   |

| V1.1            | Update: Known issue and workaround added to section 1.2.2. Current consumption figures updated. | 21 November 2013 |

| V1.2            | Digital input trigger level data added                                                          | 3 February 2014  |

| V1.3            | Figure 9.1 corrected – top view changed to bottom view                                          | 22 May 2014      |

|                 | Movement figures Figure 1.2 and Figure 1.3 updated to show the practical case                   |                  |

| V1.4            | Package MSL rating updated                                                                      | 30 May 2014      |

|                 | Section on minimizing resistor straps added.                                                    |                  |

|                 | Figure 1.2 and Figure 1.3 updated to be more intuitive                                          |                  |

| V1.5            | Table 4.1 updated to show related counts for activation and release.                            | 14 Jul 2014      |

|                 | Figure 9.3 updated to show correct relation to package outline                                  |                  |

| V1.6            | Document contact information updated                                                            | 4 Aug 2014       |

|                 | Extended datasheet created from v1.6 of standard datasheet                                      |                  |

|                 | Section 2 updated to show pin-out information for $I^2C$ debug mode and programming             |                  |

| V1.7            | Last page contact & patent information updated                                                  | 10 Apr 2015      |

|                 | Reseed/Sleep instruction timing specified                                                       |                  |

| V1.8            | Updated Electrical Specifications                                                               | 15 October 2015  |

| V1.9            | Digital output voltage levels added                                                             | 8 March 2016     |

## Appendix A OTP Options

The IQS229 offers various user selectable options. Most common user options have been directed as external configuration pins.

Configuration of the OTP settings can be done on packaged devices or in-circuit. In-circuit configuration may be limited by values of external components chosen.

Azoteq offers a Configuration Tool (CT210 or later) and associated software that can be used to program the OTP user options for prototyping purposes. For further information regarding this subject, please contact your local distributor or submit enquiries to Azoteq at: <u>ProxSenseSupport@azoteq.com</u>

## A.1 User Selectable OTP options

| bit7                             | Bank 0           |                                 |                                  |           |           | bit0            |                 |

|----------------------------------|------------------|---------------------------------|----------------------------------|-----------|-----------|-----------------|-----------------|

| Activation<br>Output<br>Polarity | Target<br>Counts | Charge<br>Transfer<br>Frequency | Activation<br>Threshold<br>Range | Debounce1 | Debounce0 | Filter<br>Halt1 | Filter<br>Halt0 |

| Bank0: bit 7   | Activation Output Polarity                                                      |

|----------------|---------------------------------------------------------------------------------|

|                | 0 = Active Low (SAR Failsafe)                                                   |

|                | 1 = Active High                                                                 |

| Bank0: bit 6   | Target Counts (Number of samples per measurement cycle)                         |

|                | 0 = 1200                                                                        |

|                | 1 = 768                                                                         |

| Bank0: bit 5   | Charge Transfer Frequency                                                       |

|                | 0 = 512 kHz                                                                     |

|                | 1 = 250 kHz                                                                     |

| Bank0: bit 4   | Activation Threshold Range (range for external strap options)                   |

|                | 0 = Sensitive                                                                   |

|                | (externally selectable: 1/512, 2, 4, 6, 10, 14, 18, 24, 32/512)                 |

|                | 1 = Less sensitive                                                              |

|                | (externally selectable: 24/512, 32, 40 48, 56, 64, 80, 96, 128/512)             |

| Bank0: bit 3:2 | Activation Debounce                                                             |

|                | 00 = 2                                                                          |

|                | 01 = 0                                                                          |

|                | 10 = 4                                                                          |

|                | 11 = 8                                                                          |

| Bank0: bit 1:0 | Filter Halt Threshold                                                           |

|                | 00 = 2                                                                          |

|                | 01 = 4                                                                          |

|                | 10 = 6                                                                          |

|                | 11 = 10                                                                         |

|                | *Prevent the filter from following a slow activation by selecting a small value |

| bit7                  | Bank 1                |                         |                              |                               |                                           | bit0           |                |

|-----------------------|-----------------------|-------------------------|------------------------------|-------------------------------|-------------------------------------------|----------------|----------------|

| Low<br>power<br>mode1 | Low<br>power<br>mode0 | Re-ATI out<br>of bounds | Short<br>Timer<br>Definition | Movement<br>Reaction<br>Speed | Streaming<br>1-wire /<br>I <sup>2</sup> C | Base<br>Value1 | Base<br>Value0 |

| Bank1: bit 7:6 | Low-Power Sleep mode                                                                                                                                                                                                                                                                                                                |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                | 00 = 32ms (30uA mode)                                                                                                                                                                                                                                                                                                               |

|                | 01 = Normal Power (100uA mode)                                                                                                                                                                                                                                                                                                      |

|                | 10 = 64ms (18uA mode)                                                                                                                                                                                                                                                                                                               |

|                | 11 = 256ms (6uA mode)                                                                                                                                                                                                                                                                                                               |

|                | *Low power sleep mode of the IQS229 was designed to give constant power consumption regardless of being in or out of activation. Therefore sleep periods remain constant between capacitive sensing conversions.                                                                                                                    |

| Bank1: bit 5   | Re-ATI when activated out of bounds                                                                                                                                                                                                                                                                                                 |

|                | 0 = No                                                                                                                                                                                                                                                                                                                              |

|                | 1 = Yes                                                                                                                                                                                                                                                                                                                             |

| Bank1: bit 4   | Short timer definition                                                                                                                                                                                                                                                                                                              |

|                | 0 = 0.5s release delay (only when short timer is 0s)                                                                                                                                                                                                                                                                                |

|                | 1 = 0s release delay (overrides all short timers of Bank2Bits3:2)                                                                                                                                                                                                                                                                   |

| Bank1: bit 3   | Movement Reaction Speed                                                                                                                                                                                                                                                                                                             |

|                | 0 = Fast (B=16)                                                                                                                                                                                                                                                                                                                     |

|                | 1 = Slow (B=64)                                                                                                                                                                                                                                                                                                                     |

| Bank1: bit 2   | Streaming (enabled with pull-up on OUT pin)                                                                                                                                                                                                                                                                                         |

|                | 0 = 1-wire                                                                                                                                                                                                                                                                                                                          |

|                | $1 = I^2 C$                                                                                                                                                                                                                                                                                                                         |

| Bank0: bit 1:0 | Base Value Range (from light capacitive loads to heavier loads)                                                                                                                                                                                                                                                                     |

|                | 00 = 225, 200, 175, 150                                                                                                                                                                                                                                                                                                             |

|                | 01 = 250, 225, 200, 175                                                                                                                                                                                                                                                                                                             |

|                | 10 = 300, 250, 200, 150                                                                                                                                                                                                                                                                                                             |

|                | 11 = 350, 325, 300, 275                                                                                                                                                                                                                                                                                                             |

|                | *Constant base values tend to give a reduced sensitivity with an increasing capacitive load. By varying the base value for the four main capacitive load regions (N=0,1,2,3) the sensor is designed with different adaptive base value sets in order to keep sensitivity high. Smaller base values lead to a more sensitive result. |

| bit7                                                                   |                                                             |                                                                                                                                                                                                                                                       | Ban                                                                                                                                                                                                                                                                | k 2                                                                                                                                                                                                                        |                                                                                                                                                                                    |                                                                                                                   | bit0                       |

|------------------------------------------------------------------------|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|----------------------------|

| Noise<br>Detection                                                     | CS<br>capacito                                              | Release Sensing No No Start-up Activation                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                            |                                                                                                                                                                                    |                                                                                                                   | Movement<br>Threshold      |

| Bank2: bit 7 Noise detection                                           |                                                             |                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                            |                                                                                                                                                                                    |                                                                                                                   |                            |

| 0 = Disable<br>1 = Enable (RF noise detection on Pin 8: THR0 – )       |                                                             |                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                            |                                                                                                                                                                                    |                                                                                                                   |                            |

| Bank2: bit 6                                                           | ;                                                           | Internal Base (                                                                                                                                                                                                                                       | Capacitor (CS)                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                            |                                                                                                                                                                                    |                                                                                                                   |                            |

|                                                                        |                                                             | 0 = Large<br>1 = Small                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                            |                                                                                                                                                                                    |                                                                                                                   |                            |

| Bank2: bit 5                                                           | ;                                                           | System Use                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                            |                                                                                                                                                                                    |                                                                                                                   |                            |

| Bank2: bit 4                                                           | 1                                                           | Sensing Techr                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                            |                                                                                                                                                                                    |                                                                                                                   |                            |

|                                                                        | ,<br>                                                       | -                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                            |                                                                                                                                                                                    |                                                                                                                   |                            |

|                                                                        |                                                             | 0 = Self Capacitance<br>1 = Projected Capacitance (Pin 7: MOV_THR becomes TX, no movement<br>threshold options – movement threshold remains default depending on<br>Bank2: bit 0)                                                                     |                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                            |                                                                                                                                                                                    |                                                                                                                   | nt                         |

| Bank2: bit 3                                                           | Bank2: bit 3:2 No-movement timer (external strap selection) |                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                            |                                                                                                                                                                                    |                                                                                                                   |                            |

| 00 = SAR specific: <b>60sec, 3min, 10min</b> (short: 0sec, 0sec, 0sec) |                                                             |                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                    | -                                                                                                                                                                                                                          |                                                                                                                                                                                    |                                                                                                                   |                            |

|                                                                        |                                                             | 00 = SAR speci                                                                                                                                                                                                                                        | fic: <b>60sec, 3mi</b>                                                                                                                                                                                                                                             | <b>n, 10min</b> (sho                                                                                                                                                                                                       | ort: 0sec, 0sec                                                                                                                                                                    | , Osec)                                                                                                           |                            |

|                                                                        |                                                             | 00 = SAR speci<br>01 = SAR speci                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                            |                                                                                                                                                                                    |                                                                                                                   | sec)                       |

|                                                                        |                                                             | -                                                                                                                                                                                                                                                     | ific (extra): 60s                                                                                                                                                                                                                                                  | ec, 3min, 10m                                                                                                                                                                                                              | in (short: 10s                                                                                                                                                                     | ec, 10sec, 10s                                                                                                    | ,                          |

|                                                                        |                                                             | 01 = SAR speci                                                                                                                                                                                                                                        | ific (extra): 60se<br>e: 2min, 5min,                                                                                                                                                                                                                               | ec, 3min, 10m<br>never timeou                                                                                                                                                                                              | iin (short: 10s<br>it (short: 30se                                                                                                                                                 | ec, 10sec, 10s<br>c, 30sec, 60se                                                                                  | ,                          |

|                                                                        |                                                             | 01 = SAR speci<br>10 = Long rang                                                                                                                                                                                                                      | ific (extra): <b>60s</b><br>e: <b>2min, 5min,</b><br>le: <b>15sec, 15se</b><br>tart when a rele<br>s detected for th<br>y feature for sa                                                                                                                           | ec, 3min, 10m<br>never timeou<br>c, 30sec (sho<br>ase is made.<br>he period of the<br>fety critical ap                                                                                                                     | in (short: 10s<br>It (short: 30se<br>ort: 0sec, 3sec<br>The output rer<br>e short timer.<br>plications. Sho                                                                        | ec, 10sec, 10s<br>c, 30sec, 60se<br>c, 10sec)<br>nains active u<br>This is an<br>ort timers can                   | ec)<br>ntil<br>also        |

|                                                                        |                                                             | 01 = SAR speci<br>10 = Long rang<br>11 = Short rang<br>"short" timers si<br>no movement is<br>enhanced safet<br>be used for app                                                                                                                       | ific (extra): <b>60s</b><br>e: <b>2min, 5min,</b><br>e: <b>15sec, 15se</b><br>tart when a rele<br>s detected for th<br>y feature for sa<br>lications to kee<br>to disable the s                                                                                    | ec, 3min, 10m<br>never timeou<br>c, 30sec (sho<br>ase is made.<br>he period of the<br>fety critical ap<br>p the load act<br>short timer in t                                                                               | nin (short: 10s<br>nt (short: 30se<br>ort: 0sec, 3sec<br>The output rer<br>e short timer.<br>plications. Sho<br>ve for a few s                                                     | ec, 10sec, 10s<br>c, 30sec, 60se<br>c, 10sec)<br>nains active u<br>This is an<br>ort timers can<br>econds after c | ec)<br>ntil<br>also<br>de- |

| Bank2: bit 1                                                           |                                                             | 01 = SAR speci<br>10 = Long rang<br>11 = Short rang<br>"short" timers st<br>no movement is<br>enhanced safet<br>be used for app<br>activation.<br><b>NOTE:</b> Be sure                                                                                | ific (extra): <b>60s</b><br>e: <b>2min, 5min,</b><br>le: <b>15sec, 15se</b><br>tart when a rele<br>s detected for th<br>y feature for sa<br>lications to kee<br>to disable the s                                                                                   | ec, 3min, 10m<br>never timeou<br>c, 30sec (sho<br>ase is made.<br>ase period of the<br>fety critical ap<br>p the load act<br>short timer in B<br>selected.                                                                 | in (short: 10s<br>it (short: 30se<br>ort: 0sec, 3sec<br>The output rer<br>e short timer.<br>plications. Sho<br>ve for a few s<br>Bank1:bit4 for                                    | ec, 10sec, 10s<br>c, 30sec, 60se<br>c, 10sec)<br>nains active u<br>This is an<br>ort timers can<br>econds after c | ec)<br>ntil<br>also<br>de- |

| Bank2: bit 1                                                           |                                                             | 01 = SAR speci<br>10 = Long rang<br>11 = Short rang<br>"short" timers st<br>no movement is<br>enhanced safet<br>be used for app<br>activation.<br><b>NOTE:</b> Be sure<br>when non-defau                                                              | ific (extra): <b>60s</b><br>e: <b>2min, 5min,</b><br>le: <b>15sec, 15se</b><br>tart when a rele<br>s detected for th<br>y feature for sa<br>lications to kee<br>to disable the s                                                                                   | ec, 3min, 10m<br>never timeou<br>c, 30sec (sho<br>ase is made.<br>ase period of the<br>fety critical ap<br>p the load act<br>short timer in B<br>selected.                                                                 | in (short: 10s<br>it (short: 30se<br>ort: 0sec, 3sec<br>The output rer<br>e short timer.<br>plications. Sho<br>ve for a few s<br>Bank1:bit4 for                                    | ec, 10sec, 10s<br>c, 30sec, 60se<br>c, 10sec)<br>nains active u<br>This is an<br>ort timers can<br>econds after c | ec)<br>ntil<br>also<br>de- |

| Bank2: bit 1                                                           |                                                             | 01 = SAR speci<br>10 = Long rang<br>11 = Short rang<br>"short" timers st<br>no movement is<br>enhanced safet<br>be used for app<br>activation.<br><b>NOTE:</b> Be sure<br>when non-defat                                                              | ific (extra): <b>60s</b><br>e: <b>2min, 5min,</b><br>ge: <b>15sec, 15se</b><br>tart when a rele<br>s detected for th<br>y feature for sa<br>lications to kee<br>to disable the s<br>ult settings are s<br><b>ation (auto-act</b>                                   | ec, 3min, 10m<br>never timeou<br>c, 30sec (sho<br>ase is made.<br>ase period of the<br>fety critical ap<br>p the load action<br>short timer in B<br>selected.                                                              | in (short: 10s<br>it (short: 30se<br>ort: 0sec, 3sec<br>The output rer<br>e short timer.<br>plications. Sho<br>ve for a few s<br>Bank1:bit4 for<br>ver-on/reset)                   | ec, 10sec, 10s<br>c, 30sec, 60se<br>c, 10sec)<br>nains active u<br>This is an<br>ort timers can<br>econds after c | ec)<br>ntil<br>also<br>de- |

| Bank2: bit 1<br>Bank2: bit 0                                           |                                                             | 01 = SAR species<br>10 = Long rang<br>11 = Short rang<br>"short" timers sin<br>no movement is<br>enhanced safet<br>be used for app<br>activation.<br>NOTE: Be sure<br>when non-defaut<br>Start-up Activation<br>0 = Disabled                          | ific (extra): <b>60s</b><br>e: <b>2min, 5min,</b><br>e: <b>15sec, 15se</b><br>tart when a rele<br>s detected for th<br>y feature for sa<br>lications to kee<br>to disable the s<br>ult settings are s<br>ation (auto-act                                           | ec, 3min, 10m<br>never timeou<br>c, 30sec (sho<br>ase is made.<br>ase period of the<br>fety critical ap<br>p the load act<br>short timer in B<br>selected.<br>ivation at pov                                               | in (short: 10s<br>it (short: 30se<br>ort: 0sec, 3sec<br>The output rer<br>e short timer.<br>plications. Sho<br>ve for a few s<br>Bank1:bit4 for<br>ver-on/reset)                   | ec, 10sec, 10s<br>c, 30sec, 60se<br>c, 10sec)<br>nains active u<br>This is an<br>ort timers can<br>econds after c | ec)<br>ntil<br>also<br>de- |

|                                                                        |                                                             | 01 = SAR speci<br>10 = Long rang<br>11 = Short rang<br>"short" timers st<br>no movement is<br>enhanced safet<br>be used for app<br>activation.<br><b>NOTE:</b> Be sure<br>when non-defat<br><b>Start-up Activa</b><br>0 = Disabled<br>1 = Enabled (lo | ific (extra): 60so<br>e: 2min, 5min,<br>e: 15sec, 15se<br>tart when a rele<br>s detected for the<br>y feature for sa<br>lications to kee<br>to disable the s<br>ation (auto-act<br>ng timer – for s<br>eshold (% of L                                              | ec, 3min, 10m<br>never timeou<br>c, 30sec (sho<br>ase is made.<br>he period of the<br>fety critical ap<br>p the load act<br>short timer in B<br>selected.<br>ivation at pove<br>afety critical ap                          | ain (short: 10s<br>at (short: 30se<br>ort: 0sec, 3sec<br>The output rere<br>e short timer.<br>plications. Sho<br>ive for a few s<br>Bank1:bit4 for<br>ver-on/reset)                | ec, 10sec, 10s<br>c, 30sec, 60se<br>c, 10sec)<br>nains active u<br>This is an<br>ort timers can<br>econds after c | ec)<br>ntil<br>also<br>de- |

|                                                                        |                                                             | 01 = SAR speci<br>10 = Long rang<br>11 = Short rang<br>"short" timers st<br>no movement is<br>enhanced safet<br>be used for app<br>activation.<br><b>NOTE:</b> Be sure<br>when non-defau<br><b>Start-up Activa</b><br>0 = Disabled<br>1 = Enabled (lo | ific (extra): 60so<br>e: 2min, 5min,<br>e: 15sec, 15se<br>tart when a rele<br>s detected for the<br>y feature for sa<br>lications to kee<br>to disable the so<br>ult settings are so<br>ation (auto-act<br>ng timer – for so<br>eshold (% of L<br>ap selection: 1/ | ec, 3min, 10m<br>never timeou<br>c, 30sec (sho<br>ase is made.<br>he period of the<br>fety critical ap<br>p the load act<br>short timer in B<br>selected.<br>ivation at pove<br>afety critical ap<br>TA)<br>256, 3/256, 5/ | ain (short: 10s<br>at (short: 30se<br>ort: 0sec, 3sec<br>The output rere<br>e short timer.<br>plications. Sho<br>ve for a few s<br>Bank1:bit4 for<br>ver-on/reset)<br>oplications) | ec, 10sec, 10s<br>c, 30sec, 60se<br>c, 10sec)<br>nains active u<br>This is an<br>ort timers can<br>econds after c | ec)<br>ntil<br>also<br>de- |