# Octal Three-Level/Quad Five-Level High-Voltage 2A Digital Pulsers with T/R Switch

### **General Description**

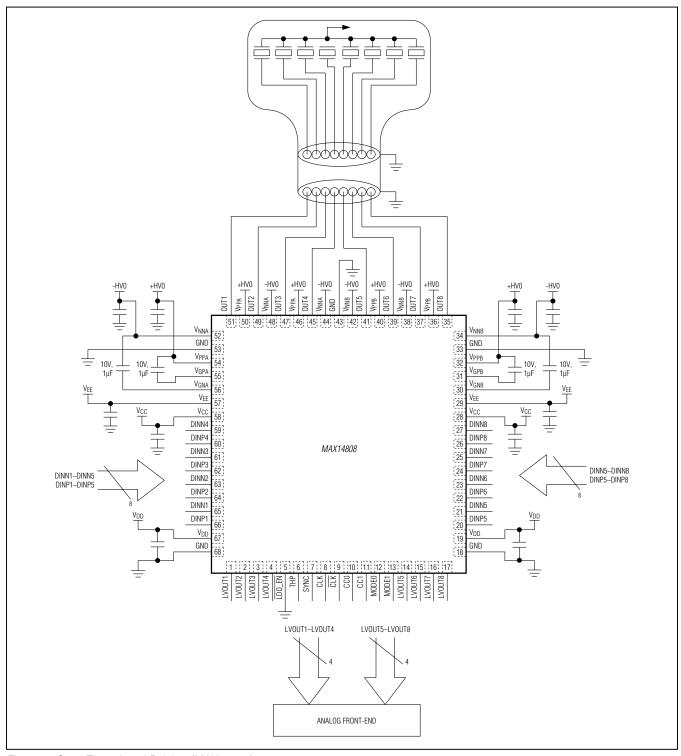

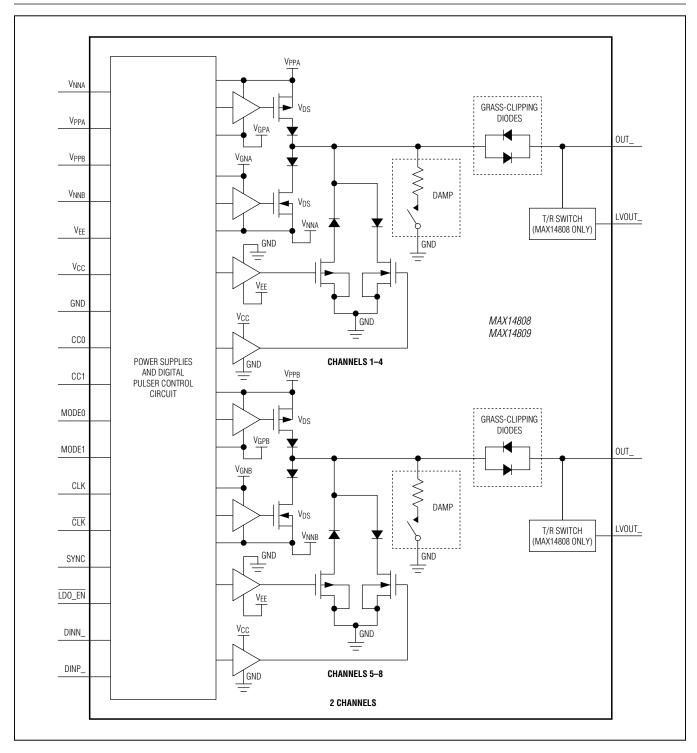

The MAX14808/MAX14809 octal three-level/quad five-level, high-voltage (HV) pulser devices generate high-frequency HV bipolar pulses (up to ±105V) from low-voltage control logic inputs for driving piezoelectric transducers in ultrasound systems. All eight channels have embedded overvoltage-protection diodes and an integrated active return-to-zero clamp. Both devices have embedded independent (floating) power supplies (FPS) and level shifters that allow signal transmission without the need for external HV capacitors. The MAX14808 also features eight integrated transmit/receive (T/R) switches. The MAX14809 does not have the T/R switch function.

The devices feature two modes of operation: an octal three-level pulser mode (with integrated active return-to-zero clamp) or a quad five-level pulser mode. In octal three-level pulser mode, each channel is controlled by two logic inputs (DINN\_/DINP\_) and the active return to zero features half the current driving of the pulser 1A (typ). In quad five-level pulser mode, each channel is controlled by three logic inputs and the active return to zero has the same current driving of the pulser 2A (typ).

The devices can operate both in clocked and transparent mode. In clocked mode, data inputs can be synchronized with a clean differential or single-ended clock to reduce phase noise associated with FPGA output signals that are detrimental for Doppler analysis. In transparent mode, the synchronization feature is disabled and output reflects the data input after a 18ns delay. Both devices feature adjustable maximum current (0.5A to 2A) to reduce power consumption when full current capability is not required.

The devices feature integrated grass-clipping diodes (with low parasitic capacitance) for receive (Rx) and transmit (Tx) isolations. Both devices feature a damping circuit that can be activated as soon as the transmit burst is over. The damping circuit has a typical on-resistance of  $500\Omega$ . It fully discharges the pulser's output internal node before the grass-clipping diodes.

The devices are available in a 68-pin (10mm x 10mm) TQFN package with an exposed pad and are specified over the -40°C to +85°C extended temperature range.

#### **Benefits and Features**

- ♦ Save Space (Optimized for High-Channel-Count Systems/Portable Systems)

- **♦ High Density**

- 8 Channels (Three-Level Operation)

- 4 Channels (Five-Level Operation) in One Package

- ♦ Integrated Low-Power T/R Switches (MAX14808)

- ♦ DirectDrive® Architecture Eliminates External High-Voltage Capacitor

- ♦ No External Floating Power Supply (FPS) Required

- High Performance (Designed to Enhance Image Quality)

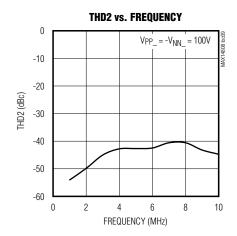

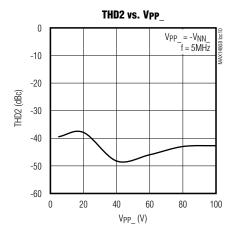

- ♦ Excellent -43dBc (typ) THD for Second Harmonic at 5MHz

- → Sync Function Eliminates Effects of FPGA Jitter and Improves Performance in Doppler Mode

- ♦ Low Propagation Delay 18ns (typ)

- **♦ Strong Active Return to Zero**

- **♦ Save Power**

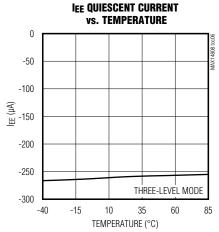

- Low Quiescent Power Dissipation (5.7mW/ Channel in Octal Mode)

- ♦ Programmable Current Capability

- ♦ Shutdown Mode and Disable Transmit Mode

### **Applications**

Ultrasound Medical Imaging Industrial Flaw Detection Piezoelectric Drivers Test Equipment

<u>Ordering Information</u> and <u>Functional Diagram</u> appear at end of data sheet.

DirectDrive is a registered trademark of Maxim Integrated Products, Inc.

For related parts and recommended products to use with this part, refer to <a href="https://www.maximintegrated.com/MAX14808.related">www.maximintegrated.com/MAX14808.related</a>.

# Octal Three-Level/Quad Five-Level High-Voltage 2A Digital Pulsers with T/R Switch

#### **ABSOLUTE MAXIMUM RATINGS**

| (All voltages referenced to GND.)  V <sub>DD</sub> Logic Supply Voltage Range0.3V to +5.6V  V <sub>CC</sub> Positive Driver Supply Voltage Range0.3V to +5.6V  V <sub>FF</sub> Negative Driver Supply Voltage Range5.6V to +0.3V | THP Logic Output Voltage Range0.3V to +5.6V V <sub>GPA</sub> , V <sub>GPB</sub> Output Voltage Rangemax[(V <sub>PP</sub> 5.6V), (V <sub>EE</sub> + 0.6V)] to (V <sub>PP</sub> _ + 0.3V) V <sub>GNA</sub> , V <sub>GNB</sub> Output Voltage |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>NNA</sub> , V <sub>NNB</sub> High Negative<br>Supply Voltage Range110V to +0.3V                                                                                                                                           | Range( $V_{NN}$ - 0.3V) to min[( $V_{CC}$ + 0.6V), ( $V_{NN}$ + 5.6V)]<br>Continuous Power Dissipation ( $T_A$ = +70°C)                                                                                                                    |

| V <sub>PPA</sub> , V <sub>PPB</sub> High Positive Supply Voltage Range0.3V to +110V OUT_ Output Voltage RangeV <sub>NN_</sub> to V <sub>PP_</sub> LVOUT_ Output Voltage Range (100mA Maximum Current)1.2V to +1.2V               | TQFN (derate 50mW/°C above +70°C)4000mW  Operating Temperature Range40°C to +85°C  Maximum Junction Temperature+150°C  Storage Temperature Range65°C to +150°C  Lead Temperature (soldering, 10s)+300°C                                    |

| DINN_, DINP_, CC_, SYNC, LDO_EN0.3V to +5.6V CLK, CLK, MODE_ Voltage Range0.3V to (V <sub>CC</sub> + 0.3V)                                                                                                                       | Soldering Temperature (reflow)+260°C                                                                                                                                                                                                       |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **PACKAGE THERMAL CHARACTERISTICS (Note 1)**

**TQFN**

Junction-to-Ambient Thermal Resistance (θ<sub>JC</sub>)............20°C/W Junction-to-Case Thermal Resistance (θ<sub>JC</sub>)..............0.5°C/W

**Note 1:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

#### DC ELECTRICAL CHARACTERISTICS

$(V_{DD} = +3V, V_{CC} = +5V, V_{EE} = -5V, V_{PPA} = +100V, V_{NNA} = -100V, V_{PPB} = +100V, V_{NNB} = -100V, 1\mu F$  bypass capacitor between  $V_{GNA}$  and  $V_{NNA}$ , 1 $\mu$ F bypass capacitor between  $V_{GPA}$  and  $V_{PPB}$ , 1 $\mu$ F bypass capacitor between  $V_{GPB}$  and  $V_{PPB}$ ,  $V_{LDO}$   $E_{R}$  = 0V, no load, unless otherwise noted. Typical values are at  $V_{R}$  = +25°C.) (Note 2)

| PARAMETER                                                     | SYMBOL                                              | CONDITIONS               | MIN                  | TYP | MAX                  | UNITS |

|---------------------------------------------------------------|-----------------------------------------------------|--------------------------|----------------------|-----|----------------------|-------|

| POWER SUPPLIES (VDD, VCC, V                                   | / <sub>EE</sub> , V <sub>PP</sub> _, V <sub>I</sub> | NN_)                     |                      |     |                      |       |

| Logic Supply Voltage                                          | V <sub>DD</sub>                                     |                          | +1.7                 | +3  | +5.25                | V     |

| Positive Drive Supply Voltage                                 | V <sub>CC</sub>                                     |                          | +4.9                 | +5  | +5.1                 | V     |

| Negative Drive Supply Voltage                                 | V <sub>EE</sub>                                     |                          | -5.1                 | -5  | -4.9                 | V     |

| High-Side Supply Voltage                                      | V <sub>PP</sub> _                                   |                          | 0                    |     | +105                 | V     |

| Low-Side Supply Voltage                                       | V <sub>NN</sub> _                                   |                          | -105                 |     | 0                    | V     |

| External Low-Side LDO Voltage                                 | V <sub>GN</sub><br>V <sub>NN</sub> _                | LDO_EN = high            | 5                    | 5.3 | 5.5                  | V     |

| External High-Side LDO Voltage                                | V <sub>PP_</sub> -<br>V <sub>GP_</sub>              | LDO_EN = high            | 5                    | 5.3 | 5.5                  | V     |

| External Floating Power-Supply Current from V <sub>GN</sub> _ | I <sub>VGN</sub> _                                  | LDO_EN = high (Note 3)   | 50                   |     |                      | mA    |

| External Floating Power-Supply Current from V <sub>GP</sub> _ | I <sub>VGP</sub> _                                  | LDO_EN = high (Note 3)   | 85                   |     |                      | mA    |

| LOGIC INPUTS/OUTPUTS (DINN                                    | _, DINP_, M                                         | ODE_, SYNC, CC_, LDO_EN) |                      |     |                      |       |

| Low-Level Input Threshold                                     | V <sub>IL</sub>                                     |                          |                      | 0   | .2 x V <sub>DD</sub> | V     |

| High-Level Input Threshold                                    | V <sub>IH</sub>                                     |                          | 0.8 x V <sub>D</sub> | )D  |                      | V     |

| Logic Input Capacitance                                       | C <sub>IN</sub>                                     |                          |                      | 4   |                      | рF    |

# Octal Three-Level/Quad Five-Level High-Voltage 2A Digital Pulsers with T/R Switch

### **DC ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = +3V, V_{CC} = +5V, V_{EE} = -5V, V_{PPA} = +100V, V_{NNA} = -100V, V_{PPB} = +100V, V_{NNB} = -100V, 1\mu F$  bypass capacitor between  $V_{GNA}$  and  $V_{NNA}$ , 1 $\mu$ F bypass capacitor between  $V_{GPA}$  and  $V_{PPA}$ , 1 $\mu$ F bypass capacitor between  $V_{GPB}$  and  $V_{PPB}$ ,  $V_{LDO} = 0V$ , no load, unless otherwise noted. Typical values are at  $V_{AB} = 0V$ , 1 $V_{AB} = 0V$ , no load, unless otherwise noted.

| PARAMETER                                         | SYMBOL                             | СО                                             | NDITIONS                                             | MIN                          | TYP | MAX                          | UNITS            |

|---------------------------------------------------|------------------------------------|------------------------------------------------|------------------------------------------------------|------------------------------|-----|------------------------------|------------------|

| Logic Input Leakage<br>(All Inputs Except LDO_EN) | I <sub>IN</sub>                    | $V_{IN} = 0V \text{ or } V_{DD}$               |                                                      | -1                           | 0   | +1                           | μA               |

| LDO_EN Pulldown Resistance                        | R <sub>LDO_EN</sub>                |                                                |                                                      | 7                            | 10  | 14                           | kΩ               |

| THP Low-Level Output Voltage                      | V <sub>OL</sub>                    | Pullup resistor to                             | $V_{DD} (R_{PULLUP} = 1k\Omega)$                     |                              | 0   | .1 x V <sub>DD</sub>         | V                |

| CLOCK INPUTS (CLK, $\overline{\text{CLK}}$ )—D    | IFFERENTIA                         | L MODE                                         |                                                      |                              |     |                              |                  |

| Differential Clock Input Voltage<br>Range         | V <sub>CLKD</sub>                  |                                                |                                                      | 0.2                          |     | 2                            | V <sub>P-P</sub> |

| Common-Mode Voltage                               | V <sub>CLKCM</sub>                 |                                                |                                                      |                              |     |                              | V                |

| Common-Mode Voltage Range                         | V <sub>CL</sub>                    |                                                |                                                      | V <sub>CC</sub> /2<br>- 0.45 |     | V <sub>CC</sub> /2<br>+ 0.45 | V                |

| D                                                 | R <sub>CLK</sub> ,                 | Differential                                   |                                                      |                              | 7   |                              | kΩ               |

| Input Resistance                                  | RCLK                               | Common mode                                    |                                                      |                              | 23  |                              | kΩ               |

| Input Capacitance                                 | C <sub>CLK</sub> ,<br>C <u>CLK</u> | Capacitance to G                               | ND (each input)                                      |                              | 4   |                              | pF               |

| CLOCK INPUTS (CLK, CLK)—S                         | INGLE-ENDE                         | D MODE (V <sub>CLK</sub> < 0                   | 0.1V)                                                |                              |     |                              |                  |

| Low-Level Input                                   | V <sub>IL</sub>                    | CLK                                            |                                                      |                              | 0   | .2 x V <sub>DD</sub>         | V                |

| High-Level Input                                  | VIH                                | CLK                                            |                                                      | 0.8 x V <sub>C</sub>         | )D  |                              | V                |

| Single-Ended Mode Selection<br>Threshold Low      | V <sub>IL</sub>                    | CLK                                            |                                                      |                              |     | 0.1                          | ٧                |

| Single-Ended Mode Selection<br>Threshold High     | V <sub>IH</sub>                    | CLK                                            |                                                      | 1                            |     |                              | V                |

| Input Capacitance (CLK)                           | C <sub>CLK</sub>                   |                                                |                                                      |                              | 4   |                              | рF               |

| Logic Input Leakage (CLK)                         | I <sub>CLK</sub>                   | V <sub>CLK</sub> = 0V or V <sub>DD</sub>       | )                                                    | -1                           | 0   | +1                           | μΑ               |

| Pullup Current (CLK)                              | ICLK                               | $V_{\overline{CLK}} = 0V$                      |                                                      |                              | 120 | 180                          | μΑ               |

| SUPPLY CURRENT—SHUTDOV                            | VN MODE (M                         | ODE0 = Low, MOD                                | E1 = Low)                                            |                              |     |                              | 1                |

| V <sub>DD</sub> Supply Current                    | I <sub>DD</sub>                    | All inputs connect                             | ted to GND or V <sub>DD</sub>                        |                              |     | 3                            | μΑ               |

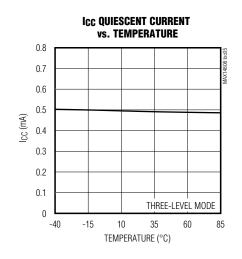

| V <sub>CC</sub> Supply Current                    | Icc                                | All inputs connect                             | ted to GND or V <sub>DD</sub>                        |                              |     | 22                           | μΑ               |

| V <sub>EE</sub> Supply Current                    | I <sub>EE</sub>                    | All inputs connect                             | ted to GND or V <sub>DD</sub>                        |                              |     | 13                           | μΑ               |

| V <sub>PP</sub> _ Supply Current                  | I <sub>PP</sub> _                  | All inputs connect                             | ted to GND or V <sub>DD</sub>                        |                              |     | 10                           | μΑ               |

| V <sub>NN</sub> _ Supply Current                  | I <sub>NN</sub> _                  | All inputs connected to GND or V <sub>DD</sub> |                                                      |                              |     | 10                           | μΑ               |

| SUPPLY CURRENT—DISABLE                            | MODE (MOD                          | E0 = High, MODE1                               | = High)                                              |                              |     |                              |                  |

|                                                   |                                    | All inputs connected to                        | Transparent or single-<br>ended clock mode           |                              | 1.7 | 3                            | μA               |

| V <sub>DD</sub> Supply Current                    | I <sub>DDQ</sub>                   | GND or V <sub>DD</sub>                         | Differential clock<br>mode, V <sub>CLKD</sub> = 0.2V |                              | 110 | 190                          | μΑ               |

# Octal Three-Level/Quad Five-Level High-Voltage 2A Digital Pulsers with T/R Switch

### **DC ELECTRICAL CHARACTERISTICS (continued)**

(( $V_{DD}$  = +3V,  $V_{CC}$  = +5V,  $V_{EE}$  = -5V,  $V_{PPA}$  = +100V,  $V_{NNA}$  = -100V,  $V_{PPB}$  = +100V,  $V_{NNB}$  = -100V, 1 $\mu$ F bypass capacitor between  $V_{GNA}$  and  $V_{NNA}$ , 1 $\mu$ F bypass capacitor between  $V_{GPA}$  and  $V_{PPA}$ , 1 $\mu$ F bypass capacitor between  $V_{GPB}$  and  $V_{PPB}$ ,  $V_{LDO}$  = 0V, no load, unless otherwise noted. Typical values are at  $T_A$  = +25°C.) (Note 2)

| PARAMETER                                                  | SYMBOL             | CONDI                         | TIONS                                                   | MIN    | TYP  | MAX  | UNITS |

|------------------------------------------------------------|--------------------|-------------------------------|---------------------------------------------------------|--------|------|------|-------|

|                                                            |                    | DINN_ = DINP_ = GN            | ID                                                      |        | 0.26 | 0.4  |       |

| V <sub>EE</sub> Supply Current                             | I <sub>EEQ</sub>   | DINN_ = DINP_ =               | MAX14808                                                |        | 9.4  | 13   | mA    |

|                                                            |                    | V <sub>DD</sub>               | MAX14809                                                |        | 1.37 | 2    |       |

|                                                            |                    | DINN_ = DINP_ = GN            | ID                                                      |        | 0.49 | 0.75 |       |

| V <sub>CC</sub> Supply Current                             | Iccq               | DINN_ = DINP_ =               | MAX14808                                                |        | 9.6  | 13.2 | mA    |

|                                                            |                    | $V_{DD}$                      | MAX14809                                                |        | 1.6  | 2.3  |       |

| V <sub>CC</sub> Supply Current Increase in Clocked Mode    | Δl <sub>CC</sub>   | Differential clock mod        | Differential clock mode                                 |        | 3.5  | 5    | mA    |

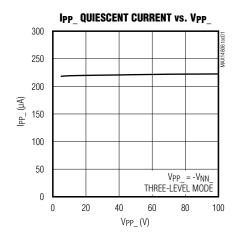

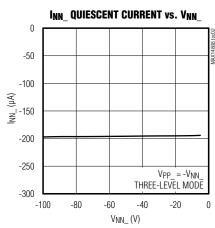

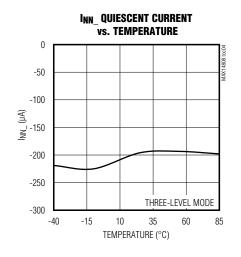

| V <sub>NN</sub> _Total Supply Current (Quiescent Mode)     | I <sub>NNQ</sub> _ | All inputs connected t        | to GND or V <sub>DD</sub>                               |        | 195  | 305  | μA    |

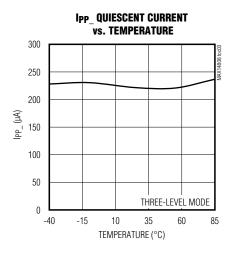

| V <sub>PP</sub> _Total Supply Current<br>(Quiescent Mode)  | I <sub>PPQ</sub> _ | All inputs connected t        | to GND or V <sub>DD</sub>                               |        | 220  | 340  | μA    |

| Total Power Dissipation per                                | P <sub>PDIS1</sub> | T/R switch off, damp of mode) | off (transparent                                        |        | 5.7  |      |       |

| Channel (Disable Mode)                                     | _                  | DINN_ = DINP_ =               | MAX14808                                                |        | 17   |      | mW    |

|                                                            | P <sub>PDIS2</sub> | V <sub>DD</sub>               | MAX14809                                                |        | 7    |      |       |

| SUPPLY CURRENT—OCTAL TH                                    | REE-LEVEL          | MODE, NO LOAD (MC             | DE0 = High, MODE1                                       | = Low) |      |      |       |

| V <sub>DD</sub> Supply Current (Quiescent                  | A                  | All inputs connected          | Transparent or single-ended clock mode                  |        | 1.7  | 3    |       |

| Mode)                                                      | I <sub>DD</sub>    | to GND or V <sub>DD</sub>     | Differential clock<br>mode, V <sub>CLKD</sub> =<br>0.2V |        | 110  | 190  | μΑ    |

|                                                            |                    | DINN_ = DINP_ = GN            | ID                                                      |        | 0.26 | 0.4  |       |

| V <sub>EE</sub> Supply Current (Quiescent Mode)            | I <sub>EEQ</sub>   | DINN_ = DINP_ =               | MAX14808                                                |        | 9.4  | 13   | mA    |

| Mode)                                                      |                    | V <sub>DD</sub>               | MAX14809                                                |        | 1.37 | 2    |       |

|                                                            |                    | DINN_ = DINP_ = GN            | ID                                                      |        | 0.49 | 0.75 |       |

| V <sub>CC</sub> Supply Current (Quiescent Mode)            | Iccq               | DINN_ = DINP_ =               | MAX14808                                                |        | 9.6  | 13.2 | mA    |

| inioue)                                                    |                    | $V_{DD}$                      | MAX14809                                                |        | 1.6  | 2.3  |       |

| V <sub>CC</sub> Supply Current Increase in Clocked Mode    | Δl <sub>CC</sub>   | Differential clock mod        | le                                                      |        | 3.5  | 5    | mA    |

| V <sub>NN</sub> _Total Supply Current<br>(Quiescent Mode)  | I <sub>NNQ</sub> _ | All inputs connected t        | to GND or V <sub>DD</sub>                               |        | 195  | 305  | μΑ    |

| V <sub>PP</sub> _ Total Supply Current<br>(Quiescent Mode) | I <sub>PPQ</sub> _ | All inputs connected t        | to GND or V <sub>DD</sub>                               |        | 220  | 340  | μА    |

# Octal Three-Level/Quad Five-Level High-Voltage 2A Digital Pulsers with T/R Switch

### **DC ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = +3V, V_{CC} = +5V, V_{EE} = -5V, V_{PPA} = +100V, V_{NNA} = -100V, V_{PPB} = +100V, V_{NNB} = -100V, 1\mu F$  bypass capacitor between  $V_{GNA}$  and  $V_{NNA}$ , 1 $\mu$ F bypass capacitor between  $V_{GPA}$  and  $V_{PPA}$ , 1 $\mu$ F bypass capacitor between  $V_{GPB}$  and  $V_{PPB}$ ,  $V_{LDO} = 0V$ , no load, unless otherwise noted. Typical values are at  $V_{AB} = 0V$ , 1 $V_{AB} = 0V$ ,

| PARAMETER                                               | SYMBOL                                                      | CONDITIONS                                                                     |                                                                                      | MIN | TYP | MAX  | UNITS |

|---------------------------------------------------------|-------------------------------------------------------------|--------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-----|-----|------|-------|

| T                                                       | P <sub>PDIS1</sub>                                          | T/R switch off, damp mode)                                                     | off (transparent                                                                     |     | 5.7 |      |       |

| Total Power Dissipation per Channel (Quiescent Mode)    |                                                             | DINN_ = DINP_ =                                                                | MAX14808                                                                             |     | 17  |      | mW    |

|                                                         | P <sub>PDIS2</sub>                                          | V <sub>DD</sub> (transparent mode)                                             | MAX14809                                                                             |     | 7   |      |       |

|                                                         | I <sub>DD1</sub>                                            | CW Doppler (Note 4) single-ended clock m                                       |                                                                                      |     | 2.2 | 3.2  | mA    |

| V <sub>DD</sub> Supply Current                          |                                                             |                                                                                | B mode (Note 5), transparent or<br>single-ended clock mode (Figure 1a)<br>(MAX14808) |     | 3.3 | 6    |       |

|                                                         | IDD2                                                        | B mode (Note 5), transparent or single-ended clock mode (Figure 1a) (MAX14809) |                                                                                      |     | 10  | 20   | - μΑ  |

| V <sub>EE</sub> Supply Current                          | I <sub>EE1</sub>                                            | 8 channels<br>switching, CW<br>Doppler (Note 4)                                | CC0 = high,<br>CC1 = high                                                            |     | 67  | 92   |       |

|                                                         |                                                             | switching, B mode                                                              | MAX14808                                                                             |     | 9.7 | 14.8 | mA    |

|                                                         | I <sub>EE2</sub> (Note 5) (Figure 1a), CC0 = low, CC1 = low | MAX14809                                                                       |                                                                                      | 2   | 3   |      |       |

|                                                         | I <sub>CC1</sub>                                            | 8 channels<br>switching, CW<br>Doppler (Note 4)                                | CC0 = high, CC1<br>= high                                                            |     | 45  | 60   |       |

| V <sub>CC</sub> Supply Current                          |                                                             | 8 channels<br>switching, B mode                                                | MAX14808                                                                             |     | 10  | 15   | mA    |

|                                                         | I <sub>CC2</sub>                                            | (Note 5) (Figure 1a),<br>CC0 = low,<br>CC1 = low                               | MAX14809                                                                             |     | 2.1 | 3.2  |       |

| V <sub>DD</sub> Supply Current Increase in Clocked Mode | Δl <sub>DD</sub>                                            | Differential clock mod                                                         | e                                                                                    |     | 1.8 |      | mA    |

| V <sub>CC</sub> Supply Current Increase in Clocked Mode | Δl <sub>CC</sub>                                            | Differential clock mod                                                         | e                                                                                    |     | 3.8 |      | mA    |

| V Supply Current                                        | I <sub>NN1</sub>                                            | 8 channels switching,<br>high, CC1 = high, R <sub>L</sub><br>(Note 4)          |                                                                                      |     | 157 | 200  | mΛ    |

| V <sub>NN</sub> _ Supply Current                        | I <sub>NN2</sub>                                            | 8 channels switching.<br>CC0 = low, CC1 = low<br>240pF (Note 5)                |                                                                                      |     | 2   | 2.8  | mA    |

# Octal Three-Level/Quad Five-Level High-Voltage 2A Digital Pulsers with T/R Switch

### **DC ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = +3V, V_{CC} = +5V, V_{EE} = -5V, V_{PPA} = +100V, V_{NNA} = -100V, V_{PPB} = +100V, V_{NNB} = -100V, 1\mu F$  bypass capacitor between  $V_{GNA}$  and  $V_{NNA}$ , 1 $\mu$ F bypass capacitor between  $V_{GPA}$  and  $V_{PPA}$ , 1 $\mu$ F bypass capacitor between  $V_{GPB}$  and  $V_{PPB}$ ,  $V_{LDO} = 0V$ , no load, unless otherwise noted. Typical values are at  $V_{AB} = 0V$ , 1 $V_{AB} = 0V$ ,

| PARAMETER                                                                        | SYMBOL                                                                                                                                                                                   | CONDITIONS                                                     |                                                                                                           | MIN       | TYP  | MAX  | UNITS |

|----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-----------|------|------|-------|

| V <sub>PP</sub> Supply Current                                                   | I <sub>PP1</sub>                                                                                                                                                                         | 8 channels switching high, CC1 = high, R <sub>L</sub> (Note 4) |                                                                                                           |           | 186  | 230  | - mA  |

| урр_ Зирріу Сипепі                                                               | I <sub>PP2</sub>                                                                                                                                                                         |                                                                | 8 channels switching, B mode (Figure 1a), CC0 = low, CC1 = low, $R_L = 1k\Omega$ , $C_L = 240pF$ (Note 5) |           | 3.1  | 4.5  | IIIA  |

|                                                                                  | PD <sub>CW</sub>                                                                                                                                                                         | 1 channel switching,                                           | CW Doppler (Note 4)                                                                                       |           | 286  |      |       |

| Power Dissipation per Channel (Octal Three-Level Mode)  SUPPLY CURRENT—QUAD FIVE | PDpu                                                                                                                                                                                     | 1 channel switching,<br>B mode (Note 5)<br>(Figure 1a), CC0 =  | MAX14808                                                                                                  |           | 73   |      | mW    |

|                                                                                  | Three-Level Mode) $\begin{array}{c c} & \text{PD}_{PW} & \text{low,} \\ & \text{CC1} = \text{low,} \\ & \text{R}_{L} = 1 \text{k} \Omega, \\ & \text{C}_{L} = 240 \text{pF} \end{array}$ | CC1 = low,<br>$R_L = 1k\Omega,$                                | MAX14809                                                                                                  |           | 69.5 |      |       |

| SUPPLY CURRENT—QUAD FIV                                                          | E-LEVEL DU                                                                                                                                                                               | AL MODE, NO LOAD                                               | (MODE0 = Low, MODE)                                                                                       | =1 = High | )    |      |       |

| V <sub>DD</sub> Supply Current (Quiescent<br>Mode)                               | escent I <sub>DDQ</sub> All inputs connect to GND or V <sub>DD</sub>                                                                                                                     | All inputs connected                                           | Transparent or single-ended clock mode                                                                    |           | 1.7  | 3    |       |

|                                                                                  |                                                                                                                                                                                          |                                                                | Differential clock<br>mode, V <sub>CLKD</sub> =<br>0.2V                                                   |           | 110  | 190  | μA    |

|                                                                                  |                                                                                                                                                                                          | DINN_ = DINP_ = GN                                             | ID                                                                                                        |           | 0.26 | 0.4  |       |

| V <sub>EE</sub> Supply Current (Quiescent                                        | I <sub>EEQ</sub>                                                                                                                                                                         | DINN_ = DINP_ =                                                | MAX14808                                                                                                  |           | 5.4  | 7.7  | mA    |

| Mode)                                                                            |                                                                                                                                                                                          | $V_{DD}$                                                       | MAX14809                                                                                                  |           | 1.35 | 2    |       |

|                                                                                  |                                                                                                                                                                                          | DINN_ = DINP_ = GN                                             | ID                                                                                                        |           | 0.49 | 0.75 |       |

| V <sub>CC</sub> Supply Current (Quiescent Mode)                                  | Iccq                                                                                                                                                                                     | DINN_ = DINP_ =                                                | MAX14808                                                                                                  |           | 5.6  | 7.8  | mA    |

| lviode)                                                                          |                                                                                                                                                                                          | $V_{DD}$                                                       | MAX14809                                                                                                  |           | 1.6  | 2.3  |       |

| V <sub>CC</sub> Supply Current Increase                                          | $\Delta$ l $_{CC}$                                                                                                                                                                       | Differential clock mod                                         | le                                                                                                        |           | 3.5  | 5    | mA    |

| V <sub>NN</sub> _Supply Current (Quiescent Mode)                                 | I <sub>NNQ</sub> _                                                                                                                                                                       | All inputs connected                                           | to GND or V <sub>DD</sub>                                                                                 |           | 195  | 305  | μА    |

| V <sub>PP</sub> _Supply Current (Quiescent Mode)                                 | I <sub>PPQ</sub> _                                                                                                                                                                       | All inputs connected                                           | to GND or V <sub>DD</sub>                                                                                 |           | 220  | 340  | μΑ    |

|                                                                                  | P <sub>PDIS1</sub>                                                                                                                                                                       | T/R switch off, DAMP mode)                                     | T/R switch off, DAMP off (transparent mode)                                                               |           | 11.3 |      |       |

| Power Dissipation per Channel (Quiescent Mode)                                   | Popies                                                                                                                                                                                   | DINN_ = DINP_ =                                                | MAX14808                                                                                                  |           | 24.1 |      | mW    |

|                                                                                  | P <sub>PDIS2</sub> V <sub>DD</sub> (transparer mode)                                                                                                                                     |                                                                | MAX14809                                                                                                  |           | 14.1 |      |       |

# Octal Three-Level/Quad Five-Level High-Voltage 2A Digital Pulsers with T/R Switch

### **DC ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = +3V, V_{CC} = +5V, V_{EE} = -5V, V_{PPA} = +100V, V_{NNA} = -100V, V_{PPB} = +100V, V_{NNB} = -100V, 1\mu F$  bypass capacitor between  $V_{GNA}$  and  $V_{NNA}$ , 1 $\mu$ F bypass capacitor between  $V_{GPA}$  and  $V_{PPA}$ , 1 $\mu$ F bypass capacitor between  $V_{GPB}$  and  $V_{PPB}$ ,  $V_{LDO} = 0V$ , no load, unless otherwise noted. Typical values are at  $V_{AB} = 0V$ , 1 $V_{AB} = 0V$ , no load, unless otherwise noted.

| PARAMETER                               | SYMBOL                   | CONDI                                            | TIONS                                                            | MIN | TYP | MAX | UNITS |

|-----------------------------------------|--------------------------|--------------------------------------------------|------------------------------------------------------------------|-----|-----|-----|-------|

| V. Cumply Correct                       | I <sub>DD1</sub>         | 4 channels switching, (Note 4)                   | CW Doppler                                                       |     | 1.4 |     | mA    |

| V <sub>DD</sub> Supply Current          | I <sub>DD2</sub>         | 4 channels switching, (Figure 1a)                | B mode (Note 5)                                                  |     | 4.3 |     | μΑ    |

|                                         | I <sub>EE1</sub>         | 4 channels<br>switching, CW<br>Doppler (Note 4)  | CC0 = high,<br>CC1 = high                                        |     | 33  |     |       |

| V <sub>EE</sub> Supply Current          |                          | 4 channels<br>switching, B mode                  | MAX14808                                                         |     | 5.9 |     | mA    |

|                                         | I <sub>EE2</sub>         | (Note 5) (Figure 1a),<br>CC0 = low,<br>CC1 = low | MAX14809                                                         |     | 1.9 |     |       |

|                                         | I <sub>CC1</sub>         | 4 channels<br>switching, CW<br>Doppler (Note 4)  | CC0 = high,<br>CC1 = high                                        |     | 22  |     |       |

| V <sub>CC</sub> Supply Current          |                          | I <sub>CC2</sub> (Note 5) (Figure 1a),           | MAX14808                                                         |     | 6   |     | mA    |

|                                         | ICC2                     |                                                  | MAX14809                                                         |     | 2   |     |       |

| V <sub>DD</sub> Supply Current Increase | Δl <sub>DD</sub>         | Differential clock mod                           | le                                                               |     | 1.8 |     | mA    |

| V <sub>CC</sub> Supply Current Increase | $\Delta$ I <sub>CC</sub> | Differential clock mod                           | le                                                               |     | 3.8 |     | mA    |

| V <sub>NN</sub> _ Supply Current        | I <sub>NN1</sub>         | 4 channels<br>switching, CW<br>Doppler (Note 4)  | CC0 = high,<br>CC1 = high,<br>$R_L = 1k\Omega,$<br>$C_L = 240pF$ |     | 90  |     | mA    |

|                                         | I <sub>NN2</sub>         | 4 channels switching,<br>(Figure 1a), CC0 = lo   |                                                                  |     | 1.3 |     |       |

| V <sub>PP</sub> _Supply Current         | I <sub>PP1</sub>         | 4 channels<br>switching, CW<br>Doppler (Note 4)  | CC0 = high,<br>CC1 = high,<br>$R_L = 1k\Omega,$<br>$C_L = 240pF$ |     | 103 |     | mA    |

|                                         | I <sub>PP2</sub>         | 4 channels switching,<br>(Figure 1a), CC0 = lo   |                                                                  |     | 2.2 |     |       |

# Octal Three-Level/Quad Five-Level High-Voltage 2A Digital Pulsers with T/R Switch

#### DC ELECTRICAL CHARACTERISTICS (continued)

$(V_{DD} = +3V, V_{CC} = +5V, V_{EE} = -5V, V_{PPA} = +100V, V_{NNA} = -100V, V_{PPB} = +100V, V_{NNB} = -100V, 1\mu F$  bypass capacitor between  $V_{GNA}$  and  $V_{NNA}$ , 1 $\mu$ F bypass capacitor between  $V_{GPA}$  and  $V_{PPA}$ , 1 $\mu$ F bypass capacitor between  $V_{GPB}$  and  $V_{PPB}$ ,  $V_{LDO} = 0V$ , no load, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 2)

| PARAMETER                                                                | SYMBOL             | CONDITIONS                                                            |                           | MIN    | TYP       | MAX                            | UNITS |

|--------------------------------------------------------------------------|--------------------|-----------------------------------------------------------------------|---------------------------|--------|-----------|--------------------------------|-------|

|                                                                          | PD <sub>CW</sub>   | 1 channel switching, 4), $R_L = 1k\Omega$ , $C_L = 24$                |                           |        | 311       |                                |       |

| Total Power Dissipation per<br>Channel (Quad Five-Level Dual<br>Mode)    | DD                 | 1 channel switching,<br>B mode (Note 5)<br>(Figure 1a), CC0 =<br>low, | MAX14808                  |        | 102       |                                | mW    |

| OUDDLY OUDDENIE - 0.5                                                    | PD <sub>PW</sub>   | $CC1 = low,$ $R_L = 1k\Omega,$ $C_L = 240pF$                          | MAX14809                  |        | 94.5      |                                |       |

| SUPPLY CURRENT—OCTAL TH<br>+5V, V <sub>GN</sub> - V <sub>NN</sub> = +5V) | REE-LEVEL          | , NO LOAD (MODE0 =                                                    | High, MODE1 = Low,        | LDO_EN | = High, \ | V <sub>PP</sub> V <sub>C</sub> | 3P_ = |

| V <sub>EE</sub> Supply Current<br>(Quiescent Mode)                       | I <sub>EEQ</sub> _ | All inputs connected                                                  | to GND                    |        | 25        | 46                             | μΑ    |

| V <sub>CC</sub> Supply Current<br>(Quiescent Mode)                       | I <sub>CCQ</sub> _ | All inputs connected                                                  | to GND                    |        | 280       | 420                            | μΑ    |

| V <sub>NN</sub> _Supply Current (Quiescent Mode)                         | I <sub>NNQ</sub> _ | All inputs connected                                                  |                           | 40     | 62        | μA                             |       |

| V <sub>PP</sub> _ Supply Current<br>(Quiescent Mode)                     | I <sub>PPQ</sub> _ | All inputs connected                                                  |                           | 40     | 62        | μA                             |       |

| OUTPUT STAGE                                                             |                    |                                                                       |                           |        | ,         |                                |       |

|                                                                          |                    |                                                                       | CC0 = low,<br>CC1 = low   |        | 8.5       |                                |       |

| V <sub>NNA</sub> , V <sub>NNB</sub> Connected Low-                       |                    | 504                                                                   | CC0 = high,<br>CC1 = low  |        | 10        |                                |       |

| Side Output Impedance                                                    | R <sub>OLS</sub>   | I <sub>OUT</sub> _ = -50mA                                            | CC0 = low,<br>CC1 = high  |        | 13.5      |                                | Ω     |

|                                                                          |                    |                                                                       | CC0 = high,<br>CC1 = high |        | 26        | 48                             |       |

|                                                                          |                    |                                                                       | CC0 = low,<br>CC1 = low   |        | 9         |                                |       |

| V <sub>PPA</sub> , V <sub>PPB</sub> Connected High-                      | Da a               | Jan - 150mA                                                           | CC0 = high,<br>CC1 = low  |        | 10.5      |                                | Ω     |

| Side Output Impedance                                                    | R <sub>OHS</sub>   | I <sub>OUT</sub> = +50mA                                              | CC0 = low,<br>CC1 = high  |        | 14.5      |                                |       |

|                                                                          |                    |                                                                       | CC0 = high,<br>CC1 = high |        | 27        | 53                             |       |

| Clamp nFET Output Impedance                                              | R <sub>ONG</sub>   | $I_{OUT}$ = -50mA,                                                    |                           |        | 13.5      |                                | Ω     |

| Clamp pFET Output Impedance                                              | R <sub>OPG</sub>   | I <sub>OUT</sub> _ = +50mA                                            |                           |        | 13.5      |                                | Ω     |

| Active Damp Output Impedance                                             | R <sub>DAMP</sub>  | Before grass-clipping                                                 | diode                     |        | 500       |                                | Ω     |

# Octal Three-Level/Quad Five-Level High-Voltage 2A Digital Pulsers with T/R Switch

#### **DC ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = +3V, V_{CC} = +5V, V_{EE} = -5V, V_{PPA} = +100V, V_{NNA} = -100V, V_{PPB} = +100V, V_{NNB} = -100V, 1\mu F$  bypass capacitor between  $V_{GNA}$  and  $V_{NNA}$ , 1 $\mu$ F bypass capacitor between  $V_{GPA}$  and  $V_{PPA}$ , 1 $\mu$ F bypass capacitor between  $V_{GPB}$  and  $V_{PPB}$ ,  $V_{LDO} = 0V$ , no load, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 2)

| PARAMETER                                                                  | SYMBOL              | CONE                                                      | DITIONS                   | MIN  | TYP  | MAX | UNITS |

|----------------------------------------------------------------------------|---------------------|-----------------------------------------------------------|---------------------------|------|------|-----|-------|

|                                                                            |                     |                                                           | CC0 = low,<br>CC1 = low   |      | 2.0  |     |       |

| V <sub>NNA.</sub> V <sub>NNB</sub> Connected Low-                          |                     | V .100V                                                   | CC0 = high,<br>CC1 = low  |      | 1.5  |     | _     |

| Side Output Current                                                        | lols                | V <sub>DS</sub> = +100V                                   | CC0 = low,<br>CC1 = high  |      | 1.0  |     | A     |

|                                                                            |                     |                                                           | CC0 = high,<br>CC1 = high |      | 0.5  |     |       |

|                                                                            |                     |                                                           | CC0 = low,<br>CC1 = low   |      | 2.0  |     |       |

| V <sub>PPA</sub> , V <sub>PPB</sub> Connected High-<br>Side Output Current |                     | V .100V                                                   | CC0 = high,<br>CC1 = low  |      | 1.5  |     | A     |

|                                                                            | lohs                | $V_{DS} = +100V$                                          | CC0 = low,<br>CC1 = high  |      | 1.0  |     | A     |

|                                                                            |                     |                                                           | CC0 = high,<br>CC1 = high |      | 0.5  |     |       |

| GND-Connected nFET Output Current                                          | I <sub>ONG</sub>    | V <sub>DS</sub> = +100V                                   |                           |      | 1    |     | А     |

| GND-Connected pFET Output Current                                          | l <sub>OPG</sub>    | V <sub>DS</sub> = +100V                                   |                           |      | 1    |     | А     |

| Diode Voltage Drop (Blocking<br>Diode and Grass-Clipping<br>Diode)         | V <sub>DROP</sub>   | I <sub>OUT</sub> _ = ±50mA                                |                           |      | 1.7  |     | V     |

| LVOUT_Diode Clamping Voltage                                               | LV <sub>CLAMP</sub> | I <sub>LOAD</sub> = 1mA (MAX1                             | 4808 only)                | -0.9 |      | +1  | V     |

| Grass-Clipping Diode Reverse Capacitance                                   | C <sub>REV</sub>    |                                                           |                           |      | 2.5  |     | pF    |

| OUT_ Equivalent Large-Signal<br>Shunt Capacitance                          | C <sub>HS</sub>     | 200V <sub>P-P</sub> signal                                |                           |      | 80   |     | pF    |

| T/R Switch On Impedance                                                    | R <sub>ON</sub>     | MAX14808 only                                             |                           |      | 11.5 |     | Ω     |

| T/R Switch Off Impedance                                                   | R <sub>OFF</sub>    | MAX14808 only                                             |                           | 1    |      |     | МΩ    |

| LVOUT_ Output Offset                                                       | LV <sub>OFF</sub>   | LVOUT_, OUT_ unconnected, $V_{CC} = +5V$ , $V_{EE} = -5V$ |                           | -40  | 0    | +40 | mV    |

| THERMAL SHUTDOWN                                                           |                     |                                                           |                           |      |      |     |       |

| Thermal-Shutdown Threshold                                                 | t <sub>SDN</sub>    | Temperature rising                                        |                           |      | +145 |     | °C    |

| Thermal-Shutdown Hysteresis                                                | t <sub>HYS</sub>    |                                                           |                           |      | 20   |     | °C    |

# Octal Three-Level/Quad Five-Level High-Voltage 2A Digital Pulsers with T/R Switch

#### **AC ELECTRICAL CHARACTERISTICS**

$(V_{DD}=+3V, V_{CC}=+5V, V_{EE}=-5V, V_{PPA}=+100V, V_{NNA}=-100V, V_{PPB}=+100V, V_{NNB}=-100V, V_{GNA}$  connected to  $V_{NNB}$  with 1µF capacitor,  $V_{GNB}$  connected to  $V_{NNB}$  with 1µF capacitor,  $V_{GPA}$  connected to  $V_{PPA}$  with 1µF capacitor,  $V_{CC0}=0V$ ,  $V_{CC1}=0V$

| PARAMETER                                                                                    | SYMBOL            | COND                                                   | ITIONS               | MIN | TYP  | MAX  | UNITS |

|----------------------------------------------------------------------------------------------|-------------------|--------------------------------------------------------|----------------------|-----|------|------|-------|

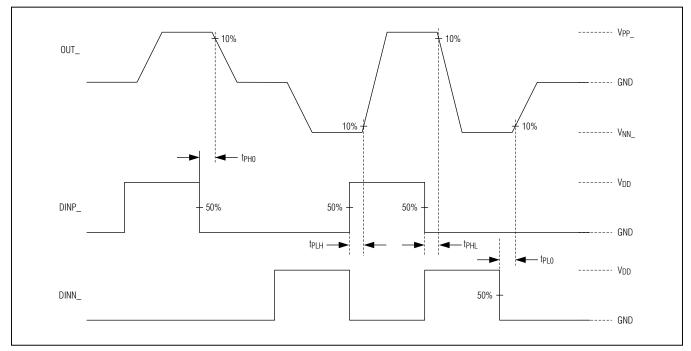

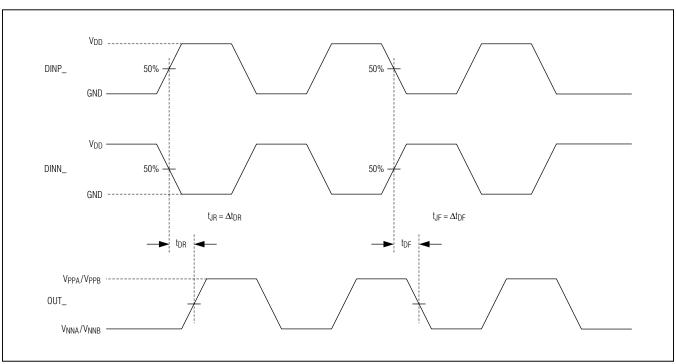

| Logic Input to Output Rise<br>Propagation Delay                                              | <sup>t</sup> PLH  | From 50% DINP_/DIN<br>mode) to 10% OUT_<br>(Figure 2a) |                      |     | 18   |      | ns    |

| Logic Input to Output Fall<br>Propagation Delay                                              | <sup>†</sup> PHL  | From 50% DINP_/DIN<br>mode) to 10% OUT_<br>(Figure 2a) |                      |     | 18   |      | ns    |

| Logic Input to Output Rise to GND Propagation Delay                                          | t <sub>PL0</sub>  | From 50% DINP_/DIN<br>mode) to 10% OUT_<br>(Figure 2a) |                      | 18  |      | ns   |       |

| Logic Input to Output Fall to GND Propagation Delay                                          | <sup>t</sup> PH0  | From 50% DINP_/DIN<br>mode) to 10% OUT_<br>(Figure 2a) |                      | 18  |      | ns   |       |

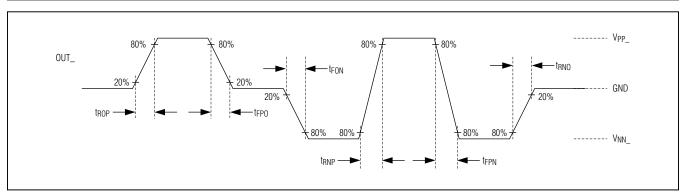

| OUT_ Fall Time ( $V_{PPA}$ to $V_{NNA}$ , $V_{PPB}$ to $V_{NNB}$ )                           | t <sub>FPN</sub>  | Figure 2b                                              |                      |     | 30   | 48   | ns    |

| OUT_ Rise Time (V <sub>NNA</sub> to V <sub>PPA,</sub> V <sub>NNB</sub> to V <sub>PPB</sub> ) | t <sub>RNP</sub>  | Figure 2b                                              |                      |     | 30   | 48   | ns    |

| OUT_ Rise Time (GND to V <sub>PPA</sub> , GND to V <sub>PPB</sub> )                          | t <sub>ROP</sub>  | Figure 2b                                              |                      |     | 15   | 22.5 | ns    |

| OUT_ Fall Time (GND to V <sub>NNA,</sub> GND to V <sub>NNB</sub> )                           | t <sub>FON</sub>  | Figure 2b                                              |                      |     | 15   | 22.5 | ns    |

|                                                                                              |                   | 20% to 80%                                             | Three-level mode     |     | 21   |      |       |

| OUT_ Rise Time (V <sub>NNA</sub> to GND, V <sub>NNB</sub> to GND)                            | t <sub>RN0</sub>  | transition<br>(Figure 2b)                              | Five-level dual mode |     | 13   |      | ns    |

|                                                                                              |                   | 20% to 80%                                             | Three-level mode     |     | 21   |      |       |

| OUT_ Fall Time (V <sub>PPA</sub> to GND <sub>,</sub><br>V <sub>PPB</sub> to GND)             | t <sub>FP0</sub>  | transition<br>(Figure 2b)                              | Five-level dual mode |     | 13   |      | ns    |

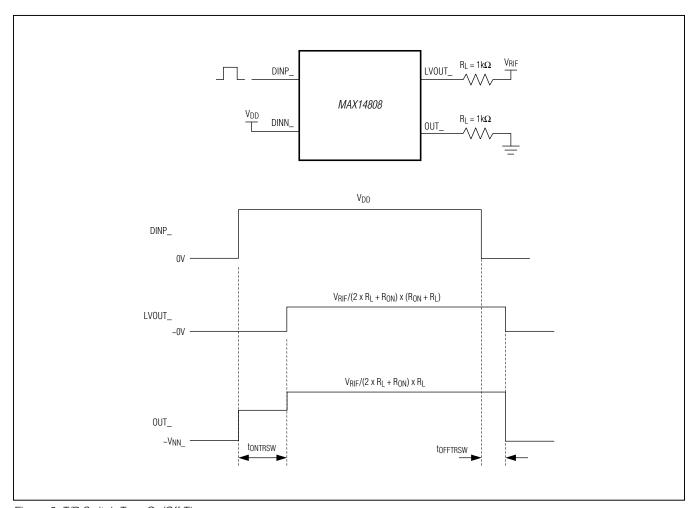

| T/R Switch Turn-On Time                                                                      | tontrsw           | (MAX14808 only) Fig                                    | ure 3                |     | 0.65 | 1.2  | μs    |

| T/R Switch Turn-Off Time                                                                     | tofftrsw          | (MAX14808 only) Figure 3 (Note 6)                      |                      |     | 0.02 | 0.1  | μs    |

| Output Enable Time (Shutdown Mode to Normal Operation)                                       | t <sub>EN1</sub>  |                                                        |                      |     |      | 100  | μs    |

| Output Disable Time (Normal Operation to Shutdown Mode)                                      | t <sub>DIS1</sub> |                                                        |                      |     |      | 10   | μs    |

# Octal Three-Level/Quad Five-Level High-Voltage 2A Digital Pulsers with T/R Switch

#### **AC ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD}=+3V,\,V_{CC}=+5V,\,V_{EE}=-5V,\,V_{PPA}=+100V,\,V_{NNA}=-100V,\,V_{PPB}=+100V,\,V_{NNB}=-100V,\,V_{GNA}\,\,\text{connected to}\,\,V_{NNA}\,\,\text{with}\,\,1\mu\text{F}\,\,\text{capacitor},\,V_{GNB}\,\,\text{connected to}\,\,V_{NNB}\,\,\text{with}\,\,1\mu\text{F}\,\,\text{capacitor},\,V_{GPB}\,\,\text{connected to}\,\,V_{PPB}\,\,\text{with}\,\,1\mu\text{F}\,\,\text{capacitor},\,V_{CC0}=0V,\,V_{CC1}=0V,\,R_L=1k\Omega,\,C_L=240\text{pF},\,\,\text{unless otherwise noted}.\,\,\text{Typical values are at}\,\,T_A=+25^\circ\text{C.})\,\,(\text{Note}\,\,2)$

| PARAMETER                                                             | SYMBOL             | CONDITIONS                                                                                                                                                                                              | MIN | TYP  | MAX | UNITS |

|-----------------------------------------------------------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|-------|

| Output Enable Time (Transmit<br>Disable Mode to Normal<br>Operation)  | <sup>t</sup> EN2   |                                                                                                                                                                                                         |     |      | 50  | ns    |

| Output Disable Time (Normal<br>Operation to Transmit Disable<br>Mode) | t <sub>DIS2</sub>  |                                                                                                                                                                                                         |     |      | 65  | ns    |

| Output Enable Time (Normal Operation to Sync Mode)                    | t <sub>EN3</sub>   |                                                                                                                                                                                                         |     |      | 4   | μs    |

| Output Disable Time (Sync<br>Mode to Normal Operation)                | t <sub>DIS3</sub>  |                                                                                                                                                                                                         |     |      | 500 | ns    |

| CLK Frequency                                                         | f <sub>CLK</sub>   | V <sub>DD</sub> = 2.5V                                                                                                                                                                                  |     |      | 200 | MHz   |

| Input Setup Time (DINN_,<br>DINP_)                                    | <sup>t</sup> SETUP | V <sub>DD</sub> = 2.5V                                                                                                                                                                                  | 2   |      |     | NS    |

| Input Hold Time (DINN_, DINP_)                                        | t <sub>HOLD</sub>  | V <sub>DD</sub> = 2.5V                                                                                                                                                                                  | 0.5 |      |     | ns    |

| Second-Harmonic Distortion (Low Voltage)                              | THD2LV             | $f_{OUT}$ = 5MHz, $V_{PPA}$ = - $V_{NNA}$ = +5 $V$ , $V_{PPB}$ = - $V_{NNB}$ = +5 $V$ , square wave (all modes)                                                                                         |     | -40  |     | dBc   |

| Second-Harmonic Distortion (High Voltage)                             | THD2HV             | $f_{OUT}$ = 5MHz, $V_{PPA}$ = - $V_{NNA}$ = +100V, $V_{PPB}$ = - $V_{NNB}$ = +100V, square wave (all modes)                                                                                             |     | -43  |     | dBc   |

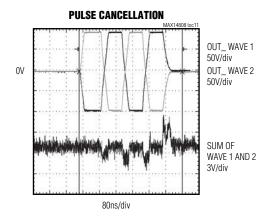

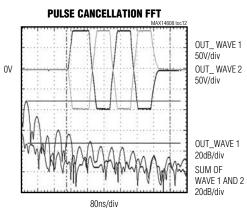

| Pulse Cancellation                                                    | PC1                | f <sub>OUT</sub> = 5MHz, V <sub>PPA</sub> = -V <sub>NNA</sub> = +100V,<br>V <sub>PPB</sub> = -V <sub>NNB</sub> = +100V, 2 periods, all<br>harmonics of the summed signed with<br>respect to the carrier |     | -40  |     | dBc   |

| Tuise Garicenation                                                    | PC2                | $f_{OUT} = 5MHz$ , $V_{PPA} = -V_{NNA} = +100V$ , $V_{PPB} = -V_{NNB} = +100V$ , 2 periods, $[(V_0 + V_{180})_{RMS}/(2 \times V_{0RMS})]_{dB}$                                                          |     | -40  |     |       |

| Pulser Bandwidth                                                      | BW                 | V <sub>PP</sub> = +60V, V <sub>NNA</sub> = -60V (Figure 4)                                                                                                                                              |     | 20   |     | MHz   |

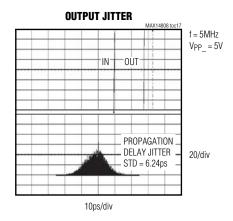

| RMS Output Jitter                                                     | t <sub>J</sub>     | f <sub>OUT</sub> = 5MHz, V <sub>PPA</sub> = -V <sub>NNA</sub> = +5V,<br>V <sub>PPB</sub> = -V <sub>NNB</sub> = +5V, both in clocked<br>mode or transparent mode (Figure 5)                              |     | 6.25 |     | ps    |

# Octal Three-Level/Quad Five-Level High-Voltage 2A Digital Pulsers with T/R Switch

#### AC ELECTRICAL CHARACTERISTICS (continued)

$(V_{DD} = +3V, V_{CC} = +5V, V_{EE} = -5V, V_{PPA} = +100V, V_{NNA} = -100V, V_{PPB} = +100V, V_{NNB} = -100V, V_{GNA} connected to <math>V_{NNA}$  with  $1\mu F$  capacitor,  $V_{GNB}$  connected to  $V_{NNB}$  with  $1\mu F$  capacitor,  $V_{GPA}$  connected to  $V_{PPA}$  with  $1\mu F$  capacitor,  $V_{GPB}$  connected to  $V_{PPB}$ with 1µF capacitor,  $V_{\overline{LDO}\ EN}$  = 0V,  $V_{\overline{CC0}}$  = 0V,  $V_{\overline{CC1}}$  = 0V,  $V_{\overline{CC1}}$  = 1k $\Omega$ ,  $C_L$  = 240pF, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C.$ ) (Note 2)

| PARAMETER                                          | SYMBOL              | CONDITIONS                                              | MIN TYP MAX |     |  | UNITS |

|----------------------------------------------------|---------------------|---------------------------------------------------------|-------------|-----|--|-------|

| T/R Switch Harmonic Distortion (MAX14808)          | THD <sub>TRSW</sub> | $R_{LOAD} = 200\Omega$ , $V_{SIGNAL} = 100$ m $V_{P-P}$ |             | -50 |  | dB    |

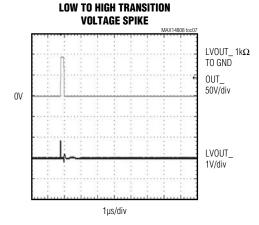

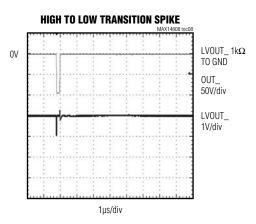

| T/R Switch Turn-On/Off Voltage<br>Spike (MAX14808) | V <sub>SPIKE</sub>  | $R_{LOAD}$ = 1k $\Omega$ at both sides of T/R switch    |             | 50  |  | mV    |

| Crosstalk                                          | СТ                  | $f = 5MHz$ , adjacent channels, $R_{LOUT} = 200\Omega$  |             | -51 |  | dB    |

- Note 2: All devices are 100% production tested at T<sub>A</sub> = +85°C. Limits over the operating temperature range are guaranteed by design.

- Note 3: Maximum operating current from V<sub>GN</sub> and V<sub>GP</sub> external power sources can vary depending on application requirements. The suggested minimum values assume 8 channels running in continuous transmission (CWD) at 5MHz with CC0 = CC1 = high.

- **Note 4:** CW Doppler: continuous wave, f = 5MHz,  $V_{DD} = +3V$ ,  $V_{CC} = -V_{EE} = +5V$ ,  $V_{PP} = -V_{NN} = +5V$ . **Note 5:** B mode: f = 5MHz, PRF = 5kHz, 1 period,  $V_{DD} = +3V$ ,  $V_{CC} = -V_{EE} = +5V$ ,  $V_{PP} = -V_{NN} = +100V$ .

- Note 6: T/R switch turn-off time is the time required to switch off the bias current of the T/R switch. The off-isolation is not guaranteed.

### **Timing Diagrams**

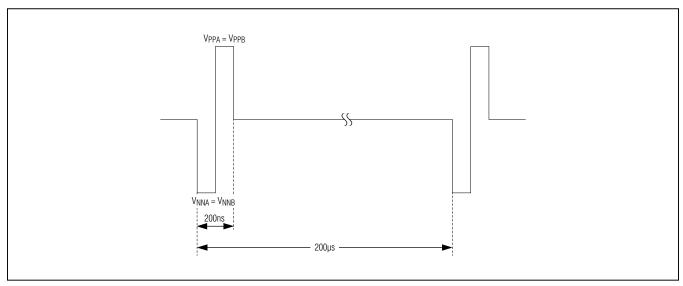

Figure 1a. High-Voltage Burst Test (Three Levels)

# Octal Three-Level/Quad Five-Level High-Voltage 2A Digital Pulsers with T/R Switch

### **Timing Diagrams (continued)**

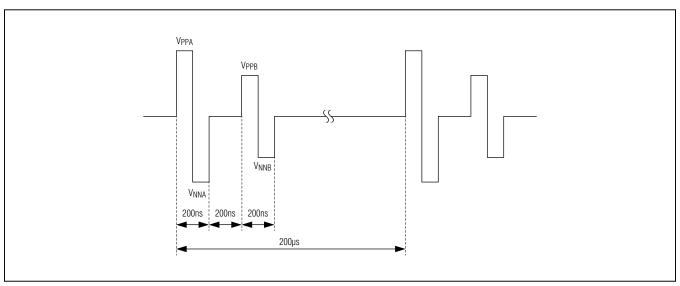

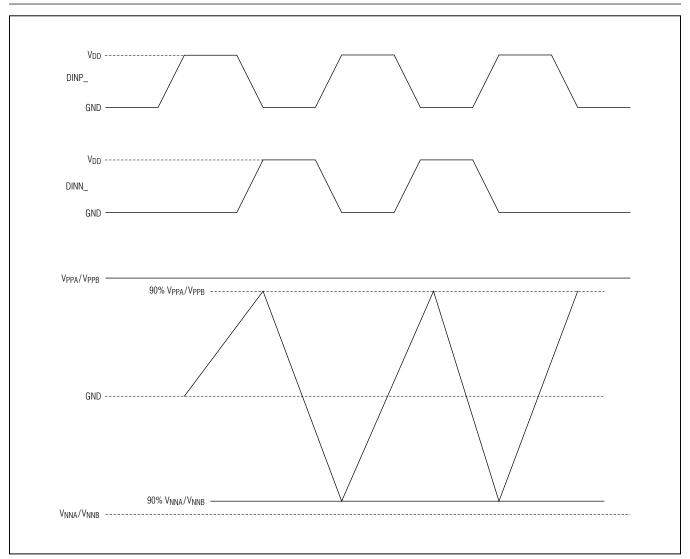

Figure 1b. High-Voltage Burst Test (Five Levels)

Figure 2a. Propagation Delay Timing

# Octal Three-Level/Quad Five-Level High-Voltage 2A Digital Pulsers with T/R Switch

### **Timing Diagrams (continued)**

Figure 2b. Output Rise/Fall Timing

Figure 3. T/R Switch Turn-On/Off Time

# Octal Three-Level/Quad Five-Level High-Voltage 2A Digital Pulsers with T/R Switch

### **Timing Diagrams (continued)**

Figure 4. Bandwidth

# Octal Three-Level/Quad Five-Level High-Voltage 2A Digital Pulsers with T/R Switch

### **Timing Diagrams (continued)**

Figure 5. Jitter Timing

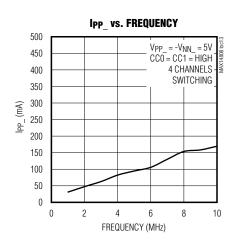

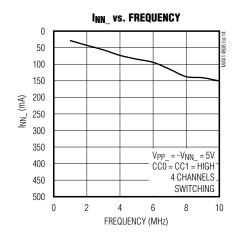

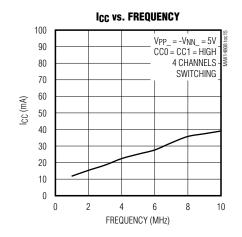

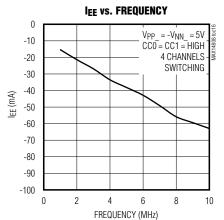

### **Typical Operating Characteristics**

$(V_{DD} = +5V, V_{CC} = +5V, V_{EE} = -5V, V_{PP} = +100V, V_{NN} = -100V, R_L = 1k\Omega, C_L = 240pF, unless otherwise noted. Typical values are at <math>T_A = +25^{\circ}C$ .)

# Octal Three-Level/Quad Five-Level High-Voltage 2A Digital Pulsers with T/R Switch

### **Typical Operating Characteristics (continued)**

$(V_{DD} = +5V, V_{CC} = +5V, V_{EE} = -5V, V_{PP} = +100V, V_{NN} = -100V, R_{L} = 1k\Omega, C_{L} = 240pF, unless otherwise noted. Typical values are at T_{A} = +25^{\circ}C.)$

# Octal Three-Level/Quad Five-Level High-Voltage 2A Digital Pulsers with T/R Switch

### **Typical Operating Characteristics (continued)**

$(V_{DD} = +5V, V_{CC} = +5V, V_{EE} = -5V, V_{PP} = +100V, V_{NN} = -100V, R_{L} = 1k\Omega, C_{L} = 240pF, unless otherwise noted. Typical values are at T_{A} = +25^{\circ}C.)$

# Octal Three-Level/Quad Five-Level High-Voltage 2A Digital Pulsers with T/R Switch

### **Typical Operating Characteristics (continued)**

$(V_{DD} = +5V, V_{CC} = +5V, V_{EE} = -5V, V_{PP} = +100V, V_{NN} = -100V, R_{L} = 1k\Omega, C_{L} = 240pF, unless otherwise noted. Typical values are at T_{A} = +25^{\circ}C.)$

# Octal Three-Level/Quad Five-Level High-Voltage 2A Digital Pulsers with T/R Switch

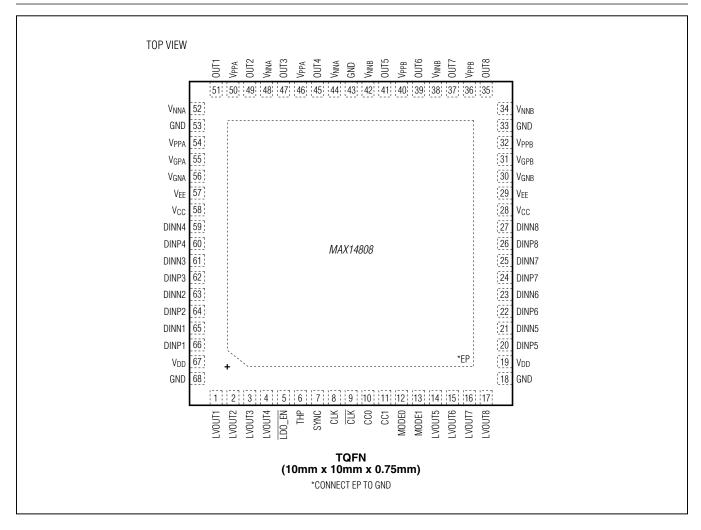

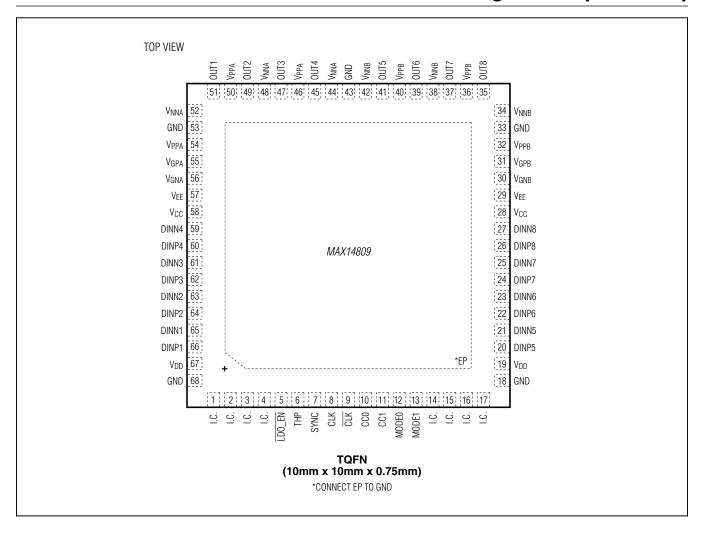

### **Pin Configurations**

# Octal Three-Level/Quad Five-Level High-Voltage 2A Digital Pulsers with T/R Switch

**Pin Configurations (continued)**

# Octal Three-Level/Quad Five-Level High-Voltage 2A Digital Pulsers with T/R Switch

### **Pin Description**

| Р                     | PIN                   |          |                                                                                                                                                                                                                                                                                                                               |  |

|-----------------------|-----------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| MAX14808              | MAX14809              | NAME     | FUNCTION                                                                                                                                                                                                                                                                                                                      |  |

| 1                     | _                     | LVOUT1   | Low-Voltage T/R Switch Output 1                                                                                                                                                                                                                                                                                               |  |

| 2                     | _                     | LVOUT2   | Low-Voltage T/R Switch Output 2                                                                                                                                                                                                                                                                                               |  |

| 3                     | _                     | LVOUT3   | Low-Voltage T/R Switch Output 3                                                                                                                                                                                                                                                                                               |  |

| 4                     | _                     | LVOUT4   | Low-Voltage T/R Switch Output 4                                                                                                                                                                                                                                                                                               |  |

| _                     | 1–4, 14–17            | I.C.     | Internally Connected. Connect I.C. to GND externally.                                                                                                                                                                                                                                                                         |  |

| 5                     | 5                     | LDO_EN   | Internal Supply Generator Control Input. Drive LDO_EN high to disable the internal power supply when using an external power supply on V <sub>GPA</sub> , V <sub>GPB</sub> , V <sub>GNA</sub> , and V <sub>GNB</sub> . LDO_EN has an internal 10kΩ pulldown resistor to GND.                                                  |  |

| 6                     | 6                     | THP      | Open-Drain Thermal-Protection Output. THP asserts and sinks a 3mA current to GND when the junction temperature exceeds +150°C.                                                                                                                                                                                                |  |

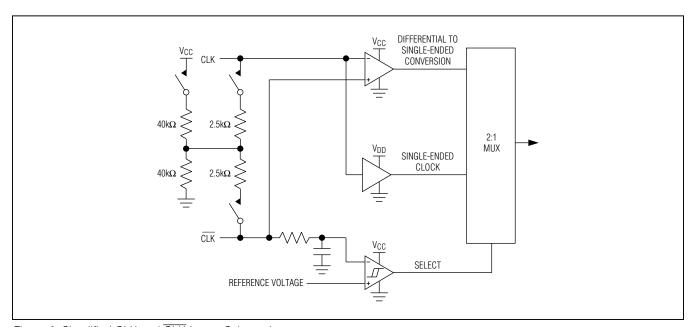

| 7                     | 7                     | SYNC     | CMOS Control Input. Drive SYNC high to enable clocked-input mode. Drive SYNC low to operate in transparent mode (see the <i>Truth Tables</i> section).                                                                                                                                                                        |  |

| 8                     | 8                     | CLK      | CMOS Control Input. Clock positive phase input. Data inputs are clocked in at the rising edge of CLK and CLK in differential clocked mode or at the rising edge of CLK in single-ended clocked mode. Clock maximum frequency is 160MHz.                                                                                       |  |

| 9                     | 9                     | CLK      | CMOS Control Input. Clock negative phase input. Data inputs are clocked in at the edge of CLK and CLK in differential clocked mode. Clock maximum frequency is 160MHz. If CLK is connected to GND, the CLK input is a single-ended logic-level clock input. Otherwise, CLK and CLK are self-biased differential clock inputs. |  |