# 10-Bit *nano*DAC with SPI/I<sup>2</sup>C Interface and 2 ppm/°C On-Chip Reference

## **Data Sheet**

### FEATURES

High relative accuracy (INL): ±0.5 LSB maximum Low drift 2.5 V reference: 2 ppm/°C typical Selectable span output: 2.5 V or 5 V Total unadjusted error (TUE): 0.06% of FSR maximum Offset error: ±1.5 mV maximum Gain error: ±0.05% of FSR maximum Low glitch: 0.1 nV-sec High drive capability: 20 mA Low power: 1.2 mW at 3.3 V Independent logic supply: 1.8 V logic compatible Wide operating temperature range: -40°C to +105°C Robust 4 kV HBM ESD protection

### **APPLICATIONS**

Process controls Data acquisition systems Digital gain and offset adjustment Programmable voltage sources Optical modules

### **GENERAL DESCRIPTION**

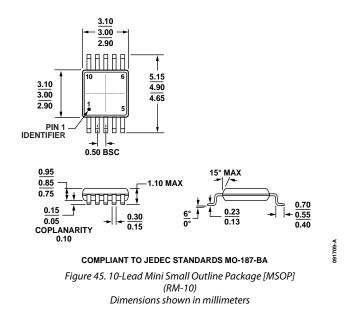

The AD5310R/AD5311R, members of the *nano*DAC<sup>\*</sup> family, are low power, single-channel, 10-bit buffered voltage output DACs. The devices include an enabled by default internal 2.5 V reference, and provides 2 ppm/°C. The output span can be programmed to be 0 V to  $V_{REF}$  or 0 V to 2 ×  $V_{REF}$ . All devices operate from a single 2.7 V to 5.5 V supply and are guaranteed monotonic by design. The devices are available in 10-lead MSOP packages.

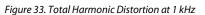

The internal power-on reset circuit of the AD5310R/AD5311R ensures that the DAC register is written to zero scale at powerup when the internal output buffer is configured in normal mode. The devices contain a power-down mode that reduces the current consumption of the device to  $2 \mu A$  at 5 V.

The AD5310R/AD5311R use a versatile SPI or I<sup>2</sup>C interface, including an asynchronous  $\overrightarrow{\text{RESET}}$  pin and a V<sub>LOGIC</sub> pin that provides 1.8 V compatibility.

# AD5310R/AD5311R

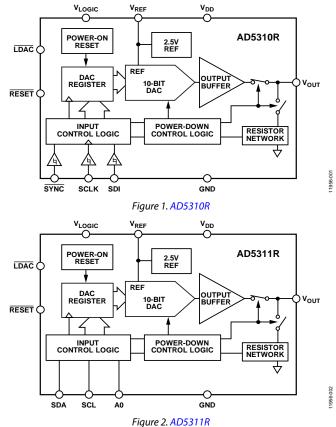

## FUNCTIONAL BLOCK DIAGRAMS

### Table 1. Related Devices

| Interface        | Reference | 12-Bit  | 10-Bit              |

|------------------|-----------|---------|---------------------|

| SPI              | External  | AD5681R | AD5310 <sup>1</sup> |

| I <sup>2</sup> C | External  |         | AD5311 <sup>1</sup> |

<sup>1</sup> The AD5310R and AD5311R are not pin-to-pin or software compatible with the AD5310 and AD5311, respectively.

### **PRODUCT HIGHLIGHTS**

- 1. High Relative Accuracy (INL): ±0.5 LSB maximum.

- 2. Low Drift 2.5 V On-Chip Reference: 5 ppm/°C maximum temperature coefficient.

**Document Feedback**

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

# TABLE OF CONTENTS

| Features                                     |

|----------------------------------------------|

| Applications1                                |

| General Description                          |

| Functional Block Diagrams1                   |

| Product Highlights 1                         |

| Revision History 2                           |

| Specifications                               |

| AC Characteristics                           |

| Timing Characteristics                       |

| Absolute Maximum Ratings                     |

| Thermal Resistance                           |

| ESD Caution                                  |

| Pin Configurations and Function Descriptions |

| Typical Performance Characteristics          |

| Terminology16                                |

| Theory of Operation17                        |

| Digital-to-Analog Converter17                |

## **REVISION HISTORY**

| 2/2017—Rev. A to Rev. B                                                                                         |

|-----------------------------------------------------------------------------------------------------------------|

| Changes to Features Section and Table 1 1                                                                       |

| Changed 1.8 V $\leq$ V <sub>LOGIC</sub> $\leq$ 5.5 V (V <sub>LOGIC</sub> = 1.8 V to 5.5 V) to                   |

| $1.62~V \leq V_{\text{LOGIC}} \leq 5.5~V$                                                                       |

| Changed 1.8 V $\leq$ V <sub>LOGIC</sub> $\leq$ V <sub>DD</sub> to 1.62 V $\leq$ V <sub>LOGIC</sub> $\leq$ 5.5 V |

| Changes to VLOGIC Parameter, Table 2 4                                                                          |

| Changed $V_{\text{LOGIC}}$ = 1.8 V to 5.5 V to 1.62 V $\leq$ $V_{\text{LOGIC}}$ $\leq$ 5.5 V 5                  |

| Changes to Table 4 and Figure 35                                                                                |

| Changed $V_{\text{LOGIC}}$ = 1.8 V to 5.5 V to 1.62 V $\leq$ $V_{\text{LOGIC}}$ $\leq$ 5.5 V 6                  |

| Changes to Table 89                                                                                             |

| Changes to Table 9 10                                                                                           |

| Changes to Terminology Section16                                                                                |

| Changes to Transfer Function Section17                                                                          |

| Transfer Function                              | 17 |

|------------------------------------------------|----|

| DAC Architecture                               | 17 |

| Serial Interface                               | 18 |

| AD5310R SPI Serial Data Interface              | 18 |

| Daisy-Chain Mode Compatibility                 | 18 |

| AD5311R I <sup>2</sup> C Serial Data Interface | 19 |

| Commands                                       | 21 |

| Load DAC (Hardware LDAC Pin)                   | 22 |

| Hardware RESET                                 | 22 |

| AD5311R, I <sup>2</sup> C Read Operation       | 22 |

| Thermal Hysteresis                             | 23 |

| Power-Up Sequence                              | 23 |

| Layout Guidelines                              | 23 |

| Outline Dimensions                             | 24 |

| Ordering Guide                                 | 24 |

### 1/2014—Rev. 0 to Rev. A

| Change to Features Section                              | 1  |

|---------------------------------------------------------|----|

| Removed Endnote 2, Endnote 3, Endnote 5, and Endnote 6, |    |

| Table 2; Renumbered Sequentially                        | 3  |

| Removed Endnote 3, Table 3                              | 4  |

| Removed Endnote 1, Table 4; Renumbered Sequentially     | 5  |

| Changes to Table 6                                      | 8  |

| Removed Solder Heat Reflow Section and Figure 44;       |    |

| Renumbered Sequentially                                 | 23 |

1/2014—Revision 0: Initial Version

# **SPECIFICATIONS**

$V_{\text{DD}} = 2.7 \text{ V to } 5.5 \text{ V}, R_{\text{L}} = 2 \text{ } k\Omega \text{ to GND}, C_{\text{L}} = 200 \text{ } p\text{F} \text{ to GND}, 2.5 \text{ } V \leq V_{\text{REF}} \leq V_{\text{DD}}, 1.62 \text{ } V \leq V_{\text{LOGIC}} \leq 5.5 \text{ } V, -40^{\circ}\text{C} < T_{\text{A}} < +105^{\circ}\text{C}, \text{ unless otherwise noted.}$

| Parameter                                | Min    | Тур      | Мах                | Unit           | Test Conditions/Comments                                                  |

|------------------------------------------|--------|----------|--------------------|----------------|---------------------------------------------------------------------------|

| STATIC PERFORMANCE <sup>1</sup>          |        | -76      |                    |                |                                                                           |

| Resolution                               | 10     |          |                    | Bits           |                                                                           |

| Relative Accuracy, INL                   | 10     |          | ±0.5               | LSB            |                                                                           |

| Differential Nonlinearity, DNL           |        |          | ±0.5               | LSB            |                                                                           |

| Zero-Code Error                          |        |          | 1.25               | mV             | All 0s loaded to DAC register                                             |

| Offset Error                             |        |          | ±1.5               | mV             | All os louded to DAE register                                             |

| Full-Scale Error                         |        |          | ±0.075             | % of FSR       | All 1s loaded to DAC register                                             |

| Gain Error                               |        |          | ±0.075             | % of FSR       | All 13 loaded to DAC register                                             |

| Total Unadjusted Error, TUE              |        |          | ±0.05<br>±0.16     | % of FSR       | Internal reference, gain = 1                                              |

|                                          |        |          | ±0.16<br>±0.14     | % of FSR       | Internal reference, gain = $2$                                            |

|                                          |        |          | ±0.14<br>±0.075    | % of FSR       | External reference, gain = 1                                              |

|                                          |        |          | ±0.075             | % of FSR       | _                                                                         |

| Zero-Code Error Drift                    |        | ±1       | ±0.06              |                | External reference, gain = 2                                              |

| Offset Error Drift                       |        |          |                    | μV/°C<br>μV/°C |                                                                           |

|                                          |        | ±1<br>±1 |                    |                |                                                                           |

| Gain Temperature Coefficient             |        |          |                    | ppm/°C         | $DAC$ code - midecole $V_{\rm e}$ - $EV_{\rm e}$ 10%                      |

| DC Power Supply Rejection<br>Ratio, PSRR |        | 0.2      |                    | mV/V           | DAC code = midscale, $V_{DD} = 5 V \pm 10\%$                              |

| OUTPUT CHARACTERISTICS                   |        |          |                    |                |                                                                           |

| Output Voltage Range                     | 0      |          | VREF               | V              | Gain = 1                                                                  |

|                                          | 0      |          | $2 \times V_{REF}$ | V              | Gain = 2                                                                  |

| Capacitive Load Stability                |        | 2        |                    | nF             | $R_L = \infty$                                                            |

|                                          |        | 10       |                    | nF             | $R_L = 2 k\Omega$                                                         |

| Resistive Load                           | 1      |          |                    | kΩ             | $C_L = 0 \ \mu F$                                                         |

| Load Regulation                          |        | 10       |                    | μV/mA          | $V_{DD} = 5 V$ , DAC code = midscale;<br>-30 mA $\leq I_{OUT} \leq 30 mA$ |

|                                          |        | 10       |                    | μV/mA          | $V_{DD} = 3 V$ , DAC code = midscale;<br>-20 mA $\leq I_{OUT} \leq 20 mA$ |

| Short-Circuit Current                    | 20     |          | 50                 | mA             |                                                                           |

| Load Impedance at Rails <sup>2</sup>     |        | 20       |                    | Ω              |                                                                           |

| REFERENCE OUTPUT                         |        |          |                    |                |                                                                           |

| Output Voltage                           | 2.4975 |          | 2.5025             | V              | At ambient temperature                                                    |

| Voltage Reference TC <sup>3</sup>        |        | 2        | 5                  | ppm/°C         | See the Terminology section                                               |

| Output Impedance                         |        | 0.05     |                    | Ω              | 5,                                                                        |

| Output Voltage Noise                     |        | 16.5     |                    | μV p-p         | 0.1 Hz to 10 Hz                                                           |

| Output Voltage Noise Density             |        | 240      |                    | nV/√Hz         | At ambient temperature; $f = 10$ kHz,                                     |

|                                          |        |          |                    |                | C <sub>L</sub> = 10 nF                                                    |

| Capacitive Load Stability                |        | 5        |                    | μF             | $R_L = 2 k\Omega$                                                         |

| Load Regulation, Sourcing                |        | 50       |                    | μV/mA          | At ambient temperature; $V_{DD} \ge 3 V$                                  |

| Load Regulation, Sinking                 |        | 30       |                    | μV/mA          | At ambient temperature                                                    |

| Output Current Load Capability           |        | ±5       |                    | mA             | $V_{DD} \ge 3 V$                                                          |

| Line Regulation                          |        | 80       |                    | μV/V           | At ambient temperature                                                    |

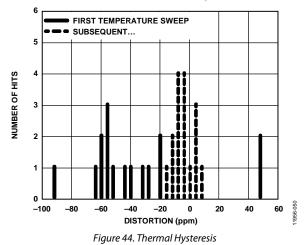

| Thermal Hysteresis                       |        | 125      |                    | ppm            | First cycle                                                               |

|                                          |        | 25       |                    | ppm            | Additional cycles                                                         |

| Parameter                            | Min                      | Тур  | Max                           | Unit | Test Conditions/Comments                      |

|--------------------------------------|--------------------------|------|-------------------------------|------|-----------------------------------------------|

| LOGIC INPUTS                         |                          |      |                               |      |                                               |

| Input Current, I <sub>IN</sub>       |                          |      | ±1                            | μΑ   | Per pin                                       |

|                                      |                          |      | ±4                            | μA   | SDA and SCL pins (AD5311R)                    |

| Input Low Voltage, VINL              |                          |      | $0.3 \times V_{\text{LOGIC}}$ | V    |                                               |

| Input High Voltage, V <sub>INH</sub> | $0.7 \times V_{LOGIC}$   |      |                               | V    |                                               |

| Pin Capacitance, C <sub>IN</sub>     |                          | 2    |                               | pF   |                                               |

| LOGIC OUTPUT (SDA)                   |                          |      |                               |      | AD5311R                                       |

| Output Low Voltage, Vol              |                          |      | 0.4                           | V    | I <sub>SINK</sub> = 200 μA                    |

| Output High Voltage, V <sub>он</sub> | $V_{\text{LOGIC}} - 0.4$ |      |                               | V    | $I_{SOURCE} = 200 \mu A$                      |

| Pin Capacitance                      |                          | 4    |                               | pF   |                                               |

| POWER REQUIREMENTS                   |                          |      |                               |      |                                               |

| VLOGIC                               | 1.62                     |      | 5.5                           | V    |                                               |

| Ilogic                               |                          | 0.25 | 3                             | μA   | $V_{IH} = V_{LOGIC} \text{ or } V_{IL} = GND$ |

| V <sub>DD</sub>                      | 2.7                      |      | 5.5                           | V    | Gain = 1                                      |

|                                      | V <sub>REF</sub> + 1.5   |      | 5.5                           | V    | Gain = 2                                      |

| ldd                                  |                          |      |                               |      | $V_{IH} = V_{DD}, V_{IL} = GND$               |

| Normal Mode <sup>4</sup>             |                          | 350  | 500                           | μΑ   | Internal reference enabled                    |

|                                      |                          | 110  | 180                           | μΑ   | Internal reference disabled                   |

| Power-Down Modes⁵                    |                          |      | 2                             | μA   |                                               |

<sup>1</sup> Linearity is calculated using a reduced code range: Code 8 to Code 1024, output unloaded.

<sup>2</sup>When drawing a load current at either rail, the output voltage headroom, with respect to that rail, is limited by the 20 Ω typical channel resistance of the output devices; for example, when sinking 1 mA, the minimum output voltage with 20  $\Omega$ , 1 mA generates 20 mV. See Figure 29.

<sup>3</sup> Reference temperature coefficient calculated as per the box method. See the Terminology section for more information.

<sup>4</sup> Interface inactive. DAC active. Code = zero-scale, DAC output unloaded.

<sup>5</sup> DAC powered down.

### **AC CHARACTERISTICS**

$V_{\text{DD}} = 2.7 \text{ V to } 5.5 \text{ V}, \\ R_{\text{L}} = 2 \text{ k} \Omega \text{ to GND}, \\ C_{\text{L}} = 200 \text{ pF to GND}, \\ 2.5 \text{ V} \le V_{\text{REF}} \le V_{\text{DD}}, \\ 1.62 \text{ V} \le V_{\text{LOGIC}} \le 5.5 \text{ V}, \\ -40^{\circ}\text{C} < T_{\text{A}} < +105^{\circ}\text{C}, \\ \text{unless} = 10^{\circ}\text{C}, \\ 1.62 \text{ V} \le V_{\text{LOGIC}} \le 5.5 \text{ V}, \\ 1.62 \text{ V} \le V_{\text{LOGIC}} \le 5.5 \text{ V}, \\ 1.62 \text{ V} \le V_{\text{LOGIC}} \le 5.5 \text{ V}, \\ 1.62 \text{ V} \le V_{\text{LOGIC}} \le 5.5 \text{ V}, \\ 1.62 \text{ V} \le V_{\text{LOGIC}} \le 5.5 \text{ V}, \\ 1.62 \text{ V} \le V_{\text{LOGIC}} \le 5.5 \text{ V}, \\ 1.62 \text{ V} \le V_{\text{LOGIC}} \le 5.5 \text{ V}, \\ 1.62 \text{ V} \le V_{\text{LOGIC}} \le 5.5 \text{ V}, \\ 1.62 \text{ V} \le 1.62 \text{ V} = 1.62 \text{$ otherwise noted.1

| Table | 3. |

|-------|----|

|-------|----|

| Parameter <sup>2</sup>                       | Тур | Max | Unit   | Conditions/Comments                                                       |

|----------------------------------------------|-----|-----|--------|---------------------------------------------------------------------------|

| Output Voltage Settling Time                 | 5   | 7   | μs     | Gain = 1, $\frac{1}{4}$ to $\frac{3}{4}$ scale settling to $\pm 0.25$ LSB |

| Slew Rate                                    | 0.7 |     | V/µs   |                                                                           |

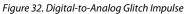

| Digital-to-Analog Glitch Impulse             | 0.1 |     | nV-sec | $\pm 1$ LSB change around major carry, gain = 1                           |

| Digital Feedthrough                          | 0.1 |     | nV-sec |                                                                           |

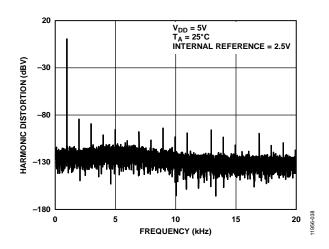

| Total Harmonic Distortion (THD)              | -83 |     | dB     | $V_{REF} = 2 V \pm 0.1 V p$ -p, f = 10 kHz                                |

| Output Noise Spectral Density                | 200 |     | nV/√Hz | DAC code = midscale, $f = 10 \text{ kHz}$                                 |

| Output Noise                                 | 6   |     | μV p-р | 0.1 Hz to 10 Hz; internal reference                                       |

| Signal-to-Noise Ratio (SNR)                  | 90  |     | dB     | At ambient temperature, BW = 20 kHz, $V_{DD}$ = 5 V, $f_{OUT}$ = 1 kHz    |

| Spurious-Free Dynamic Range (SFDR)           | 88  |     | dB     | At ambient temperature, BW = 20 kHz, $V_{DD}$ = 5 V, $f_{OUT}$ = 1 kHz    |

| Signal-to-Noise-and Distortion (SINAD) Ratio | 82  |     | dB     | At ambient temperature, BW = 20 kHz, $V_{DD}$ = 5 V, $f_{OUT}$ = 1 kHz    |

<sup>1</sup> Temperature range =  $-40^{\circ}$ C to  $+105^{\circ}$ C, typical at 25°C.

<sup>2</sup> See the Terminology section.

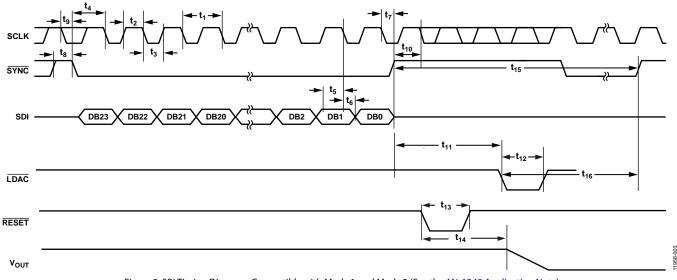

## TIMING CHARACTERISTICS

### AD5310R

$V_{\text{DD}}$  = 2.7 V to 5.5 V, 1.62 V  $\leq$  V\_{LOGIC}  $\leq$  5.5 V, -40°C <  $T_{\text{A}}$  < +105°C, unless otherwise noted.

### Table 4.

|                                                    |                             | $1.8 \text{ V} \leq \text{V}_{\text{LOGIC}} \leq 2.7 \text{ V}$ |     | ≤ 2.7 V | $2.7 \text{ V} \leq V_{\text{LOGIC}}^2 \leq 5.5 \text{ V}$ |     |     |      |

|----------------------------------------------------|-----------------------------|-----------------------------------------------------------------|-----|---------|------------------------------------------------------------|-----|-----|------|

| Parameter <sup>1</sup>                             | Symbol                      | Min                                                             | Тур | Мах     | Min                                                        | Тур | Мах | Unit |

| SCLK Cycle Time                                    | t1                          | 33                                                              |     |         | 20                                                         |     |     | ns   |

| SCLK High Time                                     | t <sub>2</sub>              | 16                                                              |     |         | 10                                                         |     |     | ns   |

| SCLK Low Time                                      | t <sub>3</sub>              | 16                                                              |     |         | 10                                                         |     |     | ns   |

| SYNC to SCLK Falling Edge Setup Time               | t <sub>4</sub>              | 15                                                              |     |         | 10                                                         |     |     | ns   |

| Data Setup Time                                    | t5                          | 5                                                               |     |         | 5                                                          |     |     | ns   |

| Data Hold Time                                     | t <sub>6</sub>              | 5                                                               |     |         | 5                                                          |     |     | ns   |

| SCLK Falling Edge to SYNC Rising Edge              | t7                          | 15                                                              |     |         | 10                                                         |     |     | ns   |

| Minimum SYNC High Time                             | t <sub>8</sub>              | 20                                                              |     |         | 20                                                         |     |     | ns   |

| SYNC Falling Edge to SCLK Fall Ignore              | t9                          | 16                                                              |     |         | 10                                                         |     |     | ns   |

| SYNC Rising Edge to SCLK Falling Edge              | t <sub>10</sub>             |                                                                 |     |         |                                                            |     |     | ns   |

| SYNC Rising Edge to LDAC Falling Edge              | t11                         | 25                                                              |     |         | 25                                                         |     |     | ns   |

| LDAC Pulse Width Low                               | t <sub>12</sub>             | 20                                                              |     |         | 15                                                         |     |     | ns   |

| <b>RESET</b> Minimum Pulse Width Low               | t13                         | 75                                                              |     |         | 75                                                         |     |     | ns   |

| <b>RESET</b> Pulse Activation Time                 | t <sub>14</sub>             | 150                                                             |     |         | 150                                                        |     |     | ns   |

| SYNC Rising Edge to SYNC Rising Edge (DAC Updates) | t <sub>15</sub>             | 1.9                                                             |     |         | 1.7                                                        |     |     | μs   |

| LDAC Falling Edge to SYNC Rising Edge              | t <sub>16</sub>             | 1.8                                                             |     |         | 1.65                                                       |     |     | μs   |

| Reference Power-Up <sup>3</sup>                    | $t_{\text{REF}_POWER_UP}^4$ |                                                                 | 600 |         |                                                            | 600 |     | μs   |

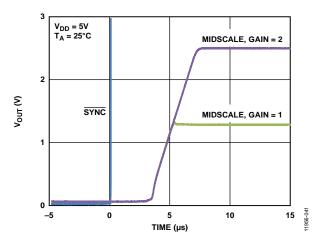

| Exit Shutdown <sup>3</sup>                         | t <sub>shutdown</sub> ⁵     |                                                                 |     | 6       |                                                            |     | 6   | μs   |

<sup>1</sup> All input signals are specified with  $t_R = t_F = 1$  ns/V (10% to 90% of V<sub>DD</sub>) and timed from a voltage level of (V<sub>IL</sub> + V<sub>IH</sub>)/2.

$^2$  Substitute  $V_{\text{DD}}$  for  $V_{\text{LOGIC}}$  on devices that do not include a  $V_{\text{LOGIC}}$  pin.

<sup>3</sup> Not shown in Figure 3.

<sup>4</sup> Same timing must be expected when powering up the device after  $V_{DD} = 2.7$  V.

<sup>5</sup> Time required to exit power-down to normal mode of AD5310R/AD5311R operation; <u>SYNC</u> rising edge to 90% of DAC midscale value, with output unloaded.

### Timing and Circuit Diagrams

Figure 3. SPI Timing Diagram, Compatible with Mode 1 and Mode 2 (See the AN-1248 Application Note)

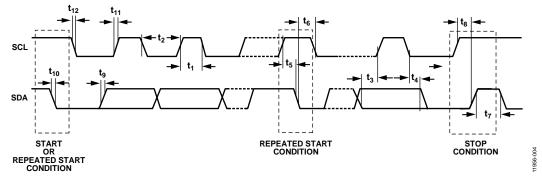

### AD5311R

$V_{\text{DD}}$  = 2.7 V to 5.5 V, 1.62 V  $\leq$  V\_{LOGIC}  $\leq$  5.5 V, -40°C < Ta < +105°C, unless otherwise noted.

| Table 5.                                                             |                               |                                    |     |     |      |

|----------------------------------------------------------------------|-------------------------------|------------------------------------|-----|-----|------|

| Parameter <sup>1</sup>                                               | Symbol                        | Min                                | Тур | Max | Unit |

| Serial Clock Frequency (Not Shown in Figure 4 or Figure 5)           | f <sub>SCL</sub> <sup>2</sup> |                                    |     | 400 | kHz  |

| SCL High Time, t <sub>HIGH</sub>                                     | t <sub>1</sub>                | 0.6                                |     |     | μs   |

| SCL Low Time, t <sub>LOW</sub>                                       | t <sub>2</sub>                | 1.3                                |     |     | μs   |

| Data Setup Time, t <sub>su; DAT</sub>                                | t <sub>3</sub>                | 100                                |     |     | ns   |

| Data Hold Time, t <sub>HD; DAT</sub>                                 | t4                            | 0                                  |     | 0.9 | μs   |

| Setup Time for a Repeated Start Condition, tsu; STA                  | t5                            | 0.6                                |     |     | μs   |

| Hold Time (Repeated) Start Condition, tHD; STA                       | t <sub>6</sub>                | 0.6                                |     |     | μs   |

| Bus Free Time Between a Stop and a Start Condition, $t_{\text{BUF}}$ | t7                            | 1.3                                |     |     | μs   |

| Setup Time for a Stop Condition, tsu; sto                            | t <sub>8</sub>                | 0.6                                |     |     | μs   |

| Rise Time of SDA Signal, t <sub>R</sub>                              | t9                            | 20                                 |     | 300 | ns   |

| Fall Time of SDA Signal, t <sub>F</sub>                              | t <sub>10</sub>               | $20 \times (V_{DD}/5.5 V)$         |     | 300 | ns   |

| Rise Time of SCL Signal, t <sub>R</sub>                              | t11                           | 20                                 |     | 300 | ns   |

| Fall Time of SCL Signal, t⊧                                          | <b>t</b> <sub>12</sub>        | $20 \times (V_{DD}/5.5 \text{ V})$ |     | 300 | ns   |

| Pulse Width of Suppressed Spike (Not Shown in Figure 4<br>Figure 5)  | t <sub>sP</sub>               | 0                                  |     | 50  | ns   |

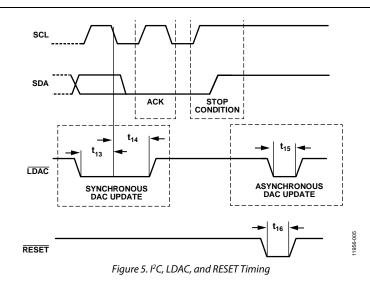

| LDAC Falling Edge to SCL Falling Edge                                | t <sub>13</sub>               | 400                                |     |     | ns   |

| LDAC Pulse Width (Synchronous Mode)                                  | t <sub>14</sub>               | 400                                |     |     | ns   |

| LDAC Pulse Width (Asynchronous Mode)                                 | t15                           | 20                                 |     |     | ns   |

| RESET Pulse Width                                                    | <b>t</b> <sub>16</sub>        | 75                                 |     |     | ns   |

| Reference Power-Up (Not Shown in Figure 4 or Figure 5)               | $t_{\text{REF}_POWER_UP}^3$   |                                    | 600 |     | μs   |

| Exit Shutdown (Not Shown in Figure 4 or Figure 5)                    | tshutdown <sup>4</sup>        |                                    |     | 6   | μs   |

<sup>1</sup> Maximum bus capacitance is limited to 400 pF. All input signals are specified with  $t_R = t_F = 1 \text{ ns/V}$  (10% to 90% of  $V_{DD}$ ) and timed from a voltage level of ( $V_{IL} + V_{IH}$ )/2. <sup>2</sup> The SDA and SCL timing is measured with the input filters enabled. Switching off the input filters improves the transfer rate; however, it has a negative effect on the EMC behavior of the device.

<sup>3</sup> Same timing should be expected when powering the device after  $V_{DD} = 2.7$  V.

<sup>4</sup> Time to exit power-down to normal mode of operation.

Figure 4. I<sup>2</sup>C Serial Interface Timing Diagram

# **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25^{\circ}C$ , unless otherwise noted.

#### Table 6.

| Parameter                     | Rating                                                           |

|-------------------------------|------------------------------------------------------------------|

| V <sub>DD</sub> to GND        | -0.3 V to +7 V                                                   |

| VLOGIC to GND                 | –0.3 V to +7 V                                                   |

| Vout to GND                   | -0.3 V to V <sub>DD</sub> + 0.3 V or +7 V<br>(whichever is less) |

| VREF to GND                   | -0.3 V to V <sub>DD</sub> + 0.3 V or +7 V<br>(whichever is less) |

| Digital Input Voltage to GND  | -0.3 V to V <sub>DD</sub> + 0.3 V or +7 V<br>(whichever is less) |

| Operating Temperature Range   |                                                                  |

| Industrial                    | -40°C to +105°C                                                  |

| Storage Temperature Range     | –65°C to +150°C                                                  |

| Junction Temperature (TJ max) | 135℃                                                             |

| Power Dissipation             | $(T_J max - T_A)/\theta_{JA}$                                    |

| ESD <sup>1</sup>              | 4 kV                                                             |

| FICDM <sup>2</sup>            | 1.25 kV                                                          |

### THERMAL RESISTANCE

$\theta_{JA}$  is defined by the JEDEC JESD51 standard, and the value is dependent on the test board and test environment.

### Table 7. Thermal Resistance

| Package Type | Αιθ              | θıc              | Unit |

|--------------|------------------|------------------|------|

| 10-Lead MSOP | 135 <sup>1</sup> | N/A <sup>2</sup> | °C/W |

<sup>1</sup> JEDEC 2S2P test board, still air (0 m/sec airflow). <sup>2</sup> N/A means not applicable.

### **ESD CAUTION**

**ESD (electrostatic discharge) sensitive device.** Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

<sup>1</sup> Human body model (HBM) classification.

<sup>2</sup> Field-induced charged-device model classification.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

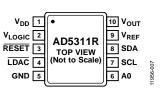

# **PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS**

Figure 6. Pin Configuration, AD5310R

Table 8. AD5310R Pin Function Descriptions

| Pin No. | Mnemonic         | Description                                                                                                                                                                                                  |

|---------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | V <sub>DD</sub>  | Power Supply Input. This device can be operated from 2.7 V to 5.5 V. Decouple the supply to GND.                                                                                                             |

| 2       | VLOGIC           | Digital Power Supply. Voltage ranges from 1.62 V to 5.5 V. Decouple the supply to GND.                                                                                                                       |

| 3       | RESET            | Hardware Reset Pin. The RESET input is low level sensitive. When RESET is low, the device is reset and                                                                                                       |

|         |                  | external pins are ignored. The input and DAC registers are loaded with zero-scale values, and the control register is loaded with default values. This pin can be tied to $V_{LOGIC}$ if not used.           |

| 4       | LDAC             | Load DAC. LDAC can be operated in asynchronous mode (see Figure 3). Pulsing this pin low allows the                                                                                                          |

|         |                  | DAC register to be updated if the input register has new data. This pin can be tied permanently low; in this case, the DAC register is automatically updated when new data is written to the input register. |

| 5       | GND              | Ground Reference.                                                                                                                                                                                            |

| 6       | SCLK             | Serial Clock Input. Data is clocked into the input shift register on the falling edge of the serial clock input.<br>Data is transferred at rates up to 50 MHz.                                               |

| 7       | SYNC             | Synchronization Data Input. When SYNC goes low, it enables the SCLK and SDI buffers and the input shift register.                                                                                            |

| 8       | SDI              | Serial Data Input. Data is sampled on the falling edge of the SCLK.                                                                                                                                          |

| 9       | Vref             | Reference Input/Output. By default, this pin is a reference output. It is recommended that this pin be decoupled with a 10 nF capacitor to GND.                                                              |

| 10      | V <sub>OUT</sub> | Analog Output Voltage from the DAC. The output amplifier has rail-to-rail operation.                                                                                                                         |

Figure 7. Pin Configuration, AD5311R

| Pin No. | Mnemonic         | Description                                                                                                                                                                                                                                                                |

|---------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | V <sub>DD</sub>  | Power Supply Input. These devices can be operated from 2.7 V to 5.5 V. Decouple the supply to GND.                                                                                                                                                                         |

| 2       | VLOGIC           | Digital Power Supply. Voltage ranges from 1.62 V to 5.5 V. Decouple the supply to GND.                                                                                                                                                                                     |

| 3       | RESET            | Hardware Reset Pin. The RESET input is low level sensitive. When RESET is low, the device is reset and external                                                                                                                                                            |

|         |                  | pins are ignored. The input and DAC registers are loaded with zero-scale value, and the control register is loaded with default values. This pin can be tied to $V_{LOGIC}$ if not used.                                                                                   |

| 4       | LDAC             | Load DAC. Transfers the contents of the input register to the DAC register. It can be operated in two modes, asynchronously and synchronously, as shown in Figure 5. This pin can be tied permanently low; the DAC updates when new data is written to the input register. |

| 5       | GND              | Ground Reference.                                                                                                                                                                                                                                                          |

| 6       | A0               | Programmable Address (ADDR1) for Multiple Package Decoding. The address pin can be updated on-the-fly.                                                                                                                                                                     |

| 7       | SCL              | Serial Clock Line.                                                                                                                                                                                                                                                         |

| 8       | SDA              | Serial Data Input/Output.                                                                                                                                                                                                                                                  |

| 9       | V <sub>REF</sub> | Reference Input/Output. The default for this pin is as a reference output. It is recommended to decouple this pin with a 10 nF capacitor to GND.                                                                                                                           |

| 10      | VOUT             | Analog Output Voltage from the DAC. The output amplifier has rail-to-rail operation.                                                                                                                                                                                       |

# **TYPICAL PERFORMANCE CHARACTERISTICS**

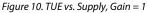

Figure 13. Supply Current vs. Temperature

**Data Sheet**

1956-018

11 956-021

Figure 19. Internal Reference Voltage vs. Supply Voltage

# **Data Sheet**

# AD5310R/AD5311R

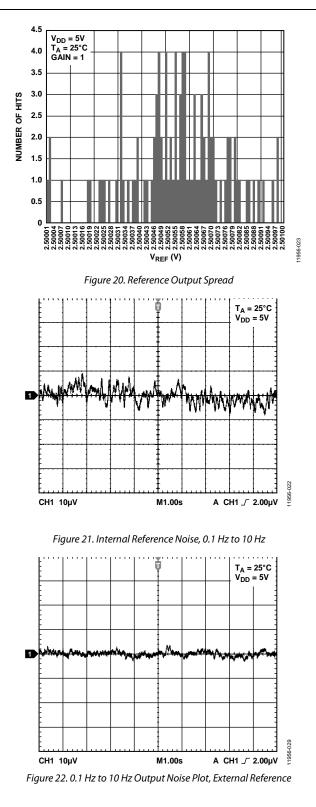

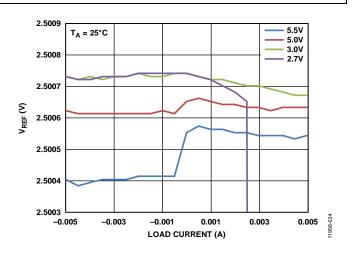

Figure 23. Internal Reference Voltage vs. Load Current

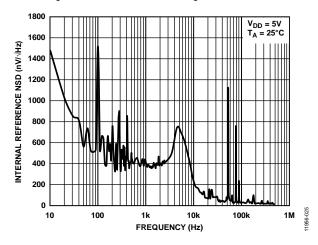

Figure 24. Internal Reference Noise Spectral Density vs. Frequency

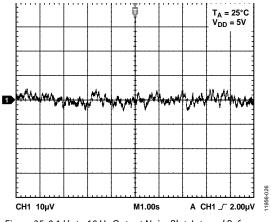

Figure 25. 0.1 Hz to 10 Hz Output Noise Plot, Internal Reference

# Data Sheet

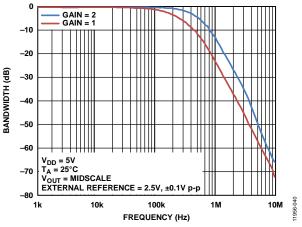

#### 0.0015 GAIN = 1 GAIN = 2 $$\label{eq:V_DD} \begin{split} &V_{DD} = 5V\\ &T_A = 25^\circ C\\ &REFERENCE = 2.5V\\ &CODE = 0x7FFF TO 0x8000 \end{split}$$ 0.0010 0.0005 0 V<sub>oUT</sub> (V) -0.0005 -0.0010 -0.0015 -0.0020 -0.0025 11956-036 0 2 6 7 3 4 5 1 TIME (µs)

AD5310R/AD5311R

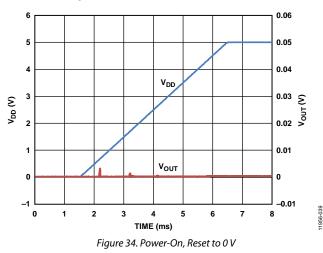

Figure 35. Multiplying Bandwidth, External Reference 2.5 V  $\pm$  0.1 V p-p, 10 kHz to 10 MHz

Figure 36. Exiting Power-Down to Midscale

## TERMINOLOGY

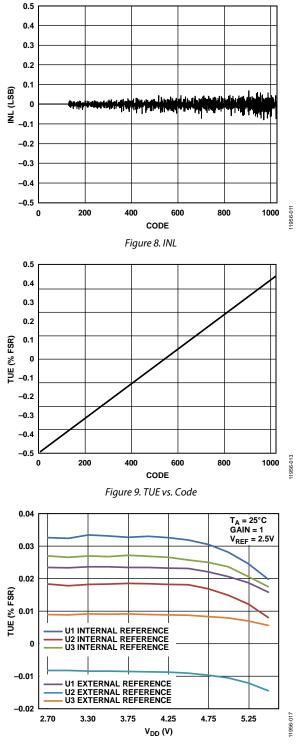

### Relative Accuracy or Integral Nonlinearity (INL)

For the DAC, relative accuracy (or integral nonlinearity) is a measurement of the maximum deviation, in LSBs, from a straight line passing through the endpoints of the DAC transfer function. See Figure 8 for a typical INL vs. code plot.

### Differential Nonlinearity (DNL)

Differential nonlinearity is the difference between the measured change and the ideal 1 LSB change between any two adjacent codes. A specified differential nonlinearity of  $\pm 1$  LSB maximum ensures monotonicity. This DAC is guaranteed monotonic by design. See Figure 11 for a typical DNL vs. code plot.

### Zero Code Error

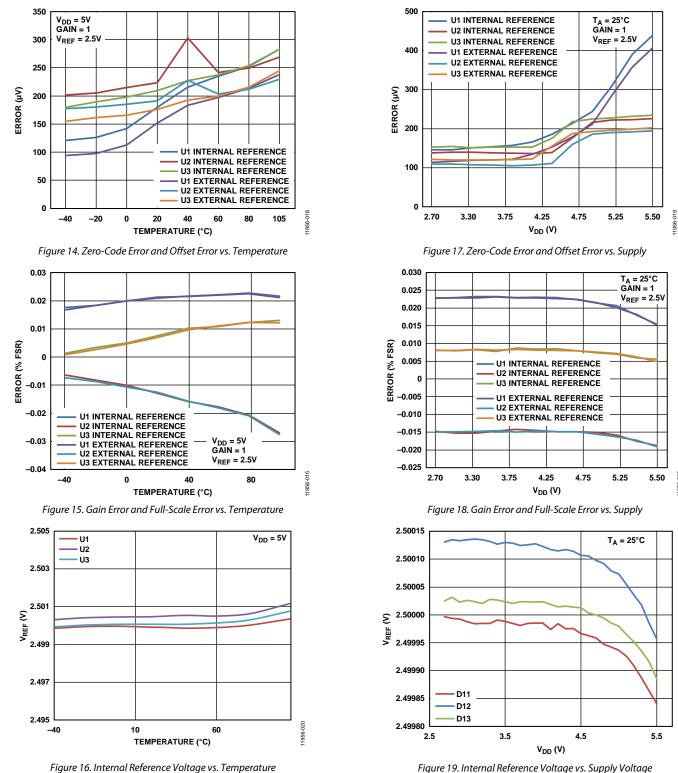

Zero code error is a measurement of the output error when zero code (0x000) is loaded to the DAC register. Ideally, the output should be 0 V. The zero code error of the input is always positive; the output of the DAC cannot fall below 0 V due to a combination of the offset errors in the DAC and in the output amplifier. Zero code error is expressed in mV. See Figure 14 and Figure 17 for plots of zero code error.

### Full-Scale Error

Full-scale error is a measurement of the output error when fullscale code (0x3FF) is loaded to the DAC register. The recommended output is  $V_{REF} - 1$  LSB or  $|2 \times V_{REF}| - 1$  LSB. Full-scale error is expressed in percent of full-scale range (% of FSR). See Figure 15 and Figure 18 for plots of full-scale error.

### **Gain Error**

Gain error is a measurement of the span error of the DAC. It is the deviation in slope of the DAC transfer characteristic from the ideal, expressed as % of FSR.

### Zero-Code Error Drift

Zero-code error drift is a measurement of the change in zerocode error with a change in temperature. It is expressed in  $\mu V/^{\circ}C$ .

### **Gain Temperature Coefficient**

Gain temperature coefficient is a measurement of the change in gain error with changes in temperature. It is expressed in ppm of FSR/°C.

### **Offset Error**

Offset error is a measure of the difference between  $V_{OUT}$  (actual) and  $V_{OUT}$ (ideal) expressed in mV in the linear region of the transfer function. Offset error is measured with Code 4 loaded in the DAC register. It can be negative or positive.

### DC Power Supply Rejection Ratio (PSRR)

PSRR indicates how the output of the DAC is affected by changes in the supply voltage. PSRR is the ratio of the change in  $V_{OUT}$  to a change in  $V_{DD}$  for full-scale output of the DAC. It is measured in dB.  $V_{REF}$  is held at 2 V, and  $V_{DD}$  varies by ±10%.

### **Output Voltage Settling Time**

Output voltage settling time is the amount of time it takes for the output of a DAC to settle to a specified level for a  $\frac{1}{4}$  to  $\frac{3}{4}$  full-scale input change.

### Digital-to-Analog Glitch Impulse

Digital-to-analog glitch impulse is the impulse injected into the analog output when the input code in the DAC register changes state. It is normally specified as the area of the glitch in nV-sec, and is measured when the digital input code is changed by 1 LSB at a major carry transition (0x1FF to 0x200).

### **Digital Feedthrough**

Digital feedthrough is a measure of the impulse injected into the analog output of the DAC from the digital inputs of the DAC, but it is measured when the DAC output is not updated. Digital feedthrough is specified in nV-sec and is measured with a full-scale code change on the data bus, that is, from all 0s to all 1s and vice versa.

### **Output Noise Spectral Density**

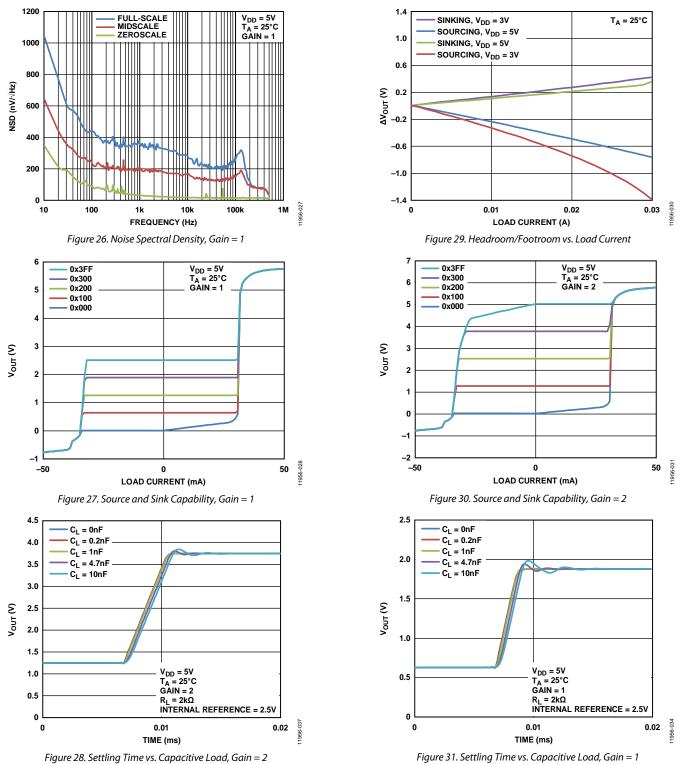

Noise spectral density is a measurement of the internally generated random noise. Random noise is characterized as a spectral density ( $nV/\sqrt{Hz}$ ). It is measured by loading the DAC to midscale and measuring noise at the output. It is measured in  $nV/\sqrt{Hz}$ . See Figure 22, Figure 25, and Figure 26 for plots of noise spectral density. See Figure 21 and Figure 24 for plots of the noise spectral density for the internal reference.

### **Multiplying Bandwidth**

The amplifiers within the DAC have a finite bandwidth. The multiplying bandwidth is a measure of this. A sine wave on the reference (with full-scale code loaded to the DAC) appears on the output. The multiplying bandwidth is the frequency at which the output amplitude falls to 3 dB below the input.

### **Total Harmonic Distortion (THD)**

THD is the difference between an ideal sine wave and its attenuated version using the DAC. The sine wave is used as the reference for the DAC, and the THD is a measurement of the harmonics present on the DAC output. It is measured in dB.

### Voltage Reference Temperature Coefficient (TC)

Voltage reference TC is a measurement of the change in the reference output voltage with a change in temperature. The reference TC is calculated using the box method, which defines the TC as the maximum change in the reference output over a given temperature range expressed in ppm/°C, as follows:

$$TC = \left[\frac{V_{REFmax} - V_{REFmin}}{V_{REFnom} \times TempRange}\right] \times 10^{6}$$

where:

$V_{REFmax}$  is the maximum reference output measured over the total temperature range.

$V_{REFmin}$  is the minimum reference output measured over the total temperature range.

$V_{REFnom}$  is the nominal reference output voltage, 2.5 V.

*TempRange* is the specified temperature range, -40°C to +105°C.

## THEORY OF OPERATION DIGITAL-TO-ANALOG CONVERTER

The AD5310R/AD5311R are single-channel, 10-bit, serial input, voltage output DACs with a 2.5 V internal reference. The devices operate from supply voltages of 2.7 V to 5.5 V. Data is written to the AD5310R/AD5311R in a 24-bit word format via an I<sup>2</sup>C serial interface or SPI interface.

The AD5310R/AD5311R incorporate a power-on reset circuit that ensures that the DAC output powers up to a zero scale. The devices also have a software power-down mode that reduces the typical current consumption to 2  $\mu$ A maximum in specs.

## TRANSFER FUNCTION

The internal reference is on by default. The input coding to the DAC is straight binary, and the ideal output voltage is given by the following equations:

For the AD5310R,

$$V_{OUT}(D) = Gain \times V_{REF} \times \left[\frac{D}{1024}\right]$$

For the AD5311R,

$$V_{OUT}(D) = Gain \times V_{REF} \times \left[\frac{D}{1024}\right]$$

where:

*D* is the decimal equivalent of the binary code that is loaded to the DAC register.

*Gain* is the gain of the output amplifier and is set to  $\times 1$  by default. The gain can also be set to 1 or 2 using the gain select bit in the control register.

## DAC ARCHITECTURE

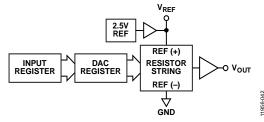

The DAC architecture implements a segmented string DAC with an internal output buffer. Figure 37 shows the internal block diagram.

Figure 37. DAC Channel Architecture Block Diagram

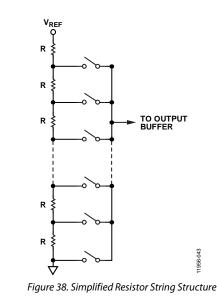

The simplified segmented resistor string DAC structure is shown in Figure 38. The code loaded to the DAC register determines the switch on the string that is connected to the output buffer.

Because each resistance in the string has the same value, R, the string DAC is guaranteed monotonic.

### Internal Reference

The AD5310R/AD5311R has a 2.5 V, 2 ppm/°C reference that provides a full-scale output of 2.5 V or 5 V, depending on the state of the gain bit, see Table 15.

The AD5310R/AD5311R on-chip reference is on at power-up but can be disabled via a write to the control register.

The internal reference is available at the  $V_{REF}$  pin. It is internally buffered and capable of driving external loads of up to 50 mA.

## **External Reference**

The  $V_{REF}$  pin can be configured as an input pin, allowing the use of an external reference if the application requires it. The default condition of the on-chip reference is on at power-up.

Before connecting an external buffer to the pin, a write to the control register is required to disable the internal reference, see the REF Bit section.

### **Output Buffer**

The output buffer is designed as an input/output rail-to-rail buffer, which gives a maximum output voltage range of up to 0 V to  $V_{DD}$ . The gain bit sets the segmented string DAC gain to  $\times 1$  or  $\times 2$  as shown in Table 15. The output buffer voltage is determined by  $V_{REF}$ , the gain bit, and the offset and gain errors.

The output buffer can drive 10nF capacitance with a 2 k $\Omega$  resistor in parallel, as shown in Figure 34. If a higher capacitance load is required, a shunt resistor must be connected between the output amplifier and the load. The slew rate is 0.7 V/µs with a ¼ to ¾ scale settling time of 5 µs.

## SERIAL INTERFACE **AD5310R SPI SERIAL DATA INTERFACE**

The AD5310R has a 3-wire serial interface (SYNC, SCLK, and SDI) that is compatible with serial peripheral interface (SPI), Mode 1 and Mode 2, and with completely synchronous interfaces such as SPORT. See Figure 3 for a timing diagram of a typical write sequence. See the AN-1248 Application Note for more information about the SPI interface.

The write sequence begins by bringing the SYNC line low. Data from the SDI line is sampled into the input shift register on the falling edge of SCLK. The SYNC pin must be held low until the complete data-word (16 bits) is loaded from the SDI pin, as shown in Figure 3. When SYNC returns high, the serial dataword is decoded according to the instructions in Table 10.

SYNC must be brought high for a minimum of 20 ns before the next write sequence such that a falling edge of  $\overline{\text{SYNC}}$  can initiate the next write sequence.

If SYNC is brought high after 16 falling clock edges occur, it is interpreted as a valid write and the first 16 bits are loaded to the input shift register.

If SYNC is brought high before 16 falling clock edges, the serial write is ignored and the write sequence is considered invalid.

To minimize power consumption, it is recommended that all serial interface pins be operated close to the supply rails.

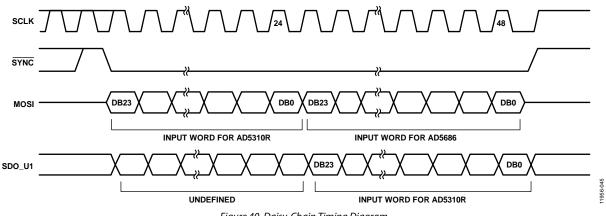

## **DAISY-CHAIN MODE COMPATIBILITY**

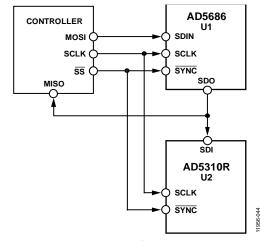

The AD5310R can be operated in a daisy-chain configuration, but cannot forward data because there is no SDO pin. To connect the AD5310R in daisy-chain mode, it is possible to connect only one device per chain, and the AD5310R should be connected the last device.

Daisy-chaining minimizes the number of pins required from the controlling IC. As shown in Figure 39, the SDO pin of one package must be tied to the SDI pin of the next package. The clock period may need to be increased because of the propagation delay of the line between subsequent devices. By default, the daisy-chain configuration mode is disabled. To enable it, the DCEN bit must be set in the control register, as shown in Table 11.

When the DCEN bit is enabled in the control register, the AD5310R accepts as a valid frame any data-word longer than 24 bits, and decodes the last 24 bits received, with the last 10 LSB as do not care bits.

Figure 39. Daisy-Chain Connection

Figure 40. Daisy-Chain Timing Diagram

| Bit |    | mand<br>I 5:DB |    | Data Bits [DB11:DB0] <sup>1</sup> |      |     |     |     |     |     |     |     |     |           |                                         |

|-----|----|----------------|----|-----------------------------------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----------|-----------------------------------------|

| С3  | C2 | C1             | С0 | DB11                              | DB10 | DB9 | DB8 | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | [DB1:DB0] | Operation                               |

| 0   | 0  | 0              | 0  | Х                                 | Х    | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | XX        | NOP. Do nothing.                        |

| 0   | 0  | 0              | 1  | DB9                               | DB8  | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 | XX        | Write input register.                   |

| 0   | 0  | 1              | 0  | Х                                 | Х    | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | XX        | Update DAC register<br>(LDAC software). |

| 0   | 0  | 1              | 1  | DB9                               | DB8  | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 | XX        | Write DAC and input register.           |

| 0   | 1  | 0              | 0  | DB9                               | DB8  | DB7 | DB6 | DB5 | DB4 | 0   | 0   | 0   | 0   | 00        | Write control register.                 |

#### Table 10. SPI Command Operation

<sup>1</sup> X = don't care.

#### Table 11. Control Register Bits

| DB11  | DB10 | DB9 | DB8 | DB7  | DB6  |

|-------|------|-----|-----|------|------|

| RESET | PD1  | PDO | REF | GAIN | DCEN |

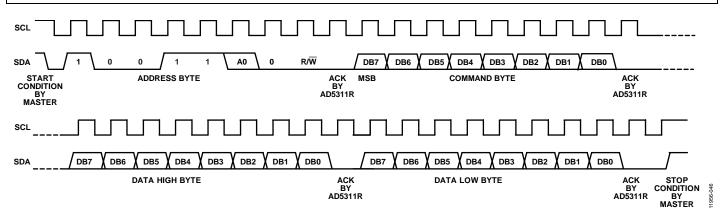

### AD5311R I<sup>2</sup>C SERIAL DATA INTERFACE

The AD5311R has a 2-wire, I<sup>2</sup>C-compatible serial interface. These devices can be connected to an I<sup>2</sup>C bus as a slave device, under the control of a master device. See Figure 4 for a timing diagram of a typical write sequence.

The AD5311R supports standard (100 kHz) and fast (400 kHz) data transfer modes. Support is not provided for 10-bit addressing and general call addressing.

The 2-wire serial bus protocol operates as follows:

- 1. The master initiates a data transfer by establishing a start condition when a high to low transition on the SDA line occurs while SCL is high. The following byte is the address byte, which consists of the 7-bit slave address. The slave address corresponding to the transmitted address responds by pulling SDA low during the ninth clock pulse (this is called the acknowledge bit). At this stage, all other devices on the bus remain idle while the selected device waits for data to be written to, or read from, its shift register.

- 2. Data is transmitted over the serial bus in sequences of nine clock pulses (eight data bits followed by an acknowledge bit). The transitions on the SDA line must occur during the low period of SCL and remain stable during the high period of SCL.

- 3. When all the data bits have been read or written, a stop condition is established. In write mode, the master pulls the SDA line high during the tenth clock pulse to establish a stop condition. In read mode, the master issues a no acknowledge for the ninth clock pulse (that is, the SDA line remains high). The master then brings the SDA line low before the tenth clock pulse, and then high during the tenth clock pulse to establish a stop condition.

### I<sup>2</sup>C Address

The AD5311R has a 7-bit slave address. The five MSBs are 10011. The second to the last bit, set by the state of the A0 address pin and the LSB, is 0. The ability to make hardwired changes to A0 lets the user have two of these devices on one bus, as outlined in Table 12. Additionally, the pin can be updated before starting the transmission, allowing multiples devices in the same bus by connecting the pin to a GPIO or a multiplexer.

#### Table 12. Device Address Selection

| A0 Pin Connection | A0 Bit | I <sup>2</sup> C Address |

|-------------------|--------|--------------------------|

| GND               | 0      | 1001100                  |

| VLOGIC            | 1      | 1001110                  |

### **I<sup>2</sup>C Write Operation**

When writing to the AD5311R, the user must begin with a start condition followed by an address byte (R/W= 0), after which the DAC acknowledges that it is prepared to receive data by pulling SDA low, as shown in Figure 41. The AD5311R requires a command byte that controls various DAC functions (see Table 13) and two bytes of data for the DAC. All these data bytes are acknowledged by the AD5311R. A stop condition follows. The write sequence is shown in Figure 41.

Figure 41. I<sup>2</sup>C Write Operation

### Table 13. I<sup>2</sup>C Command Table<sup>1</sup>

|     | (   | Comma | nd Byte |           | Data Hi   | igh Byte  | Data Low Byte |           |                                      |

|-----|-----|-------|---------|-----------|-----------|-----------|---------------|-----------|--------------------------------------|

| DB7 | DB6 | DB5   | DB4     | [DB3:DB0] | [DB7:DB3] | [DB2:DB0] | [DB7:DB6]     | [DB5:DB0] | Operation                            |

| 0   | 0   | 0     | 0       | XXXX      | XXXXX     | XXX       | XX            | XXXXX     | NOP: do nothing.                     |

| 0   | 0   | 0     | 1       | XXXX      | DB9:DB5   | DB:DB2    | DB1:DB0       | XXXXX     | Write input register.                |

| 0   | 0   | 1     | 0       | XXXX      | XXXXX     | XXX       | XX            | XXXXX     | Update DAC register (LDAC software). |

| 0   | 0   | 1     | 1       | XXXX      | DB9:DB5   | DB4:DB2   | DB1:DB0       | XXXXX     | Write DAC and input registers.       |

| 0   | 1   | 0     | 0       | XXXX      | DB9:DB5   | 000       | 00            | 00000     | Write control register.              |

$^{1}$  X = don't care.

### Table 14. Control Register Bits

| DB9   | DB8 | DB7 | DB6 | DB5  |

|-------|-----|-----|-----|------|

| RESET | PD1 | PDO | REF | GAIN |

## COMMANDS

### Write Input Register

The input register allows the preloading of a new value for the DAC register. The transfer from the input register to the DAC register can be triggered by hardware, by the  $\overline{\text{LDAC}}$  pin, or by software using Command 2.

If new data is loaded into the DAC register, the DAC register automatically overwrites the input register.

### Update DAC Register

This command transfers the contents of the input register to the DAC register and, consequently, the  $V_{OUT}$  pin is updated. The data contained in the serial write is ignored.

This operation is equivalent to a software  $\overline{\text{LDAC}}$ .

### Write DAC Register

This command updates the DAC register on completion of the write operation. The input register is refreshed automatically with the DAC register value.

### Write Control Register

The write control register command is used to set the powerdown and gain functions. It is also used to enable/disable the internal reference and perform a software reset. See Table 14 for the control register bits.

### Gain Bit

The gain bit selects the gain of the output amplifier. Table 15 shows how the output voltage range corresponds to the state of the gain bit.

### Table 15. Gain Bit

| 0 0 V to $V_{REF}$ (default)             | Gain | Output Voltage Range               |

|------------------------------------------|------|------------------------------------|

|                                          | 0    | 0 V to V <sub>REF</sub> (default)  |

| $1 \qquad 0 \lor to 2 \times \lor_{REF}$ | 1    | 0 V to 2 $\times$ V <sub>REF</sub> |

### **REF Bit**

The on-chip reference is on at power-up by default. This reference can be turned on or off by setting a software programmable bit, DB6, in the control register. Table 16 shows how the state of the bit corresponds to the mode of operation.

To reduce power consumption, it is recommended that the internal reference be disabled if the device is placed in power-down mode.

### Table 16. REF Bit

| REF | Reference Function          |

|-----|-----------------------------|

| 0   | Reference enabled (default) |

| 1   | Reference disabled          |

### PD0 and PD1 Bits

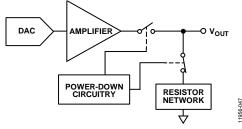

The AD5310R/AD5311R provide two separate modes of operation that are accessed by writing to the write control register.

In normal mode, the output buffer is directly connected to the  $V_{\mbox{\scriptsize OUT}}$  pin.

In power-down mode, the output buffer is internally disabled and the  $V_{\text{OUT}}$  pin output impedance can be selected to a well-known value, as shown in Table 17.

#### Table 17. Operation Modes

| Operating Mode               | PD1 | PD0 |

|------------------------------|-----|-----|

| Normal Mode                  | 0   | 0   |

| Power-Down Modes             |     |     |

| 1 kΩ Output Impedance        | 0   | 1   |

| 100 kΩ Output Impedance      | 1   | 0   |

| Three-State Output Impedance | 1   | 1   |

In power-down mode, the part disables the output buffer, but does not disable the internal reference. To achieve maximum power saving, it is recommend that the REF bit be disabled.

Disabling both the internal reference and the output buffer results in the supply current falling to 2  $\mu A$  at 5 V.

The output stage is illustrated in Figure 42.

Figure 42. Output Stage During Power-Down

The output amplifier is shut down when the power-down mode is activated. However, unless the internal reference is powered down, the bias generator, reference, and resistor string remain on. The supply current falls to 2  $\mu$ A at 5 V. The contents of the DAC register are unaffected in power-down mode, and the DAC register can be updated while the device is in power-down mode. The time that is required to exit power-down is typically 4  $\mu$ s for  $V_{DD} = 5$  V, or 600  $\mu$ s if the reference is disabled.

### **Reset Bit**

The write control register of the AD5310R/AD5311R contains a software reset bits that resets the DAC registers to zero scale and resets the input, the DAC, and the control registers to their default values. A software reset is initiated by setting the reset bit in the control register to 1. When the software reset is completed, the reset bit is cleared to 0 automatically.

## LOAD DAC (HARDWARE LDAC PIN)

The AD5310R/AD5311R have a double buffered interface consisting of an input register and a DAC register. The LDAC pin transfers data from the input register to the DAC register, and the output is updated.

### Synchronous DAC Update (AD5311R Only)

If the  $\overline{\text{LDAC}}$  pin is held low while the input register is written, the DAC register, input register, and output are updated on the last SCL falling edge before the ACK bit, as shown in Figure 5.

### Asynchronous DAC Update

$\overline{\text{LDAC}}$  is held high while data is transmitted to the device. The DAC output is updated by taking  $\overline{\text{LDAC}}$  low after the stop condition is generated. The output DAC is updated on the falling edge of the  $\overline{\text{LDAC}}$  pin.

If  $\overline{\text{LDAC}}$  is pulsed while the device is accessed, the pulse is ignored.

## HARDWARE RESET

RESET is an active low signal that resets the DAC output to zero scale and sets the input, DAC, and control registers to their default values. It is necessary to keep RESET low for 75 ns to complete the operation. When the RESET signal returns high, the output remains at zero scale until a new value is programmed. While the RESET pin is low, the AD5310R/AD5311R ignore any new command.

If  $\overline{\text{RESET}}$  is held low at power-up, the internal reference is not initialized correctly until the  $\overline{\text{RESET}}$  pin is released.

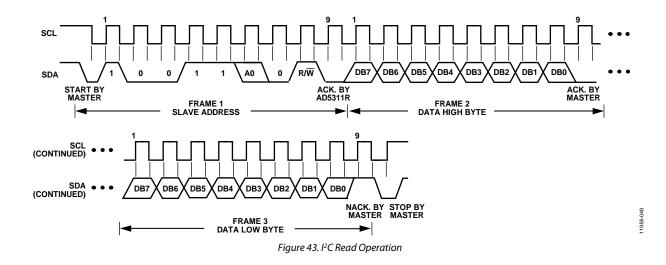

## AD5311R, I<sup>2</sup>C READ OPERATION

When reading the input register back from the AD5311R DAC, the user begins with an address byte  $(R/\overline{W} = 1)$ , after which the DAC acknowledges that it is prepared to receive data by pulling SDA low. Two bytes of data containing the contents of the input register are then read from the DAC, as shown in Figure 43. A NACK condition from the master followed by a stop condition completes the read sequence.

### THERMAL HYSTERESIS

Thermal hysteresis is the voltage difference induced on the reference voltage by sweeping the temperature from ambient to cold, to hot, and then back to ambient.

The thermal hysteresis data is shown in Figure 44. It is measured by sweeping the temperature from ambient  $+25^{\circ}$ C to  $-40^{\circ}$ C, then to  $+105^{\circ}$ C, and finally returning to ambient  $+25^{\circ}$ C. The V<sub>REF</sub> delta is next measured between the two ambient measurements and shown in the solid lines in Figure 44. The same temperature sweep and measurements are immediately repeated and the results are shown in the dashed lines in Figure 44.

### **POWER-UP SEQUENCE**

Because diodes limit the voltage compliance at the digital and analog pins, it is important to power GND first before applying any voltage to  $V_{DD}$ ,  $V_{OUT}$ , and  $V_{LOGIC}$ . Otherwise, the diode is forward-biased such that  $V_{DD}$  is powered unintentionally. The ideal power-up sequence is GND,  $V_{DD}$ ,  $V_{LOGIC}$ ,  $V_{REF}$ , followed by the digital inputs.

## LAYOUT GUIDELINES

In any circuit where accuracy is important, careful consideration of the power supply and ground return layout helps to ensure the rated performance. The PCB on which the AD5310R/AD5311R are mounted should be designed such that the AD5310R/AD5311Rare placed on the analog plane.

Ensure that the AD5310R/AD5311R have ample supply bypassing of 10  $\mu$ F in parallel with 0.1  $\mu$ F on each supply, located as close to the package as possible, ideally right up against the device. The 10  $\mu$ F capacitors are the tantalum bead type. Use a 0.1  $\mu$ F capacitor with low effective series resistance (ESR) and low effective series inductance (ESI), such as the common ceramic types, which provide a low impedance path to ground at high frequencies to handle transient currents due to internal logic switching.

## **OUTLINE DIMENSIONS**

### **ORDERING GUIDE**

| Model <sup>1</sup> | <b>Resolution (Bits)</b> | Temperature Range | Package Description | Package Option | Branding |

|--------------------|--------------------------|-------------------|---------------------|----------------|----------|

| AD5310RBRMZ        | 10                       | -40°C to +105°C   | 10-Lead MSOP        | RM-10          | DJZ      |

| AD5310RBRMZ-RL7    | 10                       | -40°C to +105°C   | 10-Lead MSOP        | RM-10          | DJZ      |

| AD5311RBRMZ        | 10                       | -40°C to +105°C   | 10-Lead MSOP        | RM-10          | XLD      |

| AD5311RBRMZ-RL7    | 10                       | -40°C to +105°C   | 10-Lead MSOP        | RM-10          | XLD      |

$^{1}$  Z = RoHS Compliant Part.

I<sup>2</sup>C refers to a communications protocol originally developed by Philips Semiconductors (now NXP Semiconductors).

©2014–2017 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. D11956-0-2/17(B)

www.analog.com

Rev. B | Page 24 of 24

#### ООО "ЛайфЭлектроникс"

ИНН 7805602321 КПП 780501001 Р/С 40702810122510004610 ФАКБ "АБСОЛЮТ БАНК" (ЗАО) в г.Санкт-Петербурге К/С 3010181090000000703 БИК 044030703

Компания «Life Electronics» занимается поставками электронных компонентов импортного и отечественного производства от производителей и со складов крупных дистрибьюторов Европы, Америки и Азии.

С конца 2013 года компания активно расширяет линейку поставок компонентов по направлению коаксиальный кабель, кварцевые генераторы и конденсаторы (керамические, пленочные, электролитические), за счёт заключения дистрибьюторских договоров

Мы предлагаем:

- Конкурентоспособные цены и скидки постоянным клиентам.

- Специальные условия для постоянных клиентов.

- Подбор аналогов.

- Поставку компонентов в любых объемах, удовлетворяющих вашим потребностям.

- Приемлемые сроки поставки, возможна ускоренная поставка.

- Доставку товара в любую точку России и стран СНГ.

- Комплексную поставку.

- Работу по проектам и поставку образцов.

- Формирование склада под заказчика.

- Сертификаты соответствия на поставляемую продукцию (по желанию клиента).

- Тестирование поставляемой продукции.

- Поставку компонентов, требующих военную и космическую приемку.

- Входной контроль качества.

- Наличие сертификата ISO.

В составе нашей компании организован Конструкторский отдел, призванный помогать разработчикам, и инженерам.

Конструкторский отдел помогает осуществить:

- Регистрацию проекта у производителя компонентов.

- Техническую поддержку проекта.

- Защиту от снятия компонента с производства.

- Оценку стоимости проекта по компонентам.

- Изготовление тестовой платы монтаж и пусконаладочные работы.

Тел: +7 (812) 336 43 04 (многоканальный) Email: org@lifeelectronics.ru

### www.lifeelectronics.ru