## 4.5V to 60V, 3A Current-Limiter with OV, UV and Reverse Protection

#### **General Description**

The Olympus series of ICs is the industry's smallest and most robust integrated system protection solution. The MAX17613A/MAX17613B/MAX17613C adjustable overvoltage and overcurrent protection devices are ideal to protect systems against positive and negative input voltage faults up to +60V and -65V, and feature low  $130 m\Omega$  (typ)  $R_{ON}$  FETs.

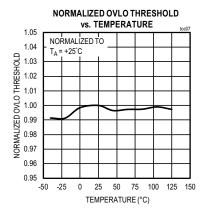

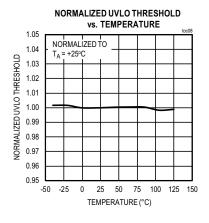

The adjustable input overvoltage protection range is 5.5V to 60V and the adjustable input undervoltage protection range is 4.5V to 59V. The input overvoltage-lockout (OVLO) and undervoltage-lockout (UVLO) thresholds are set using external resistors. Additionally, the devices offer an internal input undervoltage threshold at 4.2V (typ).

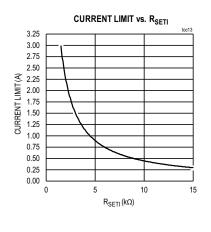

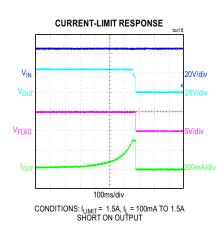

The devices feature programmable current-limit protection up to 3A; hence, controlling the inrush current at startup while charging high capacitance at the output. The current-limit threshold is programmed by connecting a resistor from the SETI pin to GND. When the device current reaches the programmed threshold, the device prevents further increases in current by modulating the FET resistance. The devices can be programmed to behave in three different ways under current-limit condition: autoretry, continuous, or latchoff modes. The voltage appearing on the SETI pin is proportional to the instantaneous current flowing through the device and can be read by an ADC.

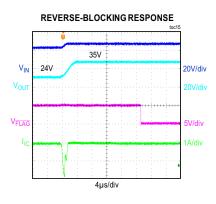

MAX17613A and MAX17613C block current flowing in the reverse direction (i.e., from OUT to IN) whereas MAX17613B allows current flow in the reverse direction. The devices feature thermal shutdown protection against excessive power dissipation.

The devices are available in a small, 20-pin (4mm x 4mm) TQFN-EP package and operate over the -40°C to +125°C extended temperature range.

Ordering Information appears at end of data sheet.

#### **Benefits and Features**

- Robust Protection Reduces System Downtime

- Wide Input-Supply Range of +4.5V to +60V

- Hot Plug-in Tolerant without TVS up to 35V Input Supply

- · Negative Input Tolerance up to -65V

- Low R<sub>ON</sub> 130mΩ (typ)

- · Reverse Current-Blocking Protection

- Thermal Overload Protection

- Programmable Startup Blanking Time

- Extended -40°C to +125°C Temperature Range

- MAX17613A Enables OV, UV, and Reverse Voltage Protection

- MAX17613B Enables OV and UV Protection

- MAX17613C Enables Reverse Voltage Protection

- Flexible Design Options Enable Reuse and Less Requalification

- · Adjustable OVLO and UVLO Thresholds

- Programmable Forward Current Limit: 0.15A to 3A with ±3.5% Accuracy

- Accuracy Over Full Temperature Range

- Programmable Overcurrent Fault Response: Autoretry, Continuous, and Latchoff Modes

- Smooth Current Transitions

- Saves Board Space and Reduces External BOM Count

- 20-Pin, 4mm x 4mm, TQFN-EP Package Integrated FETs

#### **Applications**

- Sensor Systems

- Condition Monitoring

- Factory Sensors

- Process Instrumentation

- Weighing and Batching Systems

- Industrial Applications such as PLC, Control Network Modules, Battery-Operated Modules

# 4.5V to 60V, 3A Current-Limiter with OV, UV and Reverse Protection

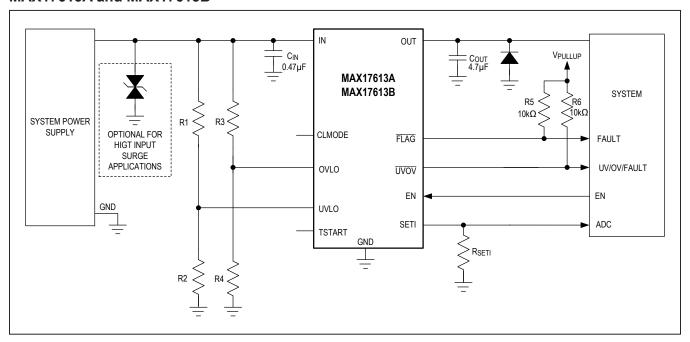

### **Typical Operating Circuit**

#### **MAX17613A and MAX17613B**

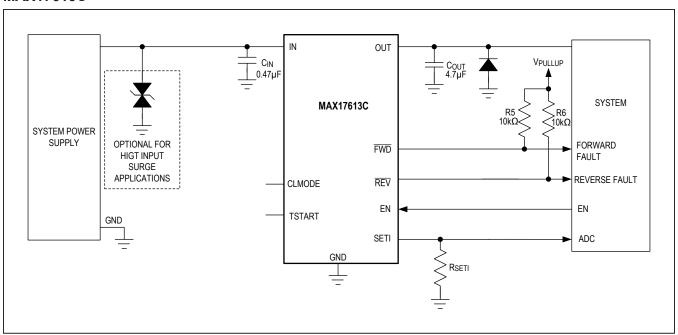

#### MAX17613C

## 4.5V to 60V, 3A Current-Limiter with OV, UV and Reverse Protection

### **Absolute Maximum Ratings**

| / tooolato maximam rtati                     |                                                 |

|----------------------------------------------|-------------------------------------------------|

| IN to GND                                    | 70V to +65V                                     |

| IN to OUT                                    | 65V to +65V                                     |

| OUT to GND                                   | 0.3V to +65V                                    |

| UVLO, OVLO to GND                            |                                                 |

| (MAX17613A and MAX17613B)                    | 0.3V to                                         |

|                                              | (max (V <sub>IN</sub> ,V <sub>OUT</sub> )+0.3V) |

|                                              | (IIIAX (V)N, VOUT) + 0.3V)                      |

| EN, CLMODE, TSTART to GND                    |                                                 |

| EN, CLMODE, TSTART to GND UVOV, FLAG to GND  |                                                 |

| UVOV, FLAG to GND (MAX17613A) and MAX17613B) | -0.3V to +6V                                    |

| UVOV, FLAG to GND                            | -0.3V to +6V                                    |

| IN Current (DC)                                              | 3.3A              |

|--------------------------------------------------------------|-------------------|

| SETI to GND (Note1)                                          | 0.3V to +1.6V     |

| Continuous Power Dissipation                                 |                   |

| $(T_A = +70^{\circ}C, derate 30.3 \text{mW/}^{\circ}C above$ | re +70°C)2424.2mW |

| Extended Operating Temperature Range                         |                   |

| (Note 2)                                                     | 40°C to +125°C    |

| Junction Temperature Range                                   | 40°C to +150°C    |

| Storage Temperature Range                                    | 65°C to +150°C    |

| Lead Temperature (Soldering, 10s)                            | +300°C            |

Note 1: The SETI pin is internally clamped. Forcing more than 5mA current into the pin can damage the device.

**Note 2:** Junction temperature greater than +125°C degrades operating life times.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **Package Information**

| PACKAGE TYPE: 20 TQFN                  |           |  |  |  |

|----------------------------------------|-----------|--|--|--|

| Package Code                           | T2044+4C  |  |  |  |

| Outline Number                         | 21-100172 |  |  |  |

| Land Pattern Number                    | 90-0409   |  |  |  |

| THERMAL RESISTANCE, FOUR-LAYER BOARD:  |           |  |  |  |

| Junction to Ambient (θ <sub>JA</sub> ) | 33°C/W    |  |  |  |

| Junction to Case (θ <sub>JC</sub> )    | 2°C/W     |  |  |  |

For the latest package outline information and land patterns (footprints), go to www.maximintegrated.com/packages. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

#### **Electrical Characteristics**

$(V_{IN} = +4.5 \text{ to } +60 \text{V}, T_A = -40 ^{\circ}\text{C to } +125 ^{\circ}\text{C unless otherwise noted. Typical values are at } V_{IN} = +24 \text{V}, T_A = +25 ^{\circ}\text{C}, R_{SETI} = 1.5 \text{k}\Omega.) \text{ (Note 3)}$

| PARAMETER                        | SYMBOL              | CONDITIONS                                                    |                            | MIN  | TYP  | MAX  | UNITS |

|----------------------------------|---------------------|---------------------------------------------------------------|----------------------------|------|------|------|-------|

| IN Voltage Range                 | V <sub>IN</sub>     |                                                               |                            | 4.5  |      | 60   | V     |

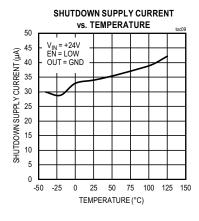

| Shutdown Input Current           | I <sub>SHDN</sub>   | V <sub>EN</sub> = 0V                                          |                            |      | 28   | 66   | μA    |

| Shutdown Output Current          | l <sub>OFF</sub>    | V <sub>EN</sub> = 0V, V <sub>OUT</sub> =                      | 0V (V <sub>IN</sub> = 60V) | -2   |      |      | μA    |

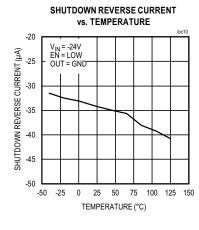

| Reverse Input Current            | I <sub>IN_RVS</sub> | V <sub>IN</sub> = -60V, V <sub>OUT</sub>                      | = 0V                       | -85  | -50  |      | μA    |

| Supply Current                   | I <sub>IN</sub>     | V <sub>IN</sub> = 24V                                         | V <sub>IN</sub> = 24V      |      | 0.88 | 1.2  | mA    |

| Internal Hadamieltana Tria Laval |                     | V <sub>IN</sub> rising                                        |                            | 3.46 | 4.2  | 4.5  | V     |

| Internal Undervoltage Trip Level |                     | V <sub>IN</sub> falling                                       |                            |      | 3.5  |      | ]     |

| UVLO, OVLO Reference             | V <sub>REF</sub>    | MAX17613A and MAX17613B                                       |                            | 1.45 | 1.5  | 1.55 | V     |

| UVLO, OVLO Threshold Hysteresis  |                     | MAX17613A and MAX17613B                                       |                            |      | 3.3  |      | %     |

| UVLO, OVLO Leakage Current       | I <sub>LEAK</sub>   | V <sub>UVLO</sub> = V <sub>OVLO</sub> MAX17613A and MAX17613B |                            | -100 |      | +100 | nA    |

| OVLO Adjustment Range            |                     | MAX17613A and I                                               | MAX17613B (Note 4)         | 5.5  |      | 60   | V     |

# 4.5V to 60V, 3A Current-Limiter with OV, UV and Reverse Protection

### **Electrical Characteristics (continued)**

$(V_{IN}$  = +4.5 to +60V,  $T_A$  = -40°C to +125°C unless otherwise noted. Typical values are at  $V_{IN}$  = +24V,  $T_A$  = +25°C,  $R_{SETI}$  = 1.5k $\Omega$ .) (Note 3)

| PARAMETER                                          | SYMBOL              | CONDITIONS                                                                                                                    | MIN  | TYP  | MAX  | UNITS |  |  |

|----------------------------------------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|--|--|

| UVLO Adjustment Range                              |                     | MAX17613A and MAX17613B (Note 4)                                                                                              | 4.5  |      | 59   | V     |  |  |

| Internal POR                                       |                     |                                                                                                                               | 3    |      | 4.3  | V     |  |  |

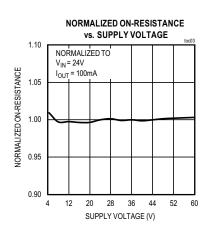

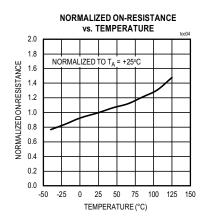

| INTERNAL FETs                                      |                     |                                                                                                                               |      |      |      |       |  |  |

|                                                    |                     | I <sub>LOAD</sub> = 100mA,V <sub>IN</sub> > 8V, T <sub>J</sub> = 25°C                                                         |      | 130  | 155  |       |  |  |

| Internal FETs On-Resistance                        | R <sub>ON</sub>     | I <sub>LOAD</sub> = 100mA,V <sub>IN</sub> > 8V, T <sub>J</sub> = 85°C                                                         |      |      | 200  | mO    |  |  |

| internal i Lis On-Nesistance                       | NON                 | I <sub>LOAD</sub> = 100mA,V <sub>IN</sub> > 8V, -40°C ≤ T <sub>J</sub> ≤ 125°C                                                |      |      | 230  | - mΩ  |  |  |

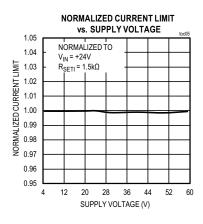

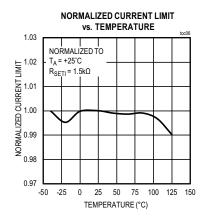

| Current-Limit Adjustment Range                     | I <sub>LIM</sub>    | (Note 5)                                                                                                                      | 0.15 |      | 3    | Α     |  |  |

| Current-Limit Accuracy                             |                     | 0.15A ≤ I <sub>LIM</sub> ≤ 3A                                                                                                 | -3.5 |      | +3.5 | %     |  |  |

| FLAG Assertion Drop Voltage<br>Threshold           | V <sub>FA</sub>     | Increase (V <sub>IN</sub> - V <sub>OUT</sub> ) drop until FLAG asserts, V <sub>IN</sub> = 24V (MAX17613A and MAX17613B)       | 400  | 500  | 600  | mV    |  |  |

| FWD Assertion Drop Voltage<br>Threshold            |                     | Increase (V <sub>IN</sub> - V <sub>OUT</sub> ) drop until <del>FWD</del> asserts, V <sub>IN</sub> = 24V (MAX17613C)           | 400  | 500  | 600  | mV    |  |  |

| Reverse Current Blocking Slow-<br>Threshold        | V <sub>RIBS</sub>   | V <sub>OUT</sub> - V <sub>IN</sub> (MAX17613A and MAX17613C)                                                                  | 2    | 11   | 20   | mV    |  |  |

| Reverse Current Blocking<br>Debounce Blanking Time | t <sub>DEBRIB</sub> | MAX17613A and MAX17613C                                                                                                       | 100  | 140  | 180  | μs    |  |  |

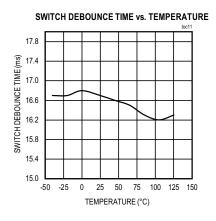

| Reverse Current Blocking Powerup Blanking Time     | t <sub>BLKRIB</sub> | MAX17613A and MAX17613C                                                                                                       | 14.4 | 16   | 17.6 | ms    |  |  |

| Reverse Current Blocking Fast-<br>Threshold        | V <sub>RIBF</sub>   | V <sub>OUT</sub> -V <sub>IN</sub> (MAX17613A and MAX17613C).                                                                  | 70   | 105  | 140  | mV    |  |  |

| Reverse Current Blocking Fast<br>Response Time     | t <sub>RIB</sub>    | Time from when I <sub>REVERSE</sub> crosses 55A and I <sub>REVERSE</sub> reaches its peak. (MAX17613A and MAX17613C) (Note 6) |      | 150  | 250  | ns    |  |  |

| Reverse Blocking Supply Current                    | I <sub>RBL</sub>    | Current into OUT when (V <sub>OUT</sub> - V <sub>IN)</sub> > 130mV (MAX17613A and MAX17613C)                                  |      | 0.92 | 1.25 | mA    |  |  |

| SETI                                               |                     |                                                                                                                               |      |      |      |       |  |  |

| R <sub>SETI</sub> x I <sub>LIM</sub>               | V <sub>RI</sub>     |                                                                                                                               |      | 1.5  |      | V     |  |  |

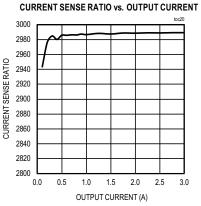

| Current Mirror Output Ratio                        | Cupatrio            | $0.15A \le I_{1N} \le 0.3A$                                                                                                   | 2910 | 3000 | 3090 | A/A   |  |  |

| Current Militor Output Natio                       | C <sub>IRATIO</sub> | 0.3A ≤ I <sub>IN</sub> ≤ 3A                                                                                                   | 2940 | 3000 | 3060 | ~~    |  |  |

| Internal SETI Clamp                                |                     | 5mA into SETI                                                                                                                 | 1.6  |      | 2.2  | V     |  |  |

| SETI Leakage Current                               |                     | V <sub>SETI</sub> = 1.6V                                                                                                      | -0.1 |      | +0.1 | μA    |  |  |

| LOGIC INPUT                                        |                     |                                                                                                                               |      |      |      |       |  |  |

| EN Input Logic High                                | V <sub>IH</sub>     |                                                                                                                               | 1.4  |      |      | V     |  |  |

| EN Input Logic Low                                 | V <sub>IL</sub>     |                                                                                                                               |      |      | 0.4  | V     |  |  |

| EN Pullup Voltage                                  |                     | EN pin unconnected. V <sub>IN</sub> = 60V                                                                                     |      | 1.4  | 2    | V     |  |  |

| EN Input Current                                   |                     | V <sub>EN</sub> = 5.5V                                                                                                        |      | 60   | 95   | μA    |  |  |

| EN Pullup Current                                  |                     | V <sub>EN</sub> = 0.4V                                                                                                        | 2.2  | 5.8  | 12   | μA    |  |  |

| CLMODE Input Logic High                            |                     |                                                                                                                               | 2    | 3.8  | 4.9  | V     |  |  |

# 4.5V to 60V, 3A Current-Limiter with OV, UV and Reverse Protection

### **Electrical Characteristics (continued)**

$(V_{IN}$  = +4.5 to +60V,  $T_A$  = -40°C to +125°C unless otherwise noted. Typical values are at  $V_{IN}$  = +24V,  $T_A$  = +25°C,  $R_{SETI}$  = 1.5k $\Omega$ .) (Note 3)

| PARAMETER                                  | SYMBOL                                    | CONDITIONS                                                                                                                                                                                                      | MIN   | TYP  | MAX   | UNITS |

|--------------------------------------------|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|-------|

| CLMODE Input Logic Low                     |                                           |                                                                                                                                                                                                                 | 0.25  | 0.60 | 0.95  | V     |

| CLMODE Pullup Input Current                |                                           |                                                                                                                                                                                                                 | 8     | 10   | 12    | μA    |

| FLAG, UVOV OUTPUTS                         |                                           |                                                                                                                                                                                                                 |       |      |       |       |

| FLAG, UVOV Output Logic Low<br>Voltage     |                                           | I <sub>SINK</sub> = 1mA (MAX17613A and MAX17613B)                                                                                                                                                               |       |      | 0.4   | V     |

| FLAG, UVOV Output Leakage<br>Current       |                                           | V <sub>IN</sub> = V <sub>FLAG</sub> = V <sub>UVOV</sub> = 5V, FLAG, and UVOV deasserted (MAX17613A and MAX17613B)                                                                                               |       |      | 1     | μΑ    |

| FWD, REV OUTPUTS                           |                                           |                                                                                                                                                                                                                 |       |      |       |       |

| FWD, REV Output Logic Low<br>Voltage       |                                           | I <sub>SINK</sub> = 1mA (MAX17613C)                                                                                                                                                                             |       |      | 0.4   | V     |

| FWD, REV Output Leakage Current            |                                           | $V_{IN} = V_{\overline{FWD}} = V_{\overline{REV}} = 5V,$<br>FWD, and REV deasserted (MAX17613C)                                                                                                                 |       |      | 1     | μA    |

| TSTART STARTUP                             |                                           |                                                                                                                                                                                                                 |       |      |       |       |

| TSTART Reference Voltage                   | V <sub>TSTART</sub> -                     |                                                                                                                                                                                                                 | 1.425 | 1.5  | 1.575 | V     |

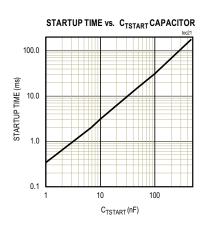

| TSTART Output Current                      | I <sub>TSTART</sub>                       |                                                                                                                                                                                                                 | 4.5   | 5    | 5.5   | μA    |

| TSTART Internal Shunt Discharge Resistance | R <sub>TSTART</sub>                       | Discharging Resistance                                                                                                                                                                                          |       |      | 260   | Ω     |

| TSTART Unconnecting Check Time Interval    | t <sub>TSTART</sub> -<br>UNCON-<br>NECTED |                                                                                                                                                                                                                 |       | 100  |       | μs    |

| TSTART default interval                    | t <sub>TSTART</sub> -                     |                                                                                                                                                                                                                 | 90    | 100  | 110   | ms    |

| TIMING CHARACTERISTICS                     |                                           |                                                                                                                                                                                                                 |       |      |       |       |

| Switch Turn-On Time                        | t <sub>ON_</sub><br>SWITCH                | $V_{IN}$ = 24V, $R_{LOAD}$ = 1k $\Omega$ , $C_{LOAD}$ = 0 $\mu$ F, $R_{SETI}$ = 1.5k $\Omega$                                                                                                                   |       | 2    | 3.3   | ms    |

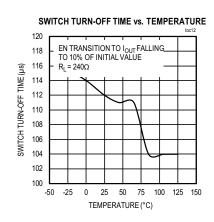

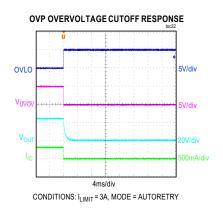

| Overvoltage Switch Turn-Off Time           | t <sub>OFF_OVP</sub>                      | From (V <sub>IN</sub> going from V <sub>IN_OVLO</sub> - 1V to V <sub>IN_OVLO</sub> + 1V in 10ns) to (V <sub>OUT</sub> = 80% of V <sub>IN_OVLO</sub> ); R <sub>LOAD</sub> = $1k\Omega$ (MAX17613A and MAX17613B) |       | 0.8  | 1.3   | μs    |

| Overvoltage Falling Edge<br>Debounce Time  | t <sub>DEB_OVP</sub>                      |                                                                                                                                                                                                                 |       | 10   |       | μs    |

| Overcurrent Protection Response<br>Time    | tocp_res                                  | I <sub>LIM</sub> = 3A, C <sub>LOAD</sub> = 0μF, I <sub>OUT</sub> step from<br>1.5A to 3A. Time to regulate I <sub>OUT</sub> to current<br>limit.                                                                |       | 100  |       | μs    |

| IN Debounce Time                           | t <sub>DEB</sub>                          | From (V <sub>IN_UVLO</sub> < V <sub>IN</sub> < V <sub>IN_OVLO</sub> )<br>and (EN = High) to V <sub>OUT</sub> = 10% of V <sub>IN</sub> .<br>Elapses only at power-up. (MAX17613A and<br>MAX17613B)               | 14.4  | 16   | 17.6  | ms    |

| Current-Limit Smooth-Transition<br>Time    | t <sub>REF_RAMP</sub>                     |                                                                                                                                                                                                                 |       | 60   |       | μs    |

### 4.5V to 60V, 3A Current-Limiter with OV, UV and Reverse Protection

#### **Electrical Characteristics (continued)**

$(V_{IN} = +4.5 \text{ to } +60 \text{V}, T_A = -40 ^{\circ}\text{C} \text{ to } +125 ^{\circ}\text{C} \text{ unless otherwise noted.}$  Typical values are at  $V_{IN} = +24 \text{V}, T_A = +25 ^{\circ}\text{C}, R_{SETI} = 1.5 \text{k}\Omega.)$  (Note 3)

| PARAMETER                    | SYMBOL              | CONDITIONS                                                                                                          | MIN | TYP  | MAX  | UNITS |

|------------------------------|---------------------|---------------------------------------------------------------------------------------------------------------------|-----|------|------|-------|

| Current-Limit Blanking Time  | t <sub>BLANK</sub>  |                                                                                                                     | 18  | 20   | 22   | ms    |

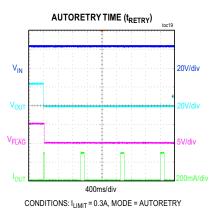

| Current-Limit Autoretry Time | tRETRY              | After blanking time from I <sub>OUT</sub> > I <sub>LIM</sub> to FLAG deasserted ( MAX17613A and MAX17613B) (Note 7) | 900 | 1000 | 1100 | ms    |

|                              |                     | After blanking time from I <sub>OUT</sub> > I <sub>LIM</sub> to FWD deasserted (MAX17613C) (Note 7)                 | 900 | 1000 | 1100 |       |

| THERMAL PROTECTION           |                     |                                                                                                                     |     |      |      |       |

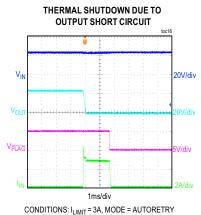

| Thermal Shutdown             | T <sub>JC_MAX</sub> |                                                                                                                     |     | 155  |      | С     |

| Thermal Shutdown Hysteresis  | T <sub>JC_HYS</sub> |                                                                                                                     |     | 15   |      | °C    |

- Note 3: All devices are 100% production tested at T<sub>A</sub> = +25°C. Limits over the operating temperature range are guaranteed by design; not production tested.

- Note 4: User settable. See overvoltage/undervoltage lockout instructions.

- Note 5: The current limit can be set below 150mA with a decreased accuracy.

- Note 6: Guaranteed by design, not production tested.

- Note 7: The ratio between autoretry time and blanking time is fixed and equal to 50.

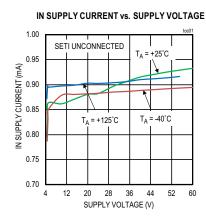

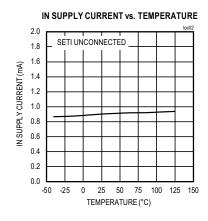

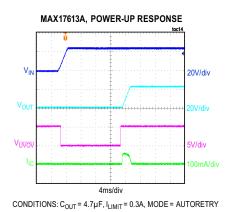

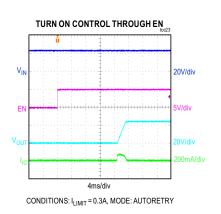

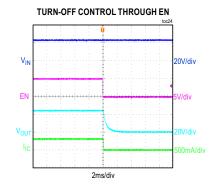

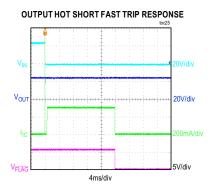

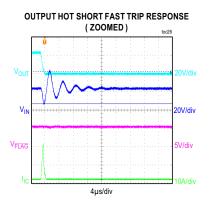

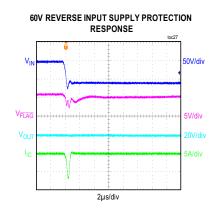

### **Typical Operating Characteristics**

$(C_{IN} = 0.47 \mu F, C_{OUT} = 4.7 \mu F, V_{IN} = 24 V, T_A = +25 °C, unless otherwise noted.)$

## 4.5V to 60V, 3A Current-Limiter with OV, UV and Reverse Protection

### **Typical Operating Characteristics (continued)**

( $C_{IN}$  = 0.47 $\mu$ F,  $C_{OUT}$  = 4.7 $\mu$ F,  $V_{IN}$  = 24V,  $T_A$  = +25 $^{\circ}$ C, unless otherwise noted.)

## 4.5V to 60V, 3A Current-Limiter with OV, UV and Reverse Protection

### **Typical Operating Characteristics (continued)**

$(C_{IN}$  = 0.47 $\mu$ F,  $C_{OUT}$  = 4.7 $\mu$ F,  $V_{IN}$  = 24V,  $T_A$  = +25°C, unless otherwise noted.)

## 4.5V to 60V, 3A Current-Limiter with OV, UV and Reverse Protection

### **Typical Operating Characteristics (continued)**

$(C_{IN}$  = 0.47 $\mu$ F,  $C_{OUT}$  = 4.7 $\mu$ F,  $V_{IN}$  = 24V,  $T_A$  = +25°C, unless otherwise noted.)

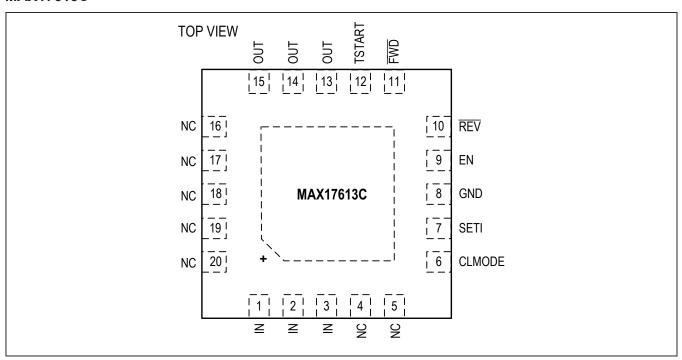

4.5V to 60V, 3A Current-Limiter with OV, UV and Reverse Protection

### **Pin Configuration**

#### **MAX17613A and MAX17613B**

#### MAX17613C

# 4.5V to 60V, 3A Current-Limiter with OV, UV and Reverse Protection

### **Pin Description**

| PI                      | IN          |        |                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------------|-------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX17613A,<br>MAX17613B | MAX17613C   | NAME   | FUNCTION                                                                                                                                                                                                                                                                                                                                                                              |

| 1-3                     | 1-3         | IN     | Input Pins. Use a low-ESR ceramic capacitor to enhance ESD protection. For Hot Plug in applications, see the <i>Applications Information</i> section.                                                                                                                                                                                                                                 |

| 4                       | _           | UVLO   | UVLO Adjustment. Connect resistive potential divider from IN to GND to set the UVLO threshold.                                                                                                                                                                                                                                                                                        |

| 5                       | _           | OVLO   | OVLO Adjustment. Connect resistive potential divider from IN to GND to set the OVLO threshold.                                                                                                                                                                                                                                                                                        |

| 6                       | 6           | CLMODE | Current-Limit Mode Selector. Connect CLMODE to GND for Continuous mode. Connect a $150 k\Omega$ resistor between CLMODE and GND for latchoff mode. Leave CLMODE unconnected for autoretry mode.                                                                                                                                                                                       |

| 7                       | 7           | SETI   | Overcurrent-Limit Adjustment Pin and Current Monitoring Output. Connect a resistor from SETI to GND to set overcurrent limit. See the <u>Setting the Current-Limiting Threshold (ILIM)</u> section.                                                                                                                                                                                   |

| 8                       | 8           | GND    | Ground                                                                                                                                                                                                                                                                                                                                                                                |

| 9                       | 9           | EN     | Active High Enable Input. Internally pulled up to 1.8V. Leave it unconnected for always on operation.                                                                                                                                                                                                                                                                                 |

| 10                      | _           | ŪVOV   | Open-Drain, Fault Indicator Output.    UVOV goes low with any of the following  Input voltage falls below UVLO threshold.  Input voltage rises above OVLO threshold.                                                                                                                                                                                                                  |

| _                       | 10          | REV    | Open-Drain, Fault Indicator Output. REV goes low when reverse current is detected.                                                                                                                                                                                                                                                                                                    |

| 11                      | _           | FLAG   | Open-Drain, Fault Indicator Output. FLAG goes low with any of the following  • Overcurrent duration exceeds the blanking time.  • Overcurrent duration exceeds the startup blanking time.  • Reverse current is detected.  • Thermal shutdown is active.  • R <sub>SETI</sub> is less than 1.5kΩ (max).                                                                               |

| _                       | 11          | FWD    | Open-Drain, Fault Indicator Output. FWD goes low when:  • Overcurrent duration exceeds the blanking time.  • Overcurrent duration exceeds the startup blanking time.  • Thermal shutdown is active.  • R <sub>SETI</sub> is less than 1.5kΩ (max).                                                                                                                                    |

| 12                      | 12          | TSTART | Programmable Startup Blanking Time. Connect a capacitor from TSTART to GND to set the desired startup blanking time. Leaving the pin unconnected enables the TSTART pin to charge faster, If the TSTART pin voltage charges within 100µs, a defaul blanking time of 100ms is set as startup time. See the <i>Programming Startup Blanking Time (TSTART)</i> section for more details. |

| 13-15                   | 13-15       | OUT    | Output Pins. For a long output cable or inductive load, see the <i>Applications Information</i> section.                                                                                                                                                                                                                                                                              |

| 16-20                   | 4, 5, 16-20 | NC     | Not Connected                                                                                                                                                                                                                                                                                                                                                                         |

|                         | _           | EP     | Exposed Pad. Connect EP to a large GND plane with several thermal vias for best thermal performance. Refer to the MAX17613A/B/C EV kit data sheet for a reference layout design.                                                                                                                                                                                                      |

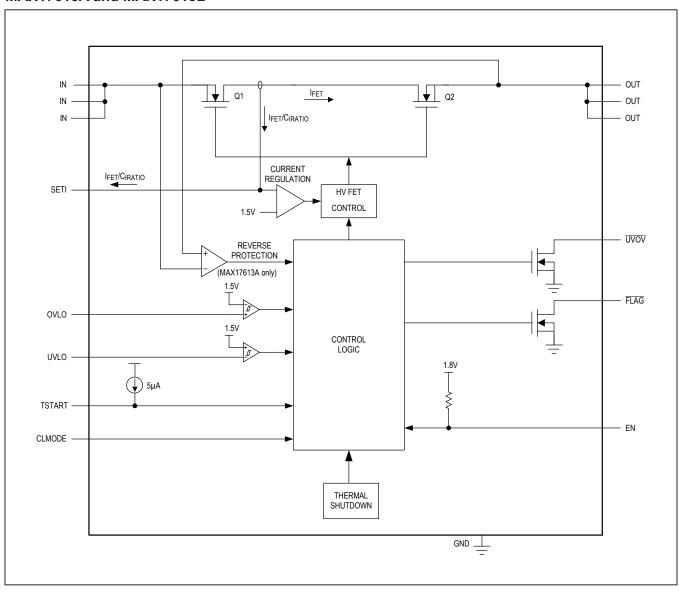

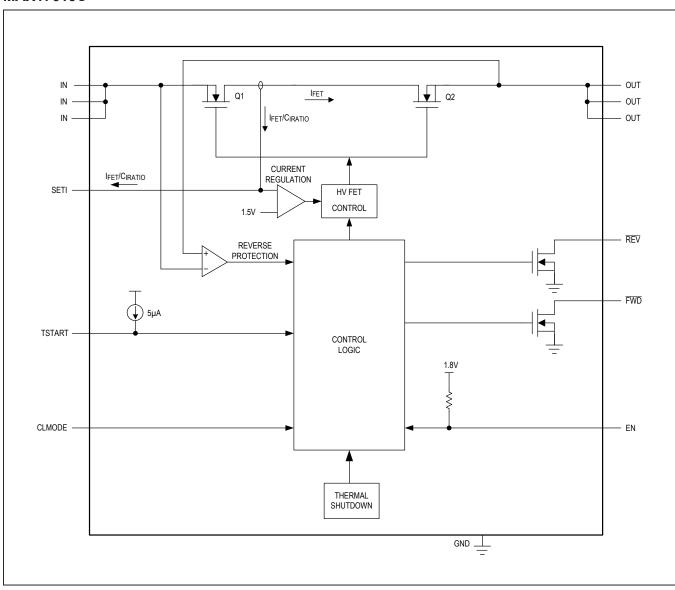

# 4.5V to 60V, 3A Current-Limiter with OV, UV and Reverse Protection

### **Functional Diagrams**

#### **MAX17613A and MAX17613B**

# 4.5V to 60V, 3A Current-Limiter with OV, UV and Reverse Protection

## **Functional Diagrams (continued)**

#### **MAX17613C**

#### **Detailed Description**

The MAX17613A/MAX17613B/MAX17613C overvoltage and overcurrent protection devices offer adjustable protection boundaries for systems against input positive and negative faults up to +60V and -65V, and output load current up to 3A. The devices feature two internal MOSFETs connected in series with a low cumulative  $R_{ON}$  of  $130 m\Omega$  (typ). The devices block out negative input voltages completely. Input undervoltage protection can be programmed between 4.5V and 59V, while the overvoltage protection can be independently programmed between 5.5V and 60V. Additionally, the devices have an internal default undervoltage lockout set at 4.2V (typ). The devices are enabled or disabled through the EN pin by a master supervisory system; hence, offering a switch operation to turn on or turn off power delivery to connected load.

The current through the devices is limited by setting a current limit, which is programmed by a resistor connected from SETI to GND. The current limit can be programmed between 0.15A to 3A. When the device current reaches or exceeds the set current limit, the on-resistance of the internal output NFET Q2 is modulated to limit the current to set limits. The devices offer three different behavioral modes when under current-limited operations: autoretry, continuous, and latchoff modes. The SETI pin also presents a voltage with reference to GND, which under normal operation is proportional to the device current. The voltage appearing on the SETI pin can be read by an ADC on the monitoring system for recording instantaneous device current. To avoid oscillation, do not connect more than 10pF to the SETI pin.

The devices offer status signals to indicate different operational and fault signals. MAX17613A and MAX17613B offer FLAG and UVOV signals, while MAX17613C offers FWD and REV signals. All status signal pins are open drain in nature and require external pullup resistors to appropriate system interface voltage. MAX17613A and MAX17613C block reverse current flow (from OUT to IN) while MAX17613B allows reverse current flow. All three devices offer internal thermal shutdown protection against excessive power dissipation.

#### Undervoltage Lockout (UVLO)

MAX17613A and MAX17613B have UVLO adjustment range from 4.5V to 59V. Connect an external resistive potential divider to the UVLO pin as shown in the

## 4.5V to 60V, 3A Current-Limiter with OV, UV and Reverse Protection

<u>Typical Operating Circuit</u> to adjust the UVLO threshold voltage. Use the following equation to adjust the UVLO threshold. The recommended value of R1 is  $2.2M\Omega$ .

$$V_{\text{UVLO}} = V_{\text{REF}} \times \left[1 + \frac{R1}{R2}\right]$$

where  $V_{REF} = 1.5V$ .

All three devices have an input UVLO threshold set at 4.2V (typ). MAX17613C has no UVLO pin to adjust the UVLO threshold voltage externally.

#### Overvoltage Lockout (OVLO)

MAX17613A and MAX17613B have OVLO adjustment range from 5.5V to 60V. Connect an external resistive potential divider to the OVLO pin as shown in the <u>Typical Operating Circuit</u> to adjust OVLO threshold voltage. Use the following equation to adjust OVLO threshold. The recommended value of R3 is  $450k\Omega-500k\Omega$ .

$$V_{OVLO} = V_{REF} \times \left[1 + \frac{R3}{R4}\right]$$

where  $V_{REF} = 1.5V$ .

The MAX17613C device has no OVLO pin to adjust the OVLO threshold voltage.

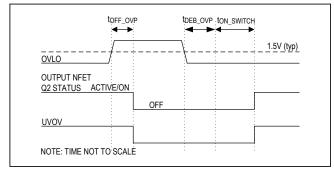

The OVLO reference voltage ( $V_{REF}$ ) is set at 1.5V. If the voltage at the OVLO pin exceeds  $V_{REF}$  for time equal to overvoltage switch turn-off time ( $t_{OFF\_OVP}$ ), the switch is turned off and  $\overline{UVOV}$  is asserted. When the OVLO condition is removed, the device takes overvoltage falling edge debounce time ( $t_{DEB\_OVP}$ ) to start the switch turn-on process. The switch turns back on after switch turn-on time ( $t_{ON\_SWITCH}$ ) and  $\overline{UVOV}$  is deasserted. Figure 1 depicts a typical behavior in overvoltage condition.

Figure 1. Overvoltage Fault Timing Diagram

#### **Input Debounce Protection**

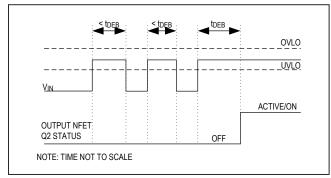

The device features input debounce protection. The device starts operation (turn on the internal FETs) only if the input voltage is higher than the UVLO threshold for a period greater than the debounce time (t<sub>DEB</sub>). The t<sub>DEB</sub> elapses only at power-up of the devices. This feature is intended for applications where the EN signal is present when the power supply ramps up. Figure 2 depicts a typical debounce timing diagram.

#### **Enable (EN)**

The device can be enabled or disabled through the EN pin by driving it above or below EN threshold voltage. Hence the device can be used to turn on or off power delivery to connected loads using the EN pin.

#### **Setting the Current-Limiting Threshold (ILIM)**

During overload events, the device continuously regulates the device current to the overcurrent limit  $I_{LIM}$  programmed by the resistor  $R_{SETI}$  connected at the SETI pin. The current limit can be programmed between 0.3A to 3A. Use the following equation to calculate current-limit setting resistor:

$$R_{SETI} = \frac{4500}{I_{LIM}}$$

where,

$I_{LIM}$  is the desired current limit in mA and  $R_{SFTI}$  is in  $k\Omega$ .

Figure 2. Debounce Timing Diagram

## 4.5V to 60V, 3A Current-Limiter with OV, UV and Reverse Protection

Do not use  $R_{SETI}$  smaller than 1.5k $\Omega$ . Table 1 shows current-limit thresholds for different resistor values.

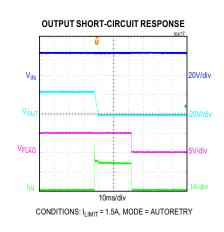

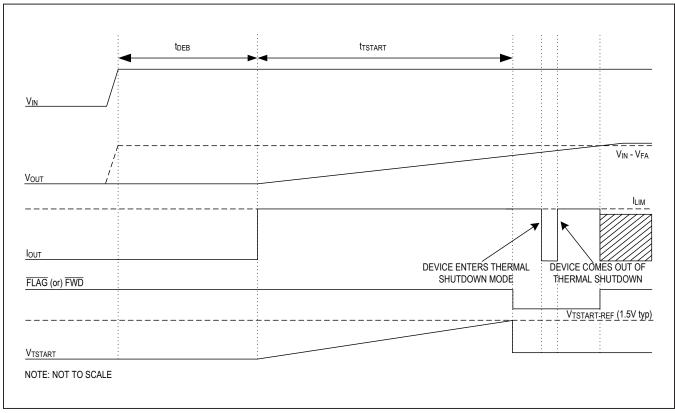

When the device current reaches or exceeds the set current limit during overload, short-circuit or during startup cycle charging large capacitance, the on-resistance of the internal output NFET Q2 is modulated to limit the current to set limits, resulting in the output voltage droop and increased power dissipation in the device. If the device junction temperature reaches the thermal shutdown threshold T<sub>JC MAX</sub> the output NFET Q2 turns off and FLAG (or FWD) is asserted. The output NFET Q2 turns back on in current-limit mode only after the junction temperature cools down by T<sub>JC HYS</sub>. The devices feature read out of the current flowing into the IN pin. A current mirror, with a ratio of CIRATIO, is implemented, using a current-sense auto-zero operational amplifier. The mirrored current flows out through the SETI pin, into the external current-limit resistor. The voltage on the SETI pin provides information about IN current with the following relationship:

$$I_{IN-OUT} = \frac{3 \times V_{SETI}}{R_{SETI}}$$

If SETI is left unconnected,  $V_{SETI} \ge 1.5V$ . The current regulator does not allow any current to flow. During startup, this causes the switches to remain off and  $\overline{FLAG}$  (or  $\overline{FWD}$ ) to assert after  $t_{BLANK}$  elapses. During startup, 270µA current is forced to flow through  $R_{SETI}$ . If the voltage at SETI is below 150mV, the switches remain off and  $\overline{FLAG}$  (or  $\overline{FWD}$ ) asserts.

Table 1. Current-Limit Threshold vs. SETI Resistor Values

| R <sub>SETI</sub> (kΩ) | CURRENT LIMIT I <sub>LIM</sub> (A) |

|------------------------|------------------------------------|

| 15.00                  | 0.3                                |

| 4.53                   | 1.0                                |

| 2.26                   | 2.0                                |

| 1.80                   | 2.5                                |

| 1.50                   | 3.0                                |

## Programming Startup Blanking Time (TSTART)

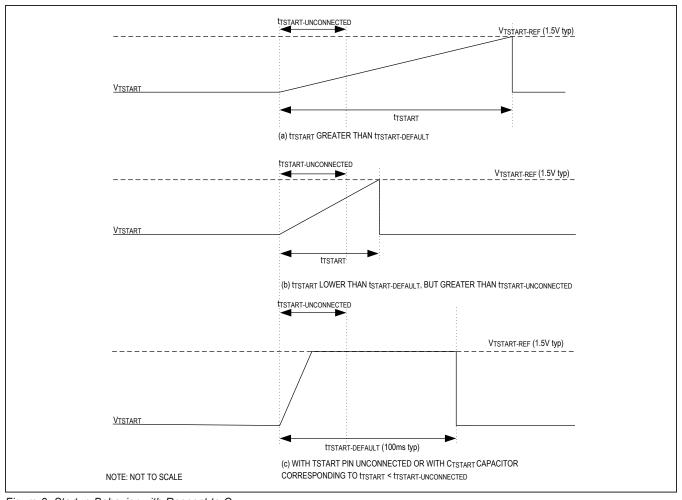

The MAX17613A/MAX17613B/MAX17613C devices offer a programmable startup blanking time that enables charging the large capacitances on the output during startup and when recovering from a fault condition. Connecting a capacitor from the TSTART pin to GND programs the startup blanking time. t<sub>TSTART</sub> is the time allowed for V<sub>OUT</sub> to reach the designated value (V<sub>IN</sub> - V<sub>FA</sub>) before the device enter in to fault mode. If the output voltage doesn't charge to its nominal set voltage (V<sub>IN</sub> - V<sub>FA</sub>) within the programmed time ( $t_{TSTART}$ ), then the  $\overline{FLAG}$  (or FWD) is asserted and both the MOSFETs are turned off. In order to allow the charging of large capacitances in all conditions, thermal fault does not induce a retry cycle (or a latchoff) during the startup phase rather a thermal and recycling happens as explained in the Thermal Shutdown Protection section. In order to program t<sub>TSTART</sub>, the capacitor CTSTART connected to the TSTART pin is charged with a constant current of 5µA. When the voltage on the capacitor reaches 1.5V, t<sub>TSTART</sub> is considered expired and the capacitor is discharged to ground.

$$t_{TSTART} = \frac{C_{TSTART}}{5\mu} \times 1.5$$

The following table presents C<sub>TSTART</sub> required for different t<sub>TSTART</sub> durations.

Table 2. CTSTART vs. tTSTART

| t <sub>TSTART</sub> (ms) | C <sub>TSTART</sub> (nF) |

|--------------------------|--------------------------|

| 15                       | 50                       |

| 60                       | 200                      |

| 300                      | 1000                     |

| 100                      | Left open                |

## 4.5V to 60V, 3A Current-Limiter with OV, UV and Reverse Protection

For the given output capacitor, the startup capacitor (C<sub>TSTART</sub>) is calculated to be

$$C_{\texttt{TSTART}} \ge \frac{3.33 \times C_{\texttt{OUT}(\texttt{MAX})} \times V_{\texttt{IN}(\texttt{MAX})}}{I_{\texttt{LIM}}}$$

The startup time (t<sub>TSTART</sub>) is related to the startup capacitor by the following equation:

$$t_{TSTART} = 300 \times C_{TSTART}$$

where,

CTSTART is in nF,

$C_{OLIT(MAX)}$  = Maximum output capacitance in  $\mu F$ ,

V<sub>IN(MAX)</sub> = Maximum input voltage in V,

I<sub>LIM</sub> = Programmed current limit in mA,

t<sub>TSTART</sub> is in µs.

If the TSTART pin is left unconnected, a situation that would correspond to a very short t<sub>TSTART</sub>, the minimum startup time is internally set to a default interval. If the voltage threshold is crossed in less than t<sub>TSTART-UNCONNECTED</sub>, the pin is considered unconnected and the device applies a preset startup time t<sub>TSTART-DEFAULT</sub>. Figure 3 depicts the startup behavior with and without a capacitor at the TSTART pin.

#### **Current Limit Type Selection (CLMODE)**

The CLMODE pin shall be used to program the overcurrent response of the device in one of the three modes. Connect a 150k $\Omega$  resistor between CLMODE and GND for latchoff current-limit mode. Connect CLMODE to GND for continuous current-limit mode. Leave the CLMODE pin unconnected for autoretry current-limit mode.

In all the three current-limit modes, if the current through the device reaches or exceeds the current-limit threshold, the device limits output current to the programmed current limit by modulating the internal output NFET Q2 on-state resistance.

# 4.5V to 60V, 3A Current-Limiter with OV, UV and Reverse Protection

Figure 3. Startup Behavior with Respect to  $C_{TSTART}$

## 4.5V to 60V, 3A Current-Limiter with OV, UV and Reverse Protection

#### **Continuous Current-Limit Mode**

In continuous current-limit mode during startup, the device starts as the startup blanking time ( $t_{TSTART}$ ) interval starts. The timer  $t_{TSTART}$  resets if the output voltage  $V_{OUT}$  reaches ( $V_{IN}$  -  $V_{FA}$ ) within  $t_{TSTART}$  and then the normal operation continues. If the output voltage  $V_{OUT}$  does not reach ( $V_{IN}$  -  $V_{FA}$ ) within  $t_{TSTART}$ , the  $t_{TSTART}$

timer resets, the  $\overline{\text{FLAG}}$  (or  $\overline{\text{FWD}}$ ) pin asserts, the output NFET Q2 is not turned off, and the operation continues. If the device enters thermal shutdown mode, the  $\overline{\text{FLAG}}$  (or  $\overline{\text{FWD}}$ ) pin asserts and the output NFET Q2 turns off and it turns back on after the junction temperature cools down by  $T_{JC\_HYS}$ . The  $\overline{\text{FLAG}}$  (or  $\overline{\text{FWD}}$ ) deasserts after  $V_{OUT}$  reaches ( $V_{IN}$  -  $V_{FA}$ ). Figure 4 depicts a typical startup behavior in continuous current-limit mode.

Figure 4. Startup Fault Timing Diagram in Continuous Current-Limit Mode

## 4.5V to 60V, 3A Current-Limiter with OV, UV and Reverse Protection

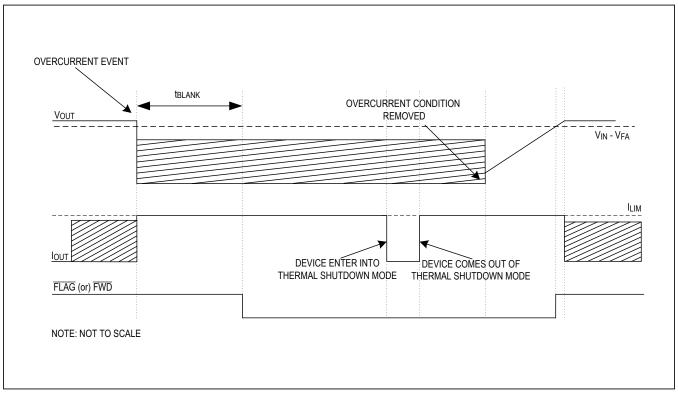

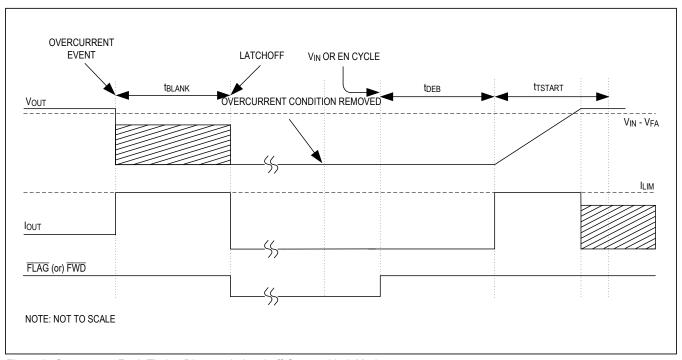

In continuous current-limit mode during normal operation, if the device enters an overcurrent condition the  $t_{BLANK}$  timer starts. The  $t_{BLANK}$  timer resets when the overcurrent condition resolves before the  $t_{BLANK}$  duration has elapsed and then the normal operation continues. If the overcurrent condition exists for the  $t_{BLANK}$  duration, the  $t_{BLANK}$  timer resets, the  $\overline{FLAG}$  (or  $\overline{FWD}$ ) pin asserts,

the output NFET Q2 is not turned-off and the operation continues. If the device enters thermal shutdown mode,  $\overline{\text{FLAG}}$  (or  $\overline{\text{FWD}}$ ) pin asserts and the output NFET Q2 turns off and it turns back on after the junction temperature cools down by  $T_{JC\_HYS}.$   $\overline{\text{FLAG}}$  (or  $\overline{\text{FWD}}$ ) deasserts after  $V_{OUT}$  reaches ( $V_{IN}$  -  $V_{FA}$ ).  $\underline{\text{Figure 5}}$  depicts a typical operating behavior in continuous current-limit mode.

Figure 5. Overcurrent Fault Timing Diagram in Continuous Current-Limit Mode

## 4.5V to 60V, 3A Current-Limiter with OV, UV and Reverse Protection

#### **Autoretry Current-Limit Mode**

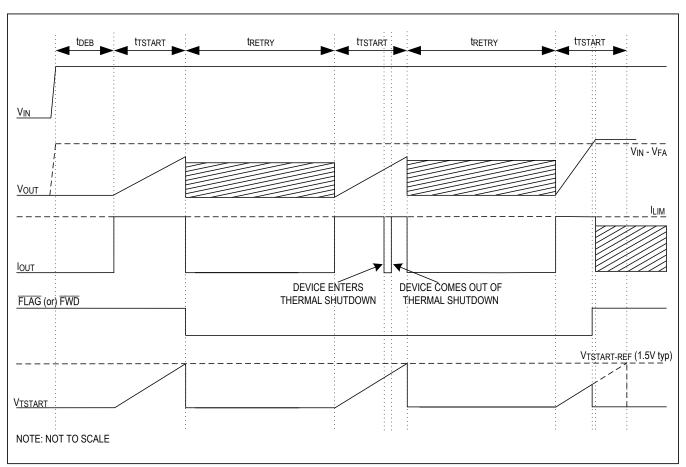

In autoretry current-limit mode during startup, the device operates in continuous current-limit mode until  $t_{TSTART}$ . The timer  $t_{TSTART}$  resets if the output voltage  $V_{OUT}$  reaches ( $V_{IN}$  -  $V_{FA}$ ) within  $t_{TSTART}$  and then the normal operation continues. If the overcurrent condition is present for startup blanking time ( $t_{TSTART}$ ), the output NFET Q2 is turned off, the timer  $t_{TSTART}$  resets, and the  $\overline{FLAG}$  (or  $\overline{FWD}$ ) pin asserts. A retry time delay ( $t_{RETRY}$ ) starts after  $t_{TSTART}$  has elapsed and after the device comes

out of thermal shutdown mode, if it was entered. During  $t_{RETRY}$  time, the output NEFT Q2 remains off. Once the  $t_{RETRY}$  time has elapsed, the device reinitiates the startup cycle again. If the overcurrent fault still exists, the autoretry startup cycle is repeated and the  $\overline{FLAG}$  (or  $\overline{FWD}$ ) pin remains asserted. If the overcurrent condition is resolved, and the output voltage ( $V_{OUT}$ ) reaches ( $V_{IN}$  -  $V_{FA}$ ) the output NFET Q2 stays on and the  $\overline{FLAG}$  (or  $\overline{FWD}$ ) deasserts. Figure 6 depicts a typical startup behavior in autoretry current-limit mode.

Figure 6. Startup Fault Timing Diagram in Autoretry Current-Limit Mode

## 4.5V to 60V, 3A Current-Limiter with OV, UV and Reverse Protection

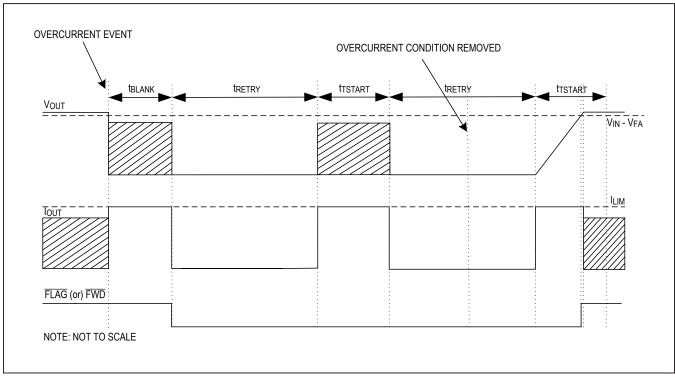

In autoretry current-limit mode during normal operation, if the device enters an overcurrent condition, the  $t_{BLANK}$  timer starts. The  $t_{BLANK}$  timer resets as and when the overcurrent condition resolves before the  $t_{BLANK}$  duration has elapsed, and then the normal operation continues. If the overcurrent condition is present for  $t_{BLANK}$  duration or if the device junction temperature reaches  $T_{JC\_MAX}$ , the output NFET Q2 is turned-off, the  $t_{BLANK}$  timer resets,

and the  $\overline{\text{FLAG}}$  (or  $\overline{\text{FWD}}$ ) pin asserts. A retry time delay (tretry) starts after treatment that device comes out of thermal shutdown mode, if it was entered. During the tretry interval, the output NFET Q2 remains turned off. Once tretry has elapsed, the device initiates the startup cycle. Figure 7 depicts a typical operating behavior in autoretry current-limit mode.

Figure 7. Overcurrent Fault Timing Diagram in Autoretry Current-Limit Mode

## 4.5V to 60V, 3A Current-Limiter with OV, UV and Reverse Protection

The autoretry feature reduces system power compared to continuous current-limit mode in case of overcurrent or short-circuit conditions. When the device is turned on for  $t_{TSTART}$  time, the supply current is held at the current limit. During  $t_{RETRY}$  time, there is no current through the switch. Thus, the average output current is much less than the programmed current limit. Calculate the average output current using the following equation:

$$I_{LOAD} = I_{LIM} \begin{bmatrix} \frac{t_{TSTART}}{t_{TSTART}} \end{bmatrix}$$

The duty cycle is dependent on  $t_{TSTART}$  time. For a current-limit threshold setting of 300mA, output voltage of 24V and output capacitance of 1000 $\mu$ F, the  $t_{TSTART}$  time is ~80ms. With 1000ms (typ) of  $t_{RETRY}$  time, the duty cycle is ~8%, resulting in a 92% power reduction when compared to the device being on the entire time.

Figure 8. Startup Fault Timing Diagram in Latchoff Current-Limit Mode

## 4.5V to 60V, 3A Current-Limiter with OV, UV and Reverse Protection

#### **Latchoff Current-Limit Mode**

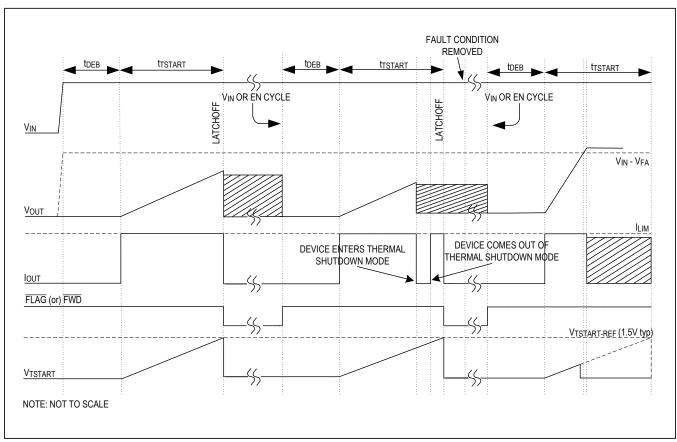

In latchoff current-limit mode during startup, the device operates in continuous current-limit mode until  $t_{TSTART}.$  The timer  $t_{TSTART}$  resets if the output voltage  $V_{OUT}$  reaches ( $V_{IN}$  -  $V_{FA}$ ) within  $t_{TSTART}$  and then the normal operation continues. If the overcurrent condition is present for longer than startup blanking time ( $t_{TSTART}$ ), the output NFET Q2 is turned off and latched, the timer  $t_{TSTART}$  resets, and the  $\overline{FLAG}$  (or  $\overline{FWD}$ ) pin asserts. To reset the device, either toggle the enable control signal (EN) or cycle the input voltage. Figure 8 depicts a typical startup behavior in latchoff current-limit mode.

In latchoff current-limit mode during normal operation, if the device enters an overcurrent condition, the  $t_{BLANK}$  timer starts. The  $t_{BLANK}$  timer resets as and when the overcurrent condition resolves before the  $t_{BLANK}$  duration has elapsed, and then the normal operation continues. If the overcurrent condition exists for the  $t_{BLANK}$  duration or if the device junction temperature reaches  $T_{JC\_MAX}$ , the output NFET Q2 is turned off and latched, the  $t_{BLANK}$  timer resets, and the  $t_{BLANK}$  (or  $t_{BLANK}$ ) pin asserts. To reset the device, either toggle enable control signal (EN) or cycle the input voltage. Figure 9 depicts a typical operating behavior in latchoff current-limit mode.

Figure 9. Overcurrent Fault Timing Diagram in Latchoff Current-Limit Mode

## 4.5V to 60V, 3A Current-Limiter with OV, UV and Reverse Protection

#### **Reverse Current Protection**

In MAX17613A and MAX17613C, the reverse current protection feature is enabled and it prevents reverse current flow from the OUT to IN pins. In MAX17613B, the reverse current protection feature is disabled, which allows reverse current flow from the OUT to IN pins. This feature is useful in applications with inductive loads.

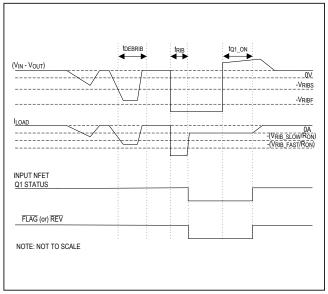

The MAX17613A and MAX17613C devices monitor  $V_{IN}$  and  $V_{OUT}$  to provide true reverse current blocking when a reverse condition or input failure condition is detected. In both MAX17613A and MAX17613C devices, two reverse current protection features are implemented.

A slow reverse current condition is detected if ( $V_{IN}$  -  $V_{OUT}$ ) < - $V_{RIBS}$  is present for reverse current blocking debounce blanking time ( $t_{DEBRIB}$ ). During this condition, only the input NFET Q1 turns off and  $\overline{FLAG}$  (or  $\overline{REV}$ ) is asserted while the output NFET Q2 is kept on. During and after this time, the device monitors the voltage difference

(Vin - Vout)

OV

-VRIBS

ILIMIT

Q1 STATUS

FLAG (or) REV

NOTE: TIME NOT TO SCALE

Figure 10. Slow Reverse Current Fault Timing Diagram

between the OUT and IN pins to determine whether the reverse current is still present. Once the reverse current condition has been removed, input NFET Q1 turns back on and the  $\overline{FLAG}$  (or  $\overline{REV}$ ) pin is deasserted. The input NFET Q1 takes ~100µs (tQ1\_ON) to turn on. Figure 10 depicts typical behavior in slow reverse current conditions.

A fast reverse current condition is detected if ( $V_{IN}$  -  $V_{OUT}$ ) < - $V_{RIBF}$  is present for reverse current blocking fast response time ( $t_{RIB}$ ). During this condition, only the input NFET Q1 turns off and  $\overline{FLAG}$  (or  $\overline{REV}$ ) is asserted while the output NFET Q2 is kept on. During and after this time, the device monitors the voltage difference between the OUT and IN pins to determine whether the reverse current is still present. Once the reverse current condition has been removed, input NFET Q1 turns back on and the  $\overline{FLAG}$  (or  $\overline{REV}$ ) pin is deasserted. The input NFET Q1 takes ~100 $\mu$ s ( $t_{Q1}$  ON) to turn on.  $\overline{Figure}$  11 depicts typical behavior in fast reverse current conditions.

Figure 11. Fast Reverse Current Fault Timing Diagram

### **Fault Output**

The MAX17613A and MAX17613B devices have two open-drain fault outputs,  $\overline{\text{FLAG}}$  and  $\overline{\text{UVOV}}$ . They require external pullup resistors to a DC supply. The  $\overline{\text{FLAG}}$  pin goes low when any of the following conditions occur:

- Overcurrent duration exceeds blanking time t<sub>BLANK</sub>.

- Overcurrent duration exceeds startup blanking time (t<sub>TSTART</sub>) during the startup cycle.

- Reverse current is detected (MAX17613A only).

- Thermal shutdown is active.

- R<sub>SETI</sub> is less than 1.5kΩ (max).

The other fault output \$\overline{UVOV}\$ goes low when input voltage falls below the UVLO threshold or rises above the OVLO threshold. Note that the UVLO fault has a debounce time of 16ms. This fault is removed 16ms after the input voltage has crossed the UVLO threshold. This debounce also elapses only at powerup. As a consequence, the \$\overline{UVOV}\$ pin fault signal is always asserted at power-up for at least 16ms.

The MAX17613C device has two open-drain fault outputs, FWD and REV. They require external pullup resistors to a DC supply. FWD goes low when any of the following conditions occur:

- Overcurrent duration exceeds the blanking time.

- Thermal shutdown is active.

- R<sub>SETI</sub> is less than 1.5kΩ (max).

- REV goes low when reverse current is detected.

#### **Thermal Shutdown Protection**

The device has the thermal shutdown feature to protect against overheating. The device turns off and the  $\overline{\text{FLAG}}$  (or  $\overline{\text{FWD}}$ ) pin asserts when the junction temperature exceeds T<sub>JC\_MAX</sub> (+155°C typ). The device exits thermal shutdown and resume normal operation after the junction temperature cools down by T<sub>JC\_HYS</sub> (15°C typ), except when in latchoff mode, the device remains latched off.

The thermal limit behaves similar to the current limit. In autoretry mode, the thermal limit works with the autoretry timer. When the device comes out of thermal limit, the part is turned on after the retry time. In latchoff mode, the device latches off until power or EN is cycled. In continuous mode, the device only disables while the temperature is over the limit. There is no blanking time for thermal protection.

## 4.5V to 60V, 3A Current-Limiter with OV, UV and Reverse Protection

#### **Applications Information**

#### **IN Capacitor**

A  $0.47\mu F$  capacitor from the IN pin to GND is recommended to hold input voltage during sudden load current changes.

#### Hot Plug-In at the IN terminal

In many system powering applications, an input-filtering capacitor is required to lower radiated emission and enhance ESD capability. In hot plug-in applications, parasitic cable inductance along with the input capacitor causes overshoot and ringing when a live power cable is connected to the input terminal.

This effect causes the protection device to see almost twice the applied voltage. A transient voltage suppressor (TVS) is often used in industrial applications to protect the system from these conditions. A TVS that is capable of limiting surge voltage to 60V (max) should be placed close to the input terminal for enhanced protection. The tolerated slew rate at the IN pins is 100V/µs (max).

#### **Input Hard Short to Ground**

In many system applications, an input short-circuit protection is required. The MAX17613A and MAX17613C devices detect reverse current entering at the OUT pin and flowing out of the IN pin, then turns off the internal FETs. The magnitude of reverse current depends on the inductance of input circuitry and any capacitance installed near the IN pins.

The devices can be damaged in case  $V_{IN}$  goes so negative that  $(V_{OUT} - V_{IN}) > 60V$ .

#### **OUT Capacitor**

The maximum capacitive load ( $C_{MAX}$  in  $\mu F$ ) that can be connected is a function of current-limit setting ( $I_{LIM}$  in mA), the startup time ( $t_{TSTART}$  in ms) and the input voltage.  $C_{MAX}$  is calculated using the following relationship:

$$C_{MAX} = \frac{I_{LIM} \times t_{TSTART}}{V_{IN}}$$

For example, for  $V_{IN}$  = 24V,  $t_{TSTART}$  = 60ms, and  $I_{LIM}$  = 1000mA,  $C_{MAX}$  equals 2500 $\mu$ F.

Output capacitor values in excess of  $C_{MAX}$  can trigger false overcurrent condition. Note that the above expression assumes no load current is drawn from the OUT pins. Any load current drawn would offset the capacitor charging current resulting in a larger charging period; hence, the possibility of a false overcurrent condition.

#### Hot Plug-In at the OUT terminal

In some applications, there might be a possibility of applying an external voltage at the OUT terminal of the devices with or without presence of input voltage. During these conditions, devices detect any reverse current entering at the OUT pin and flowing out of the IN pin and turn off the internal FETs. Parasitic cable inductance along with input and output capacitors cause overshoot and ringing when an external voltage is applied at the OUT terminal. This causes the protection devices to see up to twice the applied voltage, which can damage the devices. It is recommended to maintain overvoltages such that the voltages at the pins do not exceed the absolute maximum ratings. The tolerated slew rate at the OUT pins is 100V/µs (max).

#### **Output Freewheeling Diode for Inductive Hard Short to Ground**

In applications that require protection from a sudden short to ground with an inductive load or a long cable, a schottky diode between the OUT terminal and ground is recommended. This is to prevent a negative spike on the OUT due to the inductive kickback during a short-circuit event.

#### **Layout and Thermal Dissipation**

To optimize the switch response time to output short-circuit conditions, it is very important to keep all traces as short as possible to reduce the effect of undesirable parasitic inductance. Place input and output capacitors as close as possible to the device (no more than 5mm). The IN and OUT pins must be connected with wide short traces to the power bus. During normal operation, the power dissipation is small and the package temperature change is minimal.

Power dissipation under steady-state normal operation may be calculated as:

$$P_{(SS)} = (I_{OUT})^2 \times R_{ON}$$

Refer to the Electrical Characteristics table and Typical Operating Characteristics for RON values at various operating temperatures.

If the output is continuously shorted to ground at the maximum supply voltage, the switches with the autoretry option might not cause thermal shutdown detection to trip. Power dissipation in the devices operating in autoretry mode can be calculated using the following equation:

$$P_{(AVG)} = \frac{V_{IN(MAX)} \times I_{OUT(MAX)} \times (t_{START})}{t_{START} + t_{RETRY}}$$

Attention must be given to continuous current-limit mode when the power dissipation during a fault condition can

### 4.5V to 60V, 3A Current-Limiter with OV, UV and Reverse Protection

cause the device to reach the thermal shutdown threshold. Thermal vias from the exposed pad to the ground plane are highly recommended to increase system thermal capacitance while reducing the thermal resistance to ambient temperature.

#### **ESD Protection**

The devices are specified for ±15kV (HBM) typical ESD resistance on IN when IN is bypassed to ground with a 0.47µF low-ESR ceramic capacitor. No capacitor is required for ±2kV (HBM) typical ESD on IN. All the pins have a ±2kV (HBM) typical ESD protection.

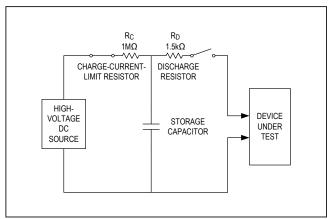

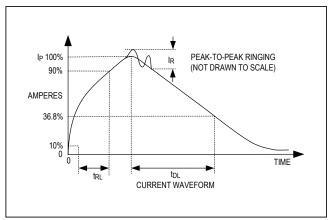

Figure 12 shows the Human Body Model and Figure 13 shows the current waveform it generates when discharged into a low impedance. This model consists of a 100pF capacitor charged to the ESD voltage of interest, which is then discharged into the device through a  $1.5k\Omega$  resistor.

Figure 12. Human Body ESD Test Model

Figure 13. Human Body Current Waveform

# 4.5V to 60V, 3A Current-Limiter with OV, UV and Reverse Protection

### **Ordering Information**

| PART           | TEMP RANGE      | PIN PACKAGE    | FEATURE DIFFERENCES                |

|----------------|-----------------|----------------|------------------------------------|

| MAX17613AATP+T | -40°C to +125°C | 20 TQFN-CU EP* | OV, UV, Reverse Voltage Protection |

| MAX17613BATP+T | -40°C to +125°C | 20 TQFN-CU EP* | OV,UV                              |

| MAX17613CATP+T | -40°C to +125°C | 20 TQFN-CU EP* | Reverse Voltage Protection         |

<sup>+</sup> Denotes a lead(Pb)-free/RoHS-compliant package.

T = Tape-and-reel.

<sup>\*</sup>EP = Exposed pad.

### 4.5V to 60V, 3A Current-Limiter with OV, UV and Reverse Protection

#### **Revision History**

| REVISION<br>NUMBER | REVISION DATE | DESCRIPTION     | PAGES<br>CHANGED |

|--------------------|---------------|-----------------|------------------|

| 0                  | 2/19          | Initial release | _                |

For pricing, delivery, and ordering information, please visit Maxim Integrated's online storefront at https://www.maximintegrated.com/en/storefront/storefront.html.

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.

OOO «ЛайфЭлектроникс" "LifeElectronics" LLC

ИНН 7805602321 КПП 780501001 P/C 40702810122510004610 ФАКБ "АБСОЛЮТ БАНК" (ЗАО) в г.Санкт-Петербурге К/С 3010181090000000703 БИК 044030703

Компания «Life Electronics» занимается поставками электронных компонентов импортного и отечественного производства от производителей и со складов крупных дистрибьюторов Европы, Америки и Азии.

С конца 2013 года компания активно расширяет линейку поставок компонентов по направлению коаксиальный кабель, кварцевые генераторы и конденсаторы (керамические, пленочные, электролитические), за счёт заключения дистрибьюторских договоров

#### Мы предлагаем:

- Конкурентоспособные цены и скидки постоянным клиентам.

- Специальные условия для постоянных клиентов.

- Подбор аналогов.

- Поставку компонентов в любых объемах, удовлетворяющих вашим потребностям.

- Приемлемые сроки поставки, возможна ускоренная поставка.

- Доставку товара в любую точку России и стран СНГ.

- Комплексную поставку.

- Работу по проектам и поставку образцов.

- Формирование склада под заказчика.

- Сертификаты соответствия на поставляемую продукцию (по желанию клиента).

- Тестирование поставляемой продукции.

- Поставку компонентов, требующих военную и космическую приемку.

- Входной контроль качества.

- Наличие сертификата ISO.

В составе нашей компании организован Конструкторский отдел, призванный помогать разработчикам, и инженерам.

Конструкторский отдел помогает осуществить:

- Регистрацию проекта у производителя компонентов.

- Техническую поддержку проекта.

- Защиту от снятия компонента с производства.

- Оценку стоимости проекта по компонентам.

- Изготовление тестовой платы монтаж и пусконаладочные работы.

Тел: +7 (812) 336 43 04 (многоканальный) Email: org@lifeelectronics.ru