# S1R72V17\*\*\* Technical Manual

#### NOTICE

No part of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not assume any liability of any kind arising out of any inaccuracies contained in this material or due to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as, medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright infringement of a third party. This material or portions thereof may contain technology or the subject relating to strategic products under the control of the Foreign Exchange and Foreign Trade Law of Japan and may require an export license from the Ministry of Economy, Trade and Industry or other approval from another government agency.

All other product names mentioned herein are trademarks and/or registered trademarks of their respective companies.

©SEIKO EPSON CORPORATION 2007, All rights reserved.

# **General Rules**

# **Scope of Application**

This specification applies to the USB2.0 Controller

"S1R72V17B00A\*\*\*/S1R72V17B00B\*\*\*/S1R72V17F00C\*\*\*" manufactured by the Semiconductor Operations Division of Seiko Epson Corporation.

# **Table of Contents**

| 1. Overv  | iew                                                          | . 1 |

|-----------|--------------------------------------------------------------|-----|

| 2. Featu  | res                                                          | . 2 |

| 3. Block  | Diagram                                                      | . 3 |

| 3.1       | Multi Transceiver Macro (MTM)                                | . 4 |

| 3.2       | Oscillator                                                   | . 4 |

| 3.3       | Device Serial Interface Engine (Device SIE)                  | . 4 |

| 3.4       | Host Serial Interface Engine (Host SIE)                      | . 4 |

| 3.5       | FIFO and FIFO Controller                                     | . 4 |

| 3.6       | CPU I/F Controller                                           | . 4 |

| 3.7       | DMA Controller                                               | . 4 |

| 3.8       | Test MUX                                                     | . 4 |

| 4. Pin La | ayout Diagram                                                | . 5 |

| 5. Pin D  | escription                                                   | .7  |

| 6. Funct  | ional Description                                            | 10  |

| 6.1       | Selection of USB Device/Host                                 | 10  |

| 6.1.1     | Selection of the USB Device/Host Functions                   | 10  |

| 6.1.2     | USB Port State Change Detection Status                       | 11  |

| 6.1       | .2.1 Example Usage of USB Port State Change Detection Status | 11  |

| 6         | 1.2.1.1 Device Port Change Status                            | 11  |

| 6         | 1.2.1.2 Host Port Change Status                              | 12  |

| 6.2       | USB Device Control                                           | 13  |

| 6.2.1     | Endpoints                                                    | 13  |

| 6.2.2     | Transactions                                                 | 15  |

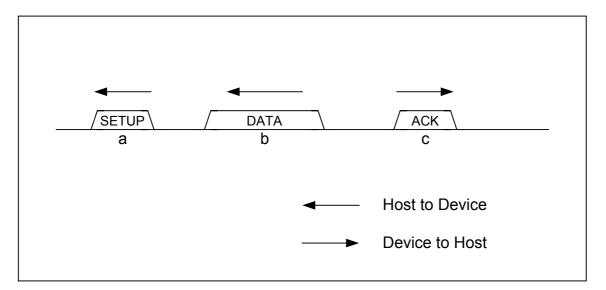

| 6.2       | .2.1 SETUP Transactions                                      | 17  |

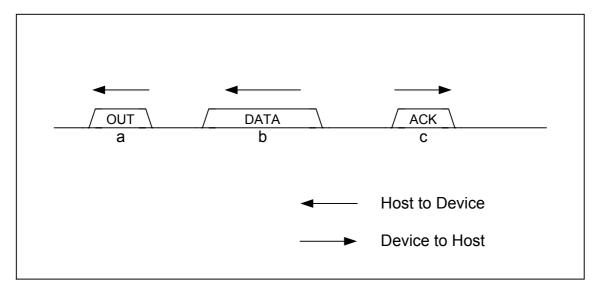

| 6.2       | .2.2 Bulk/Interrupt OUT Transactions                         | 18  |

| 6.2       | .2.3 Isochronous OUT Transaction                             | 19  |

| 6.2       | .2.4 Bulk/Interrupt IN Transactions                          | 20  |

| 6.2       | .2.5 Isochronous IN Transaction                              | 21  |

| 6.2       | .2.6 PING Transactions                                       | 21  |

| 6.2.3     | Control Transfers                                            | 22  |

| 6.2       | .3.1 Setup Stage                                             | 24  |

| 6.2       | .3.2 Data Stage and Status Stage                             | 24  |

| 6.2       | .3.3 Automatic Address Setup Function                        | 24  |

| 6.2.3.4  | Descriptor Reply Function                           | .25  |

|----------|-----------------------------------------------------|------|

| 6.2.4 B  | ulk Transfer and Interrupt Transfer                 | .25  |

| 6.2.5 D  | Data Flow                                           | 25   |

| 6.2.5.1  | OUT Transfer                                        | .25  |

| 6.2.5.2  | IN Transfer                                         | . 26 |

| 6.2.6 B  | ulk Only Support                                    | . 27 |

| 6.2.6.1  | CBW Support                                         | . 27 |

| 6.2.6.2  | CSW Support                                         | . 28 |

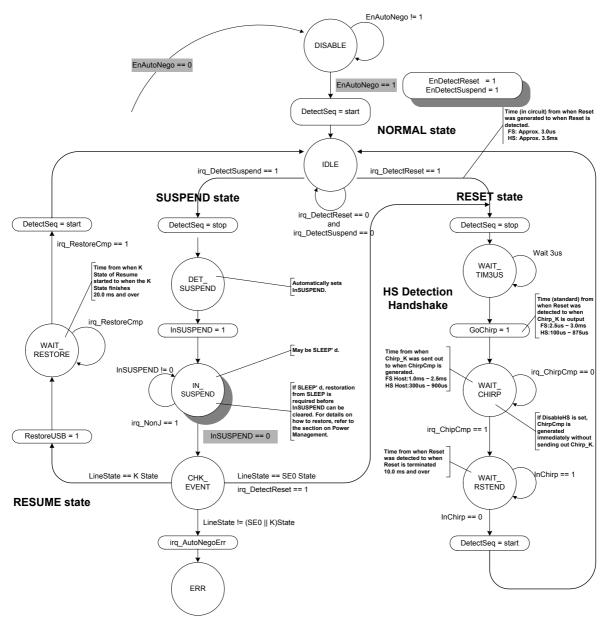

| 6.2.7 A  | uto Negotiation Function                            | . 29 |

| 6.2.7.1  | DISABLE                                             | . 30 |

| 6.2.7.2  | IDLE                                                | . 30 |

| 6.2.7.3  | WAIT_TIM3US                                         | . 30 |

| 6.2.7.4  | WAIT_CHIRP                                          | . 30 |

| 6.2.7.5  | WAIT_RSTEND                                         | . 31 |

| 6.2.7.6  | DET_SUSPEND                                         | . 31 |

| 6.2.7.7  | IN_SUSPEND                                          | . 31 |

| 6.2.7.8  | CHK_EVENT                                           | . 31 |

| 6.2.7.9  | WAIT_RESTORE                                        | . 31 |

| 6.2.7.10 | ERR                                                 | . 32 |

| 6.2.7.11 | Individual Description of Each Negotiation Function | . 32 |

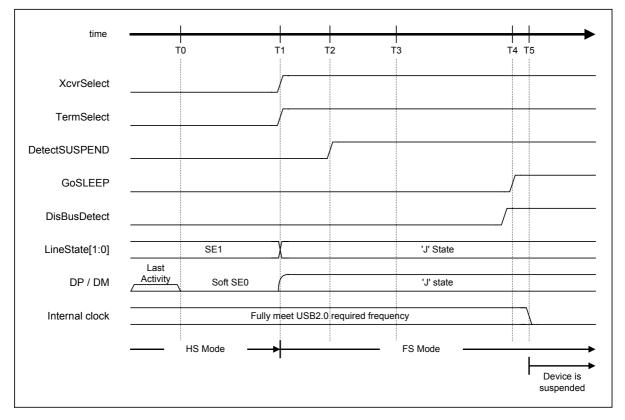

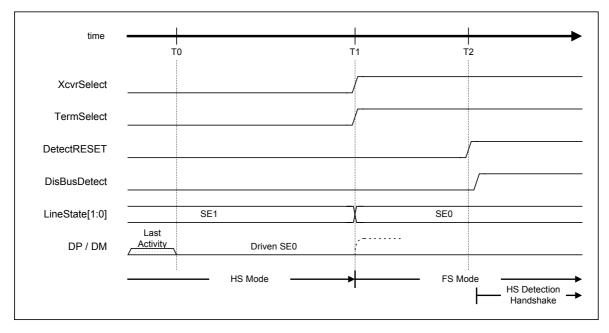

| 6.2.7.1  | 1.1 Suspend Detection (HS Mode)                     | . 32 |

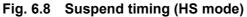

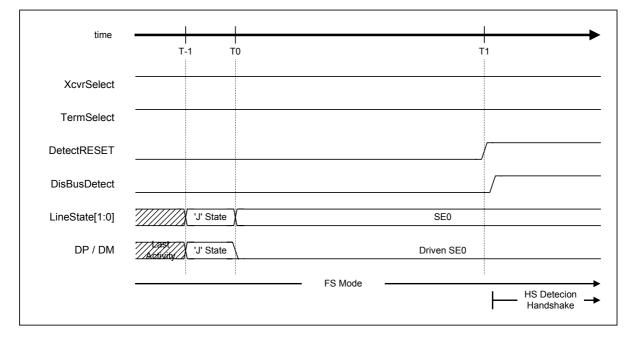

| 6.2.7.1  | 1.2 Suspend Detection (FS Mode)                     | . 34 |

| 6.2.7.1  | 1.3 Reset Detection (HS Mode)                       | . 36 |

| 6.2.7.1  | 1.4 Reset Detection (FS Mode)                       | . 37 |

| 6.2.7.1  | 1.5 HS Detection Handshaking                        | . 38 |

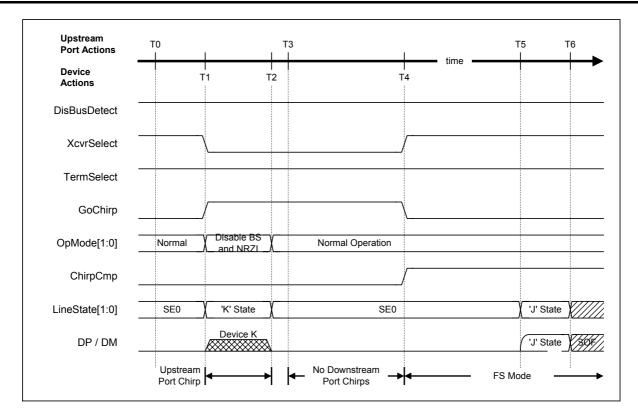

| 6.2.7    | .11.5.1 When Connected to an FS Downstream Port     | . 39 |

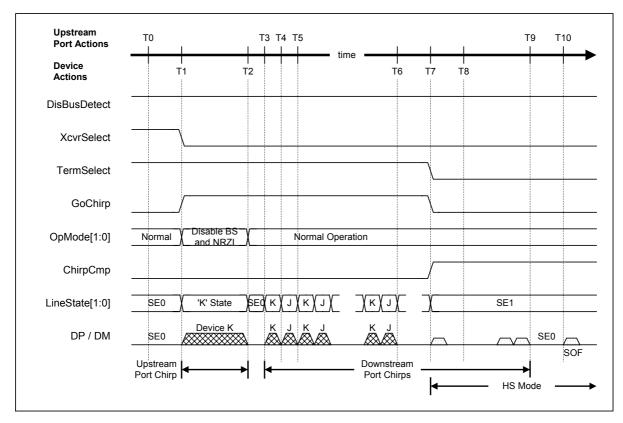

| 6.2.7    | .11.5.2 When Connected to an HS Downstream Port     | 41   |

| 6.2.7    | .11.5.3 When Reset during Sleep                     | .43  |

| 6.2.7.1  | 1.6 Issuance of Resume                              | 45   |

| 6.2.7.1  | 1.7 Detection of Resume                             | . 47 |

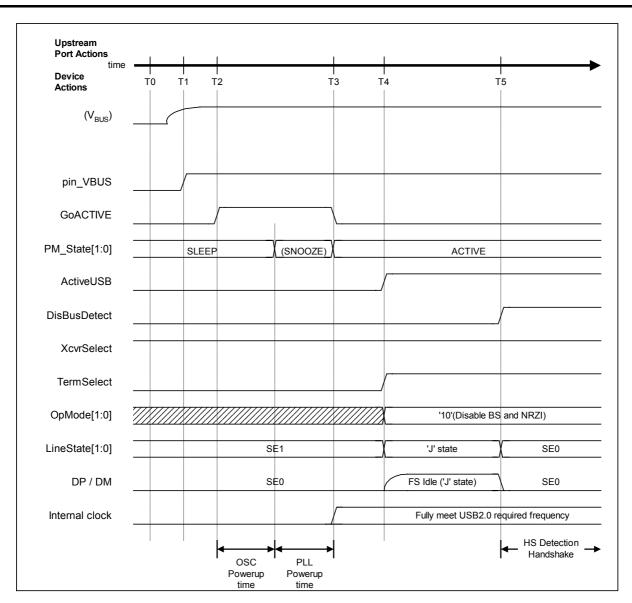

| 6.2.7.1  | 1.8 Insertion of USB Cable                          | . 49 |

| 6.3 USB  | Host Control                                        | 51   |

| 6.3.1 C  | Channels                                            | 51   |

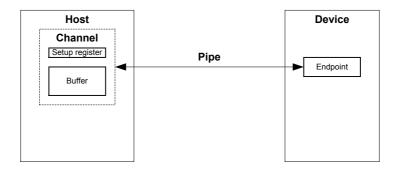

| 6.3.1.1  | Channel Overview                                    | . 51 |

| 6.3.1.2  | Control-only Channel                                | . 53 |

| 6.3.1.3  | General-purpose Channels                            | . 54 |

| 6.3.1.4  | Example for Using Channels                          | . 56 |

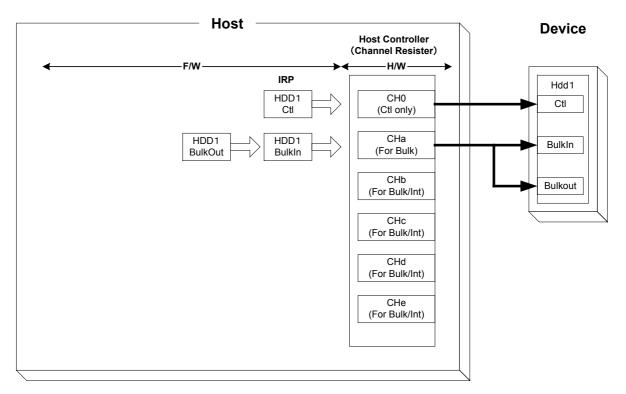

| 6.3.1.4  | .1 For One Storage Device Connected                 | . 56 |

EPSON

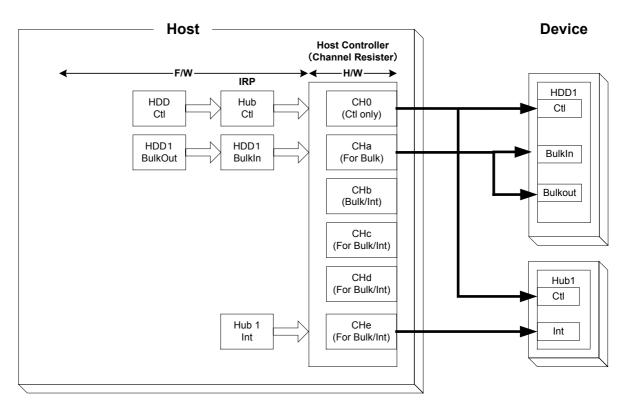

| 6.3.1   | .4.2 Co    | nnecting a Storage Device via a Hub                             | . 57 |

|---------|------------|-----------------------------------------------------------------|------|

| 6.3.2   | Schedulin  | ıg                                                              | . 58 |

| 6.3.3   | Transactio | ons                                                             | . 58 |

| 6.3.3.1 | SETUP      | Transactions                                                    | . 59 |

| 6.3.3.2 | Bulk OL    | JT Transaction                                                  | . 60 |

| 6.3.3.3 | Interrup   | t OUT Transaction                                               | . 61 |

| 6.3.3.4 | Bulk IN    | Transaction                                                     | . 62 |

| 6.3.3.5 | Interrup   | t IN Transaction                                                | . 63 |

| 6.3.3.6 | PING Tr    | ransaction                                                      | . 64 |

| 6.3.3.7 | Low-Sp     | eed (LS) Transaction                                            | . 65 |

| 6.3.3.8 | Split Tra  | insactions                                                      | . 67 |

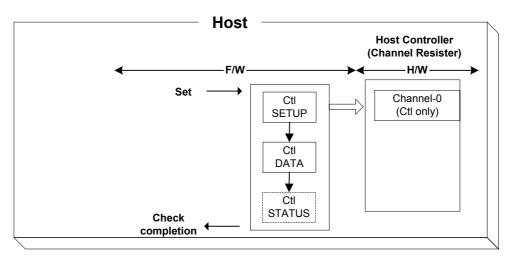

| 6.3.4   | Control Tr | ansfer                                                          | . 68 |

| 6.3.4.1 | Setup S    | itage                                                           | . 69 |

| 6.3.4.2 | Data Sta   | age and Status Stage                                            | . 69 |

| 6.3.4.3 | Control    | Transfer Support Function                                       | . 70 |

| 6.3.5   | Bulk and   | Interrupt Transfers                                             | . 73 |

| 6.3.6   | Data Flow  | /                                                               | . 73 |

| 6.3.6.1 | OUT Tra    | ansfer                                                          | . 73 |

| 6.3.6.2 | IN Trans   | sfer                                                            | . 74 |

| 6.3.7   | Zero-leng  | th Packet Auto Issue Function                                   | . 75 |

| 6.3.7.1 | Zero-ler   | ngth Packet Auto Issue Function in Bulk/Interrupt OUT Transfers | . 75 |

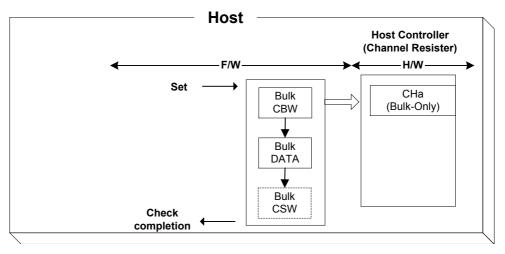

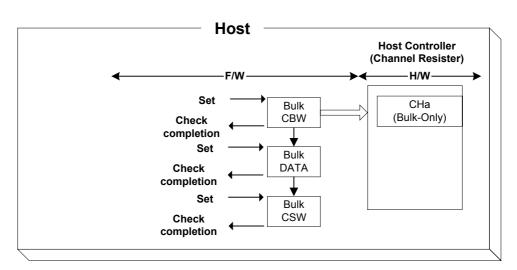

| 6.3.8   | Bulk Only  | Support Function                                                | . 75 |

| 6.3.9   | Host State | e Management Support Function                                   | . 80 |

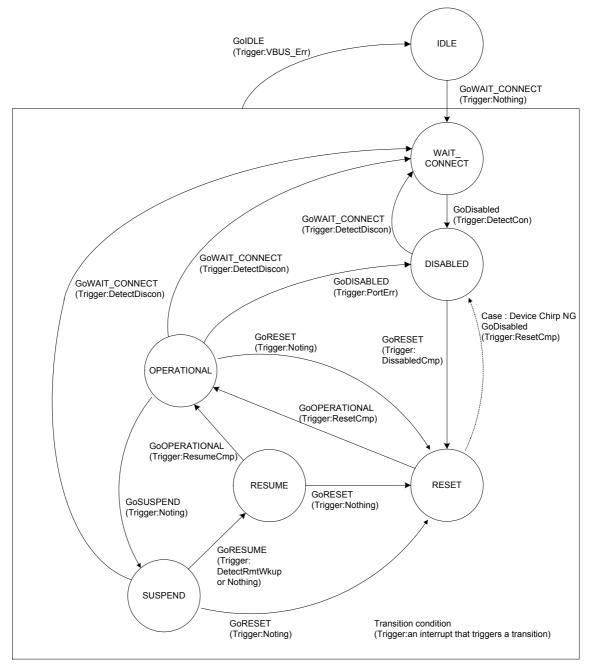

| 6.3.9.1 | Host Sta   | ates                                                            | . 80 |

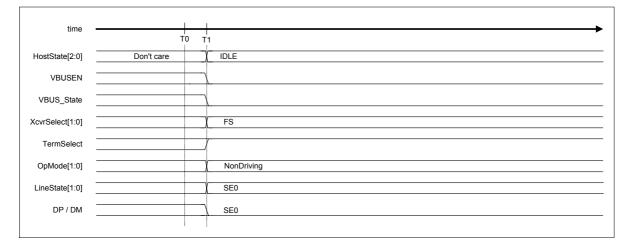

| 6.3.9   | .1.1 IDL   | .E                                                              | . 82 |

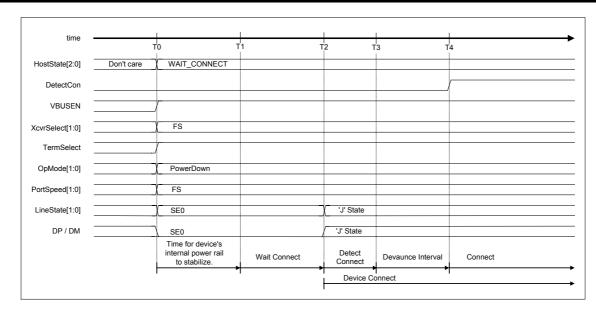

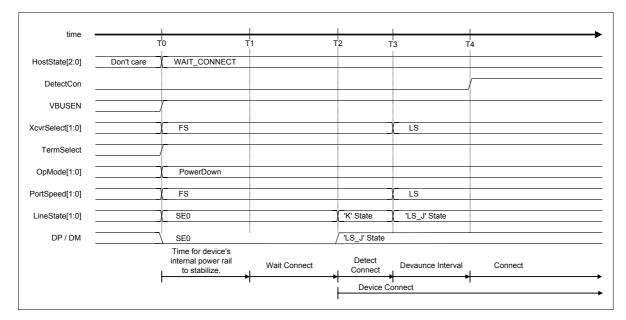

| 6.3.9   | .1.2 WA    | AIT_CONNECT                                                     | . 82 |

| 6.3.9   | .1.3 DIS   | SABLED                                                          | . 83 |

| 6.3.9   | .1.4 RE    | SET                                                             | . 83 |

| 6.3.9   | .1.5 OP    | PERATIONAL                                                      | . 85 |

| 6.3.9   | .1.6 SU    | SPEND                                                           | . 85 |

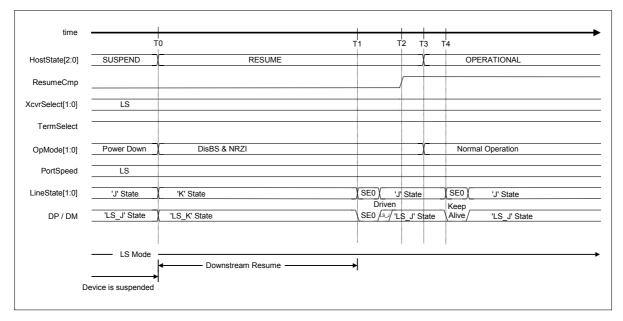

| 6.3.9   | .1.7 RE    | SUME                                                            | . 86 |

| 6.3.9.2 | Detectio   | on Functions                                                    | . 86 |

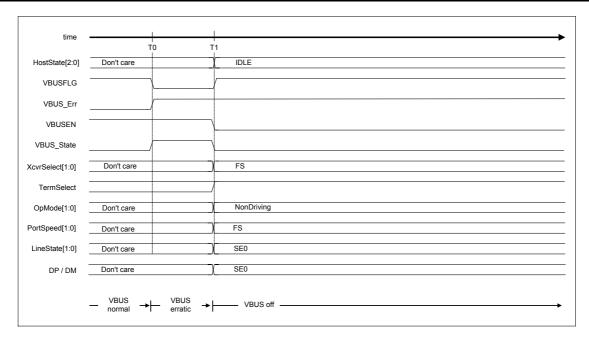

| 6.3.9   | .2.1 VB    | US Error Detection                                              | . 86 |

| 6.3.9   | .2.2 Dis   | connection Detection                                            | . 88 |

| 6.3     | .9.2.2.1   | When HS Device is Disconnected                                  | . 88 |

| 6.3     | .9.2.2.2   | When FS or LS Device is Disconnected                            | . 89 |

| 6.3.9   | .2.3 Re    | mote Wakeup Detection                                           |      |

| 6.3     | .9.2.3.1   | When HS Device is Connected                                     | . 90 |

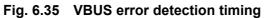

| 6.3.9.2.3.2     | When FS Device is Connected                                   |           |

|-----------------|---------------------------------------------------------------|-----------|

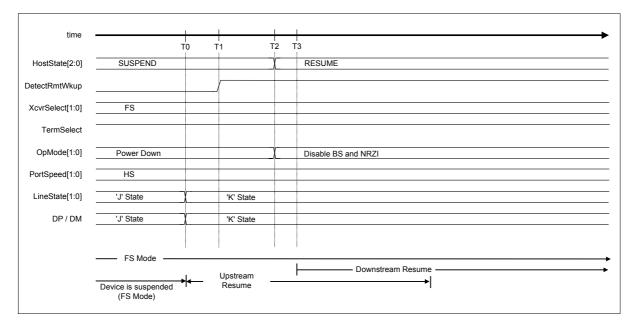

| 6.3.9.2.3.3     | When LS Device is Connected                                   |           |

| 6.3.9.2.4 De    | vice Chirp Detection Function                                 |           |

| 6.3.9.2.4.1     | When a Correct Device Chirp is Detected                       |           |

| 6.3.9.2.4.2     | When an Erratic Device Chirp is Detected                      |           |

| 6.3.9.2.5 Po    | rt Error Detection                                            |           |

| 6.3.9.3 Descrip | tion of Individual Host State Management Support Function     |           |

| 6.3.9.3.1 Go    | DIDLE                                                         |           |

| 6.3.9.3.2 Go    | WAIT_CONNECT                                                  |           |

| 6.3.9.3.2.1     | When FS Device is Connected                                   |           |

| 6.3.9.3.2.2     | When LS Device is Connected                                   | 101       |

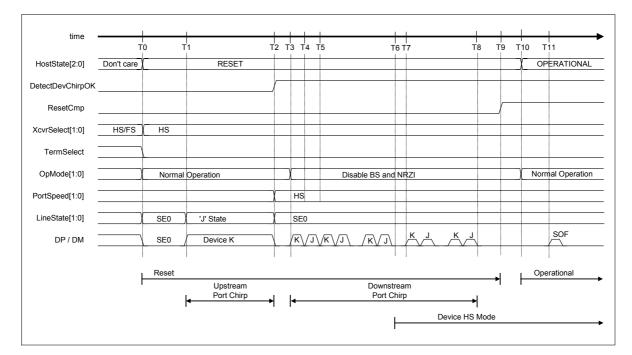

| 6.3.9.3.3 Go    | DISABLED                                                      | 103       |

| 6.3.9.3.3.1     | When HS Device is Connected                                   | 103       |

| 6.3.9.3.3.2     | When FS Device is Connected                                   | 105       |

| 6.3.9.3.3.3     | When LS Device is Connected                                   | 106       |

| 6.3.9.3.4 Go    | RESET                                                         | 107       |

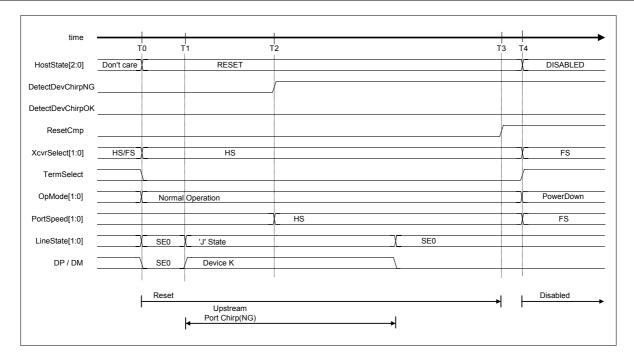

| 6.3.9.3.4.1     | Reset for an HS Device                                        | 107       |

| 6.3.9.3.4.2     | Erratic Device Chirp Detected                                 | 109       |

| 6.3.9.3.4.2.    | 1 When Chirp Complete Disable (H_NegoControl_1.DisChirpFinish | ) = 0 109 |

| 6.3.9.3.4.2.    | 2 When Chirp Complete Disable (H_NegoControl_1.DisChirpFinish | ) = 1111  |

| 6.3.9.3.4.3     | Reset for an FS Device                                        | 114       |

| 6.3.9.3.4.4     | Reset for an LS Device                                        | 116       |

| 6.3.9.3.5 Go    | OPERATIONAL                                                   | 117       |

| 6.3.9.3.6 Go    | SUSPEND                                                       | 118       |

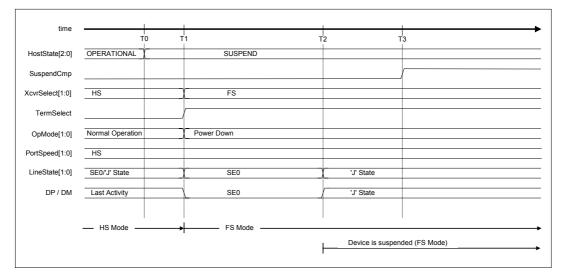

| 6.3.9.3.6.1     | When HS Device is Connected                                   | 118       |

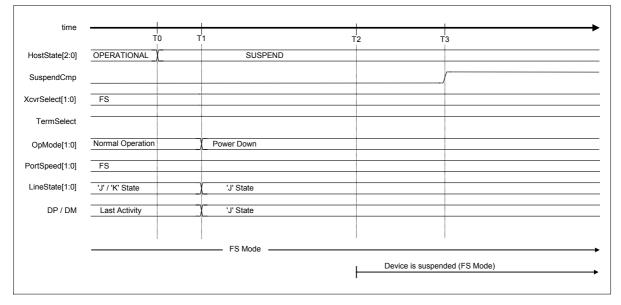

| 6.3.9.3.6.2     | When FS Device is Connected                                   | 120       |

| 6.3.9.3.6.3     | When LS Device is Connected                                   | 122       |

| 6.3.9.3.7 Go    | RESUME                                                        | 124       |

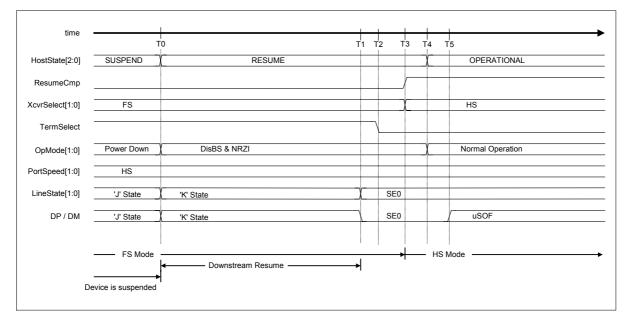

| 6.3.9.3.7.1     | When HS Device is Connected                                   | 124       |

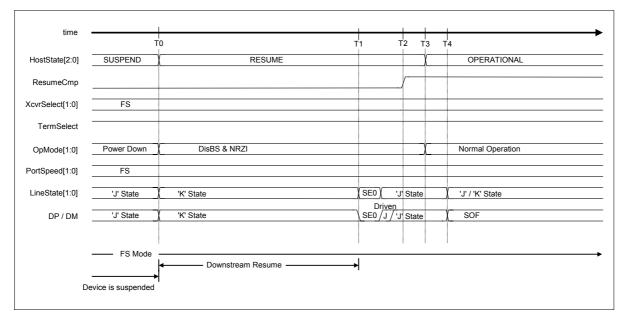

| 6.3.9.3.7.2     | When FS Device is Connected                                   | 126       |

| 6.3.9.3.7.3     | When LS Device is Connected                                   | 128       |

| 6.3.9.3.8 Go    | WAIT_CONNECTtoDIS                                             | 130       |

| 6.3.9.3.9 Go    | WAIT_CONNECTtoOP                                              | 131       |

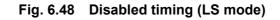

| 6.3.9.3.9.1     | When HS Device is Connected                                   | 131       |

| 6.3.9.3.9.2     | When FS or LS Device is Connected                             | 133       |

| 6.3.9.3.10 Go   | RESETtoOP                                                     | 135       |

| 6.3.9.3.10.1    | When HS Device is Connected                                   | 135       |

| 6.3.9.3.10.2    | When FS or LS Device is Connected                             | 136       |

|     | 6.3.9   | .3.11  | GoSUSPENDtoOP                                   | 137 |

|-----|---------|--------|-------------------------------------------------|-----|

|     | 6.3.9   | .3.12  | GoRESUMEtoOP                                    | 139 |

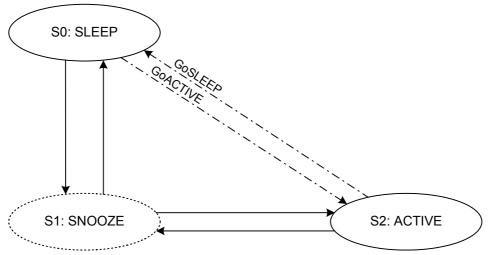

| 6.4 | Po      | wer Ma | anagement Function                              | 140 |

| 6.4 | .1      | SLEE   | P (Sleep)                                       | 141 |

| 6.4 | .2      | SNOC   | DZE (Snooze)                                    | 142 |

| 6.4 | .3      | ACTIV  | /E (Active)                                     | 142 |

| 6.4 | .4      | CPU_   | Cut Mode                                        | 142 |

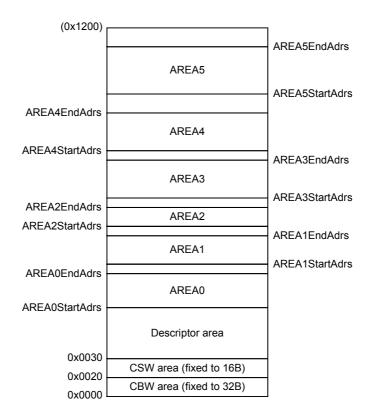

| 6.5 | FIF     | O Mar  | nagement                                        | 143 |

| 6.5 | 5.1     | FIFO   | Memory Map                                      | 143 |

| 6.5 | 5.2     | Descr  | iptor Area                                      | 144 |

| 6   | 6.5.2.1 | Writ   | ing Data into the Descriptor Area               | 145 |

| 6   | 6.5.2.2 | Exe    | cuting a Data Stage (IN) in the Descriptor Area | 145 |

| 6.5 | 5.3     | CBW    | Area                                            | 146 |

| 6   | 6.5.3.1 | CBV    | V Area (during USB Device Mode)                 | 146 |

| 6   | 6.5.3.2 | CB     | V Area (during USB Host Mode)                   | 146 |

| 6.5 | 5.4     | CSW    | Area                                            | 147 |

| 6   | 6.5.4.1 | CSV    | V Area (during USB Device Mode)                 | 147 |

| 6   | 6.5.4.2 | CSV    | N Area (during USB Host Mode)                   | 147 |

| 6.5 | 5.5     | Metho  | od for Accessing the FIFO                       | 147 |

| 6   | 6.5.5.1 | Met    | hod for Accessing the FIFO (RAM_Rd)             | 147 |

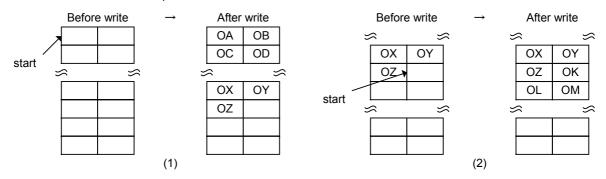

| 6   | 6.5.5.2 | Met    | hod for Accessing the FIFO (RAM_WrDoor)         | 148 |

| 6   | 6.5.5.3 | Met    | hod for Accessing the FIFO (Register Access)    | 148 |

| 6   | 6.5.5.4 | Met    | hod for Accessing the FIFO (DMA)                | 148 |

| 6   | 6.5.5.5 | Lim    | itations on FIFO Access                         | 149 |

| 6.6 | CP      | UIF    |                                                 | 150 |

| 6.6 | 5.1     | Mode   | Switching                                       | 150 |

| 6.6 | 5.2.    | Notes  | on Mode Switchover                              | 150 |

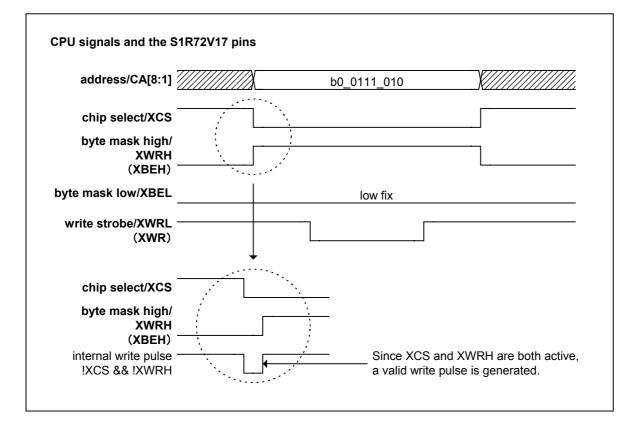

| 6   | 6.2.1   | . Whe  | en Using 16-bit BE Mode                         | 150 |

| 6   | 6.2.2   | . Whe  | en Using 8-bit Mode                             | 152 |

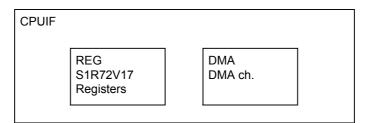

| 6.6 | 5.3     | Block  | Configuration                                   | 153 |

| 6   | 6.3.1   | REC    | G (S1R72V17 Registers)                          | 153 |

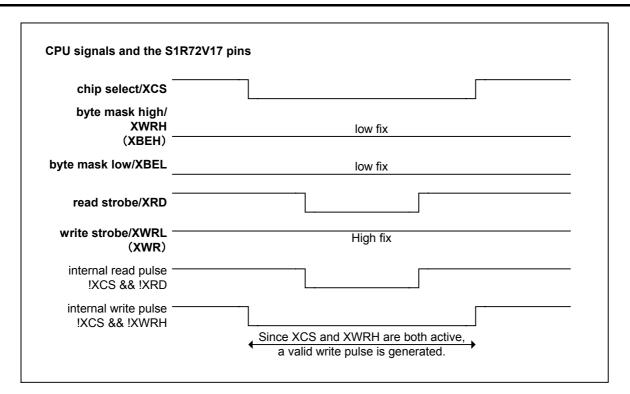

|     | 6.6.3   | .1.1   | Synchronous Register Access (Write)             | 153 |

|     | 6.6.3   | .1.2   | Synchronous Register Access (Read)              | 153 |

|     | 6.6.3   | .1.3   | FIFO Access (Write)                             | 154 |

|     | 6.6.3   | .1.4   | FIFO Access (Read)                              | 154 |

|     | 6.6.2   | .1.5   | Processing Odd Bytes in FIFO Access             | 155 |

|     | 6.6.2   | .1.6   | RAM_Rd Access                                   | 158 |

|     | 6.6.2   | .1.7   | Asynchronous Register Access (Write)            | 158 |

| 6.6.2        | .1.8    | Asynchronous Register Access (Read)             | . 158 |

|--------------|---------|-------------------------------------------------|-------|

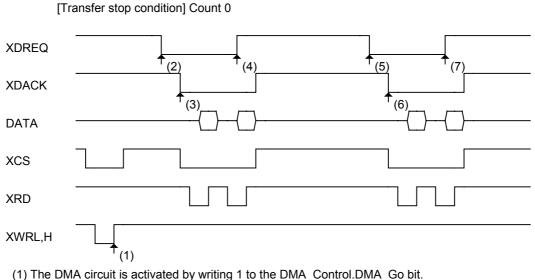

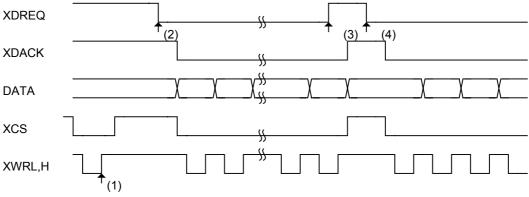

| 6.6.2.2      | DM      | A (DMA Channel)                                 | . 158 |

| 6.6.2        | .2.1    | Basic Functionality                             | . 158 |

| 6.6.2        | .2.2    | Pin Settings                                    | . 160 |

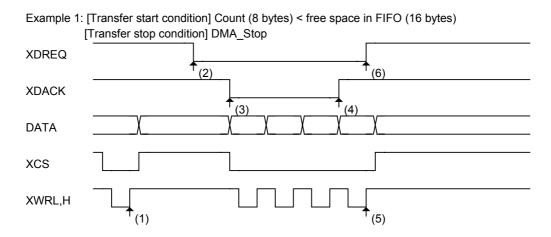

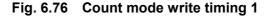

| 6.6.2        | .2.3    | Count Mode (Write)                              | . 160 |

| 6.6.2        | .2.4    | Count Mode (Read)                               | . 162 |

| 6.6.2        | .2.5    | Free-running Mode (Write)                       | . 163 |

| 6.6.2        | .2.6    | Free-running Mode (Read)                        | . 164 |

| 6.6.2        | .2.7    | REQ Assert Count Option (Write)                 | . 164 |

| 6.6.2        | .2.8    | REQ Assert Count Option (Read)                  | . 166 |

| 6.6.2        | .2.9    | FIFO Access Odd Bytes Processing in DMA         | . 166 |

| 7. Registers |         |                                                 | . 167 |

| 7.1 Dev      | vice/Ho | ost Shared Register Map                         | . 167 |

| 7.2 Dev      | vice Re | egister Map                                     | . 173 |

| 7.3 Hos      | st Regi | ister Map                                       | . 177 |

| 7.4 Det      | ailed [ | Description of Device/Host Shared Registers     | . 182 |

| 7.4.1        | 000h    | MainIntStat (Main Interrupt Status)             | . 182 |

| 7.4.2        | 001h    | USB_DeviceIntStat (USB Device Interrupt Status) | . 184 |

| 7.4.3        | 002h    | USB_HostIntStat (USB Host Interrupt Status)     | . 186 |

| 7.4.4        | 003h    | CPU_IntStat (CPU Interrupt Status)              | . 188 |

| 7.4.5        | 004h    | FIFO_IntStat (FIFO Interrupt Status)            | . 189 |

| 7.4.6        | 008h    | MainIntEnb (Main Interrupt Enable)              | . 190 |

| 7.4.7        | 009h    | USB_DeviceIntEnb (Device Interrupt Enable)      | . 191 |

| 7.4.8        | 00Ah    | USB_HostIntEnb (Host Interrupt Enable)          | . 192 |

| 7.4.9        | 00Bh    | CPU_IntEnb (CPU Interrupt Enable)               | . 193 |

| 7.4.10       | 00Ch    | FIFO_IntEnb (FIFO Interrupt Enable)             | . 194 |

| 7.4.11       | 010h    | RevisionNum (Revision Number)                   | . 195 |

| 7.4.12       | 011h    | ChipReset (Chip Reset)                          | . 196 |

| 7.4.13       | 012h    | PM_Control (Power Management Control)           | . 197 |

| 7.4.14       | 014h    | WakeupTim_H (Wakeup Time High)                  | . 199 |

| 7.4.15       | 015h    | WakeupTim_L (Wakeup Time Low)                   | . 199 |

| 7.4.16       | 016h    | H_USB_Control (Host USB Control )               | . 200 |

| 7.4.17       | 017h    | H_XcvrControl (Host Xcvr Control)               | . 201 |

| 7.4.18       | 018h    | D_USB_Status (Device USB Status)                | . 203 |

| 7.4.19       | 019h    | H_USB_Status (Host USB Status)                  | . 204 |

| 7.4.20       | 01Bh    | MTM_Config (Multi Transceiver Macro Config)     | . 205 |

| 7.4.21       | 01Fh    | HostDeviceSel (Host Device Select)              | . 206 |

| 7.4.22       | 020h    | FIFO_Rd_0 (FIFO Read 0)                         | . 207 |

| 7.4.23 | 021h FIFO_Rd_1 (FIFO Read 1)                  |     |

|--------|-----------------------------------------------|-----|

| 7.4.24 | 022h FIFO_Wr_0(FIFO Write 0)                  | 208 |

| 7.4.25 | 023h FIFO_Wr_1(FIFO Write 1)                  | 208 |

| 7.4.26 | 024h FIFO_RdRemain_H (FIFO Read Remain High)  | 209 |

| 7.4.27 | 025h FIFO_RdRemain_L (FIFO Read Remain Low)   | 209 |

| 7.4.28 | 026h FIFO_WrRemain_H (FIFO Write Remain High) | 210 |

| 7.4.29 | 027h FIFO_WrRemain_L (FIFO Write Remain Low)  | 210 |

| 7.4.30 | 028h FIFO_ByteRd(FIFO Byte Read)              | 211 |

| 7.4.31 | 030h RAM_RdAdrs_H (RAM Read Address High)     | 212 |

| 7.4.32 | 031h RAM_RdAdrs_L (RAM Read Address Low)      | 212 |

| 7.4.33 | 032h RAM_RdControl (RAM Read Control)         | 213 |

| 7.4.34 | 035h RAM_RdCount (RAM Read Counter)           | 214 |

| 7.4.35 | 038h RAM_WrAdrs_H (RAM Write Address High)    | 215 |

| 7.4.36 | 039h RAM_WrAdrs_L (RAM Write Address Low)     | 215 |

| 7.4.37 | 03Ah RAM_WrDoor_0 (RAM Write Door 0)          | 216 |

| 7.4.38 | 03Bh RAM_WrDoor_1 (RAM Write Door 1)          | 216 |

| 7.4.39 | 040h RAM_Rd_00 (RAM Read 00)                  | 217 |

| 7.4.40 | 041h RAM_Rd_01 (RAM Read 01)                  | 217 |

| 7.4.41 | 042h RAM_Rd_02 (RAM Read 02)                  | 217 |

| 7.4.42 | 043h RAM_Rd_03 (RAM Read 03)                  | 217 |

| 7.4.43 | 044h RAM_Rd_04 (RAM Read 04)                  | 217 |

| 7.4.44 | 045h RAM_Rd_05 (RAM Read 05)                  | 217 |

| 7.4.45 | 046h RAM_Rd_06 (RAM Read 06)                  | 217 |

| 7.4.46 | 047h RAM_Rd_07 (RAM Read 07)                  | 217 |

| 7.4.47 | 048h RAM_Rd_08 (RAM Read 08)                  | 217 |

| 7.4.48 | 049h RAM_Rd_09 (RAM Read 09)                  | 217 |

| 7.4.49 | 04Ah RAM_Rd_0A (RAM Read 0A)                  | 217 |

| 7.4.50 | 04Bh RAM_Rd_0B (RAM Read 0B)                  | 217 |

| 7.4.51 | 04Ch RAM_Rd_0C (RAM Read 0C)                  | 217 |

| 7.4.52 | 04Dh RAM_Rd_0D (RAM Read 0D)                  | 217 |

| 7.4.53 | 04Eh RAM_Rd_0E (RAM Read 0E)                  | 217 |

| 7.4.54 | 04Fh RAM_Rd_0F (RAM Read 0F)                  | 217 |

| 7.4.55 | 050h RAM_Rd_10 (RAM Read 10)                  | 217 |

| 7.4.56 | 051h RAM_Rd_11 (RAM Read 11)                  | 217 |

| 7.4.57 | 052h RAM_Rd_12 (RAM Read 12)                  | 217 |

| 7.4.58 | 053h RAM_Rd_13 (RAM Read 13)                  | 217 |

| 7.4.59 | 054h RAM_Rd_14 (RAM Read 14)                  | 217 |

| 7.4.60 | 055h RAM_Rd_15 (RAM Read 15)                  | 217 |

|        |                                               |     |

| 7.4.61 | 056h RAM_Rd_16 (RAM Read 16)                            | 217 |

|--------|---------------------------------------------------------|-----|

| 7.4.62 | 057h RAM_Rd_17 (RAM Read 17)                            | 217 |

| 7.4.63 | 058h RAM_Rd_18 (RAM Read 18)                            | 217 |

| 7.4.64 | 059h RAM_Rd_19 (RAM Read 19)                            | 217 |

| 7.4.65 | 05Ah RAM_Rd_1A (RAM Read 1A)                            | 217 |

| 7.4.66 | 05Bh RAM_Rd_1B (RAM Read 1B)                            | 217 |

| 7.4.67 | 05Ch RAM_Rd_1C (RAM Read 1C)                            | 217 |

| 7.4.68 | 05Dh RAM_Rd_1D (RAM Read 1D)                            | 217 |

| 7.4.69 | 05Eh RAM_Rd_1E (RAM Read 1E)                            | 217 |

| 7.4.70 | 05Fh RAM_Rd_1F (RAM Read 1F)                            | 218 |

| 7.4.71 | 061h DMA_Config (DMA Config)                            | 219 |

| 7.4.72 | 062h DMA_Control (DMA Control)                          | 221 |

| 7.4.73 | 064h DMA_Remain_H (DMA FIFO Remain High)                | 222 |

| 7.4.74 | 065h DMA_Remain_L (DMA0 FIFO Remain Low)                | 222 |

| 7.4.75 | 068h DMA_Count_HH (DMA Transfer Byte Counter High/High) | 223 |

| 7.4.76 | 069h DMA_Count_HL (DMA Transfer Byte Counter High/Low)  | 223 |

| 7.4.77 | 06Ah DMA_Count_LH (DMA Transfer Byte Counter Low/High)  | 223 |

| 7.4.78 | 06Bh DMA_Count_LL (DMA Transfer Byte Counter Low/Low)   | 223 |

| 7.4.79 | 06Ch DMA_RdData_0 (DMA Read Data 0)                     | 225 |

| 7.4.80 | 06Dh DMA_RdData_1 (DMA Read Data 1)                     | 225 |

| 7.4.81 | 06Eh DMA_WrData_0 (DMA Write Data 0)                    | 226 |

| 7.4.82 | 06Fh DMA_WrData_1 (DMA Write Data 1)                    | 226 |

| 7.4.83 | 071h ModeProtect(Mode Protection)                       | 227 |

| 7.4.84 | 073h ClkSelect (Clock Select)                           | 228 |

| 7.4.85 | 075h CPU_Config (CPU Configuration)                     | 229 |

| 7.4.86 | 077h CPU_ChgEndian(CPU Change Endian)                   | 231 |

| 7.4.87 | 080h AREA0StartAdrs_H (AREA0 Start Address High)        | 232 |

| 7.4.88 | 081h AREA0StartAdrs_L (AREA0 Start Address Low)         | 232 |

| 7.4.89 | 082h AREA0EndAdrs_H (AREA0 End Address High)            | 233 |

| 7.4.90 | 083h AREA0EndAdrs_L (AREA0 End Address Low)             | 233 |

| 7.4.91 | 084h AREA1StartAdrs_H (AREA1 Start Address High)        | 234 |

| 7.4.92 | 085h AREA1StartAdrs_L (AREA1 Start Address Low)         | 234 |

| 7.4.93 | 086h AREA1EndAdrs_H (AREA1 End Address High)            | 235 |

| 7.4.94 | 087h AREA1EndAdrs_L (AREA1 End Address Low)             | 235 |

| 7.4.95 | 088h AREA2StartAdrs_H (AREA2 Start Address High)        | 236 |

| 7.4.96 | 089h AREA2StartAdrs_L (AREA2 Start Address Low)         | 236 |

| 7.4.97 | 08Ah AREA2EndAdrs_H (AREA2 End Address High)            | 237 |

| 7.4.98 | 08Bh AREA2EndAdrs_L (AREA2 End Address Low)             | 237 |

|        |                                                         |     |

| 7.4.99  | 08Ch AREA3StartAdrs_H (AREA3 Start Address High)                |     |

|---------|-----------------------------------------------------------------|-----|

| 7.4.100 | 08Dh AREA3StartAdrs_L (AREA3 Start Address Low)                 |     |

| 7.4.101 | 08Eh AREA3EndAdrs_H (AREA3 End Address High)                    |     |

| 7.4.102 | 08Fh AREA3EndAdrs_L (AREA3 End Address Low)                     |     |

| 7.4.103 | 090h AREA4StartAdrs_H (AREA4 Start Address High)                |     |

| 7.4.104 | 091h AREA4StartAdrs_L (AREA4 Start Address Low)                 |     |

| 7.4.105 | 092h AREA4EndAdrs_H (AREA4 End Address High)                    |     |

| 7.4.106 | 093h AREA4EndAdrs_L (AREA4 End Address Low)                     |     |

| 7.4.107 | 094h AREA5StartAdrs_H (AREA5 Start Address High)                |     |

| 7.4.108 | 095h AREA5StartAdrs_L (AREA5 Start Address Low)                 |     |

| 7.4.109 | 096h AREA5EndAdrs_H (AREA5 End Address High)                    |     |

| 7.4.110 | 097h AREA5EndAdrs_L (AREA5 End Address Low)                     |     |

| 7.4.111 | 09Fh AREAnFIFO_Clr (AREAn FIFO Clear)                           | 244 |

| 7.4.112 | 0A0h AREA0Join_0 (AREA0 Join 0)                                 | 245 |

| 7.4.113 | 0A1h AREA0Join_1 (AREA0 Join 1)                                 | 246 |

| 7.4.114 | 0A2h AREA1Join_0 (AREA1 Join 0)                                 | 248 |

| 7.4.115 | 0A3h AREA1Join_1 (AREA1 Join 1)                                 | 249 |

| 7.4.116 | 0A4h AREA2Join_0 (AREA2 Join 0)                                 | 251 |

| 7.4.117 | 0A5h AREA2Join_1 (AREA2 Join 1)                                 | 252 |

| 7.4.118 | 0A6h AREA3Join_0 (AREA3 Join 0)                                 | 254 |

| 7.4.119 | 0A7h AREA3Join_1 (AREA3 Join 1)                                 | 255 |

| 7.4.120 | 0A8h AREA4Join_0 (AREA4 Join 0)                                 | 257 |

| 7.4.121 | 0A9h AREA4Join_1 (AREA4 Join 1)                                 | 258 |

| 7.4.122 | 0AAh AREA5Join_0 (AREA5 Join 0)                                 | 260 |

| 7.4.123 | 0ABh AREA5Join_1 (AREA5 Join 1)                                 | 261 |

| 7.4.124 | 0AEh ClrAREAnJoin_0 (Clear AREA n Join 0)                       | 263 |

| 7.4.125 | 0AFh ClrAREAnJoin_1 (Clear AREA n Join 1)                       | 264 |

| 7.5 De  | tailed Description of Device Registers                          | 265 |

| 7.5.1   | 0Bh D_SIE_IntStat (Device SIE Interrupt Status)                 | 265 |

| 7.5.2   | 0Bh D_BulkIntStat (Device Bulk Interrupt Status)                | 267 |

| 7.5.3   | 0Bh D_EPrIntStat (Device EPr Interrupt Status)                  | 268 |

| 7.5.4   | 0B5h D_EP0IntStat (Device EP0 Interrupt Status)                 | 270 |

| 7.5.5   | 0B6h D_EPaIntStat (Device EPa Interrupt Status)                 | 272 |

| 7.5.6   | 0B7h D_EPbIntStat (Device EPb Interrupt Status)                 | 274 |

| 7.5.7   | 0B8h D_EPcIntStat (D_EPc Interrupt Status)                      |     |

| 7.5.8   | 0B9h D_EPdIntStat (D_EPd Interrupt Status)                      | 278 |

| 7.5.9   | 0BAh D_EPeIntStat (D_EPe Interrupt Status)                      |     |

| 7.5.10  | 0BCh D_AlarmIN_IntStat_H (Device AlarmIN Interrupt Status High) | 282 |

|         |                                                                 |     |

| 7 5 44           |                                                                                                    | 000 |

|------------------|----------------------------------------------------------------------------------------------------|-----|

| 7.5.11           | 0BDh D_AlarmIN_IntStat_L (Device AlarmIN Interrupt Status Low)                                     |     |

| 7.5.12<br>7.5.13 | 0BEh D_AlarmOUT_IntStat_H (Device AlarmOUT Interrupt Status High)                                  |     |

| 7.5.13           | 0BFh D_AlarmOUT_IntStat_L (Device AlarmOUT Interrupt Status Low)                                   |     |

| 7.5.14           | 0C0h D_SIE_IntEnb (Device SIE Interrupt Enable)                                                    |     |

| 7.5.15           | 0C3h D_BulkIntEnb (Device Bulk Interrupt Enable)<br>0C4h D_EPrIntEnb (Device EPr Interrupt Enable) |     |

| 7.5.10           | 0C4h D_EPrintenb (Device EPrinterrupt Enable)                                                      |     |

| 7.5.17           | _ 、 、 ,                                                                                            |     |

| 7.5.10           | 0C6h D_EPaIntEnb (DeviceEPa Interrupt Enable)                                                      |     |

| 7.5.19           | 0C7h D_EPbIntEnb (Device EPb Interrupt Enable)                                                     |     |

| 7.5.20           | C8h D_EPcIntEnb (Device EPc Interrupt Enable)                                                      |     |

| 7.5.21           | 0C9h D_EPdIntEnb (Device EPd Interrupt Enable)                                                     |     |

| 7.5.22           | 0CAh D_EPeIntEnb (Device EPe Interrupt Enable)                                                     |     |

|                  | 0CCh D_AlarmIN_IntEnb_H (Device AlarmIN Interrupt Enable High)                                     |     |

| 7.5.24           | 0CDh D_AlarmIN_IntEnb_L (Device AlarmIN Interrupt Enable Low)                                      |     |

| 7.5.25           | 0CEh D_AlarmOUT_IntEnb_H (Device AlarmOUT Interrupt Enable High)                                   |     |

| 7.5.26           | 0CFh D_AlarmOUT_IntEnb_L (Device AlarmOUT Interrupt Enable Low)                                    |     |

| 7.5.27           | 0D0h D_NegoControl (Device Nego Control)                                                           |     |

| 7.5.28<br>7.5.29 | 0D3h D_XcvrControl (Device Xcvr Control)<br>0D4h D USB Test (Device USB Test)                      |     |

| 7.5.29           | 0D6h D_EPnControl (Device Endpoint Control)                                                        |     |

| 7.5.30           | 0D8h D_BulkOnlyControl (Device BulkOnly Control)                                                   |     |

| 7.5.31           | 0D9h D_BulkOnlyConfig (Device BulkOnly Configuration)                                              |     |

| 7.5.32           | 0E0h D EP0SETUP 0 (Device EP0 SETUP 0)                                                             |     |

|                  | 0E1h D_EP0SETUP_1 (Device EP0 SETUP 1)                                                             |     |

| 7.5.34           | 0E2h D EP0SETUP 2 (Device EP0 SETUP 2)                                                             |     |

| 7.5.35<br>7.5.36 | 0E3h D_EP0SETUP_3 (Device EP0 SETUP 3)                                                             |     |

| 7.5.30           | 0E4h D_EP0SETUP_4 (Device EP0 SETUP 4)                                                             |     |

| 7.5.38           | 0E5h D_EP0SETUP_5 (Device EP0 SETUP 5)                                                             |     |

| 7.5.39           | 0E6h D_EP0SETUP_6 (Device EP0 SETUP 6)                                                             |     |

| 7.5.40           | 0E7h D_EP0SETUP_7 (Device EP0 SETUP 7)                                                             |     |

| 7.5.40           | 0E8h D_USB_Address (Device USB Address)                                                            |     |

| 7.5.42           | 0EAh D_SETUP_Control(Device SETUP Control)                                                         |     |

| 7.5.43           | 0EEh D_FrameNumber_H (Device FrameNumber High)                                                     |     |

| 7.5.44           | 0EFh D_FrameNumber_L (Device FrameNumber Low)                                                      |     |

| 7.5.45           | 0F0h D_EP0MaxSize (Device EP0 Max Packet Size)                                                     |     |

| 7.5.46           | 0F1h D_EP0Control (Device EP0 Control)                                                             |     |

| 7.5.40           | 0F2h D_EP0ControlIN (Device EP0 Control IN)                                                        |     |

| 7.5.48           | 0F3h D_EP0ControlOUT (Device EP0 Control OUT)                                                      |     |

| 7.0.40           |                                                                                                    | 513 |

| 7.5.49 | 0F8h D_EPaMaxSize_H (Device EPa Max Packet Size High)               | 315 |

|--------|---------------------------------------------------------------------|-----|

| 7.5.50 | 0F9h D_EPaMaxSize_L (Device EPa Max Packet Size Low)                | 315 |

| 7.5.51 | 0FAh D_EPaConfig (Device EPa Configuration)                         | 316 |

| 7.5.52 | 0FCh D_EPaControl (Device EPa Control)                              | 318 |

| 7.5.53 | 100h D_EPbMaxSize_H (Device EPb Max Packet Size High)               | 320 |

| 7.5.54 | 101h D_EPbMaxSize_L (Device EPb Max Packet Size Low)                | 320 |

| 7.5.55 | 102h D_EPbConfig (Devie EPb Configuration)                          | 321 |

| 7.5.56 | 104h D_EPbControl (Device EPb Control)                              | 323 |

| 7.5.57 | 108h D_EPcMaxSize_H (Device EPc Max Packet Size High)               | 325 |

| 7.5.58 | 109h D_EPcMaxSize_L (Device EPc Max Packet Size Low)                | 325 |

| 7.5.59 | 10Ah D_EPcConfig (Device EPc Configuration)                         | 326 |

| 7.5.60 | 10Ch D_EPcControl (Device EPc Control)                              | 328 |

| 7.5.61 | 110h D_EPdMaxSize_H (Device EPd Max Packet Size High)               | 330 |

| 7.5.62 | 111h D_EPdMaxSize_L (Device EPd Max Packet Size Low)                | 330 |

| 7.5.63 | 112h D_EPdConfig (Device EPd Configuration)                         | 331 |

| 7.5.64 | 114h D_EPdControl (Device EPd Control)                              | 333 |

| 7.5.65 | 118h D_EPeMaxSize_H (Device EPe Max Packet Size High)               | 335 |

| 7.5.66 | 119h D_EPeMaxSize_L (Device EPe Max Packet Size Low)                | 335 |

| 7.5.67 | 11Ah D_EPeConfig (Device EPe Configuration)                         | 336 |

| 7.5.68 | 11Ch D_EPeControl (Device EPe Control)                              | 338 |

| 7.5.69 | 120h D_DescAdrs_H (Device Descriptor Address High)                  | 340 |

| 7.5.70 | 121h D_DescAdrs_L (Device Descriptor Address Low)                   | 340 |

| 7.5.71 | 122h D_DescSize_H (Device Descriptor Size High)                     | 341 |

| 7.5.72 | 123h D_DescSize_L (Device Descriptor Size Low)                      | 341 |

| 7.5.73 | 126h D_EP_DMA_Ctrl (Device EP DMA Control)                          | 342 |

| 7.5.74 | 128h D_EnEP_IN_H (Device Enable Endpoint-IN High)                   | 343 |

| 7.5.75 | 129h D_EnEP_IN_L (Device Enable Endpoint-IN Low)                    | 343 |

| 7.5.76 | 12Ah D_EnEP_OUT_H (Device Enable Endpoint-IN High)                  | 344 |

| 7.5.77 | 12Bh D_EnEP_OUT_L (Device Enable Endpoint-IN Low)                   | 344 |

| 7.5.78 | 12Ch D_EnEP_IN_H (Device Enable Endpoint-IN High)                   | 345 |

| 7.5.79 | 12Dh D_EnEP_IN_L (Device Enable Endpoint-IN Low)                    | 345 |

| 7.5.80 | 12Eh D_EnEP_OUT_ISO_H (Device Enable Endpoint-OUT Isochronous High) | 346 |

| 7.5.81 | 12Fh D_EnEP_OUT_ISO_L (Device Enable Endpoint-OUT Isochronous Low)  | 346 |

| 7.6 De | tailed Description of Host Registers                                | 347 |

| 7.6.1  | 140h H_SIE_IntStat_0(Host SIE Interrupt Status 0)                   | 347 |

| 7.6.2  | 141h H_SIE_IntStat_1(SIE Host Interrupt Status 1)                   | 349 |

| 7.6.3  | 143h H_FrameIntStat(Host Frame Interrupt Status )                   | 351 |

| 7.6.4  | 144h H_CHrIntStat (Host CHr Interrupt Status)                       | 352 |

|        |                                                                     |     |

| 7.6.5  | 145h H_CH0IntStat (Host CH0 Interrupt Status)                  |     |

|--------|----------------------------------------------------------------|-----|

| 7.6.6  | 146h H_CHaIntStat (Host CHa Interrupt Status)                  |     |

| 7.6.7  | 147h H_CHbIntStat (Host CHb Interrupt Status)                  |     |

| 7.6.8  | 148h H_CHcIntStat (Host CHc Interrupt Status)                  |     |

| 7.6.9  | 149h H_CHdIntStat (Host CHd Interrupt Status)                  |     |

| 7.6.10 | 14Ah H_CHeIntStat (Host CHe Interrupt Status)                  |     |

| 7.6.11 | 150h H_SIE_IntEnb_0 (Host SIE Interrupt Enable)                |     |

| 7.6.12 | 151h H_SIE_IntEnb_1(SIE Host Interrupt Enable 1)               |     |

| 7.6.13 | 152h Reserved                                                  |     |

| 7.6.14 | 153h H_FrameIntEnb(Host Frame Interrupt Enable )               | 370 |

| 7.6.15 | 154h H_CHrIntEnb(Host CHr Interrupt Enable)                    |     |

| 7.6.16 | 155h H_CH0IntEnb(Host CH0 Interrupt Enable)                    | 372 |

| 7.6.17 | 156h H_CHaIntEnb (Host CHa Interrupt Enable)                   | 373 |

| 7.6.18 | 157h H_CHbIntEnb (Host CHb Interrupt Enable)                   | 374 |

| 7.6.19 | 158h H_CHcIntEnb (Host CHc Interrupt Enable)                   | 375 |

| 7.6.20 | 159h H_CHdIntEnb (Host CHd Interrupt Enable)                   | 376 |

| 7.6.21 | 15Ah H_CHeIntEnb (Host CHe Interrupt Enable)                   | 377 |

| 7.6.22 | 160h H_NegoControl_0 (Host NegoControl 0)                      | 378 |

| 7.6.23 | 162h H_NegoControl_1 (Host NegoControl 1)                      | 380 |

| 7.6.24 | 164h H_USB_Test (Host USB_Test)                                | 381 |

| 7.6.25 | 170h H_CH0SETUP_0 (Host CH0 SETUP 0)                           | 383 |

| 7.6.26 | 171h H_CH0SETUP_1 (Host CH0 SETUP 1)                           | 383 |

| 7.6.27 | 172h H_CH0SETUP_2 (Host CH0 SETUP 2)                           | 383 |

| 7.6.28 | 173h H_CH0SETUP_3 (Host CH0 SETUP 3)                           | 383 |

| 7.6.29 | 174h H_CH0SETUP_4 (Host CH0 SETUP 4)                           | 383 |

| 7.6.30 | 175h H_CH0SETUP_5 (Host CH0 SETUP 5)                           | 383 |

| 7.6.31 | 176h H_CH0SETUP_6 (Host CH0 SETUP 6)                           | 383 |

| 7.6.32 | 177h H_CH0SETUP_7 (Host CH0 SETUP 7)                           | 383 |

| 7.6.33 | 17Eh H_FrameNumber_H (Host FrameNumber High)                   | 384 |

| 7.6.34 | 17Fh H_FrameNumber_L (Host FrameNumber Low)                    | 384 |

| 7.6.35 | 180h H_CH0Config_0(Host Channel 0 Configuration0)              | 385 |

| 7.6.36 | 181h H_CH0Config_1(Host Channel 0 Configuration1)              | 387 |

| 7.6.37 | 183h H_CH0MaxPktSize (Host Channel 0 Max Packet Size)          | 388 |

| 7.6.38 | 186h H_CH0TotalSize_H (Host Channel 0 Total Size High)         | 389 |

| 7.6.39 | 187h H_CH0TotalSize_L (Host Channel 0 Total Size Low)          | 389 |

| 7.6.40 | 188h H_CH0HubAdrs (Host Channel 0 Hub Address)                 | 390 |

| 7.6.41 | 189h H_CH0FuncAdrs (Host Channel 0 Function Address)           | 391 |

| 7.6.42 | 18Bh CTL_SupportControl (Host ControlTransfer Support Control) | 392 |

|        |                                                                |     |

| 7.6.43 | 18Eh H_CH0ConditionCode (Host Channel 0 Condition Code)                                     | 394 |

|--------|---------------------------------------------------------------------------------------------|-----|

| 7.6.44 | 190h H_CHaConfig_0(Host Channel a Configuration0)                                           | 396 |

| 7.6.45 | 191h H_CHaConfig_1(Host Channel a Configuration1)                                           | 398 |

| 7.6.46 | 192h H_CHaMaxPktSize_H (Host Channel a Max Packet Size High)                                | 399 |

| 7.6.47 | 193h H_CHaMaxPktSize_L (Host Channel a Max Packet Size Low)                                 | 399 |

| 7.6.48 | 194h H_CHaHubAdrs (Host Channel a Hub Address)                                              | 400 |

| 7.6.49 | 195h H_CHaTotalSize_HL (Host Channel a Total Size High-Low)                                 | 400 |

| 7.6.50 | 196h H_CHaTotalSize_LH (Host Channel a Total Size Low-High)                                 | 400 |

| 7.6.51 | 197h H_CHaTotalSize_LL (Host Channel a Total Size Low-Low)                                  | 400 |

| 7.6.52 | 198h H_CHaHubAdrs (Host Channel a Hub Address)                                              | 402 |

| 7.6.53 | 199h H_CHaFuncAdrs (Host Channel a Function Address)                                        | 403 |

| 7.6.54 | 19Ah H_CHaBO_SupporotCtl (Host CHa Bulk Only Transfer Supporot Control)                     | 404 |

| 7.6.55 | 19Bh H_CHaBO_CSW_RcvDataSize<br>(Host CHa Bulk Only Transfer Support CSW Receive Data Size) | 406 |

| 7.6.56 | 19Ch H_ChaBQ_OUT_EP_Ctl (Host CHa Bulk Only Transfer Support OUT Endpoint Control)          |     |

| 7.6.57 | 19Dh H_ChaBO_IN_EP_Ctl<br>(Host CHa Bulk Only Transfer Support IN Endpoint Control)         | 408 |

| 7.6.58 | 19Eh H_CHaConditionCode (Channel a Condition Code)                                          | 409 |

| 7.6.59 | 1A0h H_CHbConfig_0(Host Channel b Configuration0)                                           | 411 |

| 7.6.60 | 1A1h H_CHbConfig_1(Host Channel b Configuration1)                                           | 413 |

| 7.6.61 | 1A2h H_CHbMaxPktSize_H (Host Channel b Max Packet Size High)                                | 414 |

| 7.6.62 | 1A3h H_CHbMaxPktSize_L (Host Channel b Max Packet Size Low)                                 | 414 |

| 7.6.63 | 1A4h H_ChbTotalSize_HH (Host Channel b Total Size High-High)                                | 415 |

| 7.6.64 | 1A5h H_CHbTotalSize_HL (Host Channel b Total Size High-Low)                                 | 415 |

| 7.6.65 | 1A6h H_CHbTotalSize_LH (Host Channel b Total Size Low-High)                                 | 415 |

| 7.6.66 | 1A7h H_CHbTotalSize_LL (Host Channel b Total Size Low-Low)                                  | 415 |

| 7.6.67 | 1A8h H_CHbHubAdrs (Host Channel b Hub Address)                                              | 417 |

| 7.6.68 | 1A9h H_CHbFuncAdrs (Host Channel b Function Address)                                        | 418 |

| 7.6.69 | 1AAh CHbInterval_H(Channel b Interval High)                                                 | 419 |

| 7.6.70 | 1ABh CHbInterval_L(Channel b Interval Low)                                                  | 419 |

| 7.6.71 | 1AEh H_CHbConditionCode (Host Channel b Condition Code)                                     | 420 |

| 7.6.72 | 1B0h H_CHcConfig_0(Host Channel c Configuration0)                                           | 422 |

| 7.6.73 | 1B1h H_CHcConfig_1(Host Channel c Configuration1)                                           | 424 |

| 7.6.74 | 1B2h H_CHcMaxPktSize_H (Host Channel c Max Packet Size High)                                | 425 |

| 7.6.75 | 1B3h H_CHcMaxPktSize_L (Host Channel c Max Packet Size Low)                                 | 425 |

| 7.6.76 | 1B4h H_CHcTotalSize_HH (Host Channel c Total Size High-High)                                | 426 |

| 7.6.77 | 1B5h H_CHcTotalSize_HL (Host Channel c Total Size High-Low)                                 | 426 |

| 7.6.78 | 1B6h H_CHcTotalSize_LH (Host Channel c Total Size Low-High)                                 | 426 |

|        |                                                                                             |     |

| 7.6.79    | 9 1B7h H_CHcTotalSize_LL (Host Channel c Total Size Low-Low)    | 426 |

|-----------|-----------------------------------------------------------------|-----|

| 7.6.8     | 1B8h H_CHcHubAdrs (Host Channel c Hub Address)                  | 428 |

| 7.6.8     | 1 1B9h H_CHcFuncAdrs (Host Channel c Function Address)          | 429 |

| 7.6.82    | 2 1BAh H_CHcInterval_H(Host Channel c Interval High)            | 430 |

| 7.6.8     | 3 1BBh H_CHcInterval_L(Host Channel c Interval Low)             | 430 |

| 7.6.84    | 1BEh H_CHcConditionCode (Host Channel c Condition Code)         | 431 |

| 7.6.8     | 5 1C0h H_CHdConfig_0(Host Channel d Configuration0)             | 433 |

| 7.6.8     | 6 1C1h H_CHdConfig_1(Host Channel d Configuration1)             | 435 |

| 7.6.8     | 7 1C2h H_CHdMaxPktSize_H (Host Channel d Max Packet Size High)  | 436 |

| 7.6.8     | 1C3h H_CHdMaxPktSize_L (Host Channel d Max Packet Size Low)     | 436 |

| 7.6.8     | 9 1C4h H_CHdTotalSize_HH (Host Channel d Total Size High-High)  | 437 |

| 7.6.9     | 1C5h H_CHdTotalSize_HL (Host Channel d Total Size High-Low)     | 437 |

| 7.6.9     | 1 1C6h H_CHdTotalSize_LH (Host Channel d Total Size Low-High)   | 437 |

| 7.6.92    | 2 1C7h H_CHdTotalSize_LL (Host Channel d Total Size Low-Low)    | 437 |

| 7.6.9     | 3 1C8h H_CHdHubAdrs (Host Channel d Hub Address)                | 439 |

| 7.6.94    | 1C9h H_CHdFuncAdrs (Host Channel d Function Address)            | 440 |

| 7.6.9     | 5 1CAh H_CHdInterval_H(Host Channel d Interval High)            | 441 |

| 7.6.9     | 6 1CBh H_CHdInterval_L(Host Channel d Interval Low)             | 441 |

| 7.6.9     | 7 1CEh H_CHdConditionCode (Host Channel d Condition Code)       |     |

| 7.6.98    | 1D0h H_CHeConfig_0(Host Channel e Configuration0)               | 444 |

| 7.6.9     | 9 1D1h H_CHeConfig_1(Host Channel e Configuration1)             | 446 |

| 7.6.10    | 00 1D2h H_CHeMaxPktSize_H (Host Channel e Max Packet Size High) | 447 |

| 7.6.10    | 1D3h H_CHeMaxPktSize_L (Host Channel e Max Packet Size Low)     | 447 |

| 7.6.10    | 1D4h H_CHeTotalSize_HH (Host Channel e Total Size High-High)    | 448 |

| 7.6.10    | 1D5h H_CHeTotalSize_HL (Host Channel e Total Size High-Low)     | 448 |

| 7.6.10    | 1D6h H_CHeTotalSize_LH (Host Channel e Total Size Low-High)     | 448 |

| 7.6.1     | 1D7h H_CHeTotalSize_LL (Host Channel e Total Size Low-Low)      | 448 |

| 7.6.10    | 1D8h H_CHeHubAdrs (Host Channel e Hub Address)                  | 450 |

| 7.6.10    | 1D9h H_CHeFuncAdrs (Host Channel e Function Address)            | 451 |

| 7.6.10    | 1DAh H_CHeInterval_H(Host Channel e Interval High)              | 452 |

| 7.6.10    | 09 1DBh H_CHeInterval_L(Host Channel e Interval Low)            | 452 |

| 7.6.1     | 10 1DEh H_CHeConditionCode (Host Channel e Condition Code)      | 453 |

| . Electri | cal Characteristics                                             | 455 |

| 8.1       | Absolute Maximum Ratings                                        | 455 |

| 8.2       | Recommended Operating Conditions                                | 455 |

| 8.3       | D.C. Characteristics                                            | 456 |

| 8.4       | A.C. Characteristics                                            | 459 |

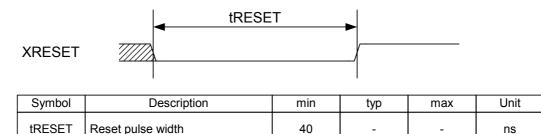

| 8.4.1     | RESET Timing                                                    | 459 |

8.

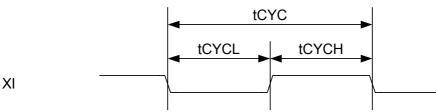

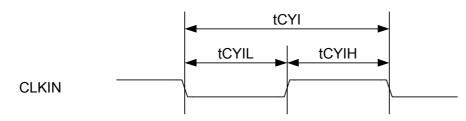

| 8.4.2     | Clock Timing                                  | 459 |

|-----------|-----------------------------------------------|-----|

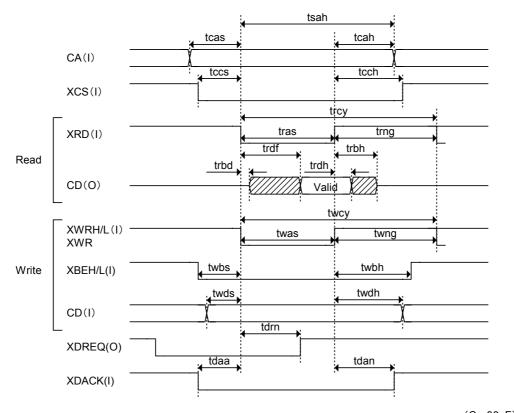

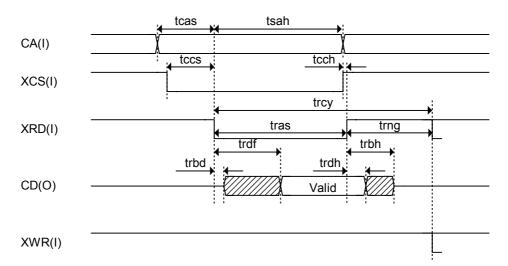

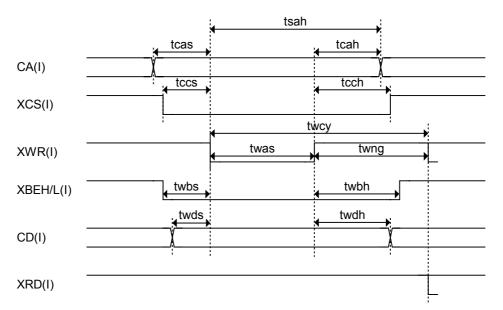

| 8.4.3     | CPU and DMA I/F Access Timing                 |     |

| 8.4.4     | USB I/F Timing                                |     |

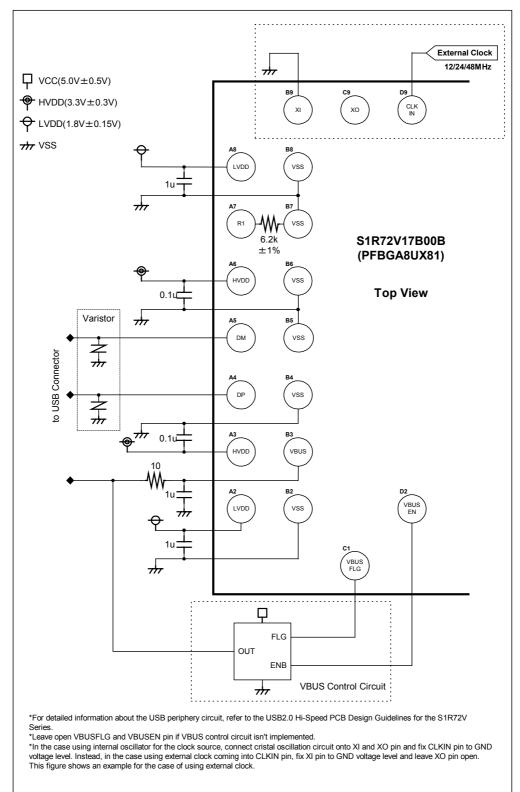

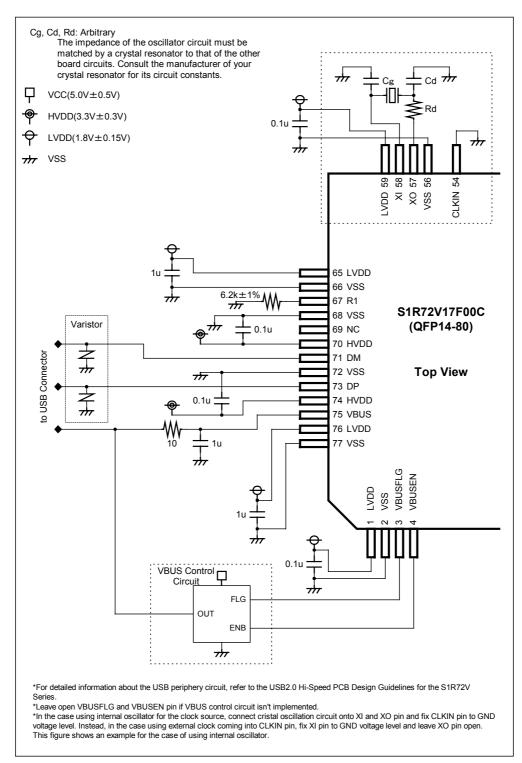

| 9. Conne  | ection Examples                               | 463 |

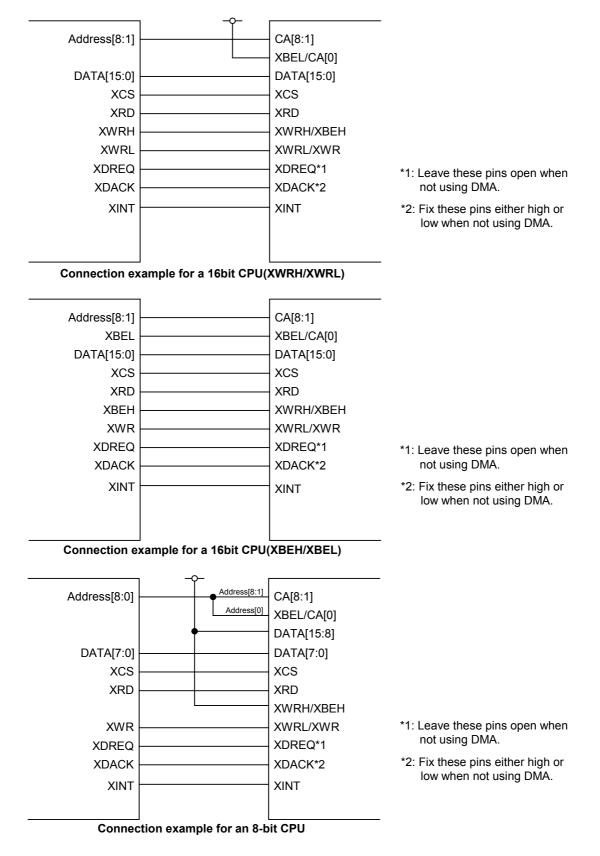

| 9.1       | CPU I/F Connection Example                    |     |

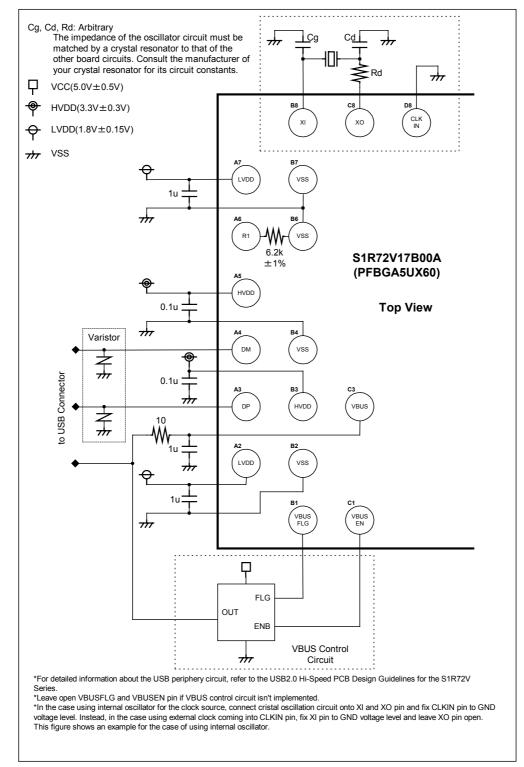

| 9.2       | USB I/F Connection Example                    |     |

| 9.2.1     | For the PFBGA5UX60                            |     |

| 9.2.2     | For the PFBGA8UX81                            |     |

| 9.2.3     | For the QFP14-80                              |     |

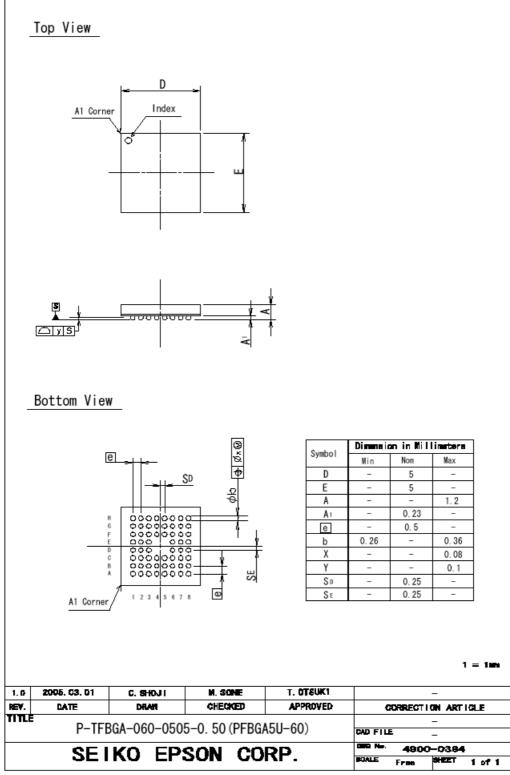

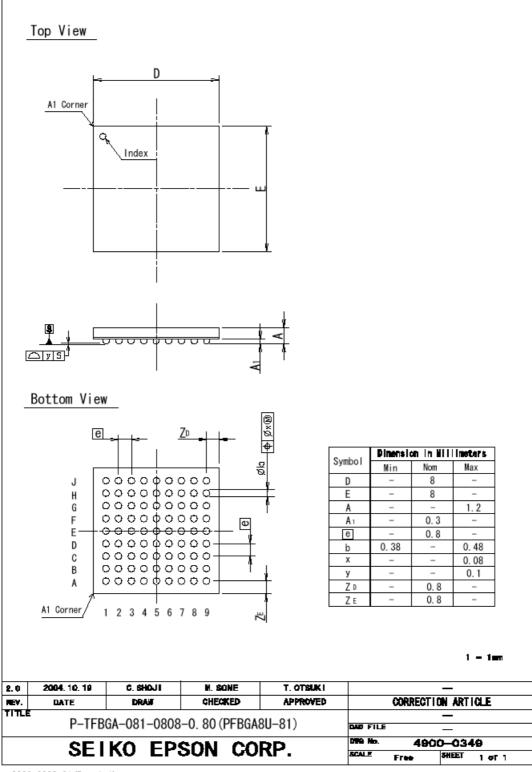

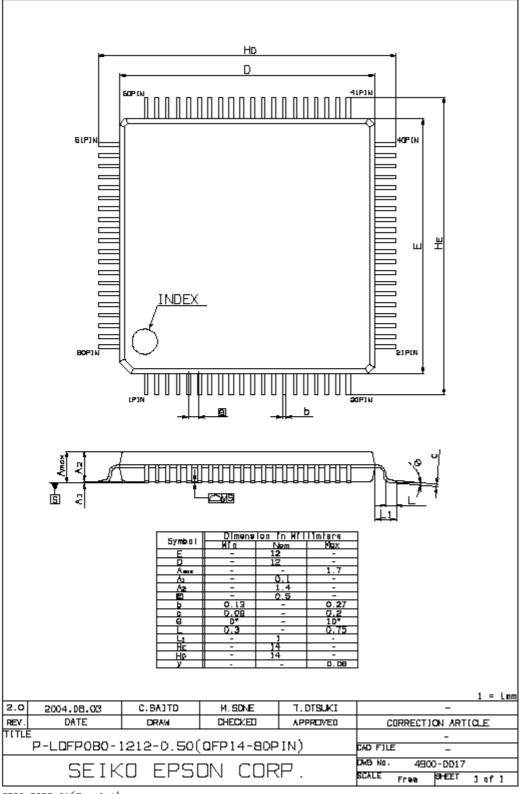

| 10. Packa | age Dimensions                                | 467 |

| 10.1      | PFBGA5UX60                                    |     |

| 10.2      | PFBGA8UX81                                    |     |

| 10.3      | QFP14-80                                      |     |

| Appendi   | x A. Connecting to Little Endian CPUs         | 470 |

| Appendi   | x B. Toggle Settings for Endpoint Changeover  |     |

| Appendi   | x C. SUSPEND during HOST High-Speed Operation |     |

| Appendi   | x D. About Responses to a SetAddress Request  |     |

| Appendi   | x E. Joining Endpoints/Channels to FIFO Areas |     |

# 1. Overview

The S1R72V17 is a USB host/device controller LSI that supports USB2.0-compliant high-speed mode. The host ports and device ports of this LSI are shared, allowing it to operate as a USB host or as a USB device when control is switched over.

This LSI also has characteristics suitable for portable equipment incorporating a DMA interface.

# 2. Features

<< USB2.0 device functions >>

- Supports HS <480 Mbps) and FS (12 Mbps) transfers.

- Includes FS/HS termination (external circuit unnecessary).

- Includes VBUS 5V interface (external circuit unnecessary).

- Supports control, bulk, interrupt, and isochronous transfers.

- Supports five general-purpose (Bulk, Interrupt, and Isochronous transfer) endpoints and Endpoint 0.

<< USB2.0 host functions >>

- Supports HS (480 Mbps), FS (12 Mbps), and LS (1.5 Mbps) transfers.

- Includes pull-down resistors for downstream ports (external circuit unnecessary).

- Includes HS termination (external circuit unnecessary).

- Supports control, bulk, and interrupt transfers. Channel structure

One (1) channel used exclusively for Control transfer

Includes five general-purpose (Bulk, and Interrupt transfer) channels.

- USB power switch interface.

<< CPU interface >>

- Accepts 16-bit or 8-bit wide general-purpose CPU interfaces.

- Incorporates one DMA channel (Multiword transfer).

- Big Endian (incorporating a bus swap function for Little Endian CPUs).

- Changeable interface voltages (3.3 V to 1.8 VTyp).

- Supports CPU\_Cut mode for reducing current consumption when the CPU is inactive.

<< Other >>

- Accepts a 12 MHz/24 MHz crystal resonator for clock input. (built-in Oscillator circuit and 1M Ωfeedback resistor)

- Dedicated pin for 12 MHz, 24 MHz, or 48 MHz clock input.

- Triple-power supply system: 3.3 V, 1.8 V and variable CPU interface power

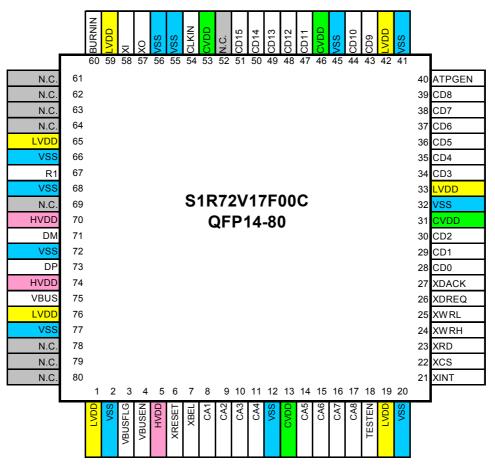

- Package type: PFBGA5UX60 (S1R72V17B00A\*\*\*) PFBGA8UX81 (S1R72V17B00B\*\*\*) QFP14-80 (S1R72V17F00C\*\*\*)

- Guaranteed operation temperature range: -40°C to 85°C

- \* This LSI is not designed to resist radiation.

# 3. Block Diagram

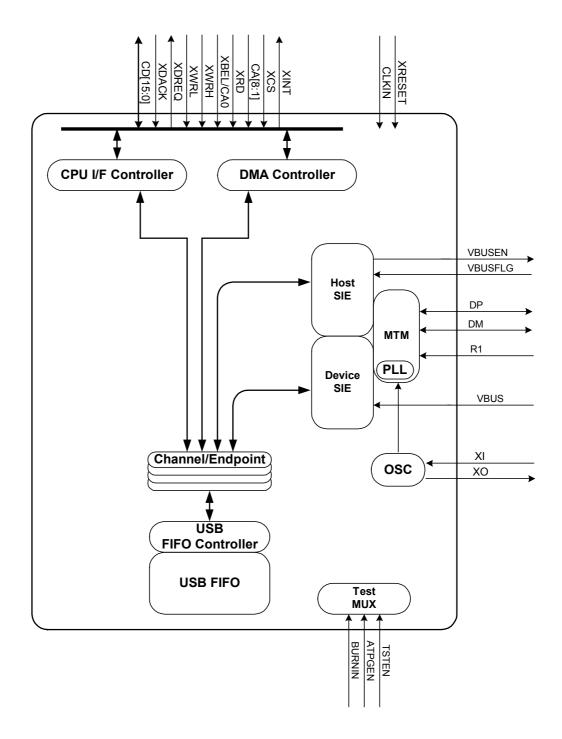

Fig. 3.1 General block diagram

### 3.1 Multi Transceiver Macro (MTM)

This USB 2.0 transceiver macro is shared by the USB host and USB device. Incorporating an analog circuit and high-speed logic circuit, it supports HS mode (480 Mbps) and FS mode (12 Mbps). LS mode (1.5 Mbps) is supported only for USB hosts.

Incorporates a transmitter, receiver, termination, etc. that together comprise a USB host/device interface.

Furthermore, it has a built-in PLL that generates a 480 MHz clock needed for HS transfer. Internal oscillator or incoming clock through CLKIN pin can be the clock source of the PLL.

# 3.2 Oscillator

The input clock accepts a 12 MHz or 24 MHz crystal resonator. A 1 MΩ feedback resistor is built-in.

# 3.3 Device Serial Interface Engine (Device SIE)

This block manages transactions and generates packets.

Furthermore, it controls bus events such as suspend, resume, and reset.

# 3.4 Host Serial Interface Engine (Host SIE)

This block schedules transactions, manages transactions, and generates packets.

Furthermore, it controls bus events such as suspend, resume, and reset.

It also detects connect/disconnect status and controls the VBUS (in cooperation with an external USB power switch).

# 3.5 FIFO and FIFO Controller

These blocks comprise a channel/endpoint buffer.

# 3.6 CPU I/F Controller

Controls the CPU interface timing, allowing registers to be accessed properly.

### 3.7 DMA Controller

Controls the DMA timing of the CPU interface, allowing access to FIFO. It incorporates one DMA channel.

### 3.8 Test MUX

This is a test circuit.

# 4. Pin Layout Diagram

|   | 1       | 2    | 3    | 4     | 5    | 6    | 7    | 8      |

|---|---------|------|------|-------|------|------|------|--------|

| Α | NC      | LVDD | DP   | DM    | HVDD | R1   | LVDD | BURNIN |

| в | VBUSFLG | VSS  | HVDD | VSS   | VSS  | VSS  | VSS  | XI     |

| с | VBUSEN  | HVDD | VBUS | CA1   | CA3  | CD15 | LVDD | хо     |

| D | XRESET  | XBEL | CA5  |       |      | CD13 | CVDD | CLKIN  |

| Е | CA2     | CA4  | XINT |       |      | CD4  | CD11 | CD14   |

| F | CA7     | CA8  | XWRH | XDACK | CD3  | CD7  | CD10 | CD12   |

| G | CA6     | LVDD | XRD  | XDREQ | CD1  | CD6  | VSS  | CD9    |

| н | TESTEN  | xcs  | XWRL | CD0   | CD2  | CD5  | CD8  | ATPGEN |

#### S1R72V17B00A/PFBGA5UX60 TOP View

Fig. 4.1 Pin Layout Diagram of the PFBGA5UX60 package

|   | 1       | 2      | 3      | 4     | 5     | 6    | 7      | 8      | 9     |

|---|---------|--------|--------|-------|-------|------|--------|--------|-------|

| Α | NC      | LVDD   | HVDD   | DP    | DM    | HVDD | R1     | LVDD   | NC    |

| в | VSS     | VSS    | VBUS   | VSS   | VSS   | VSS  | VSS    | VSS    | XI    |

| с | VBUSFLG | HVDD   | LVDD   | XBEL  | CA1   | CVDD | BURNIN | LVDD   | хо    |

| D | XRESET  | VBUSEN | CA3    | NC    | NC    | NC   | CD12   | CD15   | CLKIN |

| Е | CA2     | VSS    | CA4    | NC    | NC    | NC   | VSS    | CD13   | CD14  |

| F | CVDD    | CA5    | CA8    | NC    | NC    | NC   | CD7    | CD9    | CD11  |

| G | CA7     | CA6    | TESTEN | xcs   | XDACK | CD0  | CD4    | CD8    | CD10  |

| н | LVDD    | XINT   | XWRL   | XRD   | CD1   | CVDD | CD6    | ATPGEN | LVDD  |

| J | NC      | VSS    | XWRH   | XDREQ | CD2   | CD3  | CD5    | VSS    | NC    |

#### S1R72V17B00B/PFBGA8UX81 TOP View

Fig. 4.2 Pin Layout Diagram of the PFBGA8UX81 package

Fig. 4.3 Pin Layout Diagram of the QFP14.80 package

# 5. Pin Description

### OSC

| QFP14 | PFBGA8 | PFBGA5 | Name | I/O | RESET | Pin Type | Pin Description                                            |

|-------|--------|--------|------|-----|-------|----------|------------------------------------------------------------|

| 58    | B9     | B8     | XI   | IN  | -     | Analog   | Input for the internal oscillator circuit<br>12 MHz/24 MHz |

| 57    | C9     | C8     | ХО   | OUT | -     | Analog   | Output for the internal oscillator circuit                 |

To use the internal oscillator of the LSI, connect a crystal resonator and oscillator circuit to the XI and XO pins and attach the CLKIN pin to the GND potential. To use an external clock by feeding it from the CLKIN pin, attach the XI pin to the GND potential and leave the XO pin open.

#### TEST

| QFP14 | PFBGA8 | PFBGA5 | Name   | I/O | RESET | Pin Type | Pin Description      |

|-------|--------|--------|--------|-----|-------|----------|----------------------|

| 18    | G3     | H1     | TESTEN | IN  | (PD)  | PD       | Test pin (fixed low) |

| 40    | H8     | H8     | ATPGEN | IN  | (PD)  | PD       | Test pin (fixed low) |

| 60    | C7     | A8     | BURNIN | IN  | (PD)  | PD       | Test pin (fixed low) |

PD: Pull Down

PU: Pull Up

#### USB

| QFP14 | PFBGA8 | PFBGA5 | Name    | I/O | RESET | Pin Type      | Pin Description                                                                             |

|-------|--------|--------|---------|-----|-------|---------------|---------------------------------------------------------------------------------------------|

| 67    | A7     | A6     | R1      | IN  | -     | Analog        | Internal operation setup pin 6.2 k $\Omega$ ±1% resistor connected between this pin and VSS |

| 73    | A4     | A3     | DP      | BI  | Hi-Z  | Analog        | USB data line, Data+                                                                        |

| 71    | A5     | A4     | DM      | BI  | Hi-Z  | Analog        | USB data line, Data-                                                                        |

| 3     | C1     | B1     | VBUSFLG | IN  | (PU)  | Schmitt<br>PU | USB power switch fault detection signal<br>1: Normal; 0: Erratic                            |

| 4     | D2     | C1     | VBUSEN  | OUT | Lo    | 2mA           | USB power switch control signal                                                             |

| 75    | B3     | C3     | VBUS    | IN  | (PD)  | PD            | USB device bus detection signal                                                             |

PD: Pull Down

PU: Pull Up

| CPU I/F |        | <b>BF</b> |                |     |       | <b>.</b>         | _                                               |                    |            |

|---------|--------|-----------|----------------|-----|-------|------------------|-------------------------------------------------|--------------------|------------|

| QFP14   | PFBGA8 | PFBGA5    | Name           | I/O | RESET | Pin Type         |                                                 | Pin Description    | r          |

|         | _      |           |                |     | В     | us Mode ⇒        | 16bit Strobe<br>mode                            | 16bit BE<br>mode   | 8bit mode  |

| 6       | D1     | D1        | XRESET         | IN  | -     | Schmitt          |                                                 | Reset signal       |            |

| 54      | D9     | D8        | CLKIN          | IN  | -     | -                |                                                 | Clock input        |            |

| 23      | H4     | G3        | XRD            | IN  | -     | -                |                                                 | Read strobe        |            |

| 25      | H3     | H3        | XWRL<br>(XWR)  | IN  | -     | -                | Write strobe,<br>lower                          | Write              | strobe     |

| 24      | J3     | F3        | XWRH<br>(XBEH) | IN  | -     | -                | Write strobe, High byte upper enable Fixed high |                    | Fixed high |

| 22      | G4     | H2        | XCS            | IN  | -     | Schmitt          | С                                               | hip select signa   | al         |

| 21      | H2     | E3        | XINT           | OUT | High  | 2mA<br>Tri-state | Inte                                            | rrupt output sig   | Inal       |

| 26      | J4     | G4        | XDREQ          | OUT | High  | 2mA              |                                                 | DMA request        |            |

| 27      | G5     | F4        | XDACK          | IN  | -     | -                | DI                                              | VA acknowledg      | je         |

| 7       | C4     | D2        | XBEL<br>(CA0)  | IN  | -     | -                | Fixed high or low                               | Low byte<br>enable | Address 0  |

| 8       | C5     | C4        | CA1            | IN  | -     | -                |                                                 | •                  |            |

| 9       | E1     | E1        | CA2            | IN  | -     | -                |                                                 |                    |            |

| 10      | D3     | C5        | CA3            | IN  | -     | -                |                                                 |                    |            |

| 11      | E3     | E2        | CA4            | IN  | -     | -                | 0                                               |                    | •          |

| 14      | F2     | D3        | CA5            | IN  | -     | -                | C                                               | PU bus addres      | S          |

| 15      | G2     | G1        | CA6            | IN  | -     | -                |                                                 |                    |            |

| 16      | G1     | F1        | CA7            | IN  | -     | -                |                                                 |                    |            |

| 17      | F3     | F2        | CA8            | IN  | -     | -                |                                                 |                    |            |

| 28      | G6     | H4        | CD0            | BI  | Hi-Z  | 2mA              | CPU da                                          | ita bus            |            |

| 29      | H5     | G5        | CD1            | BI  | Hi-Z  | 2mA              |                                                 |                    |            |

| 30      | J5     | H5        | CD2            | BI  | Hi-Z  | 2mA              |                                                 |                    |            |

| 34      | J6     | F5        | CD3            | BI  | Hi-Z  | 2mA              |                                                 |                    | CPU data   |

| 35      | G7     | E6        | CD4            | BI  | Hi-Z  | 2mA              |                                                 |                    | bus        |

| 36      | J7     | H6        | CD5            | BI  | Hi-Z  | 2mA              |                                                 |                    |            |

| 37      | H7     | G6        | CD6            | BI  | Hi-Z  | 2mA              |                                                 |                    |            |

| 38      | F7     | F6        | CD7            | BI  | Hi-Z  | 2mA              |                                                 |                    |            |

| 39      | G8     | H7        | CD8            | BI  | Hi-Z  | 2mA              |                                                 |                    | Pull Up or |

| 43      | F8     | G8        | CD9            | BI  | Hi-Z  | 2mA              |                                                 |                    | Pull Down  |

| 44      | G9     | F7        | CD10           | BI  | Hi-Z  | 2mA              |                                                 |                    |            |

| 47      | F9     | E7        | CD11           | BI  | Hi-Z  | 2mA              |                                                 |                    |            |

| 48      | D7     | F8        | CD12           | BI  | Hi-Z  | 2mA              |                                                 |                    |            |

| 49      | E8     | D6        | CD13           | BI  | Hi-Z  | 2mA              |                                                 |                    |            |

| 1 | 50 | ГО | <b>_</b> _0 | CD14 | BI | Hi-Z | 0m A |

|---|----|----|-------------|------|----|------|------|

|   | 50 | E9 | E8          | CD14 | Ы  | HI-Z | 2mA  |

|   | 51 | D8 | C6          | CD15 | BI | Hi-Z | 2mA  |

The internal register can be set to operate the XINT pin in 1/0 mode or in Hi-Z/0 mode.

To use an external clock by feeding it from the CLKIN pin, attach the XI pin to the GND potential and leave the XO pin open. To use the internal oscillator of the LSI, connect a crystal resonator and oscillator circuit to the XI and XO pins and attach the CLKIN pin to the GND potential.

PD: Pull Down

PU: Pull Up

POWER

| QFP14                                      | PFBGA8                                         | PFBGA5                | Name | Voltage     | RESET                                                                                        |

|--------------------------------------------|------------------------------------------------|-----------------------|------|-------------|----------------------------------------------------------------------------------------------|

| 5,70,74                                    | A3,A6,C2                                       | A5,B3,C2              | HVDD | 3.3V        | Power supply for the USB, and I/O                                                            |

| 1,19,33,42,59,<br>65,76                    | A2,A8,C3,C8,<br>H1,H9                          | A2,A7,C7,G2           | LVDD | 1.8V        | Power supply for the internal circuit,<br>Power supply for TEST I/O, power<br>supply for OSC |

| 13,31,46,53                                | C6,F1,H6                                       | D7                    | CVDD | 3.3 to 1.8V | Power supply for CPU interface I/O                                                           |

| 2,12,20,32,41,<br>45,55,56,66,<br>68,72,77 | B1,B2,B4,B5,<br>B6,B7,B8,E2,<br>E7,J2,J8       | B2,B4,B5,B6,<br>B7,G7 | VSS  | 0V          | GND                                                                                          |

| 52,61,62,63,<br>64,69,78,79,<br>80         | A1,A9,D4,D5,<br>D6,E4,E5,E6,<br>F4,F5,F6,J1,J9 | A1                    | N.C. | 0V          | N.C. (Connect this pin to GND)                                                               |

# 6. Functional Description

This section describes the operation of the LSI.

In the explanation below, the registers are described according to the following naming conventions. Registers are described with a per-byte name.

- Names indicating a register comprising one address Register name + register Example: "MainIntStat register"

- Names indicating individual register bits Register name.bit name + bit, or bit name + bit Example: "MainIntStat.CPU\_IntStat bit"

- Registers provided for each endpoint Described as D\_EPx {x=0, a-c}...register, etc. Example: "D\_EPx {x=0, a-c} IntStat register"

- Registers provided for each channel Described as H\_CHx {x=0, a-e}...register, etc. Example: "H\_CHx {x=0, a-e} IntStat register"

- Registers provided for each area

Described as AREAn {n=0-5}...register, etc.

Example: "AREAn {n=0-5} StartAdrs\_H register"

# 6.1 Selection of USB Device/Host

To use USB with this LSI, set the HostDeviceSel.HOSTxDEVICE bit to select either the USB device or the USB host register map.

Selecting the USB device register map (hereafter referred to as device mode) enables the register bits and functions of the host/device shared registers and device registers.

Selecting the USB host register map (hereafter referred to as host mode) enables the register bits and functions of the host/device shared registers and host registers.

### 6.1.1 Selection of the USB Device/Host Functions

Table 6.1 shows the item to be set when selecting a USB device/host.

Selecting a register map

| ltem                      | Register/Bit               | Description                                                                                          |

|---------------------------|----------------------------|------------------------------------------------------------------------------------------------------|

| USB device/host selection | HostDeviceSel. HOSTxDEVICE | Selects either USB device or USB host. The registers and functions on the selected side are enabled. |

### Table 6.1 Setup Items for Selecting USB Device/Host Functions

### 6.1.2 USB Port State Change Detection Status

The S1R72V17 LSI has the function to detect USB port status.

This function can be used in both SLEEP and ACTIVE states (see the section on Power Management).

#### 6.1.2.1 Example Usage of USB Port State Change Detection Status

Examples of use of device port change status and host port change status are shown.

#### 6.1.2.1.1 Device Port Change Status

This status indicates that VBUS pin of the device port has changed state.

Table 6.2 shows the register associated with the Device port pin change status.

Table 6.2

Resisters Associated with Device Port Change Status

| Item                          | Register/Bit                 | Description                                                                                                 |

|-------------------------------|------------------------------|-------------------------------------------------------------------------------------------------------------|

| VBUS pin change status        | DeviceIntStat. VBUS_Changed  | Indicates that the VBUS pin of the device port has changed state.                                           |

| VBUS pin change status enable | DeviceIntEnb. EnVBUS_Changed | Enable/disables assertion of the<br>MainIntStat.USB_DeviceIntStat bit by<br>USB_DeviceIntStat.VBUS_Changed. |

| Device port VBUS state        | D_USB_Status. VBUS           | Indicates the VBUS pin state of the device port.                                                            |

If the device port status is changed, the firmware performs processing (1), (2), and (4) to (7).

- (1) Clear the VBUS pin change status.

- (2) Set the VBUS pin change status enable.

- (3) When VBUS is supplied to a device port, a VBUS pin change status is issued.

- (4) Check the VBUS pin change status.

- (5) Clear the VBUS pin change status.

- (6) Clear the VBUS pin change status enable.

- (7) Check the device port VBUS status. If the device port VBUS status bit = 1, the firmware determines that VBUS is supplied (i.e., the device port has a host or hub connected to it).

### 6.1.2.1.2 Host Port Change Status

This status indicates the status of the power driver that controls VBUS on host ports.

Table 6.3 shows the registers associated with the host port change status.

Table 6.3

Registers Associated with Host Port Change Status

| Item                               | Register/Bit               | Description                                                                                          |

|------------------------------------|----------------------------|------------------------------------------------------------------------------------------------------|

| VBUS error detection status        | USB_HostIntStat. VBUS_Err  | Indicates that an error occurred in VBUS.                                                            |

| VBUS error detection status enable | USB_HostIntEnb. EnVBUS_Err | Enable/disables assertion of the MainIntStat.<br>USB_HostIntStat bit by<br>USB_HostIntStat.VBUS_Err. |

| VBUS enable                        | H_USB_Control. VBUS_Enb    | Enables an external USB power switch.                                                                |

| Host port VBUS state               | H_USB_Status. VBUS_State   | Indicates the VBUS state of the host port (normal or erratic).                                       |

If a VBUS error detection status is detected, immediately turn the VBUS enable off to stop VBUS drive.

# 6.2 USB Device Control

The following describes the USB device functions.

### 6.2.1 Endpoints

The LSI stipulated herein has the endpoint for control transfer (EP0) and five general-purpose endpoints (EPa, EPb, and EPe). The endpoints EPa, EPb, EPc, EPd, and EPe can each be used simultaneously as endpoints for Bulk, Interrupt, and Isochronous transfers. The alarm endpoint function incorporated in the LSI to generate an alarm when a transaction is issued from the USB host also permits the user system to have up to 15 IN endpoints and up to 15 OUT endpoints, not including the endpoint EP0. The alarm endpoint function notifies the firmware of a state by returning a NAK response for the transaction issued to any endpoint other than the active endpoints set in EPa, EPb, EPc, EPd, and/or EPe.

The hardware of the LSI provides endpoints for the purpose of transaction management. However, it does not provide management functions for the interfaces defined in the USB standard (hereinafter referred to as the "USB-defined interface"). The USB-defined interface should be implemented by the user firmware. Set up and combine endpoints as appropriate for the descriptor definitions specific to the device, to configure the USB-defined interface.

Each endpoint has fixed basic setup items determined by the USB-defined interface and the variable control items and status to be controlled for each transfer. The basic setup items should be set up when initializing the chip or switching USB-defined interfaces from one to another.

Table 6.4 lists the basic setup items for the endpoint EP0 (default control pipe).

The endpoint EP0 shares the register set and FIFO area for transfers in IN and OUT directions. The direction of data transaction should be set by the firmware as appropriate for the execution of the data and status stages at the endpoint EP0.

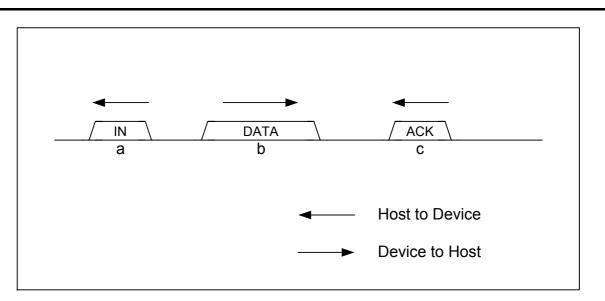

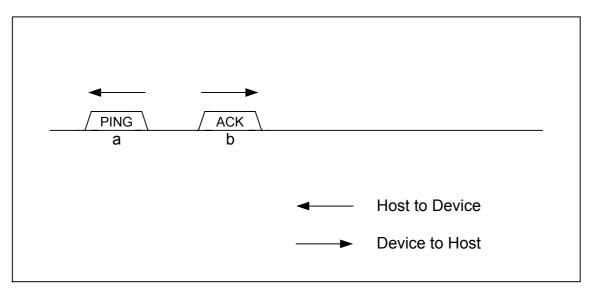

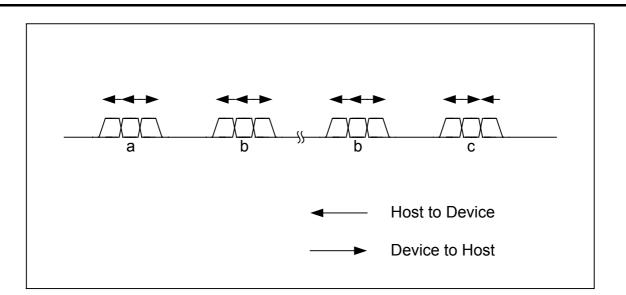

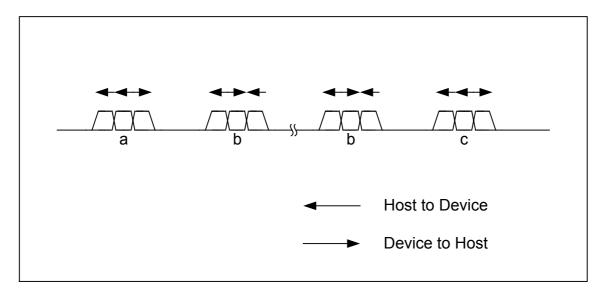

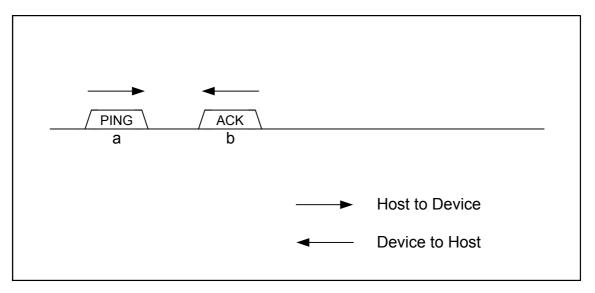

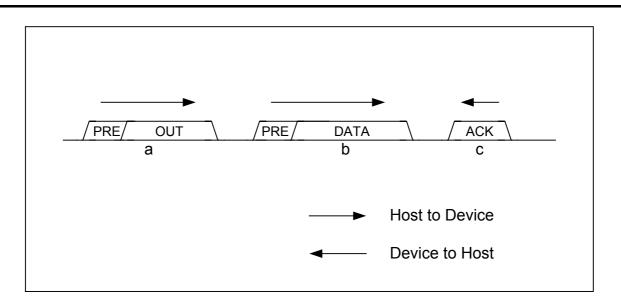

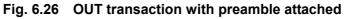

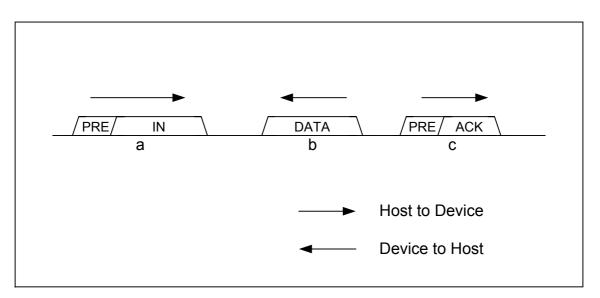

Any desired transaction can be performed by joining to the FIFO area described later. First, set AREA0StartAdrs\_H,L and AREA0EndAdrs\_H,L to reserve memory space for the FIFO area to be used. After initializing the FIFO area with AREA0FIFO\_Clr, set up AREA0Join\_1.JoinEP0CH0 for the FIFO area zero. No data transfers via a FIFO area can be performed until this joining process is executed.