## Up to 1 A step down-switching regulator for automotive applications

Datasheet - production data

#### **Features**

- Qualified following the AEC-Q100 requirements (see PPAP for more details)

- 1 A DC output current

- Operating input voltage from 4 V to 36 V

- 3.3 V / (± 2%) reference voltage

- Output voltage adjustable from 1.235 V to V<sub>IN</sub>

- Low dropout operation: 100% duty cycle

- 500 kHz Internally fixed frequency

- Voltage feed-forward

- Zero load current operation

- · Internal current limiting

- · Inhibit for zero current consumption

- Synchronization

- · Protection against feedback disconnection

- Thermal shutdown

## **Application**

· Dedicated to automotive applications

### **Description**

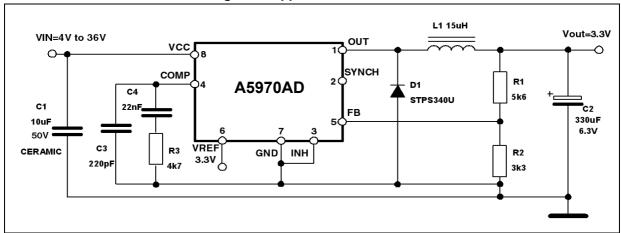

The A5970AD is a step-down monolithic power switching regulator with a minimum switch current limit of 1.35 A so it is able to deliver up to 1 A DC current to the load depending on the application conditions. The output voltage can be set from 1.235 V to  $V_{\rm IN}$ .

The device uses an internal P-channel DMOS transistor (with a typical  $R_{DS(on)}$  of 250 m $\Omega$ ) as switching element to minimize the size of the external components.

An internal oscillator fixes the switching frequency at 500 kHz. Having a minimum input voltage of 4 V only it fits the automotive applications requiring the device operation even in cold crank conditions. Pulse by pulse current limit with the internal frequency modulation offers an effective constant current short-circuit protection.

Figure 1. Application schematic

Contents A5970AD

## **Contents**

| 1 | Pin  | settings                                     | 4  |

|---|------|----------------------------------------------|----|

|   | 1.1  | Pin connection                               | 4  |

|   | 1.2  | Pin description                              | 4  |

| 2 | Elec | trical data                                  | 5  |

|   | 2.1  | Maximum ratings                              | 5  |

|   | 2.2  | Thermal data                                 | 5  |

| 3 | Elec | trical characteristics                       | 6  |

| 4 | Data | asheet parameters over the temperature range | 8  |

| 5 | Fund | ctional description                          | 9  |

|   | 5.1  | Power supply and voltage reference           | 9  |

|   | 5.2  | Voltages monitor                             | 10 |

|   | 5.3  | Oscillator and synchronization               | 10 |

|   | 5.4  | Current protection                           | 11 |

|   | 5.5  | Error amplifier                              | 12 |

|   | 5.6  | PWM comparator and power stage               | 13 |

|   | 5.7  | Inhibit function                             | 14 |

|   | 5.8  | Thermal shutdown                             | 14 |

| 6 | Add  | itional features and protection              | 15 |

|   | 6.1  | Feedback disconnection                       | 15 |

|   | 6.2  | Output overvoltage protection                | 15 |

|   | 6.3  | Zero load                                    | 15 |

| 7 | Clos | sing the loop                                | 16 |

|   | 7.1  | Error amplifier and compensation network     | 17 |

|   | 7.2  | LC filter                                    | 18 |

|   | 7.3  | PWM comparator                               | 19 |

| 8  | Applic | cation information                           | 21 |

|----|--------|----------------------------------------------|----|

|    | 8.1    | Component selection                          | 21 |

|    | 8.2    | Layout considerations                        | 24 |

|    | 8.3    | Thermal considerations                       | 24 |

|    | 8.4    | Short-circuit protection                     | 26 |

|    | 8.5    | Application circuit                          | 29 |

|    | 8.6    | Positive buck-boost regulator                | 31 |

|    | 8.7    | Negative buck-boost regulator                | 33 |

|    | 8.8    | Synchronization example                      | 34 |

|    | 8.9    | Compensation network with MLCC at the output | 34 |

|    | 8.10   | External SOFT_START network                  | 36 |

| 9  | Туріса | al characteristics                           | 37 |

| 10 | Packa  | age information                              | 39 |

| 11 | Order  | ing information                              | 41 |

| 12 | Revis  | ion history                                  | 41 |

Pin settings A5970AD

# 1 Pin settings

## 1.1 Pin connection

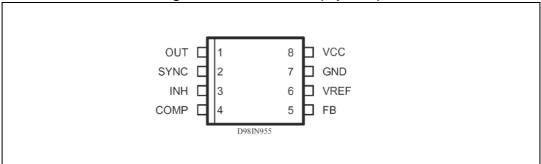

Figure 2. Pin connection (top view)

## 1.2 Pin description

Table 1. Pin description

| No. | Pin   | Description                                                                                                                                                   |

|-----|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | OUT   | Regulator output.                                                                                                                                             |

| 2   | SYNCH | Master/slave synchronization.                                                                                                                                 |

| 3   | INH   | A logical signal (active high) disables the device. If INH not used the pin must be grounded. When it is open an internal pull-up disables the device.        |

| 4   | COMP  | E/A output for frequency compensation.                                                                                                                        |

| 5   | FB    | Feedback input. Connecting directly to this pin results in an output voltage of 1.23 V. An external resistive divider is required for higher output voltages. |

| 6   | VREF  | 3.3 V V <sub>REF.</sub> No cap is requested for stability.                                                                                                    |

| 7   | GND   | Ground.                                                                                                                                                       |

| 8   | VCC   | Unregulated DC input voltage.                                                                                                                                 |

A5970AD Electrical data

## 2 Electrical data

## 2.1 Maximum ratings

Table 2. Absolute maximum ratings

| Symbol                          | Parameter                                                           | Value                   | Unit   |

|---------------------------------|---------------------------------------------------------------------|-------------------------|--------|

| V <sub>8</sub>                  | Input voltage                                                       | 40                      | V      |

| V <sub>1</sub>                  | OUT pin DC voltage OUT pin peak voltage at $\Delta t$ = 0.1 $\mu s$ | -1 to 40<br>-5 to 40    | V<br>V |

| I <sub>1</sub>                  | Maximum output current                                              | Int. limit.             |        |

| V <sub>4</sub> , V <sub>5</sub> | Analog pins                                                         | 4                       | V      |

| V <sub>3</sub>                  | INH                                                                 | -0.3 to V <sub>CC</sub> | V      |

| V <sub>2</sub>                  | SYNCH                                                               | -0.3 to 4               | V      |

| P <sub>TOT</sub>                | Power dissipation at T <sub>A</sub> ≤ 70 °C                         | 0.6                     | W      |

| TJ                              | Operating junction temperature range                                | -40 to 150              | °C     |

| T <sub>STG</sub>                | Storage temperature range                                           | -55 to 150              | °C     |

## 2.2 Thermal data

Table 3. Thermal data

| Symbol            | Parameter                                   | Value              | Unit |

|-------------------|---------------------------------------------|--------------------|------|

| R <sub>thJA</sub> | Maximum thermal resistance junction ambient | 120 <sup>(1)</sup> | °C/W |

<sup>1.</sup> Package mounted on evaluation board.

Electrical characteristics A5970AD

## 3 Electrical characteristics

$\rm T_J$  = -40 °C to 125 °C,  $\rm V_{CC}$  = 12 V, unless otherwise specified.

**Table 4. Electrical characteristics**

| Symbol              | Parameter                               | Test condition                                                      | Min.         | Тур.  | Max.             | Unit |

|---------------------|-----------------------------------------|---------------------------------------------------------------------|--------------|-------|------------------|------|

| V <sub>CC</sub>     | Operating input voltage range           |                                                                     | 4            |       | 36               | V    |

| R <sub>DS(on)</sub> | MOSFET on resistance                    |                                                                     |              | 0.250 | 0.5              | Ω    |

| 1                   | Maximum limiting current <sup>(1)</sup> | V <sub>CC</sub> = 5 V                                               | 1.35         | 1.8   |                  | ^    |

| Ι <sub>L</sub>      | Maximum limiting current                | V <sub>CC</sub> = 5 V, T <sub>J</sub> = 25 °C                       | 1.5          | 1.8   |                  | Α    |

| f <sub>SW</sub>     | Switching frequency                     |                                                                     | 430          | 500   | 570              | kHz  |

|                     | Duty cycle                              |                                                                     | 0            |       | 100              | %    |

| Dynamic o           | characteristics (see test circuit)      |                                                                     |              |       |                  |      |

| V <sub>5</sub>      | Voltage feedback                        | 4.4 V < V <sub>CC</sub> < 36 V                                      | 1.198        | 1.235 | 1.272            | V    |

| h                   | Efficiency                              | V <sub>0</sub> = 5 V, V <sub>CC</sub> = 12 V                        |              | 90    |                  | %    |

| DC charac           | cteristics                              |                                                                     |              |       | •                |      |

| I <sub>qop</sub>    | Total operating quiescent current       |                                                                     |              | 5     | 7                | mA   |

| Iq                  | Quiescent current                       | Duty cycle = 0; V <sub>FB</sub> = 1.5 V                             |              |       | 2.7              | mA   |

| I <sub>qst-by</sub> | Total standby quiescent current         | V <sub>inh</sub> > 2.2 V                                            |              | 50    | 100              | μА   |

| Inhibit             |                                         | 1                                                                   |              |       |                  |      |

|                     | INILI throughold voltage                | Device ON                                                           |              |       | 0.8              | V    |

|                     | INH threshold voltage                   | Device OFF                                                          | 2.2          |       |                  | V    |

| Error amp           | lifier                                  |                                                                     |              |       | •                |      |

| V <sub>OH</sub>     | High level output voltage               | V <sub>FB</sub> = 1 V                                               | 3.5          |       |                  | V    |

| V <sub>OL</sub>     | Low level output voltage                | V <sub>FB</sub> = 1.5 V                                             |              |       | 0.4              | V    |

| lo source           | Source output current                   | V <sub>COMP</sub> = 1.9 V; V <sub>FB</sub> = 1 V                    | 190          | 300   |                  | μА   |

| lo sink             | Sink output current                     | V <sub>COMP</sub> = 1.9 V; V <sub>FB</sub> = 1.5 V                  | 1            | 1.5   |                  | mA   |

| lb                  | Source bias current                     |                                                                     |              | 2.5   | 4                | μА   |

|                     | DC open loop gain                       | RL = ∞                                                              | 50           | 57    |                  | dB   |

| gm                  | Transconductance                        | I <sub>COMP</sub> = -0.1 mA to 0.1 mA;<br>V <sub>COMP</sub> = 1.9 V |              | 2.3   |                  | mS   |

| Synch fun           | ection                                  | -                                                                   |              | •     | •                |      |

|                     | High input voltage                      | V <sub>CC</sub> = 4.4 to 36 V                                       | 2.5          |       | V <sub>REF</sub> | V    |

|                     | Low input voltage                       | V <sub>CC</sub> = 4.4 to 36 V                                       |              |       | 0.74             | V    |

|                     | Slave synch current <sup>(2)</sup>      | V <sub>synch</sub> = 0.74 V<br>V <sub>synch</sub> = 2.33 V          | 0.11<br>0.21 |       | 0.25<br>0.45     | mA   |

Table 4. Electrical characteristics (continued)

| Symbol    | Parameter               | Test condition                                                  | Min. | Тур. | Max.  | Unit |

|-----------|-------------------------|-----------------------------------------------------------------|------|------|-------|------|

|           | Master output amplitude | I <sub>source</sub> = 3 mA                                      | 2.75 | 3    |       | V    |

|           | Output pulse width      | no load, V <sub>synch</sub> = 1.65 V                            | 0.20 | 0.35 |       | μS   |

| Reference | Reference section       |                                                                 |      |      |       |      |

|           | Reference voltage       | I <sub>REF</sub> = 0 to 5 mA<br>V <sub>CC</sub> = 4.4 V to 36 V | 3.2  | 3.3  | 3.399 | V    |

|           | Line regulation         | I <sub>REF</sub> = 0 mA<br>V <sub>CC</sub> = 4.4 V to 36 V      |      | 5    | 10    | mV   |

|           | Load regulation         | I <sub>REF</sub> = 0 mA                                         |      | 8    | 15    | mV   |

|           | Short-circuit current   |                                                                 | 5    | 18   | 35    | mA   |

<sup>1.</sup> With  $T_J$  = 85 °C,  $I_{lim\_min}$  = 1.5 A, assured by design, characterization and statistical correlation.

<sup>2.</sup> Guaranteed by design.

## 4 Datasheet parameters over the temperature range

The 100% of the population in the production flow is tested at three different ambient temperatures (-40  $^{\circ}$ C, +25  $^{\circ}$ C, +125  $^{\circ}$ C) to guarantee the datasheet parameters inside the junction temperature range (-40  $^{\circ}$ C, +125  $^{\circ}$ C).

The device operation is so guaranteed when the junction temperature is inside the (-40 °C, +150 °C) temperature range. The designer can estimate the silicon temperature increase respect to the ambient temperature evaluating the internal power losses generated during the device operation (please refer to the *Section 2.2*).

However the embedded thermal protection disables the switching activity to protect the device in case the junction temperature reaches the  $T_{SHTDWN}$  (+150 °C ± 10 °C) temperature.

All the datasheet parameters can be guaranteed to a maximum junction temperature of +125 °C to avoid triggering the thermal shutdown protection during the testing phase because of self-heating.

## 5 Functional description

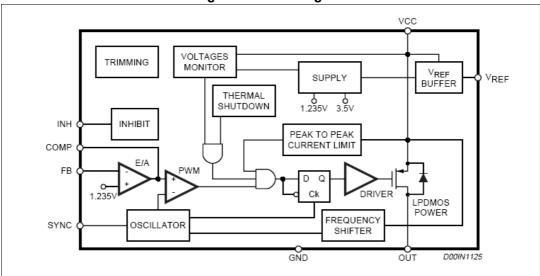

The main internal blocks are shown in the device block diagram in Figure 3. They are:

- A voltage regulator supplying the internal circuitry. From this regulator, a 3.3 V reference voltage is externally available.

- A voltage monitor circuit which checks the input and the internal voltages.

- A fully integrated sawtooth oscillator with a frequency of 500 kHz  $\pm$  15%, including also the voltage feed forward function and an input/output synchronization pin.

- Two embedded current limitation circuits which control the current that flows through the power switch. The pulse-by-pulse current limit forces the power switch OFF cycle by cycle if the current reaches an internal threshold, while the frequency shifter reduces the switching frequency in order to significantly reduce the duty cycle.

- A transconductance error amplifier.

- A pulse width modulator (PWM) comparator and the relative logic circuitry necessary to drive the internal power.

- A high side driver for the internal P-MOS switch.

- An inhibit block for standby operation.

- A circuit to implement the thermal protection function.

Figure 3. Block diagram

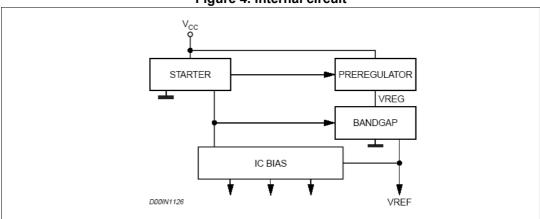

## 5.1 Power supply and voltage reference

The internal regulator circuit (shown in *Figure 4*) consists of a start-up circuit, an internal voltage pre-regulator, the bandgap voltage reference and the bias block that provides current to all the blocks. The starter supplies the start-up currents to the entire device when the input voltage goes high and the device is enabled (inhibit pin connected to ground). The pre-regulator block supplies the bandgap cell with a pre-regulated voltage V<sub>REG</sub> that has a very low supply voltage noise sensitivity.

### 5.2 Voltages monitor

An internal block continuously senses the  $V_{cc}$ ,  $V_{ref}$  and  $V_{bg}$ . If the voltages go higher than their thresholds, the regulator begins operating. There is also a hysteresis on the  $V_{CC}$  (UVLO).

Figure 4. Internal circuit

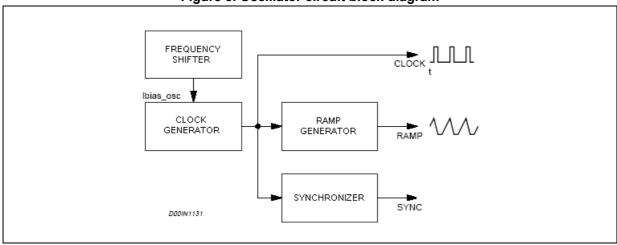

## 5.3 Oscillator and synchronization

Figure 5 shows the block diagram of the oscillator circuit.

The clock generator provides the switching frequency of the device, which is internally fixed at 500 kHz. The frequency shifter block acts to reduce the switching frequency in case of strong overcurrent or short-circuit. The clock signal is then used in the internal logic circuitry and is the input of the ramp generator and synchronizer blocks.

The ramp generator circuit provides the sawtooth signal, used for PWM control and the internal voltage feed-forward, while the synchronizer circuit generates the synchronization signal. The device also has a synchronization pin which can work both as master and slave.

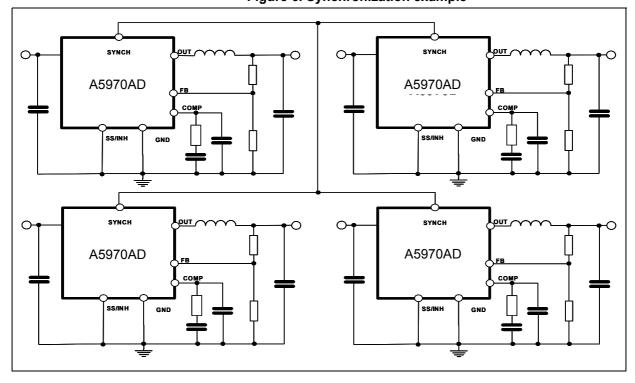

Beating frequency noise is an issue when more than one voltage rail is on the same board. A simple way to avoid this issue is to operate all the regulators at the same switching frequency.

The synchronization feature of a set of the A5970AD is simply get connecting together their SYNCH pin. The device with highest switching frequency will be the MASTER and it provides the synchronization signal to the others. Therefore the SYNCH is a I/O pin to deliver or recognize a frequency signal. The synchronization circuitry is powered by the internal reference ( $V_{REF}$ ) so a small filtering capacitor ( $\geq$  100 nF) connected between  $V_{REF}$  pin and the signal ground of the master device is suggested for its proper operation. However when a set of synchronized devices populates a board it is not possible to know in advance the one working as master, so the filtering capacitor have to be designed for whole set of devices.

When one or more devices are synchronized to an external signal, its amplitude have to be in comply with specifications given in the *Table 4 on page 6*. The frequency of the synchronization signal must be, at a minimum, higher than the maximum guaranteed natural switching frequency of the device (575 kHz, see *Table 4*) while the duty cycle of the synchronization signal can vary from approximately 10% to 90%. The small capacitor under  $V_{REF}$  pin is required for this operation.

Figure 5. Oscillator circuit block diagram

Figure 6. Synchronization example

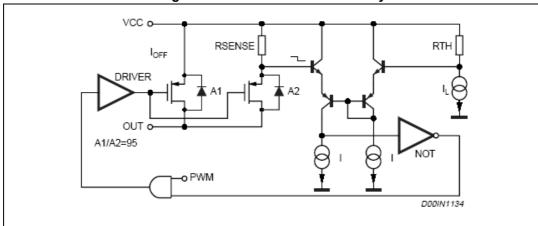

## 5.4 Current protection

The A5970AD device features two types of current limit protection: pulse-by-pulse and frequency foldback.

The schematic of the current limitation circuitry for the pulse-by-pulse protection is shown in *Figure 7*. The output power PDMOS transistor is split into two parallel PDMOS transistors. The smallest one includes a resistor in series,  $R_{\text{SENSE}}$ . The current is sensed through  $R_{\text{SENSE}}$  and if it reaches the threshold, the mirror becomes unbalanced and the PDMOS is switched off until the next falling edge of the internal clock pulse. Due to this reduction of the

ON time, the output voltage decreases. Since the minimum switch ON time necessary to sense the current in order to avoid a false overcurrent signal is too short to obtain a sufficiently low duty cycle at 500 kHz (see Section 8.4 on page 26), the output current in strong overcurrent or short-circuit conditions could be not properly limited. For this reason the switching frequency is also reduced, thus keeping the inductor current under its maximum threshold. The frequency shifter (Figure 5) functions based on the feedback voltage. As the feedback voltage decreases (due to the reduced duty cycle), the switching frequency decreases also.

Figure 7. Current limitation circuitry

### 5.5 Error amplifier

The voltage error amplifier is the core of the loop regulation. It is a transconductance operational amplifier whose non inverting input is connected to the internal voltage reference (1.235 V), while the inverting input (FB) is connected to the external divider or directly to the output voltage. The output (COMP) is connected to the external compensation network. The uncompensated error amplifier has the following characteristics:

| Description                 | Values         |

|-----------------------------|----------------|

| Transconductance            | 2300 μS        |

| Low frequency gain          | 65 dB          |

| Minimum sink/source voltage | 1500 μΑ/300 μΑ |

| Output voltage swing        | 0.4 V/3.65 V   |

| Input bias current          | 2.5 μΑ         |

Table 5. Uncompensated error amplifier characteristics

The error amplifier output is compared to the oscillator sawtooth to perform PWM control.

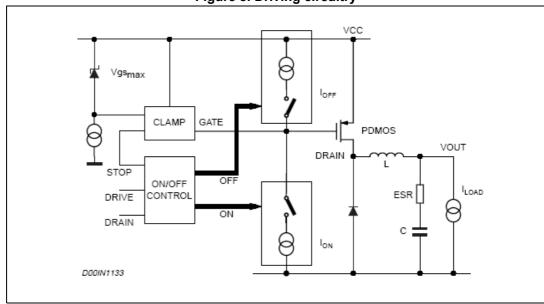

### 5.6 PWM comparator and power stage

This block compares the oscillator sawtooth and the error amplifier output signals to generate the PWM signal for the driving stage.

The power stage is a highly critical block, as it functions to guarantee a correct turn ON and turn OFF of the PDMOS. The turn ON of the power element, or more accurately, the rise time of the current at turn ON, is a very critical parameter. At a first approach, it appears that the faster the rise time, the lower the turn ON losses.

However, there is a limit introduced by the recovery time of the recirculation diode.

In fact, when the current of the power element is equal to the inductor current, the diode turns OFF and the drain of the power is able to go high. But during its recovery time, the diode can be considered a high value capacitor and this produces a very high peak current, responsible for numerous problems:

- Spikes on the device supply voltage that cause oscillations (and thus noise) due to the board parasites.

- Turn ON overcurrent leads to a decrease in the efficiency and system reliability.

- Major EMI problems.

- Shorter freewheeling diode life.

The fall time of the current during turn OFF is also critical, as it produces voltage spikes (due to the parasites elements of the board) that increase the voltage drop across the PDMOS.

In order to minimize these problems, a new driving circuit topology has been used and the block diagram is shown in *Figure 8*. The basic idea is to change the current levels used to turn the power switch ON and OFF, based on the PDMOS and the gate clamp status.

This circuitry allows the power switch to be turned OFF and ON quickly and addresses the freewheeling diode recovery time problem. The gate clamp is necessary to ensure that  $V_{GS}$  of the internal switch does not go higher than  $V_{GS}$ max. The ON/OFF Control block protects against any cross conduction between the supply line and ground.

Figure 8. Driving circuitry

### 5.7 Inhibit function

The inhibit feature is used to put the device in standby mode. With the INH pin higher than 2.2 V the device is disabled and the power consumption is reduced to less than 100  $\mu$ A. With the INH pin lower than 0.8 V, the device is enabled. If the INH pin is left floating, an internal pull up ensures that the voltage at the pin reaches the inhibit threshold and the device is disabled. The pin is also  $V_{CC}$  compatible.

### 5.8 Thermal shutdown

The shutdown block generates a signal that turns OFF the power stage if the temperature of the chip goes higher than a fixed internal threshold (150  $\pm$  10 °C). The sensing element of the chip is very close to the PDMOS area, ensuring fast and accurate temperature detection. A hysteresis of approximately 20 °C keeps the device from turning ON and OFF continuously.

## 6 Additional features and protection

#### 6.1 Feedback disconnection

If the feedback is disconnected, the duty cycle increases towards the maximum allowed value, bringing the output voltage close to the input supply. This condition could destroy the load

To avoid this hazardous condition, the device is turned OFF if the feedback pin is left floating.

## 6.2 Output overvoltage protection

Overvoltage protection, or OVP, is achieved by using an internal comparator connected to the feedback, which turns OFF the power stage when the OVP threshold is reached. This threshold is typically 30% higher than the feedback voltage.

When a voltage divider is required to adjust the output voltage (*Figure 15 on page 27*), the OVP intervention will be set at:

#### **Equation 1**

$$V_{OVP} = 1.3 \bullet \frac{R_1 + R_2}{R_2} \bullet V_{FB}$$

Where  $R_1$  is the resistor connected between the output voltage and the feedback pin, and  $R_2$  is between the feedback pin and ground.

### 6.3 Zero load

Due to the fact that the internal power is a PDMOS, no boostrap capacitor is required and so the device works properly even with no load at the output. In this case it works in burst mode, with a random burst repetition rate.

Closing the loop A5970AD

# 7 Closing the loop

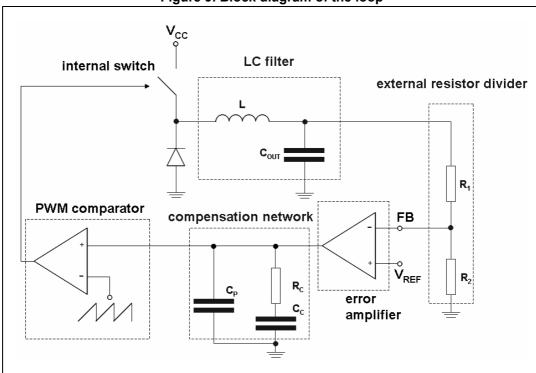

Figure 9. Block diagram of the loop

A5970AD Closing the loop

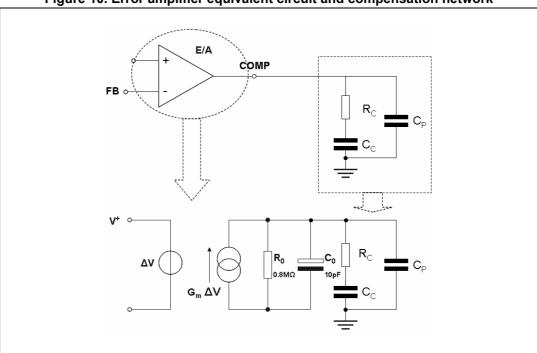

### 7.1 Error amplifier and compensation network

The output L-C filter of a step-down converter contributes with 180 degrees phase shift in the control loop. For this reason a compensation network between the COMP pin and GROUND is added. The simplest compensation network together with the equivalent circuit of the error amplifier are shown in *Figure 10*.  $R_C$  and  $C_C$  introduce a pole and a zero in the open loop gain. CP does not significantly affect system stability but it is useful to reduce the noise of the COMP pin.

The transfer function of the error amplifier and its compensation network is:

#### **Equation 2**

$$\mathsf{A}_0(s) = \frac{\mathsf{A}_{\mathsf{V0}} \bullet (1 + s \bullet \mathsf{R}_{\mathsf{c}} \bullet \mathsf{C}_{\mathsf{c}})}{s^2 \bullet \mathsf{R}_0 \bullet (\mathsf{C}_0 + \mathsf{C}_{\mathsf{p}}) \bullet \mathsf{R}_{\mathsf{c}} \bullet \mathsf{C}_{\mathsf{c}} + s \bullet (\mathsf{R}_0 \bullet \mathsf{C}_{\mathsf{c}} + \mathsf{R}_0 \bullet (\mathsf{C}_0 + \mathsf{C}_{\mathsf{p}}) + \mathsf{R}_{\mathsf{c}} \bullet \mathsf{C}_{\mathsf{c}}) + 1}$$

Where  $A_{vo} = G_{m} \cdot R_{o}$

Figure 10. Error amplifier equivalent circuit and compensation network

The poles of this transfer function are (if  $C_c >> C_0 + C_P$ ):

#### **Equation 3**

$$\mathsf{F}_{\mathsf{P1}} = \frac{1}{2 \bullet \pi \bullet \mathsf{R}_0 \bullet \mathsf{C}_{\mathsf{c}}}$$

#### **Equation 4**

$$\mathsf{F}_{\mathsf{P2}} = \frac{1}{2 \bullet \pi \bullet \mathsf{R}_{\mathsf{c}} \bullet (\mathsf{C}_{\mathsf{0}} + \mathsf{C}_{\mathsf{p}})}$$

Closing the loop A5970AD

whereas the zero is defined as:

#### **Equation 5**

$$F_{Z1} = \frac{1}{2 \cdot \pi \cdot R_c \cdot C_c}$$

$F_{P1}$  is the low frequency which sets the bandwidth, while the zero  $F_{Z1}$  is usually put near to the frequency of the double pole of the L-C filter (see below).  $F_{P2}$  is usually at a very high frequency.

### 7.2 LC filter

The transfer function of the L-C filter is given by:

#### **Equation 6**

$$\mathsf{A}_{\mathsf{LC}}(\mathsf{s}) = \frac{\mathsf{R}_{\mathsf{LOAD}} \bullet (\mathsf{1} + \mathsf{ESR} \bullet \mathsf{C}_{\mathsf{OUT}} \bullet \mathsf{s})}{\mathsf{s}^2 \bullet \mathsf{L} \bullet \mathsf{C}_{\mathsf{OUT}} \bullet (\mathsf{ESR} + \mathsf{R}_{\mathsf{LOAD}}) + \mathsf{s} \bullet (\mathsf{ESR} \bullet \mathsf{C}_{\mathsf{OUT}} \bullet \mathsf{R}_{\mathsf{LOAD}} + \mathsf{L}) + \mathsf{R}_{\mathsf{LOAD}}}$$

where  $R_{LOAD}$  is defined as the ratio between  $V_{OUT}$  and  $I_{OUT}$ .

If  $R_{I,OAD} >> ESR$ , the previous expression of  $A_{I,C}$  can be simplified and becomes:

#### **Equation 7**

$$A_{LC}(s) = \frac{1 + ESR \cdot C_{OUT} \cdot s}{L \cdot C_{OUT} \cdot s^2 + ESR \cdot C_{OUT} \cdot s + 1}$$

The zero of this transfer function is given by:

#### **Equation 8**

$$F_{O} = \frac{1}{2 \cdot \pi \cdot ESR \cdot C_{OUT}}$$

$F_0$  is the zero introduced by the ESR of the output capacitor and it is very important to increase the phase margin of the loop.

The poles of the transfer function can be calculated through the following expression:

#### **Equation 9**

$$\mathsf{F}_{\mathsf{PLC1},2} = \frac{-\mathsf{ESR} \bullet \mathsf{C}_{\mathsf{OUT}} \pm \sqrt{\left(\mathsf{ESR} \bullet \mathsf{C}_{\mathsf{OUT}}\right)^2 - 4 \bullet \mathsf{L} \bullet \mathsf{C}_{\mathsf{OUT}}}}{2 \bullet \mathsf{L} \bullet \mathsf{C}_{\mathsf{OUT}}}$$

In the denominator of A<sub>LC</sub> the typical second order system equation can be recognized:

#### **Equation 10**

$$s^2 + 2 \bullet \delta \bullet \omega_n \bullet s + \omega_n^2$$

5/

A5970AD Closing the loop

If the damping coefficient  $\delta$  is very close to zero, the roots of the equation become a double root whose value is  $\omega_n$ .

Similarly for A<sub>LC</sub> the poles can usually be defined as a double pole whose value is:

#### **Equation 11**

$$\mathsf{F}_{\mathsf{PLC}} = \frac{1}{2 \bullet \pi \bullet \sqrt{\mathsf{L} \bullet \mathsf{C}_{\mathsf{OUT}}}}$$

### 7.3 PWM comparator

The PWM gain is given by the following formula:

#### **Equation 12**

$$G_{PWM}(s) = \frac{V_{cc}}{(V_{OSCMAX} - V_{OSCMIN})}$$

where  $V_{OSCMAX}$  is the maximum value of a sawtooth waveform and  $V_{OSCMIN}$  is the minimum value. A voltage feed forward is implemented to ensure a constant GPWM. This is obtained by generating a sawtooth waveform directly proportional to the input voltage  $V_{CC}$ .

#### **Equation 13**

$$V_{OSCMAX} - V_{OSCMIN} = K \cdot V_{CC}$$

Where *K* is equal to 0.038. Therefore the PWM gain is also equal to:

#### **Equation 14**

$$G_{PWM}(s) = \frac{1}{K} = const$$

This means that even if the input voltage changes, the error amplifier does not change its value to keep the loop in regulation, thus ensuring a better line regulation and line transient response.

In summary, the open loop gain can be expressed as:

#### **Equation 15**

$$G(s) = G_{PWM}(s) \bullet \frac{R_2}{R_1 + R_2} \bullet A_O(s) \bullet A_{LC}(s)$$

Closing the loop A5970AD

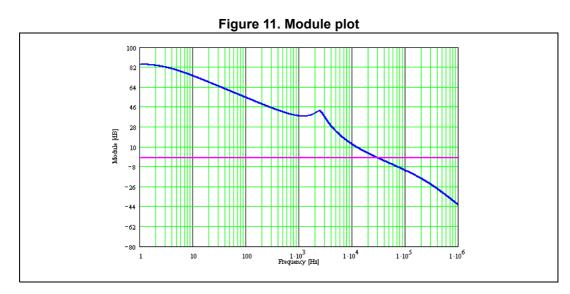

#### Example 1

Considering R<sub>C</sub> = 1.8 k $\Omega$ , C<sub>C</sub> = 68nF and C<sub>P</sub> = 330 pF, the poles and zeroes of A<sub>0</sub> are: F<sub>P1</sub> = 2.9 Hz

$F_{P2} = 265 \text{ kHz}$

$F_{Z1} = 1.3 \text{ kHz}$

If L = 15  $\mu$ H, C<sub>OUT</sub> = 330  $\mu$ F and ESR = 55 m $\Omega$ , the poles and zeroes of A<sub>LC</sub> become:

$F_{PLC} = 2.5 \text{ kHz}$

$F_{ZESR} = 8.7 \text{ kHz}$

Finally R<sub>1</sub> = 5.6 k $\Omega$  and R<sub>2</sub> = 3.3 k $\Omega$ .

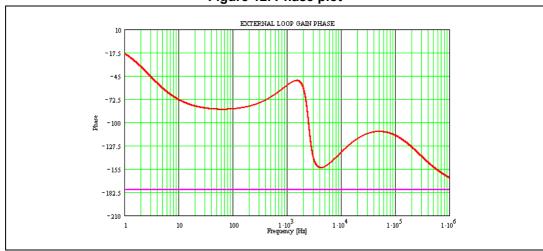

The gain and phase bode diagrams are plotted respectively in *Figure 11* and *Figure 12*.

Figure 12. Phase plot

The cut-off frequency and the phase margin are:

#### **Equation 16**

$$F_C = 24KHz$$

Phase margin =  $64^{\circ}$

## 8 Application information

## 8.1 Component selection

Input capacitor

The input capacitor must be able to support the maximum input operating voltage and the maximum RMS input current.

Since step-down converters draw current from the input in pulses, the input current is squared and the height of each pulse is equal to the output current. The input capacitor has to absorb all this switching current, which can be up to the load current divided by two (worst case, with duty cycle of 50%). For this reason, the quality of these capacitors has to be very high to minimize the power dissipation generated by the internal ESR, thereby improving system reliability and efficiency. The critical parameter is usually the RMS current rating, which must be higher than the RMS input current. The maximum RMS input current (flowing through the input capacitor) is:

#### **Equation 17**

$$I_{RMS} = I_{O} \bullet \sqrt{D - \frac{2 \bullet D^{2}}{\eta} + \frac{D^{2}}{\eta^{2}}}$$

Where  $\eta$  is the expected system efficiency, D is the duty cycle and  $I_O$  is the output DC current. This function reaches its maximum value at D = 0.5 and the equivalent RMS current is equal to  $I_O$  divided by 2 (considering  $\eta$  = 1). The maximum and minimum duty cycles are:

#### **Equation 18**

$$D_{MAX} = \frac{V_{OUT} + V_{F}}{V_{INMIN} - V_{SW}}$$

and

#### **Equation 19**

$$D_{MIN} = \frac{V_{OUT} + V_F}{V_{INMAX} - V_{SW}}$$

Where  $V_F$  is the freewheeling diode forward voltage and  $V_{SW}$  the voltage drop across the internal PDMOS. Considering the range  $D_{MIN}$  to  $D_{MAX}$ , it is possible to determine the max. IRMS going through the input capacitor.

Capacitors that can be considered are:

#### **Electrolytic capacitors:**

These are widely used due to their low price and their availability in a wide range of RMS current ratings.

The only drawback is that, considering ripple current rating requirements, they are physically larger than other capacitors.

#### Ceramic capacitors:

If available for the required value and voltage rating, these capacitors usually have a higher RMS current rating for a given physical dimension (due to very low ESR). The drawback is the considerably high cost.

#### **Tantalum capacitors:**

Very good, small tantalum capacitors with very low ESR are becoming more available. However, they can occasionally burn if subjected to very high current during charge.

Therefore, it is better to avoid this type of capacitor for the input filter of the device. They can, however, be subjected to high surge current when connected to the power supply.

| Manufacturer | Series              | Capacitor value (µF) | Rated voltage (V) |

|--------------|---------------------|----------------------|-------------------|

| TAIYO YUDEN  | UMK325BJ106MM-T     | 10                   | 50                |

| MURATA       | GRM42-2 X7R 475K 50 | 4.7                  | 50                |

Table 6. List of ceramic capacitors for the A5970AD

High dv/dt voltage spikes on the input side can be critical for DC/DC converters. A good power layout and input voltage filtering help to minimize this issue. In addition to the above considerations, a 1 µF/50 V ceramic capacitor as close as possible to the VCC and GND pins is always suggested to adequately filter VCC spikes.

#### Output capacitor

The output capacitor is very important to meet the output voltage ripple requirement.

Using a small inductor value is useful to reduce the size of the choke but it increases the current ripple. So, to reduce the output voltage ripple, a low ESR capacitor is required. Nevertheless, the ESR of the output capacitor introduces a zero in the open loop gain, which helps to increase the phase margin of the system. If the zero goes to a very high frequency, its effect is negligible. For this reason, ceramic capacitors and very low ESR capacitors in general should be avoided.

Tantalum and electrolytic capacitors are usually a good choice for this purpose. A list of some tantalum capacitor manufacturers is provided in *Table 7.: Output capacitor selection*.

| Manufacturer                | Series  | Cap value (µF) | Rated voltage (V) | ESR (m $\Omega$ ) |

|-----------------------------|---------|----------------|-------------------|-------------------|

| Sanyo POSCAP <sup>(1)</sup> | TAE     | 100 to 470     | 4 to 16           | 25 to 35          |

|                             | THB/C/E | 100 to 470     | 4 to 16           | 25 to 55          |

| AVX                         | TPS     | 100 to 470     | 4 to 35           | 50 to 200         |

| KEMET                       | T494/5  | 100 to 470     | 4 to 20           | 30 to 200         |

| Sprague                     | 595D    | 220 to 390     | 4 to 20           | 160 to 650        |

Table 7. Output capacitor selection

#### Inductor

The inductor value is very important as it fixes the ripple current flowing through the output capacitor. The ripple current is usually fixed at 20 - 40% of  $I_{omax}$ , which is 0.2 - 0.4 A with  $I_{omax} = 1$  A. The approximate inductor value is obtained using the following formula:

#### **Equation 20**

$$L = \frac{(V_{IN} - V_{OUT})}{\Delta I} \bullet T_{ON}$$

where  $T_{ON}$  is the ON time of the internal switch, given by D · T. For example, with  $V_{OUT}$  = 3.3 V,  $V_{IN}$  = 12 V and  $\Delta I_{O}$  = 0.3 A, the inductor value is about 15  $\mu$ H. The peak current through the inductor is given by:

#### **Equation 21**

$$I_{PK} = I_O + \frac{\Delta I}{2}$$

and it can be observed that if the inductor value decreases, the peak current (which must be lower than the current limit of the device) increases. So, when the peak current is fixed, a higher inductor value allows a higher value for the output current. In *Table 8* some inductor manufacturers are listed.

Table 8. Inductor selection

| Manufacturer     | Series   | Inductor value (µH) | Saturation current (A) |

|------------------|----------|---------------------|------------------------|

| Coilcraft        | DO3316T  | 15 to 33            | 2.0 to 3.0             |

| Coiltronics      | UP1B     | 22 to 33            | 2.0 to 2.4             |

| BI               | HM76-3   | 15 to 33            | 2.5 to 3.3             |

| Epcos            | B82476   | 15 to 33            | 2 to 3                 |

| Wurth Elektronik | 74456115 | 15 to 33            | 2.5 to 3               |

<sup>1.</sup> POSCAP capacitors have some characteristics which are very similar to tantalum.

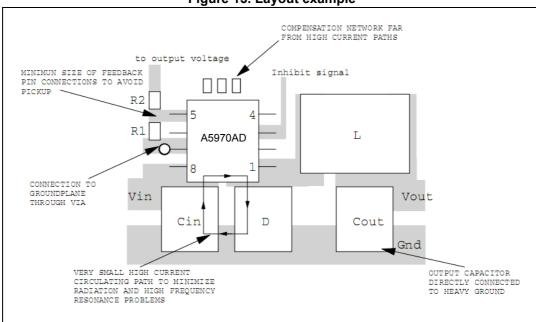

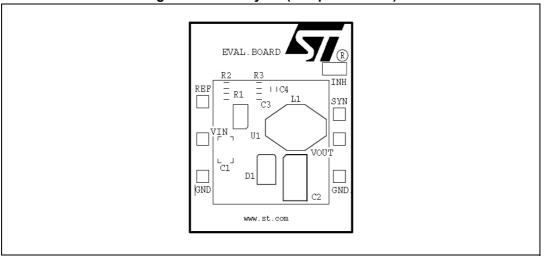

## 8.2 Layout considerations

The layout of switching DC-DC converters is very important to minimize noise and interference. Power-generating portions of the layout are the main cause of noise and so high switching current loop areas should be kept as small as possible and lead lengths as short as possible.

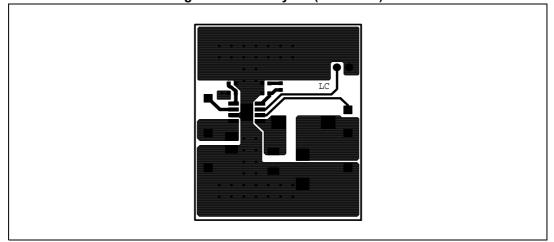

High impedance paths (in particular the feedback connections) are susceptible to interference, so they should be as far as possible from the high current paths. An layout example is provided in *Figure 13*.

The input and output loops are minimized to avoid radiation and high frequency resonance problems. The feedback pin connections to the external divider are very close to the device to avoid pick-up noise.

Figure 13. Layout example

### 8.3 Thermal considerations

The dissipated power of the device is tied to three different sources:

Conduction losses due to the not insignificant R<sub>DSON</sub>, which are equal to:

#### **Equation 22**

$$P_{ON} = R_{DSON} \bullet (I_{OUT})^2 \bullet D$$

Where D is the duty cycle of the application. Note that the duty cycle is theoretically given by the ratio between  $V_{OUT}$  and  $V_{IN}$ , but in practice it is substantially higher than this value to compensate for the losses in the overall application. For this reason, the switching losses related to the  $R_{DSON}$  increases compared to an ideal case.

577

Switching losses due to turning ON and OFF. These are derived using the following equation:

#### **Equation 23**

$$\mathsf{P}_{\mathsf{SW}} = \mathsf{V}_{\mathsf{IN}} \bullet \mathsf{I}_{\mathsf{OUT}} \bullet \frac{(\mathsf{T}_{\mathsf{ON}} + \mathsf{T}_{\mathsf{OFF}})}{2} \bullet \mathsf{F}_{\mathsf{SW}} = \mathsf{V}_{\mathsf{IN}} \bullet \mathsf{I}_{\mathsf{OUT}} \bullet \mathsf{T}_{\mathsf{SW}} \bullet \mathsf{F}_{\mathsf{SW}}$$

Where  $T_{RISE}$  and  $T_{FALL}$  represent the switching times of the power element that cause the switching losses when driving an inductive load (see *Figure 14*).  $T_{SW}$  is the equivalent switching time.

V<sub>IN</sub> OUT V<sub>DS</sub>

I<sub>O</sub> P<sub>SW</sub>

P<sub>ON</sub>

T<sub>FALL</sub>

T<sub>RISE</sub>

Figure 14. Switching losses

Quiescent current losses.

#### **Equation 24**

$$P_Q = V_{IN} \bullet I_Q$$

Where  $I_O$  is the quiescent current.

#### Example 2:

- V<sub>IN</sub> = 12 V

- V<sub>OUT</sub> = 3.3 V

- I<sub>OUT</sub> = 0.8 A

$R_{DS(on)}$  has a typical value of 0.25 at 25 °C and increases up to a maximum value of 0.5. at 150 °C. We can consider a value of 0.4  $\Omega$

$T_{SW}$  is approximately 70 ns.

$I_Q$  has a typical value of 2.7 mA at  $V_{IN}$  = 12 V.

The overall losses are:

#### **Equation 25**

$$P_{TOT} = R_{DSON} \bullet (I_{OUT})^2 \bullet D + V_{IN} \bullet I_{OUT} \bullet T_{SW} \bullet F_{SW} + V_{IN} \bullet I_Q =$$

= 0.4 \cdot 0.8 \cdot 0.3 + 12 \cdot 0.8 \cdot 70 \cdot 10^{-9} \cdot 500 \cdot 10^3 + 12 \cdot 2.7 \cdot 10^{-3} \cdot 0.55W

The junction temperature of device will be:

#### **Equation 26**

$$T_J = T_A + Rth_{J-A} \bullet P_{TOT}$$

Where  $T_A$  is the ambient temperature and  $Rth_{J-A}$  is the thermal resistance junction to ambient. Considering that the device is mounted on board with a good ground plane, that it has a thermal resistance junction to ambient (Rth<sub>J-A</sub>) of about 120°C/W, and an ambient temperature of about 50 °C:

#### **Equation 27**

$$T_J = 50 + 0.55 \bullet 120 \cong 116^{\circ}C$$

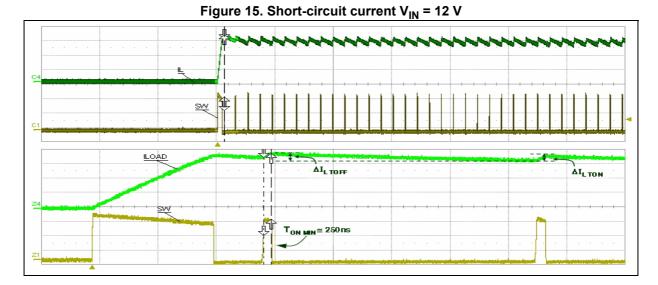

### 8.4 Short-circuit protection

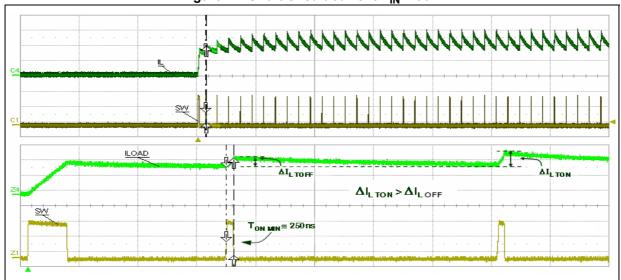

In overcurrent protection mode, when the peak current reaches the current limit, the device reduces the  $T_{ON}$  down to its minimum value (approximately 250 nsec) and the switching frequency to approximately one third of its nominal value even when synchronized to an external signal (see Section 5.4: Current protection on page 11). In these conditions, the duty cycle is strongly reduced and, in most applications, this is enough to limit the current to ILIM. In any event, in case of heavy short-circuit at the output ( $V_O = 0$  V) and depending on the application conditions ( $V_{cc}$  value and parasitic effect of external components) the current peak could reach values higher than ILIM. This can be understood considering the inductor current ripple during the ON and OFF phases:

ON phase

#### **Equation 28**

$$\Delta I_{L TON} = \frac{V_{IN} - V_{out} - (DCR_L + R_{DSON}) \cdot I}{L} (T_{ON})$$

OFF phase

#### **Equation 29**

$$\Delta I_{L \; TOFF} = \frac{-(V_D + V_{out} + DCR_L \bullet I)}{I} (T_{OFF})$$

where  $V_D$  is the voltage drop across the diode,  $DCR_L$  is the series resistance of the inductor.

In short-circuit conditions  $V_{OUT}$  is negligible so during  $T_{OFF}$  the voltage across the inductor is very small as equal to the voltage drop across parasitic components (typically the DCR of the inductor and the  $V_{FW}$  of the free wheeling diode) while during  $T_{ON}$  the voltage applied the inductor is instead maximized as approximately equal to  $V_{IN}$ .

So the Equation 28 and the Equation 29 in overcurrent conditions can be simplified to:

#### **Equation 30**

$$\Delta I_{L TON} = \frac{V_{IN} - (DCR_L + R_{DSON}) \cdot I}{L} (T_{ON MIN}) \cong \frac{V_{IN}}{L} (250 ns)$$

considering  $T_{ON}$  that has been already reduced to its minimum.

5//

#### **Equation 31**

$$\Delta I_{L \; TOFF} = \frac{-(V_D + V_{out} + DCR_L \bullet I)}{I} (3 \cdot T_{SW}) \\ \cong \frac{-(V_D + V_{out} + DCR_L \bullet I)}{I} (6 \mu s)$$

considering that  $f_{SW}$  has been already reduced to one third of the nominal.

In case a short-circuit at the output is applied and  $V_{IN}$  = 12 V the inductor current is controlled in most of the applications (see *Figure 15*). When the application must sustain the short-circuit condition for an extended period, the external components (mainly the inductor and diode) must be selected based on this value.

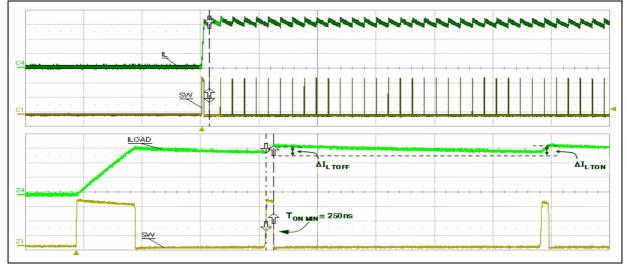

In case the V<sub>IN</sub> is very high, it could occur that the ripple current during T<sub>OFF</sub> (*Equation 31*) does not compensate the current increase during T<sub>ON</sub> (*Equation 30*). *Figure 17* shows an example of a power up phase with V<sub>IN</sub> = V<sub>IN MAX</sub> = 36 V where  $\Delta_{\text{IL TON}} > \Delta_{\text{IL TOFF}}$  so the current escalates and the balance between *Equation 30* and *Equation 31* occurs at a current slightly higher than the current limit. This must be taken into account in particular to avoid the risk of an abrupt inductor saturation.

Figure 16. Short-circuit current  $V_{IN} = 24 V$

577

Figure 17. Short-circuit current  $V_{IN}$  = 36 V

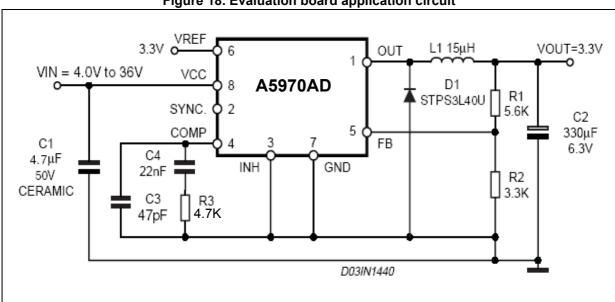

#### **Application circuit** 8.5

Figure 18 shows the evaluation board application circuit, where the input supply voltage, V<sub>CC</sub>, can range from 4 V to 36 V and the output voltage is adjustable from 1.235 V to 6.3 V due to the voltage rating of the output capacitor.

Figure 18. Evaluation board application circuit

Table 9. Component list

| Reference | Part number         | Description            | Manufacturer       |  |  |  |

|-----------|---------------------|------------------------|--------------------|--|--|--|

| C1        | GRM42-2 X7R 475K 50 | 4.7 μF, 50 V           | Murata             |  |  |  |

| C2        | POSCAP 6TAE330ML    | 330 μF, 6.3 V          | Sanyo              |  |  |  |

| C3        | C1206C221J5GAC      | 220 pF, 5%, 50 V       | KEMET              |  |  |  |

| C4        | C1206C223K5RAC      | 22 nF, 10%, 50 V       | KEMET              |  |  |  |

| R1        |                     | 5.6 kΩ, 1%, 0.1 W 0603 | Neohm              |  |  |  |

| R2        |                     | 3.3 kΩ, 1%, 0.1 W 0603 | Neohm              |  |  |  |

| R3        |                     | 4.7 kΩ, 1%, 0.1 W 0603 | Neohm              |  |  |  |

| D1        | STPS3L40U           | 2 A, 40 V              | STMicroelectronics |  |  |  |

| L1        | DO3316T-153MLD      | 15 μH, 3.1 A           | Coilcraft          |  |  |  |

Figure 19. PCB layout (component side)

Figure 20. PCB layout (bottom side)

Figure 21. PCB layout (front side)

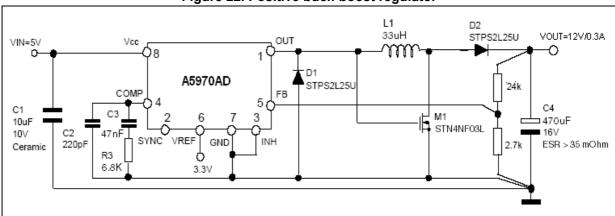

## 8.6 Positive buck-boost regulator

The device can be used to implement a step-up/down converter with a positive output voltage.

The output voltage is given by:

#### **Equation 32**

$$V_{OUT} = V_{IN} \cdot \frac{D}{1 - D}$$

where the ideal duty cycle D for the buck boost converter is:

#### **Equation 33**

$$D = \frac{V_{OUT}}{V_{IN} + V_{OUT}}$$

However, due to power losses in the passive elements, the real duty cycle is always higher than this. The real value (that can be measured in the application) should be used in the following formulas.

The peak current flowing in the embedded switch is:

#### **Equation 34**

$$I_{SW} = \frac{I_{LOAD}}{1-D} + \frac{I_{RIPPLE}}{2} = \frac{I_{LOAD}}{1-D} + \frac{V_{IN}}{2 \cdot L} \cdot \frac{D}{f_{SW}}$$

while its average current is equal to:

#### **Equation 35**

$$I_{SW} = \frac{I_{LOAD}}{1 - D}$$

This is due to the fact that the current flowing through the internal power switch is delivered to the output only during the OFF phase.

The switch peak current must be lower than the minimum current limit of the overcurrent protection (see *Table 4 on page 6* for details) while the average current must be lower than the rated DC current of the device.

As a consequence, the maximum output current is:

#### **Equation 36**

$$I_{OUT\ MAX} \cong I_{SW\ MAX} \cdot (1 - D)$$

where  $I_{SWMAX}$  represents the rated current of the device.

The current capability is reduced by the term (1 - D) and so, for example, with a duty cycle of 0.5, and considering an average current through the switch of 1 A, the maximum output current deliverable to the load is 0.5 A.

*Figure 22* shows the schematic circuit of this topology for a 12 V output voltage and 5 V input.

Figure 22. Positive buck-boost regulator

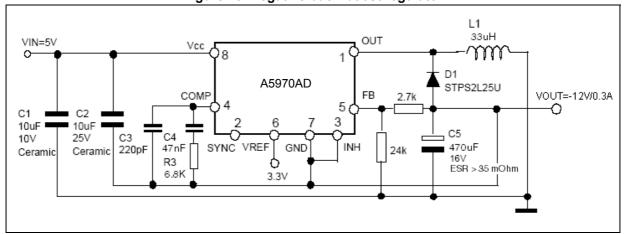

## 8.7 Negative buck-boost regulator

In *Figure 23*, the schematic circuit for a standard buck-boost topology is shown. The output voltage is:

#### **Equation 37**

$$V_{OUT} = -V_{IN} \cdot \frac{D}{1 - D}$$

where the ideal duty cycle D for the buck boost converter is:

#### **Equation 38**

$$D = \frac{-V_{OUT}}{V_{IN} - V_{OUT}}$$

The considerations given in Section 8.6 for the real duty cycle are still valid here.

Also the Equation 34 till Equation 36 can be used to calculate the maximum output current.

So, as an example, considering the conversion  $V_{IN}$  = 12 V to  $V_{OUT}$  = -5 V,  $I_{LOAD}$  = 0.3 A:

#### **Equation 39**

$$D = \frac{5}{5+12} = 0.706$$

#### **Equation 40**

$$I_{SW} = \frac{I_{LOAD}}{1 - D} = \frac{0.5}{1 - 0.706} = 1A$$

An important thing to take into account is that the ground pin of the device is connected to the negative output voltage. Therefore, the device is subjected to a voltage equal to  $V_{IN}$  -  $V_{O}$ , which must be lower than 36 V (the maximum operating input voltage).

Figure 23. Negative buck-boost regulator

#### Synchronization example 8.8

See Section 5.3: Oscillator and synchronization on page 10 for details.

VIN () VCC A5970AD A5970AD COMP COMP 5 5 GND GNE

Figure 24. Synchronization example

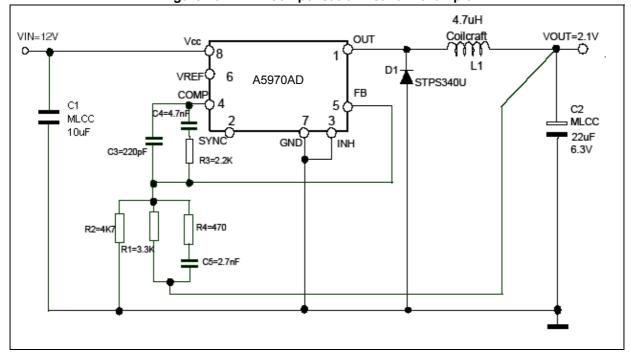

#### 8.9 Compensation network with MLCC at the output

MLCCs (multiple layer ceramic capacitor) with values in the range of 10 µF - 22 µF and rated voltages in the range of 10 V - 25 V are available today at relatively low cost from many manufacturers.

These capacitors have very low ESR values (a few mΩ) and thus are occasionally used for the output filter in order to reduce the voltage ripple and the overall size of the application.

However, a very low ESR value affects the compensation of the loop (see Section 7 on page 16) and in order to keep the system stable, a more complicated compensation network may be required. However, due to the architecture of the internal error amplifier the bandwidth with this compensation is limited.

That is why output capacitors with a not negligible ESR are suggested. The selection of the output capacitor have to guarantee that the zero introduced by this component is inside the designed system bandwidth and close to the frequency of the double pole introduced by the LC filter. A general rule for the selection of this compound for the system stability is provided in Equation 41.

#### **Equation 41**

$$\begin{aligned} f_{Z \; ESR} &= \frac{1}{2 \cdot \pi \cdot ESR \cdot C_{OUT}} < bandwidth \\ f_{LC} &< f_{Z \; ESR} < 10 \cdot f_{LC} \end{aligned}$$

*Figure 25* shows an example of a compensation network stabilizing the system with ceramic capacitors at the output (the optimum component value depends on the application).

Figure 25. MLCC compensation network example

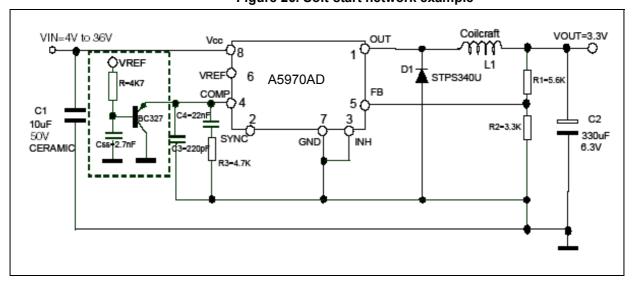

## 8.10 External SOFT\_START network

At start-up the device can quickly increase the current up to the current limit in order to charge the output capacitor. If soft ramp-up of the output voltage is required, an external soft-start network can be implemented as shown in *Figure 26*. The capacitor C is charged up to an external reference through R and the BJT clamps the COMP pin.

This clamps the duty cycle, limiting the slew rate of the output voltage.

Figure 26. Soft-start network example

# 9 Typical characteristics

Figure 27. Load regulation

Vo (V) 3.312 Vcc = 12V 3.308 Vo = 3.3V3.304 Tj = 25°C\_ 3.3 3.296 3.292 3.288 3.284 Tj = 125°C 3.28 3.276 1 1.5 lo (A)

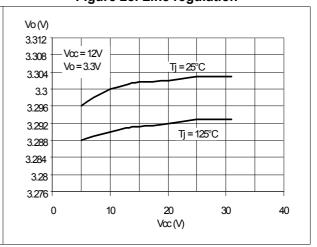

Figure 28. Line regulation

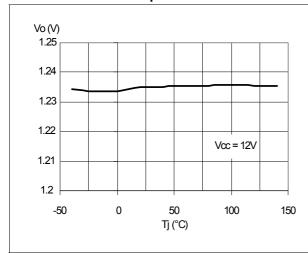

Figure 29. Output voltage vs. junction temperature

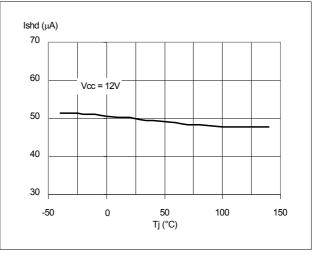

Figure 30. Shutdown current vs. junction temperature

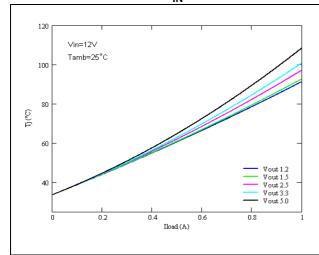

Figure 31. Junction temperature vs. output current -  $V_{\text{IN}}$  = 12 V

Figure 32. Junction temperature vs. output current -  $V_{IN} = 5 V$

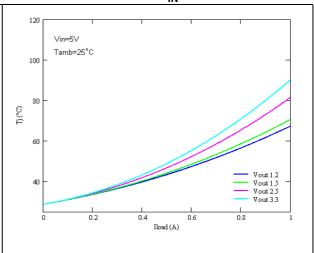

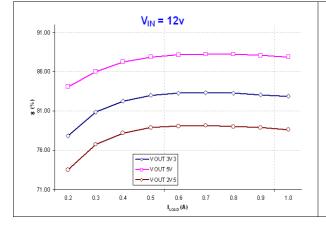

Figure 33. Efficiency vs output current -  $V_{IN}$  = 12 V

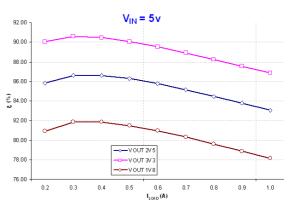

Figure 34. Efficiency vs output current -  $V_{IN} = 5 \text{ V}$

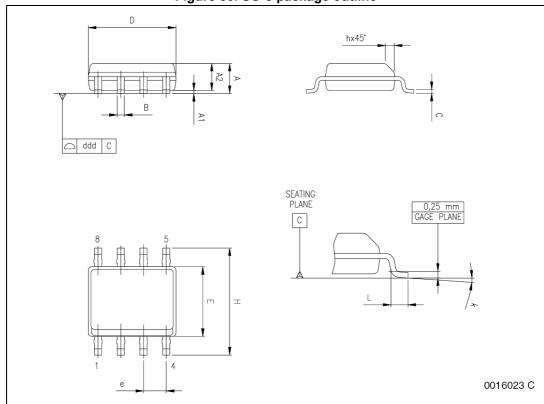

## 10 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance. ECOPACK specifications, grade definitions and product status are available at: www.st.com. ECOPACK is an ST trademark.

Figure 35. SO-8 package outline

Package information A5970AD

Table 10. SO-8 package mechanical data

| Symbol           | Dimensions           |      |      |       |       |       |  |

|------------------|----------------------|------|------|-------|-------|-------|--|

|                  | mm                   |      |      | inch  |       |       |  |

|                  | Min.                 | Тур. | Max. | Min.  | Тур.  | Max.  |  |

| Α                | 1.35                 |      | 1.75 | 0.053 |       | 0.069 |  |

|                  |                      |      |      |       |       |       |  |

| A1               | 0.10                 |      | 0.25 | 0.004 |       | 0.010 |  |

| A2               | 1.10                 |      | 1.65 | 0.043 |       | 0.065 |  |

| В                | 0.33                 |      | 0.51 | 0.013 |       | 0.020 |  |

| С                | 0.19                 |      | 0.25 | 0.007 |       | 0.010 |  |

| D <sup>(1)</sup> | 4.80                 |      | 5.00 | 0.189 |       | 0.197 |  |

| Е                | 3.80                 |      | 4.00 | 0.15  |       | 0.157 |  |

| е                |                      | 1.27 |      |       | 0.050 |       |  |

| Н                | 5.80                 |      | 6.20 | 0.228 |       | 0.244 |  |

| h                | 0.25                 |      | 0.50 | 0.010 |       | 0.020 |  |

| L                | 0.40                 |      | 1.27 | 0.016 |       | 0.050 |  |

| k                | 0° (min.), 8° (max.) |      |      |       |       |       |  |

| ddd              |                      |      | 0.10 |       |       | 0.004 |  |

<sup>1.</sup> Dimensions D does not include mold flash, protrusions or gate burrs. Mold flash, protrusions or gate burrs shall not exceed 0.15 mm (0.006 inch) in total (both sides).

# 11 Ordering information

**Table 11. Ordering information**

| Order code | Package | Packaging     |  |

|------------|---------|---------------|--|

| A5970AD    | SO8     | Tube          |  |

| A5970ADTR  | 300     | Tape and reel |  |

# 12 Revision history

**Table 12. Document revision history**

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|-------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 02-May-2008 | 1        | Initial release                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 27-Aug-2008 | 2        | Updated: coverpage and Table 4 on page 5                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| 23-Apr-2009 | 3        | Updated first feature in coverpage                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 04-Nov-2009 | 4        | Updated coverpage, Table 4 on page 6 and added Figure 27, Figure 28, Figure 29 and Figure 30 on page 37.                                                                                                                                                                                                                                                                                                                                                |  |

| 31-Mar-2014 | 5        | Updated Section 8.1: Component selection on page 21 (updated units in "Capacitor value" - header of Table 6, added text below Table 6).  Updated titles from Figure 31 to Figure 34 (added values of "V <sub>IN</sub> ").  Updated Section 10: Package information on page 39 (reversed order of Figure 35 and Table 10, updated titles, minor modifications).  Updated cross-references throughout document.  Minor modifications throughout document. |  |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

ST PRODUCTS ARE NOT DESIGNED OR AUTHORIZED FOR USE IN: (A) SAFETY CRITICAL APPLICATIONS SUCH AS LIFE SUPPORTING, ACTIVE IMPLANTED DEVICES OR SYSTEMS WITH PRODUCT FUNCTIONAL SAFETY REQUIREMENTS; (B) AERONAUTIC APPLICATIONS; (C) AUTOMOTIVE APPLICATIONS OR ENVIRONMENTS, AND/OR (D) AEROSPACE APPLICATIONS OR ENVIRONMENTS. WHERE ST PRODUCTS ARE NOT DESIGNED FOR SUCH USE, THE PURCHASER SHALL USE PRODUCTS AT PURCHASER'S SOLE RISK, EVEN IF ST HAS BEEN INFORMED IN WRITING OF SUCH USAGE, UNLESS A PRODUCT IS EXPRESSLY DESIGNATED BY ST AS BEING INTENDED FOR "AUTOMOTIVE, AUTOMOTIVE SAFETY OR MEDICAL" INDUSTRY DOMAINS ACCORDING TO ST PRODUCT DESIGN SPECIFICATIONS. PRODUCTS FORMALLY ESCC, QML OR JAN QUALIFIED ARE DEEMED SUITABLE FOR USE IN AEROSPACE BY THE CORRESPONDING GOVERNMENTAL AGENCY.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2014 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

OOO «ЛайфЭлектроникс" "LifeElectronics" LLC

ИНН 7805602321 КПП 780501001 P/C 40702810122510004610 ФАКБ "АБСОЛЮТ БАНК" (ЗАО) в г.Санкт-Петербурге К/С 3010181090000000703 БИК 044030703

Компания «Life Electronics» занимается поставками электронных компонентов импортного и отечественного производства от производителей и со складов крупных дистрибьюторов Европы, Америки и Азии.

С конца 2013 года компания активно расширяет линейку поставок компонентов по направлению коаксиальный кабель, кварцевые генераторы и конденсаторы (керамические, пленочные, электролитические), за счёт заключения дистрибьюторских договоров

#### Мы предлагаем:

- Конкурентоспособные цены и скидки постоянным клиентам.

- Специальные условия для постоянных клиентов.

- Подбор аналогов.

- Поставку компонентов в любых объемах, удовлетворяющих вашим потребностям.

- Приемлемые сроки поставки, возможна ускоренная поставка.

- Доставку товара в любую точку России и стран СНГ.

- Комплексную поставку.

- Работу по проектам и поставку образцов.

- Формирование склада под заказчика.

- Сертификаты соответствия на поставляемую продукцию (по желанию клиента).

- Тестирование поставляемой продукции.

- Поставку компонентов, требующих военную и космическую приемку.

- Входной контроль качества.

- Наличие сертификата ISO.

В составе нашей компании организован Конструкторский отдел, призванный помогать разработчикам, и инженерам.

Конструкторский отдел помогает осуществить:

- Регистрацию проекта у производителя компонентов.

- Техническую поддержку проекта.

- Защиту от снятия компонента с производства.

- Оценку стоимости проекта по компонентам.

- Изготовление тестовой платы монтаж и пусконаладочные работы.

Тел: +7 (812) 336 43 04 (многоканальный) Email: org@lifeelectronics.ru