# **PCA9626**

# 24-bit Fm+ I<sup>2</sup>C-bus 100 mA 40 V LED driver

Rev. 5 — 19 June 2014

**Product data sheet**

# 1. General description

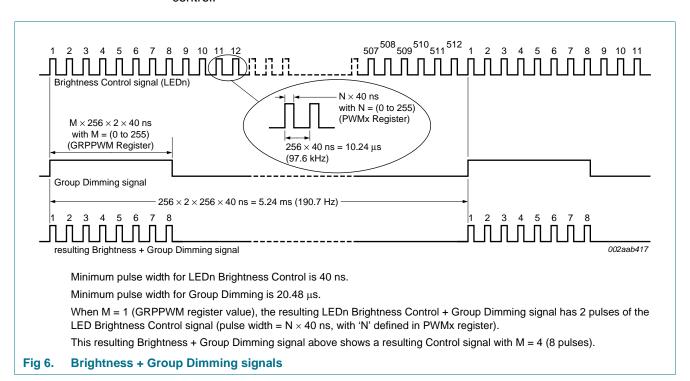

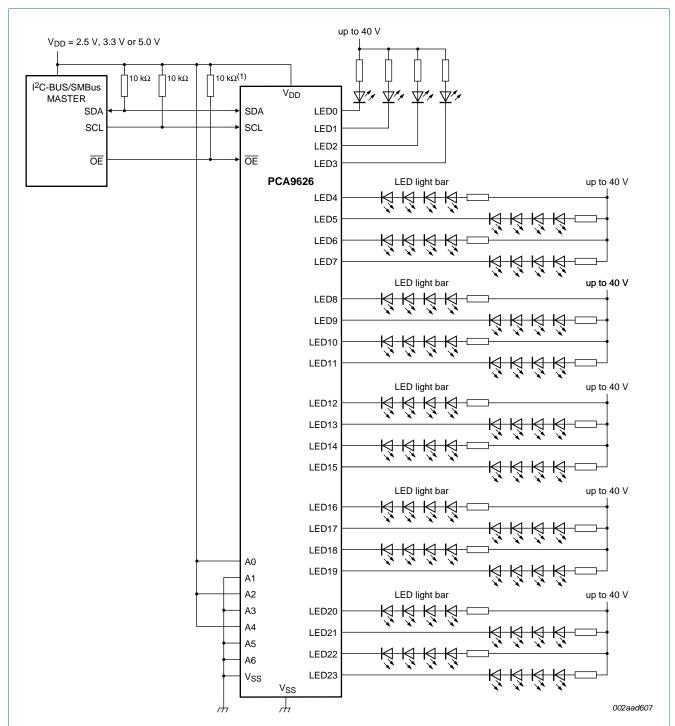

The PCA9626 is an I<sup>2</sup>C-bus controlled 24-bit LED driver optimized for voltage switch dimming and blinking 100 mA Red/Green/Blue/Amber (RGBA) LEDs. Each LED output has its own 8-bit resolution (256 steps) fixed frequency individual PWM controller that operates at 97 kHz with a duty cycle that is adjustable from 0 % to 99.6 % to allow the LED to be set to a specific brightness value. An additional 8-bit resolution (256 steps) group PWM controller has both a fixed frequency of 190 Hz and an adjustable frequency between 24 Hz to once every 10.73 seconds with a duty cycle that is adjustable from 0 % to 99.6 % that is used to either dim or blink all LEDs with the same value.

Each LED output can be off, on (no PWM control), set at its individual PWM controller value or at both individual and group PWM controller values. The PCA9626 operates with a supply voltage range of 2.3 V to 5.5 V and the 100 mA open-drain outputs allow voltages up to 40 V.

The PCA9626 is one of the first LED controller devices in a new Fast-mode Plus (Fm+) family. Fm+ devices offer higher frequency (up to 1 MHz) and more densely populated bus operation (up to 4000 pF).

The active LOW Output Enable input pin  $(\overline{OE})$  blinks all the LED outputs and can be used to externally PWM the outputs, which is useful when multiple devices must be dimmed or blinked together without using software control.

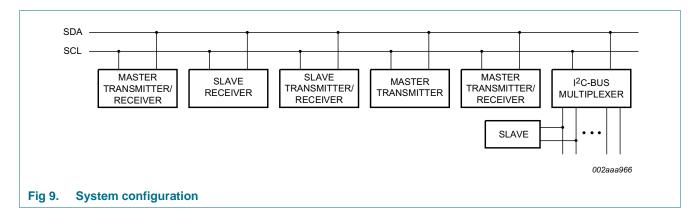

Software programmable LED Group and three Sub Call I<sup>2</sup>C-bus addresses allow all or defined groups of PCA9626 devices to respond to a common I<sup>2</sup>C-bus address, allowing for example, all red LEDs to be turned on or off at the same time or marquee chasing effect, thus minimizing I<sup>2</sup>C-bus commands. Seven hardware address pins allow up to 126 devices on the same bus.

The Software Reset (SWRST) Call allows the master to perform a reset of the PCA9626 through the I<sup>2</sup>C-bus, identical to the Power-On Reset (POR) that initializes the registers to their default state causing the output NAND FETs to be OFF (LED off). This allows an easy and quick way to reconfigure all device registers to the same condition.

In addition to these features found in PCA9633, PCA9634, PCA9635, PCA9622 and PCA9624, a new feature to control LED output pattern is incorporated in the PCA9626. A new control byte called 'Chase Byte' allows enabling or disabling of selective LED outputs depending on the value of the Chase Byte. This feature greatly reduces the number of bytes to be sent to the PCA9626 when repetitive patterns must be displayed as in creating a marquee chasing effect.

If the PCA9626 on-chip 100 mA NAND FETs do not provide enough current or voltage to drive the LEDs, then the PCA9634 and the PCA9635 with larger current or higher voltage external drivers can be used.

# 24-bit Fm+ I<sup>2</sup>C-bus 100 mA 40 V LED driver

### 2. Features and benefits

- 24 LED drivers. Each output programmable at:

- Off

- On

- Programmable LED brightness

- Programmable group dimming/blinking mixed with individual LED brightness

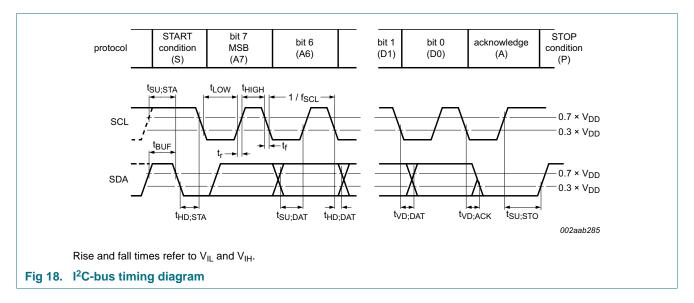

- 1 MHz Fast-mode Plus compatible I<sup>2</sup>C-bus interface with 30 mA high drive capability on SDA output for driving high capacitive buses

- 256-step (8-bit) linear programmable brightness per LED output varying from fully off (default) to maximum brightness using a 97 kHz PWM signal

- 256-step group brightness control allows general dimming (using a 190 Hz PWM signal) from fully off to maximum brightness (default)

- 256-step group blinking with frequency programmable from 24 Hz to 10.73 s and duty cycle from 0 % to 99.6 %

- 24 open-drain outputs can sink between 0 mA to 100 mA and are tolerant to a maximum off state voltage of 40 V. No input function.

- Output state change programmable on the Acknowledge or the STOP Command to update outputs byte-by-byte or all at the same time (default to 'Change on STOP').

- Active LOW Output Enable (OE) input pin allows for hardware blinking and dimming of the LEDs

- 7 hardware address pins allow 126 PCA9626 devices to be connected to the same I<sup>2</sup>C-bus and to be individually programmed

- 4 software programmable I<sup>2</sup>C-bus addresses (one LED Group Call address and three LED Sub Call addresses) allow groups of devices to be addressed at the same time in any combination (for example, one register used for 'All Call' so that all the PCA9626s on the I<sup>2</sup>C-bus can be addressed at the same time and the second register used for three different addresses so that <sup>1</sup>/<sub>3</sub> of all devices on the bus can be addressed at the same time in a group). Software enable and disable for I<sup>2</sup>C-bus address.

- A Chase Byte allows execution of predefined ON/OFF pattern for the 24 LED outputs

- Software Reset feature (SWRST Call) allows the device to be reset through the I<sup>2</sup>C-bus

- 25 MHz internal oscillator requires no external components

- Internal power-on reset

- Noise filter on SDA/SCL inputs

- No glitch on power-up

- Supports hot insertion

- Low standby current

- Operating power supply voltage (V<sub>DD</sub>) range of 2.3 V to 5.5 V

- 5.5 V tolerant inputs on non-LED pins

- -40 °C to +85 °C operation

- ESD protection exceeds 2000 V HBM per JESD22-A114 and 1000 V CDM per JESD22-C101

- Latch-up testing is done to JEDEC Standard JESD78 which exceeds 100 mA

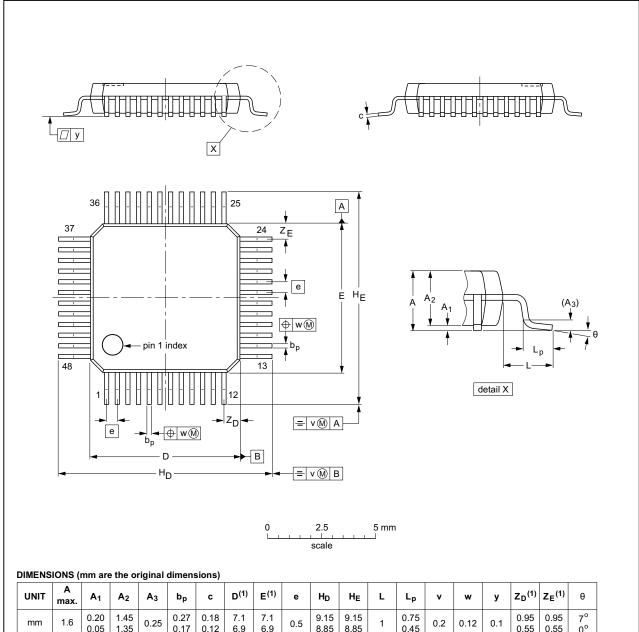

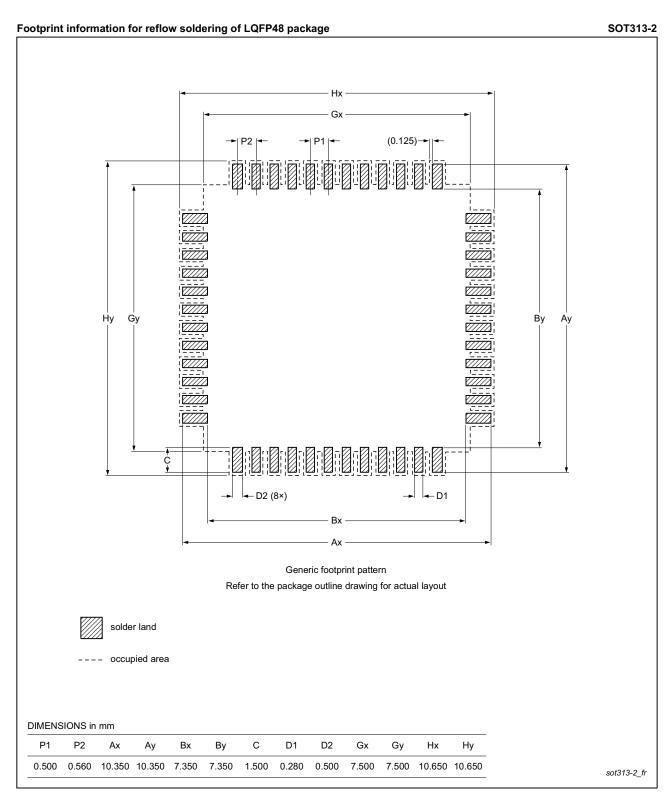

- Packages offered: LQFP48

## 24-bit Fm+ I<sup>2</sup>C-bus 100 mA 40 V LED driver

# 3. Applications

- RGB or RGBA LED drivers

- LED status information

- LED displays

- LCD backlights

- Keypad backlights for cellular phones or handheld devices

# 4. Ordering information

### Table 1. Ordering information

| Type number | Topside | Package |                                                                                          |          |

|-------------|---------|---------|------------------------------------------------------------------------------------------|----------|

|             | mark    | Name    | Description                                                                              | Version  |

| PCA9626B    | PCA9626 | LQFP48  | plastic low profile quad flat package; 48 leads; body $7 \times 7 \times 1.4 \text{ mm}$ | SOT313-2 |

# 4.1 Ordering options

### Table 2. Ordering options

| Type number | Orderable part number | Package |                                   | Minimum order quantity | Temperature                                                         |

|-------------|-----------------------|---------|-----------------------------------|------------------------|---------------------------------------------------------------------|

| PCA9626B    | PCA9626B,118          | LQFP48  | Reel 13" Q1/T1 *Standard mark SMD | 2000                   | $T_{amb} = -40  ^{\circ}\text{C} \text{ to } +85  ^{\circ}\text{C}$ |

# 24-bit Fm+ I<sup>2</sup>C-bus 100 mA 40 V LED driver

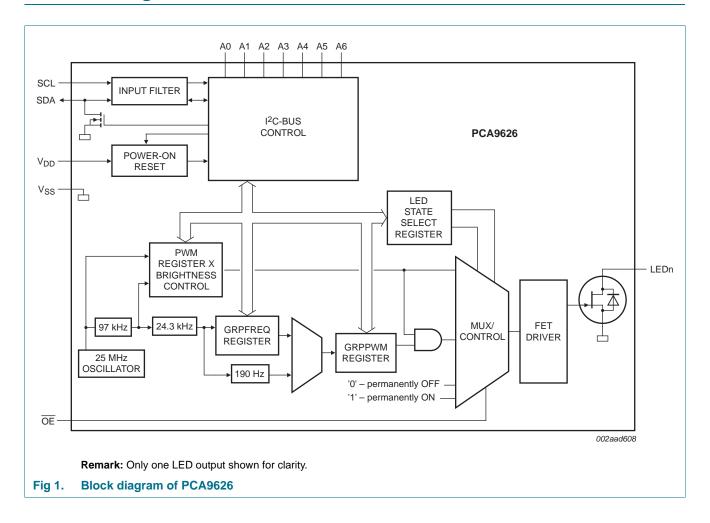

# 5. Block diagram

24-bit Fm+ I<sup>2</sup>C-bus 100 mA 40 V LED driver

# 6. Pinning information

# 6.1 Pinning

# 6.2 Pin description

Table 3. Pin description

| Symbol          | Pin                                             | Туре         | Description     |

|-----------------|-------------------------------------------------|--------------|-----------------|

| LED22           | 43                                              | 0            | LED driver 22   |

| LED23           | 44                                              | 0            | LED driver 23   |

| V <sub>SS</sub> | 1, 6, 7, 12, 16, 21, 25, 30, 31, 36, 37, 45, 48 | power supply | supply ground   |

| A0              | 46                                              | I            | address input 0 |

| A1              | 47                                              | I            | address input 1 |

| LED0            | 2                                               | 0            | LED driver 0    |

| LED1            | 3                                               | 0            | LED driver 1    |

| LED2            | 4                                               | 0            | LED driver 2    |

| LED3            | 5                                               | 0            | LED driver 3    |

| LED4            | 8                                               | 0            | LED driver 4    |

| LED5            | 9                                               | 0            | LED driver 5    |

| LED6            | 10                                              | 0            | LED driver 6    |

| LED7            | 11                                              | 0            | LED driver 7    |

| A2              | 13                                              | I            | address input 2 |

| A3              | 14                                              | I            | address input 3 |

## 24-bit Fm+ I<sup>2</sup>C-bus 100 mA 40 V LED driver

Table 3.

Pin description ...continued

| Symbol   | Pin | Туре         | Description              |

|----------|-----|--------------|--------------------------|

| A4       | 15  | I            | address input 4          |

| LED8     | 17  | 0            | LED driver 8             |

| LED9     | 18  | 0            | LED driver 9             |

| LED10    | 19  | 0            | LED driver 10            |

| LED11    | 20  | 0            | LED driver 11            |

| A5       | 22  | I            | address input 5          |

| A6       | 23  | I            | address input 6          |

| OE       | 24  | I            | active LOW output enable |

| LED12    | 26  | 0            | LED driver 12            |

| LED13    | 27  | 0            | LED driver 13            |

| LED14    | 28  | 0            | LED driver 14            |

| LED15    | 29  | 0            | LED driver 15            |

| LED16    | 32  | 0            | LED driver 16            |

| LED17    | 33  | 0            | LED driver 17            |

| LED18    | 34  | 0            | LED driver 18            |

| LED19    | 35  | 0            | LED driver 19            |

| SCL      | 38  | I            | serial clock line        |

| SDA      | 39  | I/O          | serial data line         |

| $V_{DD}$ | 40  | power supply | supply voltage           |

| LED20    | 41  | 0            | LED driver 20            |

| LED21    | 42  | 0            | LED driver 21            |

# 24-bit Fm+ I<sup>2</sup>C-bus 100 mA 40 V LED driver

# 7. Functional description

Refer to Figure 1 "Block diagram of PCA9626".

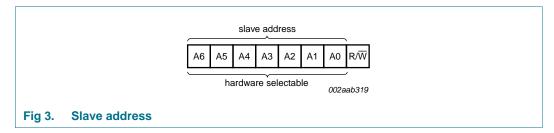

#### 7.1 Device addresses

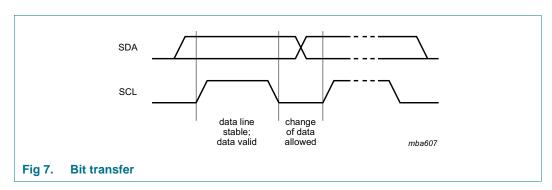

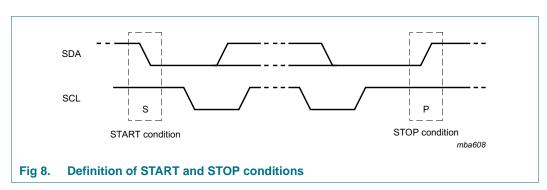

Following a START condition, the bus master must output the address of the slave it is accessing.

There are a maximum of 128 possible programmable addresses using the 7 hardware address pins. Two of these addresses, Software Reset and LED All Call, cannot be used because their default power-up state is ON, leaving a maximum of 126 addresses. Using other reserved addresses, as well as any other Sub Call address, reduces the total number of possible addresses even further.

### 7.1.1 Regular I<sup>2</sup>C-bus slave address

The I<sup>2</sup>C-bus slave address of the PCA9626 is shown in <u>Figure 3</u>. To conserve power, no internal pull-up resistors are incorporated on the hardware selectable address pins and they must be pulled HIGH or LOW externally.

**Remark:** Using reserved I<sup>2</sup>C-bus addresses interferes with other devices, but only if the devices are on the bus and/or the bus is open to other I<sup>2</sup>C-bus systems at some later date. In a closed system where the designer controls the address assignment these addresses can be used since the PCA9626 treats them like any other address. The LED All Call, Software Rest and PCA9564 or PCA9665 slave address (if on the bus) can never be used for individual device addresses.

- PCA9626 LED All Call address (1110 000) and Software Reset (0000 0110) which are active on start-up

- PCA9564 (0000 000) or PCA9665 (1110 000) slave address which is active on start-up

- 'reserved for future use' I<sup>2</sup>C-bus addresses (0000 011, 1111 1XX)

- slave devices that use the 10-bit addressing scheme (1111 0XX)

- slave devices that are designed to respond to the General Call address (0000 000)

- High-speed mode (Hs-mode) master code (0000 1XX)

The last bit of the address byte defines the operation to be performed. When set to logic 1 a read is selected, while a logic 0 selects a write operation.

### 24-bit Fm+ I2C-bus 100 mA 40 V LED driver

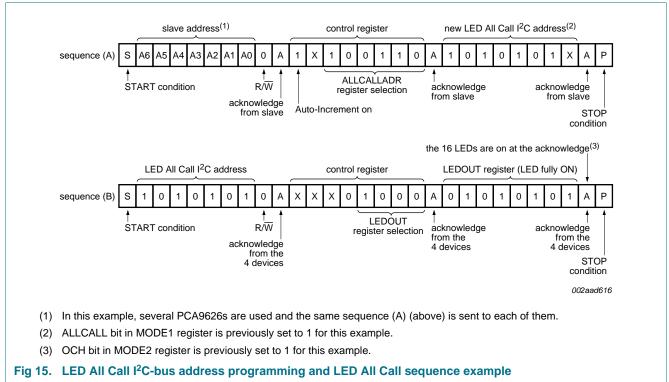

### 7.1.2 LED All Call I<sup>2</sup>C-bus address

- Default power-up value (ALLCALLADR register): E0h or 1110 000

- Programmable through I<sup>2</sup>C-bus (volatile programming)

- At power-up, LED All Call I<sup>2</sup>C-bus address is enabled. PCA9626 sends an ACK when E0h (R/W = 0) or E1h (R/W = 1) is sent by the master.

See Section 7.3.9 "ALLCALLADR, LED All Call I2C-bus address" for more detail.

**Remark:** The default LED All Call I<sup>2</sup>C-bus address (E0h or 1110 000) must not be used as a regular I<sup>2</sup>C-bus slave address since this address is enabled at power-up. All of the PCA9626s on the I<sup>2</sup>C-bus acknowledge the address if sent by the I<sup>2</sup>C-bus master.

### 7.1.3 LED Sub Call I<sup>2</sup>C-bus addresses

- 3 different I<sup>2</sup>C-bus addresses can be used

- Default power-up values:

- SUBADR1 register: E2h or 1110 001

- SUBADR2 register: E4h or 1110 010

- SUBADR3 register: E8h or 1110 100

- Programmable through I<sup>2</sup>C-bus (volatile programming)

- At power-up, Sub Call I<sup>2</sup>C-bus addresses are disabled. PCA9626 does not send an ACK when E2h (R/W = 0) or E3h (R/W = 1), E4h (R/W = 0) or E5h (R/W = 1), or E8h (R/W = 0) or E9h (R/W = 1) is sent by the master.

See Section 7.3.8 "SUBADR1 to SUBADR3, I2C-bus subaddress 1 to 3" for more detail.

**Remark:** The default LED Sub Call I<sup>2</sup>C-bus addresses may be used as regular I<sup>2</sup>C-bus slave addresses as long as they are disabled.

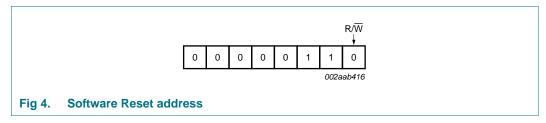

### 7.1.4 Software Reset I<sup>2</sup>C-bus address

The address shown in Figure 4 is used when a reset of the PCA9626 must be performed by the master. The Software Reset address (SWRST Call) must be used with  $R/\overline{W} = logic 0$ . If  $R/\overline{W} = logic 1$ , the PCA9626 does not acknowledge the SWRST. See Section 7.6 "Software reset" for more detail.

**Remark:** The Software Reset I<sup>2</sup>C-bus address is a reserved address and cannot be used as a regular I<sup>2</sup>C-bus slave address or as an LED All Call or LED Sub Call address.

## 24-bit Fm+ I<sup>2</sup>C-bus 100 mA 40 V LED driver

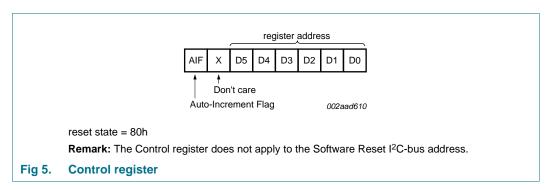

# 7.2 Control register

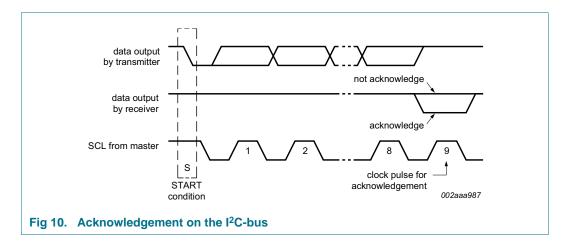

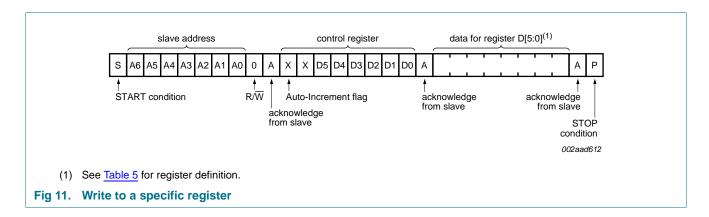

Following the successful acknowledgement of the slave address, LED All Call address or LED Sub Call address, the bus master sends a byte to the PCA9626, which is stored in the Control register.

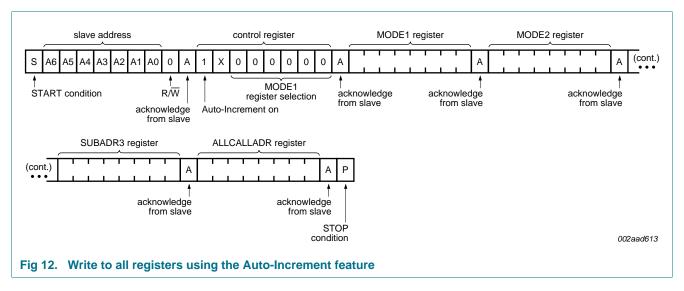

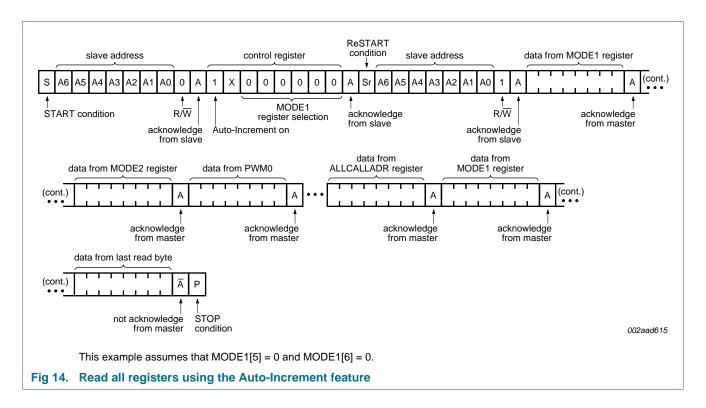

The lowest 6 bits are used as a pointer to determine which register is accessed (D[5:0]). The highest bit is used as Auto-Increment Flag (AIF).

This bit along with the MODE1 register bit 5 and bit 6 provide the Auto-Increment feature. Bit 6 of the Control register is not used.

When the Auto-Increment Flag is set (AIF = logic 1), the six low-order bits of the Control register are automatically incremented after a read or write. This allows the user to program the registers sequentially. Four different types of Auto-Increment are possible, depending on AI1 and AI0 values of MODE1 register.

Table 4. Auto-Increment options

| AIF | Al1[1] | AI0[1] | Function                                                                                                                                                           |

|-----|--------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | 0      | 0      | no Auto-Increment                                                                                                                                                  |

| 1   | 0      | 0      | Auto-Increment for all registers. D[5:0] roll over to 0h after the last register 26h is accessed.                                                                  |

| 1   | 0      | 1      | Auto-Increment for individual brightness registers only. D[5:0] roll over to 2h after the last register (19h) is accessed.                                         |

| 1   | 1      | 0      | Auto-Increment for global control registers and CHASE register. D[5:0] roll over to 1Ah after the last register (1Ch) is accessed.                                 |

| 1   | 1      | 1      | Auto-Increment for individual brightness registers; global control registers and CHASE register. D[5:0] roll over to 2h after the last register (1Ch) is accessed. |

[1] Al1 and Al0 come from MODE1 register.

**Remark:** Other combinations not shown in  $\underline{\text{Table 4}}$  (AIF + AI[1:0] = 001b, 010b, 011b and 111b) are reserved and must not be used for proper device operation.

AIF + AI[1:0] = 000b is used when the same register must be accessed several times during a single I<sup>2</sup>C-bus communication, for example, changes the brightness of a single LED. Data is overwritten each time the register is accessed during a write operation.

AIF + AI[1:0] = 100b is used when all the registers must be sequentially accessed, for example, power-up programming.

### 24-bit Fm+ I2C-bus 100 mA 40 V LED driver

AIF + AI[1:0] = 101b is used when the 16 LED drivers must be individually programmed with different values during the same I<sup>2</sup>C-bus communication, for example, changing color setting to another color setting.

AIF + AI[1:0] = 110b is used when the LED drivers must be globally programmed with different settings during the same I<sup>2</sup>C-bus communication, for example, global brightness or blinking change.

AIF + AI[1:0] = 111b is used when the 16 LED drivers must be individually programmed with different values in addition to global programming.

Only the 6 least significant bits D[5:0] are affected by the AIF, AI1 and AI0 bits.

When the Control register is written, the register entry point determined by D[5:0] is the first register that is addressed (read or write operation), and can be anywhere between 0h and 26h (as defined in <u>Table 5</u>). When AIF = 1, the Auto-Increment Flag is set and the rollover value at which the register increment stops and goes to the next one is determined by AIF, AI1 and AI2. See <u>Table 4</u> for rollover values. For example, if MODE1 register bit AI1 = 0 and AI0 = 1 and if the Control register = 1001 0010, then the register addressing sequence is (in hexadecimal):

$12 \to 13 \to ... \to 19 \to 02 \to 03 \to ... \to 19 \to 02$  ... as long as the master keeps sending or reading data.

# 7.3 Register definitions

Table 5. Register summary[1]

| Register number | D5 | D4 | D3 | D2 | D1 | D0 | Name  | Туре       | Function                 |

|-----------------|----|----|----|----|----|----|-------|------------|--------------------------|

| 00h             | 0  | 0  | 0  | 0  | 0  | 0  | MODE1 | read/write | Mode register 1          |

| 01h             | 0  | 0  | 0  | 0  | 0  | 1  | MODE2 | read/write | Mode register 2          |

| 02h             | 0  | 0  | 0  | 0  | 1  | 0  | PWM0  | read/write | brightness control LED0  |

| 03h             | 0  | 0  | 0  | 0  | 1  | 1  | PWM1  | read/write | brightness control LED1  |

| 04h             | 0  | 0  | 0  | 1  | 0  | 0  | PWM2  | read/write | brightness control LED2  |

| 05h             | 0  | 0  | 0  | 1  | 0  | 1  | PWM3  | read/write | brightness control LED3  |

| 06h             | 0  | 0  | 0  | 1  | 1  | 0  | PWM4  | read/write | brightness control LED4  |

| 07h             | 0  | 0  | 0  | 1  | 1  | 1  | PWM5  | read/write | brightness control LED5  |

| 08h             | 0  | 0  | 1  | 0  | 0  | 0  | PWM6  | read/write | brightness control LED6  |

| 09h             | 0  | 0  | 1  | 0  | 0  | 1  | PWM7  | read/write | brightness control LED7  |

| 0Ah             | 0  | 0  | 1  | 0  | 1  | 0  | PWM8  | read/write | brightness control LED8  |

| 0Bh             | 0  | 0  | 1  | 0  | 1  | 1  | PWM9  | read/write | brightness control LED9  |

| 0Ch             | 0  | 0  | 1  | 1  | 0  | 0  | PWM10 | read/write | brightness control LED10 |

| 0Dh             | 0  | 0  | 1  | 1  | 0  | 1  | PWM11 | read/write | brightness control LED11 |

| 0Eh             | 0  | 0  | 1  | 1  | 1  | 0  | PWM12 | read/write | brightness control LED12 |

| 0Fh             | 0  | 0  | 1  | 1  | 1  | 1  | PWM13 | read/write | brightness control LED13 |

| 10h             | 0  | 1  | 0  | 0  | 0  | 0  | PWM14 | read/write | brightness control LED14 |

| 11h             | 0  | 1  | 0  | 0  | 0  | 1  | PWM15 | read/write | brightness control LED15 |

| 12h             | 0  | 1  | 0  | 0  | 1  | 0  | PWM16 | read/write | brightness control LED16 |

| 13h             | 0  | 1  | 0  | 0  | 1  | 1  | PWM17 | read/write | brightness control LED17 |

| 14h             | 0  | 1  | 0  | 1  | 0  | 0  | PWM18 | read/write | brightness control LED18 |

PCA9626

# 24-bit Fm+ I<sup>2</sup>C-bus 100 mA 40 V LED driver

Table 5.

Register summary [1] ...continued

| Register number | D5 | D4 | D3 | D2 | D1 | D0 | Name       | Туре       | Function                                  |

|-----------------|----|----|----|----|----|----|------------|------------|-------------------------------------------|

| 15h             | 0  | 1  | 0  | 1  | 0  | 1  | PWM19      | read/write | brightness control LED19                  |

| 16h             | 0  | 1  | 0  | 1  | 1  | 0  | PWM20      | read/write | brightness control LED20                  |

| 17h             | 0  | 1  | 0  | 1  | 1  | 1  | PWM21      | read/write | brightness control LED21                  |

| 18h             | 0  | 1  | 1  | 0  | 0  | 0  | PWM22      | read/write | brightness control LED22                  |

| 19h             | 0  | 1  | 1  | 0  | 0  | 1  | PWM23      | read/write | brightness control LED23                  |

| 1Ah             | 0  | 1  | 1  | 0  | 1  | 0  | GRPPWM     | read/write | group duty cycle control                  |

| 1Bh             | 0  | 1  | 1  | 0  | 1  | 1  | GRPFREQ    | read/write | group frequency                           |

| 1Ch             | 0  | 1  | 1  | 1  | 0  | 0  | CHASE      | read/write | chase control                             |

| 1Dh             | 0  | 1  | 1  | 1  | 0  | 1  | LEDOUT0    | read/write | LED output state 0                        |

| 1Eh             | 0  | 1  | 1  | 1  | 1  | 0  | LEDOUT1    | read/write | LED output state 1                        |

| 1Fh             | 0  | 1  | 1  | 1  | 1  | 1  | LEDOUT2    | read/write | LED output state 2                        |

| 20h             | 1  | 0  | 0  | 0  | 0  | 0  | LEDOUT3    | read/write | LED output state 3                        |

| 21h             | 1  | 0  | 0  | 0  | 0  | 1  | LEDOUT4    | read/write | LED output state 4                        |

| 22h             | 1  | 0  | 0  | 0  | 1  | 0  | LEDOUT5    | read/write | LED output state 5                        |

| 23h             | 1  | 0  | 0  | 0  | 1  | 1  | SUBADR1    | read/write | I <sup>2</sup> C-bus subaddress 1         |

| 24h             | 1  | 0  | 0  | 1  | 0  | 0  | SUBADR2    | read/write | I <sup>2</sup> C-bus subaddress 2         |

| 25h             | 1  | 0  | 0  | 1  | 0  | 1  | SUBADR3    | read/write | I <sup>2</sup> C-bus subaddress 3         |

| 26h             | 1  | 0  | 0  | 1  | 1  | 0  | ALLCALLADR | read/write | LED All Call I <sup>2</sup> C-bus address |

<sup>[1]</sup> Only D[5:0] = 00 0000 to 10 0110 are allowed and are acknowledged. D[5:0] = 10 0111 to 11 1111 are reserved and may not be acknowledged.

### 24-bit Fm+ I<sup>2</sup>C-bus 100 mA 40 V LED driver

# 7.3.1 Mode register 1, MODE1

Table 6. MODE1 - Mode register 1 (address 00h) bit description Legend: \* default value.

| Bit | Symbol   | Access    | Value                               | Description                                                              |    |                                                                          |  |  |  |

|-----|----------|-----------|-------------------------------------|--------------------------------------------------------------------------|----|--------------------------------------------------------------------------|--|--|--|

| 7   | Al2      | read only | 0                                   | Register Auto-Increment disabled.                                        |    |                                                                          |  |  |  |

|     |          |           | 1*                                  | Register Auto-Increment enabled.                                         |    |                                                                          |  |  |  |

| 6   | Al1      | R/W       | 0*                                  | Auto-Increment bit $1 = 0$ . Auto-increment range as defined in Table 4. |    |                                                                          |  |  |  |

|     |          |           | 1                                   | Auto-Increment bit $1 = 1$ . Auto-increment range as defined in Table 4. |    |                                                                          |  |  |  |

| 5   | AIO R/W  |           | Al0 R/W 0* Auto-Increme in Table 4. |                                                                          | 0* | Auto-Increment bit $0 = 0$ . Auto-increment range as defined in Table 4. |  |  |  |

|     |          |           | 1                                   | Auto-Increment bit $0 = 1$ . Auto-increment range as define in Table 4.  |    |                                                                          |  |  |  |

| 4   | SLEEP[1] | R/W       | 0                                   | Normal mode[2].                                                          |    |                                                                          |  |  |  |

|     |          |           | 1*                                  | Low-power mode. Oscillator off[3].                                       |    |                                                                          |  |  |  |

| 3   | SUB1     | R/W       | 0*                                  | PCA9626 does not respond to I <sup>2</sup> C-bus subaddress 1.           |    |                                                                          |  |  |  |

|     |          |           | 1                                   | PCA9626 responds to I <sup>2</sup> C-bus subaddress 1.                   |    |                                                                          |  |  |  |

| 2   | SUB2     | R/W       | 0*                                  | PCA9626 does not respond to I <sup>2</sup> C-bus subaddress 2.           |    |                                                                          |  |  |  |

|     |          |           | 1                                   | PCA9626 responds to I <sup>2</sup> C-bus subaddress 2.                   |    |                                                                          |  |  |  |

| 1   | SUB3     | R/W       | 0*                                  | PCA9626 does not respond to I <sup>2</sup> C-bus subaddress 3.           |    |                                                                          |  |  |  |

|     |          |           | 1                                   | PCA9626 responds to I <sup>2</sup> C-bus subaddress 3.                   |    |                                                                          |  |  |  |

| 0   | ALLCALL  | R/W       | 0                                   | PCA9626 does not respond to LED All Call I <sup>2</sup> C-bus address.   |    |                                                                          |  |  |  |

|     |          |           | 1*                                  | PCA9626 responds to LED All Call I <sup>2</sup> C-bus address.           |    |                                                                          |  |  |  |

<sup>[1]</sup> Bit 4 must be programmed with logic 0 for proper device operation.

# 7.3.2 Mode register 2, MODE2

Table 7. MODE2 - Mode register 2 (address 01h) bit description Legend: \* default value.

| Bit | Symbol | Access    | Value | Description                       |

|-----|--------|-----------|-------|-----------------------------------|

| 7   | -      | read only | 0*    | reserved                          |

| 6   | -      | read only | 0*    | reserved                          |

| 5   | DMBLNK | R/W       | 0*    | group control = dimming.          |

|     |        |           | 1     | group control = blinking.         |

| 4   | INVRT  | read only | 0*    | reserved                          |

| 3   | OCH    | R/W       | 0*    | outputs change on STOP command[1] |

|     |        |           | 1     | outputs change on ACK             |

| 2   | -      | read only | 1*    | reserved                          |

| 1   | -      | read only | 0*    | reserved                          |

| 0   | -      | read only | 1*    | reserved                          |

<sup>[2]</sup> It takes 500 μs max. for the oscillator to be up and running once SLEEP bit has been set to logic 0. Timings on LEDn outputs are not guaranteed if PWMx, GRPPWM or GRPFREQ registers are accessed within the 500 μs window.

<sup>[3]</sup> No blinking or dimming is possible when the oscillator is off.

# 24-bit Fm+ I<sup>2</sup>C-bus 100 mA 40 V LED driver

[1] Change of the outputs at the STOP command allows synchronizing outputs of more than one PCA9626. Applicable to registers from 02h (PWM0) to 08h (LEDOUT) only.

### 7.3.3 PWM0 to PWM23, individual brightness control

Table 8. PWM0 to PWM23 - PWM registers 0 to 23 (address 02h to 19h) bit description Legend: \* default value.

| Address | Register | Bit | Symbol     | Access | Value      | Description                 |

|---------|----------|-----|------------|--------|------------|-----------------------------|

| 02h     | PWM0     | 7:0 | IDC0[7:0]  | R/W    | 0000 0000* | PWM0 Individual Duty Cycle  |

| 03h     | PWM1     | 7:0 | IDC1[7:0]  | R/W    | 0000 0000* | PWM1 Individual Duty Cycle  |

| 04h     | PWM2     | 7:0 | IDC2[7:0]  | R/W    | 0000 0000* | PWM2 Individual Duty Cycle  |

| 05h     | PWM3     | 7:0 | IDC3[7:0]  | R/W    | 0000 0000* | PWM3 Individual Duty Cycle  |

| 06h     | PWM4     | 7:0 | IDC4[7:0]  | R/W    | 0000 0000* | PWM4 Individual Duty Cycle  |

| 07h     | PWM5     | 7:0 | IDC5[7:0]  | R/W    | 0000 0000* | PWM5 Individual Duty Cycle  |

| 08h     | PWM6     | 7:0 | IDC6[7:0]  | R/W    | 0000 0000* | PWM6 Individual Duty Cycle  |

| 09h     | PWM7     | 7:0 | IDC7[7:0]  | R/W    | 0000 0000* | PWM7 Individual Duty Cycle  |

| 0Ah     | PWM8     | 7:0 | IDC8[7:0]  | R/W    | 0000 0000* | PWM8 Individual Duty Cycle  |

| 0Bh     | PWM9     | 7:0 | IDC9[7:0]  | R/W    | 0000 0000* | PWM9 Individual Duty Cycle  |

| 0Ch     | PWM10    | 7:0 | IDC10[7:0] | R/W    | 0000 0000* | PWM10 Individual Duty Cycle |

| 0Dh     | PWM11    | 7:0 | IDC11[7:0] | R/W    | 0000 0000* | PWM11 Individual Duty Cycle |

| 0Eh     | PWM12    | 7:0 | IDC12[7:0] | R/W    | 0000 0000* | PWM12 Individual Duty Cycle |

| 0Fh     | PWM13    | 7:0 | IDC13[7:0] | R/W    | 0000 0000* | PWM13 Individual Duty Cycle |

| 10h     | PWM14    | 7:0 | IDC14[7:0] | R/W    | 0000 0000* | PWM14 Individual Duty Cycle |

| 11h     | PWM15    | 7:0 | IDC15[7:0] | R/W    | 0000 0000* | PWM15 Individual Duty Cycle |

| 12h     | PWM16    | 7:0 | IDC16[7:0] | R/W    | 0000 0000* | PWM16 Individual Duty Cycle |

| 13h     | PWM17    | 7:0 | IDC17[7:0] | R/W    | 0000 0000* | PWM17 Individual Duty Cycle |

| 14h     | PWM18    | 7:0 | IDC18[7:0] | R/W    | 0000 0000* | PWM18 Individual Duty Cycle |

| 15h     | PWM19    | 7:0 | IDC19[7:0] | R/W    | 0000 0000* | PWM19 Individual Duty Cycle |

| 16h     | PWM20    | 7:0 | IDC20[7:0] | R/W    | 0000 0000* | PWM20 Individual Duty Cycle |

| 17h     | PWM21    | 7:0 | IDC21[7:0] | R/W    | 0000 0000* | PWM21 Individual Duty Cycle |

| 18h     | PWM22    | 7:0 | IDC22[7:0] | R/W    | 0000 0000* | PWM22 Individual Duty Cycle |

| 19h     | PWM23    | 7:0 | IDC23[7:0] | R/W    | 0000 0000* | PWM23 Individual Duty Cycle |

A 97 kHz fixed frequency signal is used for each output. Duty cycle is controlled through 256 linear steps from 00h (0 % duty cycle = LED output off) to FFh (99.6 % duty cycle = LED output at maximum brightness). Applicable to LED outputs programmed with LDRx = 10 or 11 (LEDOUT0 to LEDOUT5 registers).

$$duty\ cycle = \frac{IDCx[7:0]}{256} \tag{1}$$

### 24-bit Fm+ I2C-bus 100 mA 40 V LED driver

### 7.3.4 GRPPWM, group duty cycle control

Table 9. GRPPWM - Group brightness control register (address 1Ah) bit description Legend: \* default value

| Address | Register | Bit | Symbol   | Access | Value     | Description     |

|---------|----------|-----|----------|--------|-----------|-----------------|

| 1Ah     | GRPPWM   | 7:0 | GDC[7:0] | R/W    | 1111 1111 | GRPPWM register |

When DMBLNK bit (MODE2 register) is programmed with logic 0, a 190 Hz fixed frequency signal is superimposed with the 97 kHz individual brightness control signal. GRPPWM is then used as a global brightness control allowing the LED outputs to be dimmed with the same value. The value in GRPFREQ is then a 'Don't care'.

General brightness for the 16 outputs is controlled through 256 linear steps from 00h (0 % duty cycle = LED output off) to FFh (99.6 % duty cycle = maximum brightness). Applicable to LED outputs programmed with LDRx = 11 (LEDOUT0 to LEDOUT5 registers).

When DMBLNK bit is programmed with logic 1, GRPPWM and GRPFREQ registers define a global blinking pattern, where GRPFREQ contains the blinking period (from 24 Hz to 10.73 s) and GRPPWM the duty cycle (ON/OFF ratio in %).

$$duty\ cycle = \frac{GDC[7:0]}{256} \tag{2}$$

# 7.3.5 GRPFREQ, group frequency

Table 10. GRPFREQ - Group Frequency register (address 1Bh) bit description Legend: \* default value.

| Address | Register | Bit | Symbol    | Access | Value      | Description      |

|---------|----------|-----|-----------|--------|------------|------------------|

| 1Bh     | GRPFREQ  | 7:0 | GFRQ[7:0] | R/W    | 0000 0000* | GRPFREQ register |

GRPFREQ is used to program the global blinking period when DMBLNK bit (MODE2 register) is equal to 1. Value in this register is a 'Don't care' when DMBLNK = 0. Applicable to LED outputs programmed with LDRx = 11 (LEDOUT0 to LEDOUT5 registers).

Blinking period is controlled through 256 linear steps from 00h (41 ms, frequency 24 Hz) to FFh (10.73 s).

global blinking period =

$$\frac{GFRQ[7:0] + 1}{24}(s)$$

(3)

### 24-bit Fm+ I2C-bus 100 mA 40 V LED driver

### 7.3.6 CHASE control

Table 11. CHASE - Chase pattern control register (address 1Ch) bit description Legend: \* default value.

| Address | Register | Bit | Symbol   | Access | Value      | Description    |

|---------|----------|-----|----------|--------|------------|----------------|

| 1Ch     | CHASE    | 7:0 | CHC[7:0] | R/W    | 0000 0000* | CHASE register |

CHASE is used to program the LED output ON/OFF pattern. The contents of the CHASE register is used to enable one of the LED output patterns, as indicated in Table 12.

By repeated, sequential access to this table via the CHASE register, a chase pattern, for example, marquee effect, can be easily programmed with minimal number of commands. Once the CHASE register is accessed, the data bytes that follow are used as an index value to pick the LED output patterns defined by <a href="Table 12">Table 12</a> "CHASE sequence".

This register always updates on ACK. It is used to gate the  $\overline{\text{OE}}$  signal at each of the LEDn pins such that:

- $\overline{OE}$  = 1: all LEDs are off

- $\overline{\text{OE}}$  = 0: those LEDs corresponding to the Xs in Table 12 are on

Any write to this register takes effect at the ACK.

Product data sheet

Table 12. CHASE sequence X = enabled; empty cell = disabled.

| Co                                                                        | ommand | Hex | LEC | ) cha | anne | I  |                  |    |    |    |    |                  |                  |    |    |                     |    |                     |                  |    |    |    |    |    |    |    | Description                         |

|---------------------------------------------------------------------------|--------|-----|-----|-------|------|----|------------------|----|----|----|----|------------------|------------------|----|----|---------------------|----|---------------------|------------------|----|----|----|----|----|----|----|-------------------------------------|

|                                                                           |        |     | 00  | 01    | 02   | 03 | 04               | 05 | 06 | 07 | 08 | 09               | 10               | 11 | 12 | 13                  | 14 | 15                  | 16               | 17 | 18 | 19 | 20 | 21 | 22 | 23 |                                     |

| 00                                                                        | )      | 00  | Χ   | Χ     | Χ    | Χ  | Χ                | Χ  | Χ  | Χ  | Χ  | Χ                | Χ                | Χ  | Χ  | Χ                   | Χ  | Χ                   | Χ                | Χ  | Х  | Х  | Х  | Χ  | Χ  | Χ  | all LEDs ON                         |

| 01                                                                        |        | 01  |     |       |      |    |                  |    |    |    |    |                  |                  |    |    |                     |    |                     |                  |    |    |    |    |    |    |    | all LEDs OFF                        |

| 02                                                                        | 2      | 02  |     | Χ     |      | Χ  |                  | Χ  |    | Χ  |    | Χ                |                  | Χ  |    | Χ                   |    | Χ                   |                  | Χ  |    | Х  |    | Χ  |    | Χ  | ½ chase B                           |

| 03                                                                        | 3      | 03  | Χ   |       | Χ    |    | Х                |    | Χ  |    | Χ  |                  | Χ                |    | Χ  |                     | Χ  |                     | Χ                |    | Χ  |    | Χ  |    | Χ  |    | ½ chase A                           |

| 04                                                                        | 1      | 04  |     |       | Χ    |    |                  | Χ  |    |    | Χ  |                  |                  | Χ  |    |                     | Χ  |                     |                  | Χ  |    |    | Х  |    |    | Χ  | ¹/₃ chase C                         |

| 05                                                                        | 5      | 05  |     | Χ     |      |    | Χ                |    |    | Χ  |    |                  | Χ                |    |    | Χ                   |    |                     | Χ                |    |    | Χ  |    |    | Χ  |    | ¹/₃ chase B                         |

| 06                                                                        | 6      | 06  | Χ   |       |      | Χ  |                  |    | Χ  |    |    | Χ                |                  |    | Χ  |                     |    | Χ                   |                  |    | Χ  |    |    | Χ  |    |    | ¹/₃ chase A                         |

| All information provided in this document is subject to legal disclaimers | 7      | 07  | Х   |       |      |    |                  |    |    |    |    |                  |                  |    |    |                     |    |                     |                  |    |    |    |    |    |    |    | LTR_0_ON<br>(1× Left to Right_START |

| nation 08                                                                 | 3      | 80  |     | Χ     |      |    |                  |    |    |    |    |                  |                  |    |    |                     |    |                     |                  |    |    |    |    |    |    |    | LTR_1_ON                            |

| orovide 09                                                                | )      | 09  |     |       | Χ    |    |                  |    |    |    |    |                  |                  |    |    |                     |    |                     |                  |    |    |    |    |    |    |    | LTR_2_ON                            |

| 10<br>15                                                                  | )      | 0A  |     |       |      | Χ  |                  |    |    |    |    |                  |                  |    |    |                     |    |                     |                  |    |    |    |    |    |    |    | LTR_3_ON                            |

| ි<br>වූ 11                                                                |        | 0B  |     |       |      |    | Χ                |    |    |    |    |                  |                  |    |    |                     |    |                     |                  |    |    |    |    |    |    |    | LTR_4_ON                            |

| ment is                                                                   | 2      | 0C  |     |       |      |    |                  | Χ  |    |    |    |                  |                  |    |    |                     |    |                     |                  |    |    |    |    |    |    |    | LTR_5_ON                            |

| 13                                                                        | 3      | 0D  |     |       |      |    |                  |    | Χ  |    |    |                  |                  |    |    |                     |    |                     |                  |    |    |    |    |    |    |    | LTR_6_ON                            |

| ਰ<br>ਰ<br>ਹ                                                               | ļ      | 0E  |     |       |      |    |                  |    |    | Χ  |    |                  |                  |    |    |                     |    |                     |                  |    |    |    |    |    |    |    | LTR_7_ON                            |

| al disc                                                                   | 5      | 0F  |     |       |      |    |                  |    |    |    | Χ  |                  |                  |    |    |                     |    |                     |                  |    |    |    |    |    |    |    | LTR_8_ON                            |

| laimers 16                                                                | 6      | 10  |     |       |      |    |                  |    |    |    |    | Χ                |                  |    |    |                     |    |                     |                  |    |    |    |    |    |    |    | LTR_9_ON                            |

| 17                                                                        | 7      | 11  |     |       |      |    |                  |    |    |    |    |                  | Χ                |    |    |                     |    |                     |                  |    |    |    |    |    |    |    | LTR_10_ON                           |

| 18                                                                        | 3      | 12  |     |       |      |    |                  |    |    |    |    |                  |                  | Χ  |    |                     |    |                     |                  |    |    |    |    |    |    |    | LTR_11_ON                           |

| 19                                                                        | )      | 13  |     |       |      |    |                  |    |    |    |    |                  |                  |    | Χ  |                     |    |                     |                  |    |    |    |    |    |    |    | LTR_12_ON                           |

|                                                                           | )      | 14  |     |       |      |    |                  |    |    |    |    |                  |                  |    |    | Χ                   |    |                     |                  |    |    |    |    |    |    |    | LTR_13_ON                           |

| <sup>ΧΡ</sup> <sub>νει</sub> 21                                           |        | 15  |     |       |      |    | $\mathbb{L}^{-}$ |    |    |    |    | $\mathbb{L}^{-}$ | $\mathbb{L}^{-}$ |    |    | $\mathbb{L}^{\top}$ | X  | $\mathbb{L}^{\top}$ | $\mathbb{L}^{-}$ |    |    |    |    |    |    |    | LTR_14_ON                           |

| © NXP Semiconductors N.V. 2014. All rights reserved.                      | 2      | 16  |     |       |      |    |                  |    |    |    |    |                  |                  |    |    |                     |    | Х                   |                  |    |    |    |    |    |    |    | LTR_15_ON                           |

| ct 23                                                                     | 3      | 17  |     |       |      |    |                  |    |    |    |    |                  |                  |    |    |                     |    |                     | Х                |    |    |    |    |    |    |    | LTR_16_ON                           |

| .×. 24                                                                    | 1      | 18  |     |       |      |    |                  |    |    |    |    |                  |                  |    |    |                     |    |                     |                  | Χ  |    |    |    |    |    |    | LTR_17_ON                           |

| <sup>3</sup> / <sub>≜</sub> 25                                            | 5      | 19  |     |       |      |    |                  |    |    |    |    |                  |                  |    |    |                     |    |                     |                  |    | Χ  |    |    |    |    |    | LTR_18_ON                           |

| rights 26                                                                 | 3      | 1A  |     |       |      |    |                  |    |    |    |    |                  |                  |    |    |                     |    |                     |                  |    |    | Х  |    |    |    |    | LTR_19_ON                           |

| <sup>res</sup> 27                                                         | 7      | 1B  |     |       |      |    |                  |    |    |    |    |                  |                  |    |    |                     |    |                     |                  |    |    |    | Х  |    |    |    | LTR_20_ON                           |

**Table 12. CHASE sequence** ...continued X = enabled; empty cell = disabled.

|                                         | Command | Hex | LEI | O cha | anne | ı  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    | Description                         |

|-----------------------------------------|---------|-----|-----|-------|------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|-------------------------------------|

|                                         |         |     | 00  | 01    | 02   | 03 | 04 | 05 | 06 | 07 | 80 | 09 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 |                                     |

|                                         | 28      | 1C  |     |       |      |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    | Χ  |    |    | LTR_21_ON                           |

|                                         | 29      | 1D  |     |       |      |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    | Χ  |    | LTR_22_ON                           |

|                                         | 30      | 1E  |     |       |      |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    | X  | LTR_23_ON<br>(1× Left to Right_END) |

|                                         | 31      | 1F  | Χ   | Χ     |      |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    | 2× Left to Right_START              |

|                                         | 32      | 20  |     |       | Χ    | Χ  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |                                     |

|                                         | 33      | 21  |     |       |      |    | Χ  | Χ  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |                                     |

|                                         | 34      | 22  |     |       |      |    |    |    | Χ  | Χ  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |                                     |

| 2                                       | 35      | 23  |     |       |      |    |    |    |    |    | Χ  | Χ  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |                                     |

|                                         | 36      | 24  |     |       |      |    |    |    |    |    |    |    | Χ  | Χ  |    |    |    |    |    |    |    |    |    |    |    |    |                                     |

| Ī                                       | 37      | 25  |     |       |      |    |    |    |    |    |    |    |    |    | Χ  | Χ  |    |    |    |    |    |    |    |    |    |    |                                     |

|                                         | 38      | 26  |     |       |      |    |    |    |    |    |    |    |    |    |    |    | Χ  | Χ  |    |    |    |    |    |    |    |    |                                     |

| -                                       | 39      | 27  |     |       |      |    |    |    |    |    |    |    |    |    |    |    |    |    | Χ  | Χ  |    |    |    |    |    |    |                                     |

|                                         | 40      | 28  |     |       |      |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    | Χ  | Χ  |    |    |    |    |                                     |

| >====================================== | 41      | 29  |     |       |      |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    | Χ  | Χ  |    |    |                                     |

|                                         | 42      | 2A  |     |       |      |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    | Χ  | Χ  | 2× Left to Right_END                |

|                                         | 43      | 2B  | Χ   | Χ     | Χ    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    | 3× Left to Right_STAR               |

|                                         | 44      | 2C  |     |       |      | Χ  | Χ  | Χ  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |                                     |

|                                         | 45      | 2D  |     |       |      |    |    |    | Χ  | Χ  | Χ  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |                                     |

|                                         | 46      | 2E  |     |       |      |    |    |    |    |    |    | Χ  | Χ  | Χ  |    |    |    |    |    |    |    |    |    |    |    |    |                                     |

|                                         | 47      | 2F  |     |       |      |    |    |    |    |    |    |    |    |    | Χ  | Χ  | Χ  |    |    |    |    |    |    |    |    |    |                                     |

|                                         | 48      | 30  |     |       |      |    |    |    |    |    |    |    |    |    |    |    |    | Х  | Χ  | Х  |    |    |    |    |    |    |                                     |

|                                         | 49      | 31  |     |       |      |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    | Х  | Х  | Х  |    |    |    |                                     |

|                                         | 50      | 32  |     |       |      |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    | Χ  | Х  | Χ  | 3× Left to Right_END                |

| .                                       | 51      | 33  | Х   | Χ     | Х    | Х  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    | 4× Left to Right_STAR               |

|                                         | 52      | 34  |     |       |      |    | Х  | Х  | Χ  | Χ  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |                                     |

|                                         | 53      | 35  |     |       |      |    |    |    |    |    | Χ  | Χ  | Χ  | Х  |    |    |    |    |    |    |    |    |    |    |    |    |                                     |

|                                         | 54      | 36  |     |       |      |    |    |    |    |    |    |    |    |    | Х  | Х  | Χ  | Χ  |    |    |    |    |    |    |    |    |                                     |

|                                         | 55      | 37  |     |       |      |    |    |    |    |    |    |    |    |    |    |    |    |    | Χ  | Χ  | Χ  | Χ  |    |    |    |    |                                     |

| Command | Hex | LEC | ) cha | anne | ŀ  |    |    |    |    |    |                     |    |    |                     |    |    |    |    |    |    |                     |                     |                     |    |                  | Description            |

|---------|-----|-----|-------|------|----|----|----|----|----|----|---------------------|----|----|---------------------|----|----|----|----|----|----|---------------------|---------------------|---------------------|----|------------------|------------------------|

|         |     | 00  | 01    | 02   | 03 | 04 | 05 | 06 | 07 | 08 | 09                  | 10 | 11 | 12                  | 13 | 14 | 15 | 16 | 17 | 18 | 19                  | 20                  | 21                  | 22 | 23               | -                      |

| 56      | 38  |     |       |      |    |    |    |    |    |    |                     |    |    |                     |    |    |    |    |    |    |                     | Χ                   | Χ                   | Χ  | Χ                | 4× Left to Right_END   |

| 57      | 39  | Χ   | Χ     | Χ    | Χ  | Χ  |    |    |    |    |                     |    |    |                     |    |    |    |    |    |    |                     |                     |                     |    |                  | 5× Left to Right_START |

| 58      | ЗА  |     |       |      |    |    | Χ  | Χ  | Χ  | Χ  | Χ                   |    |    |                     |    |    |    |    |    |    |                     |                     |                     |    |                  |                        |

| 59      | 3B  |     |       |      |    |    |    |    |    |    |                     | Χ  | Χ  | Χ                   | Χ  | Χ  |    |    |    |    |                     |                     |                     |    |                  |                        |

| 60      | 3C  |     |       |      |    |    |    |    |    |    |                     |    |    |                     |    |    | Χ  | Χ  | Χ  | Χ  | Χ                   |                     |                     |    |                  |                        |

| 61      | 3D  |     |       |      |    |    |    |    |    |    |                     |    |    |                     |    |    |    |    |    |    |                     | Χ                   | Χ                   | Χ  | Χ                | 5× Left to Right_END   |

| 62      | 3E  | Χ   | Χ     | Χ    | Х  | Χ  | Χ  |    |    |    |                     |    |    |                     |    |    |    |    |    |    |                     |                     |                     |    |                  | 6× Left to Right_START |

| 63      | 3F  |     |       |      |    |    |    | Χ  | Χ  | Χ  | Χ                   | Χ  | Χ  |                     |    |    |    |    |    |    |                     |                     |                     |    |                  |                        |

| 64      | 40  |     |       |      |    |    |    |    |    |    |                     |    |    | Χ                   | Χ  | Χ  | Χ  | Χ  | Χ  |    |                     |                     |                     |    |                  |                        |

| 65      | 41  |     |       |      |    |    |    |    |    |    |                     |    |    |                     |    |    |    |    |    | Χ  | Χ                   | Χ                   | Χ                   | Χ  | Χ                | 6× Left to Right_END   |

| 66      | 42  | Χ   |       |      |    |    |    |    |    |    |                     |    |    |                     |    |    |    |    |    |    |                     |                     |                     |    | Χ                | 1× Implode_START       |

| 67      | 43  |     | Χ     |      |    |    |    |    |    |    |                     |    |    |                     |    |    |    |    |    |    |                     |                     |                     | Χ  |                  |                        |

| 68      | 44  |     |       | Χ    |    |    |    |    |    |    |                     |    |    |                     |    |    |    |    |    |    |                     |                     | Χ                   |    |                  |                        |

| 69      | 45  |     |       |      | Х  |    |    |    |    |    |                     |    |    |                     |    |    |    |    |    |    |                     | Χ                   |                     |    |                  |                        |

| 70      | 46  |     |       |      |    | Χ  |    |    |    |    |                     |    |    |                     |    |    |    |    |    |    | Χ                   |                     |                     |    |                  |                        |

| 71      | 47  |     |       |      |    |    | Χ  |    |    |    |                     |    |    |                     |    |    |    |    |    | Χ  |                     |                     |                     |    |                  |                        |

| 72      | 48  |     |       |      |    |    |    | Χ  |    |    |                     |    |    |                     |    |    |    |    | Χ  |    |                     |                     |                     |    |                  |                        |

| 73      | 49  |     |       |      |    |    |    |    | Х  |    |                     |    |    |                     |    |    |    | Χ  |    |    |                     |                     |                     |    |                  |                        |

| 74      | 4A  |     |       |      |    |    |    |    |    | Χ  |                     |    |    |                     |    |    | Χ  |    |    |    |                     |                     |                     |    |                  |                        |

| 75      | 4B  |     |       |      |    |    |    |    |    |    | Χ                   |    |    |                     |    | Χ  |    |    |    |    |                     |                     |                     |    |                  |                        |

| 76      | 4C  |     |       |      |    |    |    |    |    |    |                     | Χ  |    |                     | Χ  |    |    |    |    |    |                     |                     |                     |    |                  |                        |

| 77      | 4D  |     |       |      |    |    |    |    |    |    |                     |    | Χ  | Χ                   |    |    |    |    |    |    |                     |                     |                     |    |                  | 1× Implode_END         |

| 78      | 4E  | Χ   | Χ     |      |    |    |    |    |    |    |                     |    |    |                     |    |    |    |    |    |    |                     |                     |                     | Χ  | Х                | 2× Implode_START       |

| 79      | 4F  |     |       | Χ    | Χ  |    |    |    |    |    |                     |    |    |                     |    |    |    |    |    |    |                     | Χ                   | Χ                   |    |                  |                        |

| 80      | 50  |     |       |      |    | Х  | Χ  |    |    |    |                     |    |    |                     |    |    |    |    |    | Х  | Χ                   |                     |                     |    |                  |                        |

| 81      | 51  |     |       |      |    |    |    | Х  | Х  |    | $\mathbb{L}^{\top}$ |    |    | $\mathbb{L}^{\top}$ |    |    |    | Χ  | Χ  |    | $\mathbb{L}^{\top}$ | $\mathbb{L}^{\top}$ | $\mathbb{L}^{\top}$ |    | $\mathbb{L}^{-}$ |                        |

| 82      | 52  |     |       |      |    |    |    |    |    | Χ  | Χ                   |    |    |                     |    | Χ  | Χ  |    |    |    |                     |                     |                     |    |                  |                        |

| 83      | 53  |     |       |      |    |    |    |    |    |    |                     | Χ  | Χ  | Х                   | Χ  |    |    |    |    |    |                     |                     |                     |    |                  |                        |

| 84      | 54  |     |       |      |    |    |    |    |    |    |                     |    | Х  | Χ                   |    |    |    |    |    |    |                     |                     |                     |    |                  | 2× Implode_END         |

**Table 12. CHASE sequence** ...continued X = enabled; empty cell = disabled.

| Command | Hex | LEC | ) cha | anne | I  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    | Description           |

|---------|-----|-----|-------|------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|-----------------------|

|         |     | 00  | 01    | 02   | 03 | 04 | 05 | 06 | 07 | 80 | 09 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 |                       |

| 85      | 55  | Χ   | Χ     | Χ    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    | Χ  | Χ  | Χ  | 3× Implode_START      |

| 86      | 56  |     |       |      | Χ  | Χ  | Χ  |    |    |    |    |    |    |    |    |    |    |    |    | Χ  | Χ  | Χ  |    |    |    |                       |

| 87      | 57  |     |       |      |    |    |    | Χ  | Χ  | Χ  |    |    |    |    |    |    | Χ  | Χ  | Χ  |    |    |    |    |    |    |                       |

| 88      | 58  |     |       |      |    |    |    |    |    |    | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  |    |    |    |    |    |    |    |    |    |                       |

| 89      | 59  |     |       |      |    |    |    |    |    |    |    | Χ  | Χ  | Χ  | Χ  |    |    |    |    |    |    |    |    |    |    |                       |

| 90      | 5A  |     |       |      |    |    |    |    |    |    |    |    | Χ  | Χ  |    |    |    |    |    |    |    |    |    |    |    | 3× Implode_END        |

| 91      | 5B  | Χ   | Χ     | Χ    | Χ  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    | Χ  | Χ  | Χ  | Χ  | 4× Implode_START      |

| 92      | 5C  |     |       |      |    | Χ  | Χ  | Χ  | Χ  |    |    |    |    |    |    |    |    | Χ  | Χ  | Χ  | Χ  |    |    |    |    |                       |

| 93      | 5D  |     |       |      |    |    |    |    |    | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  |    |    |    |    |    |    |    |    |                       |

| 94      | 5E  |     |       |      |    |    |    |    |    |    |    | Χ  | Χ  | Χ  | Χ  |    |    |    |    |    |    |    |    |    |    |                       |

| 95      | 5F  |     |       |      |    |    |    |    |    |    |    |    | Χ  | Χ  |    |    |    |    |    |    |    |    |    |    |    | 4× Implode_END        |

| 96      | 60  | Χ   |       |      |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    | Left to Right_WIPE_ST |

| 97      | 61  | Χ   | Χ     |      |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |                       |

| 98      | 62  | Χ   | Χ     | Χ    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |                       |

| 99      | 63  | Χ   | Χ     | Χ    | Χ  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |                       |

| 100     | 64  | Χ   | Χ     | Χ    | Χ  | Χ  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |                       |

| 101     | 65  | Χ   | Χ     | Χ    | Χ  | Χ  | Χ  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |                       |

| 102     | 66  | Χ   | Χ     | Χ    | Χ  | Χ  | Χ  | Χ  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |                       |

| 103     | 67  | Χ   | Χ     | Χ    | Χ  | Χ  | Χ  | Χ  | Χ  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |                       |

| 104     | 68  | Χ   | Χ     | Χ    | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |                       |

| 105     | 69  | Χ   | Χ     | Χ    | Х  | Χ  | Χ  | Х  | Χ  | Χ  | Х  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |                       |

| 106     | 6A  | Χ   | Χ     | Χ    | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  |    |    |    |    |    |    |    |    |    |    |    |    |    |                       |

| 107     | 6B  | Χ   | Χ     | Χ    | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  |    |    |    |    |    |    |    |    |    |    |    |    |                       |

| 108     | 6C  | Х   | Х     | Χ    | Х  | Χ  | Χ  | Х  | Х  | Х  | Х  | Χ  | Х  | Х  |    |    |    |    |    |    |    |    |    |    |    |                       |

| 109     | 6D  | Х   | Х     | Χ    | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х  |    |    |    |    |    |    |    |    |    |    |                       |

| 110     | 6E  | Χ   | Χ     | Х    | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х  |    |    |    |    |    |    |    |    |    |                       |

| 111     | 6F  | Х   | Χ     | Х    | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х  |    |    |    |    |    |    |    |    |                       |

| 112     | 70  | Х   | Χ     | Х    | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х  |    |    |    |    |    |    |    |                       |

| 113     | 71  | Χ   | Χ     | Χ    | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  |    |    |    |    |    |    |                       |

Product data sheet

Product data sheet

24-bit Fm+ I<sup>2</sup>C-bus 100 mA 40 V LED driver

**Table 12. CHASE sequence** ...continued X = enabled; empty cell = disabled.

| Command | Hex | LED | ) cha | anne | el |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    | Description              |

|---------|-----|-----|-------|------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|--------------------------|

|         |     | 00  | 01    | 02   | 03 | 04 | 05 | 06 | 07 | 08 | 09 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 |                          |

| 114     | 72  | Χ   | Χ     | Х    | Х  | Х  | Χ  | Х  | Χ  | Х  | Χ  | Χ  | Χ  | Χ  | Χ  | Х  | Χ  | Χ  | Х  | Χ  |    |    |    |    |    |                          |

| 115     | 73  | Χ   | Χ     | Χ    | Χ  | Х  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  |    |    |    |    |                          |

| 116     | 74  | Χ   | Χ     | Χ    | Χ  | Х  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  |    |    |    |                          |

| 117     | 75  | Χ   | Χ     | Х    | Х  | Х  | Χ  | Χ  | Χ  | Χ  | Χ  | Х  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Х  | Χ  | Χ  | Χ  | Χ  |    |    |                          |

| 118     | 76  | Χ   | Χ     | Х    | Х  | Х  | Χ  | Х  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  |    |                          |

| 119     | 77  | Х   | Χ     | Х    | Х  | Х  | Χ  | Χ  | Χ  | Х  | Х  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Х  | Χ  | Χ  | Χ  | Χ  | Left to Right_WIPE_END   |

| 120     | 78  |     |       |      |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    | Χ  | Right to Left_WIPE_START |

| 121     | 79  |     |       |      |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    | Χ  | Χ  |                          |

| 122     | 7A  |     |       |      |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    | Χ  | Χ  | Χ  |                          |

| 123     | 7B  |     |       |      |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    | Χ  | Χ  | Χ  | Χ  |                          |

| 124     | 7C  |     |       |      |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    | Χ  | Χ  | Χ  | Χ  | Χ  |                          |

| 125     | 7D  |     |       |      |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  |                          |

| 126     | 7E  |     |       |      |    |    |    |    |    |    |    |    |    |    |    |    |    |    | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  |                          |

| 127     | 7F  |     |       |      |    |    |    |    |    |    |    |    |    |    |    |    |    | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  |                          |

| 128     | 80  |     |       |      |    |    |    |    |    |    |    |    |    |    |    |    | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  |                          |

| 129     | 81  |     |       |      |    |    |    |    |    |    |    |    |    |    |    | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  |                          |

| 130     | 82  |     |       |      |    |    |    |    |    |    |    |    |    |    | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  |                          |

| 131     | 83  |     |       |      |    |    |    |    |    |    |    |    |    | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  |                          |

| 132     | 84  |     |       |      |    |    |    |    |    |    |    |    | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  |                          |

| 133     | 85  |     |       |      |    |    |    |    |    |    |    | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  |                          |

| 134     | 86  |     |       |      |    |    |    |    |    |    | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  |                          |

| 135     | 87  |     |       |      |    |    |    |    |    | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  |                          |

| 136     | 88  |     |       |      |    |    |    |    | Х  | Х  | Х  | Х  | Χ  | Х  | Х  | Х  | X  | Χ  | Х  | Χ  | Χ  | Χ  | Х  | Χ  | Х  |                          |

| 137     | 89  |     |       |      |    |    |    | Χ  | Χ  | X  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  |                          |

| 138     | 8A  |     |       |      |    |    | Х  | Х  | Χ  | X  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Х  | Χ  | Χ  |                          |

| 139     | 8B  |     |       |      |    | Х  | Х  | Х  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  |                          |

| 140     | 8C  |     |       |      | Χ  | Х  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  |                          |

| 141     | 8D  |     |       | Χ    | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  |                          |

NXP

Semiconductors

| Command | Hex | LE | ) ch | anne | I  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    | Description                                                                                                                        |

|---------|-----|----|------|------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|------------------------------------------------------------------------------------------------------------------------------------|

|         |     | 00 | 01   | 02   | 03 | 04 | 05 | 06 | 07 | 80 | 09 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 |                                                                                                                                    |

| 142     | 8E  |    | Χ    | Χ    | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  |                                                                                                                                    |

| 143     | 8F  | Χ  | Χ    | Χ    | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Right to Left_WIPE_END                                                                                                             |

| 144     | 90  |    |      |      |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    | All LED outputs disabled for CHASE byte = 90h to FFh. Reserved for future use. CHASE byte = FFh is used to exit the CHASE mode.[1] |

<sup>[1]</sup> When the PCA9626 exits from the CHASE mode, the previous states of the LED outputs are retained.

### 24-bit Fm+ I<sup>2</sup>C-bus 100 mA 40 V LED driver

# 7.3.7 LEDOUT0 to LEDOUT5, LED driver output state

Table 13. LEDOUT0 to LEDOUT5 - LED driver output state register (address 1Dh to 22h) bit description

Legend: \* default value.

| Address | Register | Bit | Symbol | Access | Value | Description                |

|---------|----------|-----|--------|--------|-------|----------------------------|

| 1Dh     | LEDOUT0  | 7:6 | LDR3   | R/W    | 00*   | LED3 output state control  |

|         |          | 5:4 | LDR2   | R/W    | 00*   | LED2 output state control  |

|         |          | 3:2 | LDR1   | R/W    | 00*   | LED1 output state control  |

|         |          | 1:0 | LDR0   | R/W    | 00*   | LED0 output state control  |

| 1Eh     | LEDOUT1  | 7:6 | LDR7   | R/W    | 00*   | LED7 output state control  |

|         |          | 5:4 | LDR6   | R/W    | 00*   | LED6 output state control  |

|         |          | 3:2 | LDR5   | R/W    | 00*   | LED5 output state control  |

|         |          | 1:0 | LDR4   | R/W    | 00*   | LED4 output state control  |

| 1Fh     | LEDOUT2  | 7:6 | LDR11  | R/W    | 00*   | LED11 output state control |

|         |          | 5:4 | LDR10  | R/W    | 00*   | LED10 output state control |

|         |          | 3:2 | LDR9   | R/W    | 00*   | LED9 output state control  |

|         |          | 1:0 | LDR8   | R/W    | 00*   | LED8 output state control  |

| 20h     | LEDOUT3  | 7:6 | LDR15  | R/W    | 00*   | LED15 output state control |

|         |          | 5:4 | LDR14  | R/W    | 00*   | LED14 output state control |

|         |          | 3:2 | LDR13  | R/W    | 00*   | LED13 output state control |

|         |          | 1:0 | LDR12  | R/W    | 00*   | LED12 output state control |

| 21h     | LEDOUT4  | 7:6 | LDR19  | R/W    | 00*   | LED19 output state control |