# UV INDEX AND AMBIENT LIGHT SENSOR IC WITH I<sup>2</sup>C INTERFACE

#### Features

- Integrated UV index sensor

- Digital UV Index register that can be read through I<sup>2</sup>C interface

- Factory calibration to address part-to-part variation

- Integrated ambient light sensor

- 100 mlx resolution possible, allowing operation under dark glass

- 1 to 128 klx dynamic range possible across two ADC range settings

- Accurate lux measurements with IR correction algorithm

- Industry's lowest power consumption

- 1.71 to 3.6 V supply voltage

- < 500 nA standby current</p>

- Internal and external wake support

- Built-in voltage supply monitor and power-on reset controller

- I<sup>2</sup>C Serial communications

- Up to 3.4 Mbps data rate

- Slave mode hardware address decoding

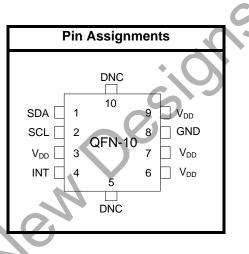

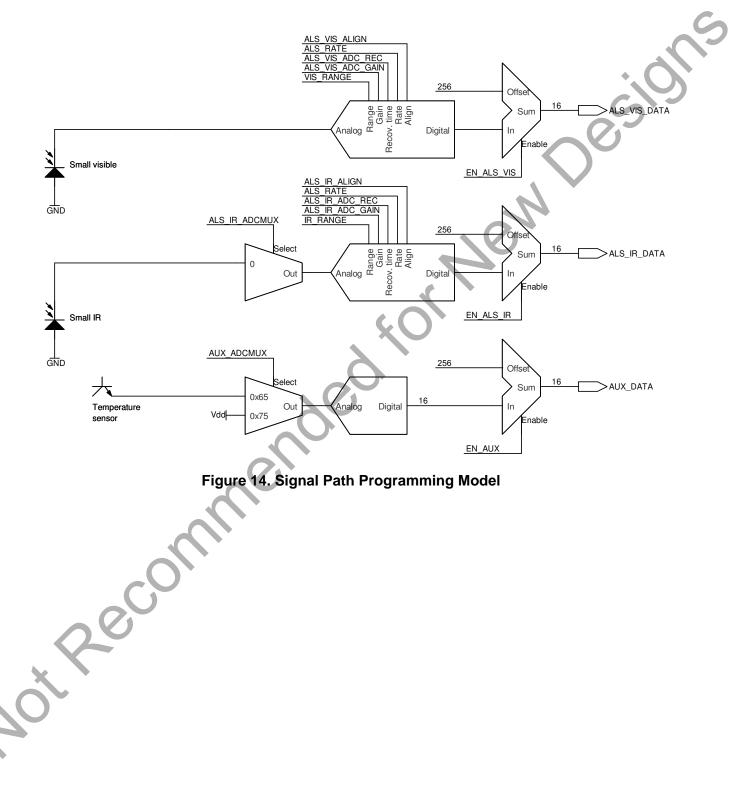

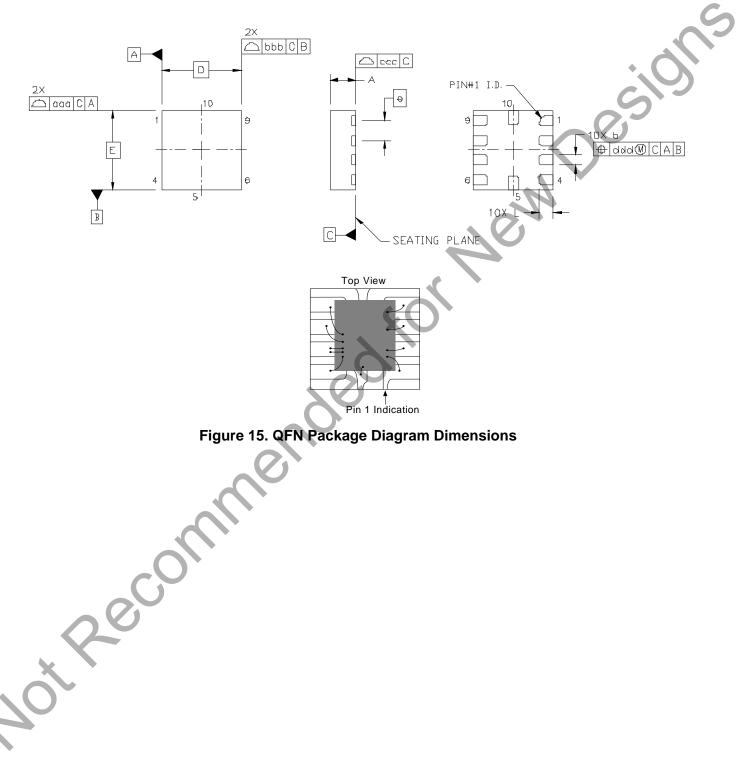

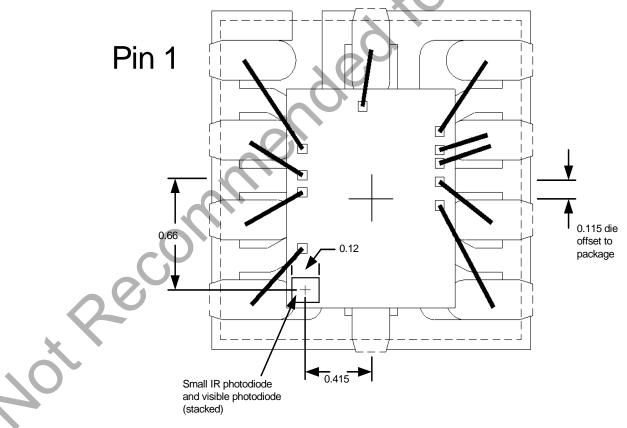

- Small-outline 10-lead 2x2 mm QFN

- Temperature Range

- -40 to +85 °C

#### Applications

- Fitness/health electronics

- Smart watches

- Smartphone handsets

- Tablets

- Portable consumer electronics

- Display-backlighting control

#### Description

The Si1132 is a low-power, ultraviolet (UV) index, and ambient light sensor with  $I^2C$  digital interface and programmable-event interrupt output. This sensor IC includes an analog-to-digital converter, integrated high-sensitivity visible and infrared photodiodes, and digital signal processor. The Si1132 offers excellent performance under a wide dynamic range and a variety of light sources including direct sunlight. The Si1132 can also work under dark glass covers. The photodiode response and associated digital conversion circuitry provide excellent immunity to artificial light flicker noise and natural light flutter noise. The Si1132 devices are provided in a 10-lead 2x2 mm QFN package and are capable of operation from 1.71 to 3.6 V over the -40 to +85 °C temperature range.

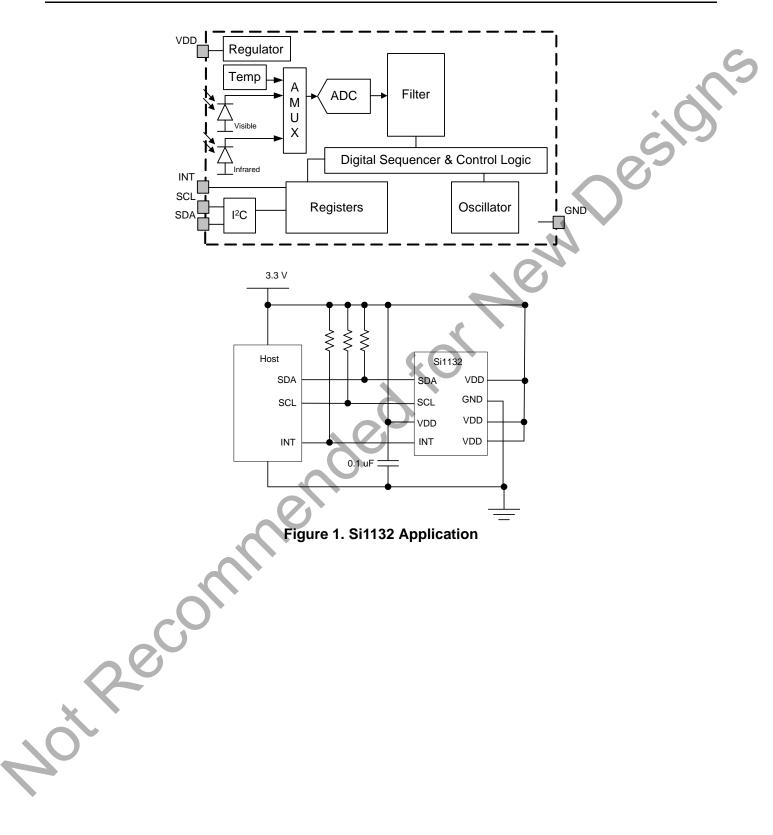

## **Functional Block Diagram**

# TABLE OF CONTENTS

| 1. Electrical Specifications                                                                                                                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1. Performance Tables                                                                                                                                                                               |

| 1.2. Typical Performance Graphs                                                                                                                                                                       |

| 2. Functional Description                                                                                                                                                                             |

| 2.1. Introduction                                                                                                                                                                                     |

| 2.2. Ambient Light                                                                                                                                                                                    |

| 2.3. Ultraviolet (UV) Index                                                                                                                                                                           |

| 2.4. Host Interface                                                                                                                                                                                   |

| 3. Operational Modes                                                                                                                                                                                  |

| 3.1. Off Mode                                                                                                                                                                                         |

| 3.2. Initialization Mode                                                                                                                                                                              |

| 3.3. Standby Mode                                                                                                                                                                                     |

| 3.4. Forced Conversion Mode                                                                                                                                                                           |

| 3.5. Autonomous Operation Mode                                                                                                                                                                        |

| 4. Programming Guide                                                                                                                                                                                  |

| 4.1. Command and Response Structure                                                                                                                                                                   |

| 4.2. Command Protocol                                                                                                                                                                                 |

| 4.3. Resource Summary                                                                                                                                                                                 |

| 4.4. Signal Path Software Model                                                                                                                                                                       |

| 4.5. I <sup>2</sup> C Registers                                                                                                                                                                       |

| 4.4. Signal Fail Software Model       23         4.5. I <sup>2</sup> C Registers       24         4.6. Parameter RAM       35         5. Pin Descriptions       42         6. Ordering Guide       43 |

| 5. Pin Descriptions                                                                                                                                                                                   |

| 6. Ordering Guide                                                                                                                                                                                     |

| 7. Package Outline: 10-Pin QFN                                                                                                                                                                        |

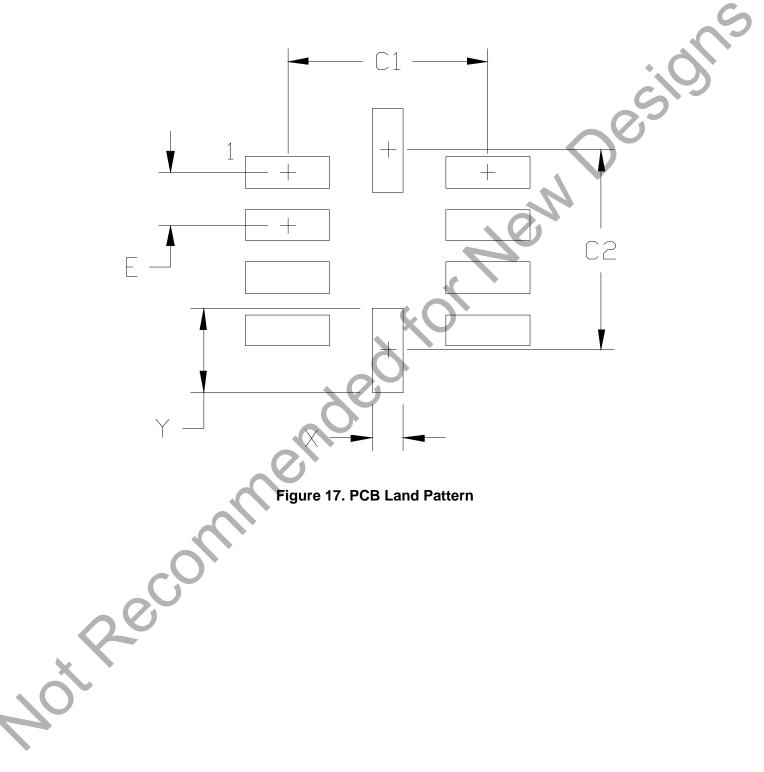

| 8. Suggested PCB Land Pattern                                                                                                                                                                         |

| Document Change List                                                                                                                                                                                  |

| Contact Information                                                                                                                                                                                   |

|                                                                                                                                                                                                       |

|                                                                                                                                                                                                       |

|                                                                                                                                                                                                       |

|                                                                                                                                                                                                       |

|                                                                                                                                                                                                       |

|                                                                                                                                                                                                       |

|                                                                                                                                                                                                       |

|                                                                                                                                                                                                       |

|                                                                                                                                                                                                       |

| NotRecoli                                                                                                                                                                                             |

|                                                                                                                                                                                                       |

|                                                                                                                                                                                                       |

|                                                                                                                                                                                                       |

# **1. Electrical Specifications**

## 1.1. Performance Tables

### **Table 1. Recommended Operating Conditions**

| Parameter                             | Symbol                          | Test Condition                          | Min                  | Tun | Мах                  | Unit |

|---------------------------------------|---------------------------------|-----------------------------------------|----------------------|-----|----------------------|------|

| Falameter                             | Symbol                          | Test condition                          | IVIIII               | Тур | IVIAX                | Unit |

| V <sub>DD</sub> Supply Voltage        | $V_{DD}$                        |                                         | 1.71                 | _   | 3.6 🔷                | V    |

| V <sub>DD</sub> OFF Supply Voltage    | $V_{DD_OFF}$                    | OFF mode                                | -0.3                 |     | 1.0                  | V    |

| V <sub>DD</sub> Supply Ripple Voltage |                                 | V <sub>DD</sub> = 3.3 V<br>1 kHz–10 MHz |                      |     | 50                   | mVpp |

| Operating Temperature                 | Т                               |                                         | -40                  | 25  | 85                   | °C   |

| SCL, SDA, Input High Logic<br>Voltage | I <sup>2</sup> C <sub>VIH</sub> |                                         | V <sub>DD</sub> x0.7 | 7   | V <sub>DD</sub>      | V    |

| SCL, SDA Input Low Logic<br>Voltage   | $I^2 C_{VIL}$                   |                                         | 0                    | _   | V <sub>DD</sub> x0.3 | V    |

| Operation under Direct Sunlight       | Edc                             | *                                       | _                    | _   | 128                  | klx  |

| Start-Up Time                         |                                 | V <sub>DD</sub> above 1.71 V            | 25                   | —   |                      | ms   |

## Table 2. Performance Characteristics<sup>1</sup>

| Parameter                            | Symbol              | Test Condition                                                                         | Min | Тур | Мах  | Unit |

|--------------------------------------|---------------------|----------------------------------------------------------------------------------------|-----|-----|------|------|

| I <sub>DD</sub> OFF Mode             | I <sub>off</sub>    | V <sub>DD</sub> < V <sub>DD_OFF</sub> (leakage from SCL,<br>SDA, and INT not included) | _   | 240 | 1000 | nA   |

| I <sub>DD</sub> Standby Mode         | I <sub>sb</sub>     | No ALS Conversions<br>No I <sup>2</sup> C Activity<br>$V_{DD} = 1.8 V$                 | —   | 150 | 500  | nA   |

| I <sub>DD</sub> Standby Mode         | I <sub>sb</sub>     | No ALS Conversions<br>No I <sup>2</sup> C Activity<br>V <sub>DD</sub> =3.3 V           |     | 1.4 |      | μA   |

| I <sub>DD</sub> Actively Measuring   | I <sub>active</sub> | V <sub>DD</sub> = 3.3 V                                                                | _   | 4.3 | 5.5  | mA   |

| INT, SCL, SDA<br>Leakage Current     |                     | V <sub>DD</sub> = 3.3 V                                                                | -1  | _   | 1    | μA   |

| Actively Measuring Time <sup>2</sup> |                     | UV or ALS VIS + ALS IR                                                                 | _   | 285 |      | μs   |

|                                      |                     |                                                                                        |     |     |      |      |

Notes:

1.

Unless specifically stated in "Conditions", electrical data assumes ambient light levels < 1 klx. Represents the time during which the device is drawing a current equal to  $I_{active}$  for power estimation purposes. 2. Assumes default settings.

| Table 2. Performance | Characteristics <sup>1</sup> | (Continued) |

|----------------------|------------------------------|-------------|

|----------------------|------------------------------|-------------|

| Parameter                             | Symbol | Test Condition                                                | Min | Тур    | Max | Unit                                |

|---------------------------------------|--------|---------------------------------------------------------------|-----|--------|-----|-------------------------------------|

| Visible Photodiode<br>Response        |        | Sunlight<br>ALS_VIS_ADC_GAIN=0<br>VIS_RANGE=0                 | _   | 0.282  | _   | ADC<br>counts/<br>lux               |

|                                       |        | 2500K incandescent bulb<br>ALS_VIS_ADC_GAIN=0<br>VIS_RANGE=0  | _   | 0.319  | C   | ADC<br>counts/<br>lux               |

|                                       |        | "Cool white" fluorescent<br>ALS_VIS_ADC_GAIN=0<br>VIS_RANGE=0 | _   | 0.146  | G   | ADC<br>counts/<br>lux               |

|                                       |        | Infrared LED (875 nm)<br>ALS_VIS_ADC_GAIN=0<br>VIS_RANGE=0    | -   | 8.277  | _   | ADC<br>counts.<br>m <sup>2</sup> /W |

| Small Infrared Photodiode<br>Response |        | Sunlight<br>ALS_IR_ADC_GAIN=0<br>IR_RANGE=0                   | -   | 2.44   | _   | ADC<br>counts/<br>lux               |

|                                       |        | 2500K incandescent bulb<br>ALS_IR_ADC_GAIN=0<br>IR_RANGE=0    | _   | 8.46   | _   | ADC<br>counts/<br>lux               |

|                                       |        | "Cool white" fluorescent<br>ALS_IR_ADC_GAIN=0<br>IR_RANGE=0   | _   | 0.71   | _   | ADC<br>counts/<br>lux               |

|                                       |        | Infrared LED (875 nm)<br>ALS_IR_ADC_GAIN=0<br>IR_RANGE=0      | _   | 452.38 | _   | ADC<br>counts.<br>m <sup>2</sup> /W |

| Visible Photodiode Noise              |        | All gain settings                                             | _   | 7      | _   | ADC<br>counts<br>RMS                |

| Small Infrared Photodiode<br>Noise    |        | All gain settings                                             | _   | 1      | _   | ADC<br>counts<br>RMS                |

Unless specifically stated in "Conditions", electrical data assumes ambient light levels < 1 klx.</li>

Represents the time during which the device is drawing a current equal to I<sub>active</sub> for power estimation purposes. Assumes default settings.

## Table 2. Performance Characteristics<sup>1</sup> (Continued)

| Parameter                 | Symbol          | Test Condition                             | Min               | Тур    | Max                 | Unit    |

|---------------------------|-----------------|--------------------------------------------|-------------------|--------|---------------------|---------|

| Visible Photodiode Offset |                 | VIS_RANGE=0                                | _                 |        | _                   | ADC     |

| Drift                     |                 | ALS_VIS_ADC_GAIN=0                         |                   | -0.3   |                     | counts/ |

|                           |                 | ALS_VIS_ADC_GAIN=1                         |                   | -0.11  |                     | O°      |

|                           |                 | ALS_VIS_ADC_GAIN=2                         |                   | -0.06  |                     |         |

|                           |                 | ALS_VIS_ADC_GAIN=3                         |                   | -0.03  |                     |         |

|                           |                 | ALS_VIS_ADC_GAIN=4                         |                   | -0.01  | C                   |         |

|                           |                 | ALS_VIS_ADC_GAIN=5                         |                   | -0.008 | 0                   |         |

|                           |                 | ALS_VIS_ADC_GAIN=6                         |                   | -0.007 | $\mathbf{O}$        |         |

|                           |                 | ALS_VIS_ADC_GAIN=7                         |                   | -0.008 |                     |         |

| Small Infrared Photodiode |                 | IR_RANGE=0                                 | —                 |        | _                   | ADC     |

| Offset Drift              |                 | IR_GAIN=0                                  |                   | -0.3   |                     | counts/ |

|                           |                 | IR_GAIN=1                                  |                   | -0.06  |                     | °C      |

|                           |                 | IR_GAIN=2                                  | $\mathcal{O}_{1}$ | -0.03  |                     |         |

|                           |                 | IR_GAIN=3                                  |                   | -0.01  |                     |         |

| SCL, SDA, INT Output Low  | V <sub>OL</sub> | I = 4 mA, V <sub>DD</sub> > 2.0 V          | _                 |        | V <sub>DD</sub> x0. | V       |

| Voltage                   | 0L              | $I = 4 \text{ mA}, V_{DD} < 2.0 \text{ V}$ | _                 | _      | 2                   | V       |

|                           |                 |                                            |                   |        | 0.4                 |         |

| Temperature Sensor Offset |                 | 25 °C                                      |                   | 11136  |                     | ADC     |

|                           |                 |                                            |                   |        |                     | counts  |

| Temperature Sensor Gain   |                 | ~~~~                                       |                   | 35     |                     | ADC     |

| •                         |                 |                                            |                   |        |                     | counts/ |

|                           |                 |                                            |                   |        |                     | °C      |

| Notes:                    | ļļ              |                                            | Į                 | ļ      | ļ                   | Į       |

#### otes:

NotRecom

Unless specifically stated in "Conditions", electrical data assumes ambient light levels < 1 klx.</li>

Represents the time during which the device is drawing a current equal to I<sub>active</sub> for power estimation purposes. Assumes default settings.

# Table 3. I<sup>2</sup>C Timing Specifications

| Parameter                  | Symbol              | Min | Тур | Max  | Unit |

|----------------------------|---------------------|-----|-----|------|------|

| Clock Frequency            | f <sub>SCL</sub>    | 95  | —   | 3400 | kHz  |

| Clock Pulse Width Low      | t <sub>LOW</sub>    | 160 |     | —    | ns   |

| Clock Pulse Width High     | t <sub>ніGн</sub>   | 60  | —   | -    | ns   |

| Rise Time                  | t <sub>R</sub>      | 10  | —   | 40   | ns   |

| Fall Time                  | t <sub>F</sub>      | 10  | —   | 40   | ns   |

| Start Condition Hold Time  | t <sub>HD.STA</sub> | 160 | -   |      | ns   |

| Start Condition Setup Time | t <sub>SU.STA</sub> | 160 | _   | V-   | ns   |

| Input Data Setup Time      | t <sub>SU.DAT</sub> | 10  | A   |      | ns   |

| Input Data Hold Time       | t <sub>HD.DAT</sub> | 0   |     | —    | ns   |

| Stop Condition Setup Time  | t <sub>SU.STO</sub> | 160 | / _ | —    | ns   |

## Table 4. Absolute Maximum Limits

| Parameter                      | Test Condition                                   | Min  | Тур | Max      | Unit    |

|--------------------------------|--------------------------------------------------|------|-----|----------|---------|

| V <sub>DD</sub> Supply Voltage |                                                  | -0.3 | —   | 4        | V       |

| Operating Temperature          |                                                  | -40  | —   | 85       | °C      |

| Storage Temperature            | XO                                               | -65  | —   | 85       | °C      |

| INT, SCL, SDA Voltage          | at V <sub>DD</sub> = 0 V, T <sub>A</sub> < 85 °C | -0.5 | _   | 3.6      | V       |

| ESD Rating                     | Human Body Model<br>Machine Model                | _    | _   | 2<br>225 | kV<br>V |

|                                | Charged-Device Model                             | —    |     | 2        | kV      |

NotRecom

## **1.2. Typical Performance Graphs**

# 2. Functional Description

## 2.1. Introduction

The Si1132 is a UV index and ambient light sensor whose operational state is controlled through registers accessible through the I<sup>2</sup>C interface. The host can command the Si1132 to initiate on-demand UV index sensing or ambient light sensing. The host can also place the Si1132 in an autonomous operational state where it performs measurements at set intervals and interrupts the host after each measurement is completed. This results in an overall system power saving allowing the host controller to operate longer in its sleep state instead of polling the Si1132. For more details, refer to "AN498: Si114x Designer's Guide".

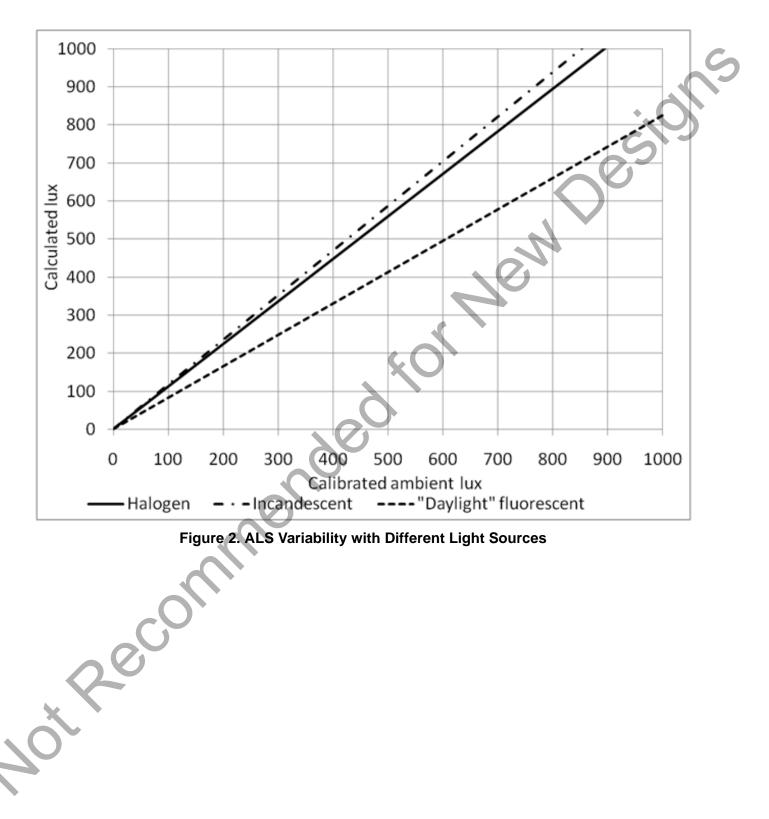

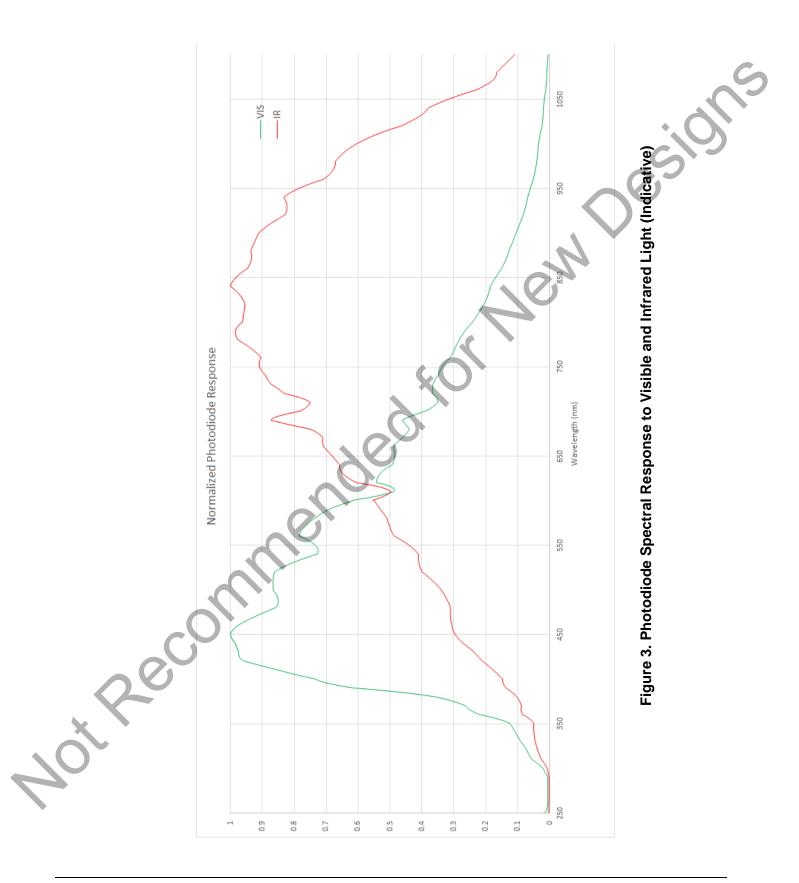

## 2.2. Ambient Light

The Si1132 has photodiodes capable of measuring both visible and infrared light. However, the visible photodiode is also influenced by infrared light. The measurement of illuminance requires the same spectral response as the human eye. If an accurate lux measurement is desired, the extra IR response of the visible-light photodiode must be compensated. Therefore, to allow the host to make corrections to the infrared light's influence, the Si1132 reports the infrared light measurement on a separate channel. The separate visible and IR photodiodes lend themselves to a variety of algorithmic solutions. The host can then take these two measurements and run an algorithm to derive an equivalent lux level as perceived by a human eye. Having the IR correction algorithm running in the host allows for the most flexibility in adjusting for system-dependent variables. For example, if the glass used in the system blocks visible light more than infrared light, the IR correction needs to be adjusted.

If the host is not making any infrared corrections, the infrared measurement can be turned off in the CHLIST parameter.

By default, the measurement parameters are optimized for indoor ambient light levels where it is possible to detect light levels as low as 6 lx. For operation under direct sunlight, the ADC can be programmed to operate in a high signal operation so that it is possible to measure direct sunlight without overflowing the 16-bit result.

For low-light applications, it is possible to increase the ADC integration time. Normally, the integration time is 25.6  $\mu$ s. By increasing this integration time to 410  $\mu$ s, the ADC can detect light levels as low as 1 lx. The ADC can be programmed with an integration time as high as 3.28 ms, allowing measurement to 100 mlx light levels. The ADC integration time for the Visible Light Ambient measurement can be programmed independently of the ADC integration time of the Infrared Light Ambient measurement. The independent ADC parameters allow operation under glass covers having a higher transmittance to Infrared Light than Visible Light.

When operating in the lower signal range, or when the integration time is increased, it is possible to saturate the ADC when the ambient light suddenly increases. Any overflow condition is reported in the RESPONSE register, and the corresponding data registers report a value of 0xFFFF. Based on either of these two overflow indicators, the host can adjust the ADC sensitivity. However, the overflow condition is not sticky. If the light levels return to a range within the capabilities of the ADC, the corresponding data registers begin to operate normally. The RESPONSE register will continue to hold the overflow condition until a NOP command is received. Even if the RESPONSE register has an overflow condition, commands are still accepted and processed.

The Si1132 can initiate ALS measurements either when explicitly commanded by the host or periodically through an autonomous process. Refer to "3. Operational Modes" on page 15 for additional details of the Si1132's Operational Modes.

## 2.3. Ultraviolet (UV) Index

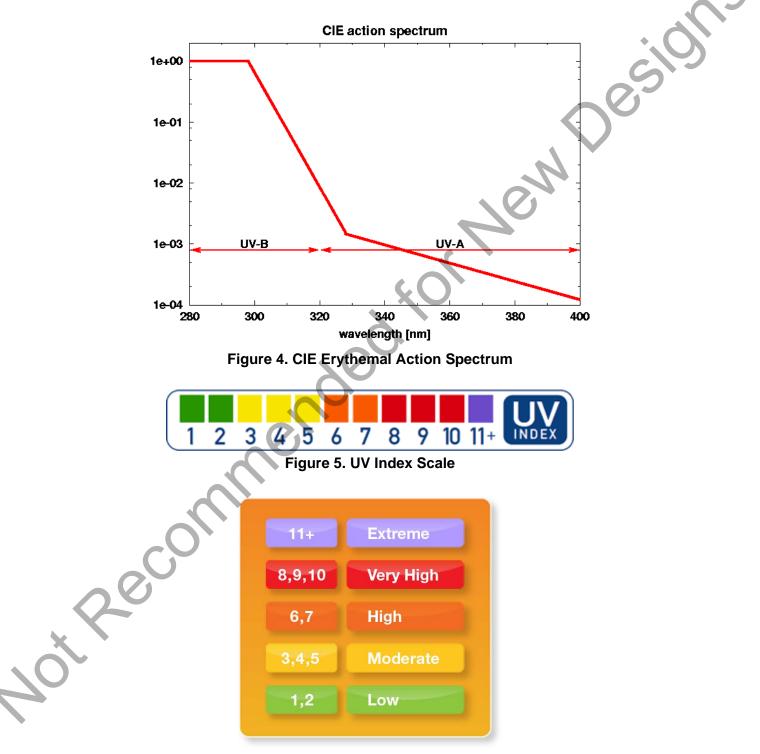

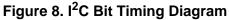

The UV Index is a number linearly related to the intensity of sunlight reaching the earth and is weighted according to the CIE Erythemal Action Spectrum as shown in Figure 4. This weighting is a standardized measure of human skin's response to different wavelengths of sunlight from UVB to UVA. The UV Index has been standardized by the World Health Organization and includes a simplified consumer UV exposure level as shown in Figures 5 and 6.

Figure 6. UV Levels

To enable UV reading, set the EN\_UV bit in CHLIST, and configure UCOEF [0:3] to the default values of 0x7B, 0x6B, 0x01, and 0x00. Also set the VIS\_RANGE and IR\_RANGE bits. If the sensor will be under an overlay that is not 100% transmissive to sunlight, contact Silicon Labs for more information on adjusting these coefficients.

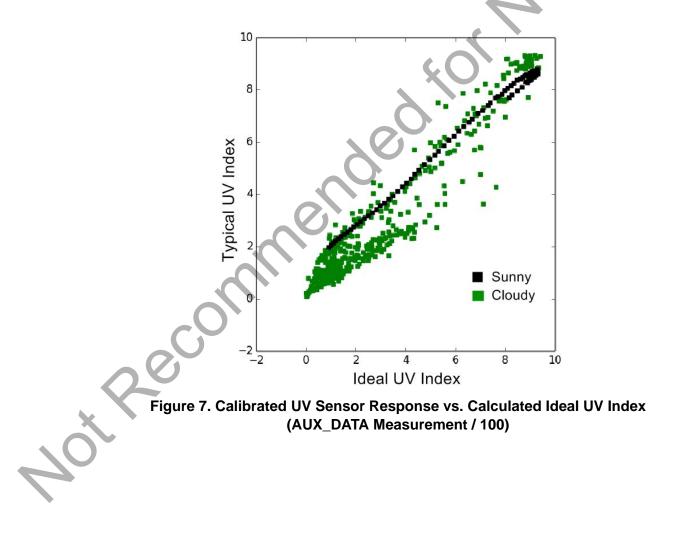

Typically, after 285 µs, AUX\_DATA will contain a 16-bit value representing 100 times the sunlight UV Index. Host software must divide the results from AUX\_DATA by 100.

The accuracy of UV readings can be improved by using calibration parameters that are programmed into the Si1132 at Silicon Labs' production facilities to adjust for normal part-to-part variation. The calibration parameters are recovered from the Si1132 by writing Command Register @ address 0x18 with the value 0x12.

When the calibration parameters are recovered, they show up at I<sup>2</sup>C registers 0x22 to 0x2D. These are the same registers used to report the VIS, IR, and AUX measurements.

The use of calibration parameters is documented in the file, Si114x\_functions.h, which is part of the Si114x Programmer's Toolkit example source code and is downloadable from Silabs.com. The host code is expected to allocate memory for the Si114x\_CAL\_S structure. The Si114x\_calibration routine will then fill it up with the appropriate values.

Once the calibration parameters have been recovered the routine Si114x\_set\_ucoef is used to modify the default values that go into the UCOEF0 to UCOEF3 UV configuration registers to remove normal part-to-part variation.

The typical calibrated UV sensor response vs. calculated ideal UV Index is shown in Figure 7 for a large database of sunlight spectra from cloudy to sunny days and at various angles of the sun/time of day.

## 2.4. Host Interface

The host interface to the Si1132 consists of three pins:

- SCL

- SDA

- INT

SCL and SDA are standard open-drain pins as required for I<sup>2</sup>C operation.

The Si1132 asserts the INT pin to interrupt the host processor. The INT pin is an open-drain output. A pull-up resistor is needed for proper operation. As an open-drain output, it can be shared with other open-drain interrupt sources in the system.

For proper operation, the Si1132 is expected to fully complete its Initialization Mode prior to any activity on the I<sup>2</sup>C.

The INT, SCL, and SDA pins are designed so that it is possible for the Si1132 to enter the Off Mode by software command without interfering with normal operation of other I<sup>2</sup>C devices on the bus.

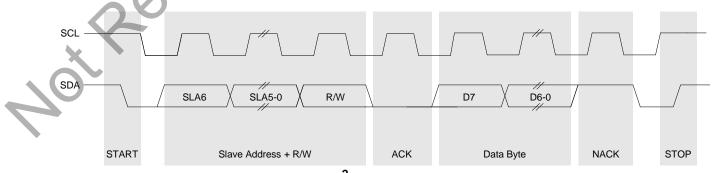

The Si1132 I<sup>2</sup>C slave address is 0x60. The Si1132 also responds to the global address (0x00) and the global reset command (0x06). Only 7-bit I<sup>2</sup>C addressing is supported; 10-bit I<sup>2</sup>C addressing is not supported. Conceptually, the I<sup>2</sup>C interface allows access to the Si1132 internal registers. Table 11 on page 24 is a summary of these registers.

An  $I^2C$  write access always begins with a start (or restart) condition. The first byte after the start condition is the  $I^2C$  address and a read-write bit. The second byte specifies the starting address of the Si1132 internal register. Subsequent bytes are written to the Si1132 internal register sequentially until a stop condition is encountered. An  $I^2C$  write access with only two bytes is typically used to set up the Si1132 internal address in preparation for an  $I^2C$  read.

The I<sup>2</sup>C read access, like the I<sup>2</sup>C write access, begins with a start or restart condition. In an I<sup>2</sup>C read, the I<sup>2</sup>C master then continues to clock SCK to allow the Si1132 to drive the I<sup>2</sup>C with the internal register contents.

The Si1132 also supports burst reads and burst writes. The burst read is useful in collecting contiguous, sequential registers. The Si1132 register map was designed to optimize for burst reads for interrupt handlers, and the burst writes are designed to facilitate rapid programming of commonly used fields.

The internal register address is a six-bit (bit 5 to bit 0) plus an Autoincrement Disable (on bit 6). The Autoincrement Disable is turned off by default. Disabling the autoincrementing feature allows the host to poll any single internal register repeatedly without having to keep updating the Si1132 internal address every time the register is read.

It is recommended that the host should read measurements (in the I<sup>2</sup>C Register Map) when the Si1132 asserts INT. Although the host can read any of the Si1132's I<sup>2</sup>C registers at any time, care must be taken when reading 2-byte measurements outside the context of an interrupt handler. The host could be reading part of the 2-byte measurement when the internal sequencer is updating that same measurement coincidentally. When this happens, the host could be reading a hybrid 2-byte quantity whose high byte and low byte are parts of different samples. If the host must read these 2-byte registers outside the context of an interrupt handler, the host should "double-check" a measurement if the measurement deviates significantly from a previous reading.

**I<sup>2</sup>C Broadcast Reset:** The I<sup>2</sup>C Broadcast Reset should be sent prior to any I<sup>2</sup>C register access to the Si1132. If any I<sup>2</sup>C register or parameter has already been written to the Si1132 when the I<sup>2</sup>C Broadcast Reset is issued, the host must send a reset command and reinitialize the Si1132 completely.

# 3. Operational Modes

The Si1132 can be in one of many operational modes at any one time. It is important to consider the operational mode since the mode has an impact on the overall power consumption of the Si1132. The various modes are:

- Off Mode

- Initialization Mode

- Standby Mode

- Forced Conversion Mode

- Autonomous Mode

### 3.1. Off Mode

ne V<sub>DD</sub> voltage is below

The Si1132 is in the Off Mode when  $V_{DD}$  is either not connected to a power supply or if the  $V_{DD}$  voltage is below the stated VDD\_OFF voltage described in the electrical specifications. As long as the parameters stated in Table 4, "Absolute Maximum Limits," on page 7 are not violated, no current will flow through the Si1132. In the Off Mode, the Si1132 SCL and SDA pins do not interfere with other I<sup>2</sup>C devices on the bus. Keeping V<sub>DD</sub> less than VDD\_OFF is not intended as a method of achieving lowest system current draw. The reason is that the ESD protection devices on the SCL, SDA and INT pins also from a current path through V<sub>DD</sub>. If V<sub>DD</sub> is grounded for example, then, current flow from system power to system ground through the SCL, SDA and INT pull-up resistors and the ESD protection devices.

Allowing V<sub>DD</sub> to be less than VDD\_OFF is intended to serve as a hardware method of resetting the Si1132 without a dedicated reset pin.

The Si1132 can also reenter the Off Mode upon receipt of either a general I<sup>2</sup>C reset or if a software reset sequence is initiated. When one of these software methods is used to enter the Off Mode, the Si1132 typically proceeds directly from the Off Mode to the Initialization Mode.

#### 3.2. Initialization Mode

When power is applied to  $V_{DD}$  and is greater than the minimum  $V_{DD}$  Supply Voltage stated in Table 1, "Recommended Operating Conditions," on page 4, the Si1132 enters its Initialization Mode. In the Initialization Mode, the Si1132 performs its initial startup sequence. Since the I<sup>2</sup>C may not yet be active, it is recommended that no I<sup>2</sup>C activity occur during this brief Initialization Mode period. The "Start-up time" specification in Table 1 is the minimum recommended time the host needs to wait before sending any I<sup>2</sup>C accesses following a power-up sequence. After Initialization Mode has completed, the Si1132 enters Standby Mode. The host must write 0x17 to the HW\_KEY register for proper operation.

#### 3.3. Standby Mode

The Si1132 spends most of its time in Standby Mode. After the Si1132 completes the Initialization Mode sequence, it enters Standby mode. While in Standby Mode, the Si1132 does not perform any measurements. However, the I<sup>2</sup>C interface is active and ready to accept reads and writes to the Si1132 registers. The internal Digital Sequence Controller is in its sleep state and does not draw much power. In addition, the INT output retains its state until it is cleared by the host.

I<sup>2</sup>C accesses do not necessarily cause the Si1132 to exit the Standby Mode. For example, reading Si1132 registers is accomplished without needing the Digital Sequence Controller to wake from its sleep state.

#### 3.4. Forced Conversion Mode

The Si1132 can operate in Forced Conversion Mode under the specific command of the host processor. The Forced Conversion Mode is entered if the ALS\_FORCE command is sent. Upon completion of the conversion, the Si1132 can generate an interrupt to the host if the corresponding interrupt is enabled.

## 3.5. Autonomous Operation Mode

The Si1132 can be placed in the Autonomous Operation Mode where measurements are performed automatically without requiring an explicit host command for every measurement. The ALS\_AUTO command is used to place the Si1132 in the Autonomous Operation Mode.

The Si1132 updates the  $I^2C$  registers for ALS automatically. Each measurement is allocated a 16-bit register in the  $I^2C$  map. It is possible to operate the Si1132 without interrupts. When doing so, the host poll rate must be at least twice the frequency of the conversion rates for the host to always receive a new measurement. The host can also choose to be notified when these new measurements are available by enabling interrupts.

The conversion frequencies for the ALS measurements are set up by the host prior to the ALS\_AUTO command. Recommended for New

# 4. Programming Guide

### 4.1. Command and Response Structure

All Si1132 I<sup>2</sup>C registers (except writes to the COMMAND register) are read or written without waking up the internal sequencer. A complete list of the I<sup>2</sup>C registers can be found in "4.5. I2C Registers" on page 24. In addition to the I<sup>2</sup>C Registers, RAM parameters are memory locations maintained by the internal sequencer. These RAM Parameters are accessible through a Command Protocol (see "4.6. Parameter RAM" on page 35). A complete list of the RAM Parameters can be found in "4.6. Parameter RAM" on page 35.

The Si1132 can operate either in Forced Measurement or Autonomous Mode. When in Forced Measurement mode, the Si1132 does not make any measurements unless the host specifically requests the Si1132 to do so via specific commands (refer to the Section 3.2). The CHLIST parameter needs to be written so that the Si1132 would know which measurements to make. The parameter MEAS\_RATE, when zero, places the internal sequencer in Forced Measurement mode. When in Forced Measurement mode, the internal sequencer wakes up only when the host writes to the COMMAND register. The power consumption is lowest in Forced Measurement mode (MEAS\_RATE = 0).

The Si1132 operates in Autonomous Operation mode when MEAS\_RATE is non-zero. The MEAS\_RATE represents the time interval at which the Si1132 wakes up periodically. Up to three measurements are made (ALS\_VIS, ALS\_IR and AUX) depending on which measurements are enabled via the upper bits of the CHLIST Parameter. All three measurements are made in the following sequence: ALS\_VIS, ALS\_IR and AUX.

The ALS Measurement group consists of the Visible Light Ambient Measurement (ALS\_VIS), the Infrared Light Ambient Measurement (ALS\_IR) and the Auxiliary measurement (AUX). Each measurement group has three measurements each. The Channel List (CHLIST) parameter enables the specific measurements for that measurement grouping.

Each measurement (ALS\_VIS, ALS\_IR, AUX) are controlled through a combination of I2C Register or Parameter RAM. Tables 7 to 9 below summarize the properties and resources used for each measurement.

## 4.2. Command Protocol

The I<sup>2</sup>C map implements a bidirectional message box between the host and the Si1132 Sequencer. Host-writable I<sup>2</sup>C registers facilitate host-to-Si1132 communication, while read-only I<sup>2</sup>C registers are used for Si1132-to-host communication.

Unlike the other host-writable I<sup>2</sup>C registers, the COMMAND register causes the internal sequencer to wake up from Standby mode to process the host request.

When a command is executed, the RESPONSE register is updated. Typically, when there is no error, the upper four bits are zeros. To allow command tracking, the lower four bits implement a 4-bit circular counter. In general, if the upper nibble of the RESPONSE register is non-zero, this indicates an error or the need for special processing.

The PARAM\_WR and PARAM\_RD registers are additional mailbox registers.

In addition to the registers in the I<sup>2</sup>C map, there are environmental parameters accessible through the Command/ Response interface. These parameters are stored in the internal ram space. These parameters generally take more I<sup>2</sup>C accesses to read and write. The Parameter RAM is described in "4.6. Parameter RAM" on page 35.

For every write to the Command register, the following sequence is required:

- 1. Write 0x00 to Command register to clear the Response register.

- 2. Read Response register and verify contents are 0x00.

- 3. Write Command value from Table 5 into Command register.

- 4. Read the Response register and verify contents are now non-zero. If contents are still 0x00, repeat this step.

The Response register will be incremented upon the successful completion of a Command. If the Response register remains 0x00 for over 25 ms after the Command write, the entire Command process should be repeated from Step 1.

Step 4 above is not applicable to the Reset Command because the device will reset itself and does not increment the Response register after reset. No Commands should be issued to the device for at least 1 ms after a Reset is issued.

| COMMAND R   | egister   | PARAM_W      | PARAM_RD  | Error Code in     | Description                                                                                                                              |

|-------------|-----------|--------------|-----------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| Name        | Encoding  | R Register   | Register  | RESPONSE Register | Description                                                                                                                              |

| PARAM_QUERY | 100 aaaaa |              | nnnn nnnn | $\checkmark$      | Reads the parameter pointed to by<br>bitfield [4:0] and writes value to<br>PARAM_RD.<br>See Table 12 for parameters.                     |

| PARAM_SET   | 101 aaaaa | dddd<br>dddd | nnnn nnnn | $\checkmark$      | Sets parameter pointed by bitfield<br>[4:0] with value in PARAM_WR, and<br>writes value out to PARAM_RD. See<br>Table 12 for parameters. |

| NOP         | 000 00000 | —            | —         | √                 | Forces a zero into the RESPONSE register                                                                                                 |

| RESET       | 000 00001 | —            | —         | √                 | Performs a software reset of the firmware                                                                                                |

| BUSADDR     | 000 00010 | —            | _         | —                 | Modifies I <sup>2</sup> C address                                                                                                        |

| Reserved    | 000 00011 | _            | _         | —                 | —                                                                                                                                        |

| Reserved    | 000 00100 |              | _         | _                 |                                                                                                                                          |

| Reserved    | 000 00101 | —            | _         | —                 | _                                                                                                                                        |

## Table 5. Command Register Summary

| COMMAND F | Register  | PARAM_W    | PARAM_RD | Error Code in     | Description                                                      |

|-----------|-----------|------------|----------|-------------------|------------------------------------------------------------------|

| Name      | Encoding  | R Register | Register | RESPONSE Register | Description                                                      |

| GET_CAL   | 0001 0010 | —          | —        |                   | Reports calibration data to I <sup>2</sup> C registers 0x22–0x2D |

| ALS_FORCE | 000 00110 |            | _        | $\checkmark$      | Forces a single ALS measurement                                  |

| Reserved  | 000 00111 | —          |          |                   | - (9)                                                            |

| Reserved  | 000 01000 |            | _        | —                 | -0.2                                                             |

| Reserved  | 000 01001 | —          | _        | _                 |                                                                  |

| ALS_PAUSE | 000 01010 | —          | _        | ✓                 | Pauses autonomous ALS                                            |

| Reserved  | 000 01011 | _          | —        | —                 | _                                                                |

| Reserved  | 000 01100 | _          |          | ✓                 | -                                                                |

| Reserved  | 000 01101 | _          | —        |                   | - 0                                                              |

| ALS_AUTO  | 000 01110 | —          | —        | 1                 | Starts/Restarts an autonomous<br>ALS Loop                        |

| Reserved  | 000 01111 | _          | _        |                   | —                                                                |

| Reserved  | 000 1xxxx | —          | _        | κÐ.               | —                                                                |

## Table 5. Command Register Summary (Continued)

## Table 6. Response Register Error Codes

| RESPONSE Register | Description                                                                                                                                                                                                                        |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                   | NO_ERROR. The lower bit is a circular counter and is incremented every time a command has completed. This allows the host to keep track of commands sent to the Si1132. The circular counter may be cleared using the NOP command. |

|                   | INVALID_SETTING. An invalid setting was encountered.<br>Clear using the NOP command.                                                                                                                                               |

|                   | ALS_VIS_ADC_OVERFLOW. Indicates visible ambient light channel conversion overflow.                                                                                                                                                 |

|                   | ALS_IR_ADC_OVERFLOW. Indicates infrared ambient light channel conversion overflow.                                                                                                                                                 |

| 1000 1110         | AUX_ADC_OVERFLOW. Indicates auxiliary channel conversion overflow.                                                                                                                                                                 |

| j. P.             |                                                                                                                                                                                                                                    |

|                   |                                                                                                                                                                                                                                    |

## 4.3. Resource Summary

|                          | Channel Enable             | Interrupt Status Output             | Interrupt Enable                  |

|--------------------------|----------------------------|-------------------------------------|-----------------------------------|

| ALS Visible              | EN_ALS_VIS<br>in CHLIST[4] | ALS_INT[1:0] in IRQ_<br>STATUS[1:0] | ALS_IE[1:0] in<br>IRQ_ENABLE[1:0] |

| ALS IR                   | EN_ALS_IR<br>in CHLIST[5]  |                                     | 000                               |

| Auxiliary<br>Measurement | EN_AUX<br>in CHLIST[6]     |                                     | <u> </u>                          |

|                          | nnenor                     |                                     |                                   |

#### Table 7. Resource Summary for Interrupts

| Measurement<br>Channel   | ADC Output                               | ADC Input Source | ADC Recovery Count                          | ADC High Signal Mode                | ADC Clock<br>Divider       | ADC<br>Alignm                      |

|--------------------------|------------------------------------------|------------------|---------------------------------------------|-------------------------------------|----------------------------|------------------------------------|

| ALS Visible              | ALS_VIS_DATA1 /<br>ALS_VIS_DATA0         |                  | VIS_ADC_REC<br>in ALS_VIS_ADC_COUNTER [6:4] | VIS_RANGE<br>in ALS_VIS_ADC_MISC[5] | ALS_VIS_<br>ADC_GAIN [3:0] | ALS_V<br>ALIG<br>in ALS<br>ENCODII |

| ALS IR                   | ALS_IR_DATA1[7:0] /<br>ALS_IR_DATA0[7:0] |                  | IR_ADC_REC<br>in ALS_IR_ADC_COUNTER [6:4]   | IR_RANGE<br>in ALS_IR_ADC_MISC[5]   | ALS_IR_<br>ADC_GAIN [3:0]  | ALS_I<br>ALIG<br>in ALS<br>ENCODII |

| Auxiliary<br>Measurement | AUX_DATA1[7:0] /<br>AUX_DATA0[7:0]       | AUX_ADCMUX[7:0]  |                                             | _                                   | _                          | _                                  |

|                          |                                          |                  | ended                                       |                                     |                            |                                    |

|                          | , Re                                     | conin            | erdeo                                       |                                     |                            |                                    |

| Pin Name | Output Drive Disable | Analog Voltage Input<br>Enable |  |  |

|----------|----------------------|--------------------------------|--|--|

| INT      | INT_OE in INT_CFG[0] | ANA_IN_KEY[31:0]               |  |  |

The interrupts of the Si1132 are controlled through the INT\_CFG, IRQ\_ENABLE, IRQ\_MODE1, IRQ\_MODE2 and IRQ\_STATUS registers.

The INT hardware pin is enabled through the INT\_OE bit in the INT\_CFG register. The hardware essentially performs an AND function between the IRQ\_ENABLE register and IRQ\_STATUS register. After this AND function, if any bits are set, the INT pin is asserted. The host is responsible for clearing the interrupt by writing to the IRQ\_STATUS register. When the specific bits of the IRQ\_STATUS register is written with 1, that specific IRQ\_STATUS bit is cleared.

Typically, the host software is expected to read the IRQ\_STATUS register, stores a local copy, and then writes the same value back to the IRQ\_STATUS to clear the interrupt source. The INT\_CFG register is normally written with 1.

The IRQ\_MODE1, IRQ\_MODE2 and IRQ\_ENABLE registers work together to define how the internal sequencer sets bits in the IRQ\_STATUS register (and as a consequence, asserting the INT pin).

The ALS interrupts are described in Table 10.

### Table 10. Ambient Light Sensing Interrupt Resources

|       | IRQ_ENABLE[1:0]<br>ALS_IE[1:0] |   | Description                                  |  |

|-------|--------------------------------|---|----------------------------------------------|--|

|       |                                |   | Description                                  |  |

|       | 0                              | 0 | No ALS Interrupts                            |  |

|       | 0                              | 1 | ALS_INT set after every ALS_VIS or UV sample |  |

| Joi R | SCC                            |   |                                              |  |

SILICON LABS

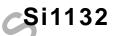

## 4.4. Signal Path Software Model

The following diagram gives an overview of the signal paths, along with the I<sup>2</sup>C register and RAM Parameter bit fields that control them. Sections with detailed descriptions of the I<sup>2</sup>C registers and Parameter RAM follow.

# 4.5. I<sup>2</sup>C Registers

| I <sup>2</sup> C Register<br>Name | Address | 7                       | 6      | 5       | 4        | 3     | 2 | 1    | 0      |

|-----------------------------------|---------|-------------------------|--------|---------|----------|-------|---|------|--------|

| PART_ID                           | 0x00    |                         |        | 1       | PART     | _ID   |   | •    |        |

| REV_ID                            | 0x01    |                         |        |         | REV_     | ID    |   | G    |        |

| SEQ_ID                            | 0x02    |                         |        |         | SEQ_     | ID    |   | 0,   |        |

| INT_CFG                           | 0x03    |                         |        |         |          |       |   | )    | INT_OE |

| IRQ_ENABLE                        | 0x04    |                         |        |         |          |       |   |      | ALS_IE |

| HW_KEY                            | 0x07    |                         |        |         | HW_K     | EΥ    | 7 |      |        |

| MEAS_RATE0                        | 0x08    |                         |        |         | MEAS_R   | ATE0  | 5 |      |        |

| MEAS_RATE1                        | 0x09    |                         |        |         | MEAS_R   | ATE1  |   |      |        |

| Reserved                          | 0x0A    |                         |        |         | ~        |       |   |      |        |

| Reserved                          | 0x0B    |                         |        | (       | kO.      | >     |   |      |        |

| Reserved                          | 0x0C    |                         |        |         |          |       |   |      |        |

| Reserved                          | 0x0D    |                         |        | 0       |          |       |   |      |        |

| Reserved                          | 0x0E    |                         | 2      | 0       |          |       |   |      |        |

| Reserved                          | 0x0F    |                         | ~      | 5       |          |       |   |      |        |

| Reserved                          | 0x10    | C                       |        |         |          |       |   |      |        |

| Reserved                          | 0x11    |                         |        |         |          |       |   |      |        |

| Reserved                          | 0x12    |                         |        |         |          |       |   |      |        |

| UCOEF0                            | 0x13    | $\overline{\mathbf{O}}$ |        |         | UCOE     | F0    |   |      |        |

| UCOEF1                            | 0x14    | )                       |        |         | UCOE     | F1    |   |      |        |

| UCOEF2                            | 0x15    |                         | UCOEF2 |         |          |       |   |      |        |

| UCOEF3                            | 0x16    |                         |        |         | UCOE     | F3    |   |      |        |

| PARAM_WR                          | 0x17    |                         |        |         | PARAM    | _WR   |   |      |        |

| COMMAND                           | 0x18    |                         |        |         | COMM     | AND   |   |      |        |

| RESPONSE                          | 0x20    |                         |        |         | RESPO    | NSE   |   |      |        |

| IRQ_STATUS                        | 0x21    |                         |        | CMD_INT |          |       |   | ALS_ | INT    |

| ALS_VIS_<br>DATA0                 | 0x22    |                         |        |         | ALS_VIS_ | DATA0 |   |      |        |

| I <sup>2</sup> C Register<br>Name | Address       | 7    | 6                  | 5 | 4        | 3     | 2       | 1       | 0     |

|-----------------------------------|---------------|------|--------------------|---|----------|-------|---------|---------|-------|

| ALS_VIS_<br>DATA1                 | 0x23          |      | ALS_VIS_DATA1      |   |          |       |         |         |       |

| ALS_IR_DATA0                      | 0x24          |      |                    |   | ALS_IR_E | DATA0 |         | +       | O'    |

| ALS_IR_DATA1                      | 0x25          |      |                    |   | ALS_IR_E | DATA1 |         | S       |       |

| Reserved                          | 0x26          |      |                    |   |          |       |         | 0       |       |

| Reserved                          | 0x27          |      |                    |   |          |       |         |         |       |

| Reserved                          | 0x28          |      |                    |   |          |       | ~       |         |       |

| Reserved                          | 0x29          |      |                    |   |          |       | ~~~     |         |       |

| Reserved                          | 0x2A          |      |                    |   |          |       | 0       |         |       |

| Reserved                          | 0x2B          |      |                    |   |          |       |         |         |       |

| AUX_DATA0/<br>UVINDEX0            | 0x2C          |      | AUX_DATA0/UVINDEX0 |   |          |       |         |         |       |

| AUX_DATA1/<br>UVINDEX1            | 0x2D          |      | AUX_DATA1/UVINDEX1 |   |          |       |         |         |       |

| PARAM_RD                          | 0x2E          |      | PARAM_RD           |   |          |       |         |         |       |

| CHIP_STAT                         | 0x30          |      | (                  |   |          |       | RUNNING | SUSPEND | SLEEF |

| ANA_IN_KEY                        | 0x3B–<br>0x3E | (    | $\sim$             |   | ANA_IN_  | _KEY  |         |         |       |

| o't P                             | ecc           | SUUL |                    |   |          |       |         |         |       |

Table 11. I<sup>2</sup>C Register Summary (Continued)

PART\_ID @ 0x00

| Bit               | 7      | 6    | 5                         | 4                       | 3        | 2         | 1                 | 0  |

|-------------------|--------|------|---------------------------|-------------------------|----------|-----------|-------------------|----|

| Name              |        |      |                           | PAR                     | T_ID     |           |                   |    |

| Туре              |        |      |                           |                         | २        |           |                   | 29 |

| Reset value = 001 | 1 0010 |      |                           |                         |          |           | ~?                | 5  |

| REV_ID @ 0x1      |        |      |                           |                         |          |           | $\mathbf{\nabla}$ |    |

| Bit               | 7      | 6    | 5                         | 4                       | 3        | 2         | 1                 | 0  |

| Name              |        |      |                           | RE                      | /_ID     | 6         |                   |    |

| Туре              |        |      |                           |                         | R        |           |                   |    |

| Reset value = 000 | 0 0000 |      |                           |                         | ~``      |           |                   |    |

| SEQ_ID @ 0x02     |        |      |                           |                         |          |           |                   |    |

| Bit               | 7      | 6    | 5                         | 4                       | 3        | 2         | 1                 | 0  |

| Name              |        | 1    | 0                         | SEC                     | DI_Q     | 1         |                   | -  |

| Туре              |        | 0    |                           |                         | २        |           |                   |    |

| Reset value = 000 | 0 1000 |      | 0                         |                         |          |           |                   |    |

| Bit               | Name   |      |                           |                         | Function |           |                   |    |

| 7:0 5             | SEQ_ID | 0x08 | <b>er Revisio</b><br>Si11 | <b>n.</b><br>32-A10 (MA | JOR_SEQ= | 1, MINOR_ | SEQ=0)            |    |

| o Re              | ç      |      |                           |                         |          |           |                   |    |

## INT\_CFG @ 0x03

| Bit  | 7 | 6 | 5 | 4 | 3 | 2 | 1  | 0      | S |

|------|---|---|---|---|---|---|----|--------|---|

| Name |   |   |   |   |   |   |    | INT_OE |   |

| Туре |   |   |   |   |   |   | RW | RW     |   |

| Reset value | e = 0000 0000 |                                                                                                                                                                                      |

|-------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit         | Name          | Function                                                                                                                                                                             |

| 7:2         | Reserved      | Reserved.                                                                                                                                                                            |

| 0           | INT_OE        | INT Output Enable.<br>INT_OE controls the INT pin drive<br>0: INT pin is never driven<br>1: INT pin driven low whenever an IRQ_STATUS and its corresponding IRQ_ENABLE<br>bits match |

## IRQ\_ENABLE @ 0x04

| Bit 7 6 | 5 4 | 3 | 2 | 1 | 0      |

|---------|-----|---|---|---|--------|

| Name    |     |   |   |   | ALS_IE |

| Туре    |     |   |   | R | N      |

Reset value = 0000 0000

| Bit | Name     | Function                                                        |

|-----|----------|-----------------------------------------------------------------|

| 7:1 | Reserved | Reserved.                                                       |

| 0   | ALS_IE   | ALS Interrupt Enable.                                           |

|     |          | Enables interrupts when VIS bit or UV bit in CHLIST is enabled. |

|     |          | 0: INT never asserts due to VIS or UV activity                  |

|     |          | 1: Assert INT pin whenever VIS or UV measurements are ready     |

|     |          |                                                                 |

20

HW\_KEY @ 0x07

| Bit                         | 7                           | 6                                                                                       | 5            | 4                      | 3                     | 2 | 1              | 0 |  |

|-----------------------------|-----------------------------|-----------------------------------------------------------------------------------------|--------------|------------------------|-----------------------|---|----------------|---|--|

| Name                        | e                           |                                                                                         | HW_KEY       |                        |                       |   |                |   |  |

| Туре                        | )                           |                                                                                         |              | R                      | W                     |   |                |   |  |

| et valu                     | ue = 0000 000               | )                                                                                       |              |                        |                       |   | 2              | ) |  |

| Bit                         | Name                        |                                                                                         |              |                        | Function              |   |                |   |  |

| 7:0                         | HW_KEY                      | _KEY The system must write the value 0x17 to this register for proper Si1132 operation. |              |                        |                       |   |                |   |  |

|                             | ATE0: MEAS_                 |                                                                                         |              |                        |                       |   | r si risz oper |   |  |

|                             | ATE0: MEAS_                 |                                                                                         |              |                        | 3                     | 2 | 1              | 0 |  |

| AS_R/                       | ATE0: MEAS_                 | RATE Data Wo                                                                            | ord Low Byte | e @ 0x08               | 3<br>RATE[7:0]        | 6 |                |   |  |

| AS_R/<br>Bit                | ATEO: MEAS_<br>7            | RATE Data Wo                                                                            | ord Low Byte | e @ 0x08<br>4<br>MEAS_ | 3                     | 6 |                |   |  |

| AS_R/<br>Bit<br>Nam<br>Type | ATEO: MEAS_<br>7            | RATE Data Wo                                                                            | ord Low Byte | e @ 0x08<br>4<br>MEAS_ | <b>3</b><br>RATE[7:0] | 6 |                |   |  |

| AS_R/<br>Bit<br>Nam<br>Type | ATEO: MEAS_<br>7<br>ne<br>e | RATE Data Wo                                                                            | ord Low Byte | e @ 0x08<br>4<br>MEAS_ | <b>3</b><br>RATE[7:0] | 2 |                |   |  |

measurements specified in CHLIST are made. Note that for the Si1132 with SEQ\_ID=0x01, there is a code error that places MEAS\_RATE0 at 0x0A with MEAS\_RATE1 at 0x08 instead. This will be fixed in future revisions of the Si1132.

JotReck

#### MEAS\_RATE1: MEAS\_RATE Data Word High Byte @ 0x09

| Bit  | 7 | 6 | 5 | 4      | 3         | 2 | 1 | 0  | S |

|------|---|---|---|--------|-----------|---|---|----|---|

| Name | · |   |   | MEAS_R | ATE[15:8] |   |   |    |   |

| Туре |   |   |   | R      | W         |   |   | 39 |   |

| Reset value | = 0000 0000     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit         | Name            | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 7:0         | MEAS_RATE[15:8] | MEAS_RATE1 and MEAS_RATE0 together form a 16-bit value: MEAS_RATE[15:0].<br>The 16-bit value, when multiplied by 31.25 µs, represents the time duration between<br>wake-up periods where measurements are made. Once the device wakes up, all<br>measurements specified in CHLIST are made.<br>Note that for the Si1132 with SEQ_ID=0x01, there is a code error that places<br>MEAS_RATE0 at 0x0A and MEAS_RATE1 at 0x08 instead. This will be fixed in<br>future revisions of the Si1132. |

#### PARAM\_WR @ 0x17

| Bit  | 7 | 6        | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|------|---|----------|---|---|---|---|---|---|--|--|

| Name |   | PARAM_WR |   |   |   |   |   |   |  |  |

| Туре |   | RW       |   |   |   |   |   |   |  |  |

Reset value = 0000 0000

JotRecom

| Bit | Name     | Function                                                                |

|-----|----------|-------------------------------------------------------------------------|

| 7:0 | PARAM_WR | Mailbox register for passing parameters from the host to the sequencer. |

O

#### COMMAND @ 0x18

| Bit          | 7           | 6 | 5 | 4    | 3    | 2 | 1 | 0   |

|--------------|-------------|---|---|------|------|---|---|-----|

| Name         |             |   | L | COMM | IAND |   | 1 |     |

| Туре         |             |   |   | RV   | V    |   |   | · O |

| eset value = | = 0000 0000 |   |   |      |      |   |   | 6   |

| Bit | Name    | Function                                                                                                                                                                                             |

|-----|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | COMMAND | COMMAND Register.                                                                                                                                                                                    |

|     |         | The COMMAND Register is the primary mailbox register into the internal sequencer.<br>Writing to the COMMAND register is the only I <sup>2</sup> C operation that wakes the device from standby mode. |

|     |         |                                                                                                                                                                                                      |

#### RESPONSE @ 0x20

| Bit  | 7 | 6  | 5 | 4 3      | 2 | 1 | 0 |  |

|------|---|----|---|----------|---|---|---|--|

| Name |   |    |   | RESPONSE |   |   |   |  |

| Туре |   | RW |   |          |   |   |   |  |

| Bit | Name     | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | RESPONSE | The Response register is used in conjunction with command processing. When an e is encountered, the response register will be loaded with an error code. All error code will have the MSB is set.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     | 2000     | The error code is retained until a RESET or NOP command is received by the sequencer. Other commands other than RESET or NOP will be ignored. However, a autonomous operation in progress continues normal operation despite any error. 0x00–0x0F: No Error. Bits 3:0 form an incrementing roll-over counter. The roll over counter in bit 3:0 increments when a command has been executed by the Si1132. C autonomous measurements have started, the execution timing of any command becomes non-deterministic since a measurement could be in progress when the COMMAND register is written. The host software must make use of the rollover cou to ensure that commands are processed. 0x80: Invalid Command Encountered during ALS-VIS measurement 0x8D: ADC Overflow encountered during ALS-IR measurement 0x8E: ADC Overflow encountered during AUX measurement |

#### IRQ\_STATUS @ 0x21

|      |   |   |         |   |   |   |   |         | _ |

|------|---|---|---------|---|---|---|---|---------|---|

| Bit  | 7 | 6 | 5       | 4 | 3 | 2 | 1 | 0       | G |

| Name |   |   | CMD_INT |   |   |   |   | ALS_INT |   |

| Туре |   | · | RW      |   |   |   | R | W       |   |

Reset value = 0000 0000

| Bit        | Name            | Function                                                                              |

|------------|-----------------|---------------------------------------------------------------------------------------|

| 7:6        | Reserved        | Reserved.                                                                             |

| 5          | CMD_INT         | Command Interrupt Status.                                                             |

| 4:2        | Reserved        | Reserved.                                                                             |

| 1:0        | ALS_INT         | ALS Interrupt Status. (Refer to Table 13 for encoding.)                               |

| Note: If t | he correspondin | g IRQ_ENABLE bit is also set when the IRQ_STATUS bit is set, the INT pin is asserted. |

### ALS\_VIS\_DATA0: ALS\_VIS\_DATA Data Word Low Byte @ 0x22

| Bit  | 7 6 5 4 3 2 1 0 |                   |  |   |   |  |  |  |  |  |

|------|-----------------|-------------------|--|---|---|--|--|--|--|--|

| Name |                 | ALS_VIS_DATA[7:0] |  |   |   |  |  |  |  |  |

| Туре |                 |                   |  | R | W |  |  |  |  |  |

|   | Bit | Name              | Function                                                                                                                                                                                                                                   |

|---|-----|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|