## 125Mbps to 3.125Gbps Integrated Limiting Amplifier/ Laser Driver with Dual-Loop Power Control

#### **General Description**

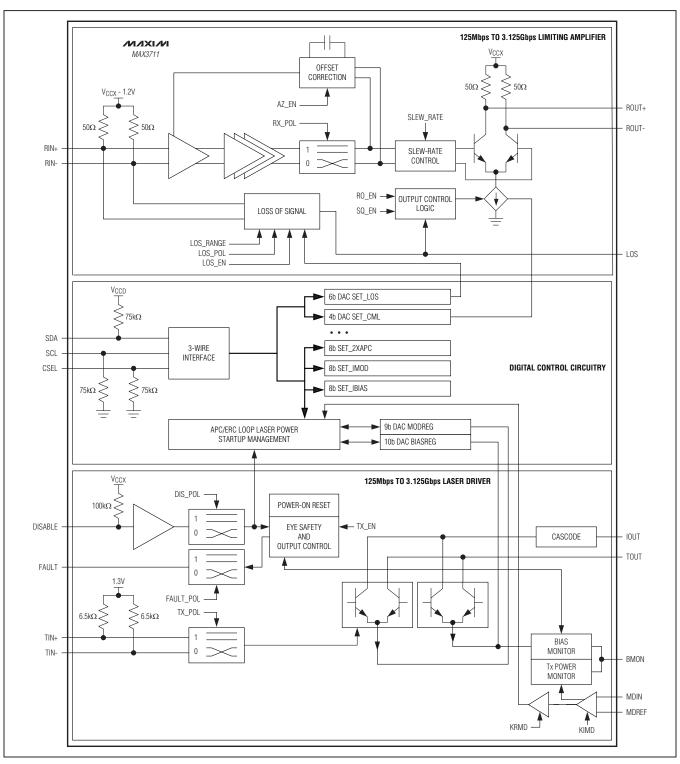

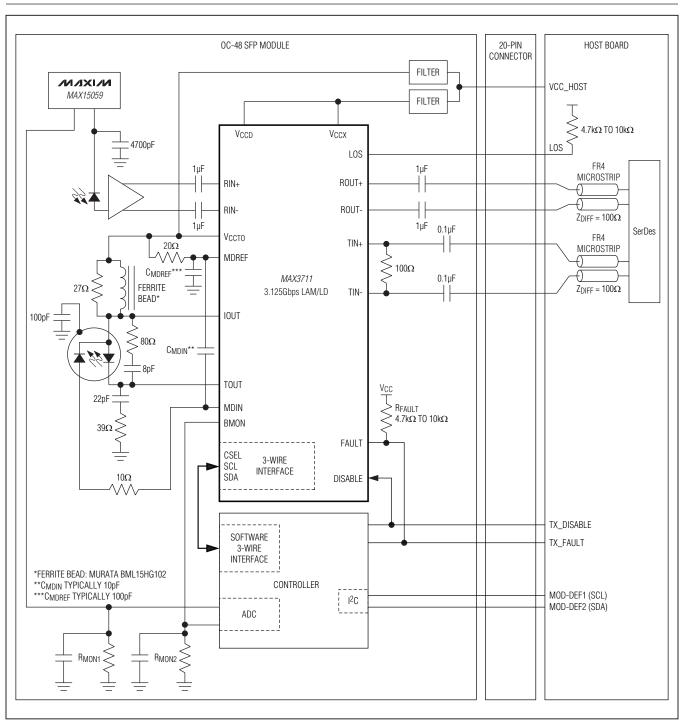

The MAX3711 limiting amplifier and laser driver provides a highly integrated, low-cost, high-performance PMD solution.

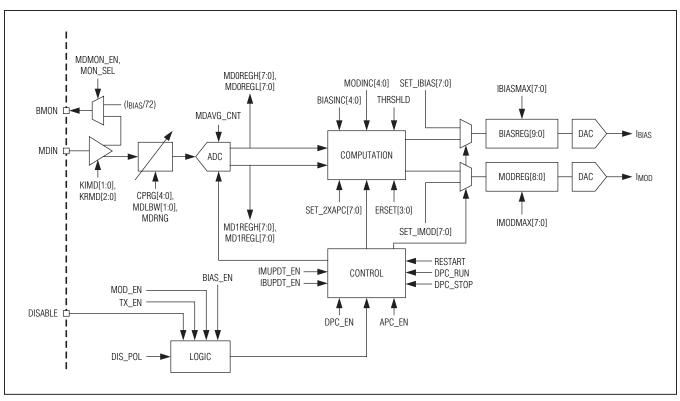

The low-jitter laser diode driver provides transmit average power control (APC) of laser bias current as well as an integrated modulation current control loop (extinction ratio control, or ERC). The ERC eliminates the need for temperature lookup tables (LUTs) controlling the modulation current.

The low-noise limiting amplifier maximizes optical sensitivity and has adjustable SD/LOS threshold plus programmable output levels. The differential CML output stage features a slew-rate adjustment for 1.25Gbps operation. Integrated bias current monitor and Tx power monitor enable a low-cost implementation of modules with digital diagnostics.

A novel auto-calibration mode enables low-cost fiber optic module production. An integrated 3-wire digital interface controls the laser driver and limiting amplifier functions, and enables communication with a low-cost controller.

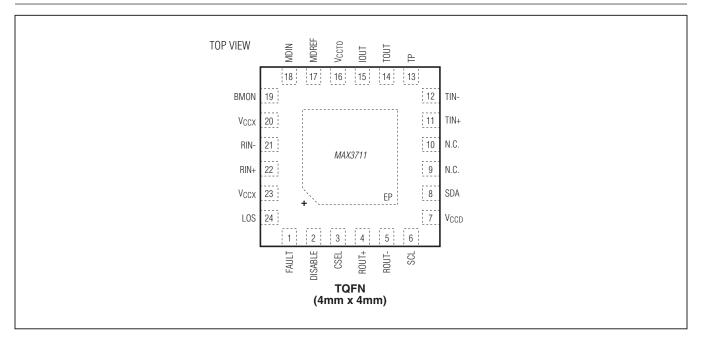

The MAX3711 is offered in a small, 4mm x 4mm, 24-pin TQFN package with exposed pad, and operates over the -40°C to +95°C temperature range.

Ordering Information appears at end of data sheet.

#### **Benefits and Features**

- **♦ Simplifies Module Manufacturing**

- **♦ Enables Single-Temperature Module Testing**

- ♦ Production Laser Auto-Calibration Mode

- **♦ Improved Performance**

- ♦ Integrated APC Loop (Operates Up to 3.125Gbps)

- ♦ Integrated ERC Loop (Operates Up to 2.7Gbps)

- ♦ 1.3mV<sub>P-P</sub> Receiver Sensitivity

- **♦** Flexibility

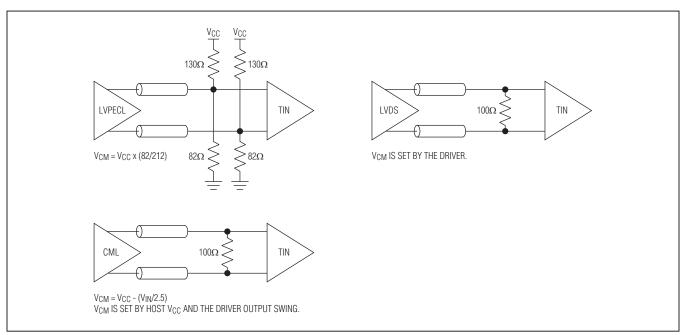

- LVDS, LVPECL, and CML Compatible High-Speed I/Os

- ♦ Programmable I/O Polarity

- ♦ 3-Wire Digital Interface

- ♦ Safety and Reliability

- ♦ Integrated Safety Features with FAULT Mask Register

- ♦ Supports SFP MSA and SFF-8472 Digital Diagnostic

- Selectable Analog Monitor of Laser Power or BIAS Current at BMON Pin

### **Applications**

OC-3 to OC-48 SFP/SFF Transceivers Ethernet SFP/SFF Transceivers CPRI/OBSAI SFP/SFF Transceivers CWDM SFP Transceivers

#### **ABSOLUTE MAXIMUM RATINGS**

| Current out of ROUT+, ROUT40mA                        |

|-------------------------------------------------------|

| Current into TOUT180mA                                |

| Current into IOUT120mA                                |

| Voltage Range at BMON0.3V to V <sub>CC</sub>          |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C) |

| TQFN (derate 27.8mW/°C above +70°C)2222mW             |

| Storage Temperature Range55°C to +150°C               |

| Die Attach Temperature+400°C                          |

| Lead Temperature (soldering, 10s)+300°C               |

| Soldering Temperature (reflow)+260°C                  |

|                                                       |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{CC}=2.97V\ to\ 3.63V,\ T_A=-40^{\circ}C\ to\ +95^{\circ}C;\ CML\ receiver\ output\ is\ AC-coupled\ to\ differential\ 100\Omega\ load;\ registers\ are\ set\ to\ default\ values,\ unless\ implied\ by\ test\ conditions.$  Typical values are at  $V_{CC}=3.3V,\ T_A=+25^{\circ}C,\ data\ rate=2.5Gbps,\ I_{BIAS}=20mA,\ and\ I_{MOD}=40mA,\ unless\ otherwise\ noted.)$  (Note 1)

| PARAMETER                       | SYMBOL             | CONDITIONS                                                                                    | MIN       | TYP  | MAX  | UNITS             |  |

|---------------------------------|--------------------|-----------------------------------------------------------------------------------------------|-----------|------|------|-------------------|--|

| OPERATING CONDITIONS            |                    |                                                                                               |           |      |      |                   |  |

| Power Supply Voltage            | V <sub>CC</sub>    |                                                                                               | 2.97      | 3.3  | 3.63 | V                 |  |

| POWER SUPPLY                    |                    |                                                                                               |           |      |      |                   |  |

| Power-Supply Current            | I <sub>CC</sub>    | Includes Rx CML output current, excludes Tx I <sub>BIAS</sub> = 20mA, I <sub>MOD</sub> = 40mA |           | 75   | 110  | mA                |  |

| POWER-ON RESET                  |                    |                                                                                               |           |      |      |                   |  |

| V <sub>CC</sub> for Enable High |                    | V <sub>CCX</sub> connected to V <sub>CCD</sub>                                                |           | 2.55 | 2.75 | V                 |  |

| V <sub>CC</sub> for Enable Low  |                    | V <sub>CCX</sub> connected to V <sub>CCD</sub>                                                | 2.3       | 2.45 |      | V                 |  |

| Rx INPUT SPECIFICATION          |                    |                                                                                               |           |      |      |                   |  |

| Differential Input Resistance   | R <sub>IN</sub>    |                                                                                               | 75        | 100  | 125  | Ω                 |  |

| Input Sensitivity               | V <sub>INMIN</sub> | 2 <sup>23</sup> - 1 PRBS, 2.5Gbps, TX_EN = 0<br>(Note 2)                                      |           | 1.3  | 2    | mV <sub>P-P</sub> |  |

| Input Overload                  | V <sub>INMAX</sub> | (Note 2)                                                                                      | 1.2       |      |      | V <sub>P-P</sub>  |  |

| Differential least Detumble     |                    | Device powered on, f ≤ 2GHz                                                                   |           | 19   |      |                   |  |

| Differential Input Return Loss  | S <sub>DD11</sub>  | Device powered on, f ≤ 5GHz                                                                   |           | 12   |      | dB                |  |

| Common-Mode Input Return        | C                  | Device powered on, 1GHz ≤ f ≤ 2GHz                                                            |           | 11   |      | dB                |  |

| Loss                            | S <sub>CC11</sub>  | Device powered on, 2GHz ≤ f ≤ 5GHz                                                            |           | 14   |      | ab ab             |  |

| Rx OUTPUT SPECIFICATION         |                    |                                                                                               |           |      |      | ,                 |  |

| Differential Output Resistance  | Routdiff           |                                                                                               | 75        | 100  | 125  | Ω                 |  |

| Differential Outrot Detumble    |                    | Device powered on, f ≤ 2GHz                                                                   |           | 19   |      | -ID               |  |

| Differential Output Return Loss | S <sub>DD22</sub>  | Device powered on, 2GHz ≤ f ≤ 5GHz                                                            |           | 15   |      | dB                |  |

| Common-Mode Output Return       | 0                  | Device powered on, f ≤ 2GHz                                                                   | ≤ 2GHz 14 |      |      | -ID               |  |

| Loss                            | S <sub>CC22</sub>  | Device powered on, $2GHz \le f \le 5GHz$                                                      |           | 10   |      | dB                |  |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC}=2.97 V \text{ to } 3.63 V, T_A=-40 ^{\circ}\text{C} \text{ to } +95 ^{\circ}\text{C}; \text{CML receiver output is AC-coupled to differential } 100 \Omega \text{ load; registers are set to default values, unless implied by test conditions. Typical values are at <math>V_{CC}=3.3 V, T_A=+25 ^{\circ}\text{C}, \text{ data rate}=2.5 \text{Gbps, } I_{BIAS}=20 \text{mA}, \text{ and } I_{MOD}=40 \text{mA}, \text{ unless otherwise noted.}) \text{ (Note 1)}$

| PARAMETER                                        | SYMBOL          | CONE                                                                                                         | DITIONS                       | MIN                   | TYP | MAX  | UNITS             |  |

|--------------------------------------------------|-----------------|--------------------------------------------------------------------------------------------------------------|-------------------------------|-----------------------|-----|------|-------------------|--|

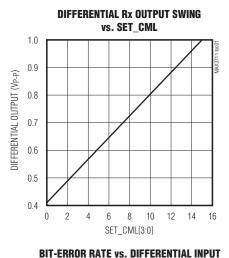

| CML Differential Output                          |                 | $4mV_{P-P} \le V_{IN} \le 120$<br>SET_CML[3:0] = 10                                                          |                               | 600                   | 800 | 1000 | \/                |  |

| Voltage                                          |                 | $4mV_{P-P} \le V_{IN} \le 120$<br>SET_CML[3:0] = 0                                                           | 0mV <sub>P-P</sub> ,          |                       | 410 |      | mV <sub>P-P</sub> |  |

| CML Differential Output<br>Voltage When Disabled |                 | Output AC-coupled<br>SET_CML[3:0] = 10                                                                       |                               |                       |     | 5    | mV <sub>P-P</sub> |  |

| Data Output Transition Time                      |                 | $4mV_{P-P} \le V_{IN} \le 120$<br>SLEW_RATE = 1                                                              | 0mV <sub>P-P</sub> ,          |                       | 85  | 115  |                   |  |

| (20% to 80%) (Note 2)                            |                 | $4mV_{P-P} \le V_{IN} \le 120$<br>SLEW_RATE = 0                                                              | 0mV <sub>P-P</sub> ,          |                       | 140 | 200  | - ps              |  |

| LOS Output High Voltage                          | V <sub>OH</sub> | $R_{LOS} = 4.7 k\Omega - 10 k$                                                                               | $\Omega$ to V $_{ m CC}$      | V <sub>CC</sub> - 0.1 |     |      | V                 |  |

| LOS Output Low Voltage                           | V <sub>OL</sub> | $R_{LOS} = 4.7 k\Omega - 10 k$                                                                               | $\Omega$ to V $_{ m CC}$      | 0                     |     | 0.4  | V                 |  |

| Rx TRANSFER CHARACTERIS                          | TICS            |                                                                                                              |                               |                       |     |      |                   |  |

|                                                  |                 | 2.5Gbps, 4mV <sub>P-P</sub> ≤ SET_CML[3:0] = 10                                                              |                               |                       | 7   | 15   |                   |  |

| Deterministic Jitter<br>(Notes 2, 3)             | DJ              | 1.25Gbps, 4mV <sub>P-P</sub> :<br>SET_CML[3:0] = 10                                                          |                               |                       | 10  | 20   | ps <sub>P-P</sub> |  |

|                                                  |                 | 125Mbps, 4mV <sub>P-P</sub> ≤ V <sub>IN</sub> ≤ 1200mV <sub>P-P</sub> ,<br>SET_CML[3:0] = 10d, K28.5 pattern |                               |                       | 21  |      |                   |  |

| Random Jitter                                    | RJ              | Input = 4mV <sub>P-P</sub> at 2<br>1111 0000 pattern,<br>(Notes 2, 4)                                        | .5Gbps,<br>SET_CML[3:0] = 10d |                       | 3.5 | 5    | ps <sub>RMS</sub> |  |

| Low-Frequency Cutoff (Simulated Value)           |                 | I/O coupling capaci                                                                                          | tors = 1µF                    |                       | 10  |      | kHz               |  |

| Small-Signal Bandwidth (Simulated Value)         |                 | SLEW_RATE = 1                                                                                                |                               |                       | 2.0 |      | GHz               |  |

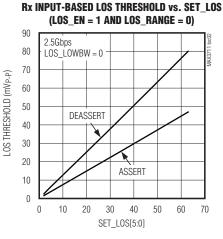

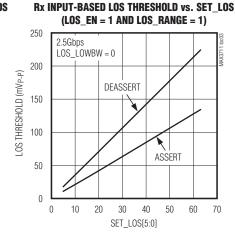

| LOS SPECIFICATIONS (Notes                        | 2, 5)           | 1                                                                                                            |                               |                       |     |      |                   |  |

| LOS Hysteresis                                   |                 | 10log(V <sub>DEASSERT</sub> /V                                                                               | ASSERT)                       | 1.25                  | 2.2 |      | dB                |  |

| LOS Assert/Deassert Time                         |                 | (Note 6)                                                                                                     |                               | 2.3                   |     | 30   | μs                |  |

| LOC Apport Consistinity Day                      |                 | LOS_RANGE = 0                                                                                                |                               | 4.6                   |     | 36   | m\/               |  |

| LOS Assert Sensitivity Range                     |                 | LOS_RANGE = 1                                                                                                |                               | 14                    |     | 115  | mV <sub>P-P</sub> |  |

|                                                  | SET_LOS = 5     |                                                                                                              | SET_LOS = 5                   | 3                     | 3.8 | 4.6  |                   |  |

|                                                  |                 | LOS assert                                                                                                   | SET_LOS = 31                  | 18                    | 23  | 28   |                   |  |

| LOS Assert/Deassert Level                        |                 |                                                                                                              | SET_LOS = 63                  | 36                    | 47  | 56   | mV <sub>P-P</sub> |  |

| (Low Range, LOS_RANGE = 0)                       |                 |                                                                                                              | SET_LOS = 5                   | 5                     | 6.5 | 8    | '-'               |  |

|                                                  |                 | LOS deassert                                                                                                 | SET_LOS = 31                  | 32                    | 39  | 46   |                   |  |

|                                                  |                 | SET_LOS = 63                                                                                                 |                               | 64                    | 80  | 95   |                   |  |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = 2.97 \text{V to } 3.63 \text{V}, T_A = -40 ^{\circ}\text{C} \text{ to } +95 ^{\circ}\text{C}; \text{CML receiver output is AC-coupled to differential } 100 \Omega \text{ load; registers are set to default values, unless implied by test conditions. Typical values are at <math>V_{CC} = 3.3 \text{V}, T_A = +25 ^{\circ}\text{C}, \text{ data rate } = 2.5 \text{Gbps, } I_{BIAS} = 20 \text{mA}, \text{ and } I_{MOD} = 40 \text{mA}, \text{ unless otherwise noted.}) \text{ (Note 1)}$

| PARAMETER                            | SYMBOL            | CONI                                                                                          | DITIONS                            | MIN                  | TYP  | MAX                                       | UNITS      |

|--------------------------------------|-------------------|-----------------------------------------------------------------------------------------------|------------------------------------|----------------------|------|-------------------------------------------|------------|

|                                      |                   |                                                                                               | SET_LOS = 5                        | 9                    | 11.5 | 14                                        |            |

|                                      |                   | LOS assert                                                                                    | SET_LOS = 31                       | 55                   | 68   | 80                                        |            |

| LOS Assert/Deassert Level            |                   |                                                                                               | SET_LOS = 63                       | 115                  | 138  | 160                                       | $mV_{P-P}$ |

| (High Range, LOS_RANGE = 1)          |                   |                                                                                               | SET_LOS = 5                        | 15                   | 19   | 23                                        | IIIVP-P    |

|                                      |                   | LOS deassert                                                                                  | SET_LOS = 31                       | 97                   | 117  | 136                                       |            |

|                                      |                   |                                                                                               | SET_LOS = 63                       | 197                  | 238  | 278                                       |            |

| Tx INPUT SPECIFICATIONS              |                   | T                                                                                             |                                    |                      |      |                                           |            |

| Differential Input Resistance        |                   |                                                                                               |                                    |                      | 13   |                                           | kΩ         |

| Internal Common-Mode Bias<br>Voltage |                   | For AC-coupled op-                                                                            | eration                            |                      | 1.3  |                                           | V          |

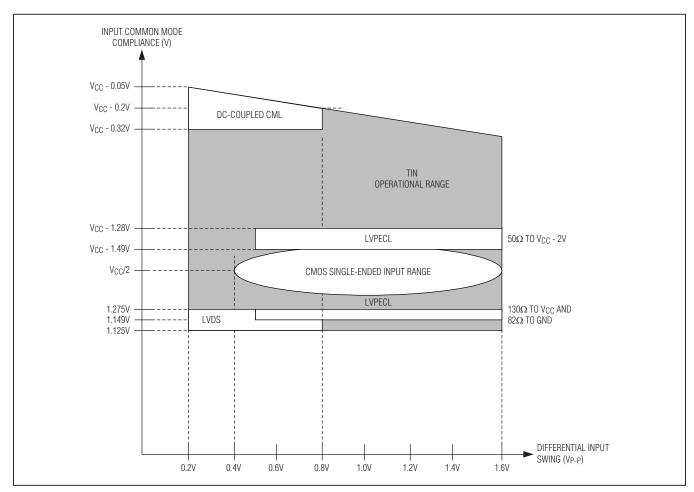

| Differential Input Voltage           |                   | DC-coupled, 100Ω,<br>Figure 1 and Figure                                                      | differential resistors, e 3        | 0.2                  |      | 1.6                                       | $V_{P-P}$  |

| Common-Mode Input Voltage<br>Range   |                   | DC-coupled, Figure                                                                            | e 1 and Figure 3                   | 1.125                |      | V <sub>CC</sub> -<br>V <sub>IN</sub> /2.5 | V          |

| DIGABLE                              |                   | DISABLE = V <sub>CC</sub>                                                                     |                                    |                      |      | 10                                        | Δ.         |

| DISABLE Input Current                |                   | DISABLE = GND                                                                                 |                                    |                      | 33   | 60.5                                      | μΑ         |

| DISABLE Input High Voltage           | V <sub>IH</sub>   |                                                                                               |                                    | 1.8                  |      | V <sub>CC</sub>                           | V          |

| DISABLE Input Low Voltage            | V <sub>IL</sub>   |                                                                                               |                                    | 0                    |      | 0.8                                       | V          |

| DISABLE Input Hysteresis             | V <sub>HYST</sub> |                                                                                               |                                    |                      | 80   |                                           | mV         |

| DISABLE Input Impedance              | R <sub>PULL</sub> | Pullup resistor                                                                               |                                    | 60                   | 100  | 138                                       | kΩ         |

| Tx OUTPUT SPECIFICATIONS             |                   | •                                                                                             |                                    |                      |      |                                           |            |

| FAULT Output High Voltage            | V <sub>OH</sub>   | R <sub>FAULT</sub> is 4.7kΩ - 1                                                               | $0$ k $\Omega$ to V $_{CC}$        | V <sub>CC</sub> - 0. | 1    |                                           | V          |

| FAULT Output Low Voltage             | V <sub>OL</sub>   | R <sub>FAULT</sub> is 4.7kΩ - 1                                                               | l0k $\Omega$ to V $_{\mathrm{CC}}$ | 0                    |      | 0.4                                       | V          |

| LASER MODULATOR                      |                   | ,                                                                                             |                                    |                      |      |                                           |            |

| Maximum Modulation-On<br>Current     |                   |                                                                                               |                                    | 85                   |      |                                           | mA         |

| Minimum Modulation-On<br>Current     |                   |                                                                                               |                                    |                      |      | 5                                         | mA         |

| Modulation Current DAC Stability     |                   | 10mA ≤ I <sub>MOD</sub> ≤ 85mA (Notes 2, 7)                                                   |                                    |                      | 1    | 4                                         | %          |

| Modulation Current Rise/Fall         |                   | 20% to 80%, 10mA $\leq$ I <sub>MOD</sub> $\leq$ 85mA, R <sub>LOAD</sub> = 12Ω, TRF[1:0] = 11b |                                    |                      | 65   | 120                                       | no         |

| Time (Note 2)                        |                   | 20% to 80%, 10mA<br>$R_{LOAD} = 12\Omega$ , TRF                                               |                                    |                      | 72   |                                           | ps         |

| Compliance Voltage at TOUT           | V <sub>TOUT</sub> | Instantaneous volta<br>10mA ≤ I <sub>MOD</sub> ≤ 85n                                          | <u> </u>                           | 0.6                  |      | 2.4                                       | V          |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC}=2.97 \text{V to } 3.63 \text{V}, T_A=-40 ^{\circ}\text{C} \text{ to } +95 ^{\circ}\text{C}; \text{CML receiver output is AC-coupled to differential } 100 \Omega \text{ load; registers are set to default values, unless implied by test conditions. Typical values are at <math>V_{CC}=3.3 \text{V}, T_A=+25 ^{\circ}\text{C}, \text{ data rate}=2.5 \text{Gbps, } I_{BIAS}=20 \text{mA}, \text{ and } I_{MOD}=40 \text{mA}, \text{ unless otherwise noted.}) \text{ (Note 1)}$

| PARAMETER                                                       | SYMBOL                | CONDITIONS                                                                      | MIN | TYP | MAX  | UNITS             |

|-----------------------------------------------------------------|-----------------------|---------------------------------------------------------------------------------|-----|-----|------|-------------------|

|                                                                 |                       | 10mA ≤ I <sub>MOD</sub> ≤ 85mA, 2.5Gbps                                         |     | 15  | 40   |                   |

| Deterministic Jitter                                            | DJ                    | 10mA ≤ I <sub>MOD</sub> ≤ 85mA, 1.25Gbps                                        |     | 15  |      | nce e             |

| (Notes 2, 3)                                                    | D3                    | $10\text{mA} \le I_{\text{MOD}} \le 85\text{mA}, 125\text{Mbps},$ K28.5 pattern |     | 20  |      | psp₋p             |

| Random Jitter                                                   | RJ                    | 10mA ≤ I <sub>MOD</sub> ≤ 20mA, 1111 0000 pattern                               |     | 1.2 | 1.65 | 202112            |

| (Notes 2, 4)                                                    | NJ                    | $20\text{mA} \le I_{MOD} \le 85\text{mA}$ , 1111 0000 pattern                   |     | 1   | 1.45 | ps <sub>RMS</sub> |

| BIAS GENERATOR                                                  |                       |                                                                                 |     |     |      |                   |

| Maximum Bias Current                                            |                       | Current into TOUT                                                               | 70  |     |      | mA                |

| Minimum Bias Current                                            |                       | Current into TOUT                                                               |     |     | 1    | mA                |

| Bias Current DAC Stability                                      |                       | $2mA \le I_{BIAS} \le 70mA$ , $V_{TOUT} = 2V$ (Notes 2, 7)                      |     | 1   | 4    | %                 |

|                                                                 |                       | External resistor to GND defines voltage gain, I <sub>BIAS</sub> = 1.5mA        | 54  | 58  | 72   |                   |

| Bias Current Monitor Current                                    | I <sub>BIAS</sub> /   | External resistor to GND defines voltage gain, I <sub>BIAS</sub> = 5.7mA        | 54  | 65  | 73   | A/A               |

| Gain                                                            | IBMON E               | External resistor to GND defines voltage gain, I <sub>BIAS</sub> = 39mA         | 64  | 72  | 80   | AVA               |

|                                                                 |                       | External resistor to GND defines voltage gain, I <sub>BIAS</sub> = 70mA         | 64  | 72  | 80   |                   |

| Compliance Voltage Range at BMON                                | V <sub>BMON</sub>     |                                                                                 | 0   |     | 1.8  | V                 |

| BMON Current Gain Stability (as Bias Monitor)                   |                       | $2mA \le I_{BIAS} \le 70mA \text{ (Notes 2, 7)}$                                |     | 2   | 5    | %                 |

| LASER CONTROL SPECIFICAT                                        | TIONS                 |                                                                                 |     |     |      |                   |

| APC Loop Stability (1.25Gbps,                                   |                       | $I_{MDINAVG} = 50\mu A, K_{MD} \times SE = 0.005$                               |     | 0.1 |      | 10log(dB)         |

| 2 <sup>23</sup> - 1 PRBS Pattern) (Note 8)                      |                       | $I_{MDINAVG} = 2mA, K_{MD} \times SE = 0.05$                                    |     | 0.1 |      | Tolog(db)         |

| APC Loop Stability (2.5Gbps,                                    |                       | $I_{MDINAVG} = 50\mu A, K_{MD} \times SE = 0.005$                               |     | 0.1 |      | 10log(dB)         |

| 2 <sup>23</sup> - 1 PRBS Pattern) (Note 8)                      |                       | $I_{MDINAVG} = 2mA, K_{MD} \times SE = 0.05$                                    |     | 0.1 |      | Tolog(db)         |

| ERC Loop Stability (1.25Gbps, 2 <sup>23</sup> - 1 PRBS Pattern, |                       | $I_{MDINAVG} = 50\mu A, K_{MD} \times SE = 0.005$                               |     | 0.5 |      | 10log(dB)         |

| e <sub>R</sub> = 11dB) (Note 8)                                 |                       | $I_{MDINAVG} = 2mA, K_{MD} \times SE = 0.05$                                    |     | 0.5 |      | 7 3 3 (1 7        |

| ERC Loop Stability (2.5Gbps, 2 <sup>23</sup> - 1 PRBS Pattern,  |                       | $I_{MDINAVG} = 50\mu A, K_{MD} \times SE = 0.005$                               |     | 1.3 |      | 10log(dB)         |

| e <sub>R</sub> = 11dB) (Note 8)                                 |                       | $I_{MDINAVG} = 2mA, K_{MD} \times SE = 0.05$                                    |     | 1.1 |      |                   |

| MDIN Bias Voltage                                               | V <sub>MDIN</sub>     |                                                                                 |     | 1.2 |      | V                 |

| MD Average Current Range                                        | I <sub>MDINAV</sub> G | Average current into MDIN                                                       | 50  |     | 2000 | μΑ                |

| Programmable Extinction Ratio Range                             | e <sub>R</sub>        | P1/P0 (DPC closed-loop operation)                                               | 5   | 16  | 24   |                   |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC}=2.97 \text{V to } 3.63 \text{V}, T_A=-40 ^{\circ}\text{C} \text{ to } +95 ^{\circ}\text{C}; \text{CML receiver output is AC-coupled to differential } 100 \Omega \text{ load; registers are set to default values, unless implied by test conditions. Typical values are at <math>V_{CC}=3.3 \text{V}, T_A=+25 ^{\circ}\text{C}, \text{ data rate}=2.5 \text{Gbps, } I_{BIAS}=20 ^{\circ}\text{MA}, \text{ and } I_{MOD}=40 ^{\circ}\text{MA}, \text{ unless otherwise noted.}) \text{ (Note 1)}$

| PARAMETER                                  | SYMBOL               | CONDITIONS                                                                                                                                                                  | MIN                     | TYP       | MAX                         | UNITS             |  |

|--------------------------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-----------|-----------------------------|-------------------|--|

| MD Current Monitor/BMON<br>Activation Time |                      | From the rising edge of the final SCL clock of the 3-wire cycle to 90% of steady state at BMON                                                                              |                         | 100       |                             | ns                |  |

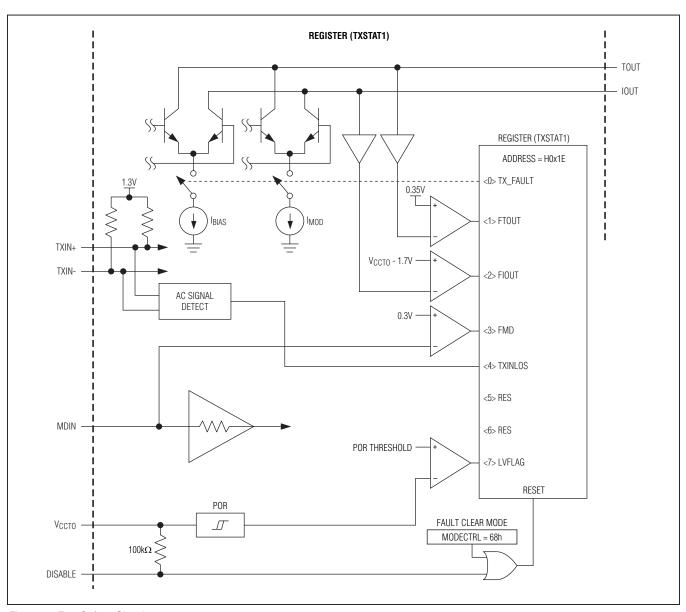

| SAFETY FEATURES                            |                      |                                                                                                                                                                             |                         |           |                             |                   |  |

| Fault Threshold Voltage at TOUT            | V <sub>TOUT</sub>    | Fault always occurs for $V_{TOUT} < 0.35V$ , fault never occurs for $V_{TOUT} \ge 0.55V$                                                                                    | 0.35                    |           | 0.55                        | V                 |  |

| Fault Threshold Voltage at MDIN            | V <sub>MDIN</sub>    | Fault always occurs for $V_{MDIN} < 0.3V$ , fault never occurs for $V_{MDIN} \ge 0.5V$                                                                                      | 0.3                     |           | 0.5                         | V                 |  |

| Fault Threshold Voltage at IOUT            |                      | Fault always occurs for V <sub>IOUT</sub> < V <sub>CCTO</sub> - 1.7V, fault never occurs for V <sub>IOUT</sub> ≥ V <sub>CCTO</sub> - 1.45V, V <sub>CCTO</sub> = 3.3V        | V <sub>CCTO</sub> - 1.7 |           | V <sub>ССТО</sub><br>- 1.45 | V                 |  |

| Fault Threshold Voltage at VCCTO           |                      | Fault always occurs for $V_{CCTO} < 2V$ ; fault never occurs for $V_{CCTO} \ge 2.95V$                                                                                       | 2                       |           | 2.95                        | V                 |  |

| Maximum Laser Current in Disable State     |                      | Combined total current into TOUT during fault, DISABLE = 1, or TX_EN = 0                                                                                                    |                         |           | 100                         | μΑ                |  |

| Tx TIMING SPECIFICATIONS                   |                      |                                                                                                                                                                             |                         |           |                             |                   |  |

| DPC Loop Initialization Time               | <sup>†</sup> APCINIT | I <sub>BIAS</sub> = 40mA and I <sub>MOD</sub> = 60mA,<br>I <sub>BIAS_INT</sub> = 8mA, time from restart to<br>I <sub>BIAS</sub> and I <sub>MOD</sub> at 90% of steady state |                         | 3         |                             | μs                |  |

| DISABLE Assert Time                        | t <sub>OFF</sub>     | Time from rising edge of DISABLE input signal to I <sub>BIAS</sub> and I <sub>MOD</sub> at 10% of steady state (Note 2)                                                     |                         | 30        | 100                         | ns                |  |

| DISABLE Negate Time                        | t <sub>ON</sub>      | Time from falling edge of DISABLE input signal to I <sub>BIAS</sub> and I <sub>MOD</sub> at 90% of steady state (Note 2)                                                    |                         | 200       | 300                         | ns                |  |

| Fault Assert Time                          | <sup>‡</sup> FAULT   | Time from fault condition to FAULT high, $C_{FAULT} \leq 20pF$ , $R_{FAULT}$ is $4.7k\Omega$ - $10k\Omega$ to $V_{CC}$ (Note 2)                                             |                         | 2.5       | 10                          | μs                |  |

| DISABLE to Reset                           |                      | Minimum required time DISABLE must be held high to reset a fault                                                                                                            |                         | 100       |                             | ns                |  |

| Rx OUTPUT LEVEL DAC                        |                      |                                                                                                                                                                             |                         |           |                             |                   |  |

| Full-Scale Voltage                         | V <sub>FS</sub>      | SET_CML[3:0] = 15d                                                                                                                                                          | 820                     | 1000      |                             | mV <sub>P-P</sub> |  |

| Resolution                                 |                      | 4 bits                                                                                                                                                                      |                         | 40        |                             | mV <sub>P-P</sub> |  |

| LOS THRESHOLD DAC                          |                      |                                                                                                                                                                             |                         |           |                             |                   |  |

| Full-Scale Voltage                         |                      | LOS_RANGE = 0  LOS_RANGE = 1                                                                                                                                                |                         | 47<br>138 |                             | $mV_{P-P}$        |  |

|                                            |                      | LOS_RANGE = 0                                                                                                                                                               |                         | 0.75      |                             |                   |  |

| Resolution                                 |                      | LOS_RANGE = 1                                                                                                                                                               | 2.2                     |           |                             | mV <sub>P-P</sub> |  |

| Integral Nonlinearity                      |                      | SET_LOS[5:0] = 5d to 63d                                                                                                                                                    |                         | ±0.7      |                             | LSB               |  |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC}=2.97V\ to\ 3.63V,\ T_A=-40^{\circ}C\ to\ +95^{\circ}C;\ CML\ receiver\ output\ is\ AC$ -coupled to differential 100 $\Omega$  load; registers are set to default values, unless implied by test conditions. Typical values are at  $V_{CC}=3.3V,\ T_A=+25^{\circ}C,\ data\ rate=2.5Gbps,\ I_{BIAS}=20mA,\ and\ I_{MOD}=40mA,\ unless\ otherwise\ noted.)$  (Note 1)

| PARAMETER                                   | SYMBOL                            | CONDITIONS                                                                       | MIN                   | TYP | MAX             | UNITS |

|---------------------------------------------|-----------------------------------|----------------------------------------------------------------------------------|-----------------------|-----|-----------------|-------|

| BIAS CURRENT DAC                            |                                   |                                                                                  |                       |     |                 |       |

| Full-Scale Current                          | I <sub>FS_BIAS</sub>              | I <sub>BIAS</sub> = (12 + BIASREG[9:0]) x LSB_BIAS                               | 70                    | 78  |                 | mA    |

| Resolution                                  | LSB_BIAS                          | 10-bit DAC                                                                       |                       | 75  |                 | μΑ    |

| MODULATION CURRENT DAC                      |                                   |                                                                                  |                       |     |                 |       |

| Full-Scale Current                          | I <sub>FS_MOD</sub>               | I <sub>MOD</sub> = (20 + MODREG[8:0]) x<br>LSB_MOD                               | 85                    | 89  |                 | mA    |

| Resolution                                  | LSB_MOD                           | 9-bit DAC                                                                        |                       | 167 |                 | μΑ    |

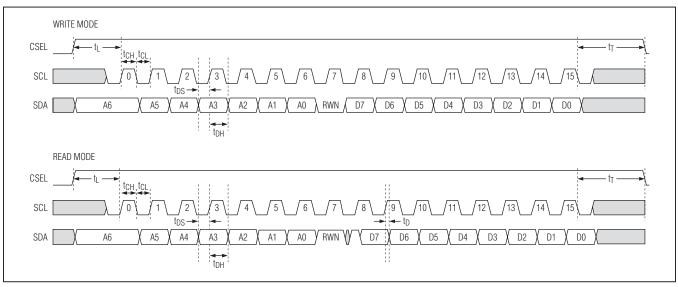

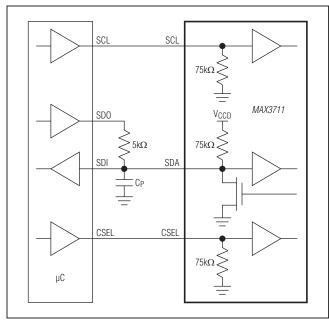

| 3-WIRE DIGITAL INTERFACE                    |                                   |                                                                                  |                       |     |                 |       |

| Input High Voltage                          | V <sub>IH</sub>                   |                                                                                  | 2.0                   |     | V <sub>CC</sub> | V     |

| Input Low Voltage                           | V <sub>IL</sub>                   |                                                                                  |                       |     | 0.8             | V     |

| Input Hysteresis                            | V <sub>HYST</sub>                 |                                                                                  |                       | 80  |                 | mV    |

| Input Leakage Current                       | I <sub>IL</sub> , I <sub>IH</sub> | Voltage at pin 0V to $V_{CC}$ , internal pullup or pulldown 75k $\Omega$ typical |                       |     | 85              | μΑ    |

| Output High Voltage                         | V <sub>OH</sub>                   | External pullup of 4.7kΩ to V <sub>CC</sub>                                      | V <sub>CC</sub> - 0.1 |     |                 | V     |

| Output Low Voltage                          | V <sub>OL</sub>                   | External pullup of 4.7k $\Omega$ to V <sub>CC</sub>                              |                       |     | 0.4             | V     |

| 3-WIRE DIGITAL INTERFACE T                  | IMING (Figure                     | 6)                                                                               |                       |     |                 |       |

| SCL Clock Frequency                         | fscl                              |                                                                                  |                       |     | 1               | MHz   |

| SCL Pulse-Width High                        | t <sub>CH</sub>                   |                                                                                  | 0.5                   |     |                 | μs    |

| SCL Pulse-Width Low                         | t <sub>CL</sub>                   |                                                                                  | 0.5                   |     |                 | μs    |

| SDA Setup Time                              | t <sub>DS</sub>                   |                                                                                  |                       | 100 |                 | ns    |

| SDA Hold Time                               | t <sub>DH</sub>                   |                                                                                  |                       | 100 |                 | ns    |

| SCL Rise to SDA Propagation Time            | t <sub>D</sub>                    |                                                                                  |                       | 5   |                 | ns    |

| CSEL Pulse-Width Low                        | t <sub>CSW</sub>                  |                                                                                  | 500                   |     |                 | ns    |

| CSEL Leading Time Before the First SCL Edge | tL                                |                                                                                  |                       | 500 |                 | ns    |

| CSEL Trailing Time After the Last SCL Edge  | t <sub>T</sub>                    |                                                                                  |                       | 500 |                 | ns    |

| SDA, SCL External Load                      | C <sub>B</sub>                    | Total bus capacitance on one line                                                |                       |     | 20              | pF    |

- **Note 1:** Specifications at  $T_A = -40^{\circ}C$  and  $T_A = +95^{\circ}C$  are guaranteed by design and characterization, .

- **Note 2:** Guaranteed by design and characterization,  $T_A = -40^{\circ}\text{C}$  to  $+95^{\circ}\text{C}$ .

- Note 3: The data input transition time is controlled by 4th-order Bessel filter with f<sub>-3dB</sub> = 0.75 x 1.25GHz and f<sub>-3dB</sub> = 0.75 x 2.5GHz, respectively. The deterministic jitter caused by this filter is not included in the DJ. A 2<sup>23</sup> 1 PRBS equivalent pattern was used.

- Note 4: RJ was tested without input filter.

- Note 5: For all Rx LOS specifications LOS\_LOWBW = 1 for 1.25Gbps operation and LOS\_LOWBW = 0 for 2.5Gbps operation.

- Note 6: Measurement includes an input AC-coupling capacitor of 0.1μF. The signal at the RIN input is switched between two amplitudes: Signal\_ON and Signal\_OFF.

- 1) Receiver operates at sensitivity level plus 1dB power penalty

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC}=2.97V\ to\ 3.63V,\ T_A=-40^{\circ}C\ to\ +95^{\circ}C;\ CML\ receiver\ output\ is\ AC-coupled\ to\ differential\ 100\Omega\ load;\ registers\ are\ set\ to\ default\ values,\ unless\ implied\ by\ test\ conditions.$  Typical values are at  $V_{CC}=3.3V,\ T_A=+25^{\circ}C,\ data\ rate=2.5Gbps,\ I_{BIAS}=20mA,\ and\ I_{MOD}=40mA,\ unless\ otherwise\ noted.)$  (Note 1)

- a) Signal\_OFF = 0

Signal\_ON = 10log(min\_assert\_level) + 8dB

b) Signal\_ON = 10log(max\_deassert\_level) + 1dB

Signal\_OFF = 0

- 2) Receiver operates at overload

Signal\_OFF = 0 Signal\_ON =  $1.2V_{P-P}$

max\_deassert\_level and min\_assert\_level are measured for one SET\_LOS setting

Note 7: Stability is defined [I<sub>MEASURED</sub>) - (I<sub>REFERENCE</sub>)]/(I<sub>REFERENCE</sub>) over the listed current range temperature and supply variation. Reference current measured at  $V_{CC}$  = 3.3V and  $T_A$  = +25°C. Measured current is measured at  $V_{CC}$  = 3.3V ±5% and  $T_A$  = -40°C to +95°C.

Figure 1. TIN Input Voltage Diagram

# 125Mbps to 3.125Gbps Integrated Limiting Amplifier/ Laser Driver with Dual-Loop Power Control

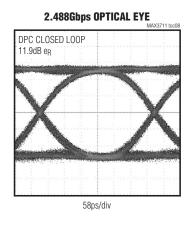

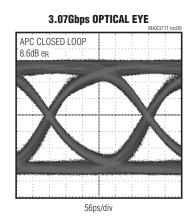

### **Typical Operating Characteristics**

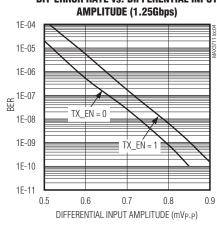

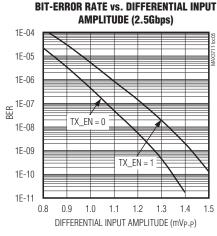

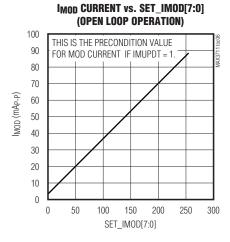

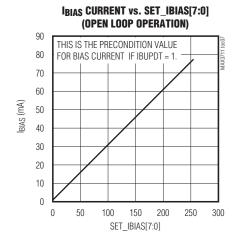

(Typical values are at  $V_{CC} = 3.3V$ ,  $T_A = +25^{\circ}C$ , data pattern =  $2^{23}$  - 1 PRBS, unless otherwise noted.)

# 125Mbps to 3.125Gbps Integrated Limiting Amplifier/ Laser Driver with Dual-Loop Power Control

### **Pin Configuration**

### **Pin Description**

| PIN | NAME    | OUTPUT FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | EQUIVALENT CIRCUIT                                |

|-----|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|

| 1   | FAULT   | Transmitter Fault, Open-Drain. Logic-high indicates a fault condition has been detected (FAULT_POL = 1). It remains high even after the fault condition has been removed. A logic-low occurs when the fault condition has been removed and the fault latch has been cleared by toggling the DISABLE signal, or by setting MODECTRL = 68h. FAULT should be pulled up to 3.3V supply through a $4.7 \mathrm{k}\Omega$ to $10 \mathrm{k}\Omega$ resistor. Note that pulling up the pin to a supply voltage above $V_{CCX}$ can turn on the ESD protection diode. | PROTECTION FAULT                                  |

| 2   | DISABLE | Transmitter Disable Input, TTL/CMOS. Set to logic-low for normal operation (DIS_POL = 1). Logic-high or open disables both the modulation current and the bias current. Internally pulled up by a $100 \text{k}\Omega$ resistor to $V_{CCX}$ .                                                                                                                                                                                                                                                                                                                | DISABLE VCCX VCCX VCCX VCCX PROTECTION PROTECTION |

## 125Mbps to 3.125Gbps Integrated Limiting Amplifier/ Laser Driver with Dual-Loop Power Control

| PIN  | NAME             | OUTPUT FUNCTION                                                                                                                                                                                                | EQUIVALENT CIRCUIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3    | CSEL             | Chip-Select Input, CMOS. Setting CSEL to logic-high starts a cycle. Setting CSEL to logic-low ends the cycle and resets the control state machine. Internally pulled down by a $75k\Omega$ resistor to ground. | CSEL PROTECTION VCCD PROTECTION TO THE PROTECTI |

| 4, 5 | ROUT+,<br>ROUT-  | Differential Receiver Data Output, CML. This output has $50\Omega$ terminations to $V_{CC}$ . Polarity is set by the RX_POL bit.                                                                               | V <sub>CCX</sub> ESD  50Ω PROTECTION  ROUT+ ROUT-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 6    | SCL              | Serial-Clock Input, CMOS. Internally pulled down by a $75 \text{k}\Omega$ resistor to ground.                                                                                                                  | SCL PROTECTION VCCD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 7    | V <sub>CCD</sub> | Power Supply. Provides supply voltage to the digital block.                                                                                                                                                    | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 8    | SDA              | Serial-Data Bidirectional Input, CMOS. Opendrain output. This pin has a 75k $\Omega$ internal pullup, but it requires an external 4.7k $\Omega$ to 10k $\Omega$ pullup to meet 3-wire timing specifications.   | SDA VCCD VCCD VCCD VCCD TSkQ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

## 125Mbps to 3.125Gbps Integrated Limiting Amplifier/ Laser Driver with Dual-Loop Power Control

| PIN       | NAME              | OUTPUT FUNCTION                                                                                                                                                        | EQUIVALENT CIRCUIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9, 10     | N.C.              | No Connection. Not internally connected.                                                                                                                               | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 11,<br>12 | TIN+/TIN-         | Differential Transmitter Data Input. This differential $13k\Omega$ input is compatible with LVDS, PECL, and CML input levels. The polarity is set by the TX_POL bit.   | $\begin{array}{c c} & & & & & & \\ & & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & \\ & & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & &$ |

| 13        | TP                | Test Pin. Leave pin unconnected.                                                                                                                                       | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |