PART NUMBER:

KXTI9-1001 Rev. 3 Dec-2012

### **Product Description**

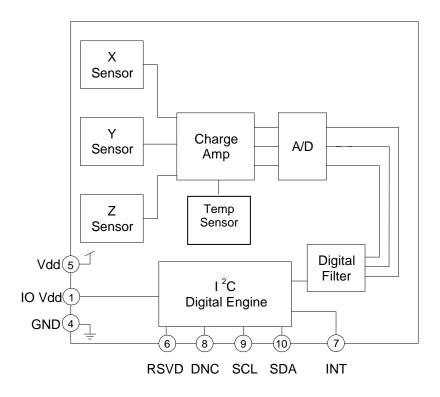

The KXTI9 is a tri-axis +/-2g, +/-4g or +/-8g silicon micromachined accelerometer with integrated orientation, tap/double tap, and activity detecting algorithms. The sense element is fabricated using Kionix's proprietary plasma micromachining process technology. Acceleration sensing is based on the principle of a differential capacitance arising from acceleration-induced motion of the sense element, which further utilizes common mode cancellation to decrease errors from process variation, temperature, and environmental stress. The sense element is hermetically sealed at the wafer level by bonding a second silicon lid wafer to the device using a glass frit. A separate ASIC device packaged with the sense element provides signal conditioning, and intelligent userprogrammable application algorithms. The accelerometer is delivered in a 3 x 3 x 0.9 mm LGA plastic package operating from a 1.8 – 3.6V DC supply. Voltage regulators are used to maintain

constant internal operating voltages over the range of input supply voltages. This results in stable operating characteristics over the range of input supply voltages and virtually undetectable ratiometric error.  $I^2C$  digital protocol is used to communicate with the chip to configure and check for updates to the orientation, Directional Tap<sup>TM</sup> detection and activity monitoring algorithms.

PART NUMBER:

KXTI9-1001 Rev. 3 Dec-2012

## **Functional Diagram**

PART NUMBER:

KXTI9-1001 Rev. 3 Dec-2012

## **Product Specifications**

#### Table 1. Mechanical

(specifications are for operation at 2.6V and T = 25C unless stated otherwise)

| F                                 | Parameters              | Units                     | Min                   | Typical               | Max  |  |

|-----------------------------------|-------------------------|---------------------------|-----------------------|-----------------------|------|--|

| Operating Temperatu               | ure Range               | °C                        | -40                   | -                     | 85   |  |

| Zero-g Offset                     |                         | mg - ±25 ±1               |                       |                       |      |  |

| Zero-g Offset Variatio            | on from RT over Temp.   | mg/ºC 0.7 (xy)<br>0.4 (z) |                       |                       |      |  |

|                                   | GSEL1=0, GSEL0=0 (± 2g) |                           | 988                   | 1024                  | 1060 |  |

| Sensitivity (12-bit) <sup>1</sup> | GSEL1=0, GSEL0=1 (± 4g) | counts/g                  | 494                   | 512                   | 530  |  |

|                                   | GSEL1=1, GSEL0=0 (± 8g) |                           | 247                   | 256                   | 265  |  |

|                                   | GSEL1=0, GSEL0=0 (± 2g) | counts/g                  | 61                    | 64                    | 67   |  |

| Sensitivity (8-bit) <sup>1</sup>  | GSEL1=0, GSEL0=1 (± 4g) |                           | 30                    | 32                    | 34   |  |

|                                   | GSEL1=1, GSEL0=0 (± 8g) |                           | 15                    | 16                    | 17   |  |

| Sensitivity Variation f           | rom RT over Temp.       | %/ºC                      |                       | 0.01 (xy)<br>0.03 (z) |      |  |

| Self Test Output cha              | nge on Activation       | g                         |                       | 0.7 (xy)<br>0.5 (z)   |      |  |

| Mechanical Resonan                | Hz                      |                           | 3500 (xy)<br>1800 (z) |                       |      |  |

| Non-Linearity                     |                         | % of FS                   |                       | 0.6                   |      |  |

| Cross Axis Sensitivity            | y                       | %                         |                       | 2                     |      |  |

Notes:

- 1. Resolution and acceleration ranges are user selectable via I<sup>2</sup>C.

- 2. Resonance as defined by the dampened mechanical sensor.

PART NUMBER:

**KXTI9-1001** Rev. 3 Dec-2012

### Table 2. Electrical

| (specifica                          | ations are for operation a                      | t 2.6V and T = | 25C unless s          | tated otherwis | se)                   |

|-------------------------------------|-------------------------------------------------|----------------|-----------------------|----------------|-----------------------|

| Par                                 | ameters                                         | Units          | Min                   | Typical        | Max                   |

| Supply Voltage (V <sub>dd</sub> )   | Operating                                       | V              | 1.71                  | 2.6            | 3.6                   |

| I/O Pads Supply Volt                | age (V <sub>IO</sub> )                          | V              | 1.7                   |                | V <sub>dd</sub>       |

|                                     | All On (RES = 1)                                |                |                       | 325            |                       |

| Current Consumptior                 | Directional Tap™<br>(RES = 0, ODR = 400Hz)      | μA             |                       | 165            |                       |

|                                     | <sup>'</sup> Low Power<br>(RES = 0, ODR ≤ 25Hz) | μΛ             |                       | 100            |                       |

|                                     | Standby                                         |                |                       | 10             |                       |

| Output Low Voltage                  | $(V_{io} < 2V)^1$                               | V              | -                     | -              | 0.2 * V <sub>io</sub> |

| Output Low Voltage                  | $(V_{io} > 2V)^1$                               | V              | -                     | -              | 0.4                   |

| Output High Voltage                 |                                                 | V              | 0.8 * V <sub>io</sub> | -              | -                     |

| Input Low Voltage                   |                                                 | V              | -                     | -              | 0.2 * V <sub>io</sub> |

| Input High Voltage                  |                                                 | V              | 0.8 * V <sub>io</sub> | -              | -                     |

| Input Pull-down Curre               | ent                                             | μA             |                       | 0              |                       |

|                                     | RES = 0                                         |                |                       | 0.050          |                       |

|                                     | RES = 1, ODR = 12.5Hz                           |                |                       | 81             |                       |

|                                     | RES = 1, ODR = 25 Hz                            |                |                       | 41             |                       |

| Start Up Time <sup>2</sup>          | RES = 1, ODR = 50Hz                             | ~~~            |                       | 21             |                       |

| Start Op Time                       | RES = 1, ODR = 100Hz                            | ms             |                       | 11             |                       |

|                                     | RES = 1, ODR = 200Hz                            |                |                       | 6              |                       |

|                                     | RES = 1, ODR = 400Hz                            |                |                       | 4              |                       |

| -                                   | RES = 1, ODR = 800Hz                            |                |                       | 2.5            |                       |

| Power Up Time <sup>3</sup>          |                                                 | ms             |                       | 10             |                       |

| I <sup>2</sup> C Communication Rate |                                                 | kHz            |                       |                | 400                   |

| Output Data Rate (O                 | DR) <sup>4</sup>                                | Hz             | 12.5                  | 50             | 800                   |

|                                     | RES = 0                                         | kHz            |                       | 1.59           |                       |

| Bandwidth (-3dB) <sup>5</sup>       | RES = 1                                         | Hz             |                       | ODR/2          |                       |

.... , . . .: - 11 ~ / . \

Notes:

- 1. For I<sup>2</sup>C communication, this assumes a minimum  $1.5k\Omega$  pull-up resistor on SCL and SDA pins.

- 2. Start up time is from PC1 set to valid outputs.

- 3. Power up time is from Vdd valid to device boot completion.

- 4. User selectable through  $I^2C$ .

- 5. User selectable and dependant on ODR and RES.

PART NUMBER:

KXTI9-1001 Rev. 3 Dec-2012

### Table 3. Environmental

| Paran                             | neters          | Units | Min  | Typical                           | Max  |

|-----------------------------------|-----------------|-------|------|-----------------------------------|------|

| Supply Voltage (V <sub>dd</sub> ) | Absolute Limits | V     | -0.5 | -                                 | 3.63 |

| Operating Temperatur              | e Range         | °C    | -40  | -                                 | 85   |

| Storage Temperature               | Range           | °C    | -55  | -                                 | 150  |

| Mech. Shock (powered              | g               | -     | -    | 5000 for 0.5ms<br>10000 for 0.2ms |      |

| ESD                               | HBM             | V     | -    | -                                 | 2000 |

Caution: ESD Sensitive and Mechanical Shock Sensitive Component, improper handling can cause permanent damage to the device.

This product conforms to Directive 2002/95/EC of the European Parliament and of the Council of the European Union (RoHS). Specifically, this product does not contain lead, mercury, cadmium, hexavalent chromium, polybrominated biphenyls (PBB), or polybrominated diphenyl ethers (PBDE) above the maximum concentration values (MCV) by weight in any of its homogenous materials. Homogenous materials are "of uniform

composition throughout."

This product is halogen-free per IEC 61249-2-21. Specifically, the materials used in this product contain a maximum total halogen content of 1500 ppm with less than 900-ppm bromine and less than 900-ppm chlorine.

### Soldering

Soldering recommendations are available upon request or from www.kionix.com.

PART NUMBER:

KXTI9-1001 Rev. 3 Dec-2012

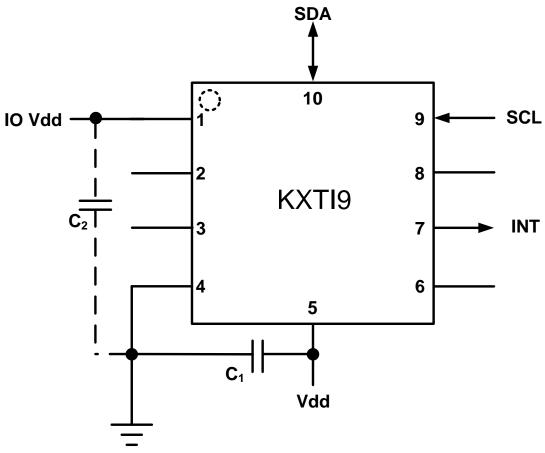

## **Application Schematic**

## Table 4. KXTI9 Pin Descriptions

| Pin | Name   | Description                                                                                                                      |

|-----|--------|----------------------------------------------------------------------------------------------------------------------------------|

| 1   | IO Vdd | The power supply input for the digital communication bus. Optionally decouple this pin to ground with a 0.1uF ceramic capacitor. |

| 2   | DNC    | Reserved – Do Not Connect                                                                                                        |

| 3   | DNC    | Reserved – Do Not Connect                                                                                                        |

| 4   | GND    | Ground                                                                                                                           |

| 5   | Vdd    | The power supply input. Decouple this pin to ground with a 0.1uF ceramic capacitor.                                              |

| 6   | RSVD   | Reserved – Float or connect to IO Vdd                                                                                            |

| 7   | INT    | Physical Interrupt                                                                                                               |

| 8   | DNC    | Reserved – Do Not Connect                                                                                                        |

| 9   | SCL    | I <sup>2</sup> C Serial Clock                                                                                                    |

| 10  | SDA    | I <sup>2</sup> C Serial Data                                                                                                     |

PART NUMBER:

KXTI9-1001 Rev. 3 Dec-2012

## **Test Specifications**

Special Characteristics:

These characteristics have been identified as being critical to the customer. Every part is tested to verify its conformance to specification prior to shipment.

### Table 5. Test Specifications

| Parameter          | Specification          | Test Conditions  |

|--------------------|------------------------|------------------|

| Zero-g Offset @ RT | 0 +/- 128 counts       | 25C, Vdd = 2.6 V |

| Sensitivity @ RT   | 1024 +/- 35.8 counts/g | 25C, Vdd = 2.6 V |

PART NUMBER:

KXTI9-1001 Rev. 3 Dec-2012

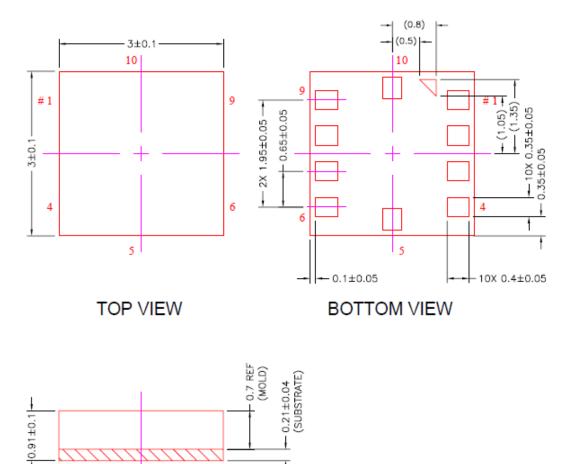

## **Package Dimensions and Orientation**

3 x 3 x 0.9 mm LGA

SIDE VIEW

All dimensions and tolerances conform to ASME Y14.5M-1994

36 Thornwood Dr. – Ithaca, NY 14850 tel: 607-257-1080 – fax:607-257-1146 www.kionix.com - <u>info@kionix.com</u>

PART NUMBER:

KXTI9-1001 Rev. 3 Dec-2012

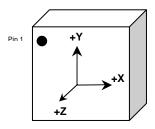

## Orientation

When device is accelerated in +X, +Y or +Z direction, the corresponding output will increase.

| Static X/Y/Z Output Response versus Orientation to Earth's surface (1g): |

|--------------------------------------------------------------------------|

| GSEL1=0, GSEL0=0 (± 2g)                                                  |

| Position          | 1    |    | 2    |    | 2 3   |     | 4     |     | 5             |    | 6             |     |

|-------------------|------|----|------|----|-------|-----|-------|-----|---------------|----|---------------|-----|

| Diagram           |      |    |      |    |       |     |       |     | Top<br>Bottom |    | Bottom<br>Top |     |

| Resolution (bits) | 12   | 8  | 12   | 8  | 12    | 8   | 12    | 8   | 12            | 8  | 12            | 8   |

| X (counts)        | 0    | 0  | 1024 | 64 | 0     | 0   | -1024 | -64 | 0             | 0  | 0             | 0   |

| Y (counts)        | 1024 | 64 | 0    | 0  | -1024 | -64 | 0     | 0   | 0             | 0  | 0             | 0   |

| Z (counts)        | 0    | 0  | 0    | 0  | 0     | 0   | 0     | 0   | 1024          | 64 | -1024         | -64 |

|                   |      |    |      |    |       |     |       |     |               |    |               |     |

| X-Polarity        | 0    |    | +    |    | 0     |     | -     |     | 0             |    | 0             |     |

| Y-Polarity        | +    |    | 0    | 0  |       |     | 0     |     | 0             |    | 0             |     |

| Z-Polarity        | 0    |    | 0    |    | 0     |     | 0     |     | +             |    | -             |     |

**↓** (1g)

Earth's Surface

PART NUMBER:

KXTI9-1001 Rev. 3 Dec-2012

## Static X/Y/Z Output Response versus Orientation to Earth's surface (1g):

|                   | GSEL1=0, GSEL0=1 (± 4g) |    |     |    |      |     |      |     |     |           |            |     |  |  |

|-------------------|-------------------------|----|-----|----|------|-----|------|-----|-----|-----------|------------|-----|--|--|

| Position          | 1                       |    | 2   |    | 3    |     | 4    | 4   |     |           | 6          |     |  |  |

| Diagram           |                         |    |     |    |      |     |      |     |     | op<br>tom | Bott<br>Tc |     |  |  |

| Resolution (bits) | 12                      | 8  | 12  | 8  | 12   | 8   | 12   | 8   | 12  | 8         | 12         | 8   |  |  |

| X (counts)        | 0 0                     |    | 512 | 32 | 0    | 0   | -512 | -32 | 0   | 0         | 0          | 0   |  |  |

| Y (counts)        | 512                     | 32 | 0   | 0  | -512 | -32 | 0    | 0   | 0   | 0         | 0          | 0   |  |  |

| Z (counts)        | 0                       | 0  | 0   | 0  | 0    | 0   | 0    | 0   | 512 | 32        | -512       | -32 |  |  |

|                   |                         |    |     |    |      |     |      |     |     |           |            |     |  |  |

| X-Polarity        | 0                       |    | +   |    | 0    |     | -    |     | 0   |           | 0          |     |  |  |

| Y-Polarity        | +                       |    | 0   |    | -    |     | 0    |     | 0   |           | 0          |     |  |  |

| Z-Polarity        | 0                       |    | 0   |    | 0    |     | 0    |     | +   |           | -          |     |  |  |

## , (1g)

Earth's Surface

### Static X/Y/Z Output Response versus Orientation to Earth's surface (1g): GSEL1=1, GSEL0=0 (± 8g)

| )      |    |                          |                                                                | 1                                                |                                                                                        |                                                                      |                                                                                                                                                                                                                                            | 5                                                                                                                                                                                                                                                                                |                                                       | 6                                                     |                                                       |

|--------|----|--------------------------|----------------------------------------------------------------|--------------------------------------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|

|        | ]  |                          |                                                                |                                                  |                                                                                        |                                                                      |                                                                                                                                                                                                                                            | Top<br>Bottom                                                                                                                                                                                                                                                                    |                                                       | Bottom<br>Top                                         |                                                       |

| 2      | 8  | 12                       | 8                                                              | 12                                               | 8                                                                                      | 12                                                                   | 8                                                                                                                                                                                                                                          | 12                                                                                                                                                                                                                                                                               | 8                                                     | 12                                                    | 8                                                     |

| )      | 0  | 256                      | 16                                                             | 0                                                | 0                                                                                      | -256                                                                 | -16                                                                                                                                                                                                                                        | 0                                                                                                                                                                                                                                                                                | 0                                                     | 0                                                     | 0                                                     |

| 56     | 16 | 0                        | 0                                                              | -256                                             | -16                                                                                    | 0                                                                    | 0                                                                                                                                                                                                                                          | 0                                                                                                                                                                                                                                                                                | 0                                                     | 0                                                     | 0                                                     |

| )      | 0  | 0                        | 0                                                              | 0                                                | 0                                                                                      | 0                                                                    | 0                                                                                                                                                                                                                                          | 256                                                                                                                                                                                                                                                                              | 16                                                    | -256                                                  | -16                                                   |

| 0      |    | +                        |                                                                | (                                                | )                                                                                      | -                                                                    |                                                                                                                                                                                                                                            | 0                                                                                                                                                                                                                                                                                |                                                       | 0                                                     |                                                       |

| +      |    | 0                        |                                                                | -                                                |                                                                                        | 0                                                                    |                                                                                                                                                                                                                                            | 0                                                                                                                                                                                                                                                                                |                                                       | 0                                                     |                                                       |

| 0      |    | 0                        |                                                                | C                                                | )                                                                                      | 0                                                                    |                                                                                                                                                                                                                                            | +                                                                                                                                                                                                                                                                                |                                                       | -                                                     |                                                       |

| (<br>( | +  | 0 0<br>56 16<br>0 0<br>• | 0 0 256<br>56 16 0<br>0 0 0<br>• • • • • • • • • • • • • • • • | 0 0 256 16<br>56 16 0 0<br>0 0 0 0<br>0 +<br>+ 0 | 0 0 256 16 0<br>56 16 0 0 -256<br>0 0 0 0 0 0<br>− − − − − − − − − − − − − − − − − − − | 0 0 256 16 0 0<br>56 16 0 0 -256 -16<br>0 0 0 0 0 0 0<br>− − − − − − | 0     0     256     16     0     0     -256       56     16     0     0     -256     -16     0       0     0     0     0     0     0     0       0     +     0     -     -       +     0     -     0     0       0     0     0     0     0 | 0     0     256     16     0     0     -256     -16       56     16     0     0     -256     -16     0     0       0     0     0     0     0     0     0     0       0     +     0     -     -     -       +     0     -     0     0     0       0     0     0     0     0     0 | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ |

PART NUMBER:

KXTI9-1001 Rev. 3 Dec-2012

## **KXTI9 Digital Interface**

The Kionix KXTI9 digital accelerometer has the ability to communicate on the I<sup>2</sup>C digital serial interface bus. This flexibility allows for easy system integration by eliminating analog-to-digital converter requirements and by providing direct communication with system micro-controllers. In doing so, all of the digital communication pins have shared responsibilities.

The serial interface terms and descriptions as indicated in Table 6 below will be observed throughout this document.

| Term        | Description                                                                               |

|-------------|-------------------------------------------------------------------------------------------|

| Transmitter | The device that transmits data to the bus.                                                |

| Receiver    | The device that receives data from the bus.                                               |

| Master      | The device that initiates a transfer, generates clock signals, and terminates a transfer. |

| Slave       | The device addressed by the Master.                                                       |

Table 6.

Serial Interface Terminologies

## I<sup>2</sup>C Serial Interface

As previously mentioned, the KXTI9 has the ability to communicate on an I<sup>2</sup>C bus. I<sup>2</sup>C is primarily used for synchronous serial communication between a Master device and one or more Slave devices. The Master, typically a micro controller, provides the serial clock signal and addresses Slave devices on the bus. The KXTI9 always operates as a Slave device during standard Master-Slave I<sup>2</sup>C operation.

I<sup>2</sup>C is a two-wire serial interface that contains a Serial Clock (SCL) line and a Serial Data (SDA) line. SCL is a serial clock that is provided by the Master, but can be held low by any Slave device, putting the Master into a wait condition. SDA is a bi-directional line used to transmit and receive data to and from the interface. Data is transmitted MSB (Most Significant Bit) first in 8-bit per byte format, and the number of bytes transmitted per transfer is unlimited. The I<sup>2</sup>C bus is considered free when both lines are high.

## I<sup>2</sup>C Operation

Transactions on the I<sup>2</sup>C bus begin after the Master transmits a start condition (S), which is defined as a highto-low transition on the data line while the SCL line is held high. The bus is considered busy after this condition. The next byte of data transmitted after the start condition contains the Slave Address (SAD) in the seven MSBs (Most Significant Bits), and the LSB (Least Significant Bit) tells whether the Master will be receiving data '1' from the Slave or transmitting data '0' to the Slave. When a Slave Address is sent, each device on the bus compares the seven MSBs with its internally stored address. If they match, the device considers itself addressed by the Master. The Slave Address associated with the KXTI9 is 0001111.

PART NUMBER:

KXTI9-1001 Rev. 3 Dec-2012

It is mandatory that receiving devices acknowledge (ACK) each transaction. Therefore, the transmitter must release the SDA line during this ACK pulse. The receiver then pulls the data line low so that it remains stable low during the high period of the ACK clock pulse. A receiver that has been addressed, whether it is Master or Slave, is obliged to generate an ACK after each byte of data has been received. To conclude a transaction, the Master must transmit a stop condition (P) by transitioning the SDA line from low to high while SCL is high. The I<sup>2</sup>C bus is now free.

### Writing to a KXTI9 8-bit Register

Upon power up, the Master must write to the KXTI9's control registers to set its operational mode. Therefore, when writing to a control register on the I<sup>2</sup>C bus, as shown Sequence 1 on the following page, the following protocol must be observed: After a start condition, SAD+W transmission, and the KXTI9 ACK has been returned, an 8-bit Register Address (RA) command is transmitted by the Master. This command is telling the KXTI9 to which 8-bit register the Master will be writing the data. Since this is I<sup>2</sup>C mode, the MSB of the RA command should always be zero (0). The KXTI9 acknowledges the RA and the Master transmits the data to be stored in the 8-bit register. The KXTI9 acknowledges that it has received the data and the Master transmits a stop condition (P) to end the data transfer. The data sent to the KXTI9 is now stored in the appropriate register. The KXTI9 automatically increments the received RA commands and, therefore, multiple bytes of data can be written to sequential registers after each Slave ACK as shown in Sequence 2 on the following page.

#### Reading from a KXTI9 8-bit Register

When reading data from a KXTI9 8-bit register on the I<sup>2</sup>C bus, as shown in Sequence 3 on the next page, the following protocol must be observed: The Master first transmits a start condition (S) and the appropriate Slave Address (SAD) with the LSB set at '0' to write. The KXTI9 acknowledges and the Master transmits the 8-bit RA of the register it wants to read. The KXTI9 again acknowledges, and the Master transmits a repeated start condition (Sr). After the repeated start condition, the Master addresses the KXTI9 with a '1' in the LSB (SAD+R) to read from the previously selected register. The Slave then acknowledges and transmits the data from the requested register. The Master does not acknowledge (NACK) it received the transmitted data, but transmits a stop condition to end the data transfer. Note that the KXTI9 automatically increments through its sequential registers, allowing data to be read from multiple registers following a single SAD+R command as shown below in Sequence 4 on the following page.

If a receiver cannot transmit or receive another complete byte of data until it has performed some other function, it can hold SCL low to force the transmitter into a wait state. Data transfer only continues when the receiver is ready for another byte and releases SCL.

PART NUMBER:

KXTI9-1001 Rev. 3 Dec-2012

### **Data Transfer Sequences**

The following information clearly illustrates the variety of data transfers that can occur on the I<sup>2</sup>C bus and how the Master and Slave interact during these transfers. Table 7 defines the I<sup>2</sup>C terms used during the data transfers.

| Term | Definition                |

|------|---------------------------|

| S    | Start Condition           |

| Sr   | Repeated Start Condition  |

| SAD  | Slave Address             |

| W    | Write Bit                 |

| R    | Read Bit                  |

| ACK  | Acknowledge               |

| NACK | Not Acknowledge           |

| RA   | Register Address          |

| Data | Transmitted/Received Data |

| Р    | Stop Condition            |

Table 7.I<sup>2</sup>C Terms

**Sequence 1.** The Master is writing one byte to the Slave.

| Master | S | SAD + W |     | RA |     | DATA |     | Р |

|--------|---|---------|-----|----|-----|------|-----|---|

| Slave  |   |         | ACK |    | ACK |      | ACK |   |

Sequence 2. The Master is writing multiple bytes to the Slave.

| Master | S | SAD + W |     | RA |     | DATA |     | DATA |     | Р |

|--------|---|---------|-----|----|-----|------|-----|------|-----|---|

| Slave  |   |         | ACK |    | ACK |      | ACK |      | ACK |   |

**Sequence 3.** The Master is receiving one byte of data from the Slave.

| Master | S | SAD + W |     | RA |     | Sr | SAD + R |     |      | NACK | Р |

|--------|---|---------|-----|----|-----|----|---------|-----|------|------|---|

| Slave  |   |         | ACK |    | ACK |    |         | ACK | DATA |      |   |

Sequence 4. The Master is receiving multiple bytes of data from the Slave.

| Master | S | SAD + W |     | RA |     | Sr | SAD + R |     |      | ACK |      | NACK | Р |

|--------|---|---------|-----|----|-----|----|---------|-----|------|-----|------|------|---|

| Slave  |   |         | ACK |    | ACK |    |         | ACK | DATA |     | DATA |      |   |

PART NUMBER:

KXTI9-1001 Rev. 3 Dec-2012

## **KXTI9 Embedded Registers**

The KXTI9 has 44 embedded 8-bit registers that are accessible by the user. This section contains the addresses for all embedded registers and also describes bit functions of each register. Table 8 below provides a listing of the accessible 8-bit registers and their addresses.

|                 | Туре       | I2C Address |           |  |

|-----------------|------------|-------------|-----------|--|

| Register Name   | Read/Write | Hex         | Binary    |  |

| XOUT_HPF_L      | R          | 0x00        | 0000 0000 |  |

| XOUT_HPF_H      | R          | 0x01        | 0000 0001 |  |

| YOUT_HPF_L      | R          | 0x02        | 0000 0010 |  |

| YOUT_HPF_H      | R          | 0x03        | 0000 0011 |  |

| ZOUT_HPF_L      | R          | 0x04        | 0000 0100 |  |

| ZOUT_HPF_H      | R          | 0x05        | 0000 0101 |  |

| XOUT_L          | R          | 0x06        | 0000 0110 |  |

| XOUT_H          | R          | 0x07        | 0000 0111 |  |

| YOUT_L          | R          | 0x08        | 0000 1000 |  |

| YOUT_H          | R          | 0x09        | 0000 1001 |  |

| ZOUT_L          | R          | 0x0A        | 0000 1010 |  |

| ZOUT_H          | R          | 0x0B        | 0000 1011 |  |

| DCST_RESP       | R          | 0x0C        | 0000 1100 |  |

| Not Used        | -          | 0x0D        | 0000 1101 |  |

| Not Used        | -          | 0x0E        | 0000 1110 |  |

| WHO_AM_I        | R          | 0x0F        | 0000 1111 |  |

| TILT_POS_CUR    | R          | 0x10        | 0001 0000 |  |

| TILT_POS_PRE    | R          | 0x11        | 0001 0001 |  |

| Kionix Reserved | -          | 0x12        | 0001 0010 |  |

| Kionix Reserved | -          | 0x13        | 0001 0011 |  |

| Kionix Reserved | -          | 0x14        | 0001 0100 |  |

| INT_SRC_REG1    | R          | 0x15        | 0001 0101 |  |

| INT_SRC_REG2    | R          | 0x16        | 0001 0110 |  |

| Not Used        | -          | 0x17        | 0001 0111 |  |

| STATUS_REG      | R          | 0x18        | 0001 1000 |  |

| Not Used        | -          | 0x19        | 0001 1001 |  |

| INT_REL         | R          | 0x1A        | 0001 1010 |  |

| CTRL_REG1*      | R/W        | 0x1B        | 0001 1011 |  |

| CTRL_REG2*      | R/W        | 0x1C        | 0001 1100 |  |

36 Thornwood Dr. – Ithaca, NY 14850 tel: 607-257-1080 – fax:607-257-1146 www.kionix.com - <u>info@kionix.com</u>

PART NUMBER:

KXTI9-1001 Rev. 3 Dec-2012

| CTRL_REG3*         R/W         0x1D         0001 1101           INT_CTRL_REG1*         R/W         0x1E         0001 1110           INT_CTRL_REG2*         R/W         0x1F         0001 0000           DATA_CTRL_REG3*         R/W         0x20         0010 0000           DATA_CTRL_REG*         R/W         0x21         0010 0001           Not Used         -         0x22 - 0x27         -           TILT_TIMER*         R/W         0x28         0010 1000           WUF_TIMER*         R/W         0x28         0010 1001           Not Used         -         0x2A         0010 1010           TDT_TIMER*         R/W         0x2B         0010 1011           TDT_TAP_TIMER*         R/W         0x2C         0010 1100           TDT_TAP_TIMER*         R/W         0x2D         0010 1101           TDT_TOTAL_TIMER*         R/W         0x30         0011 0000           TDT_WINDOW_TIMER*         R/W         0x32         0011 0100           BUF_CTRL1*         R/W         0x33         0011 0101           BUF_STATUS_REG2         R         0x34         0011 0100           BUF_STATUS_REG2         R         0x36         0111 010 <td< th=""><th></th><th></th><th></th><th></th></td<>                               |                    |     |             |           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------------|-----------|

| INT_CTRL_REG2*         R/W         0x1F         0001 1111           INT_CTRL_REG3*         R/W         0x20         0010 0000           DATA_CTRL_REG*         R/W         0x21         0010 0001           Not Used         -         0x22 - 0x27         -           TILT_TIMER*         R/W         0x28         0010 1000           WUF_TIMER*         R/W         0x29         0010 1001           Not Used         -         0x2A         0010 1010           TDT_TIMER*         R/W         0x2B         0010 1011           TDT_TAP_TIMER*         R/W         0x2C         0010 1110           TDT_L_THRESH*         R/W         0x2D         0010 1110           TDT_TOTAL_TIMER*         R/W         0x2E         0010 1111           TDT_LOTAL_TIMER*         R/W         0x30         0011 1010           TDT_VOTAL_TIMER*         R/W         0x31         0011 0001           TDT_VOTAL_TIMER*         R/W         0x32         0011 0100           BUF_CTRL1*         R/W         0x33         0011 0001           BUF_STATUS_REG2         R         0x34         0011 010           BUF_STATUS_REG2         R         0x37 - 0x39         -                                                                                 | CTRL_REG3*         | R/W | 0x1D        | 0001 1101 |

| INT_CTRL_REG3*         R/W         0x20         0010 0000           DATA_CTRL_REG*         R/W         0x21         0010 0001           Not Used         -         0x22 - 0x27         -           TILT_TIMER*         R/W         0x28         0010 1000           WUF_TIMER*         R/W         0x29         0010 1001           Not Used         -         0x2A         0010 1010           TDT_TIMER*         R/W         0x2B         0010 1011           TDT_TAP_TIMER*         R/W         0x2C         0010 1100           TDT_L_THRESH*         R/W         0x2D         0010 1110           TDT_TAP_TIMER*         R/W         0x2E         0010 1110           TDT_TOTAL_TIMER*         R/W         0x32         0011 1010           TDT_WINDOW_TIMER*         R/W         0x30         0011 0000           TDT_WINDOW_TIMER*         R/W         0x33         0011 0010           BUF_STATUS_REG1         R         0x34         0011 010           BUF_STATUS_REG2         R         0x35         0011 010           BUF_STATUS_REG2         R/W         0x3A         0011 1010           Reserved         -         0x37 - 0x39         - <td< td=""><td>INT_CTRL_REG1*</td><td>R/W</td><td>0x1E</td><td>0001 1110</td></td<> | INT_CTRL_REG1*     | R/W | 0x1E        | 0001 1110 |

| DATA_CTRL_REG*         R/W         0x21         0010 0001           Not Used         -         0x22 - 0x27         -           TILT_TIMER*         R/W         0x28         0010 1000           WUF_TIMER*         R/W         0x29         0010 1001           Not Used         -         0x2A         0010 1001           Not Used         -         0x2A         0010 1010           TDT_TIMER*         R/W         0x2B         0010 1011           TDT_L_THRESH*         R/W         0x2C         0010 1110           TDT_L_THRESH*         R/W         0x2D         0010 1110           TDT_TOTAL_TIMER*         R/W         0x2E         0010 1111           TDT_TOTAL_TIMER*         R/W         0x30         0011 0000           TDT_WINDOW_TIMER*         R/W         0x31         0011 0001           BUF_CTRL2*         R/W         0x33         0011 0010           BUF_STATUS_REG1         R         0x34         0011 010           BUF_STATUS_REG2         R         0x35         0011 1010           Reserved         -         0x38 - 0x59         -           WUF_THRESH*         R/W         0x5A         0101 1010           Reserved                                                                                   | INT_CTRL_REG2*     | R/W | 0x1F        | 0001 1111 |

| Not Used         -         0x22 - 0x27         -           TILT_TIMER*         R/W         0x28         0010 1000           WUF_TIMER*         R/W         0x29         0010 1001           Not Used         -         0x2A         0010 1010           TDT_TIMER*         R/W         0x2B         0010 1011           TDT_LTIMER*         R/W         0x2C         0010 1100           TDT_L_THRESH*         R/W         0x2D         0010 1110           TDT_TOTAL_TIMER*         R/W         0x2E         0010 1110           TDT_TOTAL_TIMER*         R/W         0x2F         0010 1111           TDT_UTOTAL_TIMER*         R/W         0x30         0011 0000           TDT_WINDOW_TIMER*         R/W         0x31         0011 0001           BUF_CTRL1*         R/W         0x33         0011 0010           BUF_STATUS_REG1         R         0x34         0011 010           BUF_STATUS_REG2         R         0x36         0011 1010           Reserved         -         0x37 - 0x39         -           SELF_TEST         R/W         0x5A         0101 1010           Reserved         -         0x5B         0101 1010           Reserved                                                                                    | INT_CTRL_REG3*     | R/W | 0x20        | 0010 0000 |

| TILT_TIMER*         R/W         0x28         0010 1000           WUF_TIMER*         R/W         0x29         0010 1001           Not Used         -         0x2A         0010 1010           TDT_TIMER*         R/W         0x2B         0010 1011           TDT_H_THRESH*         R/W         0x2C         0010 1110           TDT_L_THRESH*         R/W         0x2D         0010 1101           TDT_TAP_TIMER*         R/W         0x2E         0010 1110           TDT_TAP_TIMER*         R/W         0x2E         0010 1110           TDT_TOTAL_TIMER*         R/W         0x2F         0010 1111           TDT_VOTAL_TIMER*         R/W         0x30         0011 0000           TDT_WINDOW_TIMER*         R/W         0x31         0011 0001           BUF_CTRL1*         R/W         0x32         0011 0010           BUF_STATUS_REG1         R         0x34         0011 010           BUF_CLEAR         W         0x36         0011 010           Reserved         -         0x37 – 0x39         -           SELF_TEST         R/W         0x3A         0011 1010           Reserved         -         0x5A         0101 1010           Reserved                                                                                   | DATA_CTRL_REG*     | R/W | 0x21        | 0010 0001 |

| WUF_TIMER*         R/W         0x29         0010 1001           Not Used         -         0x2A         0010 1010           TDT_TIMER*         R/W         0x2B         0010 1011           TDT_H_THRESH*         R/W         0x2C         0010 1100           TDT_L_THRESH*         R/W         0x2D         0010 1100           TDT_L_THRESH*         R/W         0x2D         0010 1110           TDT_TAP_TIMER*         R/W         0x2E         0010 1110           TDT_TOTAL_TIMER*         R/W         0x30         0011 0000           TDT_WINDOW_TIMER*         R/W         0x31         0011 0001           BUF_CTRL1*         R/W         0x32         0011 0101           BUF_STATUS_REG1         R         0x34         0011 0100           BUF_STATUS_REG2         R         0x35         0011 010           BUF_CLEAR         W         0x36         0011 010           Reserved         -         0x37 - 0x39         -           SELF_TEST         R/W         0x5A         0101 101           Reserved         -         0x5B         0101 1010           Reserved         -         0x5B         0101 1011           TLT_ANGLE* <t< td=""><td>Not Used</td><td>-</td><td>0x22 – 0x27</td><td>-</td></t<>                  | Not Used           | -   | 0x22 – 0x27 | -         |

| Not Used         -         0x2A         0010 1010           TDT_TIMER*         R/W         0x2B         0010 1011           TDT_H_THRESH*         R/W         0x2C         0010 1100           TDT_L_THRESH*         R/W         0x2D         0010 1101           TDT_L_THRESH*         R/W         0x2D         0010 1101           TDT_TAP_TIMER*         R/W         0x2E         0010 1110           TDT_TOTAL_TIMER*         R/W         0x30         0011 0000           TDT_WINDOW_TIMER*         R/W         0x31         0011 0001           BUF_CTRL1*         R/W         0x32         0011 0010           BUF_STATUS_REG1         R         0x34         0011 0101           BUF_STATUS_REG2         R         0x35         0011 010           BUF_CLEAR         W         0x36         0011 010           BUF_CLEAR         W         0x3A         0011 1010           Reserved         -         0x3B - 0x59         -           WUF_THRESH*         R/W         0x5A         0101 1010           Reserved         -         0x5B         0101 1010           Reserved         -         0x5D - 0x5E         -           HYST_SET*                                                                                             | TILT_TIMER*        | R/W | 0x28        | 0010 1000 |

| TDT_TIMER*         R/W         0x2B         0010 1011           TDT_H_THRESH*         R/W         0x2C         0010 1100           TDT_L_THRESH*         R/W         0x2D         0010 1101           TDT_TAP_TIMER*         R/W         0x2E         0010 1110           TDT_TOTAL_TIMER*         R/W         0x2E         0010 1111           TDT_TOTAL_TIMER*         R/W         0x30         0011 0000           TDT_WINDOW_TIMER*         R/W         0x31         0011 0001           BUF_CTRL1*         R/W         0x32         0011 0010           BUF_CTRL2*         R/W         0x33         0011 0010           BUF_STATUS_REG1         R         0x34         0011 0100           BUF_CLEAR         W         0x36         0011 0101           BUF_CLEAR         W         0x36         0011 0101           Reserved         -         0x37 - 0x39         -           WUF_THRESH*         R/W         0x5A         0101 1010           Reserved         -         0x5B         0101 1010           Reserved         -         0x5B         0101 1010           Reserved         -         0x5D - 0x5E         -           HYST_SET* <t< td=""><td>WUF_TIMER*</td><td>R/W</td><td>0x29</td><td>0010 1001</td></t<>             | WUF_TIMER*         | R/W | 0x29        | 0010 1001 |

| TDT_H_THRESH*         R/W         0x2C         0010 1100           TDT_L_THRESH*         R/W         0x2D         0010 1101           TDT_TAP_TIMER*         R/W         0x2E         0010 1110           TDT_TOTAL_TIMER*         R/W         0x2F         0010 1111           TDT_LATENCY_TIMER*         R/W         0x30         0011 0000           TDT_WINDOW_TIMER*         R/W         0x31         0011 0001           BUF_CTRL1*         R/W         0x32         0011 0010           BUF_CTRL2*         R/W         0x33         0011 0010           BUF_STATUS_REG1         R         0x34         0011 0100           BUF_CLEAR         W         0x36         0011 0101           BUF_CLEAR         W         0x36         0011 0101           Reserved         -         0x37 - 0x39         -           SELF_TEST         R/W         0x3A         0011 1010           Reserved         -         0x3B - 0x59         -           WUF_THRESH*         R/W         0x5A         0101 1010           Reserved         -         0x5B         0101 1010           Reserved         -         0x5D - 0x5E         -           HYST_SET* <t< td=""><td>Not Used</td><td>-</td><td>0x2A</td><td>0010 1010</td></t<>                 | Not Used           | -   | 0x2A        | 0010 1010 |

| TDT_L_THRESH*         R/W         0x2D         0010 1101           TDT_TAP_TIMER*         R/W         0x2E         0010 1110           TDT_TOTAL_TIMER*         R/W         0x2F         0010 1111           TDT_LATENCY_TIMER*         R/W         0x30         0011 0000           TDT_WINDOW_TIMER*         R/W         0x31         0011 0001           BUF_CTRL1*         R/W         0x32         0011 0010           BUF_STATUS_REG1         R         0x34         0011 0100           BUF_STATUS_REG2         R         0x35         0011 0101           BUF_CLEAR         W         0x36         0011 0101           Reserved         -         0x37 – 0x39         -           SELF_TEST         R/W         0x5A         0101 1010           Reserved         -         0x3B – 0x59         -           WUF_THRESH*         R/W         0x5A         0101 1010           Reserved         -         0x5B         0101 1011           TILT_ANGLE*         R/W         0x5C         0101 1100           Reserved         -         0x5D – 0x5E         -           HYST_SET*         R/W         0x5F         0101 1111                                                                                                            | TDT_TIMER*         | R/W | 0x2B        | 0010 1011 |

| TDT_TAP_TIMER*         R/W         0x2E         0010 1110           TDT_TOTAL_TIMER*         R/W         0x2F         0010 1111           TDT_LATENCY_TIMER*         R/W         0x30         0011 0000           TDT_WINDOW_TIMER*         R/W         0x31         0011 0001           BUF_CTRL1*         R/W         0x32         0011 0010           BUF_CTRL2*         R/W         0x33         0011 0011           BUF_STATUS_REG1         R         0x34         0011 0100           BUF_STATUS_REG2         R         0x35         0011 0101           BUF_CLEAR         W         0x36         0011 0101           Reserved         -         0x37 – 0x39         -           SELF_TEST         R/W         0x5A         0101 1010           Reserved         -         0x3B – 0x59         -           WUF_THRESH*         R/W         0x5A         0101 1010           Reserved         -         0x5B         0101 1011           TILT_ANGLE*         R/W         0x5C         0101 1100           Reserved         -         0x5D – 0x5E         -           HYST_SET*         R/W         0x5F         0101 1111                                                                                                               | TDT_H_THRESH*      | R/W | 0x2C        | 0010 1100 |

| TDT_TOTAL_TIMER*         R/W         0x2F         0010 1111           TDT_LATENCY_TIMER*         R/W         0x30         0011 0000           TDT_WINDOW_TIMER*         R/W         0x31         0011 0001           BUF_CTRL1*         R/W         0x32         0011 0010           BUF_CTRL2*         R/W         0x33         0011 0011           BUF_STATUS_REG1         R         0x34         0011 0100           BUF_STATUS_REG2         R         0x35         0011 0101           BUF_CLEAR         W         0x36         0011 0101           BUF_CLEAR         W         0x37 - 0x39         -           SELF_TEST         R/W         0x3A         0011 1010           Reserved         -         0x38 - 0x59         -           WUF_THRESH*         R/W         0x5A         0101 1010           Reserved         -         0x5B         0101 1010           Reserved         -         0x5B         0101 1011           TILT_ANGLE*         R/W         0x5C         0101 1111           HYST_SET*         R/W         0x5F         0101 1111                                                                                                                                                                                 | TDT_L_THRESH*      | R/W | 0x2D        | 0010 1101 |

| TDT_LATENCY_TIMER*         R/W         0x30         0011 0000           TDT_WINDOW_TIMER*         R/W         0x31         0011 0001           BUF_CTRL1*         R/W         0x32         0011 0010           BUF_CTRL2*         R/W         0x33         0011 0011           BUF_STATUS_REG1         R         0x34         0011 0100           BUF_STATUS_REG2         R         0x35         0011 0101           BUF_CLEAR         W         0x36         0011 0101           Reserved         -         0x37 - 0x39         -           SELF_TEST         R/W         0x3A         0011 1010           Reserved         -         0x3B - 0x59         -           WUF_THRESH*         R/W         0x5A         0101 1010           Reserved         -         0x5B         0101 1011           TILT_ANGLE*         R/W         0x5C         0101 1110           Reserved         -         0x5D - 0x5E         -           HYST_SET*         R/W <t< td=""><td>TDT_TAP_TIMER*</td><td>R/W</td><td>0x2E</td><td>0010 1110</td></t<>                  | TDT_TAP_TIMER*     | R/W | 0x2E        | 0010 1110 |

| TDT_WINDOW_TIMER*         R/W         0x31         0011 0001           BUF_CTRL1*         R/W         0x32         0011 0010           BUF_CTRL2*         R/W         0x33         0011 0011           BUF_STATUS_REG1         R         0x34         0011 0100           BUF_STATUS_REG2         R         0x35         0011 0101           BUF_CLEAR         W         0x36         0011 0101           Reserved         -         0x37 - 0x39         -           SELF_TEST         R/W         0x3A         0011 1010           Reserved         -         0x37 - 0x39         -           WUF_THRESH*         R/W         0x3A         0011 1010           Reserved         -         0x3B - 0x59         -           WUF_THRESH*         R/W         0x5A         0101 1010           Reserved         -         0x5B         0101 1010           Reserved         -         0x5B         0101 1010           Reserved         -         0x5D - 0x5E         -           HYST_SET*         R/W         0x5F         0101 1111                                                                                                                                                                                                          | TDT_TOTAL_TIMER*   | R/W | 0x2F        | 0010 1111 |

| BUF_CTRL1*         R/W         0x32         0011 0010           BUF_CTRL2*         R/W         0x33         0011 0011           BUF_STATUS_REG1         R         0x34         0011 0100           BUF_STATUS_REG2         R         0x35         0011 0101           BUF_CLEAR         W         0x36         0011 0101           BUF_CLEAR         W         0x37 - 0x39         -           SELF_TEST         R/W         0x38         0011 1010           Reserved         -         0x38 - 0x59         -           WUF_THRESH*         R/W         0x5A         0101 1010           Reserved         -         0x5B         0101 1011           TILT_ANGLE*         R/W         0x5C         0101 1100           Reserved         -         0x5D - 0x5E         -           HYST_SET*         R/W         0x5F         0101 1111                                                                                                                                                                                                                   | TDT_LATENCY_TIMER* | R/W | 0x30        | 0011 0000 |

| BUF_CTRL2*         R/W         0x33         0011 0011           BUF_STATUS_REG1         R         0x34         0011 0100           BUF_STATUS_REG2         R         0x35         0011 0101           BUF_CLEAR         W         0x36         0011 0110           Reserved         -         0x37 – 0x39         -           SELF_TEST         R/W         0x3B – 0x59         -           WUF_THRESH*         R/W         0x5A         0101 1010           Reserved         -         0x5B         0101 1010           Reserved         -         0x5B         0101 1010           Reserved         -         0x5D         -           WUF_THRESH*         R/W         0x5C         0101 1010           Reserved         -         0x5B         0101 1011           TILT_ANGLE*         R/W         0x5D – 0x5E         -           HYST_SET*         R/W         0x5F         0101 1111                                                                                                                                                                                                                                                                                                                                                   | TDT_WINDOW_TIMER*  | R/W | 0x31        | 0011 0001 |

| BUF_STATUS_REG1         R         0x34         0011 0100           BUF_STATUS_REG2         R         0x35         0011 0101           BUF_CLEAR         W         0x36         0011 0101           Reserved         -         0x37 - 0x39         -           SELF_TEST         R/W         0x3B - 0x59         -           WUF_THRESH*         R/W         0x5A         0101 1010           Reserved         -         0x5B         0101 1010           Reserved         -         0x5D         -           WUF_THRESH*         R/W         0x5C         0101 1010           Reserved         -         0x5D         -           HYST_SET*         R/W         0x5D         0101 1111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | BUF_CTRL1*         | R/W | 0x32        | 0011 0010 |

| BUF_STATUS_REG2         R         0x35         0011 0101           BUF_CLEAR         W         0x36         0011 0110           Reserved         -         0x37 - 0x39         -           SELF_TEST         R/W         0x3A         0011 1010           Reserved         -         0x38 - 0x59         -           WUF_THRESH*         R/W         0x5A         0101 1010           Reserved         -         0x5B         0101 1010           Reserved         -         0x5D         -           HYST_SET*         R/W         0x5D - 0x5E         -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | BUF_CTRL2*         | R/W | 0x33        | 0011 0011 |

| BUF_CLEAR         W         0x36         0011 0110           Reserved         -         0x37 - 0x39         -           SELF_TEST         R/W         0x3A         0011 1010           Reserved         -         0x3B - 0x59         -           WUF_THRESH*         R/W         0x5A         0101 1010           Reserved         -         0x5B         0101 1011           TILT_ANGLE*         R/W         0x5C         0101 1100           Reserved         -         0x5D - 0x5E         -           HYST_SET*         R/W         0x5F         0101 1111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | BUF_STATUS_REG1    | R   | 0x34        | 0011 0100 |

| Reserved         -         0x37 - 0x39         -           SELF_TEST         R/W         0x3A         0011 1010           Reserved         -         0x3B - 0x59         -           WUF_THRESH*         R/W         0x5A         0101 1010           Reserved         -         0x5B         0101 1010           Reserved         -         0x5B         0101 1011           TILT_ANGLE*         R/W         0x5C         0101 1100           Reserved         -         0x5D - 0x5E         -           HYST_SET*         R/W         0x5F         0101 1111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | BUF_STATUS_REG2    | R   | 0x35        | 0011 0101 |

| SELF_TEST         R/W         0x3A         0011 1010           Reserved         -         0x3B - 0x59         -           WUF_THRESH*         R/W         0x5A         0101 1010           Reserved         -         0x5B         0101 1011           TILT_ANGLE*         R/W         0x5C         0101 1100           Reserved         -         0x5D - 0x5E         -           HYST_SET*         R/W         0x5F         0101 1111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | BUF_CLEAR          | W   | 0x36        | 0011 0110 |

| Reserved         -         0x3B - 0x59         -           WUF_THRESH*         R/W         0x5A         0101 1010           Reserved         -         0x5B         0101 1011           TILT_ANGLE*         R/W         0x5C         0101 1100           Reserved         -         0x5D - 0x5E         -           HYST_SET*         R/W         0x5F         0101 1111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Reserved           | -   | 0x37 – 0x39 | -         |

| WUF_THRESH*         R/W         0x5A         0101 1010           Reserved         -         0x5B         0101 1011           TILT_ANGLE*         R/W         0x5C         0101 1100           Reserved         -         0x5D – 0x5E         -           HYST_SET*         R/W         0x5F         0101 1111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | SELF_TEST          | R/W | 0x3A        | 0011 1010 |

| Reserved         -         0x5B         0101         1011           TILT_ANGLE*         R/W         0x5C         0101         1100           Reserved         -         0x5D – 0x5E         -           HYST_SET*         R/W         0x5F         0101         1111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Reserved           | -   | 0x3B – 0x59 | -         |

| TILT_ANGLE*         R/W         0x5C         0101 1100           Reserved         -         0x5D - 0x5E         -           HYST_SET*         R/W         0x5F         0101 1111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | WUF_THRESH*        | R/W | 0x5A        | 0101 1010 |

| Reserved         -         0x5D – 0x5E         -           HYST_SET*         R/W         0x5F         0101 1111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Reserved           | -   | 0x5B        | 0101 1011 |

| HYST_SET* R/W 0x5F 0101 1111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | TILT_ANGLE*        | R/W | 0x5C        | 0101 1100 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Reserved           | -   | 0x5D – 0x5E | -         |

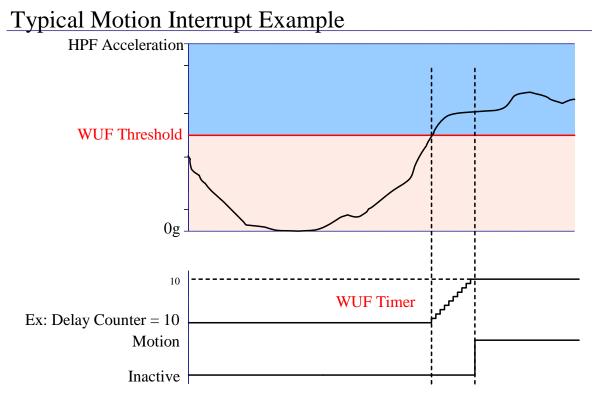

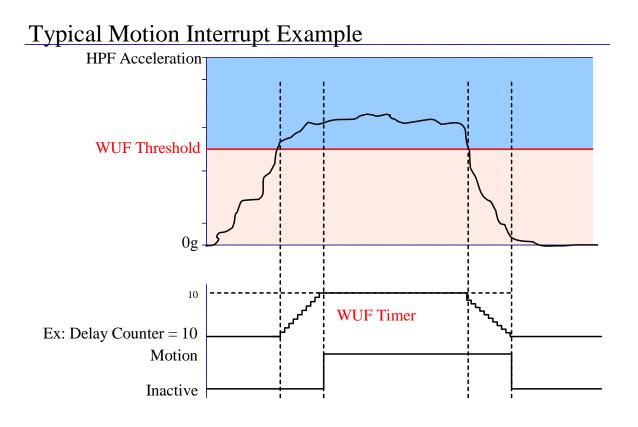

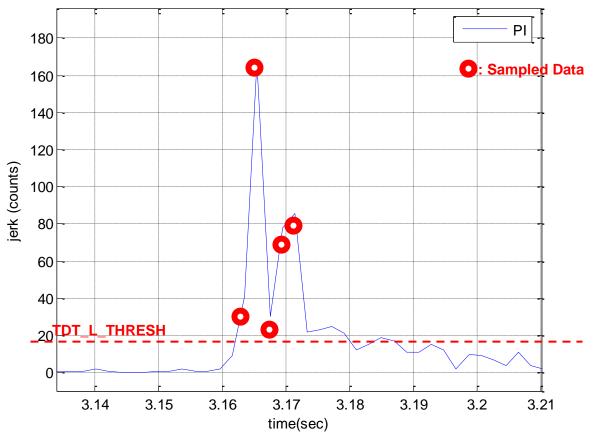

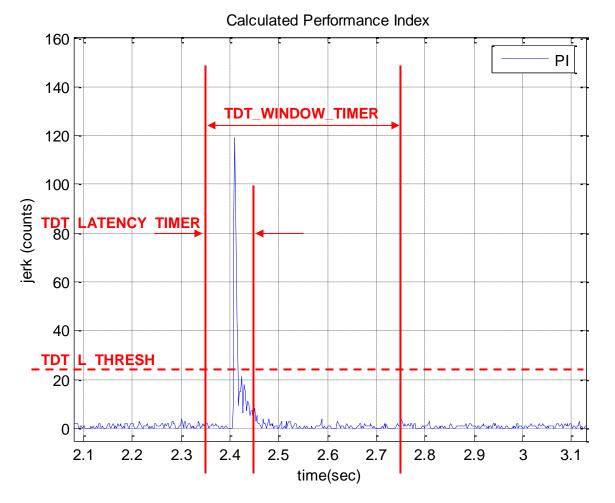

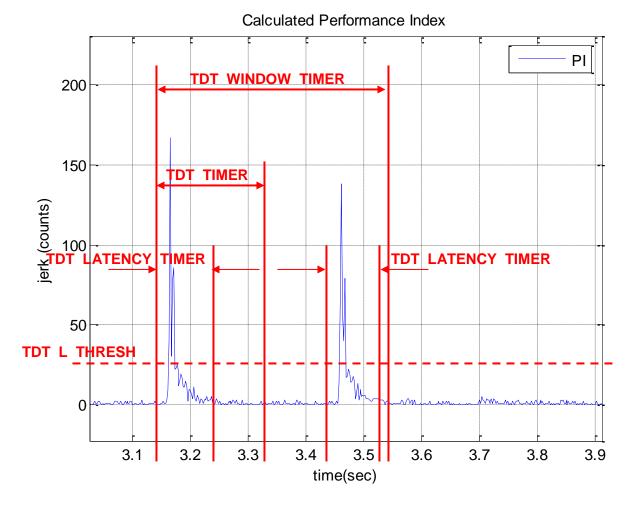

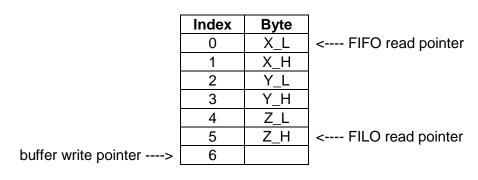

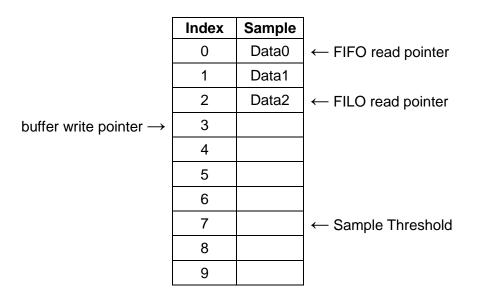

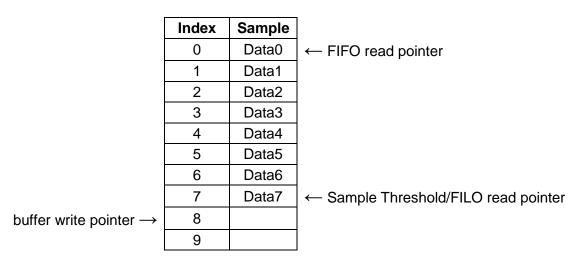

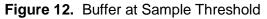

| BUF READ R 0x7F 0111 1111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | HYST_SET*          | R/W | 0x5F        | 0101 1111 |