LTC4304

### Hot Swappable 2-Wire Bus Buffer with Stuck Bus Recovery

### FEATURES

- Automatic Disconnect of SDA/SCL Lines when Bus is Stuck Low for ≥30ms

- Fault Flag for Stuck Bus

- Recovers Stuck Busses with Automatic Clocking\*

- Bidirectional Buffer\* for SDA and SCL Lines Increases Fanout

- Prevents SDA and SCL Corruption During Live Board Insertion and Removal from Backplane

- Allows Bus Pullup Voltages Above and Below V<sub>CC</sub>

- ±15kV Human Body Model ESD Protection

- Isolates Input SDA and SCL Lines from Output

- Compatible with I<sup>2</sup>C<sup>TM</sup>, I<sup>2</sup>C Fast-Mode and SMBus Standards (Up to 400kHz Operation)

- READY Open Drain Output

- IV Precharge on All SDA and SCL Lines

- High Impedance SDA, SCL Pins for V<sub>CC</sub> = 0V

- ENABLE Gates Connection from Input to Output

- MSOP 10-Pin and DFN (3mm × 3mm) Packages

### **APPLICATIONS**

- Hot Board Insertion

- Servers

- Capacitance Buffer/Bus Extender

- RAID Systems

# DESCRIPTION

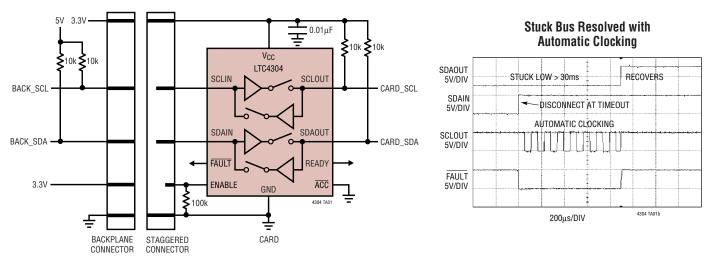

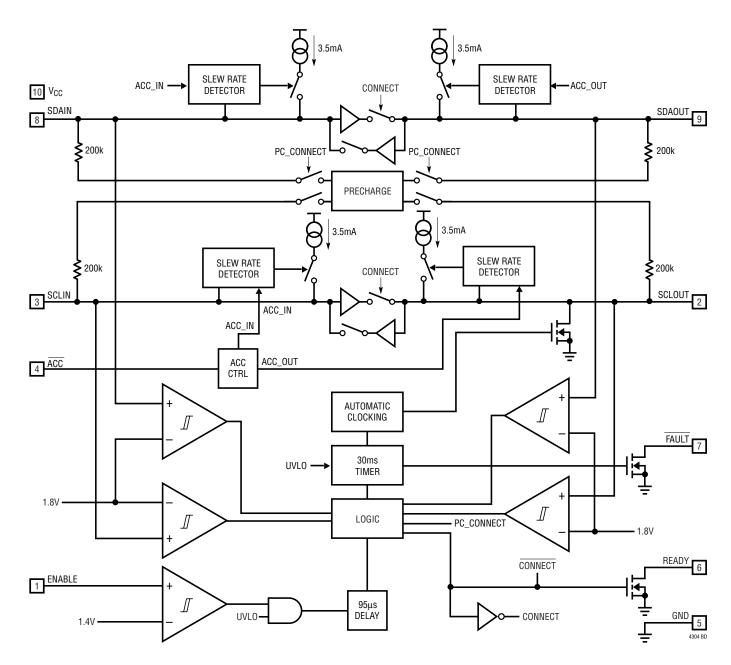

The LTC®4304 hot swappable 2-wire bus buffer allows I/O card insertion into a live backplane without corruption of the data and clock busses. When a connection is made, the LTC4304 provides bidirectional buffering, keeping the backplane and card capacitances isolated. If SDAOUT or SCLOUT is low for  $\geq$ 30ms (typ), the LTC4304 automatically breaks the data and clock bus connection and FAULT will pull low. At this time the LTC4304 automatically generates up to 16 clock pulses on SCLOUT in an attempt to free the bus. A connection will be enabled automatically when the bus becomes free. A logic low on the ACC input enables the LTC4304's rise-time accelerators. A logic high on ACC disables the rise-time accelerators, which allows SDA and SCL bus pull-up voltages below V<sub>CC</sub>.

During insertion, the SDA and SCL lines are precharged to 1V to minimize bus disturbances. When driven high, ENABLE allows the LTC4304 to connect after a stop bit or bus idle occurs. Driving ENABLE low breaks the connection between SDAIN and SDAOUT, SCLIN and SCLOUT. READY is an open drain output that indicates when the backplane and card sides are connected together.

IT, LT, LTC and LTM are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners. Protected by U.S. Patents including 6356140, 6650174, 7032051.

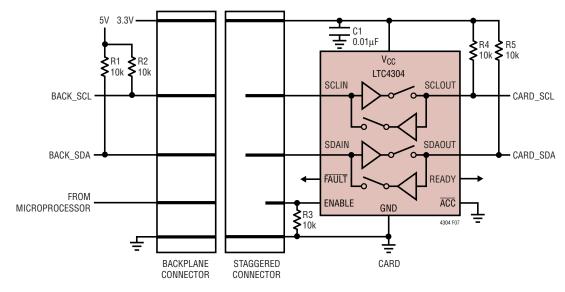

### TYPICAL APPLICATION

### ABSOLUTE MAXIMUM RATINGS (Notes 1, 2)

| V <sub>CC</sub> to GND–0.3V to 7V<br>SDAIN, SCLIN, SDAOUT, SCLOUT, READY, ENABLE, |  |

|-----------------------------------------------------------------------------------|--|

| FAULT, ACC0.3V to 7V                                                              |  |

| Operating Temperature                                                             |  |

| LTC4304C0°C to 70°C<br>LTC4304I40°C to 85°C                                       |  |

|                                                                                   |  |

| SDAIN, SCLIN, SDAOUT, SCLOUT,       |

|-------------------------------------|

| FAULT READY (Note 3)                |

| Storage Temperature Range           |

| MSOP65°C to 150°C                   |

| DFN65°C to 125°C                    |

| Lead Temperature (Soldering, 10sec) |

| MSOP 300°C                          |

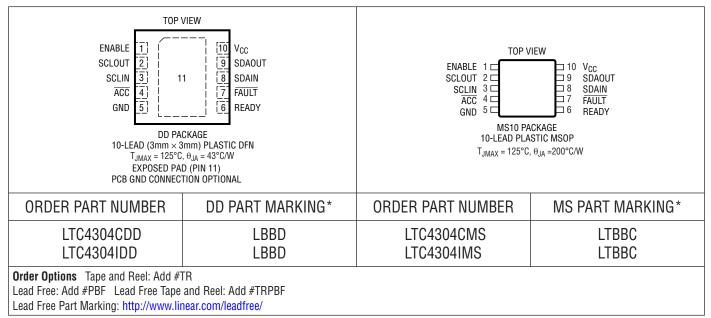

# PACKAGE/ORDER INFORMATION

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container.

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. V<sub>CC</sub> = 2.7V to 5.5V, unless otherwise noted.

| SYMBOL                  | PARAMETER                                      | CONDITIONS                                                                     |   | MIN | ТҮР      | MAX        | UNITS    |

|-------------------------|------------------------------------------------|--------------------------------------------------------------------------------|---|-----|----------|------------|----------|

| Power Supply            |                                                |                                                                                |   |     |          |            |          |

| V <sub>CC</sub>         | Positive Supply Voltage                        |                                                                                |   | 2.7 |          | 5.5        | V        |

| I <sub>CC</sub>         | Supply Current<br>Supply Current, ENABLE = GND | $V_{CC} = 5.5V, V_{SDAIN} = V_{SDAOUT} = 0V$ (Note 7)<br>$V_{CC} = 5.5V$       | • |     | 6<br>1.5 | 8          | mA<br>mA |

| Startup Circuitry       | 1                                              |                                                                                |   |     |          |            |          |

| V <sub>PRE</sub>        | Precharge Voltage                              | SDA, SCL Floating, V <sub>CC</sub> = 5.5V                                      | • | 0.8 | 1        | 1.2        | V        |

| T <sub>IDLE</sub>       | Bus Idle Time                                  |                                                                                | • | 60  | 95       | 175        | μs       |

| V <sub>OL_READY</sub>   | READY Output Low Voltage                       | I <sub>PULLUP</sub> = 3mA<br>I <sub>PULLUP</sub> = 6mA, V <sub>CC</sub> = 4.7V | • |     |          | 0.4<br>0.4 | V<br>V   |

| V <sub>THR ENABLE</sub> | ENABLE Threshold                               |                                                                                | • | 0.8 | 1.4      | 2          | V        |

| I <sub>ENABLE</sub>     | ENABLE Input Current                           | ENABLE from 0 to V <sub>CC</sub>                                               |   |     | 0.1      | ±1.5       | μA       |

| V <sub>THR</sub>        | SDA, SCL Logic Input Threshold Voltage         | Rising Edge                                                                    | • | 1.6 | 1.8      | 2          | V        |

|                         |                                                | •                                                                              |   |     |          |            | 4304fa   |

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. V<sub>CC</sub> = 2.7V to 5.5V, unless otherwise noted.

| SYMBOL                | PARAMETER                                                 | CONDITIONS                                                                                                     |   | MIN                | ТҮР       | MAX                | UNITS    |

|-----------------------|-----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|---|--------------------|-----------|--------------------|----------|

| V <sub>HYS</sub>      | SDA, SCL, Logic Input Threshold Voltage<br>Hysteresis     | (Note 6)                                                                                                       |   |                    | 50        |                    | mV       |

| t <sub>PLH</sub>      | ENABLE Delay On-Off<br>READY Delay Off-On                 | V <sub>CC</sub> = 3.3V<br>(Note 6)                                                                             |   |                    | 300<br>10 |                    | ns<br>ns |

| t <sub>PHL</sub>      | ENABLE Delay Off-On<br>READY Delay On-Off                 | V <sub>CC</sub> = 3.3V<br>(Note 6)                                                                             | • | 60                 | 95<br>10  | 175                | µs<br>ns |

| IOFF READY            | Ready Off Leakage Current                                 |                                                                                                                | ٠ |                    |           | ±10                | μA       |

| Rise-Time Acc         | elerators                                                 | · · · · · ·                                                                                                    |   |                    |           |                    |          |

| PULLUPAC              | Transient Boosted Pull-Up Current                         | Positive Transition on SDA, SCL, $V_{CC} = 2.7V$ ,<br>Slew Rate = 0.8V/ $\mu$ s (Note 5)                       |   | 2                  | 3.5       | 5.5                | mA       |

| t <sub>PDOFF</sub>    | ACC Delay, On/Off                                         | (Note 6)                                                                                                       |   |                    | 5         |                    | ns       |

| V <sub>IH</sub>       | Input High Voltage                                        | Measured on ACC                                                                                                | ٠ | 0.9V <sub>CC</sub> |           |                    | V        |

| V <sub>IL</sub>       | Input Low Voltage                                         | Measured on ACC                                                                                                | ٠ |                    |           | 0.1V <sub>CC</sub> | V        |

| I <sub>IN</sub>       | ACC Input Current                                         | ACC Shorted to GND or V <sub>CC</sub> (Note 8)                                                                 | ٠ | -100               |           | 100                | μA       |

| Bus Stuck Low         | Timeout                                                   |                                                                                                                |   |                    |           |                    |          |

| t <sub>TIMEOUT</sub>  | Bus Stuck Low Timer                                       | SDAOUT, SCLOUT = 0V                                                                                            | ٠ | 25                 | 30        | 35                 | ms       |

| VOLFAULT              | FAULT Output Low Voltage                                  | I <sub>PULLUP</sub> = 3mA                                                                                      | ٠ |                    |           | 0.4                | V        |

| IOFF_FAULT            |                                                           | V <sub>CC</sub> = 5.5V                                                                                         | • |                    |           | ±10                | μA       |

| Input-Output C        | onnection                                                 |                                                                                                                |   |                    |           |                    |          |

| V <sub>0S</sub>       | Input-Output Offset Voltage                               | 10k to $V_{CC}$ on SDA, SCL,<br>2.7k to $V_{CC}$ on SDA, SCL<br>$V_{CC}$ = 3.3V, $V_{SDA/SCL}$ = 0.2V (Note 4) | • | 40<br>50           | 80<br>100 | 120<br>150         | mV<br>mV |

| C <sub>IN</sub>       | Digital Input Capacitance<br>SDAIN, SDAOUT, SCLIN, SCLOUT | (Note 6)                                                                                                       |   |                    |           | 10                 | pF       |

| V <sub>IL, MAX</sub>  | Input Logic Low Voltage                                   |                                                                                                                | ٠ |                    |           | 0.4                | V        |

| I <sub>LEAK</sub>     | Input Leakage Current                                     | SDA, SCL, $V_{CC} = 5.5V$                                                                                      | ٠ |                    |           | ±5                 | μA       |

| V <sub>OL</sub>       | Output Low Voltage, Input = 0V                            | SDA, SCL Pins, $I_{SINK}$ = 4mA, $V_{CC}$ = 2.7V                                                               | ٠ | 0                  | 0.19      | 0.3                | V        |

| Timing Charac         | teristics                                                 |                                                                                                                |   |                    |           |                    |          |

| f <sub>I2C, MAX</sub> | I <sup>2</sup> C Maximum Operating Frequency              | (Note 6)                                                                                                       |   | 400                | 600       |                    | kHz      |

| t <sub>BUF</sub>      | Bus Free Time Between Stop and Start Condition            | (Note 6)                                                                                                       |   |                    |           | 1.3                | μs       |

| t <sub>hd, sta</sub>  | Hold Time After (Repeated)<br>Start Condition             | (Note 6)                                                                                                       |   |                    |           | 100                | ns       |

| t <sub>su, sta</sub>  | Repeated Start Condition Set-Up Time                      | (Note 6)                                                                                                       |   |                    |           | 0                  | ns       |

| t <sub>SU, STO</sub>  | Stop Condition Set-Up Time                                | (Note 6)                                                                                                       |   |                    |           | 0                  | ns       |

| t <sub>HD, DATI</sub> | Data Hold Time Input                                      | (Note 6)                                                                                                       |   |                    |           | 0                  | ns       |

| t <sub>SU, DAT</sub>  | Data Set-Up Time                                          | (Note 6)                                                                                                       |   |                    |           | 100                | ns       |

Note 1: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

Note 2: All currents into pins are positive; all voltages are referenced to GND unless otherwise specified.

Note 3: Pulsed less than 5µs.

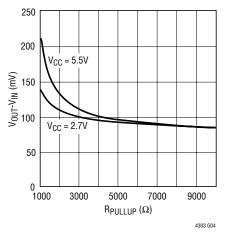

Note 4: The connection circuitry always regulates the output to a higher

voltage than its input. The magnitude of this offset voltage as a function of the pull-up resistor and  $V_{CC}$  voltage is shown in the Typical Performance Characteristics section.

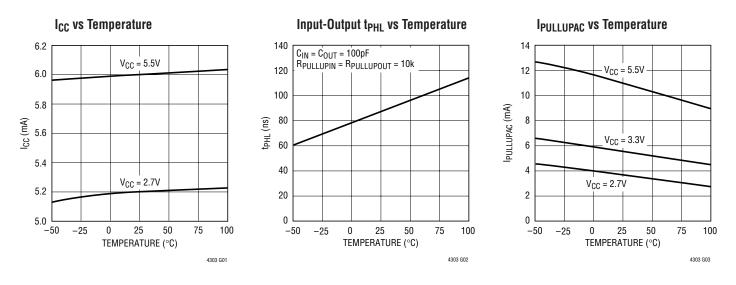

Note 5:  $I_{PULLUPAC}$  varies with temperature and  $V_{CC}$  voltage, as shown in the Typical Performance Characteristics section.

Note 6: Determined by design, not tested in production.

**Note 7:** I<sub>CC</sub> test performed with connection circuitry active.

**Note 8:** When floating, the  $\overline{ACC}$  pin can tolerate  $\pm 5\mu A$  of leakage.

### **TYPICAL PERFORMANCE CHARACTERISTICS** $T_A = 25$ °C unless otherwise indicated.

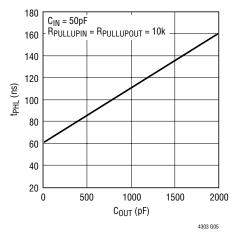

Input-Output t<sub>PHL</sub> vs C<sub>OUT</sub>

### PIN FUNCTIONS

**ENABLE (Pin 1):** Connection Enable. This is a digital threshold input pin. For normal operation ENABLE is high. Driving ENABLE below 0.8V isolates SDAIN from SDAOUT, SCLIN from SCLOUT, asserts READY low and disables automatic clocking. A rising edge on ENABLE after a fault has occurred unconditionally forces a connection between SDAIN, SDAOUT and SCLIN, SCLOUT.

**SCLOUT (Pin 2):** Serial Clock Output. Connect this pin to the SCL bus on the card.

**SCLIN (Pin 3):** Serial Clock Input. Connect this pin to SCL on the bus backplane.

**ACC** (Pin 4): Rise-Time Accelerator Control. Connect  $\overline{ACC}$  to  $V_{CC}$  to disable all four accelerators. Connect  $\overline{ACC}$  to GND to enable all four accelerators. Float  $\overline{ACC}$  to enable the SDAOUT and SCLOUT accelerators only. For applications when  $V_{CC}$  is greater than the bus pull-up voltage, connect  $\overline{ACC}$  to  $V_{CC}$ .

**GND (Pin 5):** Device Ground. Connect this pin to a ground plane for best results.

**READY (Pin 6):** Connection Status Flag. READY provides a digital flag which indicates the status of the connection circuitry described in the "Connection Circuitry" section. Connect a resistor of 10k to  $V_{CC}$  to provide the pull-up.

**FAULT (Pin 7):** Bus Stuck Low Fault. FAULT is an open drain N-channel MOSFET which pulls low to signal a bus stuck low condition. In normal operation, FAULT is high. Connect a 10k resistor from this pin to  $V_{CC}$  to provide the pull-up.

**SDAIN (Pin 8):** Serial Data Input. Connect this pin to the SDA bus on the backplane.

**SDAOUT (Pin 9):** Serial Data Output. Connect this pin to the SDA bus on the card.

$V_{CC}$  (Pin 10): Supply Voltage Input. Place a bypass capacitor of at least 0.01  $\mu F$  close to  $V_{CC}$  for best results.

**Exposed Pad (Pin 11, DFN Only):** Exposed pad may be left open or connected to the ground plane.

### **BLOCK DIAGRAM**

LTC4304 2-Wire Bus Buffer with Stuck Bus Protection

4304fa

6

### OPERATION

### Start-Up

When the LTC4304 first receives power on its V<sub>CC</sub> pin, either during power up or live insertion, it starts in an under voltage lockout (UVLO) state, ignoring any activity on the SDA or SCL pins until V<sub>CC</sub> rises above 2.5V (typical).

During this time, the precharge circuitry is active and forces 1V through 200K nominal resistors to the SDA and SCL pins. Because the I/O card is being plugged into a live backplane, the voltage on the backplane SDA and SCL busses may be anywhere between 0V and V<sub>CC</sub>. Precharging the SCL and SDA pins to 1V minimizes the worst-case voltage differential these pins will see at the moment of connection, therefore minimizing the amount of disturbance caused by the I/O card.

Once the LTC4304 comes out of UVLO, it assumes that SDAIN and SCLIN have been inserted into a live system and that SDAOUT and SCLOUT are being powered up at the same time as itself. Therefore, it looks for either a stop bit or bus idle condition on the input side to indicate the completion of a data transaction. When either one occurs, the part also verifies that both the SDAOUT and SCLOUT voltages are high. When all of these conditions are met, the input-to-output connection circuitry is activated, joining the SDA and SCL busses on the I/O card with those on the backplane and READY goes high.

### **Connection Circuitry**

Once the connection circuitry is activated, the functionality of the SDAIN and SDAOUT pins is identical. A low forced on either pin at any time results in both pin voltages being low. For proper operation, logic low input voltages should be no higher than 0.4V with respect to the ground pin voltage of the LTC4304. SDAIN and SDAOUT enter a logic high state only when all devices on both SDAIN and SDAOUT release high. The same is true for SCLIN and SCLOUT. This important feature ensures that clock stretching, clock synchronization, arbitration and the acknowledge protocol always work, regardless of how the devices in the system are tied to the LTC4304.

Another key feature of the connection circuitry is that it provides bidirectional buffering, keeping the backplane and card capacitances isolated. Because of this isolation, the waveforms on the backplane busses look slightly different than the corresponding card bus waveforms, as described here.

### Input to Output Offset Voltage

When a logic low voltage,  $V_{LOW1}$ , is driven on any of the LTC4304's data or clock pins, the LTC4304 regulates the voltage on the opposite side of the part (call it  $V_{LOW2}$ ) to a slightly higher voltage, as directed by the following equation:

$V_{LOW2} = V_{LOW1} + 75mV + (V_{CC}/R) \cdot 20\Omega$  (typical)

where R is the bus pull-up resistance in ohms. For example, if a device is forcing SDAOUT to 10mV where  $V_{CC}$  = 3.3V and the pull-up resistor R on SDAIN is 10k, then the voltage on SDAIN = 10mV + 75mV + (3.3/10000) • 20 = 91.6mV(typical). See the Typical Performance Characteristics section for curves showing the offset voltage as a function of V<sub>CC</sub> and R.

#### **Bus Stuck Low Timeout**

When SDAOUT or SCLOUT is low, an internal timer starts. The timer is only reset when SDAOUT and SCLOUT are <u>both high</u>. If they do not go high within 30ms (typical), FAULT pulls low indicating a bus stuck condition and the connection between SDAIN and SDAOUT, and SCLIN and SCLOUT is broken. After a delay of at least 40µs, the LTC4304 automatically generates up to 16 clock pulses at 8.5kHz (typical) on SCLOUT in an attempt to unstick the bus. When SDAOUT and SCLOUT go high, FAULT is cleared and reconnection occurs when the conditions described in the "Start-Up" section above are satisfied.

When powering up into a bus stuck low condition, the connection circuitry joining the SDA and SCL busses on the I/O card with those on the backplane is not activated. 30ms after UVLO, FAULT pulls low indicating a bus stuck low condition, and automatic clocking takes place as described above.

#### **Propagation Delays**

During a rising edge, the rise-time on each side is determined by the bus pull-up resistor and the equivalent capacitance on the line. If the pull-up resistors are the

# LTC4304

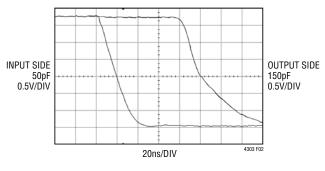

### OPERATION OUTPUT SIDE 50FP 0.5V/DIV UDU 200ns/DIV 4303 F01

Figure 1. Input-Output Connection t<sub>PLH</sub>

Figure 2. Input-Output Connection t<sub>PHL</sub>

same, a difference in rise-time occurs which is directly proportional to the difference in capacitance between the two sides. This effect is displayed in Figure 1 for a  $V_{CC}$  = 3.3V and a 10k pull-up resistor on each side (50pF on one side and 150pF on the other). Since the output side has less capacitance than the input, it rises faster and the effective t<sub>PLH</sub> is negative.

There is a propagation delay,  $t_{PHL}$ , through the connection circuitry for falling waveforms. Figure 2 shows the falling edge waveforms. An external driver pulls down the voltage on the side with 50pF capacitance; LTC4304 pulls down the voltage on the opposite side with a delay of 80ns. This delay is always positive and is a function of supply voltage, temperature and the pull-up resistors and equivalent bus capacitances on both sides of the bus. The Typical Performance Characteristics section shows  $t_{PHL}$  as a function of temperature and voltage for 10k pull-up resistors and 100pF equivalent capacitance on both sides of the part. Larger output capacitances translate to longer delays. Users must quantify the difference in propagation times for a rising edge versus a falling edge in their systems and adjust setup and hold times accordingly.

### **READY Digital Output**

The READY pin provides a digital flag which indicates the status of the connection circuitry described previously in the "Connection Circuitry" section. READY is high when the connection circuitry is active, and pulls low when there is not a valid connection. The pin is driven by an open drain pull-down capable of sinking 3mA while holding 0.4V on the pin. Connect a resistor of 10k to  $V_{CC}$  to provide the pull-up.

### FAULT Digital Output

The FAULT pin provides a digital flag which is low when SDAOUT and SCLOUT have not both been high within 30ms (typical). The pin is driven by an open drain pull-down capable of sinking 3mA while holding 0.4V on the pin. Connect a resistor of 10k to  $V_{CC}$  to provide the pull-up.

### ENABLE

When the ENABLE pin is driven below 0.8V with respect to the LTC4304's ground, the backplane side is disconnected from the card side, and the READY pin is internally pulled low. When the pin is driven above 2V, the part waits for data transactions on both the backplane and card sides to be complete (as described in the Start-Up section) before connecting the two sides. At this time the internal pulldown on READY releases. When ENABLE is low, automatic clocking is disabled.

### OPERATION

A rising edge on ENABLE after a stuck bus condition has occurred forces a connection between SDAIN, SDAOUT and SCLIN, SCLOUT even if bus idle conditions are not met. At this time the internal 30ms timer is reset but not disabled.

### **Rise Time Accelerators**

Once connection has been established, rise time accelerator circuits on all four SDA and SCL pins are activated (assuming accelerators are enabled, see ACC pin description). These allow the use of a large pull-up resistor to

reduce power consumption, or bus capacitance beyond that specified in  $I^2C$ , while still meeting system rise time requirements. During positive bus transitions, the LTC4304 switches in 3.5mA (typical) of current to quickly slew the SDA and SCL lines once their DC voltages exceed 0.8V. Choose a pull-up resistor so that the bus will rise on its own at a rate of at least 0.8V/µs to guarantee activation of the accelerators. Rise time accelerators turn off when SDA and SCL lines are approximately 1V below V<sub>CC</sub>. Rise time accelerators are automatically disabled during automatic clocking.

### **APPLICATIONS INFORMATION**

### **Resistor Pull-Up Selection**

The system pull-up resistors must be strong enough to provide a positive slew rate of  $0.8V/\mu s$  on the SDA and SCL pins, in order to activate the rise time accelerators during rising edges. Choose maximum resistor value  $R_{PULL-UP(MAX)}$  using the formula:

$R_{PULLUP(MAX)}[k\Omega] = \frac{\left(V_{BUS(MIN)} - 0.8V\right) \bullet 1250[ns/V]}{C_{BUS}[pF]}$

where  $V_{BUSMIN}$  is the minimum operating  $\ pull-up$  supply voltage, and  $C_{BUS}$  the total capacitance on respective bus line.

For example, assume  $V_{BUS} = V_{CC} = 3.3V$ , and assuming ±10% supply tolerance,  $V_{BUSMIN} = 2.97V$ . With  $C_{BUS} = 100pF$ ,  $R_{PULL-UP, MAX} = 27.1k$ . Therefore a smaller pull-up resistor than 27.1k must be used, so 10k works fine.

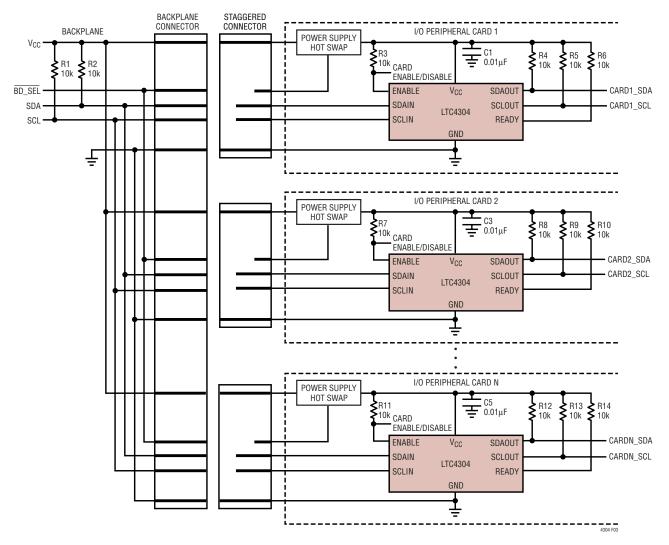

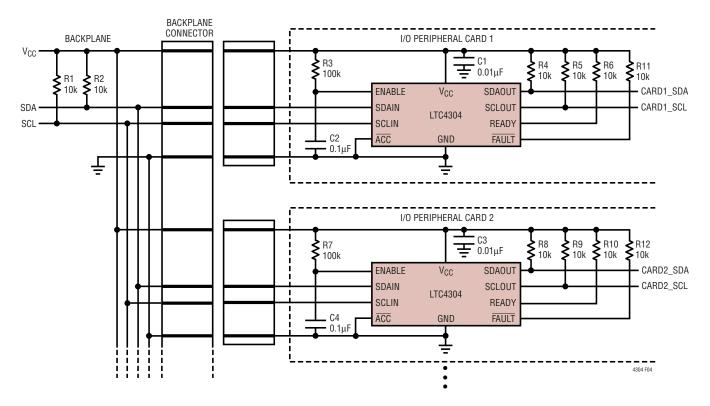

### Live Insertion and Capacitance Buffering Application

Figures 3 through 6 illustrate applications of the LTC4304 that take advantage of both its Hot Swap<sup>™</sup> controlling and capacitance buffering features. In all of these applications, note that if the I/O cards were plugged directly into the backplane without the LTC4304 buffer, all of the backplane and card capacitances would add directly together, making rise- and fall-time requirements difficult to meet. Placing a LTC4304 on the edge of each card, however, isolates the card capacitance from the backplane. For a given I/O card,

the LTC4304 drives the capacitance on the card side and the backplane must drive only the digital input capacitance of the LTC4304, which is less than 10pF.

In most applications the LTC4304 will be used with a staggered connector where  $V_{CC}$  and GND will be long pins. SDA and SCL are medium length pins to ensure that the  $V_{CC}$  and GND pins make contact first. This will allow the precharge circuitry to be activated on SDA and SCL before they make contact. ENABLE is a short pin that is pulled down when not connected. This is to ensure that the connection between the backplane and the cards data and clock busses is not enabled until the transients associated with live insertion have settled.

Figure 3 shows the LTC4304 in a CompactPCI<sup>TM</sup> configuration. Connect V<sub>CC</sub> and ENABLE to the output of one of the CompactPCI power supply Hot Swap circuits. Use a pull-up resistor to ENABLE for a card side enable/disable. V<sub>CC</sub> is monitored by a filtered UVLO circuit. With the V<sub>CC</sub> voltage powering up after all the other pins have established connection, the UVLO circuit ensures that the backplane and the card data and clock busses are not connected until the transients associated with live insertion have settled. Owing to their small capacitance, the SDAIN and SCLIN pins cause minimal disturbance on the backplane busses when they make contact with the connector.

Hot Swap is a trademark of Linear Technology Corporation.

Figure 3. Inserting Multiple I/O Cards into a Live Backplane Using the LTC4304 in a CompactPCI System

Figure 4 shows the LTC4304 in a PCI application where all of the pins have the same length. In this case, a RC filter circuit on the I/O card with a product of 10ms provides a

filter to prevent the LTC4304 from becoming activated until the transients associated with live insertion have settled. Connect the capacitor between ENABLE and GND, and the resistor from  $V_{CC}$  to ENABLE.

Figure 4. Inserting Multiple I/O Cards into a Live Backplane Using the LTC4304 in a PCI System

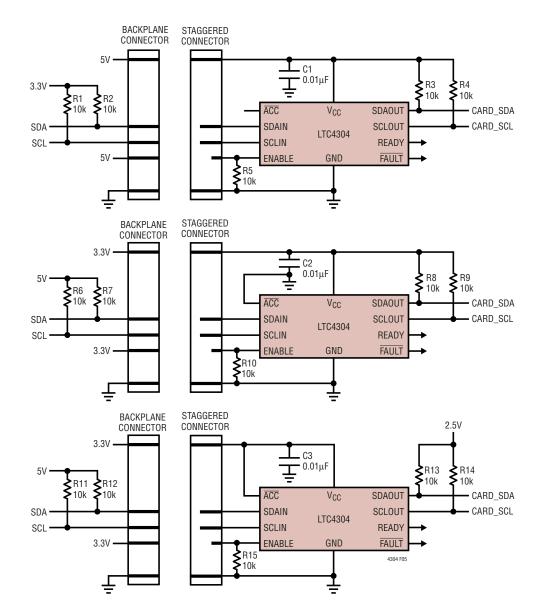

### Supply Independent Operation

Figure 5 illustrates applications of the LTC4304 with different bus pull up and  $V_{CC}$  voltages, demonstrating its ability to recognize and buffer bus data levels that are above or below its  $V_{CC}$  supply voltage. In applications where  $V_{CC}$  voltage is greater than bus pull-up voltages, rise-time ac-

celerators cannot be used. Float  $\overrightarrow{ACC}$  in applications where the pull-up voltage on SDAIN and SCLIN is  $< V_{CC}$  and the pull-up voltage on SDAOUT and SCLOUT is  $\geq V_{CC}$ . Connect  $\overrightarrow{ACC}$  to ground in applications where  $V_{CC}$  is  $\leq$  SDA and SCL pull-up voltages. Connect  $\overrightarrow{ACC}$  to  $V_{CC}$  for applications where SDA and SCL pull-up voltages are  $\leq V_{CC}$ .

Figure 5. Typical Supply Independent Applications

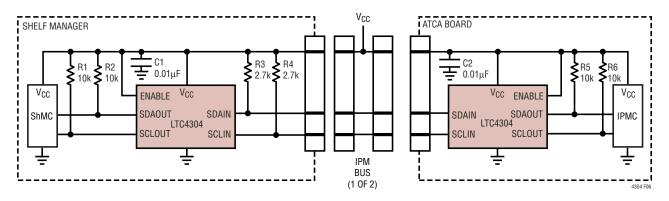

Figure 6. Simplified ATCA IPMB Application

### PACKAGE DESCRIPTION

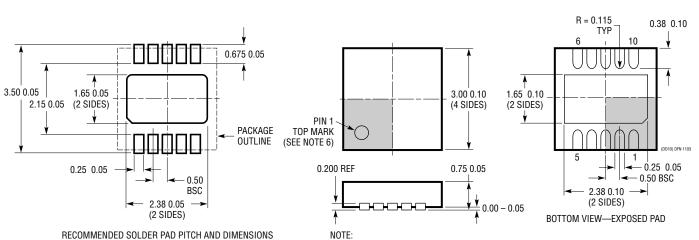

**DD** Package 10-Lead Plastic DFN (3mm × 3mm) (Reference LTC DWG # 05-08-1699)

NOTE:

1. DRAWING TO BE MADE A JEDEC PACKAGE OUTLINE M0-229 VARIATION OF (WEED-2).

CHECK THE LTC WEBSITE DATA SHEET FOR CURRENT STATUS OF VARIATION ASSIGNMENT

2. DRAWING NOT TO SCALE

3. ALL DIMENSIONS ARE IN MILLIMETERS

4. DIMENSIONS OF EXPOSED PAD ON BOTTOM OF PACKAGE DO NOT INCLUDE MOLD FLASH. MOLD FLASH, IF PRESENT, SHALL NOT EXCEED 0.15mm ON ANY SIDE

5. EXPOSED PAD SHALL BE SOLDER PLATED

6. SHADED AREA IS ONLY A REFERENCE FOR PIN 1 LOCATION ON THE TOP AND BOTTOM OF PACKAGE

### PACKAGE DESCRIPTION

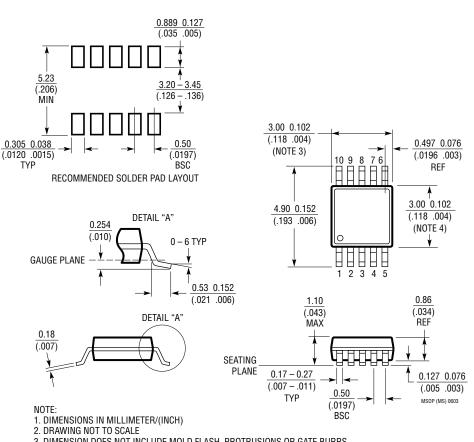

#### **MS Package 10-Lead Plastic MSOP** (Reference LTC DWG # 05-08-1661)

3. DIMENSION DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS.

- MOLD FLASH, PROTRUSIONS OR GATE BURRS SHALL NOT EXCEED 0.152mm (.006") PER SIDE

- 4. DIMENSION DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS.

- INTERLEAD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.152mm (.006") PER SIDE 5. LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.102mm (.004") MAX

### TYPICAL APPLICATION

## **RELATED PARTS**

| PART NUMBER           | DESCRIPTION                                                                      | COMMENTS                                                                                                              |

|-----------------------|----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| LTC1380/LTC1393       | Single-Ended 8-Channel/Differential 4-Channel Analog<br>Mux with SMBus Interface | Low $R_{ON}$ : 35 $\Omega$ Single-Ended/70 $\Omega$ Differential, Expandable to 32 Single or 16 Differential Channels |

| LTC1427-50            | Micropower, 10-Bit Current Output DAC<br>with SMBus Interface                    | Precision 50µA ± 2.5% Tolerance Over Temperature,<br>4 Selectable SMBus Addresses, DAC Powers up at Zero or Midscale  |

| LTC1623               | Dual High Side Switch Controller with SMBus Interface                            | 8 Selectable Addresses/16-Channel Capability                                                                          |

| LTC1663               | SMBus Interface 10-Bit Rail-to-Rail Micropower DAC                               | DNL < 0.75LSB Max, 5-Lead SOT-23 Package                                                                              |

| LTC1694/LTC1694-1     | SMBus Accelerator                                                                | Improved SMBus/I <sup>2</sup> C Rise-Time,<br>Ensures Data Integrity with Multiple SMBus/I <sup>2</sup> C Devices     |

| LT1786F               | SMBus Controlled CCFL Switching Regulator                                        | 1.25A, 200kHz, Floating or Grounded Lamp Configurations                                                               |

| LTC1695               | SMBus/I <sup>2</sup> C Fan Speed Controller in ThinSOT™                          | 0.75Ω PMOS 180mA Regulator, 6-Bit DAC                                                                                 |

| LTC1840               | Dual I <sup>2</sup> C Fan Speed Controller                                       | Two 100µA 8-Bit DACs, Two Tach Inputs, Four GPI0                                                                      |

| LTC4300A-1/LTC4300A-2 | Hot Swappable 2-Wire Bus Buffer                                                  | Isolates Backplane and Card Capacitances                                                                              |

| LTC4300A-3            | Hot Swappable 2-Wire Bus Buffer                                                  | Provides Level Shifting and Enable Functions                                                                          |

| LTC4301               | Supply Independent Hot Swappable 2-Wire Bus Buffer                               | Supply Independent                                                                                                    |

| LTC4301L              | Hot Swappable 2-Wire Bus Buffer<br>with Low Voltage Level Translation            | Allows Bus Pull-Up Voltages as Low as 1V on SDAIN and SCLIN                                                           |

| LTC4302-1/LTC4302-2   | Addressable 2-Wire Bus Buffer                                                    | Address Expansion, GPIO, Software Controlled                                                                          |

| LTC4303               | Hot Swappable 2-Wire Bus Buffer with Stuck<br>Bus Recovery                       | Provides Automatic Clocking to Free Stuck I <sup>2</sup> C Busses                                                     |

ThinSOT is a trademark of Linear Technology Corporation.

#### ООО "ЛайфЭлектроникс"

ИНН 7805602321 КПП 780501001 Р/С 40702810122510004610 ФАКБ "АБСОЛЮТ БАНК" (ЗАО) в г.Санкт-Петербурге К/С 3010181090000000703 БИК 044030703

Компания «Life Electronics» занимается поставками электронных компонентов импортного и отечественного производства от производителей и со складов крупных дистрибьюторов Европы, Америки и Азии.

С конца 2013 года компания активно расширяет линейку поставок компонентов по направлению коаксиальный кабель, кварцевые генераторы и конденсаторы (керамические, пленочные, электролитические), за счёт заключения дистрибьюторских договоров

Мы предлагаем:

- Конкурентоспособные цены и скидки постоянным клиентам.

- Специальные условия для постоянных клиентов.

- Подбор аналогов.

- Поставку компонентов в любых объемах, удовлетворяющих вашим потребностям.

- Приемлемые сроки поставки, возможна ускоренная поставка.

- Доставку товара в любую точку России и стран СНГ.

- Комплексную поставку.

- Работу по проектам и поставку образцов.

- Формирование склада под заказчика.

- Сертификаты соответствия на поставляемую продукцию (по желанию клиента).

- Тестирование поставляемой продукции.

- Поставку компонентов, требующих военную и космическую приемку.

- Входной контроль качества.

- Наличие сертификата ISO.

В составе нашей компании организован Конструкторский отдел, призванный помогать разработчикам, и инженерам.

Конструкторский отдел помогает осуществить:

- Регистрацию проекта у производителя компонентов.

- Техническую поддержку проекта.

- Защиту от снятия компонента с производства.

- Оценку стоимости проекта по компонентам.

- Изготовление тестовой платы монтаж и пусконаладочные работы.

Тел: +7 (812) 336 43 04 (многоканальный) Email: org@lifeelectronics.ru

#### www.lifeelectronics.ru