# SLRC610

# High-performance ICODE frontend SLRC610 and SLRC610 plus

Rev. 4.7 — 26 February 2020 227647 Product data sheet COMPANY PUBLIC

# 1 General description

SLRC610, the low-cost RFID frontend.

The SLRC610 multi-protocol NFC frontend IC supports the following operating modes:

- Read/write mode supporting ISO/IEC 15693

- Read/write mode supporting ICODE EPC UID/ EPC OTP

- Read/write mode supporting ISO/IEC 18000-3 mode 3/ EPC Class-1 HF

The SLRC610 supports the vicinity protocol according to ISO/IEC15693, EPC UID and ISO/IEC 18000-3 mode 3/ EPC Class-1 HF.

The following host interfaces are supported:

- Serial Peripheral Interface (SPI)

- Serial UART (similar to RS232 with voltage levels dependent on pin voltage supply)

- I<sup>2</sup>C-bus interface (two versions are implemented: I2C and I2CL)

The SLRC610 supports the connection of a secure access module (SAM). A dedicated separate I<sup>2</sup>C interface is implemented for a connection of the SAM. The SAM can be used for high secure key storage and acts as a very performant crypto coprocessor. A dedicated SAM is available for connection to the SLRC610.

### High-performance ICODE frontend SLRC610 and SLRC610 plus

### 2 Features and benefits

- RFID frontend

- Supports ISO/IEC15693, ICODE EPC UID and ISO/IEC 18000-3 mode 3/ EPC Class-1 HF

- · Low-power card detection

- Antenna connection with minimum number of external components

- · Supported host interfaces:

- SPI up to 10 Mbit/s

- I<sup>2</sup>C-bus interfaces up to 400 kBd in Fast mode, up to 1000 kBd in Fast mode plus

- RS232 Serial UART up to 1228.8 kBd, with voltage levels dependent on pin voltage supply

- Separate I<sup>2</sup>C-bus interface for connection of a secure access module (SAM)

- FIFO buffer with size of 512 byte for highest transaction performance

- Flexible and efficient power saving modes including hard power down, standby and low-power card detection

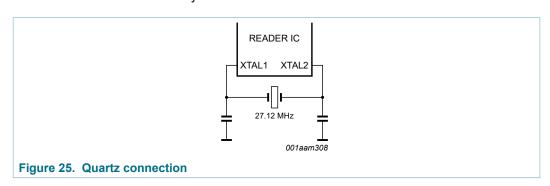

- Cost saving by integrated PLL to derive system clock from 27.12 MHz RF quartz crystal

- 3 V to 5.5 V power supply (SLRC61002)

2.5 V to 5.5 V power supply (SLRC61003)

- Up to 8 free programmable input/output pins

- The version SLRC61003 offers a more flexible configuration for Low-Power Card detection compared to the SLRC6102 with the new register LPCD\_OPTIONS. In addition, the SLRC61003 offers new additional settings for the Load Protocol which fit very well to smaller antennas. The SLRC61003 is therefore the recommended version for new designs

High-performance ICODE frontend SLRC610 and SLRC610 plus

# 3 Applications

- Industrial

- · Access control

- Gaming

### High-performance ICODE frontend SLRC610 and SLRC610 plus

### Quick reference data

Table 1. Quick reference data SLRC61002HN

| Symbol                | Parameter                     | Conditions                |     | Min | Тур | Max      | Unit |

|-----------------------|-------------------------------|---------------------------|-----|-----|-----|----------|------|

| $V_{DD}$              | supply voltage                |                           |     | 3.0 | 5.0 | 5.5      | V    |

| $V_{DD(PVDD)}$        | PVDD supply voltage           |                           | [1] | 3.0 | 5.0 | $V_{DD}$ | V    |

| V <sub>DD(TVDD)</sub> | TVDD supply voltage           |                           |     | 3.0 | 5.0 | 5.5      | V    |

| I <sub>pd</sub>       | power-down current            | PDOWN pin pulled HIGH     | [2] | -   | 8   | 40       | nA   |

| I <sub>DD</sub>       | supply current                |                           |     | -   | 17  | 20       | mA   |

| I <sub>DD(TVDD)</sub> | TVDD supply current           |                           |     | -   | 100 | 250      | mA   |

| T <sub>amb</sub>      | operating ambient temperature |                           |     | -25 | +25 | +85      | °C   |

| T <sub>stg</sub>      | storage temperature           | no supply voltage applied |     | -55 | +25 | +125     | °C   |

VDD(PVDD) must always be the same or lower voltage than VDD.  $\rm I_{pd}$  is the sum of all supply currents

Table 2. Quick reference data SLRC61003HN

| Symbol                | Parameter                     | Conditions                                                     |     | Min | Тур | Max      | Unit |

|-----------------------|-------------------------------|----------------------------------------------------------------|-----|-----|-----|----------|------|

| $V_{DD}$              | supply voltage                |                                                                |     | 2.5 | 5.0 | 5.5      | V    |

| V <sub>DD(PVDD)</sub> | PVDD supply voltage           |                                                                | [1] | 2.5 | 5.0 | $V_{DD}$ | V    |

| V <sub>DD(TVDD)</sub> | TVDD supply voltage           |                                                                |     | 2.5 | 5.0 | 5.5      | V    |

| I <sub>pd</sub>       | power-down current            | PDOWN pin pulled HIGH                                          | [2] | -   | 8   | 40       | nA   |

| I <sub>DD</sub>       | supply current                |                                                                |     | -   | 17  | 20       | mA   |

| I <sub>DD(TVDD)</sub> | TVDD supply current           |                                                                |     | -   | 180 | 350      | mA   |

|                       |                               | absolute limiting value                                        |     | -   | -   | 500      | mA   |

| T <sub>amb</sub>      | operating ambient temperature | device mounted on PCB which allows sufficient heat dissipation |     | -40 | +25 | +105     | °C   |

| T <sub>stg</sub>      | storage temperature           | no supply voltage applied                                      |     | -55 | +25 | +125     | °C   |

VDD(PVDD) must always be the same or lower voltage than VDD.

<sup>[2]</sup>

I<sub>pd</sub> is the sum of all supply currents

### High-performance ICODE frontend SLRC610 and SLRC610 plus

# **Ordering information**

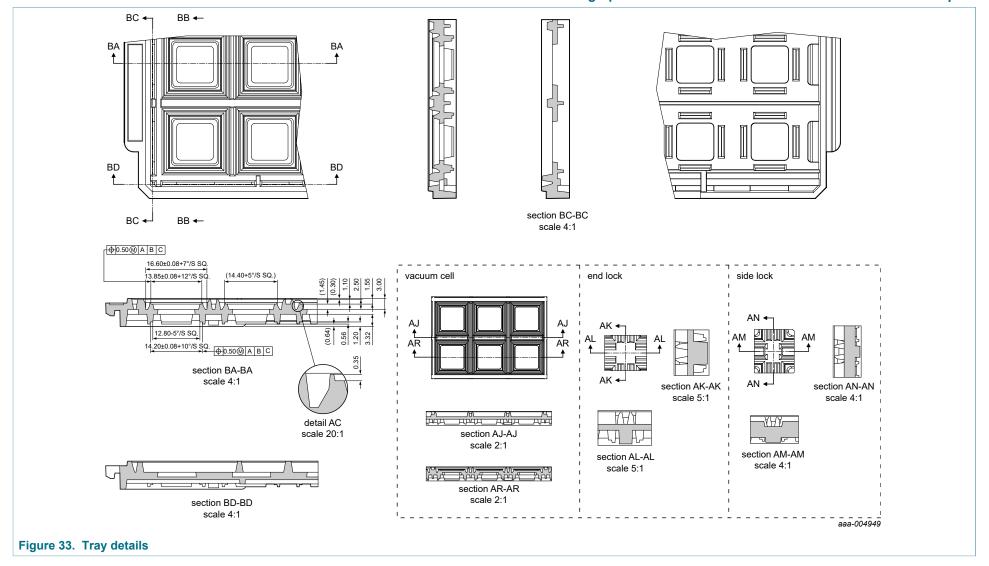

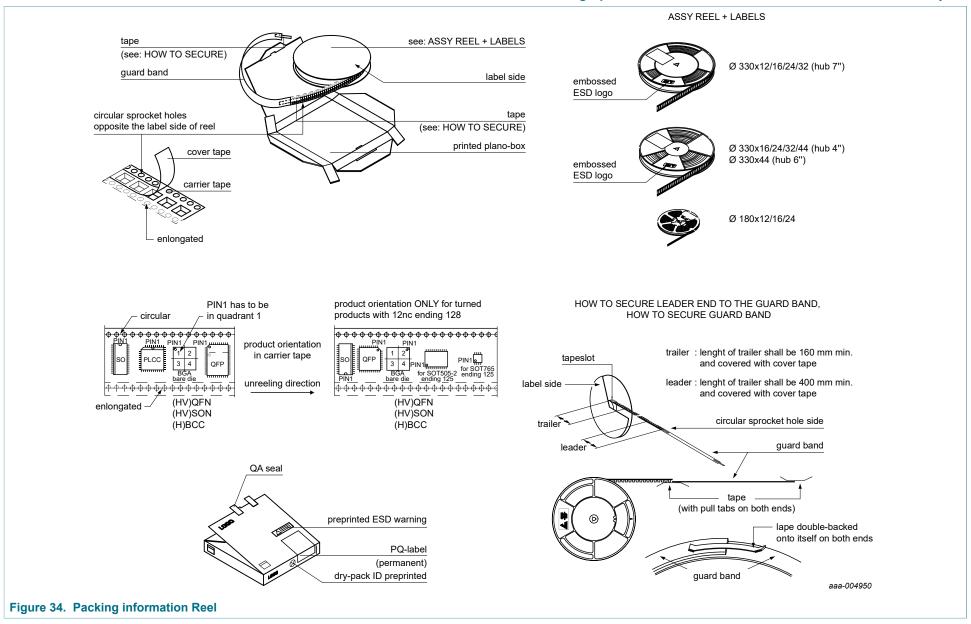

#### **Table 3. Ordering information**

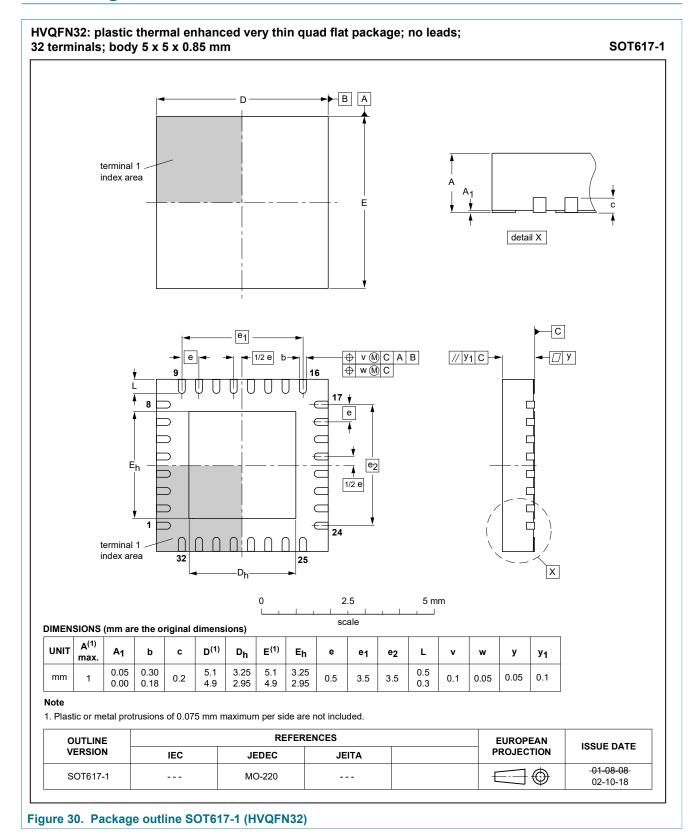

| Type number                       | Package |                                                                                     |         |  |

|-----------------------------------|---------|-------------------------------------------------------------------------------------|---------|--|

|                                   | Name    | Description                                                                         | Version |  |

| SLRC61002HN/TRAYB <sup>[1]</sup>  | HVQFN32 | plastic thermal enhanced very thin quad flat package; no                            |         |  |

| SLRC61002HN/TRAYBM <sup>[2]</sup> |         | leads; MSL1, 32 terminals + 1 central ground; body 5 × 5 × 0.85 mm                  |         |  |

| SLRC61002HN/T/R <sup>[3]</sup>    |         |                                                                                     |         |  |

| SLRC61003HN/TRAYB <sup>[4]</sup>  |         | plastic thermal enhanced very thin quad flat package; no                            | -       |  |

| SLRC61003HN/T/R <sup>[5]</sup>    |         | leads; MSL2, 32 terminals + 1 central ground; body 5 × 5 × 0.85 mm, wettable flanks |         |  |

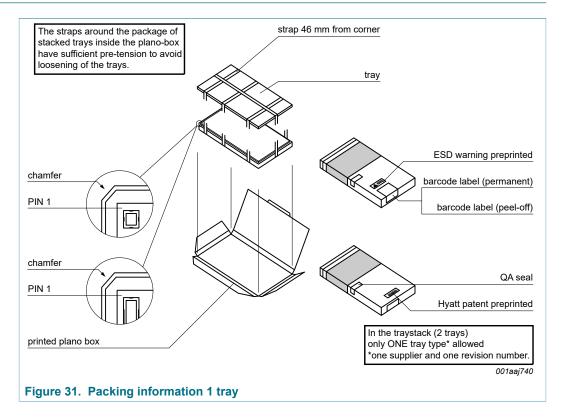

- Delivered in one tray

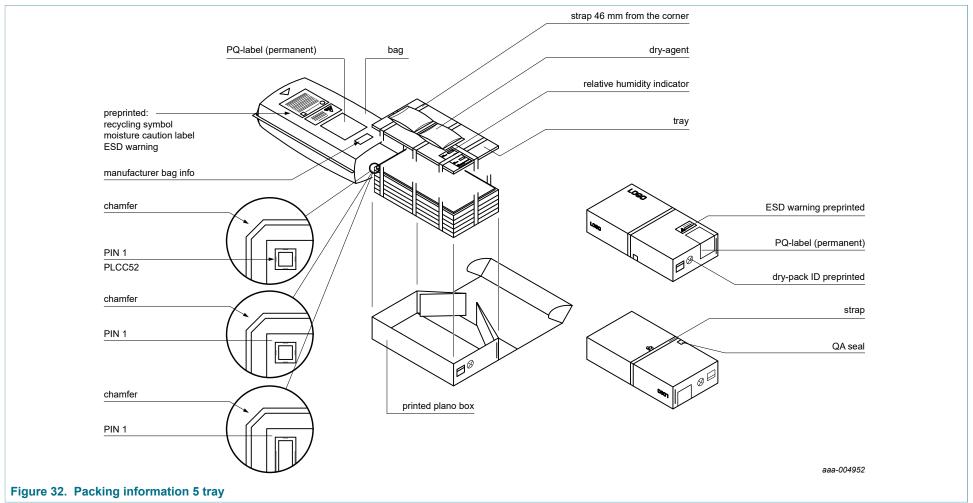

Delivered in five trays

Delivered on reel with 6000 pieces

Delivered in one tray, MOQ (Minimum order quantity): 490 pcs

Delivered on reel with 6000 pieces; MOQ (Minimum order quantity): 6000 pcs [1] [2] [3] [4] [5]

### High-performance ICODE frontend SLRC610 and SLRC610 plus

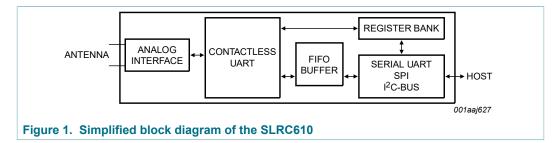

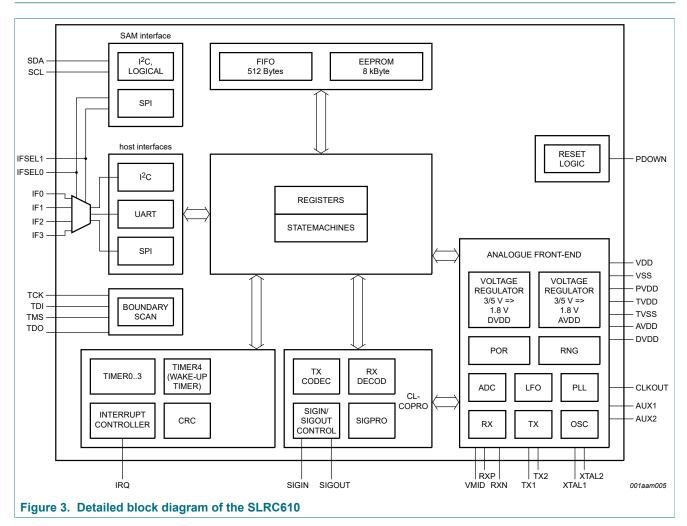

## 6 Block diagram

The analog interface handles the modulation and demodulation of the antenna signals for the contactless interface.

The contactless UART manages the protocol dependency of the contactless interface settings managed by the host.

The FIFO buffer ensures fast and convenient data transfer between host and the contactless UART.

The register bank contains the settings for the analog and digital functionality.

### High-performance ICODE frontend SLRC610 and SLRC610 plus

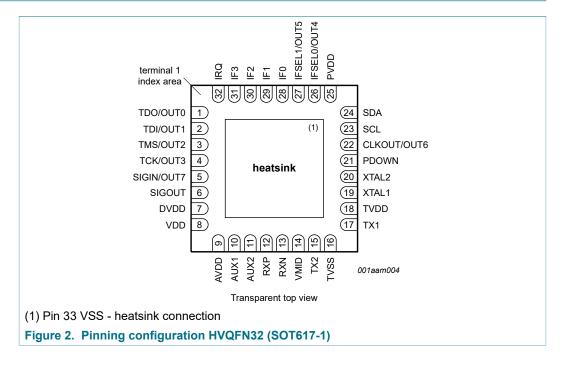

# 7 Pinning information

### 7.1 Pin description

Table 4. Pin description

| Pin | Symbol      | Туре | Description                                                             |

|-----|-------------|------|-------------------------------------------------------------------------|

| 1   | TDO / OUT0  | 0    | test data output for boundary scan interface / general purpose output 0 |

| 2   | TDI / OUT1  | I    | test data input boundary scan interface / general purpose output 1      |

| 3   | TMS / OUT2  | I    | test mode select boundary scan interface / general purpose output 2     |

| 4   | TCK / OUT3  | I    | test clock boundary scan interface / general purpose output 3           |

| 5   | SIGIN /OUT7 | I/O  | Contactless communication interface output. / general purpose output 7  |

| 6   | SIGOUT      | 0    | Contactless communication interface input.                              |

| 7   | DVDD        | PWR  | digital power supply buffer <sup>[1]</sup>                              |

| 8   | VDD         | PWR  | power supply                                                            |

| 9   | AVDD        | PWR  | analog power supply buffer <sup>[1]</sup>                               |

| 10  | AUX1        | 0    | auxiliary outputs: Pin is used for analog test signal                   |

| 11  | AUX2        | 0    | auxiliary outputs: Pin is used for analog test signal                   |

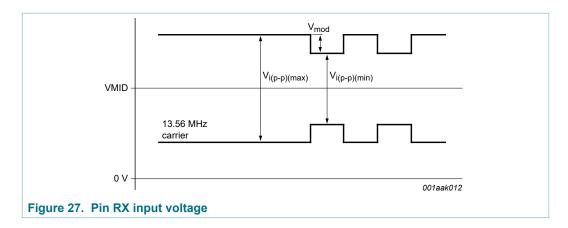

| 12  | RXP         | I    | receiver input pin for the received RF signal.                          |

| 13  | RXN         | I    | receiver input pin for the received RF signal.                          |

| 14  | VMID        | PWR  | internal receiver reference voltage [1]                                 |

| 15  | TX2         | 0    | transmitter 2: delivers the modulated 13.56 MHz carrier                 |

| 16  | TVSS        | PWR  | transmitter ground, supplies the output stage of TX1, TX2               |

| 17  | TX1         | 0    | transmitter 1: delivers the modulated 13.56 MHz carrier                 |

# High-performance ICODE frontend SLRC610 and SLRC610 plus

| Pin | Symbol        | Туре | Description                                                                                                                                                   |

|-----|---------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18  | TVDD          | PWR  | transmitter voltage supply                                                                                                                                    |

| 19  | XTAL1         | I    | crystal oscillator input: Input to the inverting amplifier of the oscillator. This pin is also the input for an externally generated clock (fosc = 27.12 MHz) |

| 20  | XTAL2         | 0    | crystal oscillator output: output of the inverting amplifier of the oscillator                                                                                |

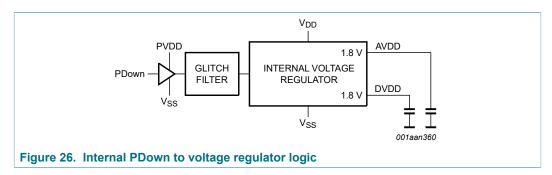

| 21  | PDOWN         | I    | Power Down (RESET)                                                                                                                                            |

| 22  | CLKOUT / OUT6 | 0    | clock output / general purpose output 6                                                                                                                       |

| 23  | SCL           | 0    | Serial Clock line                                                                                                                                             |

| 24  | SDA           | I/O  | Serial Data Line                                                                                                                                              |

| 25  | PVDD          | PWR  | pad power supply                                                                                                                                              |

| 26  | IFSEL0 / OUT4 | I    | host interface selection 0 / general purpose output 4                                                                                                         |

| 27  | IFSEL1 / OUT5 | I    | host interface selection 1 / general purpose output 5                                                                                                         |

| 28  | IF0           | I/O  | interface pin, multifunction pin: Can be assigned to host interface RS232, SPI, $\rm I^2C$ , $\rm I^2C$ -L                                                    |

| 29  | IF1           | I/O  | interface pin, multifunction pin: Can be assigned to host interface SPI, I <sup>2</sup> C, I <sup>2</sup> C-L                                                 |

| 30  | IF2           | I/O  | interface pin, multifunction pin: Can be assigned to host interface RS232, SPI, $\rm I^2C$ , $\rm I^2C$ -L                                                    |

| 31  | IF3           | I/O  | interface pin, multifunction pin: Can be assigned to host interface RS232, SPI, I $^2$ C, I $^2$ C-L                                                          |

| 32  | IRQ           | 0    | interrupt request: output to signal an interrupt event                                                                                                        |

| 33  | VSS           | PWR  | ground and heat sink connection                                                                                                                               |

<sup>[1]</sup> This pin is used for connection of a buffer capacitor. Connection of a supply voltage might damage the device.

### High-performance ICODE frontend SLRC610 and SLRC610 plus

# 8 Functional description

#### 8.1 Interrupt controller

The interrupt controller handles the enabling/disabling of interrupt requests. All of the interrupts can be configured by firmware. Additionally, the firmware has possibilities to trigger interrupts or clear pending interrupt requests. Two 8-bit interrupt registers IRQ0 and IRQ1 are implemented, accompanied by two 8-bit interrupt enable registers IRQ0En and IRQ1En. A dedicated functionality of bit 7 to set and clear bits 0 to 6 in this interrupt controller registers is implemented.

The SLRC610 indicates certain events by setting bit IRQ in the register Status1Reg and additionally, if activated, by pin IRQ. The signal on pin IRQ may be used to interrupt the host using its interrupt handling capabilities. This allows the implementation of efficient host software.

Table 4. shows the available interrupt bits, the corresponding source and the condition for its activation. The interrupt bits Timer0IRQ, Timer1IRQ, Timer2IRQ, Timer3OIRQ, in register IRQ1 indicate an interrupt set by the timer unit. The setting is done if the timer underflows.

### High-performance ICODE frontend SLRC610 and SLRC610 plus

The TxIRQ bit in register IRQ0 indicates that the transmission is finished. If the state changes from sending data to transmitting the end of the frame pattern, the transmitter unit sets the interrupt bit automatically.

The bit RxIRQ in register IRQ0 indicates an interrupt when the end of the received data is detected.

The bit IdleIRQ in register IRQ0 is set if a command finishes and the content of the command register changes to idle.

The register WaterLevel defines both - minimum and maximum warning levels - counting from top and from bottom of the FIFO by a single value.

The bit HiAlertIRQ in register IRQ0 is set to logic 1 if the HiAlert bit is set to logic 1, that means the FIFO data number has reached the top level as configured by the register WaterLevel and bit WaterLevelExtBit.

The bit LoAlertIRQ in register IRQ0 is set to logic 1 if the LoAlert bit is set to logic 1, that means the FIFO data number has reached the bottom level as configured by the register WaterLevel.

The bit ErrIRQ in register IRQ0 indicates an error detected by the contactless UART during receive. This is indicated by any bit set to logic 1 in register Error.

The bit LPCDIRQ in register IRQ0 indicates a card detected.

The bit RxSOFIRQ in register IRQ0 indicates a detection of a SOF or a subcarrier by the contactless UART during receiving.

The bit GlobalIRQ in register IRQ1 indicates an interrupt occurring at any other interrupt source when enabled.

Table 5. Interrupt sources

| Interrupt bit | Interrupt source      | Is set automatically, when                                                                 |

|---------------|-----------------------|--------------------------------------------------------------------------------------------|

| Timer0IRQ     | Timer Unit            | the timer register T0 CounterVal underflows                                                |

| Timer1IRQ     | Timer Unit            | the timer register T1 CounterVal underflows                                                |

| Timer2IRQ     | Timer Unit            | the timer register T2 CounterVal underflows                                                |

| Timer3IRQ     | Timer Unit            | the timer register T3 CounterVal underflows                                                |

| TxIRQ         | Transmitter           | a transmitted data stream ends                                                             |

| RxIRQ         | Receiver              | a received data stream ends                                                                |

| IdleIRQ       | Command Register      | a command execution finishes                                                               |

| HiAlertIRQ    | FIFO-buffer pointer   | the FIFO data number has reached the top level as configured by the register WaterLevel    |

| LoAlertIRQ    | FIFO-buffer pointer   | the FIFO data number has reached the bottom level as configured by the register WaterLevel |

| ErrIRQ        | contactless UART      | a communication error had been detected                                                    |

| LPCDIRQ       | LPCD                  | a card was detected when in low-power card detection mode                                  |

| RxSOFIRQ      | Receiver              | detection of a SOF or a subcarrier                                                         |

| GlobalIRQ     | all interrupt sources | will be set if another interrupt request source is set                                     |

### High-performance ICODE frontend SLRC610 and SLRC610 plus

### 8.2 Timer module

Timer module overview

The SLRC610 implements five timers. Four timers -Timer0 to Timer3 - have an input clock that can be configured by register T(x)Control to be 13.56 MHz, 212 kHz, (derived from the 27.12 MHz quartz) or to be the underflow event of the fifth Timer (Timer4). Each timer implements a counter register which is 16 bit wide. A reload value for the counter is defined in a range of 0000h to FFFFh in the registers TxReloadHi and TxReloadLo. The fifth timer Timer4 is intended to be used as a wakeup timer and is connected to the internal LFO (Low Frequency Oscillator) as input clock source.

The TControl register allows the global start and stop of each of the four timers Timer0 to Timer3. Additionally, this register indicates if one of the timers is running or stopped. Each of the five timers implements an individual configuration register set defining timer reload value (e.g. T0ReloadHi,T0ReloadLo), the timer value (e.g. T0CounterValHi, T0CounterValLo) and the conditions which define start, stop and clockfrequency (e.g. T0Control).

The external host may use these timers to manage timing relevant tasks. The timer unit may be used in one of the following configurations:

- · Time-out counter

- · Watch-dog counter

- · Stop watch

- · Programmable one-shot timer

- · Periodical trigger

The timer unit can be used to measure the time interval between two events or to indicate that a specific event has occurred after an elapsed time. The timer register content is modified by the timer unit, which can be used to generate an interrupt to allow an host to react on this event.

The counter value of the timer is available in the registers T(x)CounterValHi, T(x)CounterValLo. The content of these registers is decremented at each timer clock.

If the counter value has reached a value of 0000h and the interrupts are enabled for this specific timer, an interrupt will be generated as soon as the next clock is received.

If enabled, the timer event can be indicated on the pin IRQ (interrupt request). The bit Timer(x)IRQ can be set and reset by the host controller. Depending on the configuration, the timer will stop counting at 0000h or restart with the value loaded from registers T(x)ReloadHi, T(x)ReloadLo.

The counting of the timer is indicated by bit TControl.T(x)Running.

The timer can be started by setting bits TControl.T(x)Running and TControl.T(x)StartStopNow or stopped by setting the bits TControl.T(x)StartStopNow and clearing TControl.T(x)Running.

Another possibility to start the timer is to set the bit T(x)Mode.T(x)Start, this can be useful if dedicated protocol requirements need to be fulfilled.

### 8.2.1 Timer modes

### High-performance ICODE frontend SLRC610 and SLRC610 plus

### 8.2.1.1 Time-Out- and Watch-Dog-Counter

Having configured the timer by setting  $register\ T(x)Reload\ Value$  and starting the counting of Timer(x) by setting bit TControl. T(x)StartStop and TControl. T(x)Running, the timer unit decrements the  $T(x)Counter\ Value$  Register beginning with the configured start event. If the configured stop event occurs before the Timer(x) underflows (e.g. a bit is received from the card), the timer unit stops (no interrupt is generated).

If no stop event occurs, the timer unit continues to decrement the counter registers until the content is zero and generates a timer interrupt request at the next clock cycle. This allows to indicate to a host that the event did not occur during the configured time interval.

### 8.2.1.2 Wake-up timer

The wake-up Timer4 allows to wakeup the system from standby after a predefined time. The system can be configured in such a way that it is entering the standby mode again in case no card had been detected.

This functionality can be used to implement a low-power card detection (LPCD). For the low-power card detection it is recommended to set T4Control.T4AutoWakeUp and T4Control.T4AutoRestart, to activate the Timer4 and automatically set the system in standby. The internal low frequency oscillator (LFO) is then used as input clock for this Timer4. If a card is detected the host-communication can be started. If bit T4Control.T4AutoWakeUp is not set, the SLRC610 will not enter the standby mode again in case no card is detected but stays fully powered.

#### 8.2.1.3 Stop watch

If an underflow occurred which can be identified by evaluating the corresponding IRQ bit, the performed time measurement according to the formula above is not correct.

The elapsed time between a configured start- and stop event may be measured by the CLRC663 timer unit. By setting the registers T(x)ReloadValueHi, T(x)reloadValueLo the timer starts to decrement as soon as activated. If the configured stop event occurs, the timer stops decrementing. The elapsed time between start and stop event can then be calculated by the host dependent on the timer interval TTimer:

$$\Delta T = (Treload_{value} - Timer_{value})^* T_{Timer}$$

(1)

If an underflow occurred which can be identified by evaluating the corresponding IRQ bit, the performed time measurement according to the formula above is not correct.

### 8.2.1.4 Programmable one-shot timer

The host configures the interrupt and the timer, starts the timer and waits for the interrupt event on pin IRQ. After the configured time the interrupt request will be raised.

### 8.2.1.5 Periodical trigger

If the bit T(x)Control.T(x)AutoRestart is set and the interrupt is activated, an interrupt request will be indicated periodically after every elapsed timer period.

SLRC610

### High-performance ICODE frontend SLRC610 and SLRC610 plus

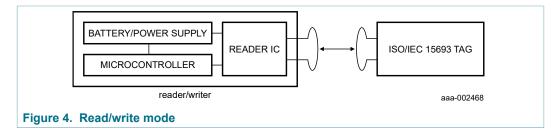

### 8.3 Contactless interface unit

The contactless interface unit of the SLRC610 supports the following read/write operating modes:

- ISO/IEC15693/ICODE

- ICODE EPC UID

- ISO/IEC 18000-3 mode 3/ EPC Class-1 HF

A typical system using the SLRC610 is using a microcontroller to implement the higher levels of the contactless communication protocol and a power supply (battery or external supply).

### 8.3.1 ISO/IEC15693 functionality

The physical parameters are described in <u>Table 5</u>.

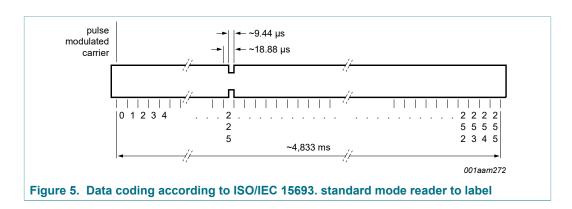

Table 6. Communication overview for ISO/IEC 15693 reader/writer reader to label

| Communication direction                                      | Signal type            | Transfer speed                   |                                    |  |  |

|--------------------------------------------------------------|------------------------|----------------------------------|------------------------------------|--|--|

|                                                              |                        | fc / 8192 kbit/s                 | fc / 512 kbit/s                    |  |  |

| Reader to label<br>(send data from the<br>SLRC610 to a card) | reader side modulation | 10 % to 30 % ASK or<br>100 % ASK | 10 % to 30 % ASK 90 % to 100 % ASK |  |  |

|                                                              | bit encoding           | 1/256                            | 1/4                                |  |  |

|                                                              | data rate              | 1,66 kbit/s                      | 26,48kbit/s                        |  |  |

Table 7. Communication overview for ISO/IEC 15693 reader/writer label to reader

| Communication direction                                                        | Signal type             | Transfer speed        |                             |                                                       |                                                   |  |  |

|--------------------------------------------------------------------------------|-------------------------|-----------------------|-----------------------------|-------------------------------------------------------|---------------------------------------------------|--|--|

|                                                                                |                         | 6.62 (6.67)<br>kbit/s | 13.24 kbit/s <sup>[1]</sup> | 26.48<br>(26.69) kbit/s                               | 52.96 kbit/s                                      |  |  |

| Label to reader<br>(SLRC610<br>receives data<br>from a card)<br>fc = 13.56 MHz | card side<br>modulation | not<br>supported      | not supported               | single (dual)<br>subcarrier load<br>modulation<br>ASK | single<br>subcarrier<br>load<br>modulation<br>ASK |  |  |

|                                                                                | bit length<br>(µs)      | -                     | -                           | 37.76 (37.46)                                         | 18.88                                             |  |  |

|                                                                                | bit encoding            | -                     | -                           | Manchester coding                                     | Manchester coding                                 |  |  |

### High-performance ICODE frontend SLRC610 and SLRC610 plus

| Communication | Signal type                      | Transfer speed        |                             |                         |              |  |  |

|---------------|----------------------------------|-----------------------|-----------------------------|-------------------------|--------------|--|--|

| direction     |                                  | 6.62 (6.67)<br>kbit/s | 13.24 kbit/s <sup>[1]</sup> | 26.48<br>(26.69) kbit/s | 52.96 kbit/s |  |  |

|               | subcarrier<br>frequency<br>[MHz] | -                     | -                           | fc / 32 (fc / 28)       | fc / 32      |  |  |

[1] Fast inventory (page) read command only (ICODE proprietary command).

### 8.3.2 EPC-UID/UID-OTP functionality

The physical parameters are described in Table 7.

Table 8. Communication overview for EPC/UID

| Communication direction                                     | Signal type            | Transfer speed   |                                   |  |

|-------------------------------------------------------------|------------------------|------------------|-----------------------------------|--|

|                                                             |                        | 26.48 kbit/s     | 52.96 kbit/s                      |  |

| Reader to card<br>(send data from the<br>SLRC610 to a card) | reader side modulation | 10 % to 30 % ASK |                                   |  |

|                                                             | bit encoding           | RTZ              |                                   |  |

| ,                                                           | bit length             | 37.76 μs         |                                   |  |

| Card to reader<br>(SLRC610 receives                         | card side modulation   |                  | single subcarrier load modulation |  |

| data from a card)                                           | bit length             |                  | 18.88 µs                          |  |

|                                                             | bit encoding           |                  | Manchester coding                 |  |

Data coding and framing according to EPC global 13.56 MHz ISM (industrial, scientific and medical) Band Class 1 Radio Frequency Identification Tag Interface Specification (Candidate Recommendation, Version 1.0.0).

### 8.3.3 ISO/IEC 18000-3 mode 3/ EPC Class-1 HF functionality

The ISO/IEC 18000-3 mode 3/ EPC Class-1 HF is not described in this document. For a detailed explanation of the protocol, refer to the ISO/IEC 18000-3 mode 3/ EPC Class-1 HF standard.

### High-performance ICODE frontend SLRC610 and SLRC610 plus

### 8.3.3.1 Data encoding ICODE

The ICODE protocols have mainly three different methods of data encoding:

- "1" out of "4" coding scheme

- "1" out of "256" coding scheme

- "Return to Zero" (RZ) coding scheme

Data encoding for all three coding schemes is done by the ICODE generator.

The supported EPC Class-1 HF modes are:

- 2 pulse for 424 kbit subcarrier

- 4 pulse for 424 kbit subcarrier

- 2 pulse for 848 kbit subcarrier

- 4 pulse for 848 kbit subcarrier

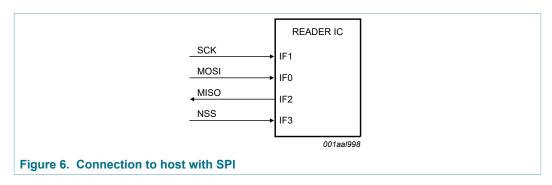

#### 8.4 Host interfaces

### 8.4.1 Host interface configuration

The SLRC610 supports direct interfacing of various hosts as the SPI, I<sup>2</sup>C, I<sup>2</sup>CL and serial UART interface type. The SLRC610 resets its interface and checks the current host interface type automatically having performed a power-up or resuming from power down. The SLRC610 identifies the host interface by the means of the logic levels on the control pins after the Cold Reset Phase. This is done by a combination of fixed pin connections. The following table shows the possible configurations defined by IFSEL1, IFSEL0:

Table 9. Connection scheme for detecting the different interface types

| Pin | Pin Symbol | UART    | SPI     | I <sup>2</sup> C | I <sup>2</sup> C-L |

|-----|------------|---------|---------|------------------|--------------------|

| 28  | IF0        | RX      | MOSI    | ADR1             | ADR1               |

| 29  | IF1        | n.c.    | SCK     | SCL              | SCL                |

| 30  | IF2        | TX      | MISO    | ADR2             | SDA                |

| 31  | IF3        | PAD_VDD | NSS     | SDA              | ADR2               |

| 26  | IFSEL0     | VSS     | VSS     | PAD_VDD          | PAD_VDD            |

| 27  | IFSEL1     | VSS     | PAD_VDD | VSS              | PAD_VDD            |

### 8.4.2 SPI interface

### High-performance ICODE frontend SLRC610 and SLRC610 plus

#### 8.4.2.1 **General**

The SLRC610 acts as a slave during the SPI communication. The SPI clock SCK has to be generated by the master. Data communication from the master to the slave uses the Line MOSI. Line MISO is used to send data back from the SLRC610 to the master.

A serial peripheral interface (SPI compatible) is supported to enable high speed communication to a host. The implemented SPI compatible interface is according to a standard SPI interface. The SPI compatible interface can handle data speed of up to 10 Mbit/s. In the communication with a host SLRC610 acts as a slave receiving data from the external host for register settings and to send and receive data relevant for the communication on the RF interface.

NSS (Not Slave Select) enables or disables the SPI interface. When NSS is logical high, the interface is disabled and reset. Between every SPI command the NSS must go to logical high to be able to start the next command read or write.

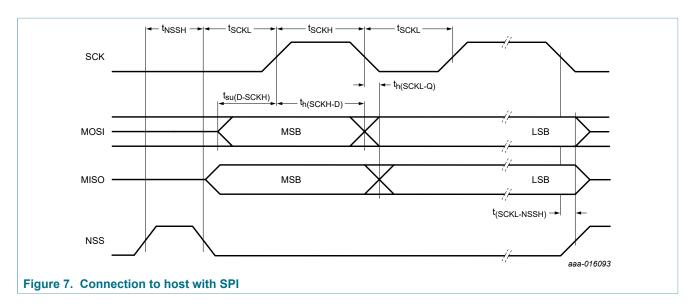

On both data lines (MOSI, MISO) each data byte is sent by MSB first. Data on MOSI line shall be stable on rising edge of the clock line (SCK) and is allowed to change on falling edge. The same is valid for the MISO line. Data is provided by the SLRC610 on the falling edge and is stable on the rising edge. The polarity of the clock is low at SPI idle.

#### 8.4.2.2 Read data

To read out data from the SLRC610 by using the SPI compatible interface the following byte order has to be used.

The first byte that is sent defines the mode (LSB bit) and the address.

Table 10. Byte Order for MOSI and MISO

|      | byte 0    | byte 1    | byte 2    | byte 3 to n-1 | byte n     | byte n+1 |

|------|-----------|-----------|-----------|---------------|------------|----------|

| MOSI | address 0 | address 1 | address 2 |               | address n  | 00h      |

| MISO | X         | data 0    | data 1    |               | data n - 1 | data n   |

Remark: The Most Significant Bit (MSB) has to be sent first.

#### 8.4.2.3 Write data

To write data to the SLRC610 using the SPI interface the following byte order has to be used. It is possible to write more than one byte by sending a single address byte (see.8.5.2.4).

The first send byte defines both, the mode itself and the address byte.

SLRC610

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2020. All rights reserved

### High-performance ICODE frontend SLRC610 and SLRC610 plus

Table 11. Byte Order for MOSI and MISO

|      | byte 0    | byte 1 | byte 2 | 3 to n-1 | byte n     | byte n + 1 |

|------|-----------|--------|--------|----------|------------|------------|

| MOSI | address 0 | data 0 | data 1 |          | data n - 1 | data n     |

| MISO | Χ         | X      | X      |          | X          | X          |

Remark: The Most Significant Bit (MSB) has to be sent first.

### 8.4.2.4 Address byte

The address byte has to fulfil the following format:

The LSB bit of the first byte defines the used mode. To read data from the SLRC610 the LSB bit is set to logic 1. To write data to the SLRC610 the LSB bit has to be cleared. The bits 6 to 0 define the address byte.

NOTE: When writing the sequence [address byte][data0][data1][data2]..., [data0] is written to address [address byte], [data1] is written to address [address byte + 1] and [data2] is written to [address byte + 2].

Exception: This auto increment of the address byte is not performed if data is written to the FIFO address

Table 12. Address byte 0 register; address MOSI

| 7         | 6         | 5         | 4         | 3         | 2         | 1         | 0                     |

|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------------------|

| address 6 | address 5 | address 4 | address 3 | address 2 | address 1 | address 0 | 1 (read)<br>0 (write) |

| MSB       |           |           |           |           |           |           | LSB                   |

### 8.4.2.5 Timing Specification SPI

The timing condition for SPI interface is as follows:

Table 13. Timing conditions SPI

| Symbol                  | Parameter                          | Min | Тур | Max | Unit |

|-------------------------|------------------------------------|-----|-----|-----|------|

| t <sub>SCKL</sub>       | SCK LOW time                       | 50  | -   | -   | ns   |

| t <sub>SCKH</sub>       | SCK HIGH time                      | 50  | -   | -   | ns   |

| t <sub>h(SCKH-D)</sub>  | SCK HIGH to data input hold time   | 25  | -   | -   | ns   |

| t <sub>su(D-SCKH)</sub> | data input to SCK HIGH set-up time | 25  | -   | -   | ns   |

| t <sub>h(SCKL-Q)</sub>  | SCK LOW to data output hold time   | -   | -   | 25  | ns   |

| t(SCKL-NSSH)            | SCK LOW to NSS HIGH time           | 0   | -   | -   | ns   |

| t <sub>NSSH</sub>       | NSS HIGH time                      | 50  | -   | -   | ns   |

### High-performance ICODE frontend SLRC610 and SLRC610 plus

**Remark:** To send more bytes in one data stream the NSS signal must be LOW during the send process. To send more than one data stream the NSS signal must be HIGH between each data stream.

#### 8.4.3 RS232 interface

#### 8.4.3.1 Selection of the transfer speeds

The internal UART interface is compatible to a RS232 serial interface. The levels supplied to the pins are between VSS and PVDD. To achieve full compatibility of the voltage levels to the RS232 specification, a RS232 level shifter is required.

<u>Table 14 "Selectable transfer speeds"</u> describes examples for different transfer speeds and relevant register settings. The resulting transfer speed error is less than 1.5 % for all described transfer speeds. The default transfer speed is 115.2 kbit/s.

To change the transfer speed, the host controller has to write a value for the new transfer speed to the register SerialSpeedReg. The bits BR\_T0 and BR\_T1 define factors to set the transfer speed in the SerialSpeedReg.

Table 13 "Settings of BR\_T0 and BR\_T1" describes the settings of BR\_T0 and BR\_T1.

Table 14. Settings of BR T0 and BR T1

| BR_T0        | 0       | 1        | 2        | 3        | 4        | 5        | 6        | 7        |

|--------------|---------|----------|----------|----------|----------|----------|----------|----------|

| factor BR_T0 | 1       | 1        | 2        | 4        | 8        | 16       | 32       | 64       |

| range BR_T1  | 1 to 32 | 33 to 64 |

Table 15. Selectable transfer speeds

| Transfer speed (kbit/s) | Serial SpeedReg | Transfer speed accuracy (%) |  |

|-------------------------|-----------------|-----------------------------|--|

|                         | (Hex.)          |                             |  |

| 7.2                     | FA              | -0.25                       |  |

| 9.6                     | ЕВ              | 0.32                        |  |

SLRC610

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2020. All rights reserved

### High-performance ICODE frontend SLRC610 and SLRC610 plus

| Transfer speed (kbit/s) | Serial SpeedReg | Transfer speed accuracy (%) |

|-------------------------|-----------------|-----------------------------|

|                         | (Hex.)          |                             |

| 14.4                    | DA              | -0.25                       |

| 19.2                    | СВ              | 0.32                        |

| 38.4                    | AB              | 0.32                        |

| 57.6                    | 9A              | -0.25                       |

| 115.2                   | 7A              | -0.25                       |

| 128                     | 74              | -0.06                       |

| 230.4                   | 5A              | -0.25                       |

| 460.8                   | 3A              | -0.25                       |

| 921.6                   | 1C              | 1.45                        |

| 1228.8                  | 15              | 0.32                        |

The selectable transfer speeds as shown are calculated according to the following formulas:

```

if BR_T0 = 0: transfer speed = 27.12 MHz / (BR_T1 + 1) if BR_T0 > 0: transfer speed = 27.12 MHz / (BR_T1 + 33)/2^{(BR_T0 - 1)}

```

Remark: Transfer speeds above 1228.8 kBits/s are not supported.

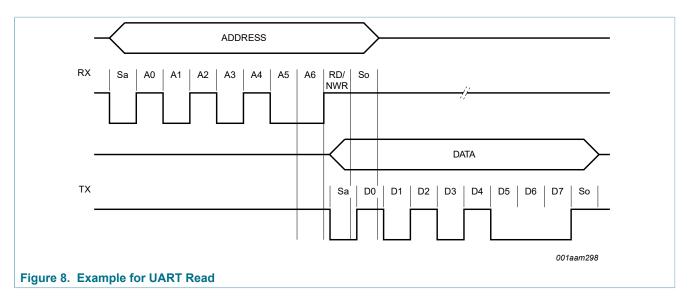

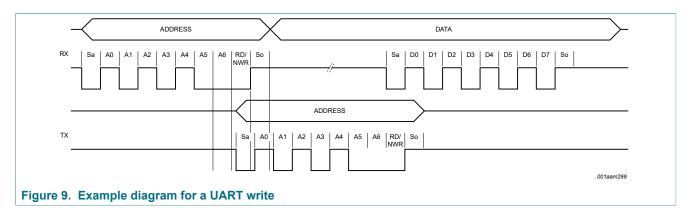

#### 8.4.3.2 Framing

Table 16. UART framing

| Table 101 Of all Halling |        |       |  |  |  |

|--------------------------|--------|-------|--|--|--|

| Bit                      | Length | Value |  |  |  |

| Start bit (Sa)           | 1 bit  | 0     |  |  |  |

| Data bits                | 8 bit  | Data  |  |  |  |

| Stop bit (So)            | 1 bit  | 1     |  |  |  |

**Remark:** For data and address bytes the LSB bit has to be sent first. No parity bit is used during transmission.

**Read data:** To read out data using the UART interface the flow described below has to be used. The first send byte defines both the mode itself and the address. The Trigger on pin IF3 has to be set, otherwise no read of data is possible.

Table 17. Byte Order to Read Data

| Mode | byte 0  | byte 1 |

|------|---------|--------|

| RX   | address | -      |

| TX   | -       | data 0 |

### High-performance ICODE frontend SLRC610 and SLRC610 plus

#### Write data:

To write data to the SLRC610 using the UART interface the following sequence has to be used.

The first send byte defines both, the mode itself and the address.

Table 18. Byte Order to Write Data

| Mode | byte 0    | byte 1    |

|------|-----------|-----------|

| RX   | address 0 | data 0    |

| TX   |           | address 0 |

Remark: Data can be sent before address is received.

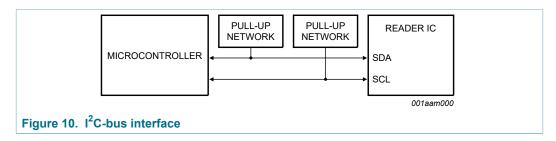

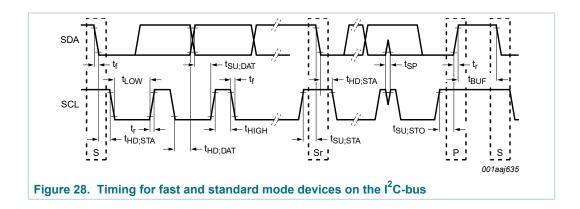

### 8.4.4 I<sup>2</sup>C-bus interface

#### 8.4.4.1 **General**

An Inter IC ( $I^2C$ ) bus interface is supported to enable a low cost, low pin count serial bus interface to the host. The implemented  $I^2C$  interface is mainly implemented according the NXP Semiconductors  $I^2C$  interface specification, rev. 3.0, June 2007. The SLRC610 can

SLRC610

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2020. All rights reserved.

### High-performance ICODE frontend SLRC610 and SLRC610 plus

act as a slave receiver or slave transmitter in standard mode, fast mode and fast mode plus.

The following features defined by the NXP Semiconductors I<sup>2</sup>C interface specification, rev. 3.0, June 2007 are not supported:

- The SLRC610 I2C interface does not stretch the clock

- The SLRC610 I2C interface does not support the general call. This means that the SLRC610 does not support a software reset

- The SLRC610 does not support the I2C device ID

- The implemented interface can only act in slave mode. Therefore no clock generation and access arbitration is implemented in the SLRC610.

- · High speed mode is not supported by the SLRC610

The voltage level on the I2C pins is not allowed to be higher than PVDD.

SDA is a bidirectional line, connected to a positive supply voltage via a pull-up resistor. Both lines SDA and SCL are set to HIGH level if no data is transmitted. Data on the I<sup>2</sup>C-bus can be transferred at data rates of up to 400 kbit/s in fast mode, up to 1 Mbit/s in the fast mode+.

If the I<sup>2</sup>C interface is selected, a spike suppression according to the I<sup>2</sup>C interface specification on SCL and SDA is automatically activated.

For timing requirements refer to <u>Table 200 "I2C-bus timing in fast mode and fast mode plus"</u>

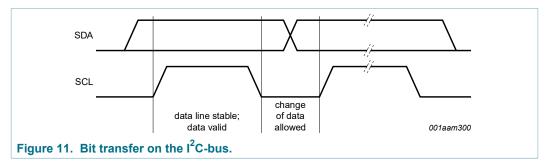

### 8.4.4.2 I<sup>2</sup>C Data validity

Data on the SDA line shall be stable during the HIGH period of the clock. The HIGH state or LOW state of the data line shall only change when the clock signal on SCL is LOW.

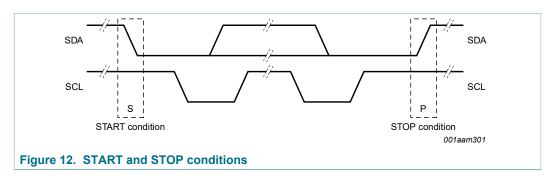

### 8.4.4.3 I<sup>2</sup>C START and STOP conditions

To handle the data transfer on the I<sup>2</sup>C-bus, unique START (S) and STOP (P) conditions are defined.

SLRC610

### High-performance ICODE frontend SLRC610 and SLRC610 plus

A START condition is defined with a HIGH-to-LOW transition on the SDA line while SCL is HIGH.

A STOP condition is defined with a LOW-to-HIGH transition on the SDA line while SCL is HIGH.

The master always generates the START and STOP conditions. The bus is considered to be busy after the START condition. The bus is considered to be free again a certain time after the STOP condition.

The bus stays busy if a repeated START (Sr) is generated instead of a STOP condition. In this respect, the START (S) and repeated START (Sr) conditions are functionally identical. Therefore, the S symbol will be used as a generic term to represent both the START and repeated START (Sr) conditions.

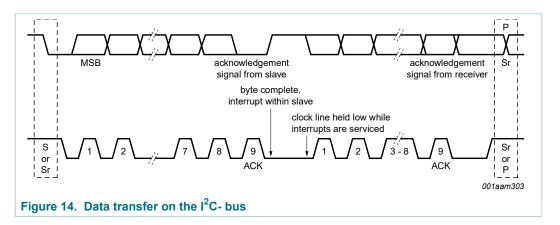

### 8.4.4.4 I<sup>2</sup>C byte format

Each byte has to be followed by an acknowledge bit. Data is transferred with the MSB first, see <u>Figure 12 "START and STOP conditions"</u>. The number of transmitted bytes during one data transfer is unrestricted but shall fulfil the read/write cycle format.

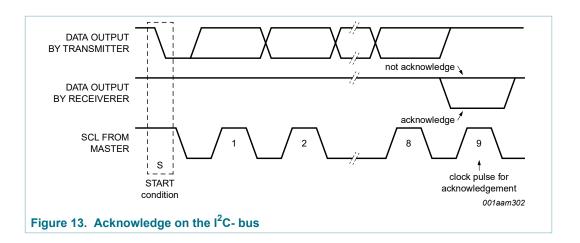

### 8.4.4.5 I<sup>2</sup>C Acknowledge

An acknowledge at the end of one data byte is mandatory. The acknowledge-related clock pulse is generated by the master. The transmitter of data, either master or slave, releases the SDA line (HIGH) during the acknowledge clock pulse. The receiver shall pull down the SDA line during the acknowledge clock pulse so that it remains stable LOW during the HIGH period of this clock pulse.

The master can then generate either a STOP (P) condition to stop the transfer, or a repeated START (Sr) condition to start a new transfer.

A master-receiver shall indicate the end of data to the slave- transmitter by not generating an acknowledge on the last byte that was clocked out by the slave. The slave-transmitter shall release the data line to allow the master to generate a STOP (P) or repeated START (Sr) condition.

### High-performance ICODE frontend SLRC610 and SLRC610 plus

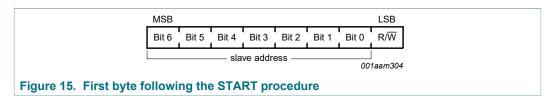

### 8.4.4.6 I<sup>2</sup>C 7-bit addressing

During the I<sup>2</sup>C-bus addressing procedure, the first byte after the START condition is used to determine which slave will be selected by the master.

Alternatively the I<sup>2</sup>C address can be configured in the EEPROM. Several address numbers are reserved for this purpose. During device configuration, the designer has to ensure, that no collision with these reserved addresses in the system is possible. Check the corresponding I<sup>2</sup>C specification for a complete list of reserved addresses.

For all SLRC610 devices the upper 5 bits of the device bus address are reserved by NXP and set to 01010(bin). The remaining 2 bits (ADR\_2, ADR\_1) of the slave address can be freely configured by the customer in order to prevent collisions with other I<sup>2</sup>C devices by using the interface pins (refer to <u>Table 8</u>) or the value of the I<sup>2</sup>C address EEPROM register (refer to <u>Table 30</u>).

### High-performance ICODE frontend SLRC610 and SLRC610 plus

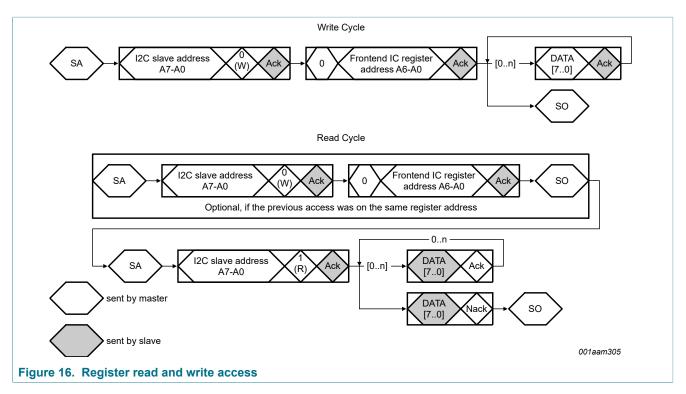

### 8.4.4.7 I<sup>2</sup>C-register write access

To write data from the host controller via I<sup>2</sup>C to a specific register of the SLRC610 the following frame format shall be used.

The read/write bit shall be set to logic 0.

The first byte of a frame indicates the device address according to the I<sup>2</sup>C rules. The second byte indicates the register address followed by up to n-data bytes. In case the address indicates the FIFO, in one frame all n-data bytes are written to the FIFO register address. This enables for example a fast FIFO access.

### 8.4.4.8 I<sup>2</sup>C-register read access

To read out data from a specific register address of the SLRC610 the host controller shall use the procedure:

First a write access to the specific register address has to be performed as indicated in the following frame:

The first byte of a frame indicates the device address according to the I<sup>2</sup>C rules. The second byte indicates the register address. No data bytes are added.

The read/write bit shall be logic 0.

Having performed this write access, the read access starts. The host sends the device address of the SLRC610. As an answer to this device address the SLRC610 responds with the content of the addressed register. In one frame n-data bytes could be read using the same register address. The address pointing to the register is incremented automatically (exception: FIFO register address is not incremented automatically). This enables a fast transfer of register content. The address pointer is incremented automatically and data is read from the locations [address], [address+1], [address+2]... [address+(n-1)]

In order to support a fast FIFO data transfer, the address pointer is not incremented automatically in case the address is pointing to the FIFO.

The read/write bit shall be set to logic 1.

### High-performance ICODE frontend SLRC610 and SLRC610 plus

### 8.4.4.9 I<sup>2</sup>CL-bus interface

The SLRC610 provides an additional interface option for connection of a SAM. This logical interface fulfills the  $I^2C$  specification, but the rise/fall timings will not be compliant to the  $I^2C$  standard. The  $I^2CL$  interface uses standard I/O pads, and the communication speed is limited to 5 MBaud. The protocol itself is equivalent to the fast mode protocol of  $I^2C$ . The SCL levels are generated by the host in push/pull mode. The RC610 does not stretch the clock. During the high period of SCL the status of the line is maintained by a bus keeper.

The address is 01010xxb, where the last two bits of the address can be defined by the application. The definition of this bits can be done by two options. With a pin, where the higher bit is fixed to 0 or the configuration can be defined via EEPROM. Refer to the EEPROM configuration in <u>Section 7.7</u>.

Table 19. Timing parameter I<sup>2</sup>CL

| Parameter           | Min | Max | Unit |

|---------------------|-----|-----|------|

| f <sub>SCL</sub>    | 0   | 5   | MHz  |

| t <sub>HD;STA</sub> | 80  | -   | ns   |

| t <sub>LOW</sub>    | 100 | -   | ns   |

| t <sub>HIGH</sub>   | 100 | -   | ns   |

| t <sub>SU;SDA</sub> | 80  | -   | ns   |

| t <sub>HD;DAT</sub> | 0   | 50  | ns   |

| t <sub>SU;DAT</sub> | 0   | 20  | ns   |

| t <sub>SU;STO</sub> | 80  | -   | ns   |

| t <sub>BUF</sub>    | 200 | -   | ns   |

SLRC610

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2020. All rights reserved

### High-performance ICODE frontend SLRC610 and SLRC610 plus

The pull-up resistor is not required for the I<sup>2</sup>CL interface. Instead, a on chip buskeeper is implemented in the SLRC610 for SDA of the I<sup>2</sup>CL interface. This protocol is intended to be used for a point to point connection of devices over a short distance and does not support a bus capability. The driver of the pin must force the line to the desired logic voltage. To avoid that two drivers are pushing the line at the same time following regulations must be fulfilled:

SCL: As there is no clock stretching, the SCL is always under control of the Master.

SDA: The SDA line is shared between master and slave. Therefore the master and the slave must have the control over the own driver enable line of the SDA pin. The following rules must be followed:

- In the idle phase the SDA line is driven high by the master

- In the time between start and stop condition the SDA line is driven by master or slave when SCL is low. If SCL is high the SDA line is not driven by any device

- To keep the value on the SDA line a on chip buskeeper structure is implemented for the line

### 8.4.5 SAM interface

#### 8.4.5.1 SAM functionality

The SLRC610 implements a dedicated I2C or SPI interface to integrate a SAM (Secure Access Module) in a very convenient way into applications (e.g. a proximity reader).

The SAM can be connected to the microcontroller to operate like a cryptographic coprocessor. For any cryptographic task, the microcontroller requests a operation from the SAM, receives the answer and sends it over a host interface (e.g. I2C, SPI) interface to the connected reader IC.

### 8.4.5.2 SAM connection

The SLRC610 provides an interface to connect a SAM dedicated to the SLRC610. Both interface options of the SLRC610, I<sup>2</sup>C, I<sup>2</sup>CL or SPI can be used for this purpose. The interface option of the SAM itself is configured by a host command sent from the host to the SAM.

The I<sup>2</sup>CL interface is intended to be used as connection between two IC's over a short distance. The protocol fulfills the I<sup>2</sup>C specification, but does support a single device connected to the bus only.

The SPI block for SAM connection is identical with the SPI host interface block.

The pins used for the SAM SPI are described in Table 19.

Table 20. SPI SAM connection

| SPI functionality | PIN    |

|-------------------|--------|

| MISO              | SDA2   |

| SCL               | SCL2   |

| MOSI              | IFSEL1 |

| NSS               | IFSEL0 |

### High-performance ICODE frontend SLRC610 and SLRC610 plus

### 8.4.6 Boundary scan interface

The SLRC610 provides a boundary scan interface according to the IEEE 1149.1. This interface allows to test interconnections without using physical test probes. This is done by test cells, assigned to each pin, which override the functionality of this pin.

To be able to program the test cells, the following commands are supported:

Table 21. Boundary scan command

| Value<br>(decimal) | Command               | Parameter in           | Parameter out |

|--------------------|-----------------------|------------------------|---------------|

| 0                  | bypass                | -                      | -             |

| 1                  | preload               | data (24)              | -             |

| 1                  | sample                | -                      | data (24)     |

| 2                  | ID code (default)     | -                      | data (32)     |

| 3                  | USER code             | -                      | data (32)     |

| 4                  | Clamp                 | -                      | -             |

| 5                  | HIGH Z                | -                      | -             |

| 7                  | extest                | data (24)              | data (24)     |

| 8                  | interface on/off      | interface (1)          | -             |

| 9                  | register access read  | address (7)            | data (8)      |

| 10                 | register access write | address (7) - data (8) | -             |

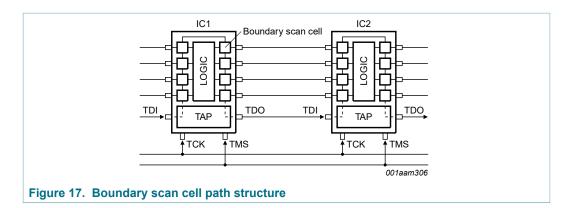

The Standard IEEE 1149.1 describes the four basic blocks necessary to use this interface: Test Access Port (TAP), TAP controller, TAP instruction register, TAP data register;

#### 8.4.6.1 Interface signals

The boundary scan interface implements a four line interface between the chip and the environment. There are three Inputs: Test Clock (TCK); Test Mode Select (TMS); Test Data Input (TDI) and one output Test Data Output (TDO). TCK and TMS are broadcast signals, TDI to TDO generate a serial line called Scan path.

Advantage of this technique is that independent of the numbers of boundary scan devices the complete path can be handled with four signal lines.

The signals TCK, TMS are directly connected with the boundary scan controller. Because these signals are responsible for the mode of the chip, all boundary scan devices in one scan path will be in the same boundary scan mode.

### 8.4.6.2 Test Clock (TCK)

The TCK pin is the input clock for the module. If this clock is provided, the test logic is able to operate independent of any other system clocks. In addition, it ensures that multiple boundary scan controllers that are daisy-chained together can synchronously communicate serial test data between components. During normal operation, TCK is driven by a free-running clock. When necessary, TCK can be stopped at 0 or 1 for extended periods of time. While TCK is stopped at 0 or 1, the state of the boundary scan controller does not change and data in the Instruction and Data Registers is not lost.

### High-performance ICODE frontend SLRC610 and SLRC610 plus

The internal pull-up resistor on the TCK pin is enabled. This assures that no clocking occurs if the pin is not driven from an external source.

#### 8.4.6.3 Test Mode Select (TMS)

The TMS pin selects the next state of the boundary scan controller. TMS is sampled on the rising edge of TCK. Depending on the current boundary scan state and the sampled value of TMS, the next state is entered. Because the TMS pin is sampled on the rising edge of TCK, the IEEE Standard 1149.1 expects the value on TMS to change on the falling edge of TCK.

Holding TMS high for five consecutive TCK cycles drives the boundary scan controller state machine to the Test-Logic-Reset state. When the boundary scan controller enters the Test-Logic-Reset state, the Instruction Register (IR) resets to the default instruction, IDCODE. Therefore, this sequence can be used as a reset mechanism.

The internal pull-up resistor on the TMS pin is enabled.

### 8.4.6.4 Test Data Input (TDI)

The TDI pin provides a stream of serial information to the IR chain and the DR chains. TDI is sampled on the rising edge of TCK and, depending on the current TAP state and the current instruction, presents this data to the proper shift register chain. Because the TDI pin is sampled on the rising edge of TCK, the IEEE Standard 1149.1 expects the value on TDI to change on the falling edge of TCK.

The internal pull-up resistor on the TDI pin is enabled.

#### 8.4.6.5 Test Data Output (TDO)

The TDO pin provides an output stream of serial information from the IR chain or the DR chains. The value of TDO depends on the current TAP state, the current instruction, and the data in the chain being accessed. In order to save power when the port is not being used, the TDO pin is placed in an inactive drive state when not actively shifting out data. Because TDO can be connected to the TDI of another controller in a daisy-chain configuration, the IEEE Standard 1149.1 expects the value on TDO to change on the falling edge of TCK.

#### 8.4.6.6 Data register

According to the IEEE1149.1 standard there are two types of data register defined: bypass and boundary scan

The bypass register enable the possibility to bypass a device when part of the scan path. Serial data is allowed to be transferred through a device from the TDI pin to the TDO pin without affecting the operation of the device.

The boundary scan register is the scan-chain of the boundary cells. The size of this register is dependent on the command.

### 8.4.6.7 Boundary scan cell

The boundary scan cell opens the possibility to control a hardware pin independent of its normal use case. Basically the cell can only do one of the following: control, output and input.

### High-performance ICODE frontend SLRC610 and SLRC610 plus

### 8.4.6.8 Boundary scan path

This chapter shows the boundary scan path of the SLRC610.

Table 22. Boundary scan path of the SLRC610

| Number (decimal) | Cell | Port   | Function |

|------------------|------|--------|----------|

| 23               | BC_1 | -      | Control  |

| 22               | BC_8 | CLKOUT | Bidir    |

| 21               | BC_1 | -      | Control  |

| 20               | BC_8 | SCL2   | Bidir    |

| 19               | BC_1 | -      | Control  |

| 18               | BC_8 | SDA2   | Bidir    |

| 17               | BC_1 | -      | Control  |

| 16               | BC_8 | IFSEL0 | Bidir    |

| 15               | BC_1 | -      | Control  |

| 14               | BC_8 | IFSEL1 | Bidir    |

| 13               | BC_1 | -      | Control  |

| 12               | BC_8 | IF0    | Bidir    |

| 11               | BC_1 | -      | Control  |

| 10               | BC_8 | IF1    | Bidir    |

| 9                | BC_1 | -      | Control  |

| 8                | BC_8 | IF2    | Bidir    |

| 7                | BC_1 | IF2    | Output2  |

| 6                | BC_4 | IF3    | Bidir    |

| 5                | BC_1 | -      | Control  |

| 4                | BC_8 | IRQ    | Bidir    |

| 3                | BC_1 | -      | Control  |

| 2                | BC_8 | SIGIN  | Bidir    |

| 1                | BC_1 | -      | Control  |

| 0                | BC_8 | SIGOUT | Bidir    |

### High-performance ICODE frontend SLRC610 and SLRC610 plus

Refer to the SLRC610 BSDL file.

### 8.4.6.9 Boundary Scan Description Language (BSDL)

All of the boundary scan devices have a unique boundary structure which is necessary to know for operating the device. Important components of this language are:

- · available test bus signal

- · compliance pins

- · command register

- · data register

- boundary scan structure (number and types of the cells, their function and the connection to the pins.)

The SLRC610 is using the cell BC\_8 for the IO-Lines. The I<sup>2</sup>C Pin is using a BC\_4 cell. For all pad enable lines the cell BC1 is used.

The manufacturer's identification is 02Bh.

- attribute IDCODEISTER of SLRC610: entity is "0001" and -- version

- "0011110010000010b" and -- part number (3C82h)

- "00000010101b" and -- manufacturer (02Bh)

- "1b"; -- mandatory

The user code data is coded as followed:

- product ID (3 bytes)

- version

These four bytes are stored as the first four bytes in the EEPROM.

#### 8.4.6.10 Non-IEEE1149.1 commands

**Interface on/off:** With this command the host/SAM interface can be deactivated and the Read and Write command of the boundary scan interface is activated. (Data = 1). With Update-DR the value is taken over.

**Register Access Read:** At Capture-DR the actual address is read and stored in the DR. Shifting the DR is shifting in a new address. With Update-DR this address is taken over into the actual address.

**Register Access Write:** At the Capture-DR the address and the data is taken over from the DR. The data is copied into the internal register at the given address.

#### 8.5 Buffer

#### 8.5.1 Overview

An 512 × 8-bit FIFO buffer is implemented in the SLRC610. It buffers the input and output data stream between the host and the internal state machine of the SLRC610. Thus, it is possible to handle data streams with lengths of up to 512 bytes without taking timing constraints into account. The FIFO can also be limited to a size of 255 byte. In this case all the parameters (FIFO length, Watermark...) require a single byte only for definition. In case of a 512 byte FIFO length the definition of this values requires 2 bytes.

### High-performance ICODE frontend SLRC610 and SLRC610 plus

### 8.5.2 Accessing the FIFO buffer

When the  $\mu$ -Controller starts a command, the SLRC610 may, while the command is in progress, access the FIFO-buffer according to that command. Physically only one FIFO-buffer is implemented, which can be used in input and output direction. Therefore the  $\mu$ -Controller has to take care, not to access the FIFO buffer in a way that corrupts the FIFO data.

### 8.5.3 Controlling the FIFO buffer

Besides writing to and reading from the FIFO buffer, the FIFO-buffer pointers might be reset by setting the bit FIFOFlush in FIFOControl to 1. Consequently, the FIFOLevel bits are set to logic 0, the actually stored bytes are not accessible any more and the FIFO buffer can be filled with another 512 bytes (or 255 bytes if the bit FIFOSize is set to 1) again.

#### 8.5.4 Status Information about the FIFO buffer

The host may obtain the following data about the FIFO-buffers status:

- Number of bytes already stored in the FIFO-buffer. Writing increments, reading decrements the FIFO level: FIFOLength in register FIFOLength (and FIFOControl Register in 512 byte mode)

- Warning, that the FIFO-buffer is almost full: HiAlert in register FIFOControl according

to the value of the water level in register WaterLevel (Register 02h bit [2], Register 03h

bit[7:0])

- Warning, that the FIFO-buffer is almost empty: LoAlert in register FIFOControl

according to the value of the water level in register WaterLevel (Register 02h bit [2],

Register 03h bit[7:0])

- FIFOOvI bit indicates, that bytes were written to the FIFO buffer although it was already full: ErrIRQ in register IRQ0.

WaterLevel is one single value defining both HiAlert (counting from the FIFO top) and LoAlert (counting from the FIFO bottom). The CLRC663 can generate an interrupt signal if:

- LoAlertIRQEn in register IRQ0En is set to logic 1 it will activate pin IRQ when LoAlert in the register FIFOControl changes to 1.

- HiAlertIRQEN in register IRQ0En is set to logic 1 it will activate pin IRQ when HiAlert in the register FIFOControl changes to 1.

The bit HiAlert is set to logic 1 if maximum water level bytes (as set in register WaterLevel) or less can be stored in the FIFO-buffer. It is generated according to the following equation:

$$HiAlert = (FiFoSize + - FiFoLength) \le WaterLevel$$

(2)

The bit LoAlert is set to logic 1 if water level bytes (as set in register WaterLevel) or less are actually stored in the FIFO-buffer. It is generated according to the following equation:

$LoAlert = FIFOLength \le WaterLevel$

SLRC610

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2020. All rights reserved

### High-performance ICODE frontend SLRC610 and SLRC610 plus

(3)

### 8.6 Analog interface and contactless UART

#### 8.6.1 General

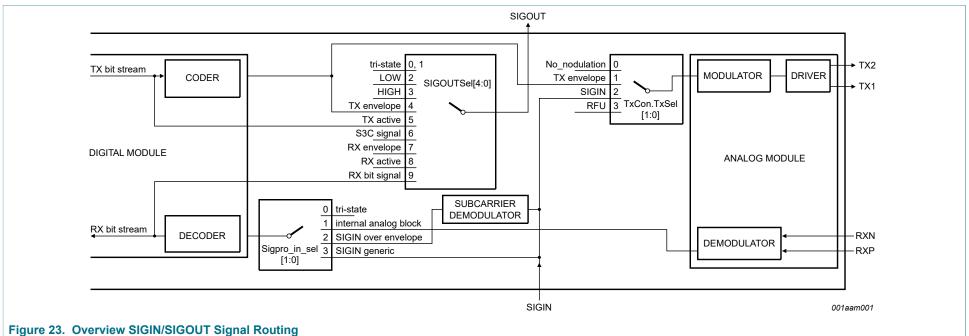

The integrated contactless UART supports the external host online with framing and error checking of the protocol requirements up to 848 kbit/s. An external circuit can be connected to the communication interface pins SIGIN and SIGOUT to modulate and demodulate the data.

The contactless UART handles the protocol requirements for the communication schemes in co-operation with the host. The protocol handling itself generates bit- and byte-oriented framing and handles error detection like Parity and CRC according to the different contactless communication schemes.

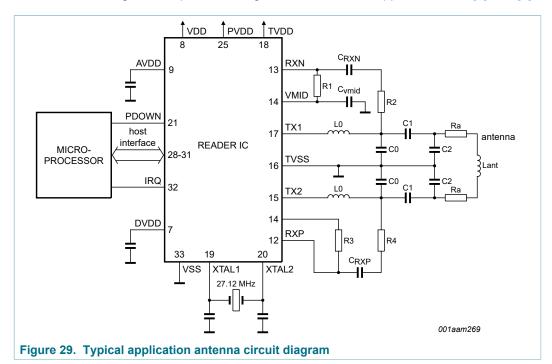

The size, the tuning of the antenna, and the supply voltage of the output drivers have an impact on the achievable field strength. The operating distance between reader and card depends additionally on the type of card used.

#### 8.6.2 TX transmitter

The signal delivered on pin TX1 and pin TX2 is the 13.56 MHz carrier modulated by an envelope signal for energy and data transmission. It can be used to drive an antenna directly, using a few passive components for matching and filtering, see <a href="Section 13">Section 13</a><a href="Matching and Filtering">"Application information"</a>. The signal on TX1 and TX2 can be configured by the register DrvMode, see <a href="Section 8.8.1" TxMode"</a>.

The modulation index can be set by the TxAmp.

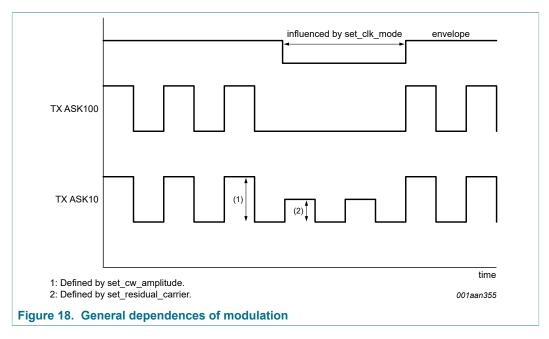

Following figure shows the general relations during modulation

Note: When changing the continuous carrier amplitude, the residual carrier amplitude also changes, while the modulation index remains the same.

SLRC610

### High-performance ICODE frontend SLRC610 and SLRC610 plus

The registers <u>Section 8.8</u> and <u>Section 8.10</u> control the data rate, the framing during transmission and the setting of the antenna driver to support the requirements at the different specified modes and transfer speeds.

Table 23. Settings for TX1 and TX2

| TxClkMode (binary) | Tx1 and TX2 output                                               | Remarks                                                                                                       |

|--------------------|------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| 000                | High impedance                                                   | -                                                                                                             |

| 001                | 0                                                                | output pulled to 0 in any case                                                                                |

| 010                | 1                                                                | output pulled to 1 in any case                                                                                |

| 110                | RF high side push                                                | open drain, only high side (push) MOS supplied with clock, clock parity defined by invtx; low side MOS is off |

| 101                | RF low side pull                                                 | open drain, only low side (pull) MOS supplied with clock, clock parity defined by invtx; high side MOS is off |

| 111                | 13.56 MHz clock derived<br>from 27.12 MHz quartz<br>divided by 2 | push/pull Operation, clock polarity defined by invtx; setting for 10% modulation                              |

Register TXamp and the bits for set\_residual\_carrier define the modulation index:

Table 24. Setting residual carrier and modulation index by TXamp.set\_residual\_carrier

| set_residual_carrier (decimal) | residual carrier [%] | modulation index [%] |

|--------------------------------|----------------------|----------------------|

| 0                              | 99                   | 0.5                  |

| 1                              | 98                   | 1.0                  |

| 2                              | 96                   | 2.0                  |

| 3                              | 94                   | 3.1                  |

| 4                              | 91                   | 4.7                  |

| 5                              | 89                   | 5.8                  |

| 6                              | 87                   | 7.0                  |

| 7                              | 86                   | 7.5                  |

| 8                              | 85                   | 8.1                  |

| 9                              | 84                   | 8.7                  |

| 10                             | 83                   | 9.3                  |

| 11                             | 82                   | 9.9                  |

| 12                             | 81                   | 10.5                 |

| 13                             | 80                   | 11.1                 |

| 14                             | 79                   | 11.7                 |

| 15                             | 78                   | 12.4                 |

| 16                             | 77                   | 13.0                 |

| 17                             | 76                   | 13.6                 |

| 18                             | 75                   | 14.3                 |

### High-performance ICODE frontend SLRC610 and SLRC610 plus

| set_residual_carrier (decimal) | residual carrier [%] | modulation index [%] |

|--------------------------------|----------------------|----------------------|

| 19                             | 74                   | 14.9                 |

| 20                             | 72                   | 16.3                 |

| 21                             | 70                   | 17.6                 |

| 22                             | 68                   | 19.0                 |

| 23                             | 65                   | 21.2                 |

| 24                             | 60                   | 25.0                 |

| 25                             | 55                   | 29.0                 |

| 26                             | 50                   | 33.3                 |

| 27                             | 45                   | 37.9                 |

| 28                             | 40                   | 42.9                 |

| 29                             | 35                   | 48.1                 |

| 30                             | 30                   | 53.8                 |

| 31                             | 25                   | 60.0                 |

Note: At VDD(TVDD) <5 V and residual carrier settings <50%, the accuracy of the modulation index may be low in dependency of the antenna tuning impedance

### 8.6.2.1 Overshoot protection

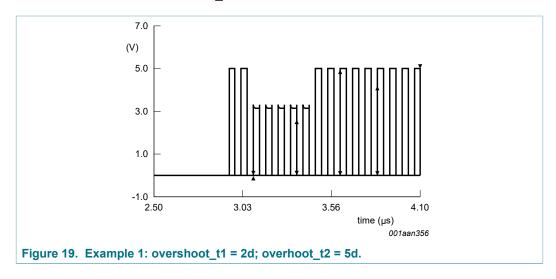

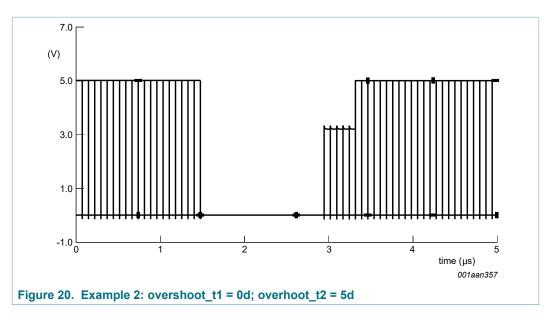

The SLRC610 provides an overshoot protection for 100% ASK to avoid overshoots during a PCD communication. Therefore two timers overshoot\_t1 and overshoot\_t2 can be used.

During the timer overshoot\_t1 runs an amplitude defined by set\_cw\_amplitude bits is provided to the output driver. Followed by an amplitude denoted by set\_residual\_carrier bits with the duration of overshoot\_t2.

### High-performance ICODE frontend SLRC610 and SLRC610 plus

#### 8.6.2.2 Bit generator

The default coding of a data stream is done by using the Bit-Generator. It is activated when the value of TxFrameCon.DCodeType is set to 0000 (bin). The Bit-Generator encodes the data stream byte-wise and can apply the following encoding steps to each data byte.

- 1. Add a start-bit of specified type at beginning of every byte

- 2. Add a stop-bit and EGT bits of a specified type. The maximum number of EGT bit is 6, only full bits are supported

- 3. Add a parity-bit of a specified type

- 4. TxLastBits (skips a given number of bits at the end of the last byte in a frame)

- 5. Encrypt data-bit (MIFARE Classic encryption)

It is not possible to skip more than 8 bit of a single byte!

By default, data bytes are always treated LSB first.

### 8.6.3 Receiver circuitry

#### 8.6.3.1 General

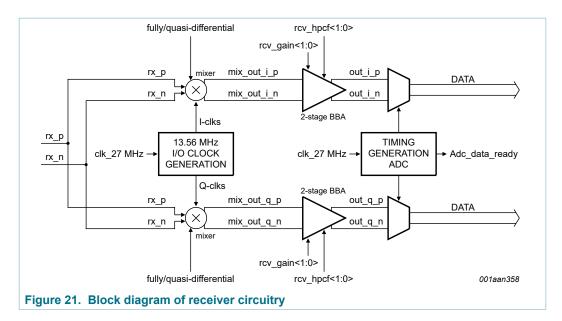

The SLRC610 features a versatile quadrature receiver architecture with fully differential signal input at RXP and RXN. It can be configured to achieve optimum performance for reception of various 13.56 MHz based protocols.

For all processing units various adjustments can be made to obtain optimum performance.

### 8.6.3.2 Block diagram

<u>Figure 21</u> shows the block diagram of the receiver circuitry. The receiving process includes several steps. First the quadrature demodulation of the carrier signal of 13.56 MHz is done. Several tuning steps in this circuit are possible.

SLRC610

### High-performance ICODE frontend SLRC610 and SLRC610 plus

The receiver can also be operated in a single ended mode. In this case the Rcv\_RX\_single bit has to be set. In the single ended mode, the two receiver pins RXP and RXN need to be connected together and will provide a single ended signal to the receiver circuitry.

When using the receiver in a single ended mode the receiver sensitivity is decreased and the achievable reading distance might be reduced, compared to the fully differential mode.

Table 25. Configuration for single or differential receiver

| Mode               | rcv_rx_single | pins RXP and RXN                                                                                         |

|--------------------|---------------|----------------------------------------------------------------------------------------------------------|

| Fully differential | 0             | provide differential signal from<br>differential antenna by separate rx-<br>coupling branches            |

| Quasi differential | 1             | connect RXP and RXN together and provide single ended signal from antenna by a single rx-coupling branch |

The quadrature-demodulator uses two different clocks, Q-clock and I-clock, with a phase shift of 90° between them. Both resulting baseband signals are amplified, filtered, digitized and forwarded to a correlation circuitry.

The typical application is intended to implement the Fully differential mode and will deliver maximum reader/writer distance. The Quasi differential mode can be used together with dedicated antenna topologies that allow a reduction of matching components at the cost of overall reading performance.

During low power card detection the DC levels at the I- and Q-channel mixer outputs are evaluated. This requires that mixers are directly connected to the ADC. This can be configured by setting the bit Rx ADCmode in register Rcv (38h).

### High-performance ICODE frontend SLRC610 and SLRC610 plus

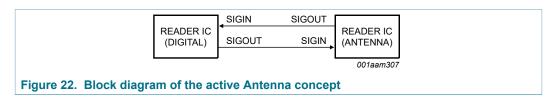

# 8.6.4 Active antenna concept