# RENESAS

NOT RECOMMENDED FOR NEW DESIGNS Contact our Technical Support Center at 1-888-INTERSIL or www.intersil.com/tsc

## TW2836

4-Channel Video QUAD/MUX Controller for Security Applications

FN7741 Rev. 1.00 July 2, 2012

DATASHEET

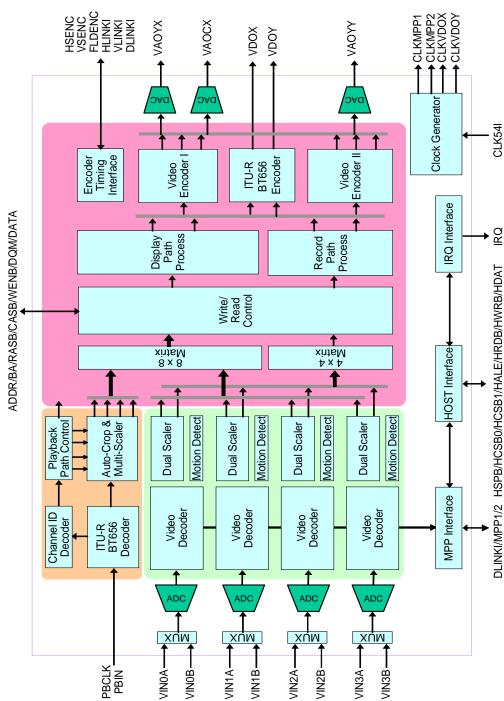

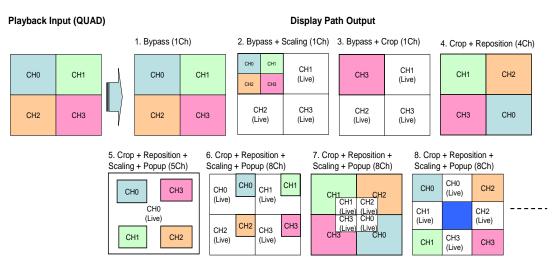

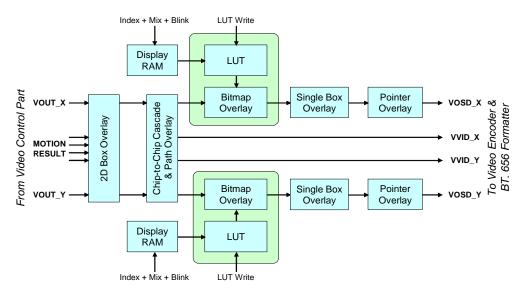

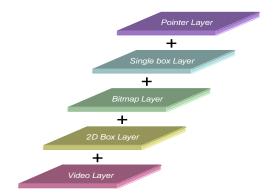

The TW2836 has four high quality NTSC/PAL video decoders, dual color display controllers and dual video encoders. The TW2836 contains four built-in analog anti-aliasing filters, four 10 bit Analog-to-Digital converters, and proprietary digital gain/clamp controller, high quality Y/C separator to reduce cross-noise and high performance free scaler. Four built-in motion, blind and night detectors can increase the security system feature. The TW2836 has flexible video display/record/playback controller, including basic display and MUX functions. The TW2836 also has an excellent graphic overlay function that displays bitmap for OSD, single box, 2D array box, and mouse pointer. The built-in channel ID CODEC allows auto decoding and displaying during playback and the additional scaler on the playback supports multi-cropping function of the same field or frame image. The TW2836 contains two video encoders with three 10 bit Digital-to-Analog converters to provide 2 composite or S-video. The TW2836 can be extended up to 8/16 channel video controller using chip-to-chip cascade connection.

## **Features**

#### Four Video Decoders

- Accepts all NTSC(M/N/4.43) / PAL(B/D/G/H/I/K/L/M/N/60) standards with auto detection

- Integrated four video analog anti-aliasing filters and 10 bit CMOS ADCs

- High performance adaptive 4H comb filters for all NTSC/PAL standards

- IF compensation filter for improvement of color demodulation

- Color Transient Improvement (CTI)

- Automatic white peak control

- Programmable hue, saturation, contrast, brightness and sharpness

- High performance horizontal and vertical scaler for each path including playback input

- Fast video locking system for non-realtime application

- Four built-in motion detectors with 16X12 cells and blind and night detectors

- Additional digital input for playback with ITU-R BT.656 standard

- Auto cropping / strobe for playback input with Channel ID decoder

- Supports four channel full D1 record mode

### **Dual Video Controllers**

- Supports full triplex function with 4ch live, 4ch playback display and 4ch record output

- Analog/Digital channel ID CODEC for record and playback application

- Supports adaptive median filter for Record

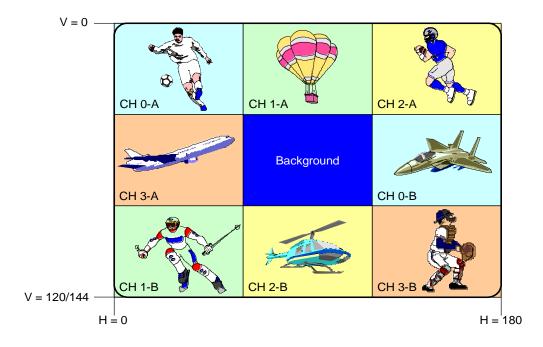

- Supports pseudo 8 channel and/or dual page mode

- Horizontal/Vertical mirroring for each channel

- Last image captured when video-loss detected

- Auto sequence switch with 128 queues and/or manual switch by interrupt for record path

- Channel skip in auto sequence switch for record path when video-loss detected

- Image enhancement for zoomed or still image in display path

- High performance 2X zoom to horizontal

- Extendable up to 8/16 channel video controller using cascade connection

- Quad MUX switch with 32 queues and/or manual control by interrupt for record path

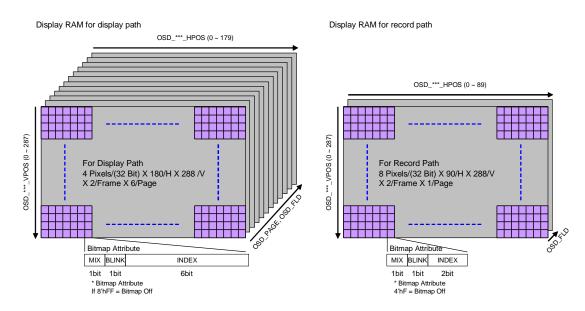

- 64 color bitmap OSD overlay with 720x480 in NTSC / 720x588 resolution in PAL

- Four programmable single boxes and four 2D arrayed boxes overlay

- Mouse pointer overlay

#### **Dual Video Encoders**

- Dual path digital outputs with ITU-R BT.656 standard

- Dual path analog outputs with all analog NTSC/PAL standards

- Programmable bandwidth of luminance and chrominance signal for each path

- Three 10 bit video CMOS DACs

and vertical direction for display path

## Applications

- Analog QUAD/MUX System

- 4/8/16 Channel DVR System

- Car Rear Vision System

- Hair Shop System

- Dental Care System

VIN1B-

RENESAS

VIN2B-

VIN3B-

VIN0B-

## **Block Diagram**

| Ordering Information   |                 |                      |  |  |  |  |  |  |  |

|------------------------|-----------------|----------------------|--|--|--|--|--|--|--|

| PART<br>NUMBER         | PART<br>MARKING | PACKAGE<br>(Pb-free) |  |  |  |  |  |  |  |

| TW2836-BA1-GR (Note 1) | TW2836 DABA1-GR | 256 Ld LBGA          |  |  |  |  |  |  |  |

| TW2836-PA1-GE (Note 2) | TW2836 DAPA1-GE | 208 Ld PQFP          |  |  |  |  |  |  |  |

NOTE:

- These Intersil Pb-free WLCSP and BGA packaged products employ special Pb-free material sets; molding compounds/die attach materials and SnAgCu - e1 solder ball terminals, which are RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free WLCSP and BGA packaged products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

- 2. These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

## Table of Contents

| Pin Descriptions                                                                                                                                   | 8                                                                                                                                |

|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| Pin Diagram                                                                                                                                        | 14                                                                                                                               |

| Functional Description                                                                                                                             |                                                                                                                                  |

| Video Input                                                                                                                                        |                                                                                                                                  |

| Analog Video Input                                                                                                                                 |                                                                                                                                  |

| Anti-aliasing Filter                                                                                                                               |                                                                                                                                  |

| Analog-to-Digital Converter                                                                                                                        | 19                                                                                                                               |

| Sync Processing                                                                                                                                    |                                                                                                                                  |

| Color Decoding                                                                                                                                     | 21                                                                                                                               |

| Luminance Processing                                                                                                                               |                                                                                                                                  |

| Chrominance Processing                                                                                                                             |                                                                                                                                  |

| Realtime Record Mode                                                                                                                               |                                                                                                                                  |

| Digital Video Input                                                                                                                                |                                                                                                                                  |

| Digital Video Input Format                                                                                                                         |                                                                                                                                  |

| Channel ID Decoder                                                                                                                                 |                                                                                                                                  |

| Cropping and Scaling Function                                                                                                                      |                                                                                                                                  |

| Cropping Function for Live                                                                                                                         |                                                                                                                                  |

| Scaling Function for Live                                                                                                                          |                                                                                                                                  |

| Cropping and Scaling Function for Playback                                                                                                         |                                                                                                                                  |

| Motion Detection                                                                                                                                   |                                                                                                                                  |

| Mask and Detection Region Selection                                                                                                                |                                                                                                                                  |

|                                                                                                                                                    |                                                                                                                                  |

| Sensitivity Control                                                                                                                                |                                                                                                                                  |

| Sensitivity Control<br>Level Sensitivity                                                                                                           |                                                                                                                                  |

| -                                                                                                                                                  |                                                                                                                                  |

| Level Sensitivity                                                                                                                                  |                                                                                                                                  |

| Level Sensitivity                                                                                                                                  |                                                                                                                                  |

| Level Sensitivity<br>Spatial Sensitivity<br>Temporal Sensitivity                                                                                   |                                                                                                                                  |

| Level Sensitivity<br>Spatial Sensitivity<br>Temporal Sensitivity<br>Velocity Control                                                               |                                                                                                                                  |

| Level Sensitivity<br>Spatial Sensitivity<br>Temporal Sensitivity<br>Velocity Control<br>Blind Detection                                            |                                                                                                                                  |

| Level Sensitivity<br>Spatial Sensitivity<br>Temporal Sensitivity<br>Velocity Control<br>Blind Detection<br>Night Detection                         |                                                                                                                                  |

| Level Sensitivity<br>Spatial Sensitivity<br>Temporal Sensitivity<br>Velocity Control<br>Blind Detection<br>Night Detection<br><b>Video Control</b> | 38<br>38<br>38<br>38<br>38<br>39<br>41<br>41<br>41<br>41<br>41<br>42<br>43                                                       |

| Level Sensitivity                                                                                                                                  |                                                                                                                                  |

| Level Sensitivity                                                                                                                                  |                                                                                                                                  |

| Level Sensitivity                                                                                                                                  |                                                                                                                                  |

| Level Sensitivity                                                                                                                                  | 38<br>38<br>38<br>38<br>38<br>39<br>41<br>41<br>41<br>41<br>41<br>41<br>42<br>43<br>43<br>44<br>44<br>44<br>44<br>44             |

| Level Sensitivity                                                                                                                                  |                                                                                                                                  |

| Level Sensitivity                                                                                                                                  |                                                                                                                                  |

| Level Sensitivity                                                                                                                                  | 38<br>38<br>38<br>38<br>38<br>39<br>41<br>41<br>41<br>41<br>42<br>43<br>44<br>44<br>44<br>44<br>45<br>45<br>47<br>51<br>51<br>51 |

| Last Image Captured                         |    |

|---------------------------------------------|----|

| Horizontal / Vertical Mirroring             |    |

| Field to Frame Conversion                   |    |

| Display Path Control                        | 53 |

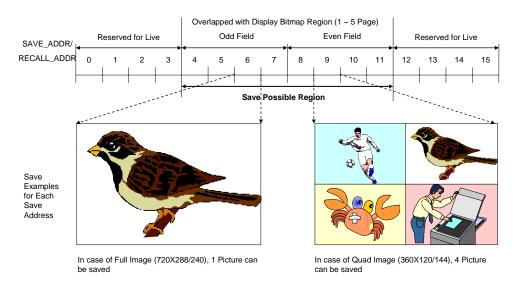

| Save and Recall Function                    | 53 |

| Image Enhancement                           | 54 |

| Zoom Function                               | 54 |

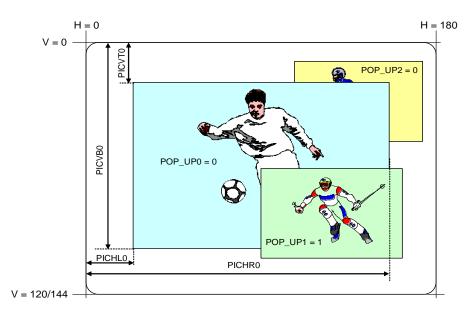

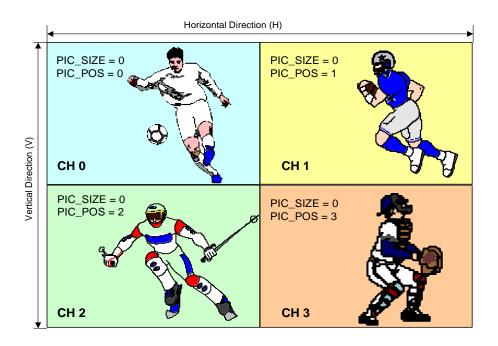

| Picture Size and Popup Control              | 55 |

| Full Triplex Function                       | 56 |

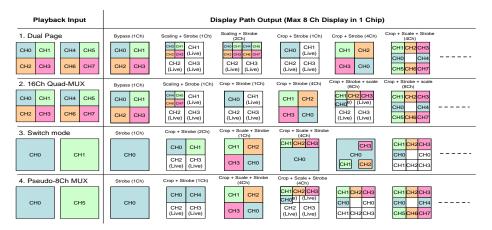

| Playback Path Control                       | 57 |

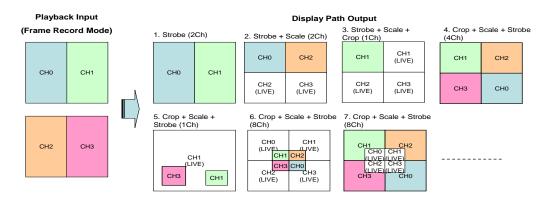

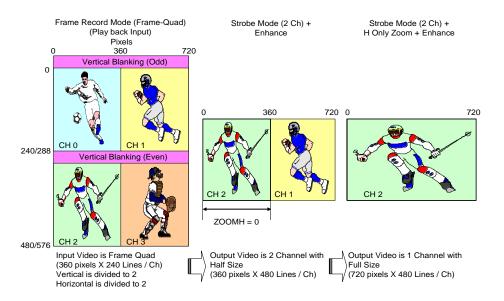

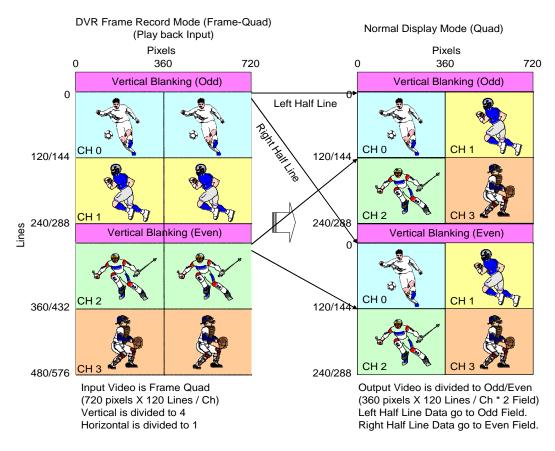

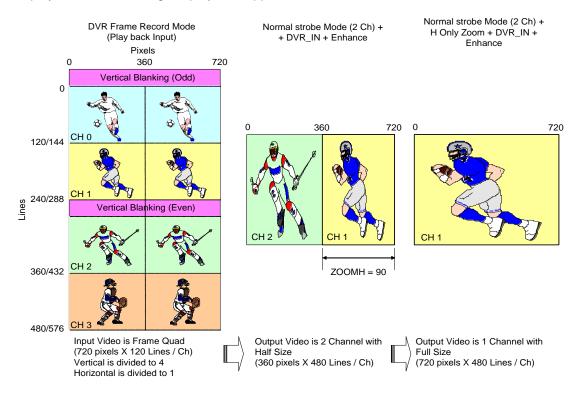

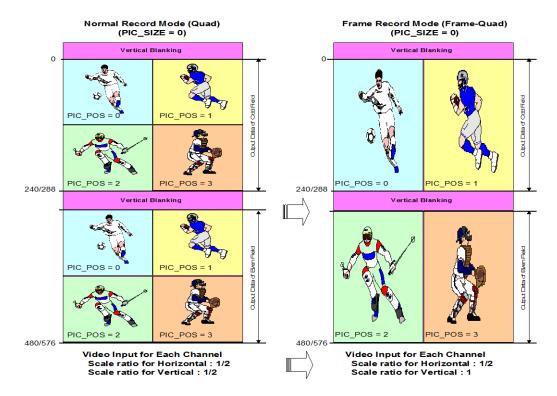

| Frame Record Mode                           | 59 |

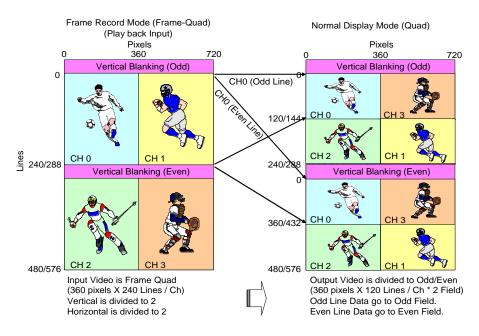

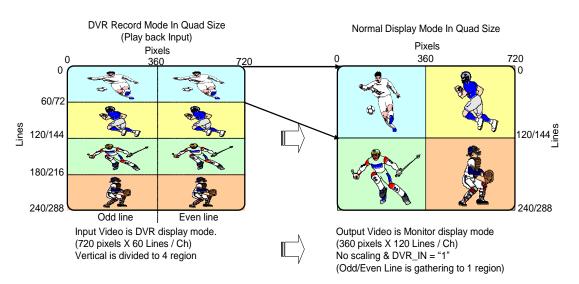

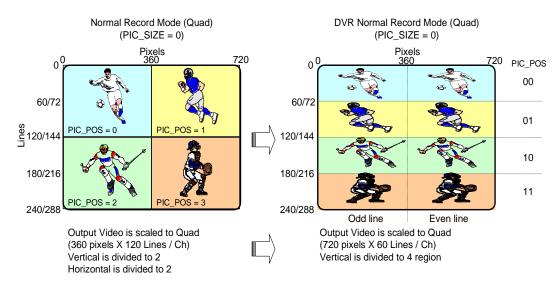

| DVR Normal Record Mode                      | 61 |

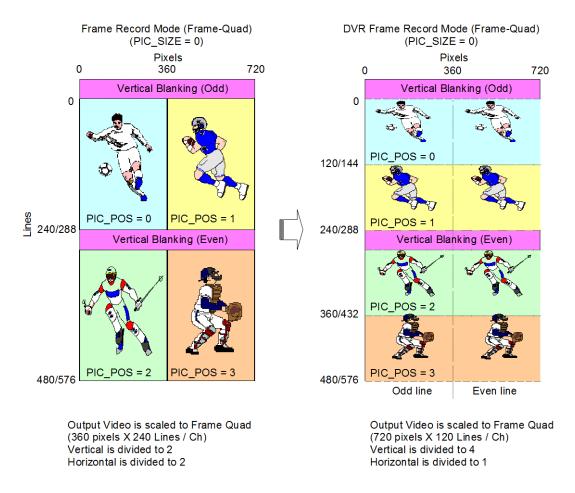

| DVR Frame Record Mode                       | 62 |

| Record Path Control                         | 64 |

| Normal Record Mode                          | 65 |

| Frame Record Mode                           | 66 |

| DVR Normal Record Mode                      | 67 |

| DVR Frame Record Mode                       | 68 |

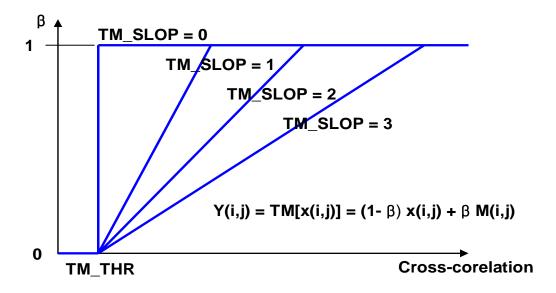

| Noise Reduction                             | 69 |

| Channel ID Encoder                          | 70 |

| Channel ID Information                      | 70 |

| Analog Type Channel ID in VBI               | 73 |

| Digital Type Channel ID in VBI              | 74 |

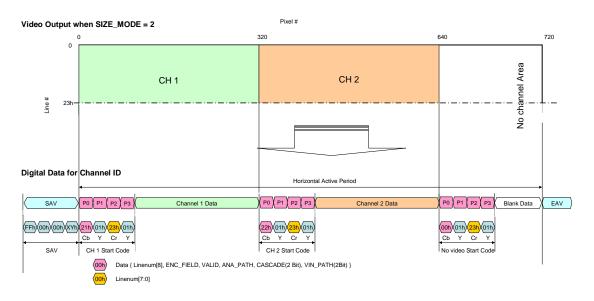

| Digital Type Channel ID in Channel Boundary | 75 |

| Chip-to-Chip Cascade Operation              | 76 |

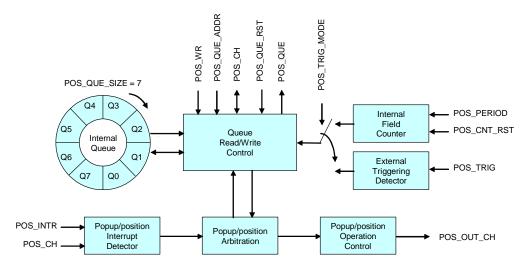

| Channel Priority Control                    | 76 |

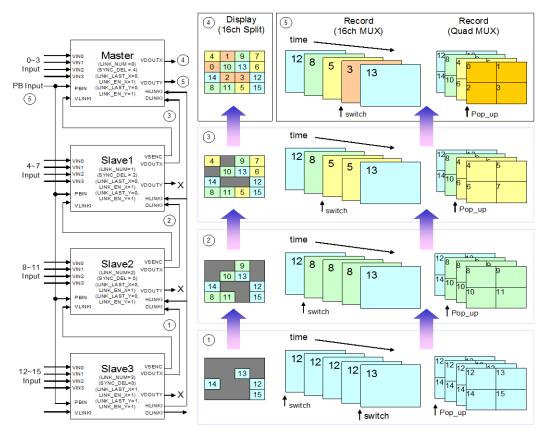

| 120 CIF/Sec Record Mode                     | 78 |

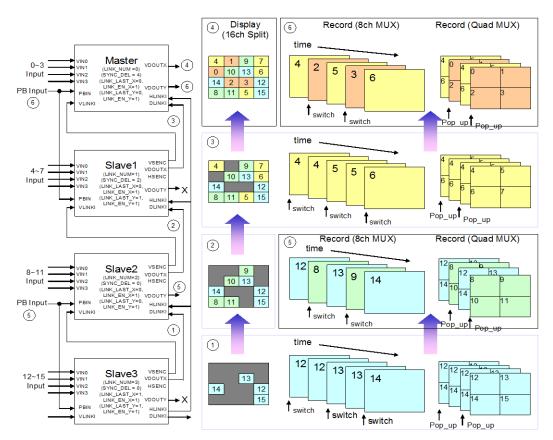

| 240 CIF/Sec Record Mode                     | 79 |

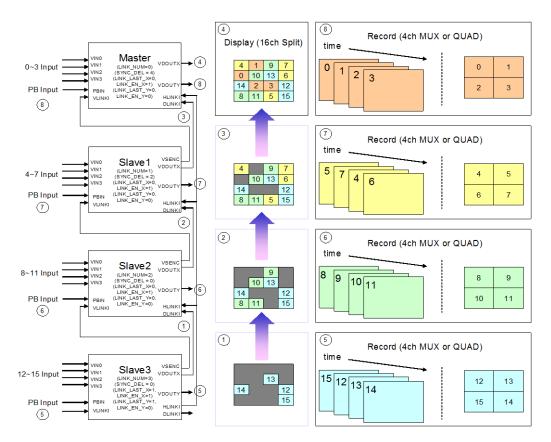

| 480 CIF/Sec Record Mode                     |    |

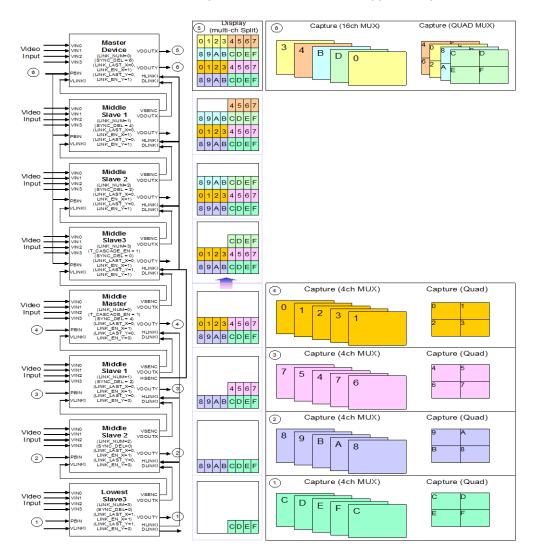

| Infinite Cascade Mode for Display Path      |    |

| OSD (On Screen Display) Control             |    |

| 2 Dimensional Arrayed Box                   |    |

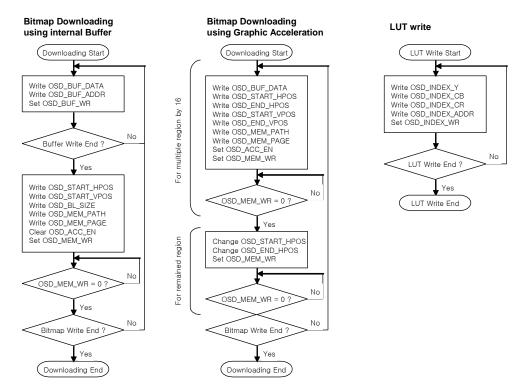

| Bitmap Overlay                              |    |

| Single Box                                  |    |

| Mouse Pointer                               |    |

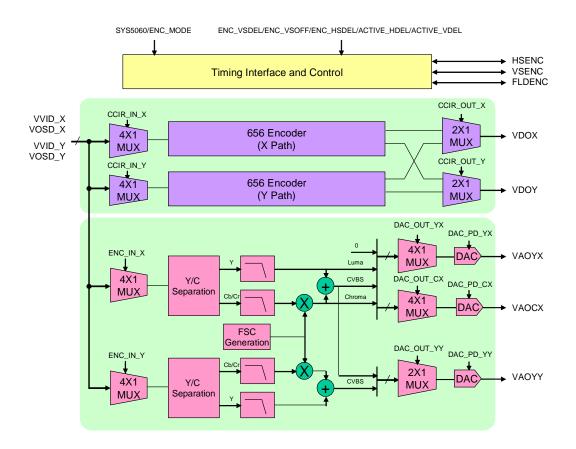

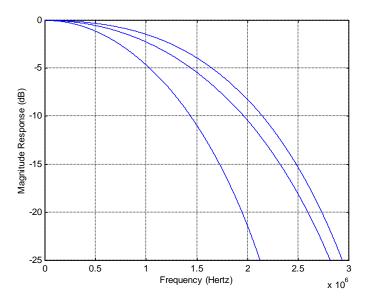

| Video Output                                | 90 |

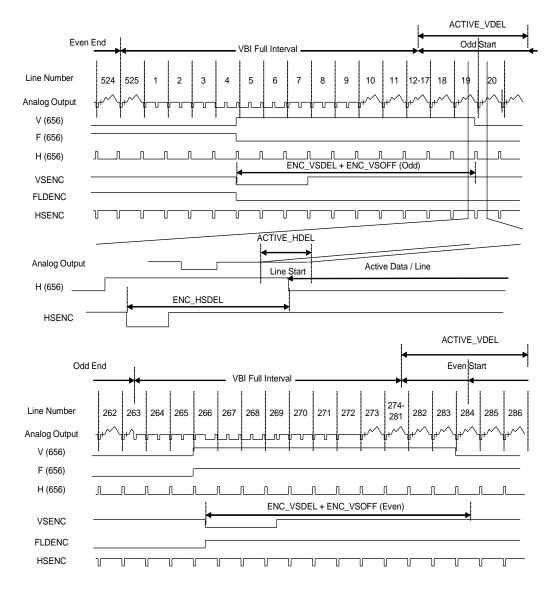

| Timing Interface and Control                | 91 |

| Analog Video Output                         |    |

| Output Standard Selection                   |    |

| Luminance Filter                            | 94 |

| Chrominance Filter                          | 94 |

| Digital-to-Analog Converter                 |    |

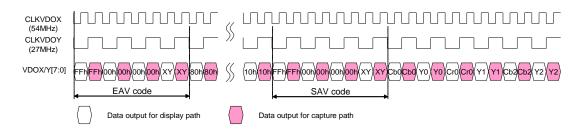

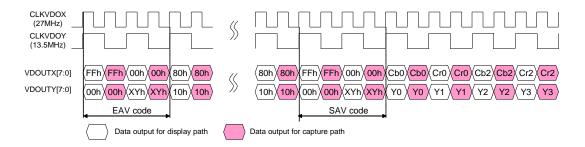

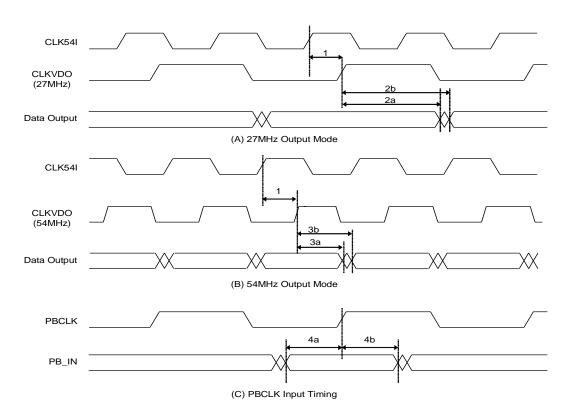

| Digital Video Output     | 96  |

|--------------------------|-----|

| Single Output Mode       | 97  |

| Dual Output Mode         | 98  |

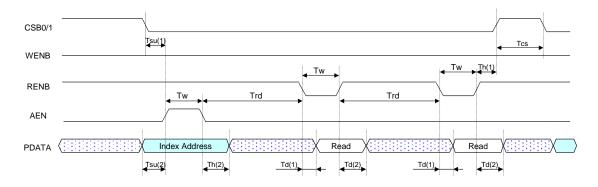

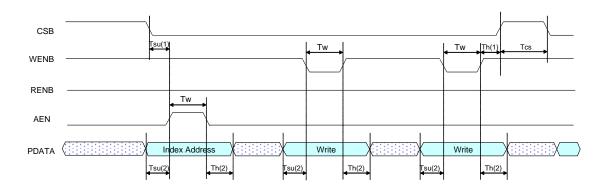

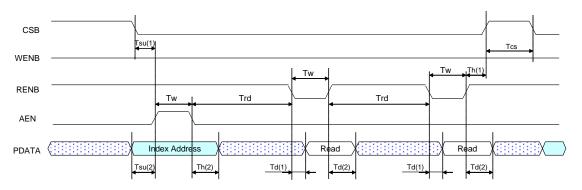

| Host Interface           | 99  |

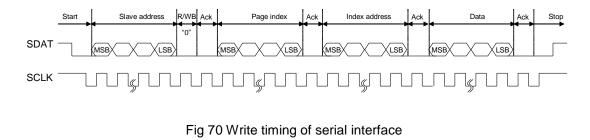

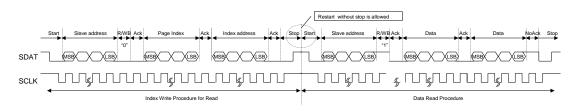

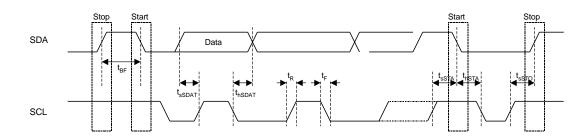

| Serial Interface         | 100 |

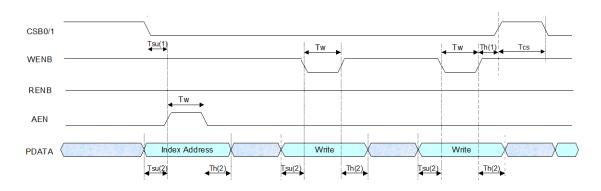

| Parallel Interface       | 102 |

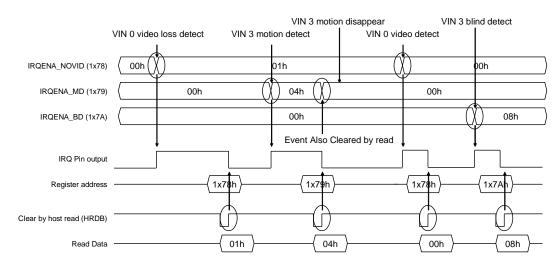

| Interrupt Interface      | 104 |

| MPP Pin Interface        | 105 |

| Control Register         | 106 |

| Register Map             | 106 |

| Recommended Value        | 115 |

| Register Description     | 120 |

| Parametric Information   | 231 |

| DC Electrical Parameters | 231 |

| AC Electrical Parameters | 233 |

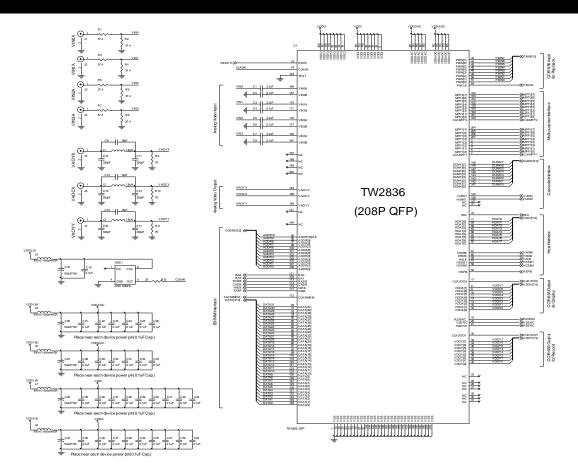

| Application Schematic    | 237 |

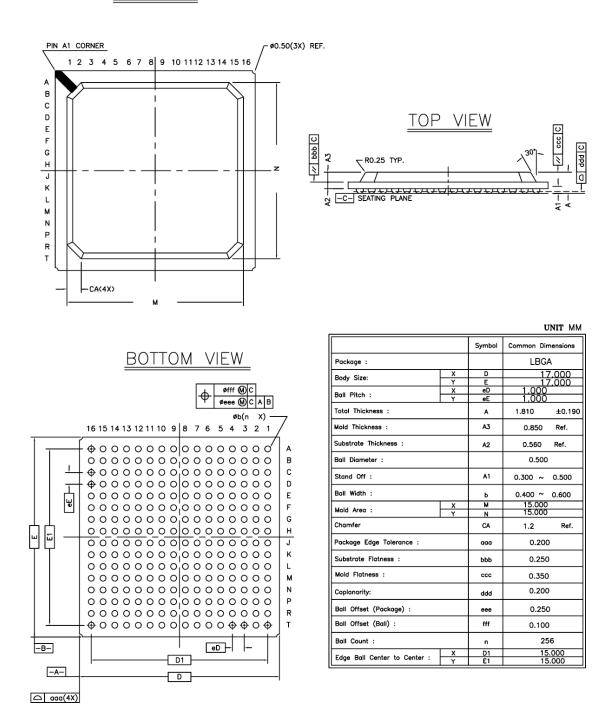

| Package Dimension        | 238 |

| Revision History         | 240 |

## **Pin Descriptions**

Analog Interface Pins

| Name  | Nun | nber | Turne | Description                           |  |

|-------|-----|------|-------|---------------------------------------|--|

| Name  | QFP | LBGA | Туре  | Description                           |  |

| VIN0A | 166 | B12  | А     | Composite video input A of channel 0. |  |

| VIN0B | 167 | C12  | А     | Composite video input B of channel 0. |  |

| VIN1A | 170 | B11  | А     | Composite video input A of channel 1. |  |

| VIN1B | 171 | C11  | А     | Composite video input B of channel 1. |  |

| VIN2A | 176 | B10  | А     | Composite video input A of channel 2. |  |

| VIN2B | 177 | C10  | А     | Composite video input B of channel 2. |  |

| VIN3A | 180 | B9   | А     | Composite video input A of channel 3. |  |

| VIN3B | 181 | C9   | А     | Composite video input B of channel 3. |  |

| VAOYX | 184 | C8   | А     | Analog video output.                  |  |

| VAOCX | 186 | D8   | А     | Analog video output.                  |  |

| VAOYY | 189 | C7   | А     | Analog video output.                  |  |

| NC    | 191 | D7   | А     | No connection.                        |  |

| NC    | 197 | B6   | А     | No connection.                        |  |

| NC    | 198 | C6   | А     | No connection.                        |  |

| NC    | 199 | B5   | А     | No connection.                        |  |

| NC    | 200 | C5   | А     | No connection.                        |  |

| NC    | 194 | D5   | Α     | No connection.                        |  |

#### **Digital Video Interface Pins**

| Nomo       | Name                                |                                     | Tuno | Description                                                                              |  |  |

|------------|-------------------------------------|-------------------------------------|------|------------------------------------------------------------------------------------------|--|--|

| Name       | QFP                                 | LBGA                                | Туре | Description                                                                              |  |  |

| VDOX [7:0] | 8,9,<br>10,11,<br>13,14,<br>15,16   | C1,C2,<br>D2,D3,<br>E1,E2,<br>E3,E4 | 0    | Digital video data output for display path.<br>Or link signal for multi-chip connection. |  |  |

| VDOY [7:0] | 33,34,<br>36,37,<br>38,39,<br>40,42 | J4,K2,<br>K3,L1,<br>L2,L3,<br>L4,M1 | ο    | Digital video data output for record path.                                               |  |  |

| CLKVDOX    | 17                                  | F1                                  | 0    | Clock output for VDOUTX.                                                                 |  |  |

| CLKVDOY    | 32                                  | J3                                  | 0    | Clock output for VDOUTY                                                                  |  |  |

| HSENC      | 21                                  | F4                                  | 0    | Encoder horizontal sync.                                                                 |  |  |

| VSENC      | 20                                  | F3                                  | 0    | Encoder vertical sync.<br>Or link signal for multi-chip connection.                      |  |  |

| FLDENC     | 19                                  | F2                                  | 0    | Encoder field flag.                                                                      |  |  |

| PBDIN[7:0] | 43,44,<br>45,46,<br>48,49,<br>50,51 | M2,M3,<br>M4,N2,<br>N3,P1,<br>P2,R1 | I    | Video data of playback input.                                                            |  |  |

| PBCLK      | 54                                  | R2                                  | I    | Clock of playback input.                                                                 |  |  |

| NC         | 27                                  | H3                                  | 0    | No connection.                                                                           |  |  |

| NC         | 26                                  | H2                                  | 0    | No connection.                                                                           |  |  |

| NC         | 25                                  | H1                                  | 0    | No connection.                                                                           |  |  |

| NC         | 23                                  | G3                                  | 0    | No connection.                                                                           |  |  |

| NC         | 31                                  | J2                                  | I    | No connection.                                                                           |  |  |

| NC         | 30                                  | J1                                  | I    | No connection.                                                                           |  |  |

| NC         | 28                                  | H4                                  | I    | No connection.                                                                           |  |  |

| NC         | 137                                 | F15                                 | I    | No connection.                                                                           |  |  |

| NC         | 22                                  | G2                                  | 0    | No connection.                                                                           |  |  |

#### Multi-purpose Pins

| Name        | Nun                                         | nber | Turne | Description                                                                                                                                            |  |

|-------------|---------------------------------------------|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| INAITIE     | QFP                                         | LBGA | Туре  | Description                                                                                                                                            |  |

| HLINKI      | 138                                         | F14  | I/O   | Link signal for multi-chip connection.                                                                                                                 |  |

| VLINKI      | 140                                         | F13  | Ι     | Link signal for multi-chip connection.                                                                                                                 |  |

| DLINKI[7:0] | 149,148,<br>147,146,<br>144,143,<br>142,141 |      | I/O   | Link signal for multi-chip connection.<br>Or decoder's bypassed data output.<br>Or decoder's timing signal output.<br>Or general purpose input/output. |  |

| MPP1[7:0]   | 204,205,<br>206,207,<br>2,3,<br>4,5         |      | I/O   | Decoder's bypassed data output.<br>Or decoder's timing signal output.<br>Or general purpose input/output.                                              |  |

| MPP2[7:0]   | 152,153,<br>154,155,<br>158,159,<br>160,161 |      | I/O   | Decoder's bypassed data output.<br>Or decoder's timing signal output.<br>Or general purpose input/output.                                              |  |

| CLKMPP1     | 7                                           | B1   | 0     | Clock output for MPP1 data.                                                                                                                            |  |

| CLKMPP2     | 150                                         | C14  | 0     | Clock output for MPP2 data.                                                                                                                            |  |

#### **Memory Interface Pins**

| Name       | Number                                                               |                                                                 | Туре | Description                        |  |

|------------|----------------------------------------------------------------------|-----------------------------------------------------------------|------|------------------------------------|--|

| Name       | QFP                                                                  | LBGA                                                            | туре | Description                        |  |

| DATA[31:0] | 120,121,<br>123,124,<br>125,126,<br>127,129,<br>130,131,<br>132,134, |                                                                 | I/O  | SDRAM data bus.                    |  |

| ADDR[10:0] | 97,98,<br>100,101,<br>102,103,                                       | N12,R13,<br>P13,T14,<br>R14,P14,<br>T15,R15,<br>R16,P16,<br>P15 | 0    | SDRAM address bus. ADDR[10] is AP. |  |

| BA1        | 109                                                                  | N15                                                             | 0    | SDRAM bank1 selection.             |  |

| BA0        | 111                                                                  | N14                                                             | 0    | SDRAM bank0 selection.             |  |

| RASB       | 113                                                                  | M15                                                             | 0    | SDRAM row address selection.       |  |

| CASB       | 114                                                                  | M14                                                             | 0    | SDRAM column address selection.    |  |

| WEB        | 115                                                                  | M13                                                             | 0    | SDRAM write enable.                |  |

| DQM        | 117                                                                  | L16                                                             | 0    | SDRAM write mask.                  |  |

| CLK54MEM   | 112                                                                  | M16                                                             | 0    | SDRAM clock.                       |  |

#### **System Control Pins**

| Nomo      | Name                                |                                     | Tuno | Description                                                                                                                                  |

|-----------|-------------------------------------|-------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------|

| Name      | QFP                                 | LBGA                                | Туре | Description                                                                                                                                  |

| TEST      | 164                                 | D12                                 | I    | Only for the test purpose.<br>Must be connected to VSSO.                                                                                     |

| RSTB      | 73                                  | P7                                  | I    | System reset. Active low.                                                                                                                    |

| IRQ       | 72                                  | R7                                  | 0    | Interrupt request signal.                                                                                                                    |

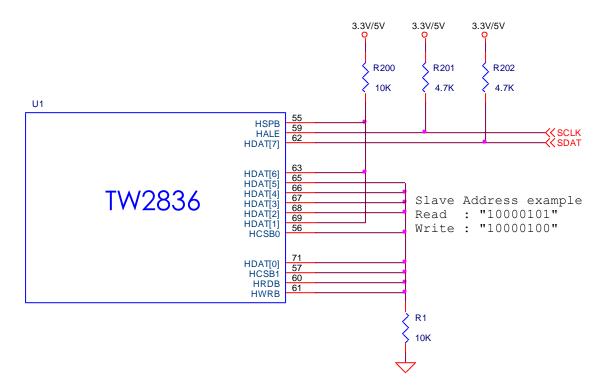

| HDAT[7:0] | 62,63,<br>65,66,<br>67,68,<br>69,71 | T5,R5,<br>P5,N5,<br>T6,R6,<br>P6,N6 | I/O  | Data bus for parallel interface.<br>HDAT[7] is serial data for serial interface.<br>HDAT[6:1] is slave address[6:1] for serial<br>interface. |

| HWRB      | 61                                  | P4                                  | I    | Write enable for parallel interface.<br>VSSO for serial interface.                                                                           |

| HRDB      | 60                                  | R4                                  | I    | Read enable for parallel interface.<br>VSSO for serial interface.                                                                            |

| HALE      | 59                                  | P3                                  | I    | Address line enable for parallel interface.<br>Serial clock for serial interface.                                                            |

| HCSB1     | 57                                  | R3                                  | I    | Chip select 1 for parallel interface.<br>VSSO for serial interface.                                                                          |

| HCSB0     | 56                                  | Т3                                  | I    | Chip select 0 for parallel interface.<br>Slave address[0] for serial interface.                                                              |

| HSPB      | 55                                  | T2                                  | I    | Select serial/parallel host interface.                                                                                                       |

| CLK54I    | 74                                  | Т8                                  | I    | 54MHz system clock.                                                                                                                          |

#### **Power / Ground Pins**

| Name   | Nun                                                                                                      | nber                                                                                           | Туре | Description                            |  |  |

|--------|----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|------|----------------------------------------|--|--|

| Name   | QFP                                                                                                      | LBGA                                                                                           | туре | Description                            |  |  |

| VDDO   | 18,47,<br>64,93,<br>110,139,<br>157,208                                                                  | A1,A16,<br>K1,K16,<br>T1,T7,<br>T10,T16                                                        | Ρ    | Digital power for output driver 3.3V.  |  |  |

| VDDI   | 6,24,<br>41,58,<br>99,116,<br>133,151,                                                                   | D1,D16,<br>G1,G16,<br>N1,N16,<br>T4,T13                                                        | Ρ    | Digital power for internal logic 1.8V. |  |  |

| VDDADC | 165,172,<br>173,175,<br>182                                                                              | A8,A9,<br>A10,A11,<br>A12                                                                      | Ρ    | Analog power for ADC 1.8V.             |  |  |

| VSSADC | 168,169,<br>174,178,<br>179                                                                              | D10,D11,<br>D13,E11,<br>E12                                                                    | G    | Analog ground for ADC 1.8V.            |  |  |

| VDDDAC | 185,187,<br>190,193,<br>201                                                                              | A5,A6,<br>A7,B7,<br>B8                                                                         | Ρ    | Analog power for DAC 1.8V.             |  |  |

| VSSDAC | 183,188,<br>192,195,<br>196                                                                              | D4,D6,<br>D9,E5,<br>E6,E7,<br>E8,E9,<br>E10                                                    | G    | Analog ground for DAC 1.8V.            |  |  |

| VSS    | 1,12,<br>29,35,<br>52,53,<br>70,75,<br>81,87,<br>104,105,<br>122,128,<br>145,156,<br>162,163,<br>202,203 | F5~F12,<br>G4~G13,<br>H5~H12,<br>J5~J12,<br>K4~K13,<br>L5~L12,<br>M5~M12,<br>N4,N7,<br>N10,N13 | G    | Ground.                                |  |  |

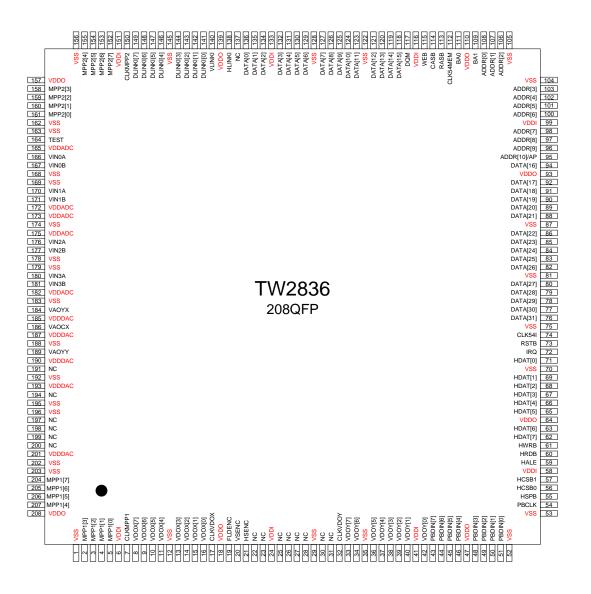

## Pin Diagram

208 QFP Pin Diagram (Top -> Bottom View)

#### 256 LBGA Pin Diagram (Top->Bottom View)

|    | A           | В           | С             | D             | Е             | F           | G           | Н           | J            | К            | L            | М            | Ν               | Ρ            | R            | Т            |    |

|----|-------------|-------------|---------------|---------------|---------------|-------------|-------------|-------------|--------------|--------------|--------------|--------------|-----------------|--------------|--------------|--------------|----|

| 16 | VDDO        | MPP2<br>[7] | DLINKI<br>[6] | VDDI          | DLINKI<br>[0] | DATA<br>[0] | VDDI        | DATA<br>[6] | DATA<br>[10] | VDDO         | DQM          | CLK<br>54MEM | VDDI            | ADDR<br>[1]  | ADDR<br>[2]  | VDDO         | 16 |

| 15 | MPP2<br>[5] | MPP2<br>[6] | DLINKI<br>[7] | DLINKI<br>[4] | DLINKI<br>[1] | NC          | DATA<br>[2] | DATA<br>[5] | DATA<br>[9]  | DATA<br>[12] | DATA<br>[15] | RASB         | BA1             | ADDR<br>[0]  | ADDR<br>[3]  | ADDR<br>[4]  | 15 |

| 14 | MPP2<br>[4] | MPP2<br>[3] | CLK<br>MPP2   | DLINKI<br>[5] | DLINKI<br>[2] | HLINKI      | DATA<br>[1] | DATA<br>[4] | DATA<br>[8]  | DATA<br>[11] | DATA<br>[14] | CASB         | BA0             | ADDR<br>[5]  | ADDR<br>[6]  | ADDR<br>[7]  | 14 |

| 13 | MPP2<br>[2] | MPP2<br>[1] | MPP2<br>[0]   | VSS           | DLINKI<br>[3] | VLINKI      | VSS         | DATA<br>[3] | DATA<br>[7]  | VSS          | DATA<br>[13] | WEB          | VSS             | ADDR<br>[8]  | ADDR<br>[9]  | VDDI         | 13 |

| 12 | VDD<br>ADC  | VINOA       | VINOB         | TEST          | VSS           | VSS         | VSS         | VSS         | VSS          | VSS          | VSS          | VSS          | ADDR<br>[10]/AP | DATA<br>[16] | DATA<br>[17] | DATA<br>[18] | 12 |

| 11 | VDD<br>ADC  | VIN1A       | VIN1B         | VSS           | VSS           | VSS         | VSS         | VSS         | VSS          | VSS          | VSS          | VSS          | DATA<br>[19]    | DATA<br>[20] | DATA<br>[21] | DATA<br>[22] | 11 |

| 10 | VDD<br>ADC  | VIN2A       | VIN2B         | VSS           | VSS           | VSS         | VSS         | VSS         | VSS          | VSS          | VSS          | VSS          | VSS             | DATA<br>[23] | DATA<br>[24] | VDDO         | 10 |

| 9  | VDD<br>ADC  | VIN3A       | VIN3B         | VSS           | VSS           | VSS         | VSS         | VSS         | VSS          | VSS          | VSS          | VSS          | DATA<br>[25]    | DATA<br>[26] | DATA<br>[27] | DATA<br>[28] | 9  |

| 8  | VDD<br>ADC  | VDD<br>DAC  | VAOYX         | VAOCX         | VSS           | VSS         | VSS         | VSS         | VSS          | VSS          | VSS          | VSS          | DATA<br>[29]    | DATA<br>[30] | DATA<br>[31] | CLK54I       | 8  |

| 7  | VDD<br>DAC  | VDD<br>DAC  | VAOYY         | NC            | VSS           | VSS         | VSS         | VSS         | VSS          | VSS          | VSS          | VSS          | VSS             | RSTB         | IRQ          | VDDO         | 7  |

| 6  | VDD<br>DAC  | NC          | NC            | VSS           | VSS           | VSS         | VSS         | VSS         | VSS          | VSS          | VSS          | VSS          | HDAT<br>[0]     | HDAT<br>[1]  | HDAT<br>[2]  | HDAT<br>[3]  | 6  |

| 5  | VDD<br>DAC  | NC          | NC            | NC            | VSS           | VSS         | VSS         | VSS         | VSS          | VSS          | VSS          | VSS          | HDAT<br>[4]     | HDAT<br>[5]  | HDAT<br>[6]  | HDAT<br>[7]  | 5  |

| 4  | MPP1<br>[7] | MPP1<br>[6] | MPP1<br>[5]   | VSS           | VDOX<br>[0]   | HS<br>ENC   | VSS         | NC          | VDOY<br>[7]  | VSS          | VDOY<br>[1]  | PBDIN<br>[5] | VSS             | HWRB         | HRDB         | VDDI         | 4  |

| 3  | MPP1<br>[4] | MPP1<br>[3] | MPP1<br>[2]   | VDOX<br>[4]   | VDOX<br>[1]   | VS<br>ENC   | NC          | NC          | CLK<br>VDOY  | VDOY<br>[5]  | VDOY<br>[2]  | PBDIN<br>[6] | PBDIN<br>[3]    | HALE         | HCSB1        | HCSB0        | 3  |

| 2  | MPP1<br>[1] | MPP1<br>[0] | VDOX<br>[6]   | VDOX<br>[5]   | VDOX<br>[2]   | FLD<br>ENC  | NC          | NC          | NC           | VDOY<br>[6]  | VDOY<br>[3]  | PBDIN<br>[7] | PBDIN<br>[4]    | PBDIN<br>[1] | PB<br>CLK    | HSPB         | 2  |

| 1  | VDDO        | CLK<br>MPP1 | VDOX<br>[7]   | VDDI          | VDOX<br>[3]   | CLK<br>VDOX | VDDI        | NC          | NC           | VDDO         | VDOY<br>[4]  | VDOY<br>[0]  | VDDI            | PBDIN<br>[2] | PBDIN<br>[0] | VDDO         | 1  |

|    | Α           | В           | С             | D             | Е             | F           | G           | Н           | J            | к            | L            | М            | N               | Р            | R            | т            | /  |

## **Functional Description**

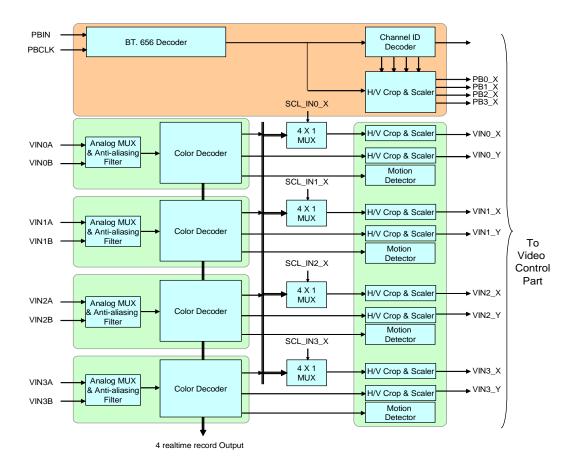

#### Video Input

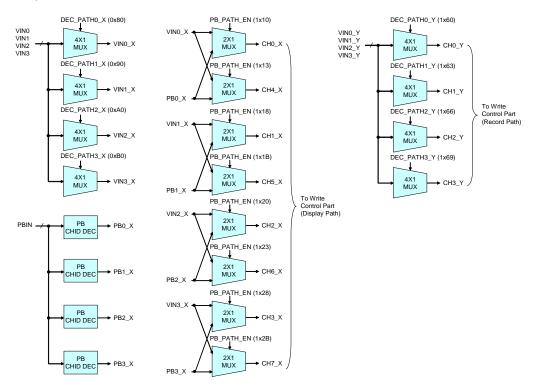

The TW2836 has 5 input interfaces that consist of 1 digital video input and 4 analog composite video inputs. Four analog video inputs are converted to digital video stream through 10 bits ADC and luminance/chrominance processor in built-in four video decoders. One digital input for playback application are decoded by internal ITU-R BT656 decoder and then fed to video control part and channel ID decoder. Each built-in video decoder has its own motion detector and dual scaler. Four additional scalers are also embedded for playback display application. The structure of video input is shown in the following Fig 1.

Fig 1 The structure of video input

#### TW2836

For the special 4ch real-time record application, the TW2836 supports 4 realtime video decoder outputs through the multi-purpose output pins (MPP1[7:0] and MPP2[7:0]).

#### **Analog Video Input**

The TW2836 supports all NTSC/PAL video standards for analog input and contains automatic standard detection circuit. Automatic standard detection can be overridden by writing the value into the IFMTMAN and IFORMAT (0x01, 0x11, 0x21, and 0x31) registers. Even if video loss is detected, the TW2836 can be forced to free-running in a particular video standard mode by IFORMAT register. The Table 1 shows the video input standards supported by TW2836.

| IFORMAT | PEDEST | Format     | Line/Fv (Hz) | Fh (KHz) | Fsc (MHz)  |  |

|---------|--------|------------|--------------|----------|------------|--|

| 0       | 0      | PAL-BDGHI  | 625/50       | 15.625   | 4.43361875 |  |

| 0       | 1      | PAL-N*     | 625/50       | 15.625   | 4.43301075 |  |

| 1       | 1      | PAL-M*     | 525/59.94    | 15.734   | 3.57561149 |  |

| 2       | 0      | PAL-NC     | 625/50       | 15.625   | 3.58205625 |  |

| 3       | 0      | PAL-60     | 525/59.94    | 15.734   | 4.43361875 |  |

| 4       | 0      | NTSC-J     | 525/59.94    | 15.734   | 2 570545   |  |

| 4       | 4 1    |            | 525/59.94    | 15.754   | 3.579545   |  |

| 5       | 1      | NTSC-4.43* | 525/59.94    | 15.734   | 4.43361875 |  |

| 6       | 0      | NTSC-N     | 625/50       | 15.625   | 3.579545   |  |

Table 1 Video input standards

Notes: \* 7.5 IRE Setup

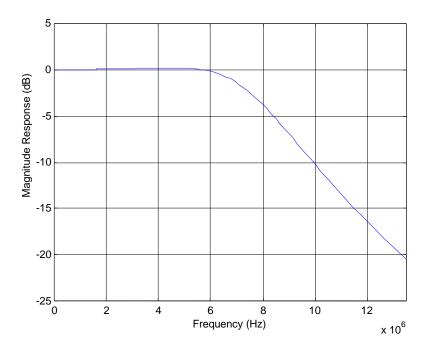

#### **Anti-aliasing Filter**

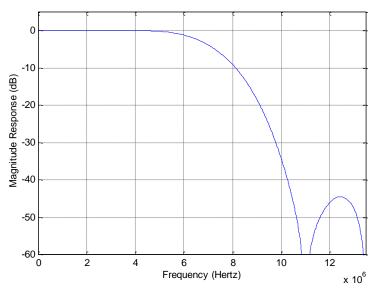

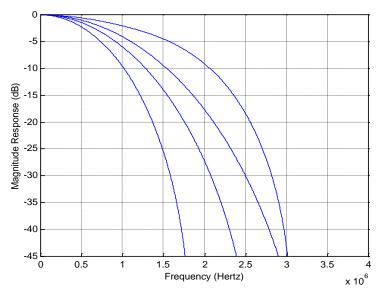

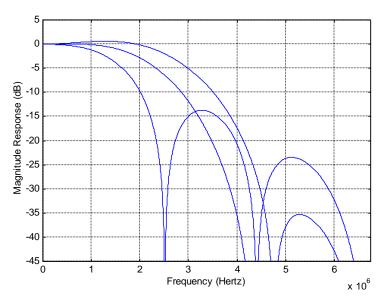

The TW2836 contains an anti-aliasing filter to prevent out-of-band frequency in analog video input signal. So there is no need of external components in analog input pin except ac coupling capacitor and termination resistor. The following Fig 2 shows the frequency response of the anti-aliasing filter.

Fig 2. The frequency response of anti-aliasing filter

#### Analog-to-Digital Converter

The TW2836 contains four 10-bit ADC (Analog to Digital Converters) to digitize the analog video inputs. Each ADC has two analog switches that are controlled by the ANA\_SW (0x0D, 0x1D, 0x2D, and 0x3D) register. The ADC can also be put into power-down mode by the ADC\_PWDN (0x4C) register.

#### Sync Processing

The sync processor of the TW2836 detects horizontal and vertical synchronization signals in the composite video signal. The TW2836 utilizes proprietary technology for locking to weak, noisy, or unstable signals such as those from on air signal or fast forward/backward play of VCR system.

A digital gain and clamp control circuit restores the ac coupled video signal to a fixed dc level. The clamping circuit provides line-by-line restoration of the video pedestal level to a fixed dc reference voltage. In no AGC mode, the gain control circuit adjusts only the video sync gain to achieve desired sync amplitude so that the active video is bypassed regardless of the gain control. But when AGC mode is enabled, both active video and sync are adjusted by the gain control.

The horizontal synchronization processor contains a sync separator, a PLL and the related decision logic. The horizontal sync separator detects the horizontal sync by examining low-pass filtered video input whose level is lower than a threshold. Additional logic is also used to avoid false detection on glitches. The horizontal PLL locks onto the extracted horizontal sync in all conditions to provide jitter free image output. In case of missing horizontal sync, the PLL is on free running status that matches the standard raster frequency.

The vertical sync separator detects the vertical synchronization pattern in the input video signals. The field status is determined at vertical synchronization time. When the location of the detected vertical sync is inline with a horizontal sync, it indicates a frame start or the odd field start. Otherwise, it indicates an even field.

#### **Color Decoding**

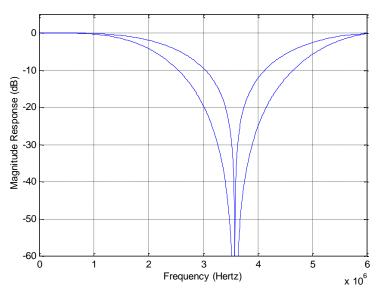

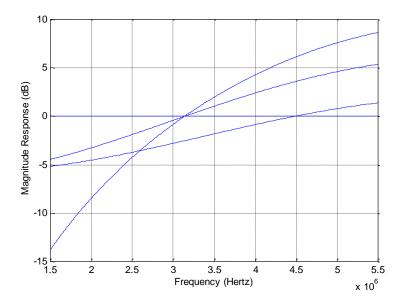

The digitized composite video data at 2X pixel clock rate first passes through decimation filter. The decimation filter is required to achieve optimum performance and prevent high frequency components from being aliased back into the video image. The following Fig 3 shows the frequency characteristic of the decimation filter.

Fig 3 The frequency characteristic of the decimation Filter

The adaptive comb filter is used for high performance luminance/chrominance separation from NTSC/PAL composite video signals. The comb filter improves the luminance resolution and reduces noise such as cross-luminance and cross-color. The adaptive algorithm eliminates most of errors without introducing new artifacts or noise. To accommodate some viewing preferences, additional chrominance trap filters are also available in the luminance path.

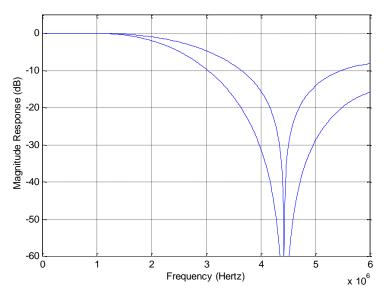

Fig 4 and Fig 5 show the frequency response of notch filter for each system NTSC and PAL.

Fig 4 The frequency response of luminance notch filter for NTSC

Fig 5 The frequency response of luminance notch filter for PAL

#### Luminance Processing

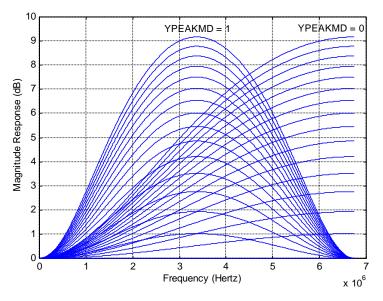

The luminance signal separated by adaptive comb or trap filter is then fed to a peaking circuit. The peaking filter enhances the high frequency components of the luminance signal via the Y\_PEAK (0x0B, 0x1B, 0x2B, and 0x3B) register. The following Fig 6 shows the characteristics of the peaking filter for four different gain modes.

Fig 6 The frequency characteristic of luminance peaking filter

The picture contrast and brightness adjustment is provided through the CONT (0x09, 0x19, 0x29, and 0x39) and BRT (0x0A, 0x1A, 0x2A, and 0x3A) registers. The contrast adjustment range is from approximately 0 to 200 percent and the brightness adjustment is in the range of  $\pm 25$  IRE.

#### **Chrominance Processing**

The chrominance demodulation is done by first quadrature mixing for NTSC and PAL. The mixing frequency is equal to the sub-carrier frequency of NTSC and PAL. After the mixing, a LPF is used to remove 2X carrier signal and yield chrominance components. The characteristic of LPF can be selected for optimized transient color performance. The Fig 7 is showing the frequency response of chrominance LPF.

Fig 7 The frequency response of chrominance LPF

In case of a mistuned IF source, IF compensation filter makes up for any attenuation at higher frequencies or asymmetry around the color sub-carrier. The gain for the upper chrominance side band is controlled by the IFCOMP (0x46) register. The Fig 8 shows the frequency response of IF-compensation filter.

Fig 8 The frequency characteristics of IF-compensation filter

The ACC (Automatic Color gain Control) compensates for reduced chrominance amplitudes caused by high frequency suppression in video signal. The range of ACC is from –6dB to 30dB approximately. For black & white video or very weak & noisy signals, the internal color killer circuit will turn off the color. The color killing function can also be always enabled or disabled by programming CKIL (0x0C, 0x1C, 0x2C, and 0x3C) register.

The color saturation can be adjusted by changing SAT (0x08, 0x18, 0x28, and 0x38) register. The Cb and Cr gain can be also adjusted independently by programming UGAIN (0x48) and VGAIN (0x49) registers. Likewise, the Cb and Cr offset can be programmed through the U\_OFF (0x4A) and V\_OFF (0x4B) registers. Hue control is achieved with phase shift of the digitally controlled oscillator. The phase shift can be programmed through the HUE (0x07, 0x17, 0x27, and 0x37) register.

#### **Realtime Record Mode**

The TW2836 supports four channel real-time record outputs with full D1 format through the DLINKI and MPP1/2 pins. Four channel real-time record outputs are independent of display and record path mode. The TW2836 also supports H/V/F signals for each channel through the DLINKI and MPP1/2 pins. The output modes of DLINKI and MPP1/2 pins are controlled via the MPP\_MD (1xB0) and MPP\_SET (1xB1, 1xB3, and 1xB5) registers.

#### **Digital Video Input**

The TW2836 supports digital video input with 8bit ITU-R BT.656 standard for playback. This digital input is decoded in built-in ITU-R BT 656 decoder and fed to the scaler block in order to display the scaled video data. The TW2836 supports error correction mode for decoding ITU-R BT.656. The decoded video data are also transferred to channel ID decoder part for auto cropping and strobe function.

#### Digital Video Input Format

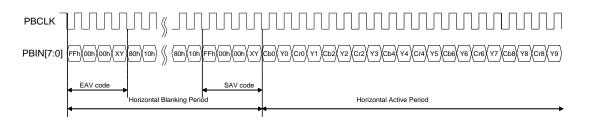

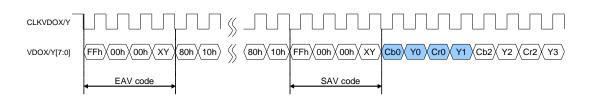

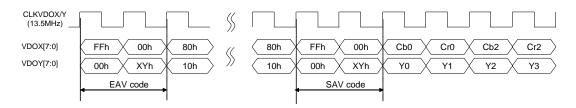

The timing of digital video input is illustrated in Fig 9.

Fig 9 Timing diagram of ITU-R BT.656 format for digital video input

The SAV and EAV sequences are shown in Table 2.

| Condition |          |            | 656 FVH Value |   |   | SAV/EAV Code Sequence |        |       |        |

|-----------|----------|------------|---------------|---|---|-----------------------|--------|-------|--------|

| Field     | Vertical | Horizontal | F             | V | Н | First                 | Second | Third | Fourth |

| EVEN      | Blank    | EAV        | 1             | 1 | 1 | 0xFF                  | 0x00   | 0x00  | 0xF1   |

|           |          | SAV        |               |   | 0 |                       |        |       | 0xEC   |

| EVEN      | Active   | EAV        | 1             | 0 | 1 |                       |        |       | 0xDA   |

|           |          | SAV        |               |   | 0 |                       |        |       | 0xC7   |

| ODD       | Blank    | EAV        | 0             | 1 | 1 |                       |        |       | 0xB6   |

|           |          | SAV        |               |   | 0 |                       |        |       | 0xAB   |

| ODD       | Active   | EAV        | 0             | 0 | 1 |                       |        |       | 0x9D   |

|           |          | SAV        |               |   | 0 |                       |        |       | 0x80   |

Table 2 ITU-R BT.656 SAV and EAV code sequence

#### Channel ID Decoder

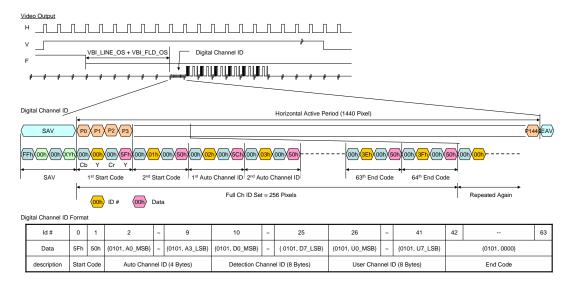

The TW2836 provides channel ID decoding function for playback input. The TW2836 supports three kinds of channel ID such as User channel ID, Detection channel ID, and auto channel ID. The User channel ID is used for customized information like system information and date. The Detection channel ID is used for detected information of current live input such as motion, video loss, blind and night detection information. The auto channel ID is employed for automatic identification of picture configuration which includes the channel number, analog switch, event, region enable and field/frame mode information. The TW2836 also supports both analog and digital type channel ID during VBI period. The digital channel ID has priority over analog channel ID. The analog type channel ID decoding is enabled via the VBI\_ENA (1x86) register and the digital type channel ID decoding is operated via VBI\_CODE\_EN (1x86) register. Additionally to detect properly the analog channel ID against noise such as VCR source, the channel ID LPF can be enabled via the VBI\_FLT\_EN (1x86) register. The decoded channel ID information is used for auto cropping / strobe function and can also be read through the host interface. The detailed auto cropping / strobe function for playback input will be described at "Cropping Function" section (page 34) and "Playback Path Control" section (page 57).

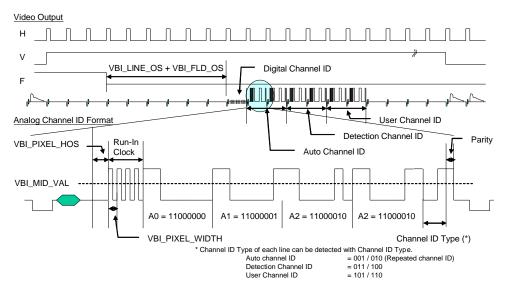

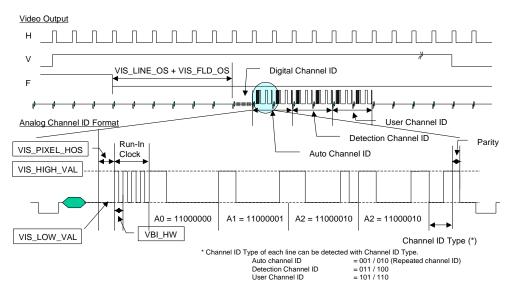

For channel ID detection mode, the TW2836 supports both automatic channel ID detection mode and manual channel ID detection mode. For an automatic channel ID detection mode, the playback input should include a run-in clock. But for a manual channel ID detection mode, the playback input can include a run-in clock or not via VBI\_RIC\_ON (1x88) register. In a manual detection mode, the TW2836 has several related register such as the VBI\_PIXEL\_HOS (1x87) to define horizontal start offset, the VBI\_FLD\_OS (1x88) to define line offset between odd and even field, the VBI\_PIXEL\_HW to define pulse width for 1 bit data, the VBI\_LINE\_SIZE (1x89) to define channel ID line size and the VBI\_LINE\_OS (1x89) to define line offset for channel ID. The VBI\_MID\_VAL (1x8A) register is used to define the threshold level between high and low. Even in automatic channel ID detection mode, the line size and bit width can be discriminated by reading the VBI\_LINE\_SIZE and VBI\_PIXEL\_HW (1xCB) register. The Fig 10 shows the relationship between channel ID and register setting.

This channel ID information can be read through the CHID\_TYPE or CHID\_VALID (1x8B), AUTO\_CHID 0/1/2/3 (1x8C~ 1x8F), DET\_CHID 0/1/2/3/4/5/6/7 (1x98~1x9F), and USER\_CHID 0/1/2/3/4/5/6/7 (1x90~1x97) registers. The CHID\_TYPE register discriminates between the Auto channel ID (CHID\_TYPE = "1") and User channel ID (CHID\_TYPE = "0"). The CHID\_VALID register indicates whether the detected channel ID type is valid or not. The AUTO\_CHID, DET\_CHID and USER\_CHID registers are used to check the decoded channel ID data when the VBI\_RD\_CTL (1x88) register value is "1".

Basically the channel ID is located in VBI period and auto strobe and cropping is executed after channel ID decoding. But for some case, the channel ID can be placed in vertical active period instead of VBI period. For this mode, the TW2836 also supports the channel ID decoding function

within vertical active period via the VAV\_CHK (1x89) register and manual cropping function via the MAN\_PBCROP (0xC0) register with proper VDELAY value.

Fig 10 The related register for manual channel ID detection

#### **Cropping and Scaling Function**

The TW2836 provides two methods to reduce the amount of video pixel data, scaling and cropping. The scaling function provides video image at lower resolution while the cropping function supplies only a portion of the video image. The TW2836 also supports an auto cropping function for playback input with channel ID decoding. The TW2836 has a free scaler for a variable image size in display path, but has a limitation of image size in record path such as Full / QUAD / CIF format.

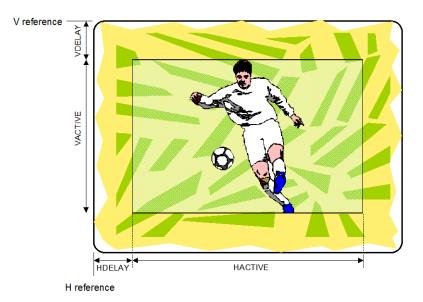

#### **Cropping Function for Live**

The cropping function allows only subsection of a video image to be output. The active video region is determined by the HDELAY, HACTIVE, VDELAY and VACTIVE ( $0x02 \sim 0x06$ ,  $0x12 \sim 0x16$ ,  $0x22 \sim 0x26$ ,  $0x32 \sim 0x36$ ) register. The first active line is defined by the VDELAY register and the first active pixel is defined by the HDELAY register. The VACTIVE register can be programmed to define the number of active lines in a video field, and the HACTIVE register can be programmed to define the number of active pixels in a video line. This function is used to implement for panning and tilt.

The horizontal delay register HDELAY determines the number of pixel delays between the horizontal reference and the leading edge of the active region. The horizontal active register HACTIVE determines the number of active pixels to be processed. Note that these values are referenced to the pixel number before scaling. Therefore, even if the scaling ratio is changed, the active video region used for scaling remains unchanged as set by the HDEALY and HACTIVE register. In order for the cropping to work properly, the following equation should be satisfied.

HDELAY + HACTIVE < Total number of pixels per line

Where the total number of pixels per line is 858 for NTSC and 864 for PAL

To process full size region, the HDELAY should be set to 32 and HACTIVE set to 720 for both NTSC and PAL system.

The vertical delay register (VDELAY) determines the number of line delays from the vertical reference to the start of the active video lines. The vertical active register (VACTIVE) determines the number of lines to be processed. These values are referenced to the incoming scan lines before the vertical scaling. In order for the vertical cropping to work properly, the following equation should be satisfied.

VDELAY + VACTIVE < Total number of lines per field

Where the total number of lines per field is 262 for NTSC and 312 for PAL

To process full size region, the VDELAY should be set to 6 and VACTIVE set to 240 for NTSC and the VDELAY should be also set to 5 and VACTIVE set to 288 for PAL.

#### **Scaling Function for Live**

The TW2836 includes a high quality free horizontal and vertical down scaler for display path. But the TW2836 cannot use a free scaler function in record path because channel size definition for record path has a limitation such as Full / QUAD / CIF (Please refer to "Record Path Control" section, page 64).

The video images can be downscaled in both horizontal and vertical direction to an arbitrary size. The luminance horizontal scaler includes an anti-aliasing filter to reduce image artifacts in the resized image via the HSFLT (0x80/90/A0/B0, 0x85/95/A5/B5 and 0x8A/9A/AA/BA) register and a 32 poly-phase filter to accurately interpolate the value of a pixel. This results in more aesthetically pleasing video as well as higher compression ratio in bandwidth-limited application.

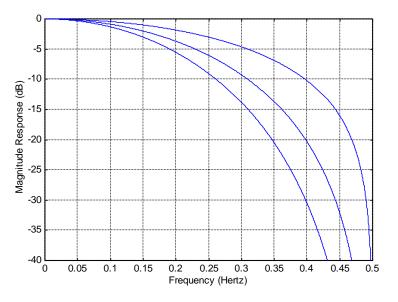

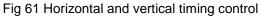

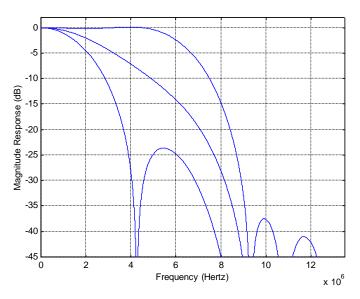

The following Fig 11 shows the frequency response of anti-aliasing filter for horizontal scaling.

Fig 11 The frequency response of anti-aliasing filter for horizontal scaling

Similarly, the vertical scaler also contains an anti-aliasing filter controlled via the VSFLT (0x80/90/A0/B0, 0x85/95/A5/B5 and 0x8A/9A/AA/BA) register and 16 poly-phase filters for down scaling. The filter characteristics are shown in the Fig 12.

Fig 12 The characteristics of anti-aliasing filter for vertical scaling

Down scaling is achieved by programming the scaling register HSCALE and VSCALE (0x81 ~ 0x84, 0x91 ~ 0x94, 0xA1 ~ 0xA4, 0xB1 ~ 0xB4) register. When no scaled video image, the TW2836 will output the number of pixels as specified by the HACTIVE and VACTIVE (0x02 ~ 0x06, 0x12 ~ 0x16, 0x22 ~ 0x26, 0x32 ~ 0x36) register. If the number of output pixels required is smaller than the number specified by the HACTIVE/VACTIVE register, the 16bit HSCALE/ VSCALE register is used to reduce the output pixels to the desired number.

The following equation is used to determine the horizontal scaling ratio to be written into the 16bit HSCALE register.

HSCALE =  $[N_{pixel\_desired} / HACTIVE] * (2^{16} - 1)$

Where N<sub>pixel\_desired</sub> is the desired number of active pixels per line

For example, to scale picture from full size (HACTIVE = 720) to CIF (360 pixels), the HSCALE value can be found as:

The following equation is used to determine the vertical scaling ratio to be written into the 16bit VSCALE register.

VSCALE = [N<sub>line\_desired</sub> / VACTIVE] \* (2^16 - 1)

Where  $N_{\text{line\_desired}}$  is the desired number of active lines per field

For example, to scale picture from full size (VACTIVE = 240 lines for NTSC and 288 lines for PAL) to CIF (120 lines for NTSC and 144 lines for PAL), the VSCALE value can be found as:

VSCALE = [120 / 240] \* (2^16 - 1) = 0x7FFF for NTSC

VSCALE = [144 / 288] \* (2^16 - 1) = 0x7FFF for PAL

The scaling ratios of popular case are listed in Table 3.

| Scaling Ratio | Format | Output Resolution | HSCALE | VSCALE |  |

|---------------|--------|-------------------|--------|--------|--|

| 1             | NTSC   | 720x480           | 0xFFFF | 0xFFFF |  |

| I             | PAL    | 720x576           | 0xFFFF | 0xFFFF |  |

|               | NTSC   | 360x240           | 0x7FFF | 0x7FFF |  |

| 1/2 (CIF)     | PAL    | 360x288           | 0x7FFF | 0x7FFF |  |

| 1/4 (QCIF)    | NTSC   | 180x120           | 0x3FFF | 0x3FFF |  |

|               | PAL    | 180x144           | 0x3FFF | 0x3FFF |  |

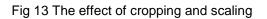

The effect of scaling and cropping is shown in Fig 13.

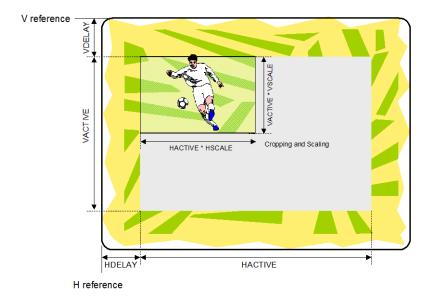

#### **Cropping and Scaling Function for Playback**

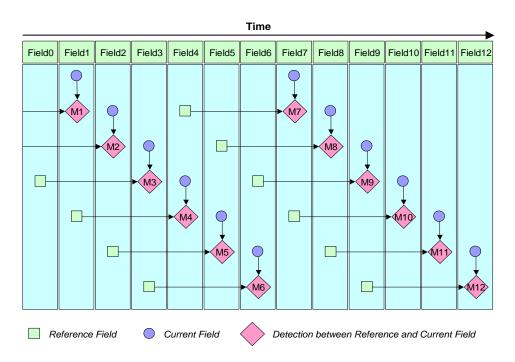

The TW2836 supports an auto cropping function with channel ID decoding for playback input. Each channel with the multiplexed playback input can be mapped into the desired position with the auto cropping function.

If the PB\_AUTO\_EN (1x16) = "0", the TW2836 is set to a manual cropping mode so that user can control cropping with VDELAY\_PB and HDELAY\_PB (0x8B~0x8F, 0x9B~9F, 0xAB~AF and 0xBB~BF) register. If the PB\_AUTO\_EN = "1", the TW2836 is set into an auto cropping mode. In this mode, the desired channel can be chosen by PB\_CH\_NUM register (1x16, 1x1E, 1x26, 1x2E) and it will be cropped automatically to horizontal and vertical direction in playback input. The TW2836 has several related registers for this mode such as PB\_CROP\_MD, PB\_ACT\_MD and MAN\_PBCROP (0xC0). The PB\_CROP\_MD defines the record mode of the playback input such as normal record mode or DVR record mode (Please refer to "Record Path Control" section, page 64). The PB\_ACT\_MD defines an active pixel size of horizontal direction such as 720 / 704 / 640 pixels. The MAN\_PBCROP controls the horizontal and vertical starting offset in the auto cropping mode with HDELAY\_PB and VDELAY\_PB registers. It is useful in case that the encoded channel ID is located at vertical active area in ITU-R BT.656 data stream.

CH0 : PB\_CH\_NUM0 = 0, (cropping H/V) CH1 : PB\_CH\_NUM1 = 1, (cropping V) CH2 : PB\_CH\_NUM2 = 2, (cropping H) CH3 : PB\_CH\_NUM3 = 3, (No cropping)

Fig 14 The effect of auto cropping function

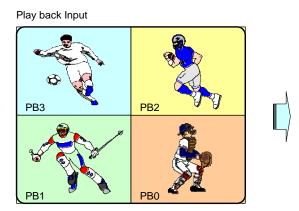

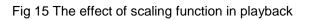

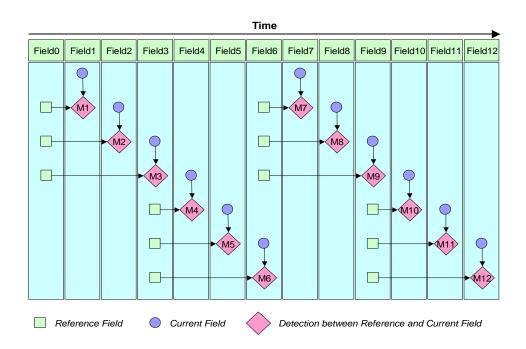

The TW2836 includes four additional free down scaler for playback path so that the video image from playback input can be downscaled to an arbitrary size in both horizontal and vertical direction. Therefore, using this cropping and scaling function, the TW2836 supports free size and positioning function for both live and playback input in display path. The following Fig 15 shows the effect of scaling and cropping operation in playback.

PB0 : PB\_CH\_NUM0 = 0, (cropping H/V + Scaling) PB2 : PB\_CH\_NUM2 = 2, (cropping H)

Display Scaling Output with New position

PB1 : PB\_CH\_NUM1 = 1, (cropping V + Scaling) PB3 : PB\_CH\_NUM3 = 3, (No cropping)

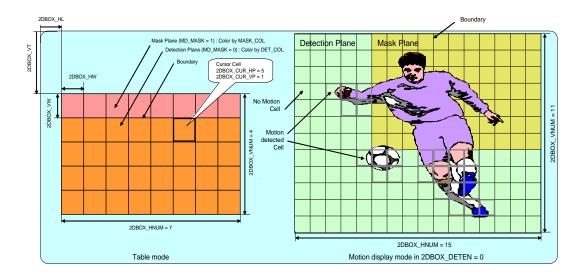

## **Motion Detection**

The TW2836 supports motion detector individually for 4 analog video inputs. The built-in motion detection algorithm uses the difference of luminance level between current and reference field. The TW2836 also supports blind and night input detection for 4 analog video inputs.

To detect motion properly according to situation, the TW2836 provides several sensitivity and velocity control parameters for each motion detector. The TW2836 supports manual strobe function to update motion detection so that it is more appropriate for user-defined motion sensitivity control.

When motion, blind and night input are detected in any video inputs, the TW2836 provides the interrupt request to host via the IRQ pin. The host processor can take the information of motion, blind or night detection by accessing the IRQENA\_MD (1x79), IRQENA\_BD (1x7A) and the IRQENA\_ND (1x7B) register. This status information is updated in the vertical blank period of each input.

The TW2836 also provides the motion, blind and night detection result through the DLINKI and MPP0/1 pin with the control of MPP\_MD (1xB0) and MPP\_SET (1xB1, 1xB3 and 1xB5) register. The TW2836 supports an overlay function to display the motion detection result in the picture with 2D arrayed box.

#### **Mask and Detection Region Selection**

The motion detection algorithm utilizes the full screen video data and detects individual motion of 16x12 cells. This full screen for motion detection consists of 704 pixels and 240 lines for NTSC and 288 lines for PAL. Starting pixel in horizontal direction can be shifted from 0 to 15 pixels using the MD\_ALIGN (2x82, 2xA2, 2xC2, and 2xE2) register.

Each cell can be masked via the MD\_MASK ( $2x86 \sim 2x9D$ ,  $2xA6 \sim 2xBD$ ,  $2xC6 \sim 2xDD$ ,  $2xE6 \sim 2xFD$ ) register as illustrated in Fig 16. If the mask bit in specific cell is programmed to high, the related cell is ignored for motion detection.

|                 | 704 Pixels (44 Pixels/Cell) |                     |                     |                     |                     |                     |                     |                     |                     |                     |                      |                      |                      |                      |                      |                      |

|-----------------|-----------------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|

| Ê               | MD_<br>MASK0                | MD_<br>MASK0        | MD_<br>MASK0        | MD_<br>MASK0        | MD_<br>MASK0        | MD_<br>MASK0        | MD_<br>MASK0        | MD_<br>MASK0        | MD_<br>MASK0        | MD_<br>MASK0        | MD_<br>MASK0         | MD_<br>MASK0         | MD_<br>MASK0         | MD_<br>MASK0         | MD_<br>MASK0         | MD_<br>MASK0         |

| <u>e</u>        | [0]                         | [1]                 | [2]                 | [3]                 | [4]                 | [5]                 | [6]                 | [7]                 | [8]                 | [9]                 | [10]                 | [11]                 | [12]                 | [13]                 | [14]                 | [15]                 |

| (24 Lines/Cell) | MD_<br>MASK1                | MD_<br>MASK1        | MD_<br>MASK1        | MD_<br>MASK1        | MD_<br>MASK1        | MD_<br>MASK1        | MD_<br>MASK1        | MD_<br>MASK1        | MD_<br>MASK1        | MD_<br>MASK1        | MD_<br>MASK1         | MD_<br>MASK1         | MD_<br>MASK1         | MD_<br>MASK1         | MD_<br>MASK1         | MD_<br>MASK1         |

|                 | [0]                         | [1]                 | [2]                 | [3]                 | [4]                 | [5]                 | [6]                 | [7]                 | [8]                 | [9]                 | [10]                 | [11]                 | [12]                 | [13]                 | [14]                 | [15]                 |

|                 | MD_<br>MASK2                | MD_<br>MASK2        | MD_<br>MASK2        | MD_<br>MASK2        | MD_<br>MASK2        | MD_<br>MASK2        | MD_<br>MASK2        | MD_<br>MASK2        | MD_<br>MASK2        | MD_<br>MASK2        | MD_<br>MASK2         | MD_<br>MASK2         | MD_<br>MASK2         | MD_<br>MASK2         | MD_<br>MASK2         | MD_<br>MASK2         |

| 보               | [0]                         | [1]                 | [2]                 | [3]                 | [4]                 | [5]                 | [6]                 | [7]                 | [8]                 | [9]                 | [10]                 | [11]                 | [12]                 | [13]                 | [14]                 | [15]                 |

| 50Hz            | MD_<br>MASK3                | MD_<br>MASK3        | MD_<br>MASK3        | MD_<br>MASK3        | MD_<br>MASK3        | MD_<br>MASK3        | MD_<br>MASK3        | MD_<br>MASK3        | MD_<br>MASK3        | MD_<br>MASK3        | MD_<br>MASK3         | MD_<br>MASK3         | MD_<br>MASK3         | MD_<br>MASK3         | MD_<br>MASK3         | MD_<br>MASK3         |

| for             | [0]                         | [1]                 | [2]                 | [3]                 | [4]                 | [5]                 | [6]                 | [7]                 | [8]                 | [9]                 | [10]                 | [11]                 | [12]                 | [13]                 | [14]                 | [15]                 |

| Lines f         | MD_<br>MASK4                | MD_<br>MASK4        | MD_<br>MASK4        | MD_<br>MASK4        | MD_<br>MASK4        | MD_<br>MASK4        | MD_<br>MASK4        | MD_<br>MASK4        | MD_<br>MASK4        | MD_<br>MASK4        | MD_<br>MASK4         | MD_<br>MASK4         | MD_<br>MASK4         | MD_<br>MASK4         | MD_<br>MASK4         | MD_<br>MASK4         |

| Ē               | [0]                         | [1]                 | [2]                 | [3]                 | [4]                 | [5]                 | [6]                 | [7]                 | [8]                 | [9]                 | [10]                 | [11]                 | [12]                 | [13]                 | [14]                 | [15]                 |

| 288             | MD_<br>MASK5<br>[0]         | MD_<br>MASK5<br>[1] | MD_<br>MASK5<br>[2] | MD_<br>MASK5<br>[3] | MD_<br>MASK5<br>[4] | MD_<br>MASK5<br>[5] | MD_<br>MASK5<br>[6] | MD_<br>MASK5<br>[7] | MD_<br>MASK5<br>[8] | MD_<br>MASK5<br>[9] | MD_<br>MASK5<br>[10] | MD_<br>MASK5<br>[11] | MD_<br>MASK5<br>[12] | MD_<br>MASK5<br>[13] | MD_<br>MASK5<br>[14] | MD_<br>MASK5<br>[15] |

| ell),           | MD                          | MD                  | MD                  | MD                  | MD                  | MD                  | MD                  | MD                  | MD                  | MD                  | MD                   | MD                   | MD                   | MD                   | MD                   | MD                   |

| Lines/Ce        | MD_<br>MASK6<br>[0]         | MASK6<br>[1]        | MASK6<br>[2]        | MASK6<br>[3]        | MASK6<br>[4]        | MASK6<br>[5]        | MASK6<br>[6]        | MASK6<br>[7]        |                     | MASK6<br>[9]        | MASK6<br>[10]        | MASK6<br>[11]        | MASK6<br>[12]        | MASK6<br>[13]        | MASK6<br>[14]        | MASK6<br>[15]        |

| ee              | MD                          | MD                  | MD                  | MD                  | MD                  | MD                  | MD                  | MD                  | MD                  | MD                  | MD                   | MD                   | MD                   | MD                   | MD                   | MD                   |

|                 | MASK7                       | MASK7               | MASK7               | MASK7               | MASK7               | MASK7               | MASK7               | MASK7               | MASK7               | MASK7               | MASK7                | MASK7                | MASK7                | MASK7                | MASK7                | MASK7                |

| (20             | [0]                         | [1]                 | [2]                 | [3]                 | [4]                 | [5]                 | [6]                 | [7]                 | [8]                 | [9]                 | [10]                 | [11]                 | [12]                 | [13]                 | [14]                 | [15]                 |

| 60Hz (          | MD_<br>MASK8                | MD_<br>MASK8        | MD_<br>MASK8        | MD_<br>MASK8        | MD_<br>MASK8        | MD_<br>MASK8        | MD_<br>MASK8        | MD_<br>MASK8        | MD_<br>MASK8        | MD_<br>MASK8        | MD_<br>MASK8         | MD_<br>MASK8         | MD_<br>MASK8         | MD_<br>MASK8         | MD_<br>MASK8         | MD_<br>MASK8         |

| 00              | [0]                         | [1]                 | [2]                 | [3]                 | [4]                 | [5]                 | [6]                 | [7]                 | [8]                 | [9]                 | [10]                 | [11]                 | [12]                 | [13]                 | [14]                 | [15]                 |

| for             | MD_<br>MASK9                | MD_<br>MASK9        | MD_<br>MASK9        | MD_<br>MASK9        | MD_<br>MASK9        | MD_<br>MASK9        | MD_<br>MASK9        | MD_<br>MASK9        | MD_<br>MASK9        | MD_<br>MASK9        | MD_<br>MASK9         | MD_<br>MASK9         | MD_<br>MASK9         | MD_<br>MASK9         | MD_<br>MASK9         | MD_<br>MASK9         |

| es              | [0]                         | [1]                 | [2]                 | [3]                 | [4]                 | [5]                 | [6]                 | [7]                 | [8]                 | [9]                 | [10]                 | [11]                 | [12]                 | [13]                 | [14]                 | [15]                 |

| 240             | MD_<br>MASK10               | MD_<br>MASK10       |                     |                     |                     |                     |                     | MD_<br>MASK10       |                     |                     | MD_<br>MASK10        | MD_<br>MASK10        |                      |                      | MD_<br>MASK10        | MD_<br>MASK10        |

|                 | [0]                         | [1]                 | [2]                 | [3]                 | [4]                 | [5]                 | [6]                 | [7]                 | [8]                 | [9]                 | [10]                 | [11]                 | [12]                 | [13]                 | [14]                 | [15]                 |

|                 | MD_<br>MASK11               | MD_<br>MASK11       | MD_<br>MASK11       | MD_<br>MASK11       | MD_<br>MASK11       | MD_<br>MASK11       | MD_<br>MASK11       | MD_<br>MASK11       | MD_<br>MASK11       | MD_<br>MASK11       | MD_<br>MASK11        | MD_<br>MASK11        | MD_<br>MASK11        | MD_<br>MASK11        | MD_<br>MASK11        | MD_<br>MASK11        |

| _               | [0]                         | [1]                 | [2]                 | [3]                 | [4]                 | [5]                 | [6]                 | [7]                 | [8]                 | [9]                 | [10]                 | [11]                 | [12]                 | [13]                 | [14]                 | [15]                 |

Fig 16 Motion mask and detection cell

The MD\_MASK register has different function for reading and writing mode. For writing mode, setting "1" to MD\_MASK register inhibits the specific cell from detecting motion. For reading mode, the MD\_MASK register has three kinds of information depending on the MASK\_MODE (2x82, 2xA2, 2xC2, and 2xE2) register. For MASK\_MODE = "0", the state of MD\_MASK register means the result of VIN\_A motion detection that "1" indicates detecting motion and "0" denotes no motion detection in the cell. For MASK\_MODE = "1", the state of MD\_MASK register means the result of VIN\_B motion detection. For MASK\_MODE = "2 or 3", the state of MD\_MASK register means masking information of cell.

#### **Sensitivity Control**

The motion detector has 4 sensitivity parameters to control threshold of motion detection such as the level sensitivity via the MD\_LVSENS (2x83, 2xA3, 2xC3, and 2xE3) register, the spatial sensitivity via the MD\_SPSENS (2x85, 2xA5, 2xC5, 2xE5) and MD\_CELSENS (2x83, 2xA3, 2xC3, and 2xE3) register, and the temporal sensitivity parameter via the MD\_TMPSENS (2x85, 2xA5, 2xC5, and 2xE5) register.

# Level Sensitivity

In built-in motion detection algorithm, the motion is detected when luminance level difference between current and reference field is greater than MD\_LVSENS value. Motion detector is more sensitive for the smaller MD\_LVSENS value and less sensitive for the larger. When the MD\_LVSENS is too small, the motion detector may be weak in noise.

# **Spatial Sensitivity**

The TW2836 uses 192 (16x12) detection cells in full screen for motion detection. Each detection cell is composed of 44 pixels and 20 lines for NTSC and 24 lines for PAL. Motion detection from only luminance level difference between two fields is very weak in spatial random noise. To remove the fake motion detection from the random noise, the TW2836 supports a spatial filter via the MD\_SPSENS register which defines the number of detected cell to decide motion detection in full size image. The large MD\_SPSENS value increases the immunity of spatial random noise.