ŧ

# 1/3-Inch CMOS Digital Image Sensor

# AR0130CS Datasheet, Rev. 12

For the latest datasheet, please visit www.onsemi.com

# Features

- Superior low-light performance both in VGA mode and HD mode

- Excellent Near IR performance

- HD video (720p60)

- On-chip AE and statistics engine

- Auto black level calibration

- Context switching

- Progressive Scan

- Supports 2:1 scaling

- Internal master clock generated by on-chip phase locked loop (PLL) oscillator.

- Parallel output

# **Applications**

- Gaming systems

- Video surveillance

- 720p60 video applications

# **General Description**

ON Semiconductor's AR0130 is a 1/3-inch CMOS digital image sensor with an active-pixel array of 1280H x 960V. It captures images with a rolling-shutter readout. It includes sophisticated camera functions such as auto exposure control, windowing, and both video and single frame modes. It is programmable through a simple two-wire serial interface. The AR0130 produces extraordinarily clear, sharp digital pictures, and its ability to capture both continuous video and single frames makes it the perfect choice for a wide range of applications, including gaming systems, surveillance, and HD video.

#### Table 1: Key Parameters

| Paramete            | r                          | Typical Value                                           |  |  |  |  |

|---------------------|----------------------------|---------------------------------------------------------|--|--|--|--|

| Optical fo          | ormat                      | 1/3-inch (6 mm)                                         |  |  |  |  |

| Active pix          | cels                       | 1280 x 960 = 1.2 Mp                                     |  |  |  |  |

| Pixel size          |                            | 3.75 μm                                                 |  |  |  |  |

| Color filte         | er array                   | Monochrome, RGB Bayer                                   |  |  |  |  |

| Shutter ty          | уре                        | Electronic rolling shutter                              |  |  |  |  |

| Input cloc          | :k range                   | 6 – 50 MHz                                              |  |  |  |  |

| Output cl           | ock maximum                | 74.25 MHz                                               |  |  |  |  |

| Output              | Parallel                   | 12-bit                                                  |  |  |  |  |

|                     | 1.2 Mp (full FOV)          | 45 fps                                                  |  |  |  |  |

|                     | 720pHD (reduced FOV)       | 60 fps                                                  |  |  |  |  |

| Max.<br>Frame       | VGA (full FOV)             | 45 fps                                                  |  |  |  |  |

| rates               | VGA (reduced FOV)          | 60 fps                                                  |  |  |  |  |

|                     | 800 x 800 (reduced<br>FOV) | 60 fps                                                  |  |  |  |  |

| Responsiv           | vity at 550 nm (Mono)      | 6.5 V/lux-sec                                           |  |  |  |  |

| Responsiv<br>green) | vity at 550 nm (RGB        | 5.6 V/lux-sec                                           |  |  |  |  |

| SNR <sub>MAX</sub>  |                            | 44 dB                                                   |  |  |  |  |

| Dynamic             | range                      | 82 dB                                                   |  |  |  |  |

| Cumula              | I/O                        | 1.8 or 2.8 V                                            |  |  |  |  |

| Supply<br>voltage   | Digital                    | 1.8 V                                                   |  |  |  |  |

| Tortuge             | Analog                     | 2.8 V                                                   |  |  |  |  |

| Power co            | nsumption                  | 270 mW (1280x720 60<br>fps)                             |  |  |  |  |

| Operating           | g temperature              | −30°C to + 70°C (ambient)<br>−30°C to + 80°C (junction) |  |  |  |  |

| Package o           | option                     | Bare die, iLCC, PLCC                                    |  |  |  |  |

# **Ordering Information**

#### Table 2: Available Part Numbers

ΠΝ

| Part Number                   | Base Description          | Variant Description                                      |

|-------------------------------|---------------------------|----------------------------------------------------------|

| AR0130CSSC00SPBA0-DP1         | RGB Bayer 48-Pin PLCC     | Dry Pack with Protective Film                            |

| AR0130CSSC00SPBA0-DR1         | RGB Bayer 48-Pin PLCC     | Dry Pack without Protective Film                         |

| AR0130CSSC00SPCA0-DPBR1       | RGB Bayer 48-Pin iLCC     | Dry Pack with Protective Film, Double Side BBAR Glass    |

| AR0130CSSC00SPCA0-DRBR1       | RGB Bayer 48-Pin iLCC     | Dry Pack without Protective Film, Double Side BBAR Glass |

| AR0130CSSC00SPCAD3-GEVK       | RGB Bayer demo kit iLCC   |                                                          |

| AR0130CSSC00SPCAD3-S115-GEVK  | RGB Bayer demo kit iLCC   |                                                          |

| AR0130CSSC00SPCAD3-S213A-GEVK | RGB Bayer demo kit iLCC   |                                                          |

| AR0130CSSC00SPCAD-GEVK        | RGB Bayer demo kit iLCC   |                                                          |

| AR0130CSSC00SPCAD-S115-GEVK   | RGB Bayer demo kit iLCC   |                                                          |

| AR0130CSSC00SPCAD-S213A-GEVK  | RGB Bayer demo kit iLCC   |                                                          |

| AR0130CSSC00SPCAH-GEVB        | RGB Bayer headboard iLCC  |                                                          |

| AR0130CSSC00SPCAH-S115-GEVB   | RGB Bayer headboard iLCC  |                                                          |

| AR0130CSSC00SPCAH-S213A-GEVB  | RGB Bayer headboard iLCC  |                                                          |

| AR0130CSSC00SPCAW-GEVB        | RGB Bayer headboard iLCC  |                                                          |

| AR0130CSSM00SPCA0-DRBR1       | Monochrome 48-Pin iLCC    | Dry Pack without Protective Film, Double Side BBAR Glass |

| AR0130CSSM00SPCAD-S213A-GEVK  | Monochrome demo kit iLCC  |                                                          |

| AR0130CSSM00SPCAH-S213A-GEVB  | Monochrome headboard iLCC |                                                          |

See the ON Semiconductor Device Nomenclature document (TND310/D) for a full description of the naming convention used for image sensors. For reference documentation, including information on evaluation kits, please visit our web site at www.onsemi.com.

# **Table of Contents**

| Features                           | 1                         |

|------------------------------------|---------------------------|

| Applications                       | 1                         |

| General Description                | 1                         |

|                                    | 1<br>د                    |

| Ordering Information               | · · · · · · · · · · · . Z |

| General Description                |                           |

| Functional Overview                | 4                         |

| Pixel Data Format                  |                           |

| Output Data Format                 |                           |

| Real-Time Context Switching        |                           |

| Features                           |                           |

| Two-Wire Serial Register Interface |                           |

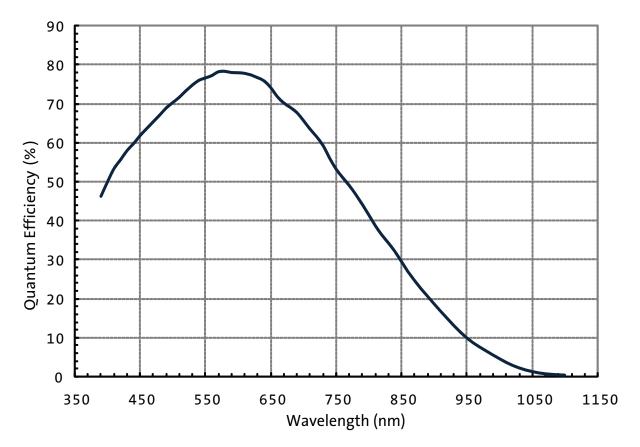

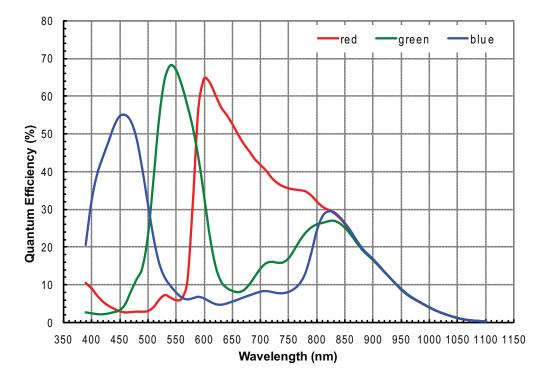

| Spectral Characteristics           |                           |

| Electrical Specifications          |                           |

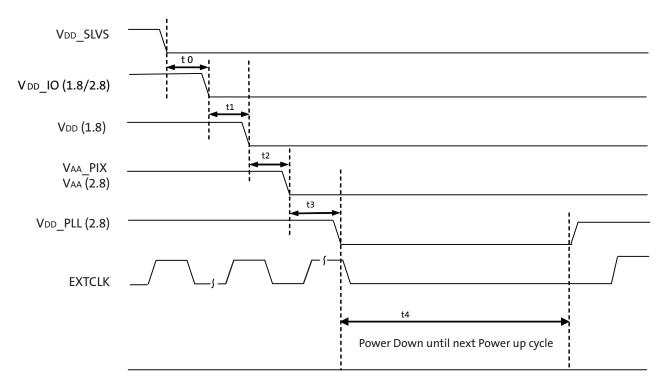

| Power-On Reset and Standby Timing. |                           |

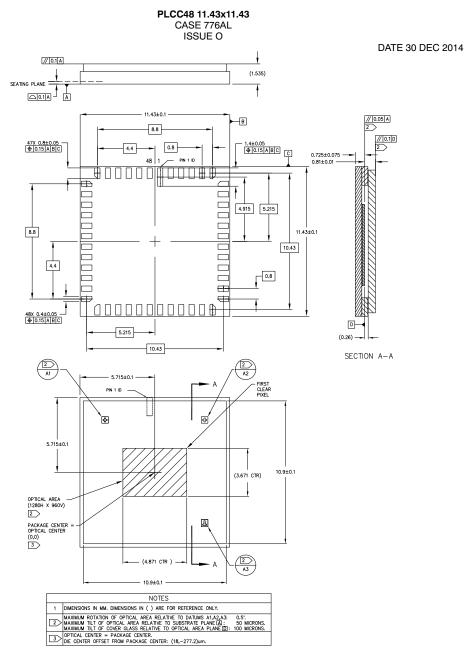

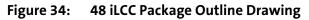

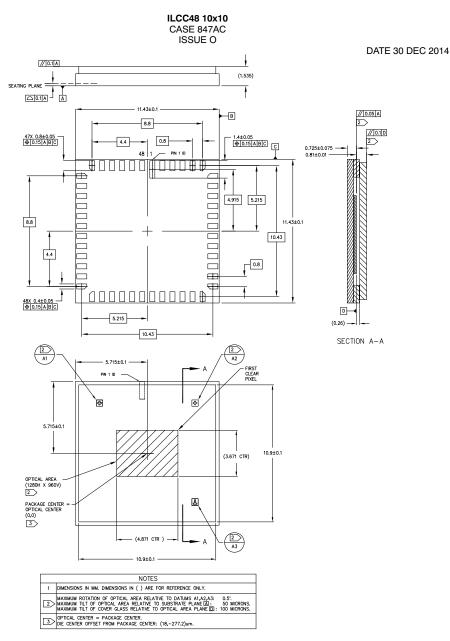

| Package Dimensions                 |                           |

# **General Description**

The ON Semiconductor AR0130 can be operated in its default mode or programmed for frame size, exposure, gain, and other parameters. The default mode output is a 960p-resolution image at 45 frames per second (fps). It outputs 12-bit raw data over the parallel port. The device may be operated in video (master) mode or in single frame trigger mode.

FRAME\_VALID and LINE\_VALID signals are output on dedicated pins, along with a synchronized pixel clock in parallel mode.

The AR0130 includes additional features to allow application-specific tuning: windowing and offset, adjustable auto-exposure control, and auto black level correction. Optional register information and histogram statistic information can be embedded in first and last 2 lines of the image frame.

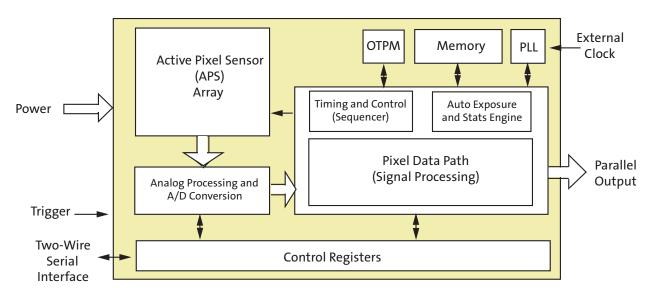

# **Functional Overview**

The AR0130 is a progressive-scan sensor that generates a stream of pixel data at a constant frame rate. It uses an on-chip, phase-locked loop (PLL) that can be optionally enabled to generate all internal clocks from a single master input clock running between 6 and 50 MHz The maximum output pixel rate is 74.25 Mp/s, corresponding to a clock rate of 74.25 MHz. Figure 1 shows a block diagram of the sensor.

### Figure 1: Block Diagram

User interaction with the sensor is through the two-wire serial bus, which communicates with the array control, analog signal chain, and digital signal chain. The core of the sensor is a 1.2 Mp Active- Pixel Sensor array. The timing and control circuitry sequences through the rows of the array, resetting and then reading each row in turn. In the time interval between resetting a row and reading that row, the pixels in the row integrate incident light. The exposure is controlled by varying the time interval between reset and readout. Once a row has been read, the data from the columns is sequenced through an analog signal chain (providing offset correction and gain), and then through an analogto-digital converter (ADC). The output from the ADC is a 12-bit value for each pixel in the array. The ADC output passes through a digital processing signal chain (which

provides further data path corrections and applies digital gain). The pixel data are output at a rate of up to 74.25 Mp/s, in parallel to frame and line synchronization signals.

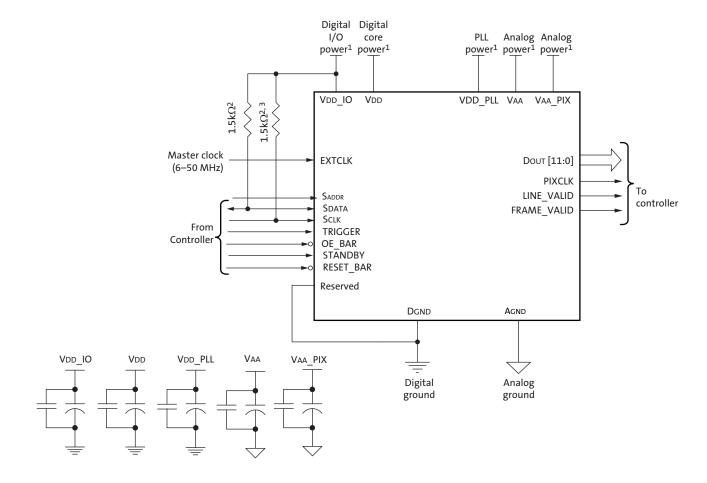

### Figure 2: Typical Configuration: Parallel Pixel Data Interface

Notes:

s: 1. All power supplies must be adequately decoupled.

- 2. ON Semiconductor recommends a resistor value of  $1.5k\Omega$ , but a greater value may be used for slower two-wire speed.

- 3. This pull-up resistor is not required if the controller drives a valid logic level on SCLK at all times.

- 4. ON Semiconductor recommends that VDD\_SLVS pad (only available in bare die) is left unconnected.

- 5. ON Semiconductor recommends that 0.1μF and 10μF decoupling capacitors for each power supply are mounted as close as possible to the pad. Actual values and results may vary depending on layout and design considerations. Check the AR0130 demo headboard schematics for circuit recommendations.

- 6. ON Semiconductor recommends that analog power planes are placed in a manner such that coupling with the digital power planes is minimized.

- 7. I/O signals voltage must be configured to match VDD\_IO voltage to minimize any leakage currents.

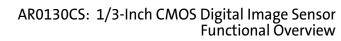

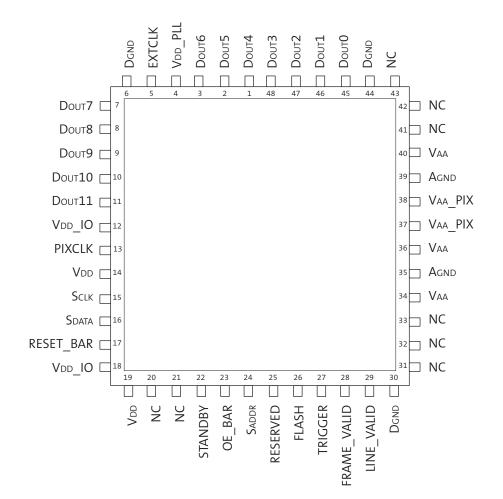

| Name        | Туре   | Description                                                                    |  |  |  |

|-------------|--------|--------------------------------------------------------------------------------|--|--|--|

| STANDBY     | Input  | Standby-mode enable pin (active HIGH).                                         |  |  |  |

| VDD_PLL     | Power  | PLL power.                                                                     |  |  |  |

| VAA         | Power  | Analog power.                                                                  |  |  |  |

| EXTCLK      | Input  | External input clock.                                                          |  |  |  |

| VDD_SLVS    | Power  | Digital power (do not connect).                                                |  |  |  |

| Dgnd        | Power  | Digital ground.                                                                |  |  |  |

| Vdd         | Power  | Digital power.                                                                 |  |  |  |

| Agnd        | Power  | Analog ground.                                                                 |  |  |  |

| SADDR       | Input  | Two-Wire Serial Interface address select.                                      |  |  |  |

| Sclk        | Input  | Two-Wire Serial Interface clock input.                                         |  |  |  |

| Sdata       | I/O    | Two-Wire Serial Interface data I/O.                                            |  |  |  |

| VAA_PIX     | Power  | Pixel power.                                                                   |  |  |  |

| LINE_VALID  | Output | Asserted when DOUT line data is valid.                                         |  |  |  |

| FRAME_VALID | Output | Asserted when DOUT frame data is valid.                                        |  |  |  |

| PIXCLK      | Output | Pixel clock out. Do∪⊤ is valid on rising edge of this clock.                   |  |  |  |

| VDD_IO      | Power  | I/O supply power.                                                              |  |  |  |

| Dout8       | Output | Parallel pixel data output.                                                    |  |  |  |

| Dout9       | Output | Parallel pixel data output.                                                    |  |  |  |

| Dout10      | Output | Parallel pixel data output.                                                    |  |  |  |

| Dout11      | Output | Parallel pixel data output (MSB)                                               |  |  |  |

| Reserved    | Input  | Connect to DGND.                                                               |  |  |  |

| Dout4       | Output | Parallel pixel data output.                                                    |  |  |  |

| Dout5       | Output | Parallel pixel data output.                                                    |  |  |  |

| Dout6       | Output | Parallel pixel data output.                                                    |  |  |  |

| Dout7       | Output | Parallel pixel data output.                                                    |  |  |  |

| TRIGGER     | Input  | Exposure synchronization input.                                                |  |  |  |

| OE_BAR      | Input  | Output enable (active LOW).                                                    |  |  |  |

| Dout0       | Output | Parallel pixel data output (LSB)                                               |  |  |  |

| Dout1       | Output | Parallel pixel data output.                                                    |  |  |  |

| Dout2       | Output | Parallel pixel data output.                                                    |  |  |  |

| Dout3       | Output | Parallel pixel data output.                                                    |  |  |  |

| RESET_BAR   | Input  | Asynchronous reset (active LOW). All settings are restored to factory default. |  |  |  |

| FLASH       | Output | Flash control output.                                                          |  |  |  |

| NC          | Input  | Do not connect.                                                                |  |  |  |

#### Table 3:Pad Descriptions

# Figure 3: 48-Pin iLCC Pinout Diagram

### AR0130CS: 1/3-Inch CMOS Digital Image Sensor Functional Overview

# Figure 4: 48-Pin PLCC Pinout Diagram

# **Pixel Data Format**

# **Pixel Array Structure**

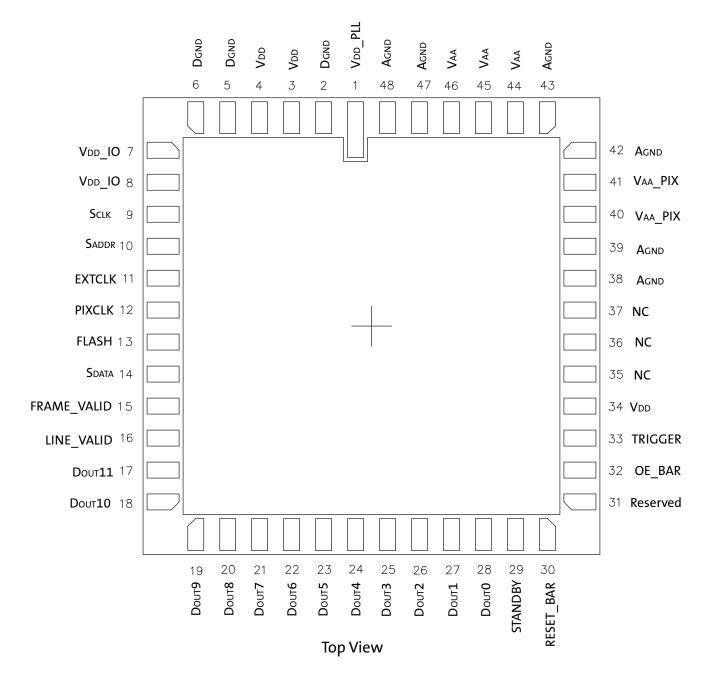

The AR0130 pixel array is configured as 1412 columns by 1028 rows, (see Figure 5). The dark pixels are optically black and are used internally to monitor black level. Of the right 108 columns, 64 are dark pixels used for row noise correction. Of the top 24 rows of pixels, 12 of the dark rows are used for black level correction. There are 1296 columns by 976 rows of optically active pixels. While the sensor's format is 1280 x 960, the additional active columns and active rows are included for use when horizontal or vertical mirrored readout is enabled, to allow readout to start on the same pixel. The pixel adjustment is always performed for monochrome or color versions. The active area is surrounded with optically transparent dummy pixels to improve image uniformity within the active area. Not all dummy pixels or barrier pixels can be read out.

### Figure 5: Pixel Array Description

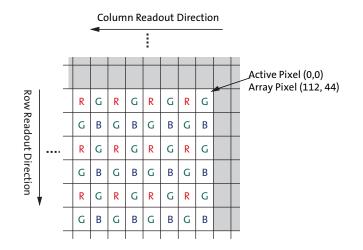

# Figure 6: Pixel Color Pattern Detail (Top Right Corner)

# Default Readout Order

By convention, the sensor core pixel array is shown with pixel (0,0) in the top right corner (see Figure 6). This reflects the actual layout of the array on the die. Also, the first pixel data read out of the sensor in default condition is that of pixel (112, 44).

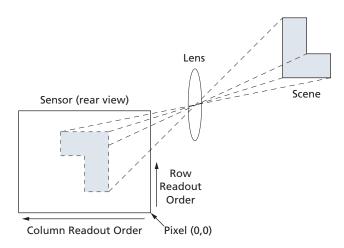

When the sensor is imaging, the active surface of the sensor faces the scene as shown in Figure 7. When the image is read out of the sensor, it is read one row at a time, with the rows and columns sequenced as shown in Figure 7 on page 10.

#### Figure 7: Imaging a Scene

# **Output Data Format**

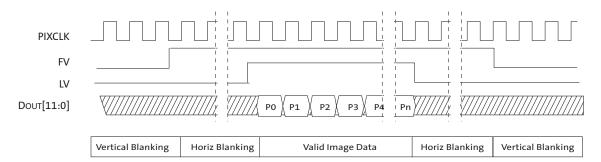

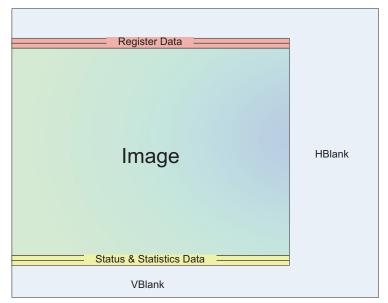

The AR0130 image data is read out in a progressive scan. Valid image data is surrounded by horizontal and vertical blanking (see Figure 8). The amount of horizontal row time (in clocks) is programmable through R0x300C. The amount of vertical frame time (in rows) is programmable through R0x300A. LINE\_VALID (LV) is HIGH during the shaded region of Figure 8. Optional Embedded Register setup information and Histogram statistic information are available in first 2 and last row of image data.

#### Figure 8: Spatial Illustration of Image Readout

| $\begin{array}{c} P_{0,0} \ P_{0,1} \ P_{0,2} P_{0,n-1} \ P_{0,n} \\ P_{1,0} \ P_{1,1} \ P_{1,2} P_{1,n-1} \ P_{1,n} \end{array}$ | 00 00 00 00 00 00<br>00 00 00 00 00 00              |

|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

| VALID IMAGE                                                                                                                       | HORIZONTAL<br>BLANKING                              |

| $\begin{array}{c} {P_{m-1,0}} \ {P_{m-1,1}} \\ {P_{m,0}} \ {P_{m,1}} \\ \dots \\ \dots \\ {P_{m,n-1}} \ {P_{m,n}} \end{array}$    | 00 00 00 00 00 00<br>00 00 00 00 00 00 00           |

| 00 00 00                                                                                                                          | 00 00 00 00 00 00                                   |

| 00 00 00 00 00 00 VERTICAL BLANKING                                                                                               | 00 00 0000 00 00<br>VERTICAL/HORIZONTAL<br>BLANKING |

| 00 00 00 00 00 00<br>00 00 00 00 00 00                                                                                            | 00 00 00 00 00 00<br>00 00 00 00 00 00              |

# **Readout Sequence**

Typically, the readout window is set to a region including only active pixels. The user has the option of reading out dark regions of the array, but if this is done, consideration must be given to how the sensor reads the dark regions for its own purposes.

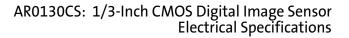

# **Parallel Output Data Timing**

The output images are divided into frames, which are further divided into lines. By default, the sensor produces 968 rows of 1288 columns each. The FV and LV signals indicate the boundaries between frames and lines, respectively. PIXCLK can be used as a clock to latch the data. For each PIXCLK cycle, with respect to the falling edge, one 12-bit pixel datum outputs on the DOUT pins. When both FV and LV are asserted, the pixel is valid. PIXCLK cycles that occur when FV is de-asserted are called vertical blanking. PIXCLK cycles that occur when only LV is de-asserted are called horizontal blanking.

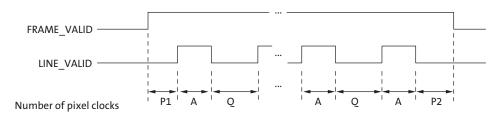

#### Figure 9: Default Pixel Output Timing

#### LV and FV

The timing of the FV and LV outputs is closely related to the row time and the frame time.

FV will be asserted for an integral number of row times, which will normally be equal to the height of the output image.

LV will be asserted during the valid pixels of each row. The leading edge of LV will be offset from the leading edge of FV by 6 PIXCLKs. Normally, LV will only be asserted if FV is asserted; this is configurable as described below.

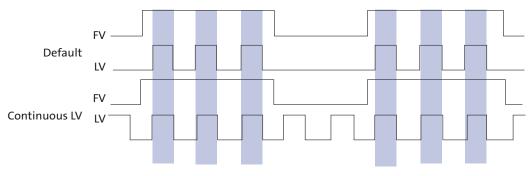

#### LV Format Options

The default situation is for LV to be de-asserted when FV is de-asserted. By configuring R0x306E[1:0], the LV signal can take two different output formats. The formats for reading out four lines and two vertical blanking lines are shown in Figure 10.

#### Figure 10: LV Format Options

The timing of an entire frame is shown in Figure 11: "Line Timing and FRAME\_VALID/ LINE\_VALID Signals," on page 13.

# **Frame Time**

The pixel clock (PIXCLK) represents the time needed to sample 1 pixel from the array. The sensor outputs data at the maximum rate of 1 pixel per PIXCLK. One row time (<sup>t</sup>ROW) is the period from the first pixel output in a row to the first pixel output in the next row. The row time and frame time are defined by equations in Table 4.

# Figure 11: Line Timing and FRAME\_VALID/LINE\_VALID Signals

#### Table 4: Frame Time (Example Based on 1280 x 960, 45 Frames Per Second)

| Parameter                   | Name                 | Equation                                                                                                               | Timing at 74.25 MHz                 |

|-----------------------------|----------------------|------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

| А                           | Active data time     | Context A: R0x3008 - R0x3004 + 1<br>Context B: R0x308E - R0x308A + 1                                                   | 1280 pixel clocks<br>= 17.23μs      |

| P1                          | Frame start blanking | 6 (fixed)                                                                                                              | 6 pixel clocks<br>= 0.08μs          |

| P2                          | Frame end blanking   | 6 (fixed)                                                                                                              | 6 pixel clocks<br>= 0.08μs          |

| Q                           | Horizontal blanking  | R0x300C - A                                                                                                            | 370 pixel clocks<br>= 4.98μs        |

| A+Q (tROW)                  | Line (Row) time      | R0x300C                                                                                                                | 1650 pixel clocks<br>= 22.22μs      |

| v                           | Vertical blanking    | cal blanking Context A: (R0x300A-(R0x3006-R0x3002+1)) x (A + Q)<br>Context B: ((R0x30AA-(R0x3090-R0x308C+1)) x (A + Q) |                                     |

| Nrows x (t <sub>ROW</sub> ) | Frame valid time     | Context A: ((R0x3006-R0x3002+1)*(A+Q))-Q+P1+P2<br>Context B: ((R0x3090-R0x308C+1)*(A+Q))-Q+P1+P2                       | 1,583,642 pixel clocks<br>= 21.33ms |

| F                           | Total frame time     | V + (Nrows x (A + Q))                                                                                                  | 1,633,500 pixel clocks<br>= 22.22ms |

Sensor timing is shown in terms of pixel clock cycles (see Figure 8 on page 11). The recommended pixel clock frequency is 74.25 MHz. The vertical blanking and the total frame time equations assume that the integration time (coarse integration time plus fine integration time) is less than the number of active lines plus the blanking lines:

Window Height + Vertical Blanking

(EQ 1)

If this is not the case, the number of integration lines must be used instead to determine the frame time, (see Table 5). In this example, it is assumed that the coarse integration time control is programmed with 2000 rows and the fine shutter width total is zero.

For Master mode, if the integration time registers exceed the total readout time, then the vertical blanking time is internally extended automatically to adjust for the additional integration time required. This extended value is **not** written back to the frame\_length\_lines register. The frame\_length\_lines register can be used to adjust frame-to-frame readout time. This register does not affect the exposure time but it may extend the readout time.

#### Table 5: Frame Time: Long Integration Time

| Paramet | er Name                                  |                                                                                                            | Default Timing<br>at 74.25 MHz      |

|---------|------------------------------------------|------------------------------------------------------------------------------------------------------------|-------------------------------------|

| F'      | Total frame time (long integration time) | Context A: (R0x3012 x (A + Q)) + R0x3014 + P1 + P2<br>Context B: (R0x3016 x (A + Q)) + V R0x3018 + P1 + P2 | 3,300,012 pixel clocks<br>= 44.44ms |

Note: The AR0130 uses column parallel analog-digital converters; thus short line timing is not possible. The minimum total line time is 1390 columns (horizontal width + horizontal blanking). The minimum horizontal blanking is 110.

#### **Exposure**

Total integration time is the result of Coarse\_Integration\_Time and Fine\_Integration\_-Time registers, and depends also on whether manual or automatic exposure is selected.

The actual total integration time, t<sub>INT</sub> is defined as:

$$t_{INT} = t_{INTCoarse} - 410 - t_{INTFine} \tag{EQ 2}$$

= (number of lines of integration x line time) - (410 pixel clocks of conversion time overhead) - (number of pixels of integration x pixel time)

where:

- Number of Lines of Integration (Auto Exposure Control: Enabled)

When automatic exposure control (AEC) is enabled, the number of lines of integration may vary from frame to frame, with the limits controlled by R0x311E (minimum auto exposure time) and R0x311C (maximum auto exposure time).

- Number of Lines of Integration (Auto Exposure Control: Disabled)

If AEC is disabled, the number of lines of integration equals the value in R0x3012 (context A) or R0x3016 (context B).

- Number of Pixels of Integration The number of fine shutter width pixels is independent of AEC mode (enabled or disabled):

- Context A: the number of pixels of integration equals the value in R0x3014.

- Context B: the number of pixels of integration equals the value in R0x3018.

Typically, the value of the Coarse\_Integration\_Time register is limited to the number of lines per frame (which includes vertical blanking lines), such that the frame rate is not affected by the integration time. For more information on coarse and fine integration time settings limits, please refer to the Register Reference document.

# **Real-Time Context Switching**

In the AR0130, the user may switch between two full register sets (listed in Table 6) by writing to a context switch change bit in R0x30B0[13]. This context switch will change all registers (no shadowing) at the frame start time and have the new values apply to the immediate next exposure and readout time.

#### Table 6: Real-Time Context-Switchable Registers

|                         | Register Number |              |  |  |  |

|-------------------------|-----------------|--------------|--|--|--|

| Register Description    | Context A       | Context B    |  |  |  |

| Y_Addr_Start            | R0x3002         | R0x308C      |  |  |  |

| X_Addr_Start            | R0x3004         | R0x308A      |  |  |  |

| Y_Addr_End              | R0x3006         | R0x3090      |  |  |  |

| X_Addr_End              | R0x3008         | R0x308E      |  |  |  |

| Coarse_Integration_Time | R0x3012         | R0x3016      |  |  |  |

| Fine_Integration_Time   | R0x3014         | R0x3018      |  |  |  |

| Y_Odd_Inc               | R0x30A6         | R0x30A8      |  |  |  |

| Green1_Gain (GreenR)    | R0x3056         | R0x30BC      |  |  |  |

| Blue_Gain               | R0x3058         | R0x30BE      |  |  |  |

| Red_Gain                | R0x305A         | R0x30C0      |  |  |  |

| Green2_Gain (GreenB)    | R0x305C         | R0x30C2      |  |  |  |

| Global_Gain             | R0x305E         | R0x30C4      |  |  |  |

| Analog Gain             | R0x30B0[5:4]    | R0x30B0[9:8] |  |  |  |

| Frame_Length_Lines      | R0x300A         | R0x30AA      |  |  |  |

| Digital_Binning         | R0x3032[1:0]    | R0x3032[5:4] |  |  |  |

# Features

|                     | See the AR0130 Register Reference for additional details.                                                                                                                                                                                                                                                                                                                                                              |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reset               |                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                     | The AR0130 may be reset by using RESET_BAR (active LOW) or the reset register.                                                                                                                                                                                                                                                                                                                                         |

| Hard Reset of Logic |                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                     | The RESET_BAR pin can be connected to an external RC circuit for simplicity. The recommended RC circuit uses a $10k\Omega$ resistor and a $0.1\mu$ F capacitor. The rise time for the RC circuit is $1\mu$ s maximum.                                                                                                                                                                                                  |

| Soft Reset of Logic |                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                     | Soft reset of logic is controlled by the R0x301A Reset register. Bit 0 is used to reset the digital logic of the sensor while preserving the existing two-wire serial interface configuration. Furthermore, by asserting the soft reset, the sensor aborts the current frame it is processing and starts a new frame. This bit is a self-resetting bit and also returns to "0" during two-wire serial interface reads. |

| Clocks              |                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                     | The AR0130 requires one clock input (EXTCLK).                                                                                                                                                                                                                                                                                                                                                                          |

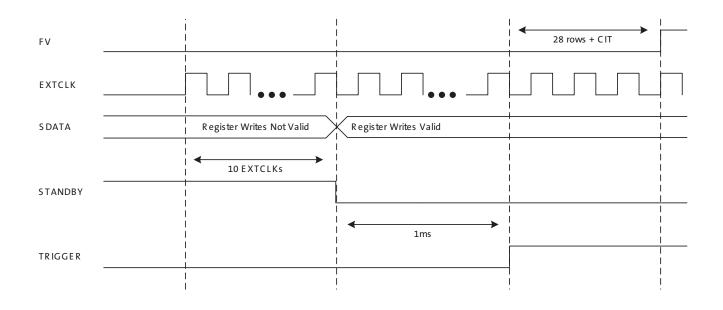

#### **PLL-Generated Master Clock**

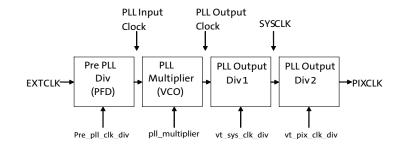

The PLL contains a prescaler to divide the input clock applied on EXTCLK, a VCO to multiply the prescaler output, and two divider stages to generate the output clock. The clocking structure is shown in Figure 12. PLL control registers can be programmed to generate desired master clock frequency.

**Note:** The PLL control registers must be programmed while the sensor is in the software Standby state. The effect of programming the PLL divisors while the sensor is in the streaming state is undefined.

#### Figure 12: PLL-Generated Master Clock PLL Setup

The PLL is enabled by default on the AR0130.

#### To Configure and Use the PLL:

- 1. Bring the AR0130 up as normal; make sure that <sup>f</sup>EXTCLK is between 6 and 50MHz and ensure the sensor is in software standby (R0x301A[2]= 0). PLL control registers must be set in software standby.

- 2. Set pll\_multiplier, pre\_pll\_clk\_div, vt\_sys\_clk\_div, and vt\_pix\_clk\_div based on the desired input (*f*<sub>EXTCLK</sub>) and output (*f*<sub>PIXCLK</sub>) frequencies. Determine the M, N, P1, and P2 values to achieve the desired *f*<sub>PIXCLK</sub> using this formula:

$$\begin{split} f_{PIXCLK} &= (\mathbf{f}_{\text{EXTCLK}} \times M) / (N \times P1 \ x \ P2) \\ where \\ M &= PLL\_Multiplier \ (R0x3030) \\ N &= Pre\_PLL\_Clk\_Div \ (R0x302E) \\ P1 &= Vt\_Sys\_Clk\_Div \ (R0x302C) \\ P2 &= Vt\_PIX\_Clk\_Div \ (R0x302A) \end{split}$$

- 3. Wait 1ms to ensure that the VCO has locked.

- 4. Set R0x301A[2]=1 to enable streaming and to switch from EXTCLK to the PLL-generated clock.

- **Notes:** 1. The PLL can be bypassed at any time (sensor will run directly off EXTCLK) by setting R0x30B0[14]=1. However, only the parallel data interface is supported with the PLL bypassed. The PLL is always bypassed in software standby mode. To disable the PLL, the sensor must be in standby mode (R0x301A[2] = 0)

- 2. The following restrictions apply to the PLL tuning parameters:

$32 \le M \le 255$  $1 \le N \le 63$

$$l \leq Pl \leq 16$$

#### $4 \leq P2 \leq 16$

Additionally, the VCO frequency, defined as  $f_{\rm VCO} = f_{\rm EXTCLK} \times M / N$  must be within 384-768MHz and the EXTCLK must be within 2MHz =<  $f_{\rm EXTCLK} / N$  <= 24MHz

The user can utilize the Register Wizard tool accompanying DevWare to generate PLL settings given a supplied input clock and desired output frequency.

#### Spread-Spectrum Clocking

To facilitate improved EMI performance, the external clock input allows for spread spectrum sources, with no impact on image quality. Limits of the spread spectrum input clock are:

- 5% maximum clock modulation

- 35 KHz maximum modulation frequency

- Accepts triangle wave modulation, as well as sine or modified triangle modulations.

#### Stream/Standby Control

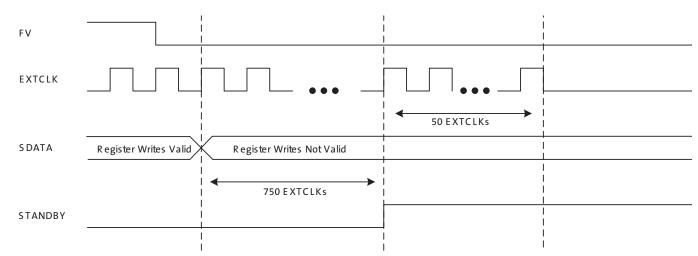

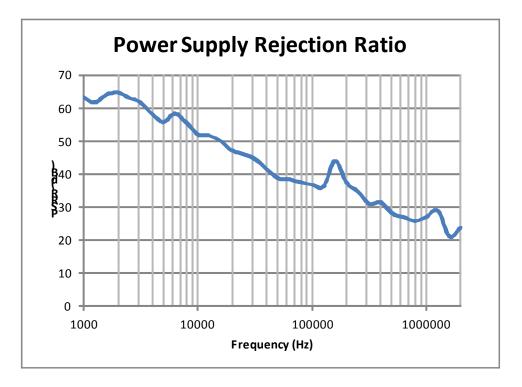

The sensor supports two standby modes: Hard Standby and Soft Standby. In both modes, external clock can be optionally disabled to further minimize power consumption. If this is done, then the "Power-Up Sequence" on page 44 must be followed.

#### Soft Standby

Soft Standby is a low power state that is controlled through register R0x301A[2]. Depending on the value of R0x301A[4], the sensor will go to standby after completion of the current frame readout (default behavior) or after the completion of the current row readout. When the sensor comes back from Soft Standby, previously written register settings are still maintained.

A specific sequence needs to be followed to enter and exit from Soft Standby.

#### To Enter Soft Standby:

- 1. R0x301A[12] = 1 if serial mode was used

- 2. Set R0x301A[2] = 0

3. External clock can be turned off to further minimize power consumption (Optional)

#### To Exit Soft Standby:

- 1. Enable external clock if it was turned off

- 2. R0x301A[2] = 1

- 3. R0x301A[12] = 0 if serial mode is used

#### Hard Standby

| Hard Standby puts the sensor in lower power state; previously written register settings are still maintained. |

|---------------------------------------------------------------------------------------------------------------|

| A specific sequence needs to be followed to enter and exit from Hard Standby.                                 |

#### To Enter Hard Standby:

- 1. R0x301A[8] = 1

- 2. R0x301A[12] = 1 if serial mode was used

- 3. Assert STANDBY pin

- 4. External clock can be turned off to further minimize power consumption (Optional)

#### To Exit Hard Standby:

- 1. Enable external clock if it was turned off

- 2. De-assert STANDBY pin

- 3. Set R0x301A[8] = 0

# **Window Control**

Registers x\_addr\_start, x\_addr\_end, y\_addr\_start, and y\_addr\_end control the size and starting coordinates of the image window.

The exact window height and width out of the sensor is determined by the difference between the Y address start and end registers or the X address start and end registers, respectively.

The AR0130 allows different window sizes for context A and context B.

# **Blanking Control**

Horizontal blank and vertical blank times are controlled by the line\_length\_pck and frame\_length\_lines registers, respectively.

- Horizontal blanking is specified in terms of pixel clocks. It is calculated by subtracting the X window size from the line\_length\_pck register. The minimum horizontal blanking is 110 pixel clocks.

- Vertical blanking is specified in terms of numbers of lines. It is calculated by subtracting the Y window size from the frame\_length\_lines register. The minimum vertical blanking is 26 lines.

The actual imager timing can be calculated using Table 4 on page 13 and Table 5 on page 14, which describe the Line Timing and FV/LV signals.

**Digital Binning**

By default, the resolution of the output image is the full width and height of the FOV as defined above. The output resolution can be reduced by digital binning. For RGB and monochrome mode, this is set by the register R0x3032. For Context A, use bits [1:0], for Context B, use bits [5:4]. Available settings are:

00 = No binning

01 = Horizontal binning

10 = Horizontal and vertical binning

Binning gives the advantage of reducing noise at the cost of reduced resolution. When both horizontal and vertical binning are used, a 2x improvement in SNR is achieved therefore improving low light performance

# **Bayer Space Resampling**

All of the pixels in the FOV contribute to the output image in digital binning mode. This can result in a more pleasing output image with reduced subsampling artifacts. It also improves low-light performance. For RGB mode, resampling can be enabled by setting of register 0x306E[4] = 1.

#### Mirror

#### **Column Mirror Image**

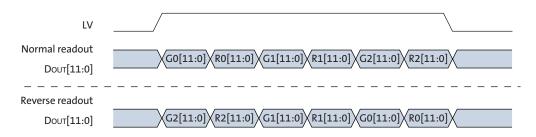

By setting R0x3040[14] = 1, the readout order of the columns is reversed, as shown in Figure 15. The starting color, and therefore the Bayer pattern, is preserved when mirroring the columns.

When using horizontal mirror mode, the user must retrigger column correction. Please refer to the column correction section to see the procedure for column correction retriggering. Bayer resampling must be enabled, by setting bit 4 of register  $0 \ge 306E[4] = 1$ .

#### Figure 15: Six Pixels in Normal and Column Mirror Readout Modes

#### **Row Mirror Image**

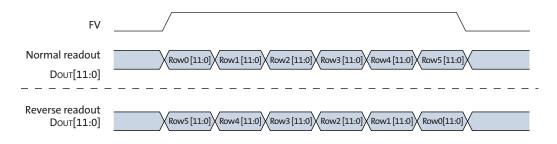

By setting R0x3040[15] = 1, the readout order of the rows is reversed as shown in Figure 16. The starting Bayer color pixel is maintained in this mode by a 1-pixel shift in the imaging array. When using horizontal mirror mode, the user must retrigger column correction. Please refer to the column correction section to see the procedure for column correction retriggering.

#### Figure 16: Six Rows in Normal and Row Mirror Readout Modes

# **Maintaining a Constant Frame Rate**

Maintaining a constant frame rate while continuing to have the ability to adjust certain parameters is the desired scenario. This is not always possible, however, because register updates are synchronized to the read pointer, and the shutter pointer for a frame is usually active during the readout of the previous frame. Therefore, any register changes that could affect the row time or the set of rows sampled causes the shutter pointer to start over at the beginning of the next frame.

By default, the following register fields cause a "bubble" in the output rate (that is, the vertical blank increases for one frame) if they are written in video mode, even if the new value would not change the resulting frame rate. The following list shows only a few examples of such registers; a full listing can be seen in the AR0130 Register Reference.

- x\_addr\_start

- x\_addr\_end

- y\_addr\_start

- y\_addr\_end

- frame\_length\_lines

- line\_length\_pclk

- coarse\_integration\_time

- fine\_integration\_time

- read\_mode

The size of this bubble is (Integration\_Time  $\times$   $t_{ROW}$ ), calculating the row time according to the new settings.

The Coarse\_Integration\_Time and Fine\_Integration\_Time fields may be written to without causing a bubble in the output rate under certain circumstances. Because the shutter sequence for the next frame often is active during the output of the current frame, this would not be possible without special provisions in the hardware. Writes to these registers take effect two frames after the frame they are written, which allows the integration time to increase without interrupting the output or producing a corrupt frame (as long as the change in integration time does not affect the frame time).

#### Synchronizing Register Writes to Frame Boundaries

Changes to most register fields that affect the size or brightness of an image take effect on the frame after the one during which they are written. These fields are noted as "synchronized to frame boundaries" in the AR0130 Register Reference. To ensure that a register update takes effect on the next frame, the write operation must be completed after the leading edge of FV and before the trailing edge of FV.

As a special case, in single frame mode, register writes that occur after FV but before the next trigger will take effect immediately on the next frame, as if there had been a Restart. However, if the trigger for the next frame occurs during FV, register writes take effect as with video mode.

Fields not identified as being frame-synchronized are updated immediately after the register write is completed. The effect of these registers on the next frame can be difficult to predict if they affect the shutter pointer.

#### Restart

To restart the AR0130 at any time during the operation of the sensor, write a "1" to the Restart register (R0x301A[1] = 1). This has two effects: first, the current frame is interrupted immediately. Second, any writes to frame-synchronized registers and the shutter width registers take effect immediately, and a new frame starts (in video mode). The current row completes before the new frame is started, so the time between issuing the Restart and the beginning of the next frame can vary by about  $t_{ROW}$ .

#### Image Acquisition Modes

The AR0130 supports two image acquisition modes: video (also known as master) and single frame.

#### Video

The video mode takes pictures by scanning the rows of the sensor twice. On the first scan, each row is released from reset, starting the exposure. On the second scan, the row is sampled, processed, and returned to the reset state. The exposure for any row is therefore the time between the first and second scans. Each row is exposed for the same duration, but at slightly different point in time, which can cause a shear in moving subjects as is typical with electronic rolling shutter sensors.

#### **Single Frame**

The single-frame mode operates similar to the video mode. It also scans the rows of the sensor twice, first to reset the rows and second to read the rows. Unlike video mode where a continuous stream of images are output from the image sensor, the single-frame mode outputs a single frame in response to a high state placed on the TRIGGER input pin. As long as the TRIGGER pin is held in a high state, new images will be read out. After the TRIGGER pin is returned to a low state, the image sensor will not output any new images and will wait for the next high state on the TRIGGER pin.

The TRIGGER pin state is detected during the vertical blanking period (i.e. the FV signal is low). The pin is level sensitive rather than edge sensitive. As such, image integration will only begin when the sensor detects that the TRIGGER pin has been held high for 3 consecutive clock cycles.

During integration time of single-frame mode and video mode, the FLASH output pin is at high.

#### **Continuous Trigger**

In certain applications, multiple sensors need to have their video streams synchronized (E.g. surround view or panorama view applications). The TRIGGER pin can also be used to synchronize output of multiple image sensors together and still get a video stream. This is called continuous trigger mode. Continuous trigger is enabled by holding the TRIGGER pin high. Alternatively, the TRIGGER pin can be held high until the stream bit is enabled (R0x301A[2]=1) then can be released for continuous synchronized video streaming.

If the TRIGGER pins for all connected AR0130 sensors are connected to the same control signal, all sensors will receive the trigger pulse at the same time. If they are configured to have the same frame timing, then the usage of the TRIGGER pin guarantees that all sensors will be synchronized within 1 PIXCLK cycle if PLL is disabled, or 2 PIXCLK cycles if PLL is enabled.

With continuous trigger mode, the application can now make use of the video streaming mode while guaranteeing that all sensor outputs are synchronized. As long as the initial trigger for the sensors takes place at the same time, all subsequent video streams will be synchronous.

#### **Automatic Exposure Control**

The integrated automatic exposure control (AEC) is responsible for ensuring that optimal settings of exposure and gain are computed and updated every other frame. AEC can be enabled or disabled by R0x3100[0].

When AEC is disabled (R0x3100[0] = 0), the sensor uses the manual exposure value in coarse and fine shutter width registers and the manual gain value in the gain registers.

When AEC is enabled (R0x3100[0]=1), the target luma value is set by R0x3102. For the AR0130 this target luma has a default value of 0x0800 or about half scale.

The exposure control measures current scene luminosity by accumulating a histogram of pixel values while reading out a frame. It then compares the current luminosity to the desired output luminosity. Finally, the appropriate adjustments are made to the exposure time and gain. All pixels are used, regardless of color or mono mode.

AEC does not work if digital binning is enabled.

#### **Embedded Data and Statistics**

The AR0130 has the capability to output image data and statistics embedded within the frame timing. There are two types of information embedded within the frame readout:

- 1. Embedded Data: If enabled, these are displayed on the two rows immediately before the first active pixel row is displayed.

- 2. Embedded Statistics: If enabled, these are displayed on the two rows immediately after the last active pixel row is displayed.

- Note: Both embedded statistics and data must be enabled and disabled together.

#### Figure 17: Frame Format with Embedded Data Lines Enabled

#### **Embedded** Data

The embedded data contains the configuration of the image being displayed. This includes all register settings used to capture the current frame. The registers embedded in these rows are as follows:

Line 1: Registers R0x3000 to R0x312F

Line 2: Registers R0x3136 to R0x31BF, R0x31D0 to R0x31FF

**Note:** All undefined registers will have a value of 0.

In parallel mode, since the pixel word depth is 12-bits/pixel, the sensor 16-bit register data will be transferred over 2 pixels where the register data will be broken up into 8 MSB and 8 LSB. The alignment of the 8-bit data will be on the 8 MSB bits of the 12-bit pixel word. For example, of a register value of 0x1234 is to be transmitted, it will be transmitted over 2, 12-bit pixels as follows: 0x120, 0x340.

The first pixel of each line in the embedded data is a tag value of 0x0A0. This signifies that all subsequent data is 8 bit data aligned to the MSB of the 12-bit pixel.

The figure below summarizes how the embedded data transmission looks like. It should be noted that data, as shown in Figure 18, is aligned to the MSB of each word:

#### Figure 18: Format of Embedded Data Output within a Frame

|             | data_format_<br>code =8'h0A | 8'hAA | {register_<br>address_MSB} | 8'hA5 | {register_<br>address_LSB} | 8'h5A | {register_<br>value_MSB} | 8'h5A |

|-------------|-----------------------------|-------|----------------------------|-------|----------------------------|-------|--------------------------|-------|

| Data line 1 |                             |       | {register_<br>value_LSB}   | 8'h5A |                            |       |                          |       |

|             | data_format_<br>code =8'h0A | 8'hAA | {register_<br>address_MSB} | 8'hA5 | {register_<br>address_LSB} | 8'h5A | {register_<br>value_MSB} | 8'h5A |

| Data line 2 |                             |       | {register_<br>value_LSB}   | 8'h5A |                            |       |                          |       |

The data embedded in these rows are as follows:

- 0x0A0 identifier

- 0xAA0

- Register Address MSB of the first register

- 0xA50

- Register Address LSB of the first register

- 0x5A0

- Register Value MSB of the first register addressed

- 0x5A0

- Register Value LSB of the first register addressed

- 0x5A0

- Register Value MSB of the register at first address + 2

- 0x5A0

- Register Value LSB of the register at first address + 2

- 0x5A0

- etc.

#### **Embedded Statistics**

The embedded statistics contain frame identifiers and histogram information of the image in the frame. This can be used by downstream auto-exposure algorithm blocks to make decisions about exposure adjustment.

This histogram is divided into 244 bins with a bin spacing of 64 evenly spaced bins for digital code values 0 to  $2^{12}$ , 120 evenly spaced bins for values  $2^{12}$  to  $2^{16}$ , 60 evenly spaced bins for values  $2^{16}$  to  $2^{20}$ .

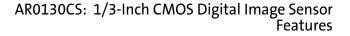

The first pixel of each line in the embedded statistics is a tag value of 0x0B0. This signifies that all subsequent statistics data is 10 bit data aligned to the MSB of the 12-bit pixel.

The figure below summarizes how the embedded statistics transmission looks like. It should be noted that data, as shown in Figure 19, is aligned to the msb of each word:

#### Figure 19: Format of Embedded Statistics Output within a Frame

The statistics embedded in these rows are as follows:

Line 1:

- 0x0B0 identifier

- Register 0x303A frame\_count

- Register 0x31D2 frame ID

- Histogram data histogram bins 0-243

Line 2:

- 0x0B0 (identifier)

- Mean

- Histogram Begin

- Histogram End

- Low End Histogram Mean

- Percentage of Pixels Below Low End Mean

- Normal Absolute Deviation

#### Gain

| Digital Gain           |                                                                                                                                                                                                                                                                                                      |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                        | Digital gain can be controlled globally by R0x305E (Context A) or R0x30C4 (Context B).<br>There are also registers that allow individual control over each Bayer color (GreenR,<br>GreenB, Red, Blue).                                                                                               |

|                        | The format for digital gain setting is <i>xxx.yyyyy</i> where 0b00100000 represents a 1x gain setting and 0b00110000 represents a 1.5x gain setting. The step size for yyyyy is 0.03125 while the step size for xxx is 1. Therefore to set a gain of 2.09375 one would set digital gain to 01000011. |

| Analog Gain            |                                                                                                                                                                                                                                                                                                      |

|                        | The AR0130 has a column parallel architecture and therefore has an Analog gain stage per column.                                                                                                                                                                                                     |

|                        | There are two stages of analog gain, the first stage can be set to 1x, 2x, 4x or 8x. This is can be set in R0x30B0[5:4](Context A) or R0x30B0[9:8] (Context B). The second stage is capable of setting an additional 1x or 1.25x gain which can be set in R0x3EE4[8].                                |

|                        | This allows the maximum possible analog gain to be set to 10x.                                                                                                                                                                                                                                       |

| Black Level Correction |                                                                                                                                                                                                                                                                                                      |

|                        | Black level correction is handled automatically by the image sensor. No adjustments are provided except to enable or disable this feature. Setting R0x30EA[15] disables the automatic black level correction. Default setting is for automatic black level calibration to be enabled.                |

The automatic black level correction measures the average value of pixels from a set of optically black lines in the image sensor. The pixels are averaged as if they were light-sensitive and passed through the appropriate gain. This line average is then digitally low-pass filtered over many frames to remove temporal noise and random instabilities associated with this measurement. The new filtered average is then compared to a minimum acceptable level, low threshold, and a maximum acceptable level, high threshold. If the average is lower than the minimum acceptable level, the offset correction value is increased by a predetermined amount. If it is above the maximum level, the offset correction value is decreased by a predetermined amount. The high and low thresholds have been calculated to avoid oscillation of the black level from below to above the targeted black level. At high gain, long exposure, and high temperature conditions, the performance of this function can degrade.

#### **Row-wise Noise Correction**

Row (Line)-wise Noise Correction is handled automatically by the image sensor. No adjustments are provided except to enable or disable this feature. Clearing R0x3044[10] disables the row noise correction. Default setting is for row noise correction to be enabled.

Row-wise noise correction is performed by calculating an average from a set of optically black pixels at the start of each line and then applying each average to all the active pixels of the line.

### **Column Correction**

The AR0130 uses column parallel readout architecture to achieve fast frame rate. Without any corrections, the consequence of this architecture is that different column signal paths have slightly different offsets that might show up on the final image as structured fixed pattern noise.

AR0130 has column correction circuitry that measures this offset and removes it from the image before output. This is done by sampling dark rows containing tied pixels and measuring an offset coefficient per column to be corrected later in the signal path.

Column correction can be enabled/disabled via R0x30D4[15]. Additionally, the number of rows used for this offset coefficient measurement is set in R0x30D4[3:0]. By default this register is set to 0x7, which means that 8 rows are used. This is the recommended value. Other control features regarding column correction can be viewed in the AR0130 Register reference. Any changes to column correction settings need to be done when the sensor streaming is disabled and the appropriate triggering sequence must be followed as described below.

#### **Column Correction Triggering**

Column correction requires a special procedure to trigger depending on which state the sensor is in.

#### Column Triggering on Startup

When streaming the sensor for the first time after power-up, a special sequence needs to be followed to make sure that the column correction coefficients are internally calculated properly.

- 1. Follow proper power up sequence for power supplies and clocks

- 2. Apply sequencer settings if needed

- 3. Apply frame timing and PLL settings as required by application

- 4. Set analog gain to 1x and low conversion gain

- 5. Enable column correction and settings

- 6. Disable auto re-trigger for change in conversion gain or col\_gain, and enable column correction always. (R0x30BA = 0x0008).

- 7. Enable streaming (R0x301A[2] = 1) or drive the TRIGGER pin HIGH.

- 8. Wait 9 frames to settle. (First frame after coming up from standby is internally column correction disabled.)

- 9. Disable streaming (R0x301A[2] = 0) or drive the TRIGGER pin LOW.

After this, the sensor has calculated the proper column correction coefficients and the sensor is ready for streaming. Any other settings (including gain, integration time and conversion gain etc.) can be done afterwards without affecting column correction.

#### Column Correction Retriggering Due to Mode Change

Since column offsets is sensitive to changes in the analog signal path, such changes require column correction circuitry to be retriggered for the new path. Examples of such mode changes include: horizontal mirror, vertical mirror, changes to column correction settings.

When such changes take place, the following sequence needs to take place:

- 1. Disable streaming (R0x301A[2]=0) or drive the TRIGGER pin LOW.

- 2. Enable streaming (R0x301A[2]=1) or drive the TRIGGER pin HIGH.

- 3. Wait 9 frames to settle.

**Note:** The above steps are not needed if the sensor is being reset (soft or hard reset) upon the mode change.

### **Test Patterns**

The AR0130 has the capability of injecting a number of test patterns into the top of the datapath to debug the digital logic. With one of the test patterns activated, any of the datapath functions can be enabled to exercise it in a deterministic fashion. Test patterns are selected by Test\_Pattern\_Mode register (R0x3070). Only one of the test patterns can be enabled at a given point in time by setting the Test\_Pattern\_Mode register according to Table 7. When test patterns are enabled the active area will receive the value specified by the selected test pattern and the dark pixels will receive the value in Test\_Pattern\_Green (R0x3074 and R0x3078) for green pixels, Test\_Pattern\_Blue (R0x3076) for blue pixels, and Test\_Pattern\_Red (R0x3072) for red pixels.

Note: Turn off black level calibration (BLC) when Test Pattern is enabled.

#### Table 7: Test Pattern Modes

| Test_Pattern_Mode | Test Pattern Output                 |

|-------------------|-------------------------------------|

| 0                 | No test pattern (normal operation)  |

| 1                 | Solid color test pattern            |

| 2                 | 100% color bar test pattern         |

| 3                 | Fade-to-gray color bar test pattern |

| 256               | Walking 1s test pattern (12-bit)    |

#### **Color Field**

When the color field mode is selected, the value for each pixel is determined by its color. Green pixels will receive the value in Test\_Pattern\_Green, red pixels will receive the value in Test\_Pattern\_Red, and blue pixels will receive the value in Test\_Pattern\_Blue.

#### **Vertical Color Bars**

When the vertical color bars mode is selected, a typical color bar pattern will be sent through the digital pipeline.

#### Walking 1s

When the walking 1s mode is selected, a walking 1s pattern will be sent through the digital pipeline. The first value in each row is 1.

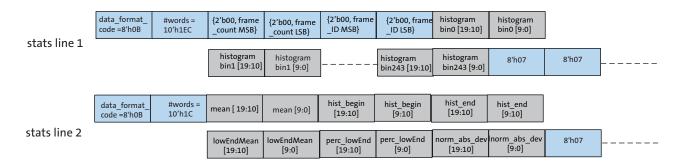

# **Two-Wire Serial Register Interface**

ΟN

|                                   | The two-wire serial interface bus enables read/write access to control and status regis-<br>ters within the AR0130. This interface is designed to be compatible with the electrical<br>characteristics and transfer protocols of the two-wire serial interface specification.                                                                                                                                                                                                                                                                                                                                      |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

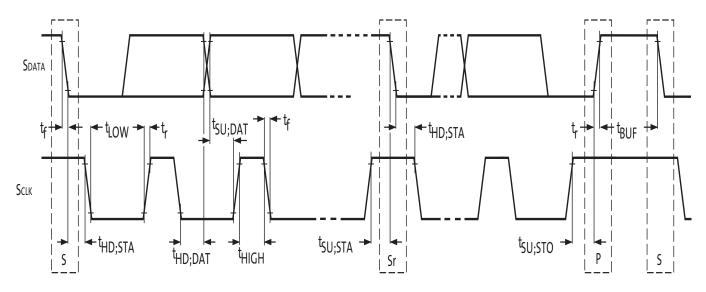

|                                   | The interface protocol uses a master/slave model in which a master controls one or<br>more slave devices. The sensor acts as a slave device. The master generates a clock (SCLK)<br>that is an input to the sensor and is used to synchronize transfers. Data is transferred<br>between the master and the slave on a bidirectional signal (SDATA). SDATA is pulled up to<br>VDD_IO off-chip by a $1.5k\Omega$ resistor. Either the slave or master device can drive SDATA<br>LOW—the interface protocol determines which device is allowed to drive SDATA at any<br>given time.                                   |

|                                   | The protocols described in the two-wire serial interface specification allow the slave device to drive SCLK LOW; the AR0130 uses SCLK as an input only and therefore never drives it LOW.                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Protocol                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Start Condition                   | Data transfers on the two-wire serial interface bus are performed by a sequence of low-<br>level protocol elements: <ol> <li>a (repeated) start condition</li> <li>a slave address/data direction byte</li> <li>an (a no) acknowledge bit</li> <li>a message byte</li> <li>a stop condition</li> </ol> The bus is idle when both SCLK and SDATA are HIGH. Control of the bus is initiated with a start condition, and the bus is released with a stop condition. Only the master can generate the start and stop conditions. A start condition is defined as a HIGH-to-LOW transition on SDATA while SCLK is HIGH. |

|                                   | At the end of a transfer, the master can generate a start condition without previously generating a stop condition; this is known as a "repeated start" or "restart" condition.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Stop Condition                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                   | A stop condition is defined as a LOW-to-HIGH transition on SDATA while SCLK is HIGH.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Data Transfer                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

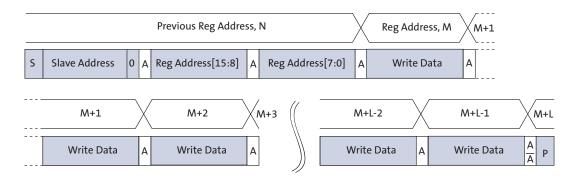

|                                   | Data is transferred serially, 8 bits at a time, with the MSB transmitted first. Each byte of data is followed by an acknowledge bit or a no-acknowledge bit. This data transfer mechanism is used for the slave address/data direction byte and for message bytes.                                                                                                                                                                                                                                                                                                                                                 |

|                                   | One data bit is transferred during each SCLK clock period. SDATA can change when SCLK is LOW and must be stable while SCLK is HIGH.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Slave Address/Data Direction Byte |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

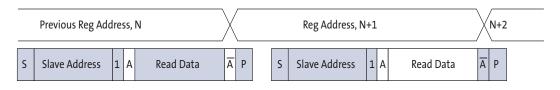

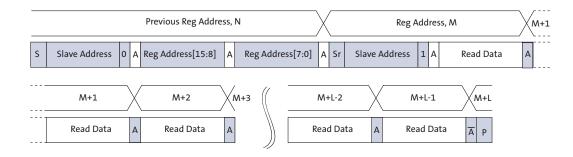

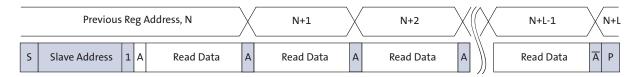

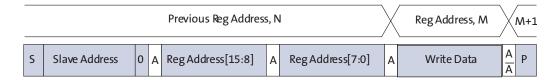

Bits [7:1] of this byte represent the device slave address and bit [0] indicates the data transfer direction. A "0" in bit [0] indicates a WRITE, and a "1" indicates a READ. The default slave addresses used by the AR0130 are 0x20 (write address) and 0x21 (read

|                    | address) in accordance with the specification. Alternate slave addresses of 0x30 (write address) and 0x31 (read address) can be selected by enabling and asserting the SADDR input.                                                                                                                                                                                                                                                                                                                                                                                               |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                    | An alternate slave address can also be programmed through R0x31FC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Message Byte       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                    | Message bytes are used for sending register addresses and register write data to the slave device and for retrieving register read data.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Acknowledge Bit    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                    | Each 8-bit data transfer is followed by an acknowledge bit or a no-acknowledge bit in the SCLK clock period following the data transfer. The transmitter (which is the master when writing, or the slave when reading) releases SDATA. The receiver indicates an acknowledge bit by driving SDATA LOW. As for data transfers, SDATA can change when SCLK is LOW and must be stable while SCLK is HIGH.                                                                                                                                                                            |

| No-Acknowledge Bit |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                    | The no-acknowledge bit is generated when the receiver does not drive SDATA LOW during the SCLK clock period following a data transfer. A no-acknowledge bit is used to terminate a read sequence.                                                                                                                                                                                                                                                                                                                                                                                 |

| Typical Sequence   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                    | A typical READ or WRITE sequence begins by the master generating a start condition on<br>the bus. After the start condition, the master sends the 8-bit slave address/data direction<br>byte. The last bit indicates whether the request is for a read or a write, where a "0" indi-<br>cates a write and a "1" indicates a read. If the address matches the address of the slave<br>device, the slave device acknowledges receipt of the address by generating an acknowl-<br>edge bit on the bus.                                                                               |