## Features

### **High Integration Device Replaces Multiple Parts**

- Serial Nonvolatile Memory

- Real-time Clock (RTC) with Alarm

- Low V<sub>DD</sub> Detection Drives Reset

- Watchdog Window Timer

- Early Power-Fail Warning/NMI

- 16-bit Nonvolatile Event Counter

- Serial Number with Write-lock for Security

### Ferroelectric Nonvolatile RAM

- 256Kb F-RAM

- High Endurance 100 Trillion (10<sup>14</sup>) Read/Writes

- 38 year Data Retention (+75°C)

- NoDelay<sup>TM</sup> Writes

### **Real-time Clock/Calendar**

- Backup Current at 2V,  $1.15 \mu A (max.)$  at +25C

- Seconds through Centuries in BCD format

- Tracks Leap Years through 2099

- Uses Standard 32.768 kHz Crystal

- Software Calibration

- Supports Battery or Capacitor Backup

## Description

The FM33256B device integrates F-RAM memory with the most commonly needed functions for processor-based systems. Major features include nonvolatile memory, real-time clock, low- $V_{DD}$  reset, watchdog timer, nonvolatile event counter, lockable 64-bit serial number area, and general purpose comparator that can be used for a power-fail (NMI) interrupt or other purpose. The device operate from 2.7 to 3.6V.

The FM33256B provides 256Kb memory capacity of nonvolatile F-RAM. Fast write speed and unlimited endurance allow the memory to serve as extra RAM or conventional nonvolatile storage. This memory is truly nonvolatile rather than battery backed.

The real-time clock (RTC) provides time and date information in BCD format. It can be permanently powered from external backup voltage source, either a battery or a capacitor. The timekeeper uses a common external 32.768 kHz crystal and provides a calibration mode that allows software adjustment of timekeeping accuracy.

#### **Processor Companion**

- Active-low Reset Output for V<sub>DD</sub> and Watchdog

- Programmable Low-V<sub>DD</sub> Reset Thresholds

- Manual Reset Filtered and Debounced

- Programmable Watchdog Window Timer

- Nonvolatile Event Counter Tracks System Intrusions or other Events

- Comparator for Power-Fail Interrupt or Other Use

- 64-bit Programmable Serial Number with Lock

### **Fast SPI Interface**

- Up to 16 MHz Maximum Bus Frequency

- RTC, Supervisor Controlled via SPI Interface

- SPI Mode 0 & 3 (CPOL, CPHA=0,0 & 1,1)

#### Easy to Use Configuration

- Operates from 2.7 to 3.6V

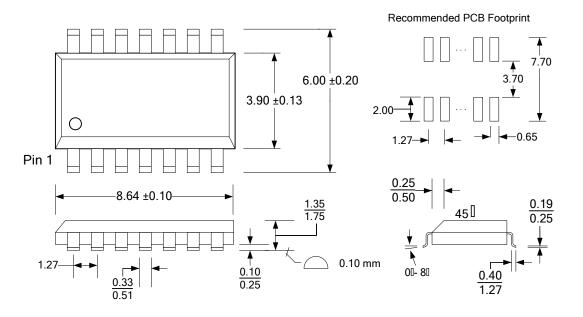

- Small Footprint "Green" 14-pin SOIC (-G)

- Low Operating Current

- -40°C to +85°C Operation

- Underwriters Laboratory (UL) Recognized

The processor companion includes commonly needed CPU support functions. Supervisory functions include a reset output signal controlled by either a low  $V_{DD}$  condition or a watchdog timeout. /RST goes active when  $V_{DD}$  drops below a programmable threshold and remains active for 100 ms (max.) after  $V_{DD}$  rises above the trip point. A programmable watchdog timer runs from 60 ms to 1.8 seconds. The timer may also be programmed for a delayed start, which functions as a window timer. The watchdog timer is optional, but if enabled it will assert the reset signal for 100 ms if not restarted by the host within the time window. A flag-bit indicates the source of the reset.

A comparator on PFI compares an external input pin to the onboard 1.5V reference. This is useful for generating a power-fail interrupt (NMI) but can be used for any purpose. The family also includes a programmable 64-bit serial number that can be locked making it unalterable. Additionally it offers an event counter that tracks the number of rising or falling edges detected on a dedicated input pin. The counter can be programmed to be non-volatile under  $V_{DD}$  power or battery-backed using only  $V_{BAK}$ . If  $V_{BAK}$  is connected to a battery or capacitor, then events will be counted even in the absence of  $V_{DD}$ .

This product conforms to specifications per the terms of the Ramtron standard warranty. The product has completed Ramtron's internal qualification testing and has reached production status.

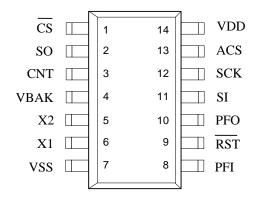

# **Pin Configuration**

| Pin Name | Function                     |  |  |  |  |

|----------|------------------------------|--|--|--|--|

| /CS      | Chip Select                  |  |  |  |  |

| SCK      | Serial Clock                 |  |  |  |  |

| SI       | Serial Data Input            |  |  |  |  |

| SO       | Serial Data Output           |  |  |  |  |

| PFI      | Power Fail Input             |  |  |  |  |

| PFO      | Power Fail Output (NMI)      |  |  |  |  |

| CNT      | Event Counter Input          |  |  |  |  |

| ACS      | Alarm/Calibration/SqWave     |  |  |  |  |

| /RST     | Reset Input/Output           |  |  |  |  |

| X1, X2   | External Crystal Connections |  |  |  |  |

|          | (optional)                   |  |  |  |  |

| VDD      | Supply Voltage               |  |  |  |  |

| VBAK     | Battery-Backup Supply        |  |  |  |  |

| VSS      | Ground                       |  |  |  |  |

## **Pin Descriptions**

| Pin Name | Туре   | Pin Description                                                                                                                                             |

|----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| /CS      | Input  | Chip Select: This active low input activates the device. When high, the device enters low-                                                                  |

|          |        | power standby mode, ignores the SCK and SI inputs, and the SO output is tri-stated.                                                                         |

|          |        | When low, the device internally activates the SCK signal. A falling edge on /CS must                                                                        |

|          |        | occur prior to every op-code.                                                                                                                               |

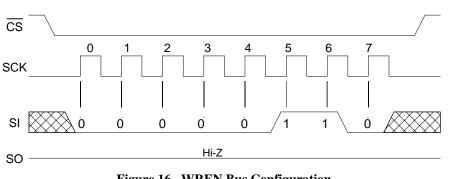

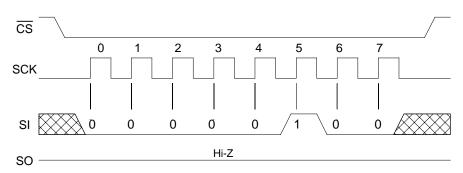

| SCK      | Input  | Serial Clock: All I/O activity is synchronized to the serial clock. Inputs are latched on the                                                               |

|          |        | rising edge and outputs occur on the falling edge. Since the device is static, the clock                                                                    |

|          | _      | frequency may be any value between 0 and 16 MHz and may be interrupted at any time.                                                                         |

| SI       | Input  | Serial Input: All data is input to the device on this pin. The pin is sampled on the rising                                                                 |

|          |        | edge of SCK and is ignored at other times. It should always be driven to a valid logic level                                                                |

|          |        | to meet $I_{DD}$ specifications. The SI pin may be connected to SO for a single pin data                                                                    |

| 50       | 0.1.1  | interface.                                                                                                                                                  |

| SO       | Output | Serial Output: This is the data output pin. It is driven during a read and remains tri-stated                                                               |

|          |        | at all other times. Data transitions are driven on the falling edge of the serial clock. The SO pin may be connected to SI for a single pin data interface. |

| CNT      | Input  | Event Counter Input: This input increments the counter when an edge is detected on this                                                                     |

| CIVI     | Input  | pin. The polarity is programmable and the counter value is nonvolatile or battery-backed,                                                                   |

|          |        | depending on the mode. This pin should be tied to ground if unused.                                                                                         |

| ACS      | Output | Alarm/Calibration/SquareWave: This is an open-drain output that requires an external                                                                        |

|          | ourput | pullup resistor. In normal operation, this pin acts as the active-low alarm output. In                                                                      |

|          |        | Calibration mode, a 512 Hz square-wave is driven out. In SquareWave mode, the user                                                                          |

|          |        | may select a frequency of 1, 512, 4096, or 32768 Hz to be used as a continuous output.                                                                      |

|          |        | The SquareWave mode is entered by clearing the AL/SW and CAL bits in register 18h.                                                                          |

| X1, X2   | I/O    | 32.768 kHz crystal connection (see Crystal Type section for suggestions). See AN407                                                                         |

|          |        | app. note for details on how to connect external oscillator.                                                                                                |

| /RST     | I/O    | Reset: This active-low output is open drain with weak pull-up. It is also an input when                                                                     |

|          |        | used as a manual reset. This pin should be left floating if unused.                                                                                         |

| PFI      | Input  | Early Power-fail Input: Typically connected to an unregulated power supply to detect an                                                                     |

|          |        | early power failure. This pin must be tied to ground if unused.                                                                                             |

| PFO      | Output | Early Power-fail Output: This pin is the early power-fail output and is typically used to                                                                   |

|          | -      | drive a microcontroller NMI pin. PFO drives low when the PFI voltage is <1.5V.                                                                              |

| VBAK     | Supply | Backup supply voltage: A 3V battery or a large value capacitor. If no backup supply is                                                                      |

|          |        | used, this pin should be tied to $V_{SS}$ and the VBC bit should be cleared. The trickle charger                                                            |

| UDD      |        | is UL recognized and ensures no excessive current when using a lithium battery.                                                                             |

| VDD      | Supply | Supply Voltage.                                                                                                                                             |

| VSS      | Supply | Ground                                                                                                                                                      |

This product conforms to specifications per the terms of the Ramtron standard warranty. The product has completed Ramtron's internal qualification testing and has reached production status.

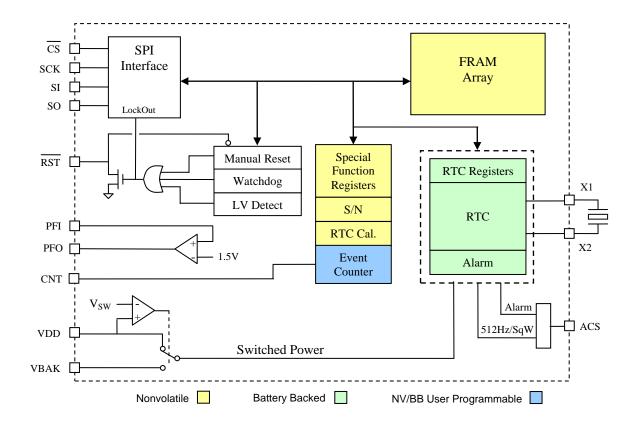

Figure 1. Block Diagram

| Ordering Information |        |           |            |                       |                          |  |  |  |

|----------------------|--------|-----------|------------|-----------------------|--------------------------|--|--|--|

| Base                 | Memory | Operating | Max. Clock | Reset Thresholds      | Ordering Part Number     |  |  |  |

| Configuration        | Size   | Voltage   | Freq.      |                       |                          |  |  |  |

| FM33256B             | 256Kb  | 2.7-3.6V  | 16 MHz     | 2.6V, 2.75, 2.9, 3.0V | FM33256B-G               |  |  |  |

| FM33256B             | 256Kb  | 2.7-3.6V  | 16 MHz     | 2.6V, 2.75, 2.9, 3.0V | FM33256B-GTR (tape&reel) |  |  |  |

## Overview

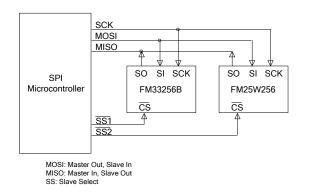

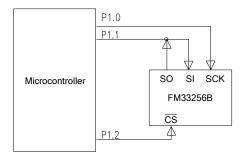

The FM33256B device combines a serial nonvolatile RAM with a real-time clock (RTC) and a processor companion. The companion is a highly integrated peripheral including a processor supervisor, analog comparator, a nonvolatile counter, and a serial number. The FM33256B integrates these complementary but distinct functions under a common interface in a single package. The product is organized as two logical devices. The first is a memory and the second is the companion which includes all the remaining functions. From the system perspective they appear to be two separate devices with unique op-codes on the serial bus.

The memory is organized as a standalone nonvolatile SPI memory using standard op-codes. The real-time clock and supervisor functions are accessed under their own op-codes. The clock and supervisor functions are controlled by 30 special function registers. The RTC/alarm and some control registers are maintained by the power source on the VBAK pin, allowing them to operate from battery or backup capacitor power when  $V_{DD}$  drops below a set threshold. Each functional block is described below.

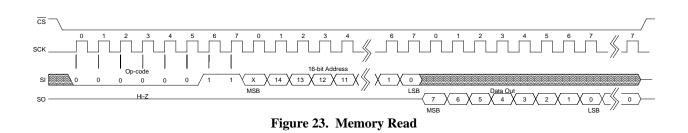

## **Memory Operation**

The FM33256B is available with 256Kb of memory. The device uses two-byte addressing for the memory portion of the chip. This makes the device software compatible with its standalone memory counterparts, such as the FM25W256.

Memory is organized in bytes. The 256Kb memory is  $32,768 \times 8$ . The memory is based on F-RAM technology. Therefore it can be treated as RAM and is read or written at the speed of the SPI bus with no delays for write operations. It also offers effectively unlimited write endurance unlike other nonvolatile memory technologies. The SPI protocol is described on page 18.

The memory array can be write-protected by software. Two bits (BP0, BP1) in the Status Register control the protection setting. Based on the setting, the protected addresses cannot be written. The Status Register & Write Protection is described in more detail on page 20.

### **Processor Companion**

In addition to nonvolatile RAM, the FM33256B incorporates a real-time clock with alarm and highly integrated processor companion. The companion includes a low- $V_{DD}$  reset, a programmable watchdog timer, a 16-bit nonvolatile event counter, a comparator for early power-fail detection or other purposes, and a 64-bit serial number.

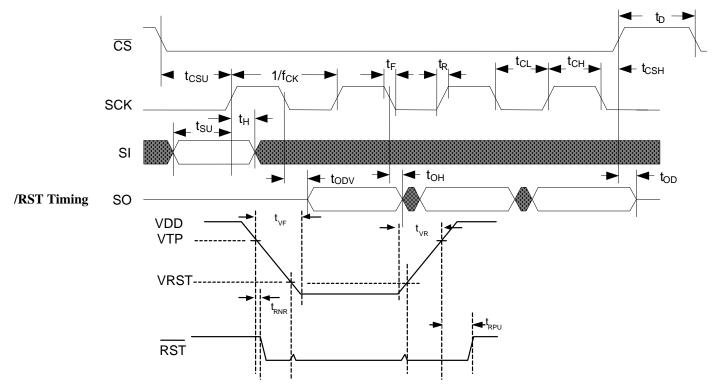

### **Processor Supervisor**

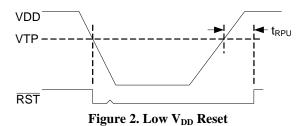

Supervisors provide a host processor two basic functions: Detection of power supply fault conditions and a watchdog timer to escape a software lockup condition. The FM33256B has a reset pin (/RST) to drive a processor reset input during power faults, power-up, and software lockups. It is an open drain output with a weak internal pull-up to V<sub>DD</sub>. This allows other reset sources to be wire-OR'd to the /RST pin. When  $V_{\text{DD}}$  is above the programmed trip point, /RST output is pulled weakly to V<sub>DD</sub>. If V<sub>DD</sub> drops below the reset trip point voltage level  $(V_{TP})$ , the /RST pin will be driven low. It will remain low until V<sub>DD</sub> falls too low for circuit operation which is the  $V_{RST}$  level. When  $V_{DD}$  rises again above  $V_{TP}$ , /RST continues to drive low for at least 50 ms  $(t_{RPU})$ to ensure a robust system reset at a reliable  $V_{DD}$  level. After t<sub>RPU</sub> has been met, the /RST pin will return to the weak high state. While /RST is asserted, serial bus activity is locked out even if a transaction occurred as V<sub>DD</sub> dropped below V<sub>TP</sub>. A memory operation started while  $V_{DD}$  is above  $V_{TP}$  will be completed internally.

Table 1 below shows how bits VTP(1:0) control the trip point of the low- $V_{DD}$  reset. They are located in register 18h, bits 0 and 1. The reset pin will drive low when  $V_{DD}$  is below the selected  $V_{TP}$  voltage, and the SPI interface and F-RAM array will be locked out. Figure 2 illustrates the reset operation in response to a low  $V_{DD}$ .

| VTP Setting | VTP1 | VTP0 |

|-------------|------|------|

| 2.6V        | 0    | 0    |

| 2.75V       | 0    | 1    |

| 2.9V        | 1    | 0    |

| 3.0V        | 1    | 1    |

Table 1.

This product conforms to specifications per the terms of the Ramtron standard warranty. The product has completed Ramtron's internal qualification testing and has reached production status.

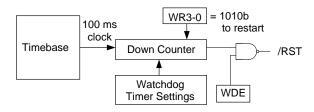

A watchdog timer can also be used to drive an active reset signal. The watchdog is a free-running programmable timer. The timeout period can be software programmed from 60 ms to 1.8 seconds in 60 ms increments via a 5-bit nonvolatile setting (register 0Ch).

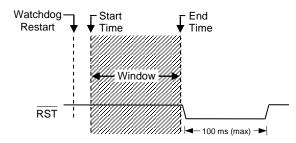

Figure 3. Watchdog Timer

The watchdog also incorporates a window timer feature that allows a delayed start. The starting time and ending time defines the window and each may be set independently. The starting time has 25 ms resolution and 0 ms to 775 ms range.

**Figure 4. Window Timer**

The watchdog EndTime value is located in register OCh, bits 4-0, the watchdog enable is bit 7. The watchdog is restarted by writing the pattern 1010b to the lower nibble of register 0Ah. Writing the correct pattern will also cause the timer to load new timeout values. Writing other patterns to this address will not affect its operation. Note the watchdog timer is freerunning. Prior to enabling it, users should restart the timer as described above. This assures that the full timeout is provided immediately after enabling. The watchdog is disabled when  $V_{DD}$  drops below  $V_{TP}$ . Note setting the EndTime timeout setting to all zeroes (00000b) disables the timer to save power. The listing below summarizes the watchdog bits.

| Watchdog StartTime | WDST4-0 | 0Bh, bits 4-0 |

|--------------------|---------|---------------|

| Watchdog EndTime   | WDET4-0 | 0Ch, bits 4-0 |

| Watchdog Enable    | WDE     | 0Ch, bit 7    |

| Watchdog Restart   | WR3-0   | 0Ah, bits 3-0 |

| Watchdog Flags     | EWDF,   | 09h, bit 7    |

|                    | LWDF    | 09h, bit 6    |

The programmed StartTime value is a guaranteed maximum time while the EndTime value is a guaranteed minimum time, and both vary with temperature and  $V_{DD}$  voltage. The watchdog has two additional controls associated with its operation. The nonvolatile enable bit WDE allows the /RST to go active if the watchdog reaches the timeout without being restarted. If a reset occurs, the timer will restart on the rising edge of the reset pulse. If WDE is not enabled, the watchdog timer still runs but has no effect on /RST. The second control is a nibble that restarts the timer, thus preventing a reset. The timer should be restarted after changing the timeout value.

This procedure must be followed to properly load the watchdog registers:

|    |                                   | Address |

|----|-----------------------------------|---------|

| 1. | Write the StartTime value         | 0Bh     |

| 2. | Write the EndTime value and WDE=1 | 0Ch     |

3. Issue a Restart command 0Ah

The restart command in step 3 must be issued before  $t_{DOG2}$ , which was programmed in step 2. The window timer starts counting when the restart command is issued.

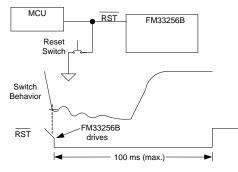

#### **Manual Reset**

The /RST is a bi-directional signal allowing the FM33256B to filter and de-bounce a manual reset switch. The /RST input detects an external low condition and responds by driving the /RST signal low for 100 ms (max.). This effectively filters and debounces a reset switch. After this timeout ( $t_{RPU}$ ), the user may continue pulling down on the /RST pin, but SPI commands will not be locked out.

This product conforms to specifications per the terms of the Ramtron standard warranty. The product has completed Ramtron's internal qualification testing and has reached production status.

Figure 5. Manual Reset

Note the internal weak pull-up eliminates the need for additional external components.

#### **Reset Flags**

In case of a reset condition, a flag bit will be set to indicate the source of the reset. A low- $V_{DD}$  reset is indicated by the POR bit, register 09h bit 5. There are two watchdog reset flags - one for an early fault (EWDF) and the other for a late fault (LWDF), located in register 09h bits 7 and 6. A manual reset will result in no flag being set, so the absence of a flag is a manual reset. Note that the bits are set in response to reset sources but they must be cleared by the user. It is possible to read the register and have both sources indicated if both have occurred since the user cleared them.

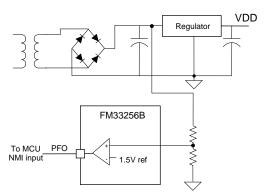

#### **Power Fail Comparator**

An analog comparator compares the PFI input pin to an onboard 1.5V reference. When the PFI input voltage drops below this threshold, the comparator will drive the PFO pin to a low state. The comparator has 100 mV of hysteresis (rising voltage only) to reduce noise sensitivity. The most common application of this comparator is to create an early warning power fail interrupt (NMI). This can be accomplished by connecting the PFI pin to an upstream power supply via a resistor divider. An application circuit is shown below. The comparator is a general purpose device and its application is not limited to the NMI function.

Figure 6. Comparator as a Power-Fail Warning

If the power-fail comparator is not used, the PFI pin should be tied to either  $V_{DD}$  or  $V_{SS}$ . Note that the PFO output will drive to  $V_{DD}$  or  $V_{SS}$  as well.

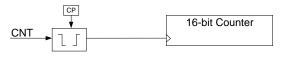

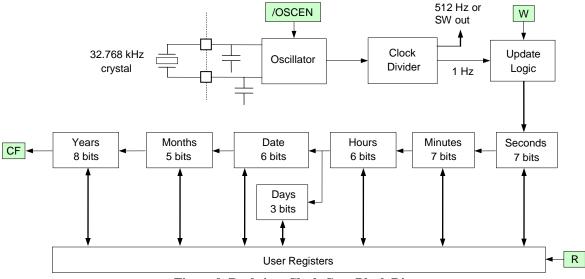

### **Event Counter**

The FM33256B offers the user a nonvolatile 16-bit event counter. The input pin CNT has a programmable edge detector. The CNT pin clocks the counter. The counter is located in registers 0E-0Fh. When the programmed edge polarity occurs, the counter will increment its count value. The register value is read by setting the RC bit (register 0Dh, bit 3) to 1. This takes a snapshot of the counter byte allowing a stable value even if a count occurs during the read. The register value can be written by first setting the WC bit (register 0Dh, bit 2) to 1. The user then may clear or preset the counter by writing to registers 0E-0Fh. Counts are blocked when the WC bit is set, so the user must clear the bit to allow counts.

The counter polarity control bit is CP, register 0Dh bit 0. When CP is 0, the counter increments on a falling edge of CNT, and when CP is set to 1, the counter increments on a rising edge of CNT. The polarity bit CP is nonvolatile.

**Figure 7. Event Counter**

The counter <u>does</u> <u>not</u> wrap back to zero when it reaches the limit of 65,535 (FFFFh). Care must be taken prior to the rollover, and a subsequent counter reset operation must occur to continue counting.

There is also a control bit that allows the user to define the counter as nonvolatile or battery-backed.

This product conforms to specifications per the terms of the Ramtron standard warranty. The product has completed Ramtron's internal qualification testing and has reached production status.

The counter is nonvolatile when the NVC bit (register 0Dh, bit 7) is logic 1 and battery-backed when the NVC bit is logic 0. Setting the counter mode to battery-backed allows counter operation under  $V_{BAK}$  (as well as  $V_{DD}$ ) power. The lowest operating voltage for battery-backed mode is 2.0V. When set to "nonvolatile" mode, the counter operates only when  $V_{DD}$  is applied and is above the  $V_{TP}$  voltage.

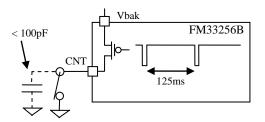

The event counter may be programmed to detect a tamper event, such as the system's case or access door being opened. A normally closed switch is tied to the CNT pin and the other contact to the case chassis, usually ground. The typical solution uses a pullup resistor on the CNT pin and will continuously draw battery current. The FM33256B chip allows the user to invoke a polled mode, which occasionally samples the pin in order to minimize battery drain. It internally tries to pull the CNT pin up and if open circuit will be pulled up to a V<sub>IH</sub> level, which will trip the edge detector and increment the event counter value. Setting the POLL bit (register 0Dh, bit 1) places the CNT pin into this mode. This mode allows the event counter to detect a rising edge tamper event but the user is restricted to operating in batterybacked mode (NVC=0) and using rising edge detection (CP=1). The CNT pin is polled once every 125ms. The additional average I<sub>BAK</sub> current is less than 20nA. The polling timer circuit operates from the RTC, so the oscillator must be enabled for this to function properly.

In the polled mode, the internal pullup circuit can source a limited amount of current. The maximum capacitance (switch open circuit) allowed on the CNT pin is 100pF.

#### Serial Number

A memory location to write a 64-bit serial number is provided. It is a writeable nonvolatile memory block that can be locked by the user once the serial number is set. The 8 bytes of data and the lock bit are all accessed via unique op-codes for the RTC and Processor Companion registers. Therefore the serial number area is separate and distinct from the memory array. The serial number registers can be written an unlimited number of times, so these locations are general purpose memory. *However once the lock bit is set, the values cannot be altered and the lock cannot be removed.* Once locked the serial number registers can still be read by the system.

The serial number is located in registers 10h to 17h. The lock bit is SNL, register 18h bit 7. Setting the SNL bit to a 1 disables writes to the serial number registers, and *the SNL bit cannot be cleared*.

#### Alarm

The alarm function compares user-programmed values to the corresponding time/date values and operates under  $V_{DD}$  or  $V_{BAK}$  power. When a match occurs, an alarm event occurs. The alarm drives an internal flag AF (register 00h, bit 6) and may drive the ACS pin, if desired, by setting the AL/SW bit (register 18h, bit 6) in the Companion Control register. The alarm condition is cleared by writing a '0' to the AF bit.

There are five alarm match fields. They are Month, Date, Hours, Minutes, and Seconds. Each of these fields also has a Match bit that is used to determine if the field is used in the alarm match logic. Setting the Match bit to '0' indicates that the corresponding field will be used in the match process.

Depending on the Match bits, the alarm can occur as specifically as one particular second on one day of the month, or as frequently as once per second continuously. The MSB of each Alarm register is a Match bit. Examples of the Match bit settings are shown in Table 3. Selecting none of the match bits (all '1's) indicates that no match is required. The alarm occurs every second. Setting the match select bit for seconds to '0' causes the logic to match the seconds alarm value to the current time of day. Since a match will occur for only one value per minute, the alarm occurs once per minute. Likewise setting the seconds and minutes match select bits causes an exact match of these values. Thus, an alarm will occur once per hour. Setting seconds, minutes, and hours causes a match once per day. Lastly, selecting all match-values causes an exact time and date match. Selecting other bit combinations will not produce meaningful results, however the alarm circuit will follow the functions described.

There are two ways a user can detect an alarm event, by reading the AF flag or monitoring the ACS pin.

This product conforms to specifications per the terms of the Ramtron standard warranty. The product has completed Ramtron's internal qualification testing and has reached production status.

### RAMTRON

The interrupt pin on the host processor may be used to detect an alarm event. The AF flag in register 00h (bit 6) will indicate that a time/date match has occurred. The AF flag will be set to '1' when a match occurs. The AEN bit must be set to enable the AF flag on alarm matches. The flag and ACS pin will remain in this state until the AF bit is cleared by writing it to a '0'. Clearing the AEN bit will prevent further matches from setting AF but will not automatically clear the AF flag.

The RTC alarm is integrated into the special function registers and shares its output pin with the 512Hz calibration and square wave outputs. When the RTC calibration mode is invoked by setting the CAL bit (register 00h, bit 2), the ACS output pin will be driven with a 512 Hz square wave and the alarm will continue to operate. Since most users only invoke the calibration mode during production this should have no impact on the otherwise normal operation of the alarm.

The ACS output may also be used to drive the system with a frequency other than 512 Hz. The AL/SW bit (register 18h, bit 6) must be '0'. A user-selectable frequency is provided by F0 and F1 (register 18h, bits 4 and 5). The other frequencies are 1, 4096, and 32768 Hz. If a continuous frequency output is enabled with CAL mode, the alarm function will not be available.

Following is a summary table that shows the relationship between register control settings and the state of the ACS pin.

| Table 2. State of Register Dit |         |             |             |  |  |  |

|--------------------------------|---------|-------------|-------------|--|--|--|

| State                          | of Regi | Function of |             |  |  |  |

| CAL                            | AEN     | AL/SW       | ACS pin     |  |  |  |

| 0                              | 1       | 1           | /Alarm      |  |  |  |

| 0                              | Х       | 0           | Sq Wave out |  |  |  |

| 1                              | Х       | Х           | 512 Hz out  |  |  |  |

| 0                              | 0       | 1           | Hi-Z        |  |  |  |

Table 2. State of Register Bit

| Table 3. | Alarm | Match | Bit | Examples |

|----------|-------|-------|-----|----------|

|----------|-------|-------|-----|----------|

| Seconds | Minutes | Hours | Date | Months | Alarm condition                                                |

|---------|---------|-------|------|--------|----------------------------------------------------------------|

| 1       | 1       | 1     | 1    | 1      | No match required = alarm 1/second                             |

| 0       | 1       | 1     | 1    | 1      | Alarm when seconds match = alarm 1/minute                      |

| 0       | 0       | 1     | 1    | 1      | Alarm when seconds, minutes match = alarm 1/hour               |

| 0       | 0       | 0     | 1    | 1      | Alarm when seconds, minutes, hours match = alarm 1/date        |

| 0       | 0       | 0     | 0    | 1      | Alarm when seconds, minutes, hours, date match = alarm 1/month |

## **Real-time Clock Operation**

The real-time clock (RTC) is a timekeeping device that can be capacitor- or battery-backed for permanently-powered operation. It offers a software calibration feature that allows high accuracy.

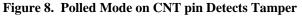

The RTC consists of an oscillator, clock divider, and a register system for user access. It divides down the 32.768 kHz time-base and provides a minimum resolution of seconds (1Hz). Static registers provide the user with read/write access to the time values. It includes registers for seconds, minutes, hours, dayof-the-week, date, months, and years. A block diagram shown in Figure 9 illustrates the RTC function.

The user registers are synchronized with the timekeeper core using R and W bits in register 00h. The R bit is used to read the time. Changing the R bit from 0 to 1 transfers timekeeping information from

This product conforms to specifications per the terms of the Ramtron standard warranty. The product has completed Ramtron's internal qualification testing and has reached production status. the core into the user registers 02-08h that can be read by the user. If a timekeeper update is pending when R is set, then the core will be updated prior to loading the user registers. The user registers are frozen and will not be updated again until the R bit is cleared to a '0'.

The W bit is used to write new time/date values. Setting the W bit to a '1' stops the RTC and allows the timekeeping core to be written with new data. Clearing it to '0' causes the RTC to start running based on the new values loaded in the timekeeper core. The RTC may be synchronized to another clock source. On the 8<sup>th</sup> clock of the write to register 00h (W=0), the RTC starts counting with a timebase that has been reset to zero milliseconds. Note: Users should be certain not to load invalid values, such as FFh, to the timekeeping registers. Updates to the timekeeping core occur continuously except when locked.

Figure 9. Real-time Clock Core Block Diagram

#### **Backup Power**

The real-time clock/calendar is intended to be permanently powered. When the primary system power fails, the voltage on the  $V_{DD}$  pin will drop. When  $V_{DD}$  is less 2.5V, the RTC (and event counters) will switch to the backup power supply on  $V_{BAK}$ . The clock operates at extremely low current in order to maximize battery or capacitor life. However, an advantage of combining a clock function with FRAM

memory is that data is not lost regardless of the backup power source.

<u>Note</u>: The minimum  $V_{BAK}$  voltage has been characterized at -40°C and +85°C but is not 100% tested.

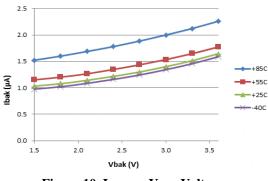

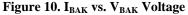

The  $I_{BAK}$  current varies with temperature and voltage (see DC parametric table). Figure 10 shows  $I_{BAK}$  as a function of  $V_{BAK}$ . These curves are useful for calculating backup time when a capacitor is used as the  $V_{BAK}$  source.

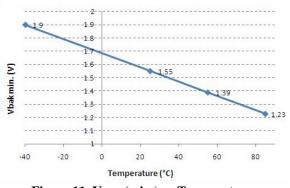

The minimum  $V_{BAK}$  voltage varies linearly with temperature. The user can expect the minimum  $V_{BAK}$  voltage to be 1.23V at +85°C and 1.90V at -40°C. The tested limit is 1.55V at +25°C.

Figure 11. V<sub>BAK</sub> (min.) vs Temperature

This product conforms to specifications per the terms of the Ramtron standard warranty. The product has completed Ramtron's internal qualification testing and has reached production status.

### **Trickle Charger**

To facilitate capacitor backup, the VBAK pin can optionally provide a trickle charge current. When the VBC bit (register 18h bit 3) is set to a '1', the  $V_{BAK}$  pin will source approximately 80  $\mu$ A until  $V_{BAK}$  reaches  $V_{DD}$ . This charges the capacitor to  $V_{DD}$  without an external diode and resistor charger. There is a Fast Charge mode which is enabled by the FC bit (register 18h, bit 2). In this mode the trickle charger current is set to approximately 1 mA, allowing a large backup capacitor to charge more quickly.

• In the case where no battery is used, the  $V_{BAK}$  pin should be tied to  $V_{SS}$  and VBC bit cleared.

**\*** Note: systems using lithium batteries should clear the VBC bit to 0 to prevent battery charging. The VBAK circuitry includes an internal 1 K $\Omega$  series resistor as a safety element. The trickle charger is UL Recognized.

### Calibration

When the CAL bit in register 00h is set to a '1', the clock enters calibration mode. The FM33256B employs a digital method for calibrating the crystal oscillator frequency. The digital calibration scheme applies a digital correction to the RTC counters based on the calibration settings, CALS and CAL.4-0. In calibration mode (CAL=1), the ACS pin is driven with a 512 Hz (nominal) square wave and the alarm is temporarily unavailable. Any measured deviation

from 512 Hz translates into a timekeeping error. The user measures the frequency and writes the appropriate correction value to the calibration register. The correction codes are listed in the table below. For convenience, the table also shows the frequency error in ppm. Positive ppm errors require a negative adjustment that removes pulses. Negative ppm errors require a positive correction that adds pulses. Positive ppm adjustments have the CALS (sign) bit set to 1, where as negative ppm adjustments have the CALS = 0. After calibration, the clock will have a maximum error of  $\pm 2.17$  ppm or  $\pm 0.09$  minutes per month at the calibrated temperature.

The user will not be able to see the effect of the calibration setting on the 512 Hz output. The addition or subtraction of digital pulses occurs after the 512 Hz output.

The calibration setting is stored in F-RAM so it is not lost should the backup source fail. It is accessed with bits CAL.4-0 in register 01h. This value only can be written when the CAL bit is set to a 1. To exit the calibration mode, the user must clear the CAL bit to a logic 0. When the CAL bit is 0, the ACS pin will revert to the function according to Table 2.

## **Crystal Type**

The crystal oscillator is designed to use a 12.5pF crystal without the need for external components, such as loading capacitors. The FM33256B device has built-in loading capacitors that match the crystal.

If a 32.768kHz crystal is not used, an external oscillator may be connected to the FM33256B. Refer to Application Note AN407 for recommendations on how to implement this.

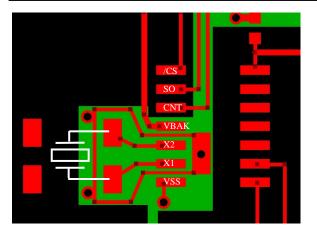

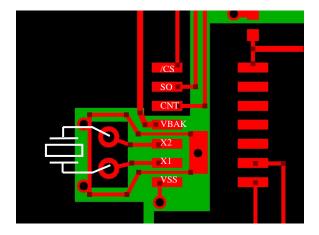

## Layout Recommendations

The X1 and X2 crystal pins employ very high impedance circuits and the oscillator connected to these pins can be upset by noise or extra loading. To reduce RTC clock errors from signal switching noise, a guard ring should be placed around these pads and the guard ring grounded. High speed SPI traces should be routed away from the X1/X2 pads. The X1 and X2 trace lengths should be less than 5 mm. The use of a ground plane on the backside or inner board layer is preferred. See layout example. Red is the top layer, green is the bottom layer.

This product conforms to specifications per the terms of the Ramtron standard warranty. The product has completed Ramtron's internal qualification testing and has reached production status.

**Layout for Surface Mount Crystal** (red = top layer, green = bottom layer)

**Layout for Through Hole Crystal** (red = top layer, green = bottom layer)

Table 4. Digital Calibration Adjustments

|    | Positive     | Calibration for slow | clocks: Calibra | tion will achieve | $\pm$ 2.17 PPM after calibration |

|----|--------------|----------------------|-----------------|-------------------|----------------------------------|

|    | Measured Fre | equency Range        | Error Range (   | PPM)              |                                  |

|    | Min          | Max                  | Min             | Max               | Program Calibration Register to: |

| 0  | 512.0000     | 511.9989             | 0               | 2.17              | 000000                           |

| 1  | 511.9989     | 511.9967             | 2.18            | 6.51              | 100001                           |

| 2  | 511.9967     | 511.9944             | 6.52            | 10.85             | 100010                           |

| 3  | 511.9944     | 511.9922             | 10.86           | 15.19             | 100011                           |

| 4  | 511.9922     | 511.9900             | 15.20           | 19.53             | 100100                           |

| 5  | 511.9900     | 511.9878             | 19.54           | 23.87             | 100101                           |

| 6  | 511.9878     | 511.9856             | 23.88           | 28.21             | 100110                           |

| 7  | 511.9856     | 511.9833             | 28.22           | 32.55             | 100111                           |

| 8  | 511.9833     | 511.9811             | 32.56           | 36.89             | 101000                           |

| 9  | 511.9811     | 511.9789             | 36.90           | 41.23             | 101001                           |

| 10 | 511.9789     | 511.9767             | 41.24           | 45.57             | 101010                           |

| 11 | 511.9767     | 511.9744             | 45.58           | 49.91             | 101011                           |

| 12 | 511.9744     | 511.9722             | 49.92           | 54.25             | 101100                           |

| 13 | 511.9722     | 511.9700             | 54.26           | 58.59             | 101101                           |

| 14 | 511.9700     | 511.9678             | 58.60           | 62.93             | 101110                           |

| 15 | 511.9678     | 511.9656             | 62.94           | 67.27             | 101111                           |

| 16 | 511.9656     | 511.9633             | 67.28           | 71.61             | 110000                           |

| 17 | 511.9633     | 511.9611             | 71.62           | 75.95             | 110001                           |

| 18 | 511.9611     | 511.9589             | 75.96           | 80.29             | 110010                           |

| 19 | 511.9589     | 511.9567             | 80.30           | 84.63             | 110011                           |

| 20 | 511.9567     | 511.9544             | 84.64           | 88.97             | 110100                           |

| 21 | 511.9544     | 511.9522             | 88.98           | 93.31             | 110101                           |

| 22 | 511.9522     | 511.9500             | 93.32           | 97.65             | 110110                           |

| 23 | 511.9500     | 511.9478             | 97.66           | 101.99            | 110111                           |

| 24 | 511.9478     | 511.9456             | 102.00          | 106.33            | 111000                           |

| 25 | 511.9456     | 511.9433             | 106.34          | 110.67            | 111001                           |

| 26 | 511.9433     | 511.9411             | 110.68          | 115.01            | 111010                           |

| 27 | 511.9411     | 511.9389             | 115.02          | 119.35            | 111011                           |

| 28 | 511.9389     | 511.9367             | 119.36          | 123.69            | 111100                           |

| 29 | 511.9367     | 511.9344             | 123.70          | 128.03            | 111101                           |

| 30 | 511.9344     | 511.9322             | 128.04          | 132.37            | 111110                           |

| 31 | 511.9322     | 511.9300             | 132.38          | 136.71            | 111111                           |

### RAMTRON

|    | Negative     | Calibration for fast | clocks: Calibrat | tion will achieve | ± 2.17 PPM after calibration     |

|----|--------------|----------------------|------------------|-------------------|----------------------------------|

|    | Measured Fre | equency Range        | Error Ran        | ge (PPM)          |                                  |

|    | Min          | Max                  | Min              | Max               | Program Calibration Register to: |

| 0  | 512.0000     | 512.0011             | 0                | 2.17              | 000000                           |

| 1  | 512.0011     | 512.0033             | 2.18             | 6.51              | 000001                           |

| 2  | 512.0033     | 512.0056             | 6.52             | 10.85             | 000010                           |

| 3  | 512.0056     | 512.0078             | 10.86            | 15.19             | 000011                           |

| 4  | 512.0078     | 512.0100             | 15.20            | 19.53             | 000100                           |

| 5  | 512.0100     | 512.0122             | 19.54            | 23.87             | 000101                           |

| 6  | 512.0122     | 512.0144             | 23.88            | 28.21             | 000110                           |

| 7  | 512.0144     | 512.0167             | 28.22            | 32.55             | 000111                           |

| 8  | 512.0167     | 512.0189             | 32.56            | 36.89             | 001000                           |

| 9  | 512.0189     | 512.0211             | 36.90            | 41.23             | 001001                           |

| 10 | 512.0211     | 512.0233             | 41.24            | 45.57             | 001010                           |

| 11 | 512.0233     | 512.0256             | 45.58            | 49.91             | 001011                           |

| 12 | 512.0256     | 512.0278             | 49.92            | 54.25             | 001100                           |

| 13 | 512.0278     | 512.0300             | 54.26            | 58.59             | 001101                           |

| 14 | 512.0300     | 512.0322             | 58.60            | 62.93             | 001110                           |

| 15 | 512.0322     | 512.0344             | 62.94            | 67.27             | 001111                           |

| 16 | 512.0344     | 512.0367             | 67.28            | 71.61             | 010000                           |

| 17 | 512.0367     | 512.0389             | 71.62            | 75.95             | 010001                           |

| 18 | 512.0389     | 512.0411             | 75.96            | 80.29             | 010010                           |

| 19 | 512.0411     | 512.0433             | 80.30            | 84.63             | 010011                           |

| 20 | 512.0433     | 512.0456             | 84.64            | 88.97             | 010100                           |

| 21 | 512.0456     | 512.0478             | 88.98            | 93.31             | 010101                           |

| 22 | 512.0478     | 512.0500             | 93.32            | 97.65             | 010110                           |

| 23 | 512.0500     | 512.0522             | 97.66            | 101.99            | 010111                           |

| 24 | 512.0522     | 512.0544             | 102.00           | 106.33            | 011000                           |

| 25 | 512.0544     | 512.0567             | 102.00           | 110.67            | 011001                           |

| 26 | 512.0567     | 512.0589             | 110.68           | 115.01            | 011010                           |

| 27 | 512.0589     | 512.0601             | 115.02           | 119.35            | 011010                           |

| 28 | 512.0611     | 512.0633             | 119.36           | 123.69            | 011100                           |

| 20 | 512.0633     | 512.0656             | 123.70           | 128.03            | 011100                           |

| 30 | 512.0656     | 512.0678             | 128.04           | 132.37            | 011110                           |

| 31 | 512.0678     | 512.0700             | 132.38           | 132.37            | 011111                           |

## **Register Map**

The RTC and processor companion functions are accessed via 30 special function registers, which are mapped to unique op-codes. The interface protocol is described on page 18. The registers contain timekeeping data, alarm settings, control bits, and information flags. A description of each register follows the summary table.

#### **Register Map Summary Table**

| Battery-backed = | ed = |

|------------------|------|

|------------------|------|

Nonvolatile =

BB/NV User Programmable =

| Address | D7     | D6    | D5          | D4         | D3          | D2      | D1      | D0         | Function              | Range |

|---------|--------|-------|-------------|------------|-------------|---------|---------|------------|-----------------------|-------|

| 1Dh     | /Match | 0     | 0           | 10 mo      |             | Alarm   | months  |            | Alarm Month           | 01-12 |

| 1Ch     | /Match | 0     | 10          | date       |             | Alarn   | n date  | Alarm Date | 01-31                 |       |

| 1Bh     | /Match | 0     | Alarm 1     | 10 hours   |             | Alarm   | hours   |            | Alarm Hours           | 00-23 |

| 1Ah     | /Match | Ala   | arm 10 minu | tes        |             | Alarm I | minutes |            | Alarm Minutes         | 00-59 |

| 19h     | /Match | Ala   | arm 10 seco | nds        |             | Alarm   | seconds |            | Alarm Seconds         | 00-59 |

| 18h     | SNL    | AL/SW | F1          | F0         | VBC         | FC      | VTP1    | VTP0       | Companion Control     |       |

| 17h     |        |       |             | Serial Nun | nber Byte 7 |         |         |            | Serial Number 7       | FFh   |

| 16h     |        |       |             | Serial Nun | nber Byte 6 |         |         |            | Serial Number 6       | FFh   |

| 15h     |        |       |             | Serial Nun | nber Byte 5 |         |         |            | Serial Number 5       | FFh   |

| 14h     |        |       |             | Serial Nun | nber Byte 4 |         |         |            | Serial Number 4       | FFh   |

| 13h     |        |       |             | Serial Nun | nber Byte 3 |         |         |            | Serial Number 3       | FFh   |

| 12h     |        |       |             | Serial Nun | nber Byte 2 |         |         |            | Serial Number 2       | FFh   |

| 11h     |        |       |             | Serial Nun | nber Byte 1 |         |         |            | Serial Number 1       | FFh   |

| 10h     |        |       |             | Serial Nun | nber Byte 0 |         |         |            | Serial Number 0       | FFh   |

| 0Fh     |        |       |             | Event Cour | nter Byte 1 |         |         |            | Event Counter 1       | FFh   |

| 0Eh     |        |       |             | Event Cour | nter Byte 0 |         |         |            | Event Counter 0       | FFh   |

| 0Dh     | NVC    | -     | -           | -          | RC          | WC      | POLL    | CP         | Event Counter Control |       |

| 0Ch     | WDE    | -     | -           | WDSET4     | WDET3       | WDET2   | WDET1   | WDET0      | Watchdog Control      |       |

| 0Bh     | -      | -     | -           | WDST4      | WDST3       | WDST2   | WDST1   | WDST0      | Watchdog Control      |       |

| 0Ah     | -      | -     | -           | -          | WR3         | WR2     | WR1     | WR0        | Watchdog Restart      |       |

| 09h     | EWDF   | LWDF  | POR         | LB         | -           | -       | -       | -          | Watchdog Flags        |       |

| 08h     |        | 10 y  | rears       | 1          |             | ye      | ars     |            | Years                 | 00-99 |

| 07h     | 0      | 0     | 0           | 10 mo      |             | -       | nths    |            | Month                 | 01-12 |

| 06h     | 0      | 0     | 10          | date       |             | da      | ate     |            | Date                  | 01-31 |

| 05h     | 0      | 0     | 0           | 0          | 0           |         | day     |            | Day                   | 01-07 |

| 04h     | 0      | 0     | -           | nours      |             |         | urs     |            | Hours                 | 00-23 |

| 03h     | 0      |       | 10 minutes  |            |             | min     | utes    |            | Minutes               | 00-59 |

| 02h     | 0      |       | 10 seconds  |            |             | sec     | onds    |            | Seconds               | 00-59 |

| 01h     | -      | -     | CALS        | CAL4       | CAL3        | CAL2    | CAL1    | CAL0       | CAL/Control           |       |

| 00h     | /OSCEN | AF    | CF          | AEN        | reserved    | CAL     | W       | R          | RTC/Alarm Control     |       |

Note: When the device is first powered up and programmed, all timekeeping registers must be written because the batterybacked register values cannot be guaranteed. The table below shows the default values of the non-volatile registers and some of the battery-backed bits. All other register values should be treated as unknown.

### **Default Register Values**

| Address | Hex Value |

|---------|-----------|

| 1Dh     | 0x81      |

| 1Ch     | 0x81      |

| 1Bh     | 0x80      |

| 1Ah     | 0x80      |

| 19h     | 0x80      |

| 18h     | 0x40      |

| 17h     | 0x00      |

| 16h     | 0x00      |

| 15h     | 0x00      |

| 14h     | 0x00      |

| 13h     | 0x00      |

| Address | Hex Value |

|---------|-----------|

| 12h     | 0x00      |

| 11h     | 0x00      |

| 10h     | 0x00      |

| 0Fh     | 0x00      |

| 0Eh     | 0x00      |

| 0Dh     | 0x01      |

| 0Ch     | 0x00      |

| 0Bh     | 0x00      |

| 01h     | 0x00      |

| 00h     | 0x80      |

|         |           |

This product conforms to specifications per the terms of the Ramtron standard warranty. The product has completed Ramtron's internal qualification testing and has reached production status.

# **Register Description**

Address Description

| 1Dh Alarm – Month |               |                                                                                                    |                                  |                  |                   |                  |                   |                 |  |  |

|-------------------|---------------|----------------------------------------------------------------------------------------------------|----------------------------------|------------------|-------------------|------------------|-------------------|-----------------|--|--|

|                   | D7            | D6                                                                                                 | D5                               | D4               | D3                | D2               | D1                | D0              |  |  |

|                   | M             | 0                                                                                                  | 0                                | 10 Month         | Month.3           | Month.2          | Month.1           | Month.0         |  |  |

|                   | Contains the  | alarm value for                                                                                    | or the month ar                  | nd the mask bit  | to select or de   | select the Mon   | th value.         |                 |  |  |

| /M                |               | U U                                                                                                | causes the Mo                    |                  |                   | •                | c. Setting this   | bit to 1        |  |  |

| 1Ch               |               | causes the match circuit to ignore the Month value. Battery-backed, read/write.       Alarm – Date |                                  |                  |                   |                  |                   |                 |  |  |

| ICI               | D7            | D6                                                                                                 | D5                               | D4               | D3                | D2               | D1                | D0              |  |  |

|                   | M             | 0                                                                                                  | 10 date.1                        | 10 date.0        | Date.3            | Date.2           | Date.1            | Date.0          |  |  |

|                   | Contains the  | alarm value for                                                                                    | or the date and                  | the mask bit to  | select or dese    | lect the Date v  | alue.             |                 |  |  |

| /M                |               |                                                                                                    | causes the Dat<br>the Date value |                  |                   | m match logic.   | Setting this bi   | t to 1 causes   |  |  |

| 1Bh               | Alarm – H     | ours                                                                                               |                                  |                  |                   |                  |                   |                 |  |  |

|                   | D7            | D6                                                                                                 | D5                               | D4               | D3                | D2               | D1                | D0              |  |  |

|                   | M             | 0                                                                                                  | 10 hours.1                       | 10 hours.0       | Hours.3           | Hours2           | Hours.1           | Hours.0         |  |  |

|                   | Contains the  | alarm value for                                                                                    | or the hours and                 | d the mask bit   | to select or des  | elect the Hour   | s value.          |                 |  |  |

| /M                |               |                                                                                                    | causes the Hou<br>the Hours valu |                  |                   |                  | c. Setting this l | bit to 1 causes |  |  |

| 1Ah               | Alarm – M     | ě                                                                                                  |                                  |                  |                   |                  |                   |                 |  |  |

|                   | D7            | D6                                                                                                 | D5                               | D4               | D3                | D2               | D1                | D0              |  |  |

|                   | M             | 10 min.2                                                                                           | 10 min.1                         | 10 min.0         | Min.3             | Min.2            | Min.1             | Min.0           |  |  |

|                   | Contains the  | alarm value fo                                                                                     | or the minutes a                 | and the mask b   | it to select or c | leselect the Mi  | nutes value       | •               |  |  |

| /M                | Match: Settin | ng this bit to 0                                                                                   | causes the Mir                   | nutes value to b | be used in the a  | alarm match lo   | gic. Setting thi  | s bit to 1      |  |  |

|                   | causes the m  | atch circuit to                                                                                    | ignore the Min                   | utes value. Ba   | ttery-backed, r   | ead/write.       |                   |                 |  |  |

| 19h               | Alarm – Se    | econds                                                                                             |                                  |                  |                   |                  |                   |                 |  |  |

|                   | D7            | D6                                                                                                 | D5                               | D4               | D3                | D2               | D1                | D0              |  |  |

|                   | M             | 10 sec.2                                                                                           | 10 sec.1                         | 10 sec.0         | Seconds.3         | Seconds.2        | Seconds.1         | Seconds.0       |  |  |

|                   | Contains the  | alarm value for                                                                                    | or the seconds a                 | and the mask b   | it to select or c | leselect the Sec | conds value.      |                 |  |  |

| /M                |               |                                                                                                    | causes the Sec                   |                  |                   |                  | gic. Setting thi  | s bit to 1      |  |  |

|                   | causes the m  | atch circuit to                                                                                    | ignore the Seco                  | onds value. Ba   | ttery-backed, r   | ead/write.       |                   |                 |  |  |

| 18h      | Companion       | Control                              |                                  |                 |               |                                      |                |                      |

|----------|-----------------|--------------------------------------|----------------------------------|-----------------|---------------|--------------------------------------|----------------|----------------------|

|          | D7              | D6                                   | D5                               | D4              | D3            | D2                                   | D1             | D0                   |

|          | SNL             | AL/SW                                | F1                               | F0              | VBC           | FC                                   | VTP1           | VTP0                 |

| SNL      |                 | er Lock: Setting<br>onvolatile, read |                                  | s registers 10h | to 17h and SN | IL read-only. SI                     | NL cannot be   | cleared once         |

| AL/SW    | set to '0', the |                                      | e Wave Freq w                    | ,               |               | e ACS pin as we<br>a, and an alarm a |                | 0                    |

| F(1:0)   | both '0'. Non   | volatile.                            |                                  |                 |               | in when the CA                       | L and AL/SW    | / bits are           |

|          | <u>Sei</u>      |                                      | <u>1:0)</u><br>0 (default)       |                 | -             | <u>1:0)</u><br>0                     |                |                      |

|          | 5               | 512 Hz 0                             | < / /                            |                 | 68Hz 1        |                                      |                |                      |

| VBC      | c               | ·                                    | U                                | · /             | •             | A (1 mA if FC=<br>Battery-backed,    | ,              | ge current to        |

| FC       | 0               | U U                                  | '1' (and VBC=<br>s the charge cu |                 |               | arge current to write.               | be supplied or | n V <sub>BAK</sub> . |

| VTP(1:0) |                 |                                      |                                  |                 |               | function. Whe<br>rface will be loc   |                |                      |

This product conforms to specifications per the terms of the Ramtron standard warranty. The product has completed Ramtron's internal qualification testing and has reached production status.

|      | read/write.         |                                         |                 |                 |               |                 |               |       |

|------|---------------------|-----------------------------------------|-----------------|-----------------|---------------|-----------------|---------------|-------|

|      |                     |                                         |                 |                 |               |                 |               |       |

|      |                     |                                         | (1:0)           |                 |               |                 |               |       |

|      |                     |                                         | (factory defa   | ault)           |               |                 |               |       |

|      |                     | 75V 01<br>9V 10                         |                 |                 |               |                 |               |       |

|      |                     | V 10                                    |                 |                 |               |                 |               |       |

|      | ~                   |                                         |                 |                 |               |                 |               |       |

| 17h  | Serial Num<br>D7    | 1ber Byte 7<br>D6                       | D5              | D4              | D3            | D2              | D1            | D0    |

|      |                     |                                         |                 |                 |               |                 |               |       |

| 16h  | SN.63<br>Serial Nur | SN.62<br>1ber Byte 6                    | SN.61           | SN.60           | SN.59         | SN.58           | SN.57         | SN.56 |

| Ion  | D7                  | D6                                      | D5              | D4              | D3            | D2              | D1            | D0    |

|      | SN.55               | SN.54                                   | SN.53           | SN.52           | SN.51         | SN.50           | SN.49         | SN.48 |

| 15h  |                     | iber Byte 5                             |                 |                 |               |                 | 200.0         |       |

|      | D7                  | D6                                      | D5              | D4              | D3            | D2              | D1            | D0    |

|      | SN.47               | SN.46                                   | SN.45           | SN.44           | SN.43         | SN.42           | SN.41         | SN.40 |

| 14h  |                     | nber Byte 4                             |                 |                 |               |                 |               |       |

|      | D7                  | D6                                      | D5              | D4              | D3            | D2              | D1            | D0    |

| 101  | SN.39               | SN.38                                   | SN.37           | SN.36           | SN.35         | SN.34           | SN.33         | SN.32 |

| 13h  | Serial Num<br>D7    | nber Byte 3<br>D6                       | D5              | D4              | D3            | D2              | D1            | D0    |

|      |                     |                                         |                 |                 | -             |                 |               |       |

| 12h  | Serial Nur          | SN.30<br>1ber Byte 2                    | SN.29           | SN.28           | SN.27         | SN.26           | SN.25         | SN.24 |

| 1211 | D7                  | D6                                      | D5              | D4              | D3            | D2              | D1            | D0    |

|      | SN.23               | SN.22                                   | SN.21           | SN.20           | SN.19         | SN.18           | SN.17         | SN.16 |

| 11h  | Serial Num          | nber Byte 1                             |                 |                 |               | -               |               |       |

|      | D7                  | D6                                      | D5              | D4              | D3            | D2              | D1            | D0    |

|      | SN.15               | SN.14                                   | SN.13           | SN.12           | SN.11         | SN.10           | SN.9          | SN.8  |

| 10h  | Serial Num          | , i i i i i i i i i i i i i i i i i i i | D5              | D4              | D1            | D2              | D1            | D0    |

|      | D7                  | D6                                      | D5              | D4              | D3            | D2              | D1            | D0    |

|      | SN.7                | SN.6<br>mber bytes are                  | SN.5            | SN.4            | SN.3          | SN.2            | SN.1          | SN.0  |

|      | All serial liu      | linder bytes are                        | icad/witte wit  | cii 511L-0, ica | d-only when 5 |                 | latile.       |       |

| 0Fh  | Event Cou           | · · · ·                                 |                 |                 |               | T               | I             | I     |

|      | D7                  | D6                                      | D5              | D4              | D3            | D2              | D1            | D0    |

|      | EC.15               | EC.14                                   | EC.13           | EC.12           | EC.11         | EC.10           | EC.9          | EC.8  |

|      |                     | er Byte 1. Increated when NVC           |                 |                 | event on CNT  | 'input. Nonvol  | atile when NV | C=1,  |

| 0Eh  |                     | nter Byte 0                             | -0, iedd wine.  |                 |               |                 |               |       |

|      | D7                  | D6                                      | D5              | D4              | D3            | D2              | D1            | D0    |

|      | EC.7                | EC.6                                    | EC.5            | EC.4            | EC.3          | EC.2            | EC.1          | EC.0  |

|      |                     | er Byte 0. Incre                        |                 |                 | event on CNT  | ' input. Nonvol | atile when NV | C=1,  |

|      | Battery-back        | ed when NVC                             | =0, read/write. |                 |               |                 |               |       |

| 0Dh  | Event Cou           | nter Control                            |                 |                 |               |                 |               |       |

|      | D7                  | D6                                      | D5              | D4              | D3            | D2              | D1            | D0    |

|      | NVC                 | -                                       | -               | -               | RC            | WC              | POLL          | СР    |

| NVC  |                     | Volatile Count                          |                 |                 |               |                 |               |       |

|      |                     | er than $V_{TP}$ . So power. If the l   |                 |                 |               |                 |               |       |

|      | · DAK OF (DD        | r s en in une i                         |                 |                 |               |                 |               |       |

This product conforms to specifications per the terms of the Ramtron standard warranty. The product has completed Ramtron's internal qualification testing and has reached production status.

### RAMTRON

|            |                         |                                                    |                                   |                                 |                        |                     |                              |                  | -                          |                       |

|------------|-------------------------|----------------------------------------------------|-----------------------------------|---------------------------------|------------------------|---------------------|------------------------------|------------------|----------------------------|-----------------------|

| RC         |                         | nter. Setting thi                                  |                                   |                                 |                        |                     |                              | ng the s         | ystem to re                | ead the               |

| WC         | Write Cou               | inter. Setting th<br>com count even                | is bit to a 1 allo                | ows the user to                 | o write tl             | he counte           | er bytes. Wl                 |                  |                            |                       |

| POLL       | Polled Mo<br>internally | ode: When POI<br>cleared and the<br>in polled mode | LL=1, the CNT<br>cP bit is set to | pin is sample<br>detect a risin | ed for 30<br>g edge. ' | µs every<br>The RTC | 125ms. If P<br>Coscillator n | OLL is nust be o | set, the NV<br>enabled (/0 | VC bit is<br>OSCEN=0) |

| СР         |                         | pin detects falli                                  |                                   |                                 |                        |                     |                              |                  |                            |                       |

|            |                         |                                                    |                                   |                                 |                        |                     |                              |                  |                            |                       |

| 0Ch        |                         | og Control                                         |                                   | -                               |                        |                     |                              |                  |                            |                       |

|            | D7                      | D6                                                 | D5                                | D4                              | ]                      | D3                  | D2                           | _                | D1                         | D0                    |

|            | WDE                     | -                                                  | -                                 | WDET4                           |                        | DET3                | WDET2                        |                  | WDET1                      | WDET0                 |

| WDE        |                         | Enable: When<br>r runs but has n                   |                                   |                                 |                        |                     |                              | al to go         | active. W                  | hen WDE =             |

| WDET(4:0)  | Watchdog                | EndTime: Sets                                      | s the ending tin                  | ne for the wate                 | chdog wi               | indow tir           | mer with 60                  |                  |                            |                       |

|            |                         | mer allow inde                                     |                                   |                                 |                        |                     |                              |                  |                            |                       |

|            |                         | re loaded wher<br>uit), the EndTir                 |                                   |                                 |                        |                     |                              | .(3:0). 1        | Fo save po                 | wer (disable          |

|            |                         |                                                    |                                   | 0 411 20100031 1                | (on contact            | iio, iouu,          |                              |                  |                            |                       |

|            |                         | Watchdog En                                        |                                   |                                 |                        | <u>WDET</u>         |                              | WDET             | <u>0</u>                   |                       |

|            |                         | Disables Time                                      |                                   | 0                               | 0                      | 0                   | 0                            | 0                |                            |                       |

|            |                         | (min.)<br>60 ms                                    | (max.)<br>200 ms                  | 0                               | 0                      | 0                   | 0                            | 1                |                            |                       |

|            |                         | 120 ms                                             | 400 ms                            | 0                               | 0                      | 0                   | 1                            | 0                |                            |                       |