# DS2401 Silicon Serial Number

### **BENEFITS AND FEATURES**

- Guaranteed Unique 64-Bit ROM ID Chip for Absolute Traceability

- Unique, Factory-Lasered and Tested

64-Bit Registration Number (8-Bit Family

Code +48-Bit Serial Number + 8-Bit CRC

Tester)

- 8-Bit Family Code Specifies DS2401

Communications Requirements to Reader

- Minimalist 1-Wire® Interface Lowers Cost and Interface Complexity

- Multiple DS2401 Devices Can Reside on a Common 1-Wire Net

- Built-In Multidrop Controller Ensures Compatibility with Other 1-Wire Net Products

- Reduces Control, Address, Data, and Power to a Single Pin and Communicates at Up to 16.3kbps

- Presence Pulse Acknowledges When the Reader First Applies Voltage

- Low-Cost TO-92, SOT-223, and TSOC Surface-Mount Packages

- TO-92 Tape-and-Reel Version with Leads Bent to 100-mil Spacing (Default) or with Straight Leads (DS2401-SL)

- Wide Voltage and Temperature Operating Ranges Enables Robust System Performance

- o Extended 2.8V to 6.0V Range

- o Zero Standby Power Required

- o -40°C to +85°C Industrial Temperature Range

#### **APPLICATIONS**

PCB Identification Network Node ID Equipment Registration

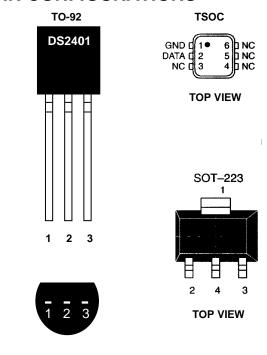

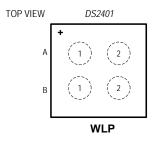

## PIN CONFIGURATIONS

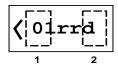

#### **BOTTOM VIEW**

Flip Chip, Top View with Laser Mark, Contacts Not Visible. "rrd" = Revision/Date

## PIN DESCRIPTIONS

|                      | PIN   |             |      |               |        |  |

|----------------------|-------|-------------|------|---------------|--------|--|

| NAME                 | TO-92 | SOT-<br>223 | TSOC | FLIP-<br>CHIP | WLP    |  |

| DATA<br>(DQ)         | 2     | 2           | 2    | 1             | A1, B1 |  |

| GROUND               | 1     | 1, 4        | 1    | 2             | A2, B2 |  |

| N.C. (No<br>Connect) | 3     | 3           | 3–6  |               |        |  |

## ORDERING INFORMATION

| PART          | TEMP RANGE     | PIN-PACKAGE               |

|---------------|----------------|---------------------------|

| DS2401+       | -40°C to +85°C | 3 TO-92                   |

| DS2401+T&R    | -40°C to +85°C | 3 TO-92 (formed leads)    |

| DS2401-SL+T&R | -40°C to +85°C | 3 TO-92 (straight leads)  |

| DS2401P+      | -40°C to +85°C | 6 TSOC                    |

| DS2401P+T&R   | -40°C to +85°C | 6 TSOC                    |

| DS2401Z+      | -40°C to +85°C | 4 SOT-223                 |

| DS2401Z+T&R   | -40°C to +85°C | 4 SOT-223                 |

| DS2401X1-S#T  | -40°C to +85°C | 2 Flip Chip (2.5k pieces) |

| DS2401X-S+T   | -40°C to +85°C | 4 WLP                     |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

## DESCRIPTION

The DS2401 enhanced silicon serial number is a low-cost, electronic registration number that provides an absolutely unique identity which can be determined with a minimal electronic interface (typically, a single port pin of a microcontroller). The DS2401 consists of a factory-lasered, 64-bit ROM that includes a unique 48-bit serial number, an 8-bit CRC, and an 8-bit Family Code (01h). Data is transferred serially via the 1-Wire protocol that requires only a single data lead and a ground return. Power for reading and writing the device is derived from the data line itself with no need for an external power source. The DS2401 is an upgrade to the DS2400. The DS2401 is fully reverse-compatible with the DS2400 but provides the additional multi-drop capability that enables many devices to reside on a single data line. The familiar TO-92, SOT-223 or TSOC package provides a compact enclosure that allows standard assembly equipment to handle the device easily.

#### **OPERATION**

The DS2401's internal ROM is accessed via a single data line. The 48-bit serial number, 8-bit family code and 8-bit CRC are retrieved using the Maxim 1-Wire protocol. This protocol defines bus transactions in terms of the bus state during specified time slots that are initiated on the falling edge of sync pulses from the bus master. All data is read and written least significant bit first.

#### 1-Wire BUS SYSTEM

The 1-Wire bus is a system which has a single bus master system and one or more slaves. In all instances, the DS2401 is a slave device. The bus master is typically a microcontroller. The discussion of this bus system is broken down into three topics: hardware configuration, transaction sequence, and 1-Wire signaling (signal type and timing).

# **Hardware Configuration**

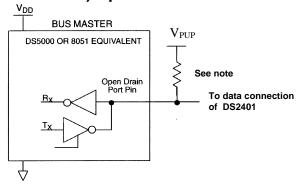

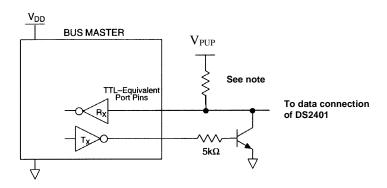

The 1-Wire bus has only a single line by definition; it is important that each device on the bus be able to drive it at the appropriate time. To facilitate this, each device attached to the 1-Wire bus must have an open-drain connection or 3-state outputs. The DS2401 is an open-drain part with an internal circuit equivalent to that shown in Figure 2. The bus master can be the same equivalent circuit. If a bidirectional pin is not available, separate output and input pins can be tied together. The bus master requires a pullup resistor at the master end of the bus, with the bus master circuit equivalent to the one shown in Figure 3. The value of the pullup resistor should be approximately  $5k\Omega$  for short line lengths. A multidrop bus consists of a 1-Wire bus with multiple slaves attached. The 1-Wire bus has a maximum data rate of 16.3kbits per second.

$T&R/T = Tape \ and \ reel.$

SL = Straight leads.

<sup>#</sup>Denotes a RoHS-compliant device that may include lead that is exempt under the RoHS requirements.

The idle state for the 1-Wire bus is high. If, for any reason, a transaction needs to be suspended, the bus MUST be left in the idle state if the transaction is to resume. If this does not occur and the bus is left low for more than 120µs, one or more of the devices on the bus may be reset.

**DS2401 MEMORY MAP** Figure 1

| 8-Bit CRC Co | ode | 48-B | it Serial Number | 8-Bit Fa | amily Code (01h) |

|--------------|-----|------|------------------|----------|------------------|

| MSB          | LSB | MSB  | LSB              | MSB      | LSB              |

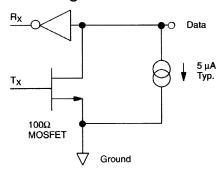

# **DS2401 EQUIVALENT CIRCUIT Figure 2**

## **BUS MASTER CIRCUIT** Figure 3

## A) Open Drain

# **B) Standard TTL**

## Note:

Depending on the 1-Wire communication speed and the bus load characteristics, the optimal pullup resistor ( $R_{PU}$ ) value will be in the  $1.5k\Omega$  to  $5k\Omega$  range.

## TRANSACTION SEQUENCE

The sequence for accessing the DS2401 via the 1-Wire port is as follows:

- Initialization

- ROM Function Command

- Read Data

#### INITIALIZATION

All transactions on the 1-Wire bus begin with an initialization sequence. The initialization sequence consists of a reset pulse transmitted by the bus master followed by a Presence Pulse(s) transmitted by the slave(s).

The Presence Pulse lets the bus master know that the DS2401 is on the bus and is ready to operate. For more details, see the 1-Wire Signaling section.

## **ROM FUNCTION COMMANDS**

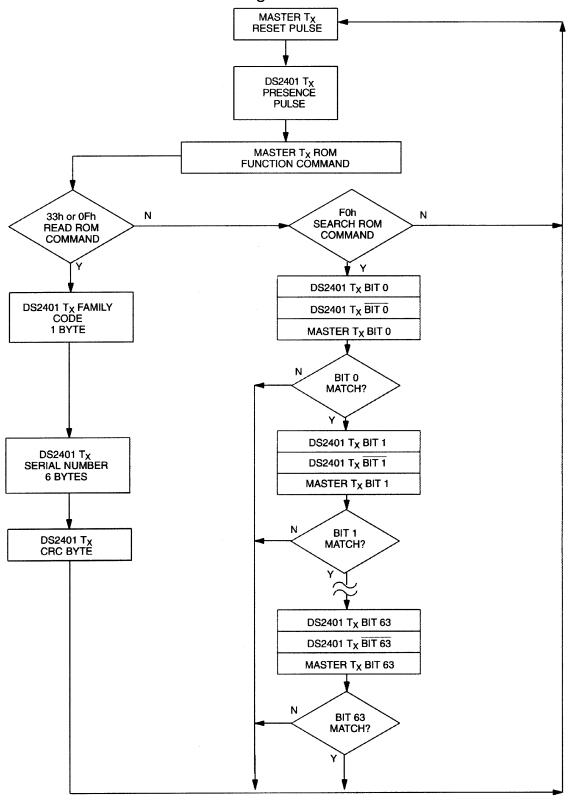

Once the bus master has detected a presence, it can issue one of the four ROM function commands. All ROM function commands are 8 bits long. A list of these commands follows (refer to flowchart in Figure 4).

## Read ROM [33h] or [0Fh]

This command allows the bus master to read the DS2401's 8-bit family code, unique 48-bit serial number, and 8-bit CRC. This command can only be used if there is a single DS2401 on the bus. If more than one slave is present on the bus, a data collision will occur when all slaves try to transmit at the same time (open drain will produce a wired-AND result). The DS2401 Read ROM function will occur with a command byte of either 33h or 0Fh in order to ensure compatibility with the DS2400, which will only respond to a 0Fh command word with its 64-bit ROM data.

# Match ROM [55h] / Skip ROM [CCh]

The complete 1-Wire protocol for all Maxim iButtons® contains a Match ROM and a Skip ROM command. Since the DS2401 contains only the 64-bit ROM with no additional data fields, the Match ROM and Skip ROM are not applicable and will cause no further activity on the 1-Wire bus if executed. The DS2401 does not interfere with other 1-Wire parts on a multidrop bus that do respond to a Match ROM or Skip ROM (for example, a DS2401 and DS1994 on the same bus).

# Search ROM [F0h]

When a system is initially brought up, the bus master might not know the number of devices on the 1-Wire bus or their 64-bit ROM codes. The search ROM command allows the bus master to use a process of elimination to identify the 64-bit ROM codes of all slave devices on the bus. The ROM search process is the repetition of a simple 3-step routine: read a bit, read the complement of the bit, then write the desired value of that bit. The bus master performs this simple 3-step routine on each bit of the ROM. After one complete pass, the bus master knows the contents of the ROM in one device. The remaining number of devices and their ROM codes may be identified by additional passes. Refer to *Application Note 187: 1-Wire Search Algorithm* for a comprehensive discussion of a ROM search, including an actual example.

iButton is a registered trademark of Maxim Integrated Products, Inc.

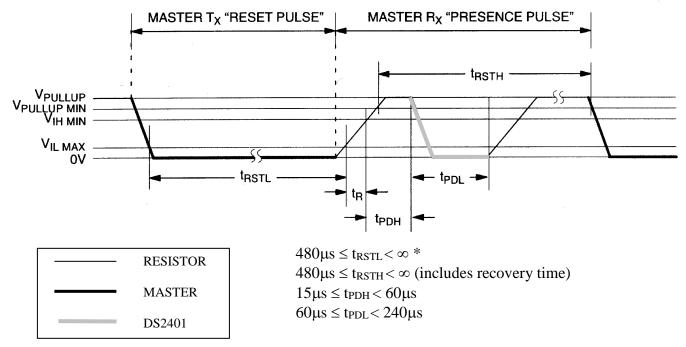

## 1-Wire SIGNALING

The DS2401 requires a strict protocol to ensure data integrity. The protocol consists of four types of signaling on one line: reset sequence with Reset Pulse and Presence Pulse, write 0, write 1, and read data. All these signals except Presence Pulse are initiated by the bus master.

The initialization sequence required to begin any communication with the DS2401 is shown in Figure 5. A reset pulse followed by a Presence Pulse indicates the DS2401 is ready to send or receive data given the correct ROM command.

The bus master transmits ( $T_X$ ) a reset pulse ( $t_{RSTL}$ , minimum 480 $\mu$ s). The bus master then releases the line and goes into receive mode ( $R_X$ ). The 1-Wire bus is pulled to a high state via the  $5k\Omega$  pullup resistor. After detecting the rising edge on the data pin, the DS2401 waits ( $t_{PDH}$ , 15-60 $\mu$ s) and then transmits the Presence Pulse ( $t_{PDL}$ , 60-240 $\mu$ s). The 1-Wire bus requires a pullup resistor range of 1.5k $\Omega$  to 5k $\Omega$ , depending on bus load characteristics.

## **READ/WRITE TIME SLOTS**

The definitions of write and read time slots are illustrated in Figure 6. All time slots are initiated by the master driving the data line low. The falling edge of the data line synchronizes the DS2401 to the master by triggering a delay circuit in the DS2401. During write time slots, the delay circuit determines when the DS2401 will sample the data line. For a read data time slot, if a "0" is to be transmitted, the delay circuit determines how long the DS2401 will hold the data line low overriding the "1" generated by the master. If the data bit is a 1, the DS2401 will leave the read data time slot unchanged.

# **ROM FUNCTIONS FLOW CHART** Figure 4

# INITIALIZATION PROCEDURE "RESET AND PRESENCE PULSES" Figure 5

\* In order not to mask interrupt signaling by other devices on the 1-Wire bus,  $t_{RSTL} + t_{R}$  should always be less than 960 $\mu$ s.

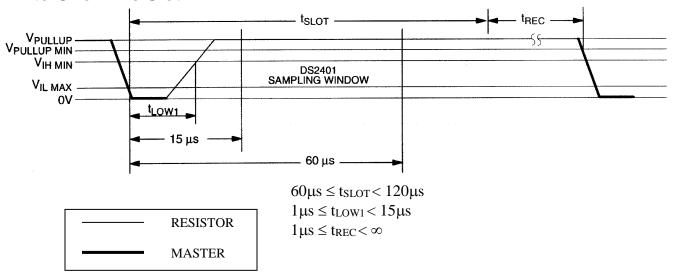

# **READ/WRITE TIMING DIAGRAM** Figure 6 Write-One Time Slot

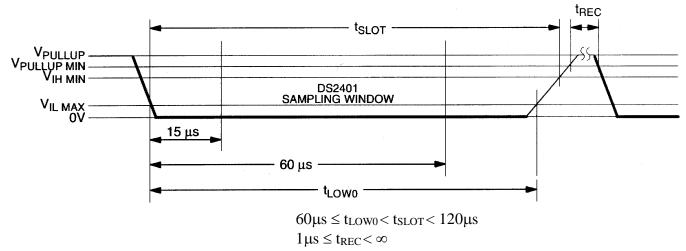

# **READ/WRITE TIMING DIAGRAM** (cont'd) Figure 6 Write-zero Time Slot

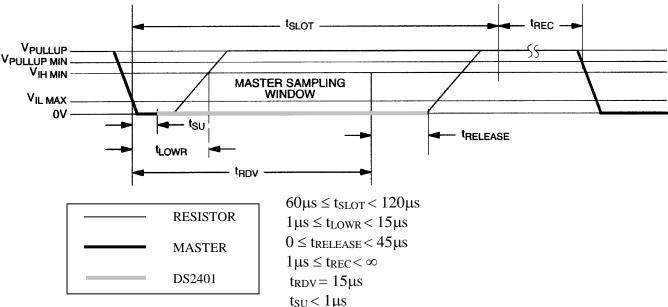

## **Read-data Time Slot**

## **CRC GENERATION**

To validate the data transmitted from the DS2401, the bus master may generate a CRC value from the data as it is received. This generated value is compared to the value stored in the last 8 bits of the DS2401. If the two CRC values match, the transmission is error-free.

The equivalent polynomial function of this CRC is:  $CRC = x^8 + x^5 + x^4 + 1$ . Additional information about the Maxim 1-Wire CRC is available in *Application Note* 27.

### **CUSTOM DS2401**

Customization of a portion of the unique 48-bit serial number by the customer is available. Maxim will register and assign a specific customer ID in the 12 most significant bits of the 48-bit field. The next most significant bits are selectable by the customer as a starting value, and the least significant bits are non-selectable and will be automatically incremented by one. Certain quantities and conditions apply for these custom parts. Contact your Maxim sales representative for more information.

## **ABSOLUTE MAXIMUM RATINGS**

Voltage Range on Any Pin Relative to Ground

Operating Temperature Range

Storage Temperature Range

Lead Temperature (TO-92, TSOC, SOT-223 only; soldering, 10s)

-0.5V to +7.0V

-40°C to +85°C

-55°C to +125°C

+300°C

Soldering Temperature (reflow)

TO-92 +250°C TSOC, SOT-223, WLP +260°C Flip Chip +240°C

This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.

## DC ELECTRICAL CHARACTERISTICS

$(T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted.})$

| PARAMETER               | SYMBOL            | MIN  | TYP | MAX  | UNITS | NOTES |

|-------------------------|-------------------|------|-----|------|-------|-------|

| Pullup Voltage          | $V_{PUP}$         | 2.8  |     | 6.0  | V     | 2     |

| Logic 1                 | $V_{ m IH}$       | 2.2  |     |      | V     | 1, 6  |

| Logic 0                 | $V_{\mathrm{IL}}$ | -0.3 |     | +0.3 | V     | 1     |

| Output Logic-Low at 4mA | $V_{\mathrm{OL}}$ |      |     | 0.4  | V     | 1     |

| Input Load Current      | $I_{\rm L}$       |      | 5   |      | μA    | 3     |

| Operating Charge        | $Q_{\mathrm{OP}}$ |      |     | 30   | nC    | 7, 8  |

## **CAPACITANCE**

$(T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

| PARAMETER    | SYMBOL              | MIN | TYP | MAX | UNITS | NOTES |

|--------------|---------------------|-----|-----|-----|-------|-------|

| I/O (1-Wire) | C <sub>IN/OUT</sub> |     |     | 800 | pF    | 9     |

### **AC ELECTRICAL CHARACTERISTICS**

$(T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted.})$

| PARAMETER            | SYMBOL               | MIN | TYP | MAX | UNITS | NOTES |

|----------------------|----------------------|-----|-----|-----|-------|-------|

| Time Slot            | $t_{SLOT}$           | 60  |     | 120 | μs    |       |

| Write 1 Low Time     | t <sub>LOW1</sub>    | 1   |     | 15  | μs    | 12    |

| Write 0 Low Time     | $t_{ m LOW0}$        | 60  |     | 120 | μs    |       |

| Read Data Valid      | $t_{ m RDV}$         |     | 15  |     | μs    | 11    |

| Release Time         | t <sub>release</sub> | 0   | 15  | 45  | μs    |       |

| Read Data Setup      | $t_{ m SU}$          |     |     | 1   | μs    | 5     |

| Recovery Time        | $t_{REC}$            | 1   |     |     | μs    |       |

| Reset Time High      | t <sub>RSTH</sub>    | 480 |     |     | μs    | 4     |

| Reset Time Low       | t <sub>RSTL</sub>    | 480 |     | 960 | μs    | 10    |

| Presence Detect High | t <sub>PDH</sub>     | 15  |     | 60  | μs    |       |

| Presence Detect Low  | $t_{\mathrm{PDL}}$   | 60  |     | 240 | μs    |       |

## **NOTES:**

- 1) All voltages are referenced to ground.

- 2)  $V_{PUP}$  = external pullup voltage.

- 3) Input load is to ground.

- 4) An additional reset or communication sequence cannot begin until the reset high time has expired.

- 5) Read data setup time refers to the time the host must pull the 1-Wire bus low to read a bit. Data is guaranteed to be valid within 1μs of this falling edge and will remain valid for 14μs minimum (15μs total from falling edge on 1-Wire bus).

- 6)  $V_{IH}$  is a function of the external pullup resistor and  $V_{PUP}$ .

- 7) 30 nanocoulombs per 72 time slots at 5.0V.

- 8) At  $V_{PUP} = 5.0 \text{V}$  with a  $5 \text{k}\Omega$  pullup to  $V_{PUP}$  and a maximum time slot of  $120 \mu \text{s}$ .

- 9) Capacitance on the I/O pin could be 800pF when power is first applied. If a  $5k\Omega$  resistor is used to pullup the I/O line to  $V_{PUP}$ ,  $5\mu$ s after power has been applied the parasite capacitance will not affect normal communications.

- 10) The reset low time (t<sub>RSTL</sub>) should be restricted to a maximum of 960μs, to allow interrupt signaling, otherwise it could mask or conceal interrupt pulses if this device is used in parallel with a DS2404 or DS1994.

- 11) The optimal sampling point for the master is as close as possible to the end time of the t<sub>RDV</sub> period without exceeding t<sub>RDV</sub>. For the case of a Read-One Time slot, this maximizes the amount of time for the pullup resistor to recover to a high level. For a Read-Zero Time slot, it ensures that a read will occur before the fastest 1-Wire device(s) releases the line.

- 12) The duration of the low pulse sent by the master should be a minimum of 1µs with a maximum value as short as possible to allow time for the pullup resistor to recover the line to a high level before the 1-Wire device samples in the case of a Write-One Time or before the master samples in the case of a Read-One Time.

#### PACKAGE INFORMATION

For the latest package outline information and land patterns (footprints), go to <a href="www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE TYPE                | PACKAGE CODE | OUTLINE NO.    | LAND PATTERN NO.               |

|-----------------------------|--------------|----------------|--------------------------------|

| 3 TO-92<br>(straight leads) | Q3+1         | <u>21-0248</u> | _                              |

| 3 TO-92<br>(formed leads)   | Q3+4         | <u>21-0250</u> | _                              |

| 6 TSOC                      | D6+1         | <u>21-0382</u> | 90-0321                        |

| 4 SOT-223                   | K3+1         | <u>21-0264</u> | _                              |

| 2 Flip Chip                 | BF211#1      | <u>21-0378</u> | <u>21-0378</u>                 |

| 4 WLP                       | N40B1+1      | <u>21-0605</u> | Refer to Application Note 1891 |

## **REVISION HISTORY**

| REVISION DATE | DESCRIPTION                                                                                                                                                                                                | PAGES<br>CHANGED |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 040601        | Changed MicroLAN to 1-Wire Net; updated ordering information for tape and reel                                                                                                                             | 1                |

| 040001        | Changed soldering temperature from 260°C for 10 seconds to See J-STD-020A Specification                                                                                                                    | 9                |

| 022202        | Below Figure 3, added a note on the optimal R <sub>PUP</sub> range; added a similar note before the <i>Read/Write Time Slots</i> section                                                                   | 3, 6             |

|               | Added notes 11 to 13 to the EC table                                                                                                                                                                       | 9, 10            |

|               | Added flip chip package; added lead-free ordering information                                                                                                                                              | 1, 2             |

| 122106        | References to the <i>Book of iButton Standards</i> replaced with references to corresponding application notes                                                                                             | Various          |

|               | $V_{\rm ILMAX}$ changed from 0.8V to 0.3V, EC table note 11 deleted                                                                                                                                        | 9, 10            |

|               | Deleted standard (Pb) parts from ordering information; changed flip chip part number from DS2401X1 to DS2401X1-S#T                                                                                         | 2                |

| 5/11          | Deleted V <sub>OH</sub> from the EC table; moved V <sub>PUP</sub> from the EC table header into the EC table; changed soldering temperature from J-STD-020A reference to explicit package specific numbers | 9                |

|               | Added Package Information and Revision History sections                                                                                                                                                    | 10, 11           |

| 3/15          | Revised Benefits and Features section                                                                                                                                                                      | 1                |

| 12/16         | Added WLP package to Pin Configurations, Pin Descriptions, Ordering Information, Absolute Maximum Ratings, and Package Information sections                                                                | 1, 2, 9, 10      |

OOO «ЛайфЭлектроникс" "LifeElectronics" LLC

ИНН 7805602321 КПП 780501001 P/C 40702810122510004610 ФАКБ "АБСОЛЮТ БАНК" (ЗАО) в г.Санкт-Петербурге К/С 3010181090000000703 БИК 044030703

Компания «Life Electronics» занимается поставками электронных компонентов импортного и отечественного производства от производителей и со складов крупных дистрибьюторов Европы, Америки и Азии.

С конца 2013 года компания активно расширяет линейку поставок компонентов по направлению коаксиальный кабель, кварцевые генераторы и конденсаторы (керамические, пленочные, электролитические), за счёт заключения дистрибьюторских договоров

#### Мы предлагаем:

- Конкурентоспособные цены и скидки постоянным клиентам.

- Специальные условия для постоянных клиентов.

- Подбор аналогов.

- Поставку компонентов в любых объемах, удовлетворяющих вашим потребностям.

- Приемлемые сроки поставки, возможна ускоренная поставка.

- Доставку товара в любую точку России и стран СНГ.

- Комплексную поставку.

- Работу по проектам и поставку образцов.

- Формирование склада под заказчика.

- Сертификаты соответствия на поставляемую продукцию (по желанию клиента).

- Тестирование поставляемой продукции.

- Поставку компонентов, требующих военную и космическую приемку.

- Входной контроль качества.

- Наличие сертификата ISO.

В составе нашей компании организован Конструкторский отдел, призванный помогать разработчикам, и инженерам.

Конструкторский отдел помогает осуществить:

- Регистрацию проекта у производителя компонентов.

- Техническую поддержку проекта.

- Защиту от снятия компонента с производства.

- Оценку стоимости проекта по компонентам.

- Изготовление тестовой платы монтаж и пусконаладочные работы.

Тел: +7 (812) 336 43 04 (многоканальный) Email: org@lifeelectronics.ru