# **Linear CCD Image Sensor**

#### Description

The KLI–2113 Image Sensor is a high dynamic range, multispectral, linear CCD image sensor ideally suited for demanding color scanner applications.

The imager consists of three parallel 2098-element photodiode arrays – one for each primary color. The KLI–2113 sensor offers high sensitivity, a high data rate, low noise, and negligible lag. Independent exposure control for each channel allows color balancing at the front end. CMOS-compatible 5 V clocks, and single 12 V DC supply are all that are required to drive the KLI–2113 sensor, simplifying the design of interface electronics.

**Table 1. GENERAL SPECIFICATIONS**

| Parameter                                               | Typical Value                                                                 |

|---------------------------------------------------------|-------------------------------------------------------------------------------|

| Architecture                                            | 3 Channel, RGB Tri-linear CCD                                                 |

| Pixels Count                                            | 2098 × 3                                                                      |

| Pixel Size                                              | 14 μm (H) × 14 μm (V)                                                         |

| Pixel Pitch                                             | 14 μm                                                                         |

| Inter-Array Spacing                                     | 112 mm (8 Lines Effective)                                                    |

| Active Image Size                                       | 29.37 mm (H) × 0.24 mm (V)<br>29.4 mm (Diagonal)                              |

| Saturation Signal                                       | 170,000 e <sup>-</sup>                                                        |

| Dynamic Range                                           | 76 dB                                                                         |

| Responsivity (Wavelength)<br>460 nm<br>540 nm<br>650 nm | 25 V/μJ/cm <sup>2</sup><br>32 V/μJ/cm <sup>2</sup><br>50 V/μJ/cm <sup>2</sup> |

| Output Sensitivity                                      | 11.5 μV/e <sup>-</sup>                                                        |

| Dark Current                                            | 0.02 pA/Pixel                                                                 |

| Dark Current Doubling Rate                              | 9°C                                                                           |

| Charge Transfer Efficiency                              | 0.99999/Transfer                                                              |

| Photoresponse Non-Uniformity                            | 5% Peak-Peak                                                                  |

| Lag (First Field)                                       | 0.6%                                                                          |

| Maximum Data Rate                                       | 20 MHz/Channel                                                                |

| Package                                                 | CERDIP (Sidebrazed, CuW)                                                      |

| Cover Glass                                             | AR Coated, 2 Sides                                                            |

NOTE: Parameters above are specified at T =  $25^{\circ}$ C and 2 MHz clock rates unless otherwise noted.

# ON Semiconductor®

www.onsemi.com

Figure 1. KLI-2113 Linear CCD Image Sensor

#### **Features**

- High Resolution

- Wide Dynamic Range

- High Sensitivity

- High Operating Speed

- High Charge Transfer Efficiency

- No Image Lag

- Electronic Exposure Control

- Pixel Summing Capability

- Up to 2.0 V Peak-Peak Output

- 5.0 V Clock Inputs

- Two-Phase Register Clocking

- On-Chip Dark Reference

#### **Applications**

- Digitization

- Machine Vision

- Mapping/Aerial

- Photography

#### ORDERING INFORMATION

See detailed ordering and shipping information on page 2 of this data sheet.

# **ORDERING INFORMATION**

#### Table 2. ORDERING INFORMATION - KLI-2113 IMAGE SENSOR

| Part Number        | Description                                                                                                                    | Marking Code           |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------|------------------------|

| KLI-2113-AAA-ER-AA | Monochrome, No Microlens, CERDIP Package (Leadframe),<br>Taped Clear Cover Glass with AR Coating (2 Sides), Standard Grade     | KLI-2113<br>Lot Number |

| KLI-2113-AAA-ER-AE | Monochrome, No Microlens, CERDIP Package (Leadframe),<br>Taped Clear Cover Glass with AR Coating (2 Sides), Engineering Sample | Serial Number          |

| KLI-2113-AAB-ED-AA | Monochrome, No Microlens, CERDIP Package (Leadframe),<br>Clear Cover Glass with AR Coating (Both Sides), Standard Grade        | KLI-2113<br>Lot Number |

| KLI-2113-AAB-ED-AE | Monochrome, No Microlens, CERDIP Package (Leadframe),<br>Clear Cover Glass with AR Coating (Both Sides), Engineering Sample    | Serial Number          |

| KLI-2113-DAA-ED-AA | Color (RGB), No Microlens, CERDIP Package (Leadframe),<br>Clear Cover Glass with AR Coating (Both Sides), Standard Grade       | KLI-2113<br>Lot Number |

| KLI-2113-DAA-ED-AE | Color (RGB), No Microlens, CERDIP Package (Leadframe),<br>Clear Cover Glass with AR Coating (Both Sides), Engineering Sample   | Serial Number          |

#### Table 3. ORDERING INFORMATION – EVALUATION SUPPORT

| Part Number         | Description                     |

|---------------------|---------------------------------|

| KLI-2113-12-5-A-EVK | Evaluation Board (Complete Kit) |

See the ON Semiconductor *Device Nomenclature* document (TND310/D) for a full description of the naming convention used for image sensors. For reference documentation, including information on evaluation kits, please visit our web site at <a href="https://www.onsemi.com">www.onsemi.com</a>.

#### **DEVICE DESCRIPTION**

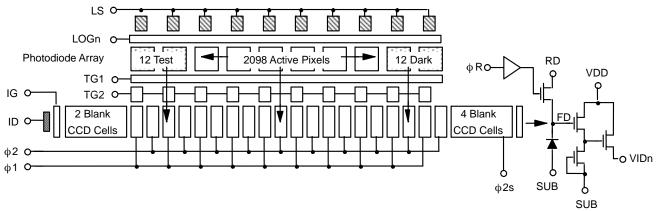

Figure 2. Single Channel Schematic

#### Exposure Control

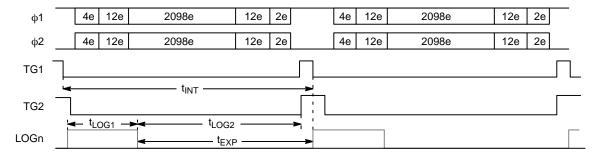

Exposure control is implemented by selectively clocking the LOG gates during portions of the scanning line time. By applying a large enough positive bias to the LOG gate, the channel potential is increased to a level beyond the 'pinning level' of the photodiode. (The 'pinning' level is the maximum channel potential that the photodiode can achieve and is fixed by the doping levels of the structure.) With TG1 in an 'off' state and LOG strongly biased, all of the photocurrent will be drawn off to the LS drain. Referring to Figure 9, one notes that the exposure can be controlled by pulsing the LOG gate to a 'high' level while TG1 is turning 'off' and then returning the LOG gate to a 'low' bias level sometime during the line scan. The effective exposure (t<sub>EXP</sub>) is the net time between the falling edge of the LOG gate and the falling edge of the TG1 gate (end of the line). Separate LOG connections for each channel are provided, enabling on-chip light source and image spectral color balancing. As a cautionary note, the switching transients of the LOG gates during line readout may inject an artifact at the sensor output. Rising edge artifacts can be avoided by switching LOG during the photodiode-to-CCD transfer period, preferably, during the TG1 falling edge. Depending on clocking speeds, the falling edge of the LOG should be synchronous with the  $\phi 1/\phi 2$  shift register readout clocks. For very fast applications, the falling edge of the LOG gate may be limited by on-chip RC delays across the array. In this case, artifacts may extend across one or more pixels. Correlated double sampling (CDS) processing of the output waveform can remove the first order magnitude of such artifacts. In high dynamic range applications, it may be advisable to limit the LOG fall times to minimize the current transients in the device substrate and limit the magnitude of the artifact to an acceptable level.

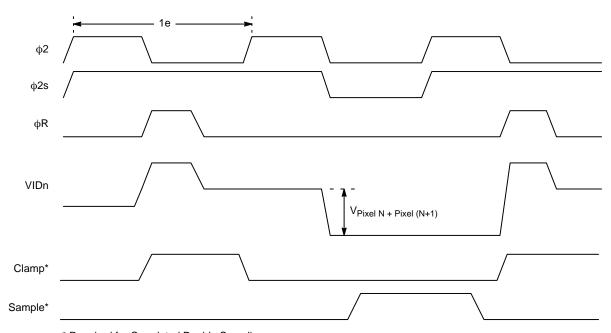

#### Pixel Summing

The effective resolution of this sensor can be varied by enabling the pixel summing feature. A separate pin is provided for the last shift register gate labeled  $\varphi$ 2s. This gate, when clocked appropriately, stores the summation of signal from adjacent pixels. This combined charge packet is then transferred onto the sense node. As an example, the sensor can be operated in 2-pixel summing mode (1,049 pixels), by supplying a  $\varphi$ 2s clock which is a 75% duty cycle signal at 1/2 the frequency of the  $\varphi$ 2 signal, and modifying the  $\varphi$ R clock as depicted in Figure 10. Applications that require full resolution mode (2,098 pixels), must tie the  $\varphi$ 2s pin to the  $\varphi$ 2 pin. Refer to Figure 9 and Figure 10 for additional details.

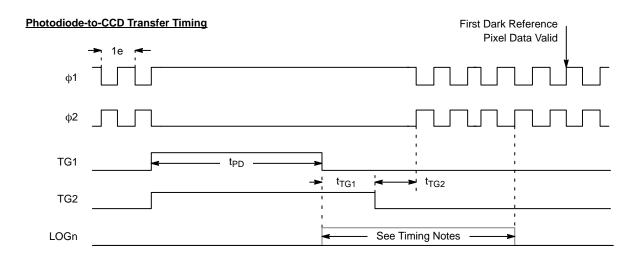

### **Image Acquisition**

During the integration period, an image is obtained by gathering electrons generated by photons incident upon the photodiodes. The charge collected in the photodiode array is a linear function of the local exposure. The charge is stored in the photodiode itself and is isolated from the CCD shift registers during the integration period by the transfer gates TG1 and TG2, which are held at barrier potentials. At the end of the integration period, the CCD register clocking is stopped with the  $\phi 1$  and  $\phi 2$  gates being held in a 'high' and 'low' state respectively. Next, the TG gates are turned 'on' causing the charge to drain from the photo-diode into the TG1 storage region. As TG1 is turned back 'off', charge is transferred through TG2 and into the  $\phi$ 1 storage region. The TG2 gate is then turned 'off', isolating the shift registers from the accumulation region once again. Complementary clocking of the  $\phi 1$  and  $\phi 2$  phases now resumes for readout of the current line of data while the next line of data is integrated.

### **Charge Transport**

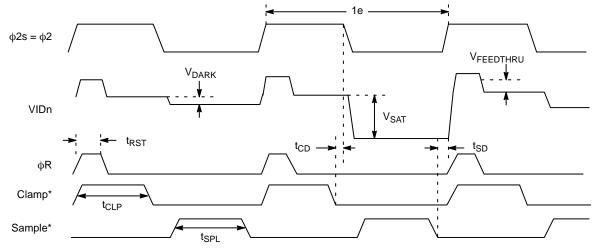

Readout of the signal charge is accomplished by two-phase, complementary clocking of the Phase 1 and Phase 2 gates ( $\phi$ 1 and  $\phi$ 2) in the horizontal (output) shift register. The register architecture has been designed for high speed clocking with minimal transport and output signal degradation, while still maintaining low (4.75 V<sub>P-P</sub> min) clock swings for reduced power dissipation, lower clock noise and simpler driver design. The data in all registers is clocked simultaneously toward the output structures. The signal is then transferred to the output structures in

a parallel format at the falling edge of the  $\varphi 2s$  clock. Resettable floating diffusions are used for the charge to voltage conversion while source followers provide buffering to external connections. The potential change on the floating diffusion is dependent on the amount of signal charge and is given by  $\Delta V_{FD} = \Delta Q \, / \, C_{FD},$  where  $\Delta V_{FD}$  is the change in potential on the floating diffusion,  $\Delta Q$  is the amount of charge, and  $C_{FD}$  is the capacitance of the floating diffusion node. Prior to each pixel output, the floating diffusion is returned to the RD level by the reset clock,  $\varphi R.$

# **Physical Description**

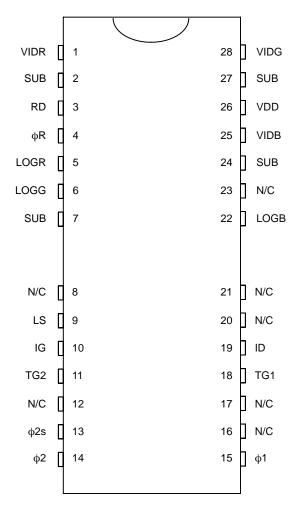

Pin Description and Device Orientation

Figure 3. KLI-2113 Pinout

**Table 4. PACKAGE PIN DESCRIPTION**

| Pin | Name | Description                              |

|-----|------|------------------------------------------|

| 1   | VIDR | Red Output Video                         |

| 2   | SUB  | Substrate                                |

| 3   | RD   | Reset Drain                              |

| 4   | φR   | Reset Clock                              |

| 5   | LOGR | Red Overflow Gate                        |

| 6   | LOGG | Green Overflow Gate                      |

| 7   | SUB  | Substrate                                |

| 8   | N/C  | No Connection                            |

| 9   | LS   | Light Shield/Exposure Drain              |

| 10  | G    | Input Gate/LOG Test Pin                  |

| 11  | TG2  | Outer Transfer Gate                      |

| 12  | N/C  | No Connection                            |

| 13  | φ2s  | Phase2 Shift Register Summing Gate Clock |

| 14  | φ2   | Phase2 Shift Register Clock              |

| Pin | Name | Description                 |

|-----|------|-----------------------------|

| 15  | φ1   | Phase1 Shift Register Clock |

| 16  | N/C  | No Connection               |

| 17  | N/C  | No Connection               |

| 18  | TG1  | Inner Transfer Gate         |

| 19  | ID   | Input Diode Test Pin        |

| 20  | N/C  | No Connection               |

| 21  | N/C  | No Connection               |

| 22  | LOGB | Blue Overflow Gate          |

| 23  | N/C  | No Connection               |

| 24  | SUB  | Substrate                   |

| 25  | VIDB | Blue Output Video           |

| 26  | VDD  | Amplifier Supply            |

| 27  | SUB  | Substrate                   |

| 28  | VIDG | Green Output Video          |

#### **IMAGING PERFORMANCE**

# **Typical Operational Conditions**

Specifications given under nominal operating conditions @25°C ambient, f<sub>CLK</sub> =2 MHz and nominal external VIDn load resistors unless otherwise specified.

**Table 5. SPECIFICATIONS**

| Description                                      | Symbol                      | Min.        | Nom.           | Max.        | Units                | Notes                       | Verification<br>Plan |

|--------------------------------------------------|-----------------------------|-------------|----------------|-------------|----------------------|-----------------------------|----------------------|

| Saturation Output Voltage                        | V <sub>SAT</sub>            | -           | 2.0            | _           | V <sub>P-P</sub>     | 1, 7                        | Die <sup>8</sup>     |

| Output Sensitivity                               | $\Delta V_{O}/\Delta N_{e}$ | -           | 11.5           | _           | μV/e <sup>-</sup>    | 7                           | Design <sup>9</sup>  |

| Saturation Signal Charge                         | N <sub>e,SAT</sub>          | -           | 170k           | -           | e <sup>-</sup>       |                             | Design <sup>9</sup>  |

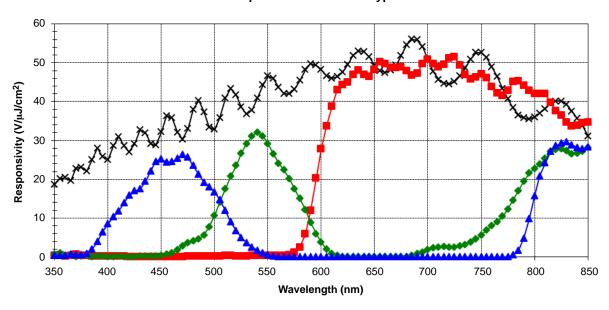

| Responsivity<br>@ 650 nm<br>@ 540 nm<br>@ 460 nm | R                           | -<br>-<br>- | 50<br>32<br>25 | -<br>-<br>- | V/μJ/cm <sup>2</sup> | 2, 7                        | Design <sup>9</sup>  |

| Output Buffer Bandwidth                          | f <sub>-3dB</sub>           | -           | 75             | _           | MHz                  | @ C <sub>LOAD</sub> = 10 pF | Design <sup>9</sup>  |

| Dynamic Range                                    | DR                          | -           | 76             | _           | dB                   | 3                           | Design <sup>9</sup>  |

| Dark Current                                     | I <sub>DARK</sub>           | -           | 0.02           | _           | pA/Pixel             | 4                           | Die <sup>8</sup>     |

| Charge Transfer Efficiency                       | CTE                         | -           | 0.99999        | -           | _                    | 5                           | Design <sup>9</sup>  |

| Lag                                              | L                           | _           | 0.6            | 1           | %                    | 1 <sup>st</sup> Field       | Design <sup>9</sup>  |

| DC Output Offset                                 | V <sub>ODC</sub>            | 6           | 7              | 9           | V                    | 7                           | Design <sup>9</sup>  |

| Photoresponse Uniformity                         | PRNU                        | -           | 5              | 10          | % p-p                | 6                           | Die <sup>8</sup>     |

| Register Clock Capacitance                       | $C_{\varphi}$               | -           | 500            | -           | pF                   | per Phase                   | Design <sup>9</sup>  |

| Transfer Gate Capacitance                        | C <sub>TG</sub>             | -           | 400            | -           | pF                   |                             | Design <sup>9</sup>  |

- 1. Defined as the maximum output level achievable before linearity or PRNU performance is degraded.

- 2. With color filter. Values specified at filter peaks. 50% bandwidth =  $\pm 30$  nm.

- 3. This device utilizes 2-phase clocking for cancellation of driver displacement currents. Symmetry between φ1 and φ2 phases must be maintained to minimize clock noise.

- 4. Dark current doubles approximately every 9°C.

5. Measured per transfer. For total line h < (0.99999)<sup>4256</sup> = 0.96

- 6. Low frequency response across array with color filter array.

- 7. Decreasing external VIDn load resistors to improve signal bandwidth will decrease these parameters.

- 8. A parameter that is measured on every sensor during production testing.

- 9. A parameter that is quantified during the design verification activity.

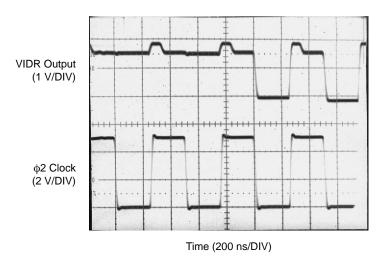

# **TYPICAL PERFORMANCE CURVES**

# (2 MHz Operation, Emitter Follower Buffered, 3/4 V<sub>SAT</sub>, Dark to Bright Transition)

Figure 4. Output Waveforms

### KLI-2113 Spectral Response Improved Color Filter – Type II

Figure 5. Typical Responsivity

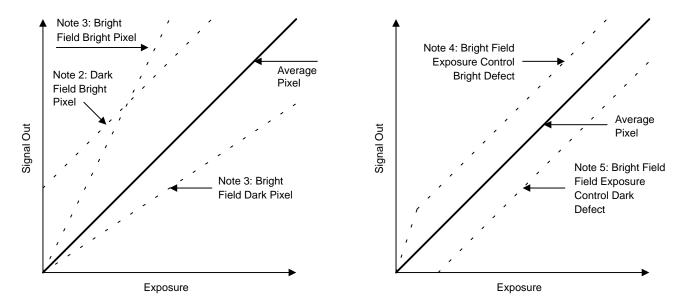

#### **DEFECT DEFINITIONS**

#### **Table 6. OPERATING CONDITION SPECIFICATIONS**

(Test Conditions: T = 25°C,  $f_{CLK} = 2$  MHz,  $t_{INT} = 1.066$  ms)

| Field  | Defect Type      | Threshold | Units | Notes   | Number |

|--------|------------------|-----------|-------|---------|--------|

| Dark   | Bright           | 8.0       | mV    | 1, 2    | 0      |

| Bright | Bright/Dark      | 10        | %     | 1, 3    | 0      |

| Bright | Exposure Control | 4.0       | mV    | 1, 4, 5 | ≤ 16   |

- 1. Defective pixels will be separated by at least one non-defective pixel within and across channels.

- 2. Pixels whose response is greater than the average response by the specified threshold. See Figure 6 below.

- Pixels whose response is greater or less than the average response by the specified threshold. See Figure 6 below.

Pixels whose response deviates from the average pixel response by the specified threshold when operating in exposure control mode. See Figure 6 below.

- 5. Defect coordinates are available upon request.

Figure 6. Illustration of Defect Classifications

#### **OPERATION**

**Table 7. ABSOLUTE MAXIMUM RATINGS**

| Description             | Symbol                | Minimum | Maximum | Unit | Notes |

|-------------------------|-----------------------|---------|---------|------|-------|

| Gate Pin Voltage        | $V_{GATE}$            | -0.5    | 16      | V    | 1, 2  |

| Pin-to-Pin Voltage      | V <sub>PIN-PIN</sub>  | -       | 16      | V    | 1, 3  |

| Diode Pin Voltage       | V <sub>DIODE</sub>    | -0.5    | 16      | V    | 1, 4  |

| Output Bias Current     | I <sub>DD</sub>       | -       | -10     | mA   | 5     |

| Output Load Capacitance | C <sub>VID,LOAD</sub> | -       | 15      | pF   |       |

| CCD Clocking Frequency  | f <sub>C</sub>        | -       | 20      | MHz  | 6     |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

- 1. Referenced to substrate voltage.

- 2. Includes pins: φ1, φ2, φ2s, TĞ1, TG2, φR, IG, and LOGn.

- 3. Voltage difference (either polarity) between any two pins.

- 4. Includes pins: VIDn, RD, VDD, LS and ID.

- 5. Care must be taken not to short output pins to ground during operation as this may cause serious damage to the output structures.

- 6. Charge transfer efficiency will degrade at frequencies higher than the nominal (2 MHz) clocking frequency. VIDn load resistor values may need to be decreased as well to achieve required output bandwidths.

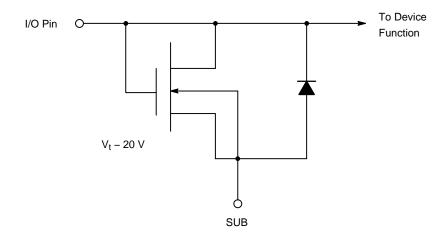

Device Input ESD Protection Circuit (Schematic)

**CAUTION:** To allow for maximum performance, this device contains limited I/O protection and may be sensitive to electrostatic induced damage. Devices should be installed in accordance with strict ESD handling procedures!

**Figure 7. ESD Protection Circuit**

# **DC Bias Operating Conditions**

**Table 8. DC BIAS OPERATING CONDITIONS**

| Description                 | Symbol           | Minimum | Nominal | Maximum | Units | Notes |

|-----------------------------|------------------|---------|---------|---------|-------|-------|

| Substrate                   | V <sub>SUB</sub> | -       | 0       | -       | V     |       |

| Reset Drain Bias            | $V_{RD}$         | 11.5    | 12.0    | 12.5    | V     |       |

| Output Buffer Supply        | $V_{DD}$         | 11.5    | 12.0    | 12.5    | V     |       |

| Light Shield/Drain Bias     | V <sub>LS</sub>  | 11.5    | 12.0    | 12.5    | V     |       |

| Output Bias Current/Channel | I <sub>DDn</sub> | -4.0    | -6.0    | -8.0    | mA    | 1     |

| Test Pin – Input Gate/LOG   | $V_{IG}$         | -       | 12.0    | -       | V     |       |

| Test Pin – Input Diode      | V <sub>ID</sub>  | _       | 12.0    | -       | V     |       |

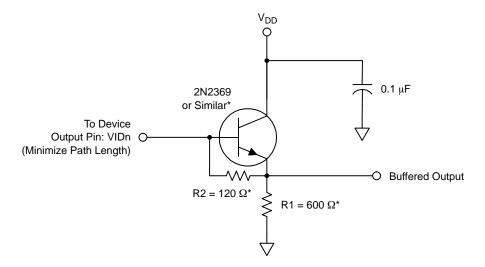

<sup>1.</sup> A current sink must be supplied for each output. Load capacitance should be minimized so as not to limit bandwidth. See Figure 8.Choose values optimized for specific operating frequency, but R2 should not be less than 75  $\Omega$ .

# Typical Output Bias/Buffer Circuit

Figure 8. Typical Output Bias/Buffer Circuit

# **AC Operating Conditions**

# **Table 9. CLOCK LEVELS**

| Description             | Symbol                                   | Minimum | Nominal | Maximum | Units | Notes |

|-------------------------|------------------------------------------|---------|---------|---------|-------|-------|

| CCD Readout Clocks High | $V_{\phi 1H}, V_{\phi 2H}, V_{\phi 2sH}$ | 4.75    | 5.0     | 5.25    | V     |       |

| CCD Readout Clocks Low  | $V_{\phi 1L}, V_{\phi 2L}, V_{\phi 2SL}$ | -0.1    | 0.0     | 0.1     | V     |       |

| Transfer Clocks High    | V <sub>TG1H</sub> , V <sub>TG2H</sub>    | 4.75    | 5.0     | 5.25    | V     |       |

| Transfer Clocks Low     | V <sub>TG1L</sub> , V <sub>TG2L</sub>    | -0.1    | 0.0     | 0.1     | V     |       |

| Reset Clock High        | $V_{\phi RH}$                            | 4.75    | 5.0     | 5.25    | V     |       |

| Reset Clock Low         | $V_{\phi RL}$                            | -0.1    | 0.0     | 0.1     | V     |       |

| Exposure Clocks High    | V <sub>LOG1H</sub> , V <sub>LOG2H</sub>  | 4.75    | 5.0     | 5.25    | V     | 1     |

| Exposure Clocks Low     | V <sub>LOG1L</sub> , V <sub>LOG2L</sub>  | -0.1    | 0.0     | 0.1     | V     | 1     |

<sup>1.</sup> Tie pin to 0  $\mbox{V}$  for applications where exposure control is not used.

# **Table 10. AC TIMING LEVELS**

| Description                | Symbol                                  | Minimum | Nominal | Maximum | Units | Notes   |

|----------------------------|-----------------------------------------|---------|---------|---------|-------|---------|

| CCD Element Duration       | 1e <sup>-</sup> (= 1/f <sub>CLK</sub> ) | 50      | 50      | _       | ns    |         |

| Line/Integration Period    | 1L (= t <sub>INT</sub> )                | 0.108   | 1.066   | _       | ms    |         |

| PD-CCD Transfer Period     | t <sub>PD</sub>                         | 1.0     | -       | -       | μS    |         |

| Transfer Gate 1 Clear      | t <sub>TG1</sub>                        | 500     | _       | _       | ns    |         |

| Transfer Gate 2 Clear      | t <sub>TG2</sub>                        | 500     | _       | _       | ns    |         |

| LOGGate Duration           | t <sub>LOG1</sub>                       | 1       | _       | _       | μS    |         |

| LOGGate Clear              | t <sub>LOG2</sub>                       | 1       | -       | _       | μS    |         |

| Reset Pulse Duration       | t <sub>RST</sub>                        | 9       | -       | -       | ns    |         |

| Clamp to φ2 Delay          | t <sub>CD</sub>                         | 5       | _       | _       | ns    | 1       |

| Sample to Reset Edge Delay | t <sub>SD</sub>                         | 5       | _       | _       | ns    | 1       |

| CCD Clock Rise Time        | t <sub>R</sub>                          | _       | 30      | _       | ns    | Typical |

<sup>1.</sup> Recommended delays for Correlated Double Sampling of output.

#### **TIMING**

#### **Line Timing**

# **Output Timing (Full Resolution Mode)**

<sup>\*</sup> Required for Correlated Double Sampling.

Figure 9. Normal Mode Timing

# **Output Timing (2-Pixel Summing Mode)**

<sup>\*</sup> Required for Correlated Double Sampling.

Figure 10. Binning Mode Timing

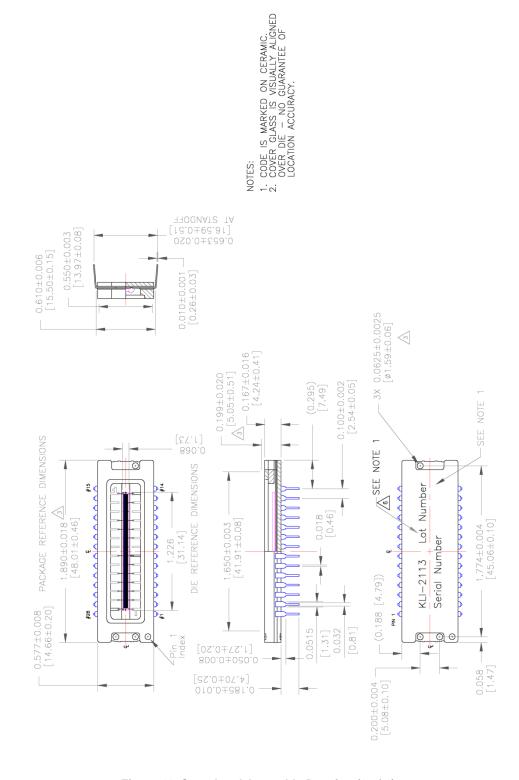

#### **MECHANICAL INFORMATION**

#### **Completed Assembly**

Figure 11. Completed Assembly Drawing (1 of 4)

# 1. DIE LOCATION SPECIFIED BY DETAILS "A" AND "B". 2. DIE IS CENTERED IN PACKAGE CAVITY. COLOR SENSOR TOP OF IMAGER TO BOTTOM OF PACKAGE 109±0.010 TOP OF IMAGER TO [2.77±.25] OF COVER GLASS ([+2.5] 001.0) [X5] B 0.100±0.010 $\bigoplus$ SEE DETAIL "B" (0.0032 [0.081]) GREEN CFA WIDTH ď SEE NOTE ď ( IMAGING PIXEL **C (** CFA **C** A 0.311±0.010 7.89±0.26mm EDGE OF GREEN C 7.96±0.26mm CENTER OF 1ST A 0.313±0.010 € SEE DETAIL "A" € € DETAIL "A" (0.887 [22.53]) [2X] **C** € (7.56mm) OF BLACK CFA A (0.298) **C** B 0.100±0.010 2.54±0.26mm CENTERLINE OF 1ST GREEN PIXEL

Figure 12. Completed Assembly Drawing (2 of 4)

# 1. DIE LOCATION SPECIFIED BY DETAILS "A" AND "B". 2. DIE IS CENTERED IN PACKAGE CAVITY. TOP OF IMAGER TO BOTTOM OF PACKAGE MONO SENSOR 0.109±0.010 TOP OF IMAGER TO TOP [2.77±.25] OF COVER GLASS - 0.090±0.010 [2.28±.25] (E)0.100±0.010 2.54±0.26mm CENTERLINE OF CENTER PIXEL ARRAY ([+2.5] 001.0) [X5] SEE DETAIL "B" € SEE NOTE DETAIL "B" ď <u>ر</u> 7.96±0.26mm CENTER OF 1ST IMAGING PIXEL 7.95±0.26mm EDGE OF 1ST IMAGING PIXEL **C** 4 A 0.313±0.010 A 0.313±0.010 € -SEE DETAIL "A" ď C DETAIL "A" (0.887 [22.53]) [2X] C C 4 (B | 0.100±0.010 | 2.54±0.26mm | CENTERLINE OF CENTER PIXEL ARRAX m

Figure 13. Completed Assembly Drawing (3 of 4)

# CENTER DIE VERTICALLY ON SILVER D/A PAD. CENTER DIE HORIZONTALLY WITH RESPECT TO OUTER EDGES OF PACKAGE BOND FINGERS. IF DIE IS LONGER OR SHORTER THAN OUTER EDGES OF BOND FINGERS THEN SPLIT THE DIFFERENCE BETWEEN THE TWO ENDS SO THAT THE DIE IS CENTERED IN THE CAVITY. (X, Y) COORDINATES SHOWN ARE FOR MEASUREMENT VERIFICATION AND ARE RELATIVE TO THE DATUMS THROUGH THE CENTER OF THE PACKAGE HOLES. MONO SENSOR IS LOCATED IN THE SAME LOCATION OF THE PACKAGE AND HAS THE SAME TARGETS AND FIDUCIALS BUT NO COLOR CFA. COLOR SENSOR NOTES: Center of Right Target (37.908, 3.208)mm DETAIL "D" 6 SEE DETAIL (0.0130 [0.329]) EDGE OF BLACK TO EDGE OF GREEN C OF 1S PIXEL ( **C C** Ъ DETAIL "C" Center of Left Target — (7.152, 3.208)mm **(** SEE DETAIL C b **@** ( Ь Corner of (Red) CFA (7.559, 1.989)mm **(** þ 4 ⋖ ىلى В

Figure 14. Completed Assembly Drawing (4 of 4)

#### **REFERENCES**

For information on ESD and cover glass care and cleanliness, please download the *Image Sensor Handling* and Best Practices Application Note (AN52561/D) from www.onsemi.com.

For information on soldering recommendations, please download the Soldering and Mounting Techniques Reference Manual (SOLDERRM/D) from www.onsemi.com.

For quality and reliability information, please download the *Quality & Reliability* Handbook (HBD851/D) from www.onsemi.com.

For information on device numbering and ordering codes, please download the *Device Nomenclature* technical note (TND310/D) from www.onsemi.com.

For information on Standard terms and Conditions of Sale, please download <u>Terms and Conditions</u> from www.onsemi.com.

ON Semiconductor and the unare registered trademarks of Semiconductor Components Industries, LLC (SCILLC) or its subsidiaries in the United States and/or other countries. SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/sike/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regardin

#### **PUBLICATION ORDERING INFORMATION**

LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303–675–2175 or 800–344–3860 Toll Free USA/Canada Fax: 303–675–2176 or 800–344–3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support:

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81-3-5817-1050 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative

OOO «ЛайфЭлектроникс" "LifeElectronics" LLC

ИНН 7805602321 КПП 780501001 P/C 40702810122510004610 ФАКБ "АБСОЛЮТ БАНК" (ЗАО) в г.Санкт-Петербурге К/С 3010181090000000703 БИК 044030703

Компания «Life Electronics» занимается поставками электронных компонентов импортного и отечественного производства от производителей и со складов крупных дистрибьюторов Европы, Америки и Азии.

С конца 2013 года компания активно расширяет линейку поставок компонентов по направлению коаксиальный кабель, кварцевые генераторы и конденсаторы (керамические, пленочные, электролитические), за счёт заключения дистрибьюторских договоров

#### Мы предлагаем:

- Конкурентоспособные цены и скидки постоянным клиентам.

- Специальные условия для постоянных клиентов.

- Подбор аналогов.

- Поставку компонентов в любых объемах, удовлетворяющих вашим потребностям.

- Приемлемые сроки поставки, возможна ускоренная поставка.

- Доставку товара в любую точку России и стран СНГ.

- Комплексную поставку.

- Работу по проектам и поставку образцов.

- Формирование склада под заказчика.

- Сертификаты соответствия на поставляемую продукцию (по желанию клиента).

- Тестирование поставляемой продукции.

- Поставку компонентов, требующих военную и космическую приемку.

- Входной контроль качества.

- Наличие сертификата ISO.

В составе нашей компании организован Конструкторский отдел, призванный помогать разработчикам, и инженерам.

Конструкторский отдел помогает осуществить:

- Регистрацию проекта у производителя компонентов.

- Техническую поддержку проекта.

- Защиту от снятия компонента с производства.

- Оценку стоимости проекта по компонентам.

- Изготовление тестовой платы монтаж и пусконаладочные работы.

Тел: +7 (812) 336 43 04 (многоканальный) Email: org@lifeelectronics.ru